(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-335751

(P2007-335751A)

(43) 公開日 平成19年12月27日(2007.12.27)

| (51) Int.C1.                 | F 1        | テーマコード(参考) |       |

|------------------------------|------------|------------|-------|

| <b>HO1L 27/146 (2006.01)</b> | HO1L 27/14 | A          | 4M118 |

| <b>HO4N 5/335 (2006.01)</b>  | HO4N 5/335 | S          | 5C024 |

|                              | HO4N 5/335 | E          |       |

審査請求 未請求 請求項の数 5 O L (全 10 頁)

|           |                              |                |           |

|-----------|------------------------------|----------------|-----------|

| (21) 出願番号 | 特願2006-167785 (P2006-167785) | (71) 出願人       | 000003078 |

| (22) 出願日  | 平成18年6月16日 (2006.6.16)       | 株式会社東芝         |           |

|           |                              | 東京都港区芝浦一丁目1番1号 |           |

|           |                              | (74) 代理人       | 100058479 |

|           |                              | 弁理士 鈴江 武彦      |           |

|           |                              | (74) 代理人       | 100091351 |

|           |                              | 弁理士 河野 哲       |           |

|           |                              | (74) 代理人       | 100088683 |

|           |                              | 弁理士 中村 誠       |           |

|           |                              | (74) 代理人       | 100108855 |

|           |                              | 弁理士 蔵田 昌俊      |           |

|           |                              | (74) 代理人       | 100075672 |

|           |                              | 弁理士 峰 隆司       |           |

|           |                              | (74) 代理人       | 100109830 |

|           |                              | 弁理士 福原 淑弘      |           |

最終頁に続く

(54) 【発明の名称】 固体撮像装置

## (57) 【要約】

【課題】増幅型MOSイメージセンサにおいて、感光画素領域(撮像領域)に強度の光が入射した場合に光電変換部で発生したキャリア(ブルーミング信号)がOB画素領域の光電変換部に侵入することを回避し、暗時レベルを安定化させる。

【解決手段】一導電型の半導体基板42上に光電変換部44と信号走査回路を含む単位画素を配置してなる感光画素領域31と、感光画素領域の一部に形成され、暗時レベル設定用のオプティカルブラック画素を配置してなるOB画素領域32と、感光画素領域の各単位画素から信号を読み出す信号線47と、OB画素領域で半導体基板に形成され、半導体基板と同一導電型であってその不純物濃度より高い不純物濃度を有するバリア層52とを具備する。

【選択図】 図1

図1

**【特許請求の範囲】****【請求項 1】**

一導電型の半導体基板上に光電変換部と信号走査回路を含む単位画素を配置してなる画素領域と、

前記画素領域の一部に形成され、暗時レベル設定用のオプティカルブラック画素を配置してなるオプティカルブラック画素領域と、

前記画素領域の各単位画素から信号を読み出す信号線と、

前記オプティカルブラック画素領域で前記半導体基板に形成され、前記半導体基板と同一導電型であって前記半導体基板の不純物濃度より高い不純物濃度を有するバリア層とを具備することを特徴とする固体撮像装置。

10

**【請求項 2】**

前記バリア層は、前記オプティカルブラック画素領域の下部に形成されていることを特徴とする請求項 1 記載の固体撮像装置。

**【請求項 3】**

前記バリア層は、さらに前記オプティカルブラック画素領域内の有効オプティカルブラック画素領域を平面的に囲む周辺部にも形成されていることを特徴とする請求項 2 記載の固体撮像装置。

**【請求項 4】**

前記オプティカルブラック画素領域の周辺部に形成されているバリア層の領域内に、前記オプティカルブラック画素領域の一部のオプティカルブラック画素が存在することを特徴とする請求項 3 記載の固体撮像装置。

20

**【請求項 5】**

前記バリア層の周辺部に、前記半導体基板とは逆導電型のドレイン領域が形成されていることを特徴とする請求項 1 記載の固体撮像装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、固体撮像装置に係り、特に同一基板上に多種の回路を持つMOS(絶縁ゲート型)イメージセンサに関するもので、例えば増幅型MOSイメージセンサに使用されるものである。

30

**【背景技術】****【0002】**

従来の増幅型MOSイメージセンサは、感光画素領域(撮像領域)、特にその周辺部に強度の光が入射された場合に、単位画素の光電変換部から溢れたキャリア(電子)が遮光画素領域(オプティカルブラック領域、以下OB領域と称する)の光電変換部に流れ込み、暗時レベル(黒基準レベル)を変動させ、ブルーミングが発生するという問題がある。具体的には、暗時レベルが変動すると、MOSイメージセンサの出力信号を再生した画面上に横帯画像が発生する。

**【0003】**

この問題を回避するため、CCD(Charge Coupled Device:電荷結合像素子)イメージセンサではN基板を使用し、縦型オーバードレイン構造を形成し、光電変換部から溢れた電子を基板側に捨てている。しかし、MOSイメージセンサは、像素子、走査回路、レジスタ回路、タイミング回路、A/Dコンバータ、コマンド回路、D/Aコンバータ、DSP(デジタルシグナルプロセッサ)などの多種の回路を同一基板上に形成し、システムを縮小化すると共に安価の製品を提供できるというメリットを活かすため、他の回路に適した基板を使用することが必要である。したがって、MOSイメージセンサでは、CCDイメージセンサと同様のN基板を使用して縦型オーバードレイン構造を形成することができず、暗時レベルの変動が問題となっている。

40

**【0004】**

なお、特許文献1には、黒基準レベルの変動を防ぐために、OB領域の全部に高濃度の

50

Nウェルを形成する点が開示されている。

【特許文献1】特開2004-39794号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

本発明は前記した従来の問題点を解決すべくなされたもので、感光画素領域（撮像領域）に強度の光が入射した場合に光電変換部で発生したキャリア（ブルーミング信号）がOB画素領域の光電変換部に侵入することを回避でき、暗時レベルが安定し、信号クランプを確実に行うことができる固体撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の固体撮像装置は、一導電型の半導体基板上に光電変換部と信号走査回路を含む単位画素セルを配置してなる画素領域と、前記画素領域の一部に形成され、暗時レベル設定用のオプティカルブラック画素を配置してなるオプティカルブラック画素領域と、前記画素領域の各単位画素から信号を読み出す信号線と、前記オプティカルブラック画素領域で前記半導体基板に選択的に形成され、前記半導体基板と同一導電型であって前記半導体基板の不純物濃度より高い不純物濃度を有するバリア層とを具備する。

【発明の効果】

【0007】

本発明の固体撮像装置によれば、感光画素領域（撮像領域）に強度の光が入射した場合に光電変換部で発生したキャリア（ブルーミング信号）がOB画素領域の光電変換部に侵入することを回避でき、暗時レベルが安定し、入力信号を確実にクランプすることができる。

【発明を実施するための最良の形態】

【0008】

以下、図面を参照して本発明の実施形態を説明する。この説明に際して、全図にわたり共通する部分には共通する参照符号を付す。

【0009】

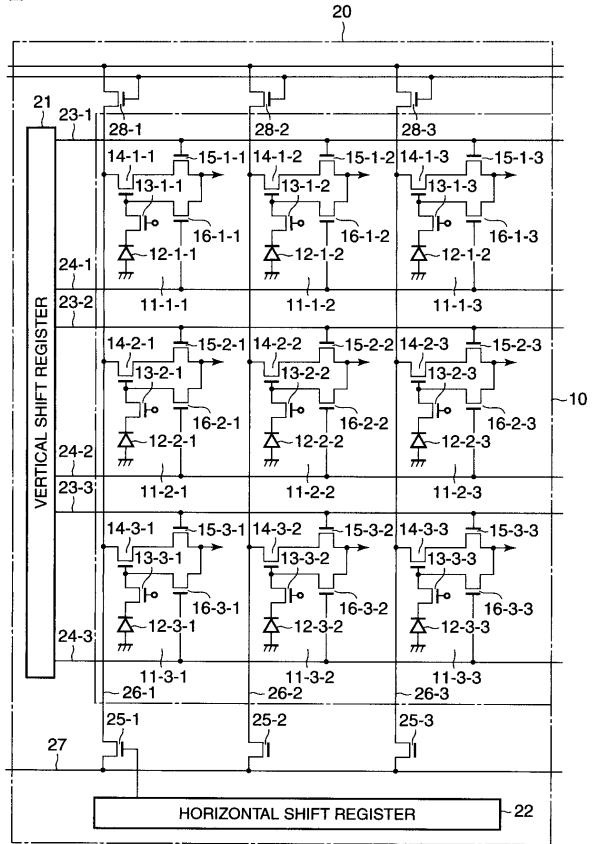

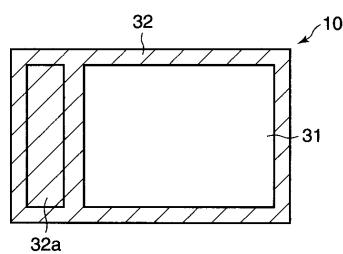

まず、図8および図9を参照して増幅型MOSイメージセンサの一般的な構成を簡単に説明しておく。図8は増幅型MOSイメージセンサの一例を概略的に示す回路図であり、図9は図8の増幅型MOSイメージセンサの平面図である。

【0010】

図8において、10は画素領域であり、20は周辺回路領域である。画素領域10の感光画素領域（撮像領域）31には、複数の単位画素（単位セル）11が二次元状に配列されている。なお、図8では、表示の簡単化のために例えば3行×3列分の単位セル11-1-1～11-3-3が示されている。撮像領域31には、単位セルの他に水平アドレス線23-1、23-2、23-3、リセット線24-1、24-2、24-3、垂直信号線26-1、26-2、26-3が設けられている。

【0011】

周辺回路領域20には、画素領域10を走査する垂直シフトレジスタ（VERTICAL SHIFT REGISTER）21、水平シフトレジスタ（HORIZONTAL SHIFT REGISTER）22、垂直信号線26-1、26-2、26-3、負荷トランジスタ28-1、28-2、28-3、水平選択トランジスタ25-1、25-2、25-3、水平信号線27が設けられている。

【0012】

各単位セル11-1-1～11-3-3は、フォトダイオード12-1-1、12-1-2、12-1-3と、フォトダイオードの出力信号（光電変換信号）を読み出す読み出しトランジスタ13-1-1、13-1-2、13-1-3と、読み出しトランジスタの出力信号を増幅する増幅トランジスタ14-1-1、14-1-2、14-1-3と、増幅トランジスタの出力信号を読み出す垂直ラインを選択する垂直選択トランジスタ15-1-1、15-1-2、15-1-3と、フォトダイオードの出力信号電荷をリセットす

10

20

30

40

50

るリセットトランジスタ 16-1-1、16-1-2、16-1-3 からなる。

【0013】

水平アドレス線 23-1、23-2、23-3 は、周辺回路領域 20 の垂直シフトレジスタ 21 から水平方向に配線され、垂直選択トランジスタ 15-1-1、15-1-2、15-1-3 のゲートに接続され、信号を読み出すラインを指定する。

【0014】

リセット線 24-1、24-2、24-3 は、リセットトランジスタのゲートに接続されている。

【0015】

垂直信号線 26-1、26-2、26-3 は、増幅トランジスタ 14-1-1、14-1-2、14-1-3 のソースに接続され、それぞれの一端には周辺回路領域 20 の負荷トランジスタ 28-1、28-2、28-3 が設けられており、他の一端は周辺回路領域 20 の水平選択トランジスタ 25-1、25-2、25-3 を介して水平信号線 27 に結線されている。水平選択トランジスタ 25-1、25-2、25-3 は、水平シフトレジスタ 22 から供給される選択パルスにより選択される。

【0016】

図 9 の平面図において、画素領域 10 には、感光画素領域（撮像領域）31 及び遮光画素（オプティカルブラック画素：OB 画素）領域 32 が形成されている。OB 画素領域 32 は有効黒基準画素領域（有効 OB 画素領域）32a を含み、有効 OB 画素領域 32a で生成された信号は、暗時のレベル（黒基準レベル）を決め、入力信号を適切にクランプするため使用される。OB 画素領域 32 には、図示しないが、複数の OB 画素が二次元状に配列されている。各 OB 画素は単位画素と同様の構成を有する。

【0017】

<第 1 実施形態>

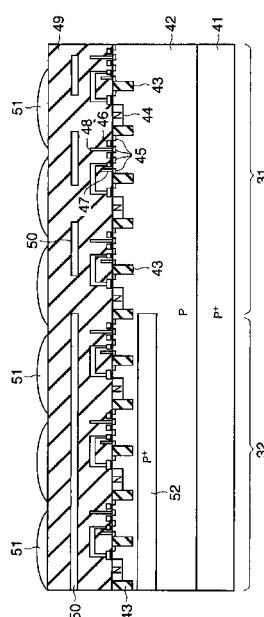

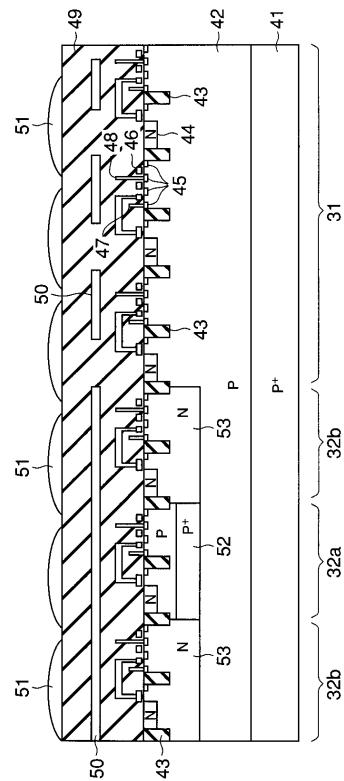

図 1 は、本発明の第 1 実施形態に係る増幅型 MOS イメージセンサの一部であり、例えば図 9 中の感光画素領域（撮像領域）31 と OB 画素領域 32 の一部を取り出した断面構造を示している。

【0018】

図 1 に示す増幅型 MOS イメージセンサにおいて、41 は P 型不純物濃度が比較的高い P<sup>+</sup> 型シリコン基板、42 は P<sup>+</sup> 型シリコン基板 41 よりも P 型不純物濃度が低い P 型シリコン基板である。P<sup>+</sup> 型シリコン基板 41 と P 型シリコン基板 42 からなる P on P<sup>+</sup> 型シリコン基板は、基板内部で光電変換された信号キャリアを低濃度の P 型シリコン基板 42 側に集める特徴を持つ。P 型シリコン基板 42 の表層部には、複数の単位画素領域および OB 画素領域をそれぞれ素子分離する素子分離領域 43 が形成されている。さらに、P 型シリコン基板 42 の各画素領域には、フォトダイオードの光電変換部（N 領域）44、及び拡散領域 45 が形成されている。

【0019】

さらに、P 型シリコン基板 42 上には、各トランジスタのゲート絶縁膜、ゲート電極 46、垂直信号線 47、ドレイン線 48、絶縁層 49、遮光膜 50 などが形成され、絶縁層 49 の最上層上にマイクロレンズ 51 が形成されている。この場合、遮光膜 50 は、OB 画素領域（図 9 中の符号 32、32a）の全面を覆うとともに、感光画素領域（図 9 中の撮像領域 31）の単位画素に光が入射するように一部が開口されている。

【0020】

さらに、第 1 の実施形態では、OB 画素領域 32 の下部の P 型シリコン基板 42 中に、P 型シリコン基板 42 と同一導電型であって P 型シリコン基板 42 の不純物濃度よりも高い不純物濃度（例えば P<sup>+</sup> 型シリコン基板 41 の不純物濃度と同等以上）を有する P<sup>+</sup> 型バリア層 52 が形成されている。この P<sup>+</sup> 型バリア層 52 は、例えば 1500 kV の加速電圧で P 型不純物をイオン注入することによって形成できる。なお、図 1 では P<sup>+</sup> 型バリア層 52 と素子分離領域 43 との間が離れて形成されているが、両者が接するように P<sup>+</sup> 型バリア層 52 と素子分離領域 43 とが形成されていてもよい。

10

20

30

40

50

## 【0021】

図1の増幅型MOSイメージセンサは、OB画素領域32の下部にP型シリコン基板42より高濃度のP<sup>+</sup>型バリア層52を局在させた構造を有する。このような構造によれば、P<sup>+</sup>型バリア層52は、感光画素領域に強い光が入射されて、光電変換された電子がOB画素領域の光電変換部へ侵入することを防ぐことができる。したがって、OB画素領域で暗時レベルの信号のみを安定して生成することができ、偽信号が暗時レベルに飛び込むことによって横筋などが発生するという不良を低減させることができる。また、P<sup>+</sup>型バリア層52をOB画素領域32の下部に局在させているので、P<sup>+</sup>型バリア層52がOB画素領域32のP型シリコン基板42の表面に影響せず、OB画素領域の全域に感光画素領域31と同様の特性を有する画素構造を採用することができる。

10

## 【0022】

## &lt;第2実施形態&gt;

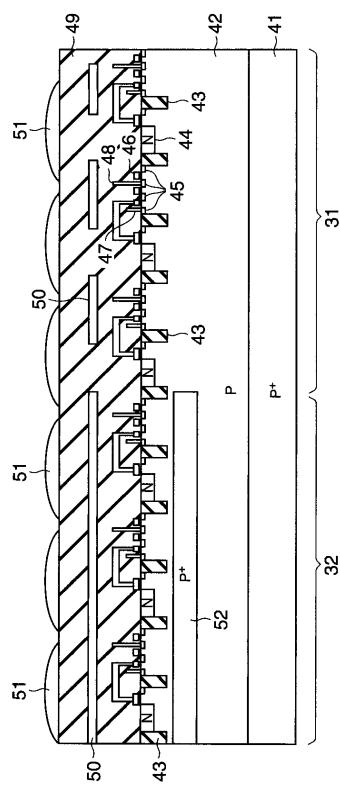

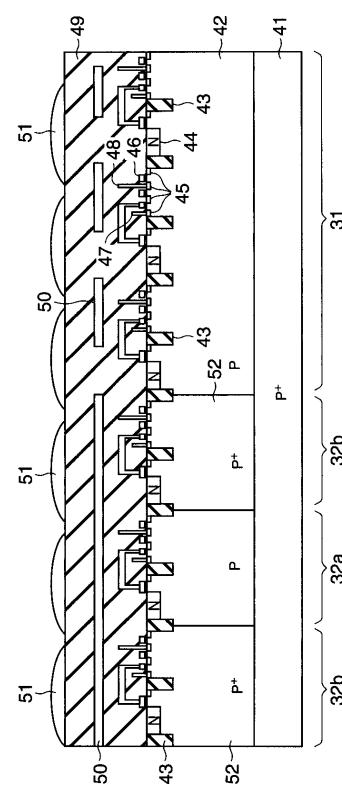

図2は、本発明の第2実施形態に係る増幅型MOSイメージセンサの一部を示す断面図である。OB画素領域32は、有効OB画素領域32a以外に、基準信号を得るためのダミーOB画素領域32bを含む。図2に示す増幅型MOSイメージセンサは、図1のイメージセンサと同様に、OB画素領域32の下部のP型シリコン基板42中に、P型シリコン基板42と同一導電型であってP型シリコン基板42の不純物濃度よりも高い不純物濃度を有するP<sup>+</sup>型バリア層52が形成されている。この場合、OB画素領域32のうちで有効OB画素領域32a以外のダミーOB画素32bの下部に、P型シリコン基板42と同一導電型であってP型シリコン基板42の不純物濃度よりも高い不純物濃度を有するP<sup>+</sup>型バリア層52が形成されている。換言すれば、P型シリコン基板42中には、OB画素領域内の有効OB画素領域32aを平面的に囲む周辺部にP<sup>+</sup>型バリア層52が形成されており、このP<sup>+</sup>型バリア層52の領域内にダミーOB画素が形成されている。

20

## 【0023】

このような構造のP<sup>+</sup>型バリア層52は、有効OB画素領域32aの下部では例えイオン注入によって実現することができ、ダミーOB画素32bの下部では、熱拡散または複数回のイオン注入によって実現することができる。

30

## 【0024】

なお、説明の都合上、図2中では有効OB画素領域32aには1つの画素のみが形成されている場合を示しているが、実際は複数の画素が形成されている。また、P<sup>+</sup>型バリア層52の形成領域は、OB画素領域において画素の二次元配列が始まる端部の列に存在していてもよく、あるいは、OB画素領域において画素の二次元配列が始まる端部から数列内側に存在していてもよい。また、P<sup>+</sup>型バリア層52は、その効果が有効であれば、その形成領域に形成される画素列は1列でも複数列であってもよい。

30

## 【0025】

図2の増幅型MOSイメージセンサは、OB画素領域を平面的に囲むようにP<sup>+</sup>型バリア層52を形成した構造を有するので、図1の固体撮像装置と同様の効果が得られる。即ち、感光画素領域31に強い光が入射されて、光電変換された電子がOB画素領域の光電変換部へ侵入することを防ぐことができる。したがって、OB画素領域で暗時レベルの信号のみを安定して生成でき、偽信号が暗時レベルに飛び込むことによって横筋などが発生するという不良を低減させることができる。

40

## 【0026】

## &lt;第3実施形態&gt;

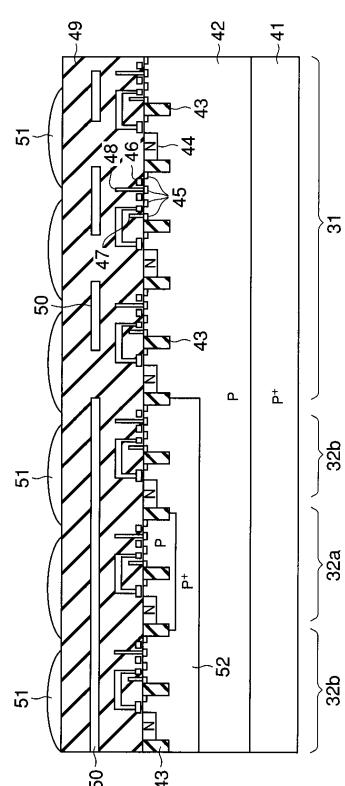

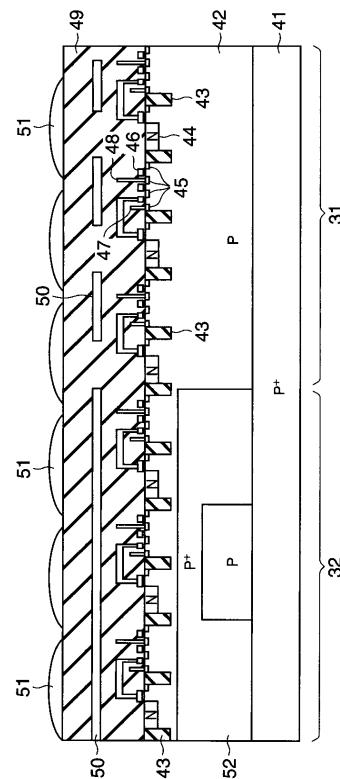

図3は、本発明の第3実施形態に係る増幅型MOSイメージセンサの一部を示す断面図である。図3に示すイメージセンサは、図2のイメージセンサと比べて、OB画素領域を平面的に囲むようにP<sup>+</sup>型バリア層52が形成されている点は同様であるが、P<sup>+</sup>型バリア層52の領域内にダミーOB画素が形成されていない点が異なる。

40

## 【0027】

図3の増幅型MOSイメージセンサによれば、図2の増幅型MOSイメージセンサと同様の効果が得られるほか、P<sup>+</sup>型バリア層52のサイズをダミーOB画素のサイズに左右

50

されることなく短く設定できるので、チップ縮小などとは異なる要因で  $P^+$  型バリア層 52 のサイズを設定することができる。

【0028】

<第4の実施形態>

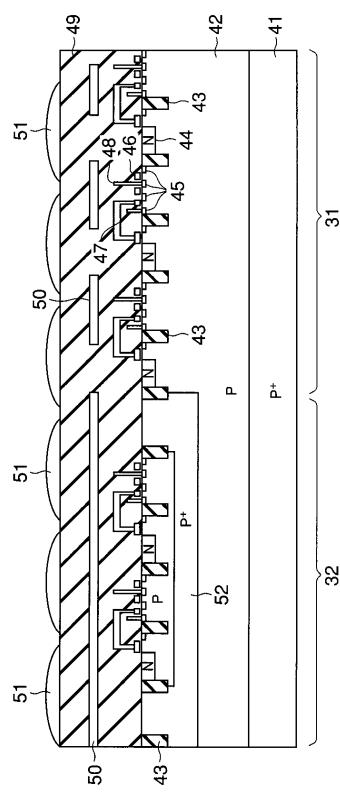

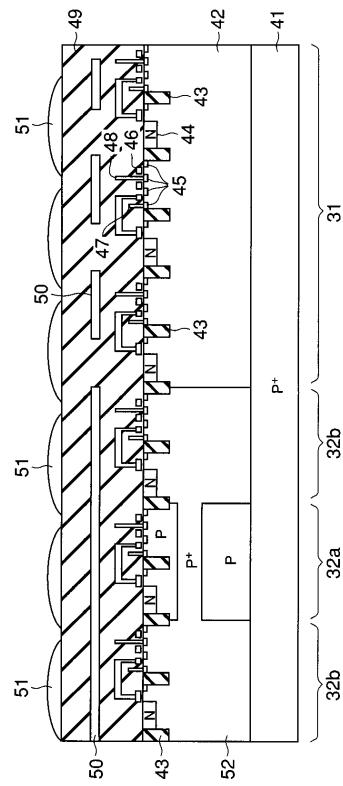

図4は、本発明の第4実施形態に係る増幅型MOSイメージセンサの一部を示す断面図である。図4に示すイメージセンサは、図2のイメージセンサと比べて、OB画素領域内で有効OB画素領域32aの下部には $P^+$ 型バリア層52が形成されており、 $P^+$ 型バリア層52の周辺でダミーOB画素32bの下部にはN型ドレイン53が形成されている点が異なる。

【0029】

なお、図4中では、 $P^+$ 型バリア層52の形成領域には1画素のみが形成されている場合を示しているが、実際は複数の画素が形成されている。また、図4中では、ダミーOB領域32bを有効OB領域32aの両端に形成する場合を示しているが、これに限定されるものではなく、ダミーOB領域32bを有効OB領域32aのいずれか一端側のみに形成してもよい。

【0030】

図4の増幅型MOSイメージセンサによれば、 $P^+$ 型バリア層52の周辺にN型ドレイン53が形成されているので、図2の増幅型MOSイメージセンサとほぼ同様の効果が得られる。即ち、感光画素領域31に強い光が入射されて、光電変換された電子は、OB画素領域に侵入することなく、N型ドレイン53により一部のブルーミング信号(キャリア)が捨てられ、さらに、OB画素領域の光電変換部へ侵入することを $P^+$ 型バリア層52によって防ぐことができる。したがって、OB画素領域で暗時レベルの信号のみを安定して生成でき、偽信号が暗時レベルに飛び込むことによって横筋などが発生するという不良を低減させることができる。

【0031】

<第5実施形態>

図5は、本発明の第5実施形態に係る増幅型MOSイメージセンサの一部を示す断面図である。図5に示すイメージセンサは、図1のイメージセンサと比べて、 $P^+$ 型バリア層52はOB画素領域32aの下部には形成されてはおらず、かつOB画素領域の端部において下部の $P^+$ 型シリコン基板41に連なるように形成されている。このような構造でも、図1の増幅型MOSイメージセンサとほぼ同様の効果が得られる。

【0032】

<第1実施形態の変形例>

$P^+$ 型バリア層52は、図6に示すように、OB画素領域32の端部において下部の $P^+$ 型シリコン基板41に連なるように形成された構造でもよい。このような構造は、P型シリコン基板42の厚さが薄い場合には、例えば1500kVの加速電圧でP型不純物のイオン注入によって実現することができる。このような構造でも、図1の増幅型MOSイメージセンサとほぼ同様の効果が得られる。

【0033】

<第2実施形態の変形例>

$P^+$ 型バリア層52は、図7に示すように、OB画素領域の端部において下部の $P^+$ 型シリコン基板41に連なるように形成された構造でもよい。このような構造は、P型シリコン基板42の厚さが薄い場合には、例えはイオン注入によって実現することができる。このような構造でも、図2の増幅型MOSイメージセンサとほぼ同様の効果が得られる。

【図面の簡単な説明】

【0034】

【図1】本発明の第1実施形態の増幅型MOSイメージセンサの断面図。

【図2】本発明の第2実施形態の増幅型MOSイメージセンサの断面図。

【図3】本発明の第3実施形態の増幅型MOSイメージセンサの断面図。

【図4】本発明の第4実施形態の増幅型MOSイメージセンサの断面図。

【図5】本発明の第5実施形態の増幅型MOSイメージセンサの断面図。

【図6】本発明の第1実施形態の変形例の断面図。

【図7】本発明の第2実施形態の変形例の断面図。

【図8】増幅型MOSイメージセンサの回路図。

【図9】図8の増幅型MOSイメージセンサの平面図。

【符号の説明】

【0035】

41...P<sup>+</sup>型シリコン基板、42...P型シリコン基板、43...素子分離領域、44...フォトダイオードの光電変換部、45...拡散領域、46...ゲート電極、47...垂直信号線、48...ドレイン線、49...絶縁層、50...遮光膜、51...マイクロレンズ、52...P<sup>+</sup>型バリア層、53...N型ドレイン。 10

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

图 7

【 四 8 】

图 8

【図9】

图 9

## フロントページの続き

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 海上 尚子

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 荒川 賢一

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

F ターム(参考) 4M118 AA05 AB01 BA14 CA04 FA06 FA25 FA42

5C024 AX01 CX01 CY47 GX03 GY31 GZ03 GZ34 GZ36 HX09 HX23