(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-56892

(P2005-56892A)

(43) 公開日 平成17年3月3日(2005.3.3)

(51) Int.Cl.<sup>7</sup>H01L 21/822

H01L 27/04

F 1

H01L 27/04

H01L 27/04

テーマコード(参考)

5FO38

M

審査請求 有 請求項の数 16 O L (全 20 頁)

(21) 出願番号

特願2003-205735 (P2003-205735)

(22) 出願日

平成15年8月4日 (2003.8.4)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74) 代理人 100058479

弁理士 鈴江 武彦

(74) 代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100084618

弁理士 村松 貞男

(74) 代理人 100092196

弁理士 橋本 良郎

最終頁に続く

(54) 【発明の名称】 ESD保護回路

## (57) 【要約】

【課題】保護能力が高く、且つ微細化しても設計や製造が容易で、製造コスト及びチップサイズを低減するESD保護回路を提供することを目的とする。

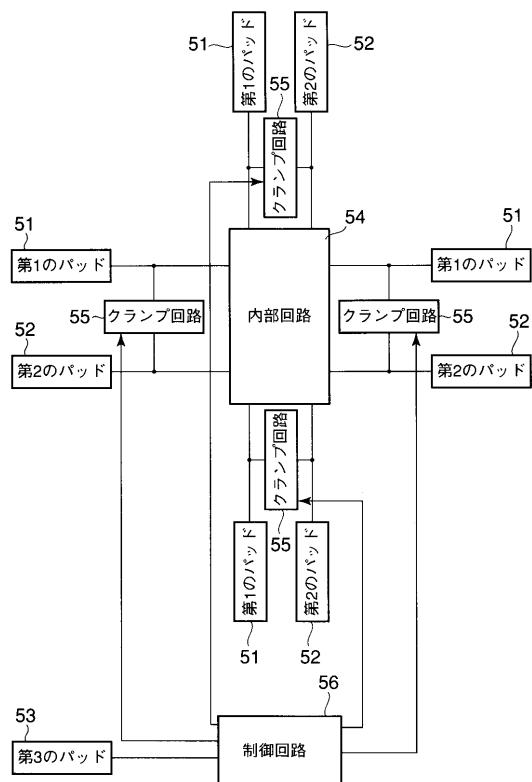

【解決手段】半導体集積回路54と、前記半導体集積回路54に接続される外部接続端子としての第1のパッド51と、前記半導体集積回路54に接続される外部接続端子としての第2のパッド52と、前記第1のパッド51と前記第2のパッド52との間に接続されるクランプ回路55と、前記クランプ回路55を導通可能状態、または非導通状態に制御するように構成された制御回路56とを具備することを特徴としている。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

半導体集積回路と、

前記半導体集積回路に接続される外部接続端子としての第1のパッドと、

前記半導体集積回路に接続される外部接続端子としての第2のパッドと、

前記第1のパッドと前記第2のパッドとの間に接続されるクランプ回路と、

前記クランプ回路を導通可能状態、または非導通状態に制御するように構成された制御回路とを具備すること

を特徴とするE S D保護回路。

**【請求項 2】**

前記クランプ回路は、前記制御回路から出力される制御信号に応答して導通可能状態または非導通状態に制御されるスイッチ素子を含むこと

を特徴とする請求項1に記載のE S D保護回路。

**【請求項 3】**

前記クランプ回路は、前記制御回路から出力される制御信号が供給されるインバータ回路と、前記インバータ回路の出力信号でオン／オフ制御されるスイッチ回路とを含むことを特徴とする請求項1に記載のE S D保護回路。

**【請求項 4】**

前記インバータ回路は、ソースが前記第1のパッドに接続され、ゲートに前記制御回路から出力される制御信号が供給される第1導電型の第1MOSトランジスタと、ドレインが前記第1MOSトランジスタのドレインに接続され、ソースが前記第2のパッドに接続され、ゲートに前記制御回路から出力される制御信号が供給される第2導電型の第2MOSトランジスタとを備えること

を特徴とする請求項3に記載のE S D保護回路。

**【請求項 5】**

前記スイッチ回路は、ドレインが前記第1のパッドに接続され、ソースが前記第2のパッドに接続され、ゲートが前記インバータ回路の出力端子に接続される第2導電型の第3MOSトランジスタを備えること

を特徴とする請求項3又は請求項4に記載のE S D保護回路。

**【請求項 6】**

前記スイッチ回路は、コレクタが前記第1のパッドに接続され、エミッタが前記第2のパッドに接続され、ベースが前記インバータ回路の出力端子に接続されるNPN型バイポーラトランジスタを備えること

を特徴とする請求項3又は請求項4に記載のE S D保護回路。

**【請求項 7】**

前記スイッチ回路は、エミッタが前記第1のパッドに接続され、コレクタが前記第2のパッドに接続され、ベースが前記インバータ回路の出力端子に接続されるPNP型バイポーラトランジスタを備えること

を特徴とする請求項3又は請求項4に記載のE S D保護回路。

**【請求項 8】**

前記スイッチ回路は、前記第1のパッドと前記第2のパッドとの間にアノードとカソードが接続されるサイリスタと、前記インバータ回路の出力信号に基づいて前記サイリスタにトリガ電流を与えてターンオン／ターンオフを制御するトリガ回路とを備えることを特徴とする請求項3又は請求項4に記載のE S D保護回路。

**【請求項 9】**

前記トリガ回路は、ソースが前記第1のパッドに接続され、ゲートが前記インバータ回路の出力端子に接続された第2導電型の第4MOSトランジスタと、一端が前記第4MOSトランジスタのドレインに接続され、他端が前記第2のパッドに接続された第1の抵抗素子とを備えること

を特徴とする請求項8に記載のE S D保護回路。

10

20

30

40

50

**【請求項 10】**

前記制御回路は、前記半導体集積回路に電源が供給されていないときに前記クランプ回路を導通可能状態に設定し、電源が供給されているときに前記クランプ回路を非導通状態に設定すること

を特徴とする請求項1乃至請求項9のいずれか1項に記載のESD保護回路。

**【請求項 11】**

前記制御回路に接続される第3のパッドを更に具備し、

前記制御回路は、前記第3のパッドに電位が印加されないときは前記クランプ回路が導通可能状態となり、所定の電位が印加されたときは前記クランプ回路が非導通状態となるように前記クランプ回路を制御すること

10

を特徴とする請求項1乃至請求項9のいずれか1項に記載のESD保護回路。

**【請求項 12】**

前記制御回路は、一端が前記第3のパッドに接続され、他端が前記第1の電位を生成する第1の電位供給源に接続される負荷回路を含むこと

を特徴とする請求項11に記載のESD保護回路。

**【請求項 13】**

前記負荷回路は、第2の抵抗素子を含むこと

を特徴とする請求項12に記載のESD保護回路。

**【請求項 14】**

前記制御回路は、前記半導体集積回路を備えた半導体チップが実装されたか否かに応じたデータがプログラムされるプログラマブル回路を備え、

20

前記プログラマブル回路にプログラムされたデータに基づいて、前記クランプ回路の導通可能状態と非導通状態とを切り替えて制御すること

を特徴とする請求項1乃至請求項9のいずれか1項に記載のESD保護回路。

**【請求項 15】**

前記プログラマブル回路は、前記半導体チップが実装された後で溶断されるヒューズ素子を有するヒューズ回路を備え、

前記半導体チップは、前記ヒューズ素子に電流を流し、前記半導体チップが実装された後で溶断するための第4、第5のパッドを更に有すること

を特徴とする請求項14に記載のESD保護回路。

30

**【請求項 16】**

前記ヒューズ回路は、前記ヒューズ素子の一端と前記第1の電位を生成する第1の電位供給源との間に接続された第3の抵抗素子と、前記ヒューズ素子の他端と前記第2の電位を生成する第2の電位供給源との間に接続される第4の抵抗素子とを含むこと

を特徴とする請求項15に記載のESD保護回路。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

この発明は、IC(Integrated Circuit)やLSI(Large Scale Integration Circuit)等の半導体集積回路をESD(Electrostatic Discharge; 静電気放電)から保護するESD保護回路に関する。

40

**【0002】****【従来の技術】**

従来、ICやLSI等の半導体集積回路をESDにより発生する高電圧から保護するため、種々のESD保護回路が提案されている。ここでは、図9乃至図13を用いて従来の3種類のESD保護回路について説明する。

**【0003】**

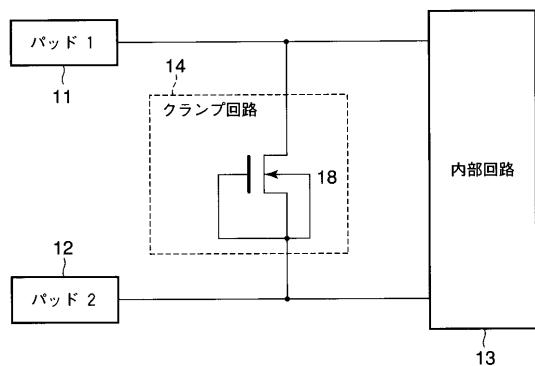

図9は、従来例1に係るESD保護回路を模式的に示した回路図である。

**【0004】**

50

図9に示すように、第1，第2のパッド11，12には内部回路13が接続され、これらのパッド11，12間には、クランプ回路14が接続されている。上記クランプ回路14は、NMOSトランジスタ18により構成される。すなわち、上記NMOSトランジスタ18のドレインが第1のパッド11に接続され、ソースが第2のパッド12に接続され、ゲートとバックゲートはソースに接続される。上記第2のパッド12は接地されている。

#### 【0005】

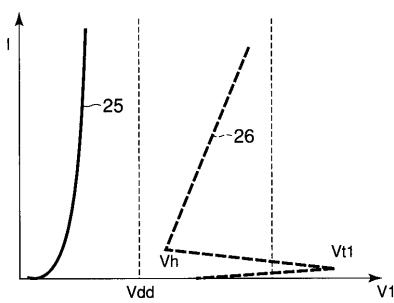

次に、図9に示した回路の動作について図10を用いて説明する。図10は、図9に示すNMOSトランジスタ18の電圧-電流特性を模式的に示す図である。図10において、横軸はNMOSトランジスタ18のドレインとソースとの間に印加される電圧値V1であり、縦軸はドレインとソースとの間に流れる電流値I1である。

10

#### 【0006】

まず、第1のパッド11と第2のパッド12の間にESDによる高電圧が印加されない場合（領域1）は、クランプ回路14であるNMOSトランジスタ18のドレインとソース間には電流は流れない。これは、上記のようにNMOSトランジスタ18のゲートとソースは互いに接続されて同電位になっており、非導通状態（オフ状態）になっているためである。従って、内部回路13を高電圧から保護する必要のない場合においては、内部回路13の通常動作には影響を与えない。

#### 【0007】

一方、第1のパッド11と第2のパッド12の間にESDによる高電圧が印加された場合（領域2）は、NMOSトランジスタ18は導通状態（オン状態）になり、ESDより発生したESD電荷が第1のパッド11からクランプ回路14を通って第2のパッド12へ抜けてゆく。即ち、内部回路13には高電圧が印加されずに内部回路13を保護することが出来る。

20

#### 【0008】

上記領域2の場合における、NMOSトランジスタ18の電圧-電流特性についてさらに詳しく説明する。NMOSトランジスタ18のドレインとソースとの間に高電圧がかかると、図10に示すように、一旦トリガ電圧Vt1に達した後、NMOSトランジスタ18にはスナップバック特性が発生する。上記スナップバック特性のために、電圧がホールド電圧Vhまで降下する。その後、急激に電流を流せるようになる。

30

#### 【0009】

尚、このときNMOSトランジスタ18に流れる電流は、ドレインから基板部分を通してソースへ流れるバイポーラアクションとして流れるオフ電流である。従って、NMOSトランジスタ18のチャネル部を流れるオン電流ではない。

#### 【0010】

しかし、上記のような構成のESD保護回路では、以下の2つの設計条件を満足しなければならない。まず、第1の設計条件として、保護すべき内部回路13の耐圧値（内部回路13が破壊される電圧）をトリガ電圧値Vt1の耐圧値よりも高くする必要がある。さらに、第2の設計条件は、ホールド電圧値Vhを内部回路13の電源電圧値Vddよりも高くする必要がある。尚、上記第2の設計条件は、内部回路13が通常動作している場合において、クランプ回路14が導通状態（オン状態）となるのを排除するために求められる設計条件である。

40

#### 【0011】

ところが、近年の半導体製造技術の微細化に伴って、内部回路に用いられるMOSFETのゲート耐圧値が急激に低下してきた。例えば、0.18~0.13ミクロンプロセスではトリガ電圧値Vt1とゲート耐圧値はほぼ同等になり、0.09ミクロンプロセスではトリガ電圧値Vt1よりもゲート耐圧値が低い状況になった。即ち、内部回路13の耐圧値がトリガ電圧値Vt1よりも低い状況となった。そのため、今後の微細化プロセスを考慮すると、上記第1の設計条件を満足することが難しくなっている。

#### 【0012】

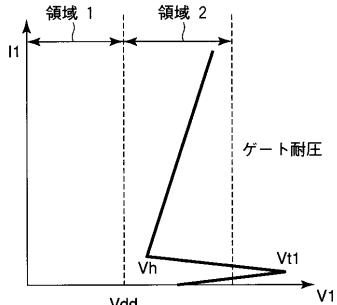

次に、図11及び図12を用いて従来例2に係るESD保護回路を説明する。図11は、

50

従来例 2 に係る ESD 保護回路を模式的に示した回路図である。

【 0 0 1 3 】

この従来例 2 に係る ESD 保護回路は、上記従来例 1 に示した ESD 保護回路に、更に時定数回路 23 を設けている。このような ESD 保護回路については、例えば特許文献 1 に記載されている。

【 0 0 1 4 】

上記時定数回路 23 は、キャパシタ C と抵抗素子 R により構成される。上記キャパシタ C の一方の電極はパッド 11 に接続され、他方の電極は NMOS ランジスタ 18 のゲートに接続される。上記抵抗素子 R の一端は上記 NMOS ランジスタのゲートに接続され、他端はパッド 12 に接続される。

10

【 0 0 1 5 】

次に、図 12 を用いて図 11 に示した ESD 保護回路の動作を説明する。図 12 は、図 11 に示す NMOS ランジスタ 18 の電圧 - 電流特性を示す図である。図 12 において、横軸は NMOS ランジスタ 18 のドレインとソースとの間に印加される電圧値 V1 であり、縦軸はドレインとソースとの間に流れる電流値 I1 である。

【 0 0 1 6 】

まず、第 1 のパッド 11 と第 2 のパッド 12 の間に ESD のによる高電圧が印加されない場合においては、上記と同様にクランプ回路 14 は非導通状態（オフ）である。そのため、内部回路 13 の通常動作には影響を与えない。

20

【 0 0 1 7 】

しかし、第 1 のパッド 11 と第 2 のパッド 12 の間に ESD による高電圧が印加された場合は、時定数回路 23 が生成する一定時間のパルスが NMOS ランジスタ 18 のゲートに印加される。そのため、NMOS ランジスタ 18 はオンとなる。即ち、クランプ回路 14 は導通状態（オン状態）となる。

【 0 0 1 8 】

そのため、ESD により発生した ESD 電荷は、第 1 のパッド 11 からクランプ回路 14 を通って第 2 のパッド 12 へ放出される。そのため、ESD により発生した高電圧から内部回路 13 を保護することが出来る。尚、上記一定時間は、概ねキャパシタ C の容量値と抵抗素子 R の抵抗値を掛け合わせた時定数により決定される。

30

【 0 0 1 9 】

ここで、図 12 を用いて、上記の第 1 のパッド 11 と第 2 のパッド 12 の間に ESD による高電圧が印加された場合における、NMOS ランジスタ 18 の電圧 - 電流特性について詳しく説明する。

【 0 0 2 0 】

図 12 中の実線 25 は NMOS ランジスタ 18 のチャネルを流れる電圧 - 電流特性を示す。即ち、実線 25 は「NMOS ランジスタ 18 がオンのとき」の特性である。さらに、図 12 中の破線 26 は、従来例 1 のスナップバック特性に相当する電圧 - 電流特性を示す。即ち、破線 26 は「NMOS ランジスタ 18 がオフのとき」の特性である。図 12 に示すように、実線 25 の特性は破線 26 の特性よりも電流を多く流すことが出来る。そのため、ESD に対する保護能力は従来例 1 よりも高い。尚、上記のように実線 25 で示す特性は、従来例 1 と異なり NMOS ランジスタ 18 のソースとドレインの間に形成されるチャネル部を流れるオン電流により示される特性である。また、破線 26 で示すような NMOS ランジスタ 18 を流れる電流は、バイポーラアクションとしてチャネル部を流れないオフ抵抗である。

40

【 0 0 2 1 】

上記のように、従来例 2 は NMOS ランジスタ 18 のオフ電流ではなくオン電流を利用する。そのため、従来例 1 における第 1 の設計条件「保護すべき内部回路の耐圧（内部回路が破壊される電圧）よりも、トリガ電圧 Vt1 が低くなくてはならない」という設計条件を考慮する必要がない。

【 0 0 2 2 】

50

しかし、従来例2では時定数回路23の設計が難しくなる。即ち、上記時定数(=キャパシタCの容量値と抵抗素子Rの抵抗値とを掛け合わせた値)が小さいと、NMOSトランジスタ18がオンとなる時間が短くなり、効果的なESD保護ができない。逆に、時定数を大きく設定すると、NMOSトランジスタ18がオンとなる時間が長くなるため効果的なESD保護をすることが出来る。しかし、抵抗素子RとキャパシタCのサイズが大きくなりチップコストは高くなる。しかも、上記時定数回路23は、各一対のパッドごとに必要となるため、チップ全体では製造コストやチップサイズの大幅な増大を招く。

#### 【0023】

次に、図13を用いて従来例3に係るESD保護回路を説明する。図13は、従来例3に係るESD保護回路を模式的に示した回路図である。このようなESD保護回路は、例えば非特許文献1に記載されている。10

#### 【0024】

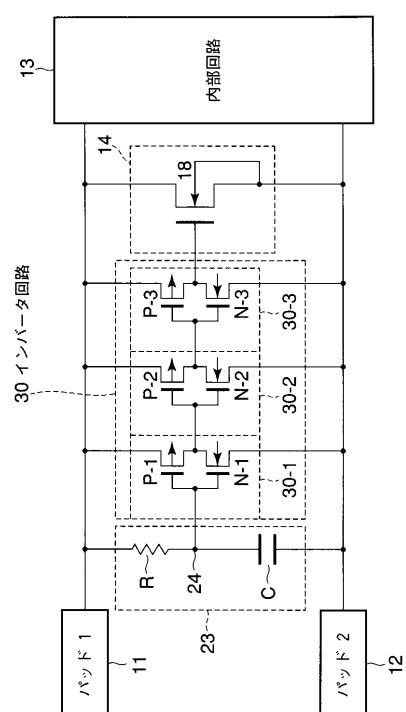

図13に示すように従来例3に係るESD保護回路は、時定数回路23とクランプ回路14との間に、第1乃至第3のインバータ30-1, 30-2, 30-3の入力端と出力端とを順次接続して設けている。

#### 【0025】

上記第1乃至第3のインバータ30-1, 30-2, 30-3は、PMOSトランジスタP-1, P-2, P-3とNMOSトランジスタN-1, N-2, N-3とで構成される。上記第1のインバータ30-1の入力端子は時定数回路23のノード24に接続され、出力端子は第2のインバータ30-2の入力端子に接続される。上記第2のインバータ30-2の出力端子は第3のインバータ30-3の入力端子に接続される。上記第3のインバータ30-3の出力端子は、上記クランプ回路14におけるNMOSトランジスタ18のゲートに接続される。20

#### 【0026】

次に動作について説明する。まず、第1のパッド11と第2のパッド12との間にESDにより発生する高電圧が印加される場合の動作を説明する。第1のパッド11と第2のパッド12との間に高電圧が印加されると、時定数回路23とインバータ回路30が生成する信号によって、クランプ回路14としてのNMOSトランジスタ18がオンする。これによって、第1のパッド11に印加されたESD電荷は、クランプ回路14を介して第2のパッド12へ抜けていき、内部回路13を保護する。その他の動作については、上記従来例2と同様であるのでその詳細な説明を省略する。30

#### 【0027】

しかし、従来例3に係るESD保護回路は、時定数回路23を用いるため、上記従来例2と同様の問題を有する。また、インバータ回路30を設けるため、チップサイズや製造コストの点で更に不利になる。

#### 【0028】

#### 【特許文献1】

米国特許 6,249,410号 明細書 (Jun. 19, 2001 FIG. 4)

#### 【0029】

#### 【非特許文献1】

ON-CHIP ESD PROTECTION FOR INTEGRATED CIRCUITS An IC Design Perspective Figure 4-24 (Albert Z.H. Wang著 Kluwer Academic Publishers Group)40

#### 【0030】

#### 【発明が解決しようとする課題】

上記のように従来のESD保護回路は、保護能力が十分ではなく、且つ微細化に伴って設計や製造が難しくなり、製造コスト及びチップサイズが増大する、という問題があった。

#### 【0031】

この発明は上記のような事情に鑑みてなされたものであり、保護能力が高く、且つ微細化50

しても設計や製造が容易で、製造コスト及びチップサイズを低減することが出来る ESD 保護回路を提供することを目的とする。

#### 【0032】

##### 【課題を解決するための手段】

この発明の一態様に係る ESD 保護回路は、半導体集積回路と、前記半導体集積回路に接続される外部接続端子としての第 1 のパッドと、前記半導体集積回路に接続される外部接続端子としての第 2 のパッドと、前記第 1 のパッドと前記第 2 のパッドとの間に接続されるクランプ回路と、前記クランプ回路を導通可能状態、または非導通状態に制御するよう構成された制御回路とを具備する。

#### 【0033】

上記のような構成によれば、クランプ回路のオン電流を用いることが出来るため、高い保護能力を有する。さらに、制御回路によりクランプ回路を導通可能状態、または非導通状態に切り替えることが出来る。そのため、トリガ電圧やホールド電圧の設計上の制限から解放され、容易に製造することが可能となる。また、上記クランプ回路に時定数回路等を必要としないため、製造コストを低減し、チップサイズを低減することが出来る。

10

#### 【0034】

##### 【発明の実施の形態】

以下、この発明の実施形態について図面を参照して説明する。なお、この説明においては、全図にわたり共通の部分には共通の参照符号を付す。

20

#### 【0035】

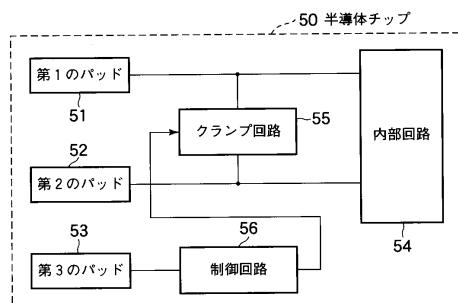

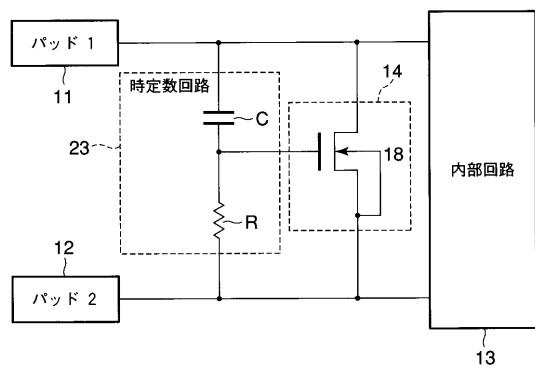

まず、図 1 及び図 2 を用いて、この発明に係る ESD 保護回路の概略構成を説明する。

#### 【0036】

図 1 に示すように、半導体チップ 50 中に保護すべき半導体集積回路である内部回路 54 が形成されている。さらに、第 1 のパッド 51 及び第 2 のパッド 52 が内部回路 54 に接続され、上記第 1 , 第 2 のパッド 51 , 52 の間にクランプ回路 55 が接続される。また、第 3 のパッド 53 は上記制御回路 56 に接続されている。上記クランプ回路 55 は制御回路 56 の出力信号により導通可能状態 / 非導通状態が制御される。

#### 【0037】

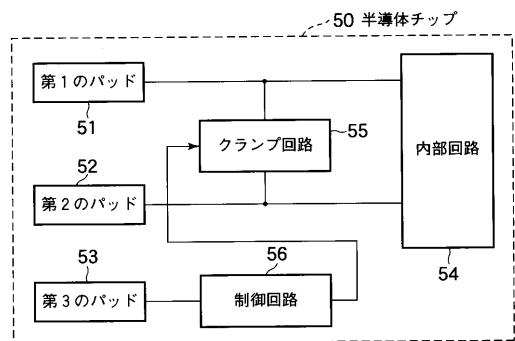

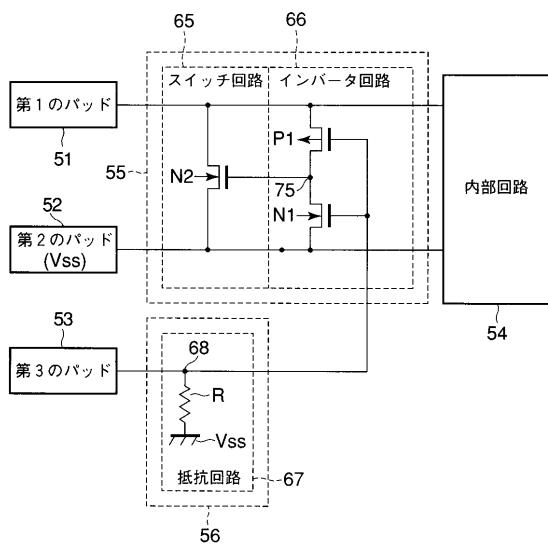

次に、図 2 を用いて図 1 で示す ESD 保護回路の動作を説明する。図 2 は図 1 のクランプ回路 55 の電圧 - 電流特性を模式的に示す図である。ここで、図 2 の横軸はクランプ回路 55 に印加される電圧値 V を示し、縦軸はクランプ回路 55 に流れる電流値 I を示す。さらに、図中の実線 61 は第 1 の電圧 - 電流特性を示し、実線 62 は第 2 の電圧 - 電流特性を示す。

30

#### 【0038】

まず、LSI 等の半導体チップ 50 が実装された後、即ち、第 1 のパッド 51 と第 2 のパッド 52 との間に ESD による高電圧が印加され得ない状況においての動作を説明する。

30

#### 【0039】

ここで、上記半導体チップ 50 が実装された後とは、例えば電子機器や家電製品等のエンジニアリング製品の中に部品として組み込まれた後のことである。換言すれば、定められた条件で通常の動作をしているような状況等をいう。上記のような状況においては、ESD により内部回路 54 に高電圧が印加される可能性は極めて低い。そのため、クランプ回路 55 を第 1 の電圧 - 電流特性 61 に設定し、非導通状態（オフ状態）とする。

40

#### 【0040】

上記のように半導体チップ 50 が実装された後では、上記第 3 のパッド 53 には制御回路 56 を適切に制御するための信号が入力される。すると、制御回路 56 の制御によりクランプ回路 55 の電圧 - 電流特性は第 1 の電圧 - 電流特性 61 となる。図 2 に示すように、第 1 の電圧 - 電流特性 61 は、電圧値 V が小さい場合においては電流値 I が流れない特性である。即ち、クランプ回路 55 が第 1 の電圧 - 電流特性 61 を示す場合には、クランプ回路 55 は非導通状態（オフ状態）となる。

#### 【0041】

50

そのため、クランプ回路 5 5 の動作が、内部回路 5 4 の動作に影響を与えることはない。従って、内部回路 5 4 は正常な動作を行うことが出来る。

【 0 0 4 2 】

一方、半導体チップ 5 0 が実装される前、即ち、第 1 のパッド 5 1 と第 2 のパッド 5 2 との間に E S D による高電圧が印加され得る状況においての動作を説明する。

【 0 0 4 3 】

ここで、上記半導体チップ 5 0 が実装される前とは、例えば製造された直後から電子機器メーカーの工場内で P C 板へ組み込まれる工程まで間の状況、又は半導体チップが半導体工場で製造されてからエンド製品に組み込まれ通常の動作を行うまでの間の状況等をいう。上記のような状況においては、E S D により内部回路 5 4 に高電圧が印加される可能性がある。そのため、クランプ回路 5 5 を導通可能状態にしておき、いつ E S D による高電圧が印加されてもよいようにしておく。即ち、クランプ回路 5 5 を第 2 の電圧 - 電流特性 6 2 に制御し、導通可能状態に設定しておく。クランプ回路 5 5 が導通可能状態であるため、高電圧により発生した電荷をクランプ回路 5 5 に通過して、接地電源 V s s に放電することが出来る。

10

【 0 0 4 4 】

上記のように半導体チップ 5 0 が実装される前では、上記第 3 のパッド 5 3 は外部より信号は与えられていないが、制御回路 5 6 の制御により、クランプ回路 5 5 の電圧 - 電流特性は第 2 の電圧 - 電流特性 6 2 となっている。図 2 に示すように、第 1 の電圧 - 電流特性 6 2 は、電圧値 V がわずかでも印加されると電流値 I が多量に流れるような特性である。即ち、クランプ回路 5 5 が第 2 の電圧 - 電流特性 6 2 を示す場合、クランプ回路 5 5 は導通可能状態となる。

20

【 0 0 4 5 】

従って、E S D により第 1 のパッド 5 1 と第 2 のパッド 5 2 との間に高電圧（例えば、数千 V 程度）が印加された場合であっても、上記高電圧はクランプ回路 5 5 を介して放電される。即ち、E S D により発生した E S D 電荷は、第 1 のパッド 5 1 からクランプ回路 5 5 を通過して第 2 のパッドへ放出される。

20

【 0 0 4 6 】

そのため、E S D による高電圧は内部回路 5 4 に印加されることがない。その結果、内部回路 5 4 が高電圧により破壊されることから保護することが出来る。

30

【 0 0 4 7 】

上記図 2 中に示すように、第 2 の電圧 - 電流特性 6 2 はオン電流を利用している。そのため、多量の電流を流すことが出来、クランプ回路 5 5 は高い保護能力を有している。

【 0 0 4 8 】

さらに、制御回路 5 6 の制御によりクランプ回路 5 5 の電圧 - 電流特性を、第 1 の電圧 - 電流特性 6 1 又は第 2 の電圧 - 電流特性 6 2 となるように制御する。即ち、クランプ回路 5 5 は、非導通状態又は導通可能状態のいずれかの状態に切り替えて使用される。そのため、従来例 1 のような設計上の条件が必要ではない。その結果、クランプ回路 5 5 の設計上の制約を考慮する必要がなく、E S D 保護回路を安易に製造することが出来る。

40

【 0 0 4 9 】

しかも、この実施形態に係る E S D 保護回路においては、内部回路 5 4 の微細化に伴う設計上の条件を懸念する必要はない。従って、今後の微細化された内部回路 5 4 にもおいても容易に対応することが出来る。

【 0 0 5 0 】

さらに、時定数回路等が不要であるため、時定数回路の時定数による製造上の制約から解放され、E S D 保護回路を容易に製造することが出来る。さらに、時定数回路等の製造に伴う製造コストの増大及びチップサイズの増大もないため、製造コスト及びチップサイズを低減することが出来る。

【 0 0 5 1 】

[ 第 1 の実施形態 ]

50

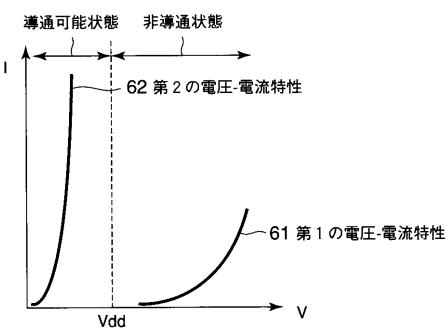

次に図3を用いて、この発明の第1の実施形態に係るE S D保護回路について説明する。図3はE S D保護回路を模式的に示す回路図である。また、以下の説明において、上記図1で示したE S D保護回路の説明と重複する部分の説明を省略し、特に相違する部分について詳しく説明する。

【0052】

図3に示すように、クランプ回路55はスイッチ回路65及びインバータ回路66から構成され、制御回路56は抵抗回路67から構成される。また、第2のパッド52は接地用のパッドであり、半導体集積回路内の接地電源線に接続されている。

【0053】

上記インバータ回路66は、PMOSトランジスタP1及びNMOSトランジスタN1から構成される。PMOSトランジスタP1のゲートは第3のパッド53に接続され、ソースは第1のパッドに接続され、ドレインはノード75に接続される。NMOSトランジスタN1のゲートは第3のパッド53に接続され、ソースは第2のパッド52に接続され、ドレインはノード75に接続される。

【0054】

上記スイッチ回路65は、NMOSトランジスタN2から構成される。上記NMOSトランジスタN2のゲートはノード75に接続され、ソースは第2のパッド52に接続され、ドレインは第1のパッド51に接続される。

【0055】

上記抵抗回路67は、プルダウン抵抗素子Rから構成される。プルダウン抵抗素子Rの一端は第3のパッド53に接続されるノード68に接続され、他端は半導体集積回路内の接地電源線Vssに接続される。

【0056】

次に、図3で示したE S D保護回路の動作について説明する。ここで、以下の動作の説明において、図2のようなクランプ回路55の電圧・電流特性の図示及びその説明は、同様であるので省略する。

【0057】

まず、半導体チップが実装された後、即ち、第1のパッド51と第2のパッド52との間にE S Dによる高電圧が印加され得ない状況においては、上記第2のパッド52は接地電源Vssに接続され、上記第3のパッド53は内部電源Vddに接続される。

【0058】

すると、PMOSトランジスタP1のゲート及びNMOSトランジスタN1のゲートに“H(High)”レベルの電圧が印加される。よって、PMOSトランジスタP1はオフし、NMOSトランジスタN1はオンする。

【0059】

そのため、ノード75を介してNMOSトランジスタN2のゲートには、第2のパッド52に接続された接地電源の“L(Low)”レベルの電圧が印加され、NMOSトランジスタN2はオフする。

【0060】

以上の動作によって、クランプ回路55は非導通状態(オフ状態)となる。そのため、クランプ回路55の動作が、内部回路55の動作に影響を与えることはなく、内部回路55の正常な動作を確保する。

【0061】

一方、半導体チップが実装される前、即ち、第1のパッド51と第2のパッド52との間にE S Dによる高電圧が印加され得る状況においては、第3のパッド53は抵抗回路67を介して接地されている。

【0062】

すると、PMOSトランジスタP1のゲート及びNMOSトランジスタN1のゲートには“L”レベルの電圧が印加される。よって、NMOSトランジスタN1はオフし、PMOSトランジスタP1はオンし得る状態となる。そのため、PMOSトランジスタP1がオ

10

20

30

40

50

ンした場合には、N MOSトランジスタN 2のゲートに第1のパッド5 1と同様な電圧値が印加される。

#### 【0063】

この時、ESDによって発生した高電圧が第1のパッド5 1と第2のパッド5 2との間に印加されると、PMOSトランジスタP 1のソースには高電圧が印加され、PMOSトランジスタP 1は完全にオンする。そのため、N MOSトランジスタN 2のゲートには高電圧が印加され、N MOSトランジスタN 2はオンする。

#### 【0064】

以上の動作によって、クランプ回路5 5は導通状態となる。従って、高電圧はクランプ回路5 5を介して放電される。即ち、ESDにより発生したESD電荷は、第1のパッド5 1からクランプ回路5 5を通過して第2のパッドへ放出される。10

#### 【0065】

そのため、ESDによる高電圧は内部回路5 4に印加されることがない。その結果、内部回路5 4の通常の動作を確保し、内部回路5 4を保護することが出来る。

#### 【0066】

上記のように、ESDによって発生した高電圧が第1のパッド5 1と第2のパッド5 2との間に印加されると、N MOSトランジスタN 2のゲートには、高電圧が印加される。そのため、N MOSトランジスタN 2はオンする。即ち、この実施形態に係るクランプ回路5 5は、MOSトランジスタのオン電流を利用する。上記オン電流はMOSトランジスタのチャネル部を流れる電流であるため、オフ電流に比べ多量の電流を流すことが出来る。従って、ESDにより発生する高電圧に対してより効果的に内部回路5 4を保護することが出来る。20

#### 【0067】

以上のようにこの実施形態に係るESD保護回路によると、製造が容易になるだけでなく、さらに多くの電流を流すことが出来る。その他の効果は、上記図1で示したESD保護回路と同様である。

#### 【0068】

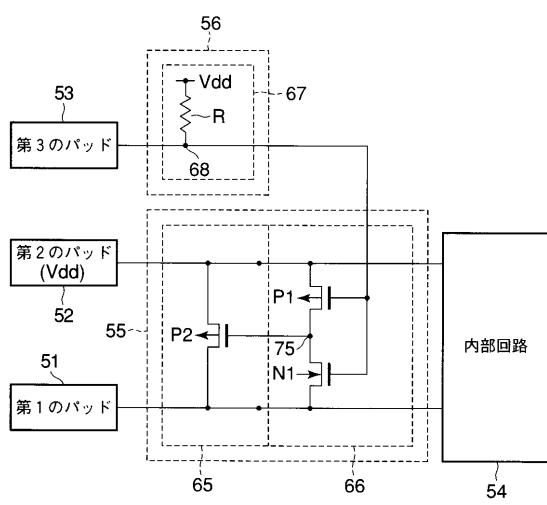

##### [第2の実施形態]

次に、図4を用いて第2の実施形態に係るESD保護回路について説明する。図4はESD保護回路を模式的に示した回路図である。以下の説明において、上記第1の実施形態と重複する部分説明を省略し、相違する部分について詳細に説明する。30

#### 【0069】

図4に示すように、スイッチ回路6 5はPMOSトランジスタP 2により構成される。上記PMOSトランジスタP 2のゲートはノード7 5に接続され、ソースは第2のパッド5 2に接続され、ドレインは第1のパッド5 1に接続される。さらに、抵抗回路6 7のブルアップ抵抗素子Rの一端は第3のパッド5 3と接続するノード6 8に接続され、他端は半導体集積回路内の内部電源線Vddに接続される。上記内部電源線Vddの電圧値は正極性である。また、第2のパッド5 2は電源供給用のパッドであり、半導体集積回路内の内部電源線Vddに接続されている。

#### 【0070】

次に、図4に示したESD保護回路の動作について説明する。40

#### 【0071】

まず、半導体チップが実装された後、即ち、第1のパッド5 1と第2のパッド5 2との間にESDによる高電圧が印加され得ない状況においては、第2のパッド5 2には内部電源Vddが供給され、第3のパッド5 3は接地される。

#### 【0072】

すると、PMOSトランジスタP 1のゲート及びN MOSトランジスタN 1のゲートには“L”レベルの電圧が印加される。よって、PMOSトランジスタP 1はオンし、N MOSトランジスタN 1はオフする。

#### 【0073】

10

20

30

40

50

そのため、ノード75を介してPMOSトランジスタP2のゲートには、第2のパッド52に接続された内部電源の“H”レベルの電圧値が印加され、PMOSトランジスタP2はオフする。

#### 【0074】

以上の動作によって、クランプ回路55は非導通状態（オフ状態）となる。そのため、クランプ回路55の動作が、内部回路54の動作に影響を与えることはなく、内部回路54は正常な動作を行うことが出来る。

#### 【0075】

一方、半導体チップが実装される前、即ち、第1のパッド51と第2のパッド52との間にESDによる高電圧が印加され得る状況においては、第3のパッド53は抵抗回路67を介して内部電源Vddに接続される。上記内部電源Vddの電圧値は正極性である。

10

#### 【0076】

すると、PMOSトランジスタP1のゲート及びNMOSトランジスタN1のゲートには“H”レベルの電圧値が印加される。よって、PMOSトランジスタP1はオフし、NMOSトランジスタN1はオンする。

#### 【0077】

そのため、PMOSトランジスタP2のゲートには第1のパッド51と同様な“L”レベルの電圧値が印加され、PMOSトランジスタP2はオンし得る状態となる。

#### 【0078】

この時、ESDによって発生した高電圧が第1のパッド51と第2のパッド52との間に印加されると、PMOSトランジスタP2のソースには高電圧が印加され、PMOSトランジスタP2は完全にオンする。

20

#### 【0079】

以上の動作によって、クランプ回路55は導通可能状態となる。従って、高電圧はクランプ回路55を介して放電され、内部回路54には印加されない。

#### 【0080】

上記のように、ESDが発生しうる状況においてはクランプ回路55があらかじめ導通可能状態となっている。そのため、より多くの電流を流すことが出来る。

#### 【0081】

上記第1実施形態及び第2の実施形態において示したように、クランプ回路55を構成するMOSトランジスタの導電型を反転した場合であっても、同様の効果を得ることが出来る。このような関係は、以下の実施形態においても同様である。

30

#### 【0082】

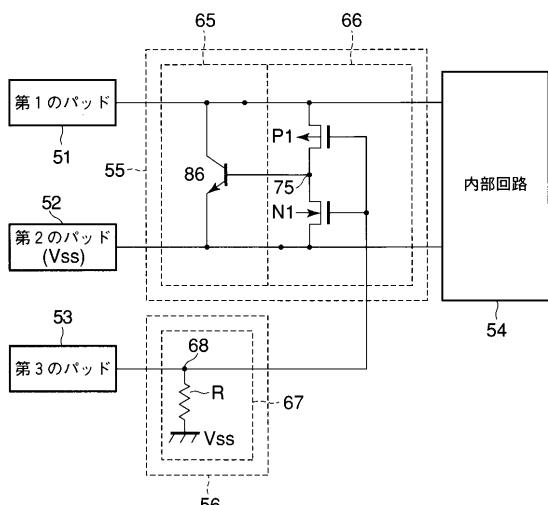

#### [第3の実施形態]

次に、図5を用いて第3の実施形態に係るESD保護回路を説明する。図5は第3の実施形態に係るESD保護回路を模式的に示した回路図である。以下の説明において、上記実施形態と重複する部分説明を省略し、相違する部分について詳細に説明する。

#### 【0083】

図5に示すように、スイッチ回路65がバイポーラトランジスタ86により構成される。上記バイポーラトランジスタ86のコレクタは第1のパッド51に接続され、エミッタは第2のパッド52に接続され、ベースはノード75に接続される。また、第2のパッド52は接地用のパッドであり、半導体集積回路内の接地電源線に接続されている。

40

#### 【0084】

次に、図5で示したESD保護回路の動作について説明する。

#### 【0085】

まず、半導体チップが実装された後、即ち、第1のパッド51と第2のパッド52との間にESDによる高電圧が印加され得ない状況においては、上記第2のパッドには接地電源Vssが接続され、上記第3のパッド53は内部電源Vddに接続される。

#### 【0086】

すると、上記実施形態と同様の動作により、NMOSトランジスタN1はオンとなる。従

50

って、バイポーラトランジスタ 8 6 のエミッタとベースには同電圧が印加されるため、バイポーラトランジスタ 8 6 はオフとなる。

#### 【 0 0 8 7 】

従って、クランプ回路 5 5 は非導通状態となるため、内部回路 5 4 の動作に影響を与えない。その結果、内部回路 5 4 は正常な動作を行うことが出来る。

#### 【 0 0 8 8 】

一方、半導体チップが実装される前、即ち、第 1 のパッド 5 1 と第 2 のパッド 5 2 との間に高電圧が印加され得る状況においては、第 3 のパッド 5 3 は抵抗回路 6 7 を介して接地電源 V<sub>ss</sub> に接続される。

#### 【 0 0 8 9 】

すると、上記実施形態と同様の動作により、PMOSトランジスタ P 1 はオンし得る状態となる。この時、ESDによって発生した高電圧が第 1 のパッド 5 1 と第 2 のパッド 5 2 との間に印加されると、第 1 のパッド 5 1 を介して PMOSトランジスタ P 1 のソースに高電圧が印加され、PMOSトランジスタ P 1 は完全にオンする。そのため、バイポーラトランジスタ 8 6 のベースには高電圧が印加される。一方、バイポーラトランジスタ 8 6 のエミッタには第 2 のパッド 5 2 を介して接地電圧 V<sub>ss</sub> が印加されている。そのため、バイポーラトランジスタ 8 6 はオンとなる。

#### 【 0 0 9 0 】

以上の動作によって、クランプ回路 5 5 は導通可能状態となる。従って、高電圧はクランプ回路 5 5 を介して放電され、ESDにより発生した ESD 電荷は、第 1 のパッド 5 1 からクランプ回路 5 5 を通過して第 2 のパッド 5 2 へ放電される。その結果、内部回路 5 4 を高電圧から保護することが出来る。

#### 【 0 0 9 1 】

一般的に、バイポーラトランジスタは MOSトランジスタに比べ動作速度が速く、多量の電流を流すことが出来る。その結果、クランプ回路 5 5 の電圧 - 電流特性をさらに向上することが出来る。

#### 【 0 0 9 2 】

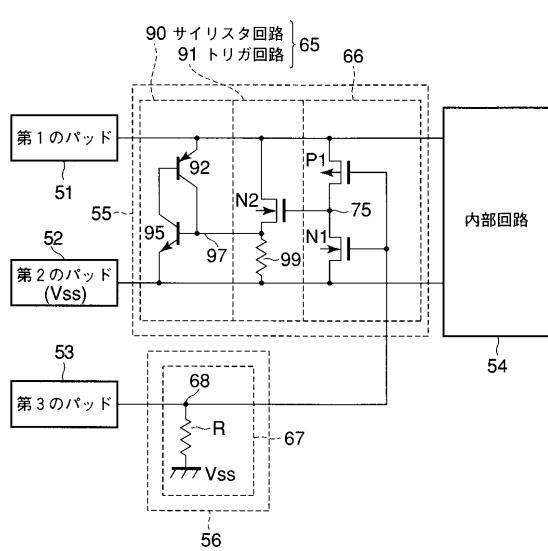

##### [ 第 4 の 実 施 形 態 ]

次に、図 6 を用いて第 4 の実施形態に係る ESD 保護回路を説明する。図 6 は ESD 保護回路を模式的に示した回路図である。以下の説明において、上記実施形態と重複する部分の説明を省略し、相違する部分について詳細に説明する。

#### 【 0 0 9 3 】

図 6 に示すように、スイッチ回路 6 5 がサイリスタ回路 9 0 及びトリガ回路 9 1 により構成されている。上記サイリスタ回路 9 0 は、バイポーラトランジスタ 9 2 及びバイポーラトランジスタ 9 5 により構成され、上記トリガ回路 9 1 は NMOSトランジスタ N 2 及び抵抗素子 9 9 により構成される。

#### 【 0 0 9 4 】

上記バイポーラトランジスタ 9 2 のエミッタは第 1 のパッド 5 1 に接続され、ベースはバイポーラトランジスタ 9 5 のコレクタに接続され、コレクタはノード 9 7 に接続される。上記バイポーラトランジスタ 9 5 のベースはノード 9 7 に接続され、エミッタ 9 8 は第 2 のパッド 5 2 に接続される。

#### 【 0 0 9 5 】

上記抵抗素子 9 9 の一端はノード 9 7 に接続され、他端は第 2 のパッド 5 2 に接続される。また、第 2 のパッド 5 2 は接地用のパッドであり、半導体集積回路内の接地電源線に接続されている。

#### 【 0 0 9 6 】

次に、図 6 で示す ESD 保護回路の動作について説明する。

#### 【 0 0 9 7 】

まず、半導体チップが実装された後、即ち、第 1 のパッド 5 1 と第 2 のパッド 5 2 との間に ESD による高電圧が印加され得ない状況においては、上記第 2 のパッドには接地電源

10

20

30

40

50

V<sub>SS</sub>が接続され、上記第3のパッド53は内部電源V<sub>DD</sub>に接続される。

【0098】

すると、上記実施形態と同様の動作により、NMOSトランジスタN1がオンする。従ってNMOSトランジスタN2のゲートには、第2のパッド52を介して“L”レベルの電圧値が印加される。そのため、NMOSトランジスタN2はオフする。すると、ノード97には“L”レベルの電圧値が印加されるため、サイリスタ回路90はオフとなる。

【0099】

以上のように、クランプ回路55は非導通状態となるため、内部回路54の動作に影響を与えない。その結果、内部回路54の正常な動作を行うことが出来る。

【0100】

一方、半導体チップが実装される前、即ち、第1のパッド51と第2のパッド52との間に高電圧が印加され得る状況においては、第3のパッド53は抵抗回路67を介して接地される。

【0101】

すると、上記実施形態と同様の動作により、PMOSトランジスタP1はオンし得る状態となる。この時、ESDによって発生した高電圧が第1のパッド51と第2のパッド52との間に印加されると、第1のパッド51を介してPMOSトランジスタP1のソースには高電圧が印加され、PMOSトランジスタP1は完全にオンする。そのため、NMOSトランジスタN2のゲートにも高電圧が印加され、NMOSトランジスタN2はオンする。

【0102】

引き続き、NMOSトランジスタN2を介して、ESDによる高電圧がバイポーラトランジスタ95のベースに印加される。一方、バイポーラトランジスタ95のエミッタには第2のパッドを介して接地電源V<sub>SS</sub>により“L”レベルの電圧が印加されている。そのため、バイポーラトランジスタ95はオンとなる。

【0103】

さらに、バイポーラトランジスタ95を介して、バイポーラトランジスタ92のベースには接地電圧V<sub>SS</sub>により“L”レベルの電圧が印加される。一方、バイポーラトランジスタ92のエミッタにはESDにより高電圧が印加される。そのため、バイポーラトランジスタ92はオンする。

【0104】

以上の動作により、クランプ回路55は導通可能状態となる。従って、ESDにより発生した高電圧は、クランプ回路55に印加され、内部回路54に印加されない。即ち、ESDにより発生したESD電荷をサイリスタ回路90を介して第2のパッド52に抜き出すことが出来る。その結果、内部回路54を保護することが出来る。

【0105】

上記のように、高電圧をサイリスタ回路90の間に印加させることより、内部回路54を高電圧から保護する。ここで、一般的に上記のような構成を有するサイリスタ回路90は、MOSトランジスタに比べて多量の電流を流すことが出来る。そのため、上記実施形態に比べさらに多くの電流を流すことため、より小さな面積において多量の電流を流すことが出来る。その結果、チップサイズを低減することが出来る。

【0106】

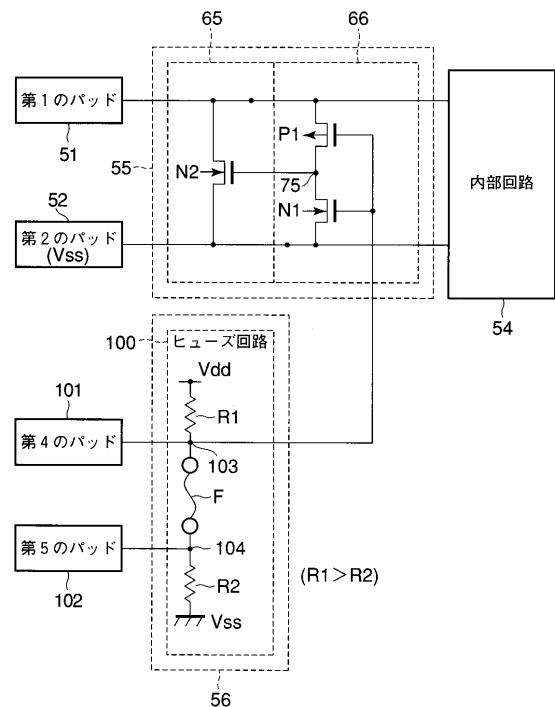

[第5の実施形態]

次に、図7を用いて第5の実施形態に係るESD保護回路を説明する。図7は第5の実施形態に係るESD保護回路を模式的に示した回路図である。以下の説明において、上記実施形態と重複する部分の説明を省略し、相違する部分について詳細に説明する。

【0107】

図7に示すように、制御回路56がヒューズ回路100から構成されている。上記ヒューズ回路100は、ヒューズF、抵抗素子R1、及び抵抗素子R2により構成される。

【0108】

10

20

30

40

50

上記ヒューズFの一端は第4のパッド101に接続されたノード103に接続され、他端は第5のパッド102に接続されたノード104に接続される。抵抗素子R1の一端は内部電源Vddに接続され、他端はノード103に接続される。抵抗素子R2の一端は接地電源Vssに接続され、他端はノード104に接続される。尚、上記実施形態と同様に第2のパッド52は接地用の端子であり、半導体集積回路内の接地電源線に接続されている。

#### 【0109】

次に、図7で示すESD保護回路の動作について説明する。

#### 【0110】

まず、半導体チップが実装される前、即ち、第1のパッド51と第2のパッド52との間に高電圧が印加され得る状況においては、ヒューズFはつながったままである。ここで、半導体チップが実装される前とは、例えばLSI等の半導体チップが工場から出荷される状況等をいう。上記のような状況では、ESDが印加され得る状況にあるためヒューズFをつなげたままにし、クランプ回路55を導通可能状態とする。

#### 【0111】

上記のようにヒューズFはつながれたままであるため、ノード103とノード104は導通している。また、Vddはオープンであるため、ノード103及び104には、“L”レベルの電圧が印加され、NMOSトランジスタN1はオフし、PMOSトランジスタP1はオンしうる状態になる。

#### 【0112】

この状態で、ESDによって発生した高電圧が第1のパッド51と第2のパッド52との間に印加されると、PMOSトランジスタP1のソースには高電圧が印加され、PMOSトランジスタP1は完全にオンする。さらに、高電圧がNMOSトランジスタN2のゲートに印加されるためNMOSトランジスタN2はオンする。

#### 【0113】

以上の動作により、クランプ回路55は導通可能状態となり高電圧はクランプ回路55を介して第1のパッド51と第2のパッド52との間に印加され、内部回路54に印加されない。その結果、ESDにより発生した高電圧から、内部回路54を保護することが出来る。

#### 【0114】

一方、半導体チップが実装された後、即ち、第1のパッド51と第2のパッド52との間にESDによる高電圧が印加され得ない状況においては、ヒューズFは溶断される。ここで、半導体チップが実装された後とは、例えばLSI等の半導体チップがボードに組み立てられた後における状況等をいう。このような状況においては、ESDが印加される可能性が極めて少ない。従って、第4のパッド101と第5のパッド102との間に高電圧を印加してヒューズFを溶断し、クランプ回路55を非導通状態とすれば良い。

#### 【0115】

上記のようにヒューズFは溶断されているため、ノード103には“H”レベルの電圧が印加され、PMOSトランジスタP1のゲート及びNMOSトランジスタN1のゲートには“H”レベルの電圧が印加される。従って、PMOSトランジスタP1はオフし、NMOSトランジスタN1はオンする。さらに、NMOSトランジスタN2のゲートには第2のパッド52を介して“L”レベルの電圧が印加される。そのため、NMOSトランジスタN2はオフする。

#### 【0116】

以上の動作により、クランプ回路55は非導通状態となるため、内部回路54の動作に影響を与えない。その結果、内部回路54の正常な動作を行うことが出来る。

#### 【0117】

上記第1乃至第4の実施形態に係る制御回路においては、半導体チップの実装後の実使用時には、制御回路の外部である第3のパッド53から常時電圧を印加する必要がある。しかし、この第5の実施形態に係る制御回路56においては、ヒューズFを切った後は、常

10

20

30

40

50

時第4のパッド101及び第5のパッド102に電圧を印加する必要がない。このため、制御回路56の取り扱いを容易にすることが出来る。

#### 【0118】

尚、上記実施形態において制御回路56の一実施形態として、抵抗回路56やヒューズ回路100を示した。しかし、制御回路56の実施形態はこれに限ったことではなく、半導体チップが実装されたか否かに応じたデータがプログラムされるプログラマブル回路であればよい。

#### 【0119】

上記プログラマブル回路の一例として、例えば不揮発性メモリ等が考えられる。さらに、内部回路54に不揮発性メモリが含まれる場合には、内部回路54と同時に作り込むことが出来る。そのため、製造コストを低減し、製造を容易にすることが出来る。10

#### 【0120】

##### [第6の実施形態]

次に、図8を用いて第6の実施形態に係るESD保護回路について説明する。図8はESD保護回路を模式的に示す回路図である。以下の説明において、上記実施形態と重複する部分の説明を省略し、相違する部分について詳細に説明する。

#### 【0121】

上記第1乃至第5の実施形態においては、一対の第1のパッド51及び第2のパッド52が内部回路54に接続される場合を例に挙げて説明したが、実際には多数のパッドが内部回路54に接続されている。20

#### 【0122】

即ち、図8に示すように、内部回路54を囲む4辺の外部端子に、夫々多数のパッド（第1のパッド51及び第2のパッド52を代表的に示す）が接続される。上記第1のパッドと第2のパッドの間には、夫々クランプ回路55が接続される。上記夫々のクランプ回路55は、単一の制御回路56の制御により電圧・電流特性が制御される。さらに、制御回路は第3のパッド53に接続される。

#### 【0123】

図8に示すESD保護回路の動作については、上記実施形態と同様であるのでその説明を省略する。

#### 【0124】

上記のように、内部回路54を囲む4辺の外部端子に、夫々多数のパッドが接続され、第1のパッドと第2のパッドの間には、夫々クランプ回路55が接続される。そのため、4辺の外部端子に接続されたパッドのいずれかにESDによる高電圧が印加された場合であっても、高電圧はクランプ回路55に印加され、内部回路54には印加されない。その結果、内部回路54を保護することが出来る。30

#### 【0125】

さらに、上記のように夫々のクランプ回路55は、単一の制御回路56の制御によりその電圧・電流特性が制御される。そのため、複数のクランプ回路55を用いる場合であっても新たに制御回路56を増加する必要がなく、製造コストを低減することが出来る。

#### 【0126】

尚、上記実施形態において、クランプ回路55はMOSトランジスタ、バイポーラトランジスタ、サイリスタ等の素子を用いて説明した。しかし、実施形態としては上記の素子に限ったことではなく、制御回路56からの制御信号に応答してオン／オフ制御され、クランプ回路55を導通可能状態又は非導通状態にするスイッチ素子であればよい。

#### 【0127】

また、制御回路56を電源電圧検出回路で構成し、内部回路54に電源電圧が印加されている時にクランプ回路55を非導通状態、電源電圧が印加されていない時にはクランプ回路55を導通可能状態に制御することも可能である。

#### 【0128】

以上、第1乃至第6の実施形態を用いてこの発明の説明を行ったが、この発明は上記各実40

施形態に限定されるものではなく、実施段階ではその要旨を逸脱しない範囲で種々に変形することが可能である。また、上記各実施形態には種々の段階の発明が含まれており、開示される複数の構成要件の適宜な組み合わせにより種々の発明が抽出され得る。例えば各実施形態に示される全構成要件からいくつかの構成要件が削除されても、発明が解決しようとする課題の欄で述べた課題の少なくとも1つが解決でき、発明の効果の欄で述べられている効果の少なくとも1つが得られる場合には、この構成要件が削除された構成が発明として抽出され得る。

### 【0129】

#### 【発明の効果】

以上説明したようにこの発明によれば、微細化しても設計や製造が容易で、製造コストを 10 低減し、チップサイズを低減することが出来る ESD 保護回路が得られる。

#### 【図面の簡単な説明】

【図1】この発明に係る ESD 保護回路の概略構成を説明するための回路図。

【図2】図1に示すクランプ回路の電圧 - 電流特性を模式的に示す図。

【図3】この発明の第1の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図4】この発明の第2の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図5】この発明の第3の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図6】この発明の第4の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図7】この発明の第5の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図8】この発明の第6の実施形態に係る ESD 保護回路を模式的に示す回路図。

【図9】従来例1に係る ESD 保護回路を示す回路図。

【図10】従来例1に係るクランプ回路の電圧 - 電流特性を示す図。

【図11】従来例2に係る ESD 保護回路を示す回路図。

【図12】従来例2に係るクランプ回路の電圧 - 電流特性を示す図。

【図13】従来例3に係る ESD 保護回路を示す回路図。

#### 【符号の説明】

51... 第1のパッド、52... 第2のパッド、53... 第3のパッド、54... 内部回路、55... クランプ回路、56... 制御回路。

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(72)発明者 崎濱 和久

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

(72)発明者 山口 明

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

F ターム(参考) 5F038 BE08 BH07 BH13 DF17 EZ20