(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6177155号

(P6177155)

(45) 発行日 平成29年8月9日(2017.8.9)

(24) 登録日 平成29年7月21日(2017.7.21)

(51) Int.Cl.

F 1

H03L 7/187 (2006.01)

H03L 7/099 (2006.01)H03L 7/187

H03L 7/099 110

請求項の数 9 (全 30 頁)

(21) 出願番号 特願2014-23064 (P2014-23064)

(22) 出願日 平成26年2月10日 (2014.2.10)

(65) 公開番号 特開2015-149694 (P2015-149694A)

(43) 公開日 平成27年8月20日 (2015.8.20)

審査請求日 平成28年1月14日 (2016.1.14)

(73) 特許権者 316005926

ソニーセミコンダクタソリューションズ株

式会社

神奈川県厚木市旭町四丁目14番1号

(74) 代理人 110001357

特許業務法人つばさ国際特許事務所

(72) 発明者 田村 昌久

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 竹内 秀倫

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 橋本 和志

最終頁に続く

(54) 【発明の名称】発振回路および周波数シンセサイザ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、前記第2のコード値に基づいて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を備え、

前記演算部は、

10

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

発振回路。

## 【請求項 2】

前記第1の入力コード値の補正による前記発振信号の周波数の変化方向と、前記第2の入力コード値の補正による前記発振信号の周波数の変化方向とは、互いに反対方向である

20

請求項 1 に記載の発振回路。

**【請求項 3】**

前記第 2 の入力コード値の補正量は、前記第 1 の感度と前記第 2 の感度との感度比、および前記第 1 の入力コード値の補正量に応じた量である

請求項 1 または請求項 2 に記載の発振回路。

**【請求項 4】**

前記比較部は、さらに、前記第 1 のコード値と、前記第 1 の所定の範囲の上限値および下限値とを比較して、前記比較結果値を生成する

請求項 1 から請求項 3 のいずれか一項に記載の発振回路。

**【請求項 5】**

前記比較結果値は、前記第 1 のコード値が前記第 2 の所定の範囲の上限値よりも大きい場合には正の値であり、前記第 1 のコード値が前記第 2 の所定の範囲の下限値よりも小さい場合には負の値であり、

前記補正部は、前記第 2 の入力コード値を前記累積値の分だけ増やすことにより前記第 2 の入力コード値を補正し、前記第 1 の入力コード値を、前記第 2 の感度を前記第 1 の感度で除算した値と前記累積値との積の分だけ減らすことにより前記第 1 の入力コード値を補正する

請求項 1 から請求項 4 のいずれか一項に記載の発振回路。

**【請求項 6】**

前記発振部は、

インダクタと

前記インダクタと並列接続され、前記第 1 のコード値に基づいて容量値が変化する第 1 の可変容量バンクと、

前記インダクタと並列接続され、前記第 2 のコード値に基づいて容量値が変化する第 2 の可変容量バンクと

を有する

請求項 1 から請求項 5 のいずれか一項に記載の発振回路。

**【請求項 7】**

前記第 1 の可変容量バンクは、前記第 1 の感度に対応する変化率で容量値が変化する第 1 の可変容量素子を複数有し、

前記第 2 の可変容量バンクは、前記第 2 の感度に対応する変化率で容量値が変化する第 2 の可変容量素子を複数有する

請求項 6 に記載の発振回路。

**【請求項 8】**

基準位相信号を生成する基準位相生成回路と、

前記基準位相信号と帰還位相信号との位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第 1 の入力コード値および第 2 の入力コード値を生成する周波数制御回路と、

前記第 1 の入力コード値および前記第 2 の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号の位相を求めて前記帰還位相信号として出力する位相検出回路とを備え、

前記発振回路は、

前記第 1 の入力コード値を補正することにより、前記第 1 の入力コード値のとりうる範囲より狭い第 1 の所定の範囲内の第 1 のコード値を生成し、前記第 1 の入力コード値の補正量に応じて前記第 2 の入力コード値を補正して第 2 のコード値を生成する演算部と、

前記第 1 のコード値に応じて第 1 の感度で発振信号の周波数が変化し、前記第 2 のコード値に応じて前記第 1 の感度よりも高い第 2 の感度で前記発振信号の周波数が変化する発振部と

を有し、

10

20

30

40

50

前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

周波数シンセサイザ。

【請求項9】

入力クロック信号と帰還クロック信号との間の位相差を検出する位相比較回路と、

10

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号を分周して前記帰還クロック信号を生成する分周回路と

を備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

20

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有し、

前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

30

を有する

周波数シンセサイザ。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、デジタル信号により発振周波数を制御する発振回路、およびそのような発振回路を備えた周波数シンセサイザに関する。

【背景技術】

【0002】

半導体装置には、所望の周波数の信号を生成するために、しばしば周波数シンセサイザが搭載される。周波数シンセサイザは、例えばアナログPLL(Phase Locked Loop)により実現することができる。アナログPLLは、アナログの制御電圧に応じて発振周波数を変化させることができる電圧制御発振回路(VCO; Voltage Controlled Oscillator)を含んで構成される。このようなアナログPLLでは、発振周波数が一定になるように、制御電圧が制御されるようになっている。

40

【0003】

近年、半導体製造プロセスの世代が進むにつれて、デバイスの耐圧が低下し、それに応じて半導体装置の電源電圧が低下してきている。これにより、アナログPLLでは、電圧制御発振回路の制御電圧の電圧範囲が狭くなってしまうため、広い周波数範囲の発振信号を生成しにくくなっている。そこで、デジタル信号により発振周波数を制御するデジ

50

タル制御発振回路（D C O ; Digitally Controlled Oscillator）を有するデジタルPLLがしばしば用いられるようになってきている。例えば、特許文献1には、分数部ビットと整数部ビットとを含む周波数制御ワードに基づいて、上位の可変容量バンクと下位の可変容量バンクの周波数を制御するデジタル制御発振回路が開示されている。

**【先行技術文献】**

**【特許文献】**

**【0 0 0 4】**

**【特許文献1】特開2009-10599号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

10

**【0 0 0 5】**

ところで、発振回路では、一般に、位相雑音を低減することが望まれておあり、デジタル制御発振回路においても、位相雑音の低減が期待されている。

**【0 0 0 6】**

本開示はかかる問題点に鑑みてなされたもので、その目的は、位相雑音を低減することができる発振回路および周波数シンセサイザを提供することにある。

**【課題を解決するための手段】**

**【0 0 0 7】**

本開示の発振回路は、演算部と、発振部とを備えている。演算部は、第1の入力コード値を補正することにより、第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成するものである。発振部は、第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、第2のコード値に基づいて第1の感度よりも高い第2の感度で発振信号の周波数が変化するものである。上記演算部は、比較部と、累積加算部と、補正部とを有している。比較部は、第1のコード値と、第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成するものである。累積加算部は、比較結果値を累積加算して累積値を求めるものである。補正部は、累積値に基づいて第1の入力コード値を補正するとともに第2の入力コード値を補正するものである。

20

**【0 0 0 8】**

30

本開示の第1の周波数シンセサイザは、基準位相生成回路と、位相比較回路と、周波数制御回路と、発振回路と、位相検出回路とを備えている。基準位相生成回路は、基準位相信号を生成するものである。位相比較回路は、基準位相信号と帰還位相信号との位相差を検出するものである。周波数制御回路は、位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成するものである。発振回路は、第1の入力コード値および第2の入力コード値に基づいて発振信号を生成するものである。位相検出回路は、発振信号の位相を求めて帰還位相信号として出力するものである。上記発振回路は、演算部と、発振部とを有している。演算部は、第1の入力コード値を補正することにより、第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成するものである。発振部は、第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、第2のコード値に基づいて第1の感度よりも高い第2の感度で発振信号の周波数が変化するものである。上記演算部は、比較部と、累積加算部と、補正部とを有している。比較部は、第1のコード値と、第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成するものである。累積加算部は、比較結果値を累積加算して累積値を求めるものである。補正部は、累積値に基づいて第1の入力コード値を補正するとともに第2の入力コード値を補正するものである。

40

**【0 0 0 9】**

本開示の第2の周波数シンセサイザは、位相比較回路と、周波数制御回路と、発振回路と、分周回路とを備えている。位相比較回路は、入力クロック信号と帰還クロック信号と

50

の間の位相差を検出するものである。周波数制御回路は、位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成するものである。発振回路は、第1の入力コード値および第2の入力コード値に基づいて発振信号を生成するものである。分周回路は、発振信号を分周して帰還クロック信号を生成するものである。上記発振回路は、演算部と、発振部とを有している。演算部は、第1の入力コード値を補正することにより、第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成するものである。発振部は、第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、第2のコード値に基づいて第1の感度よりも高い第2の感度で発振信号の周波数が変化するものである。上記演算部は、比較部と、累積加算部と、補正部とを有している。比較部は、第1のコード値と、第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成するものである。累積加算部は、比較結果値を累積加算して累積値を求めるものである。補正部は、累積値に基づいて第1の入力コード値を補正するとともに第2の入力コード値を補正するものである。

10

。

## 【0010】

本開示の発振回路、第1の周波数シンセサイザ、および第2の周波数シンセサイザでは、第1の入力コード値および第2の入力コード値に基づいて第1のコード値および第2のコード値が生成され、これらの第1のコード値および第2のコード値に基づいて発振信号が生成される。その際、第1の入力コード値が補正されることにより、第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値が生成され、第1の入力コード値の補正量に応じて第2の入力コード値が補正され、第2のコード値が生成される。

20

## 【発明の効果】

## 【0011】

本開示の発振回路および周波数シンセサイザによれば、第1の入力コード値を補正することにより、第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成したので、位相雑音を低減することができる。なお、ここに記載された効果は必ずしも限定されるものではなく、本開示中に記載されたいずれの効果があつてもよい。

30

## 【図面の簡単な説明】

## 【0012】

【図1】本開示の実施の形態に係る周波数シンセサイザの一構成例を表すブロック図である。

【図2】図1に示した発振回路の周波数制御特性を表す説明図である。

【図3】図1に示した発振回路の一構成例を表すブロック図である。

【図4】図3に示した制御部の一構成例を表すブロック図である。

40

【図5】図4に示した制御回路の一構成例を表すブロック図である。

【図6】図5に示した比較回路の一動作例を表す説明図である。

【図7】図3に示した発振部の一構成例を表すブロック図である。

【図8】図7に示した粗調整用の可変容量バンクの一構成例を表す回路図である。

【図9】図7に示した微調整用の可変容量バンクの一構成例を表す回路図である。

【図10】図1に示した周波数シンセサイザの一動作例を表すタイミング図である。

【図11】図1に示した周波数シンセサイザの一動作例を表す説明図である。

【図12】図1に示した周波数シンセサイザの他の動作例を表すタイミング図である。

【図13】図1に示した周波数シンセサイザの他の動作例を表す説明図である。

【図14】図1に示した周波数シンセサイザの他の動作例を表すタイミング図である。

50

【図15】比較例に係る周波数シンセサイザの一動作例を表すタイミング図である。

【図16】図1に示した周波数シンセサイザの他の動作例を表すタイミング図である。

【図17】図1に示した周波数シンセサイザの他の動作例を表す説明図である。

【図18】実施の形態の変形例に係る周波数シンセサイザの一構成例を表すブロック図である。

#### 【発明を実施するための形態】

##### 【0013】

以下、本開示の実施の形態について、図面を参照して詳細に説明する。

##### 【0014】

###### [構成例]

###### (全体構成例)

10

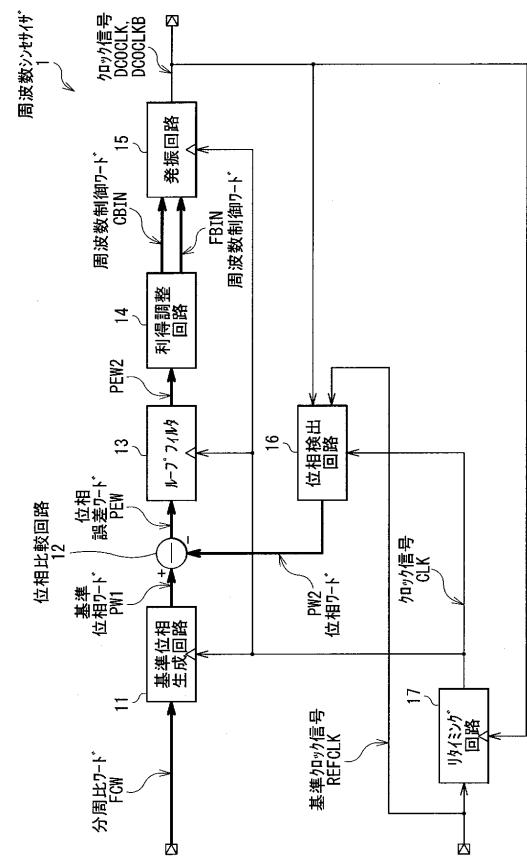

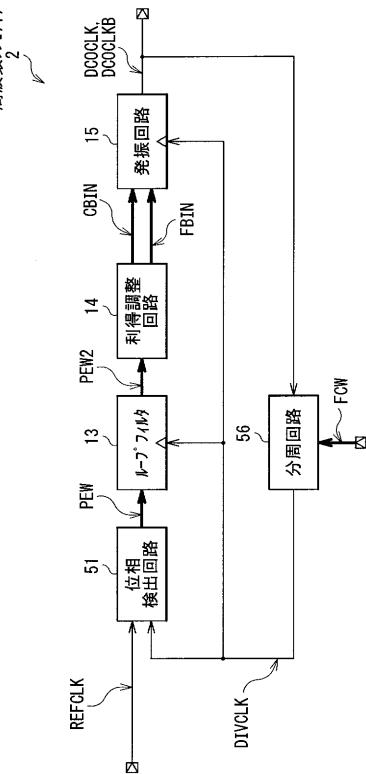

図1は、第1の実施の形態に係る周波数シンセサイザの一構成例を表すものである。図1では、太線で示した配線は、複数のビットからなるワードを伝えるいわゆるバス配線を示し、細線で示した配線は、1つの信号または差動信号を伝える配線を示す。周波数シンセサイザ1は、デジタル制御発振回路(DCO)を有するデジタルPLLである。なお、本開示の実施の形態に係る発振回路は、本実施の形態により具現化されるので、併せて説明する。

##### 【0015】

周波数シンセサイザ1は、基準位相生成回路11と、位相比較回路12と、ループフィルタ13と、利得調整回路14と、発振回路15と、位相検出回路16と、リタイミング回路17とを備えている。

20

##### 【0016】

基準位相生成回路11は、分周比ワードFCWおよびクロック信号CLKに基づいて、基準位相ワードPW1を生成するものである。具体的には、基準位相生成回路11は、分周比ワードFCWが示す値を累積加算して、基準位相値を生成し、その基準位相値を基準位相ワードPW1として出力するようになっている。

##### 【0017】

位相比較回路12は、基準位相ワードPW1および位相ワードPW2に基づいて、位相誤差ワードPEWを生成するものである。具体的には、位相比較回路12は、基準位相ワードPW1が示す基準位相値から、位相ワードPW2が示す位相値を減算することにより、位相誤差値を求め、その位相誤差値を位相誤差ワードPEWとして出力するようになっている。

30

##### 【0018】

ループフィルタ13は、位相誤差ワードPEWおよびクロック信号CLKに基づいて、位相誤差ワードPEW2を生成するものである。具体的には、ループフィルタ13は、位相誤差ワードPEWが示す位相誤差値を平滑化し、その平滑化された位相誤差値を位相誤差ワードPEW2として出力するようになっている。

##### 【0019】

利得調整回路14は、位相誤差ワードPEW2に基づいて、周波数制御ワードCBIN, FBINを生成するものである。周波数制御ワードCBINは、周波数fo(後述)を粗調整するためのワードであり、周波数制御ワードFBINは、周波数foを微調整するためのワードである。粗調整用の周波数制御ワードCBINは、この例では、7ビット(CBIN[6:0])からなるバイナリーフォーマットのワードであり、符号なし(unsigned)数値(0~127)を示すものである。また、微調整用の周波数制御ワードFBINは、この例では、10ビット(FBIN[9:0])からなるバイナリーフォーマットのワードであり、符号付き(signed)数値(-512~+511)を示すものである。この利得調整回路14は、位相誤差ワードPEW2が示す値に所定の値(利得)を乗算し、その乗算結果に基づいて周波数制御ワードCBIN, FBINを生成するようになっている。

40

##### 【0020】

50

発振回路 15 は、周波数制御ワード C B I N , F B I N およびクロック信号 C L K に基づいて、クロック信号 D C O C L K , D C O C L K B を生成するものである。ここで、クロック信号 D C O C L K , D C O C L K B は、互いに位相が 180 度ずれた信号であり、差動信号を構成するものである。なお、この例では、発振回路 15 が生成するクロック信号は、クロック信号 D C O C L K , D C O C L K B からなる差動信号としたが、これに限定されるものではなく、これに代えて、シングルエンド信号であってもよい。

#### 【 0 0 2 1 】

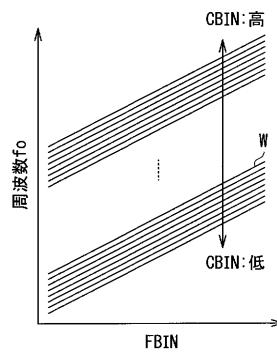

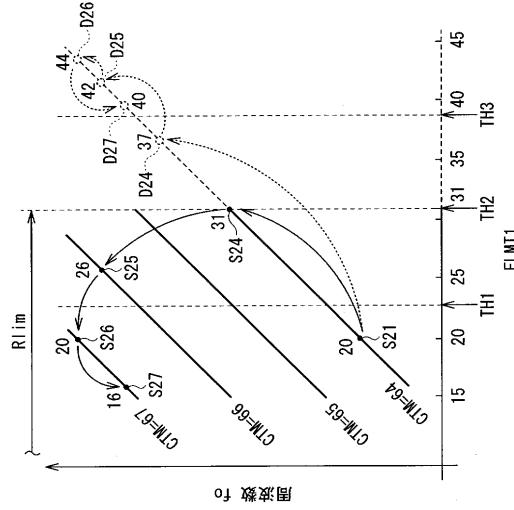

図 2 は、発振回路 15 の周波数制御特性を表すものである。図 2 において、横軸は、周波数制御ワード F B I N の値を示し、縦軸は、クロック信号 D C O C L K , D C O C L K B の周波数  $f_o$  を示す。図 2 では、複数（この例では 128）の制御特性 W を示している。発振回路 15 は、周波数制御ワード C B I N の値に応じて、複数の周波数制御特性 W のうちの 1 つを選択する。この例では、周波数制御ワード C B I N の値が低いほど周波数  $f_o$  は低く、周波数制御ワード C B I N の値が高いほど周波数  $f_o$  は高い。また、発振回路 15 は、周波数制御ワード F B I N の値に応じて、クロック信号 D C O C L K , D C O C L K B の周波数  $f_o$  を変化させる。この例では、周波数制御ワード F B I N の値が低いほど周波数  $f_o$  は低く、周波数制御ワード F B I N の値が高いほど周波数  $f_o$  は高い。図 2 に示したように、周波数制御ワード C B I N を変化させたときの周波数  $f_o$  の変化量は、周波数制御ワード F B I N を変化させたときの周波数  $f_o$  の変化量よりも大きい。このようにして、発振回路 15 では、周波数制御ワード C B I N により周波数  $f_o$  の粗調整を行い、周波数制御ワード F B I N により周波数  $f_o$  の微調整を行うようになっている。

#### 【 0 0 2 2 】

位相検出回路 16 は、クロック信号 D C O C L K , D C O C L K B 、基準クロック信号 R E F C L K 、およびクロック信号 C L K に基づいて、位相ワード P W 2 を生成するものである。具体的には、位相検出回路 16 は、クロック信号 D C O C L K , D C O C L K B により構成される差動信号の位相を固定小数点フォーマットの値として求め、その値を、位相ワード P W 2 として、クロック信号 C L K に基づくタイミングで出力するようになっている。

#### 【 0 0 2 3 】

リタイミング回路 17 は、基準クロック信号 R E F C L K をクロック信号 D C O C L K , D C O C L K B に基づくタイミングでリタイミングして、クロック信号 C L K として出力するものである。

#### 【 0 0 2 4 】

この構成により、周波数シンセサイザ 1 では、クロック信号 D C O C L K , D C O C L K B の周波数  $f_o$  が、基準クロック信号 R E F C L K の周波数と分周比ワード F C W が示す値との積（目標周波数  $f_{target}$ ）になるように負帰還制御される。すなわち、例えば、周波数  $f_o$  が目標周波数  $f_{target}$  よりも高い場合には、位相ワード P W 2 が示す値が、基準位相ワード P W 1 が示す値よりも大きくなり、位相誤差ワード P E W が示す値が小さくなるため、発振回路 15 は周波数  $f_o$  を低下させる。また、例えば、周波数  $f_o$  が目標周波数  $f_{target}$  よりも低い場合には、位相ワード P W 2 が示す値が、基準位相ワード P W 1 が示す値より小さくなり、位相誤差ワード P E W が示す値が大きくなるため、発振回路 15 は周波数  $f_o$  を上昇させる。このようにして、周波数シンセサイザ 1 では、クロック信号 D C O C L K , D C O C L K B の周波数  $f_o$  が目標周波数  $f_{target}$  になるように、負帰還制御されるようになっている。

#### 【 0 0 2 5 】

その際、周波数シンセサイザ 1 は、この例では、2 段階で負帰還制御するようになっている。具体的には、周波数シンセサイザ 1 は、例えば、電源投入直後などの初期状態では、微調整用の周波数制御ワード F B I N を所定値に固定し、粗調整用の周波数制御ワード C B I N を変化させて負帰還動作を行うことにより、周波数  $f_o$  を目標周波数  $f_{target}$  に近付ける。そして、その後に、周波数シンセサイザ 1 は、粗調整用の周波数制御ワード C B I N を固定し、微調整用の周波数制御ワード F B I N を変化させて負帰還動作を行うこ

10

20

30

40

50

とにより、周波数  $f_o$  を目標周波数  $f_{target}$  により近付け、位相同期状態を実現するようになっている。

#### 【0026】

(発振回路15)

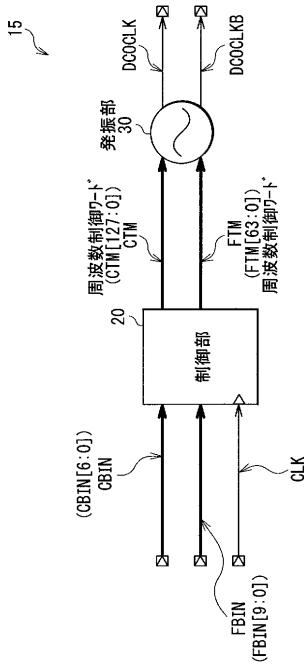

図3は、発振回路15の一構成例を表すものである。発振回路15は、制御部20と、発振部30とを有している。

#### 【0027】

制御部20は、周波数制御ワードCBIN, FBINおよびクロック信号CLKに基づいて、周波数制御ワードCBIN, FBINを、サーモメータコードを示す周波数制御ワードCTM, FTMに変換し、この周波数制御ワードCTM, FTM用いて発振部30を10制御するものである。周波数制御ワードCTMは、周波数を粗調整するためのワードであり、128ビット(CTM[127:0])からなるサーモメータコードを示すものである。また、周波数制御ワードFTMは、周波数を微調整するためのワードであり、この例では、64ビット(FTM[63:0])からなるサーモメータコードを示すものである。この制御部20は、後述するように、周波数制御ワードFBINが示す値に基づいて、周波数制御ワードFBINが示す値が取りうる範囲(この例では-512~+511)より狭い範囲(この例では0~63)の値を示す周波数制御ワードFTMを生成するとともに、周波数制御ワードFBIN, CBINに基づいて周波数制御ワードCTMを生成するようになっている。

#### 【0028】

20

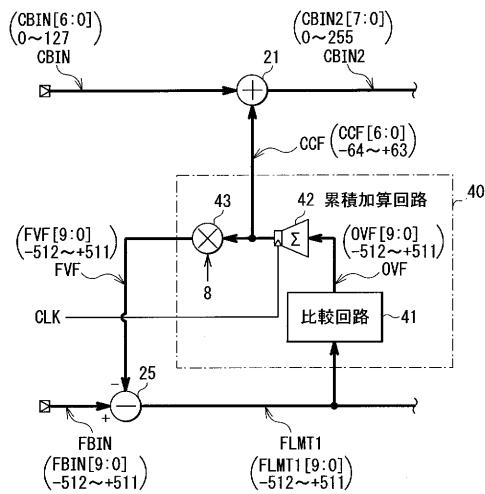

図4は、制御部20の一構成例を表すものである。制御部20は、加算回路21と、リミッタ22と、エンコーダ23と、フリップフロップ24と、減算回路25と、リミッタ26と、符号変換回路27と、エンコーダ28と、フリップフロップ29と、制御回路40とを有している。加算回路21、リミッタ22、エンコーダ23、およびフリップフロップ24は、粗調整用の周波数制御ワードCBINに係るものであり、減算回路25、リミッタ26、符号変換回路27、エンコーダ28、およびフリップフロップ29は、微調整用の周波数制御ワードFBINに係るものである。

#### 【0029】

30

加算回路21は、粗調整用の周波数制御ワードCBINが示す値と補正ワードCCFが示す値を加算して、その加算結果を示す周波数制御ワードCBIN2を生成するものである。補正ワードCCFは、この例では、7ビット(CCF[6:0])からなるバイナリーフォーマットのワードであり、符号付き数値(-64~+63)を示すものである。また、周波数制御ワードCBIN2は、この例では、8ビット(CBIN2[7:0])からなるバイナリーフォーマットのワードであり、符号なし数値(0~255)を示すものである。この周波数制御ワードCBIN2の値は、リミッタ22により規定される範囲の範囲内(この例では0~127の範囲内)に収まるように動作するようになっている。

#### 【0030】

リミッタ22は、周波数制御ワードCBIN2が示す値が所定の範囲外である場合に、その値をその所定の範囲の下限値または上限値に制限することにより、周波数制御ワードCLMTを生成するものである。この例では、上限値は“127”であり、下限値は“0”である。周波数制御ワードCLMTは、この例では、7ビット(CLMT[6:0])からなるバイナリーフォーマットのワードであり、符号なし数値(0~127)を示すものである。

#### 【0031】

40

エンコーダ23は、周波数制御ワードCLMTに基づいてサーモメータコードを生成するものである。フリップフロップ24は、エンコーダ23が生成したサーモメータコードをクロック信号CLKに基づくタイミングでリタイミングして、周波数制御ワードCTM(CTM[127:0])として出力するものである。これにより、周波数制御ワードCTMでは、例えば、最下位ビットCTM[0]から順

#### 【0032】

50

減算回路 25 は、微調整用の周波数制御ワード F B I N が示す値から補正ワード F C F が示す値を減算して、その減算結果を示す周波数制御ワード F L M T 1 を生成するものである。補正ワード F C F は、この例では、10 ビット ( F C F [ 9 : 0 ] ) からなるバイナリーフォーマットのワードであり、符号付き数値 ( - 512 ~ + 511 ) を示すものである。また、周波数制御ワード F L M T 1 は、この例では、10 ビット ( F L M T 1 [ 9 : 0 ] ) からなるバイナリーフォーマットのワードであり、符号付き数値 ( - 512 ~ + 511 ) を示すものである。後述するように、周波数制御ワード F L M T 1 の値は、リミッタ 26 により規定される範囲 R Lim の範囲内（この例では - 32 ~ + 31 の範囲内）に収まるように制御されるようになっている。

## 【 0033】

10

リミッタ 26 は、周波数制御ワード F L M T 1 が示す値が所定の範囲 R Lim の範囲外である場合に、その値をその所定の範囲 R Lim の下限値または上限値に制限することにより、周波数制御ワード F L M T 2 を生成するものである。この例では、上限値は “ + 31 ” であり、下限値は “ - 32 ” である。周波数制御ワード F L M T 2 は、この例では、6 ビット ( F L M T 2 [ 5 : 0 ] ) からなるバイナリーフォーマットのワードであり、符号付き数値 ( - 32 ~ + 31 ) を示すものである。

## 【 0034】

符号変換回路 27 は、符号付き数値を示す周波数制御ワード F L M T 2 を、符号なし数値を示す周波数制御ワード F U に変換するものである。周波数制御ワード F U は、この例では、6 ビット ( F U [ 5 : 0 ] ) からなるバイナリーフォーマットのワードであり、符号なし数値 ( 0 ~ 63 ) を示すものである。

20

## 【 0035】

エンコーダ 28 は、周波数制御ワード F U に基づいてサーモメータコードを生成するものである。フリップフロップ 29 は、エンコーダ 28 が生成したサーモメータコードをクロック信号 C L K に基づくタイミングでリタイミングして、周波数制御ワード F T M として出力するものである。これにより、周波数制御ワード F T M では、例えば、最下位ビット F T M [ 0 ] から順に、周波数制御ワード F U が示す値と同じ数だけ “ 1 ” が現れるようになっている。

## 【 0036】

制御回路 40 は、周波数制御ワード F L M T 1 およびクロック信号 C L K に基づいて、補正ワード C C F , F C F を生成するものである。具体的には、制御回路 40 は、周波数制御ワード F L M T 1 の値がリミッタ 26 により規定される範囲 R Lim の範囲内（この例では - 32 ~ + 31 の範囲内）に収まるように、補正ワード F C F を生成とともに、その補正ワード F C F に対応する補正ワード C C F を生成するようになっている。

30

## 【 0037】

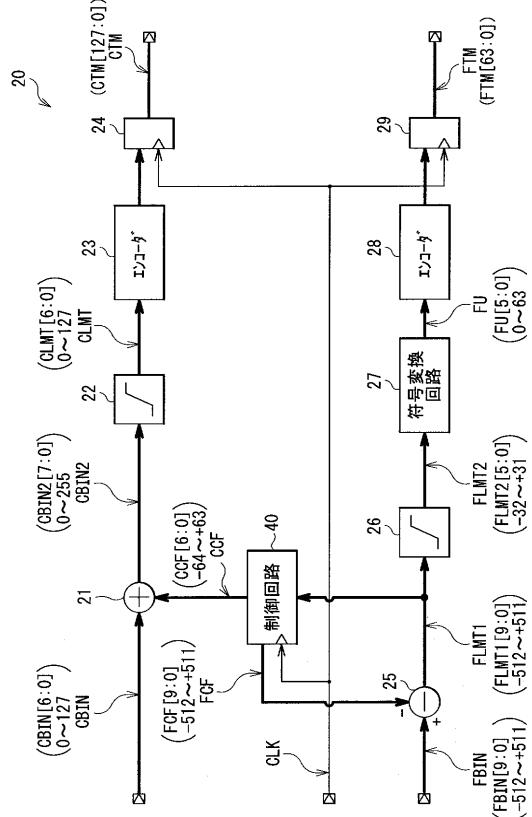

図 5 は、制御回路 40 の一構成例を表すものである。この図 5 では、制御回路 40 に加え、加算回路 21 および減算回路 25 をも示している。制御回路 40 は、比較回路 41 と、累積加算回路 42 と、乗算回路 43 とを有している。

## 【 0038】

40

比較回路 41 は、周波数制御ワード F L M T 1 が示す値と、複数の所定のしきい値とを比較して、比較結果を比較結果ワード O V F として出力するものである。比較結果ワード O V F は、この例では、10 ビット ( O V F [ 9 : 0 ] ) からなるバイナリーフォーマットのワードであり、符号付き数値 ( - 512 ~ + 511 ) を示すものである。

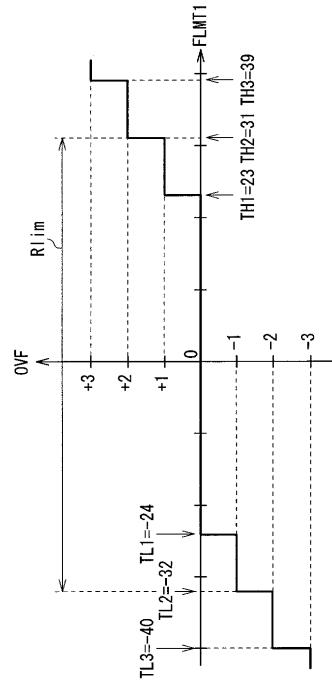

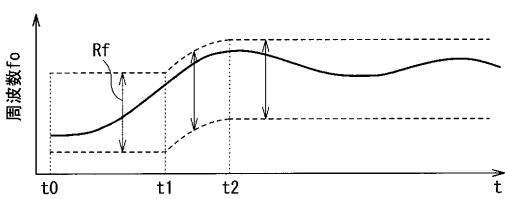

## 【 0039】

図 6 は、比較回路 41 の動作の一例を表すものである。図 6 には、リミッタ 26 により規定される範囲 R Lim についても併せて示している。比較回路 41 は、周波数制御ワード F L M T 1 が示す値と、複数のしきい値 T H 1 , T H 2 , T H 3 , ... および複数のしきい値 T L 1 , T L 2 , T L 3 , ... とを比較する。この例では、しきい値 T H 1 は “ 23 ” であり、しきい値 T H 2 は “ 31 ” であり、しきい値 T H 3 は “ 39 ” であり、しきい値 T L 1 は “ - 24 ” であり、しきい値 T L 2 は “ - 32 ” であり、しきい値 T L 3 は “ - 4 ”

50

0”である。すなわち、この例では、しきい値 T H 2 は範囲 R l i m の上限値と等しく、しきい値 T L 2 は範囲 R l i m の下限値と等しい。そして、比較回路 4 1 は、周波数制御ワード F L M T 1 が示す値が、しきい値 T L 1 以上でありかつしきい値 T H 1 以下である場合には“0”を示す比較結果ワード O V F を生成する。また、周波数制御ワード F L M T 1 が示す値が、しきい値 T H 1 より大きくかつしきい値 T H 2 以下である場合には“1”を示す比較結果ワード O V F を生成し、しきい値 T H 2 より大きくかつしきい値 T H 3 以下である場合には“2”を示す比較結果ワード O V F を生成する。周波数制御ワード F L M T 1 が示す値がさらに大きい場合についても同様である。また、周波数制御ワード F L M T 1 が示す値が、しきい値 T L 2 以上でありかつしきい値 T L 1 より小さい場合には“-1”を示す比較結果ワード O V F を生成し、しきい値 T L 3 以上でありかつしきい値 T L 2 より小さい場合には“-2”を示す比較結果ワード O V F を生成する。周波数制御ワード F L M T 1 が示す値がさらに小さい場合についても同様である。

10

#### 【0040】

累積加算回路 4 2 は、比較結果ワード O V F が示す値を累積加算し、その累積加算結果を補正ワード C C F として出力するものである。

#### 【0041】

乗算回路 4 3 は、補正ワード C C F が示す値に所定数（この例では“8”）を乗算し、その乗算結果を補正ワード F C F として出力するものである。この例では、乗算回路 4 3 は、補正ワード C C F を 3 ビット分シフトすることにより、“8”を乗ずる演算を実現している。この乗算値“8”は、後述するように、粗調整用の可変容量バンク 3 3 における各可変容量素子グループ 3 6 内の可変容量素子 3 5 の数に対応するものである。

20

#### 【0042】

この構成により、制御部 2 0 では、例えば、周波数制御ワード F L M T 1 がしきい値 T H 1 より大きい値を示す場合には、比較結果ワード O V F が示す値が大きくなり、補正ワード F C F が示す値もまた大きくなるため、減算回路 2 5 は周波数制御ワード F L M T 1 が示す値を小さくする。また、例えば、周波数制御ワード F L M T 1 がしきい値 T L 1 より小さい値を示す場合には、比較結果ワード O V F が示す値が小さくなり、補正ワード F C F が示す値もまた小さくなるため、減算回路 2 5 は周波数制御ワード F L M T 1 が示す値を大きくする。このようにして、制御部 2 0 では、周波数制御ワード F L M T 1 の値がリミッタ 2 6 により規定される範囲 R l i m の範囲内（この例では -3 2 ~ +3 1 の範囲内

30）に収まるように、負帰還制御されるようになっている。

#### 【0043】

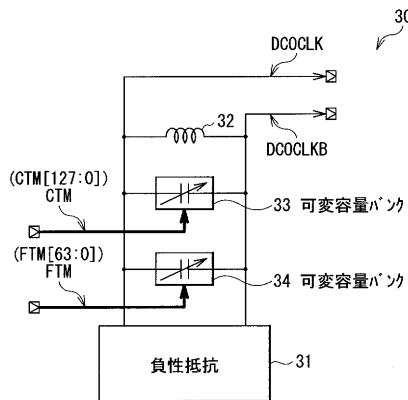

発振部 3 0 は、図 3 に示したように、周波数制御ワード C T M , F T M に基づいて、周波数制御ワード C T M , F T M に応じた周波数  $f_o$  のクロック信号 D C O C L K , D C O C L K B を生成するものである。

#### 【0044】

図 7 は、発振部 3 0 の一構成例を表すものである。発振部 3 0 は、負性抵抗 3 1 と、インダクタ 3 2 と、可変容量バンク 3 3 , 3 4 とを有している。

#### 【0045】

負性抵抗 3 1 は、トランジスタなどの能動素子を含んで構成されるものであり、一端と他端との間の抵抗値が負の極性をもつようにふるまうものである。負性抵抗 3 1 の一端は、インダクタ 3 2 の一端および可変容量バンク 3 3 , 3 4 の一端などに接続されるとともに、他端は、インダクタ 3 2 の他端および可変容量バンク 3 3 , 3 4 の他端などに接続されている。

40

#### 【0046】

インダクタ 3 2 の一端は、可変容量バンク 3 3 , 3 4 の一端および負性抵抗 3 1 の一端などに接続され、他端は、可変容量バンク 3 3 , 3 4 の他端および負性抵抗 3 1 の他端などに接続されている。

#### 【0047】

可変容量バンク 3 3 は、粗調整用の周波数制御ワード C T M に基づいて両端間のキャバ

50

シタンスが変化するものである。可変容量バンク 3 3 の一端は、インダクタ 3 2 の一端、可変容量バンク 3 4 の一端、および負性抵抗 3 1 の一端に接続されている。

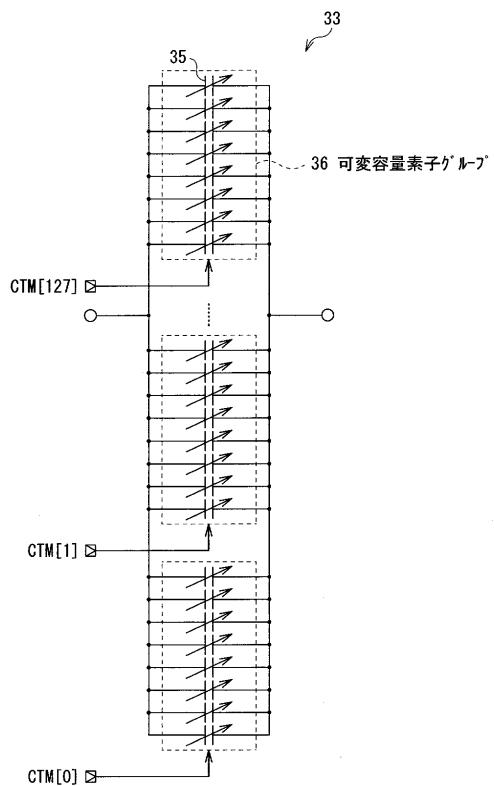

#### 【 0 0 4 8 】

図 8 は、可変容量バンク 3 3 の一構成例を表すものである。可変容量バンク 3 3 は、この例では、128 個の可変容量素子グループ 3 6 を有している。各可変容量素子グループ 3 6 は、周波数制御ワード C T M のビット C T M [ 127 : 0 ] のそれぞれと対応して設けられている。各可変容量素子グループ 3 6 は、この例では、8 つの可変容量素子 3 5 を有している。この可変容量素子 3 5 の数 “8” は、乗算回路 4 3 における乗算値 “8” に対応するものである。可変容量素子 3 5 は、容量制御端子に印加された電圧に基づいて両端間のキャパシタンスが変化するものである。これらの 8 つの可変容量素子 3 5 は、互いに並列接続されるとともに、容量制御端子も互いに接続されている。これにより可変容量素子グループ 3 6 は、可変容量素子 3 5 の 8 倍のキャパシタンスを有する可変容量素子として機能するようになっている。可変容量素子グループ 3 6 の 8 つの可変容量素子 3 5 の容量制御端子には、周波数制御ワード C T M の対応するビットに基づいて電圧が印加され、その印加された電圧に基づいて、可変容量素子グループ 3 6 の両端間のキャパシタンスが変化するようになっている。これらの可変容量素子グループ 3 6 は、互いに並列接続されている。この構成により、可変容量バンク 3 3 では、周波数制御ワード C T M に基づいて両端間のキャパシタンスが変化するようになっている。10

#### 【 0 0 4 9 】

可変容量バンク 3 4 は、微調整用の周波数制御ワード F T M に基づいて両端間のキャパシタンスが変化するものである。可変容量バンク 3 4 の一端は、インダクタ 3 2 の一端、可変容量バンク 3 3 の一端、および負性抵抗 3 1 の一端に接続されている。20

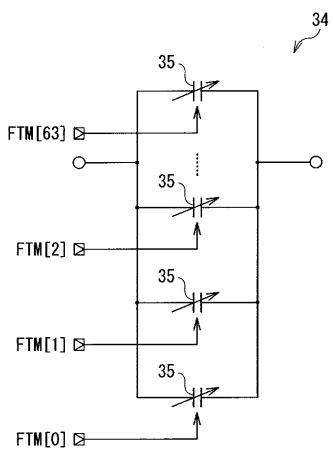

#### 【 0 0 5 0 】

図 9 は、可変容量バンク 3 4 の一構成例を表すものである。可変容量バンク 3 4 は、この例では、64 個の可変容量素子 3 5 を有している。各可変容量素子 3 5 は、周波数制御ワード F T M のビット F T M [ 63 : 0 ] のそれぞれと対応して設けられている。可変容量素子 3 5 の容量制御端子には、周波数制御ワード F T M の対応するビットに基づいて電圧が印加され、その印加された電圧に基づいて、可変容量素子 3 5 の両端間のキャパシタンスが変化するようになっている。これらの可変容量素子 3 5 は、互いに並列接続されている。この構成により、可変容量バンク 3 4 では、周波数制御ワード F T M に基づいて両端間のキャパシタンスが変化するようになっている。30

#### 【 0 0 5 1 】

可変容量バンク 3 3 と可変容量バンク 3 4 とでは、周波数制御ワード C T M , F T M のうちのビットが 1 つ変化したときの両端間のキャパシタンスの変化量が異なる。すなわち、この例では、周波数制御ワード C T M のビットが 1 つ変化することによる可変容量バンク 3 3 の両端間のキャパシタンスの変化量は、周波数制御ワード F T M のビットが 1 つ変化することによる可変容量バンク 3 4 の両端間のキャパシタンスの変化量の 8 倍になっている。

#### 【 0 0 5 2 】

この構成により、発振部 3 0 は、インダクタ 3 2 のインダクタンス、および可変容量バンク 3 3 , 3 4 のキャパシタンスによって画定される共振周波数（周波数  $f_0$ ）で発振動作を行い、クロック信号 D C O C L K , D C O C L K B を生成する。その際、周波数制御ワード C T M を変化させたときの周波数  $f_0$  の変化量は、周波数制御ワード F T M を変化させたときの周波数  $f_0$  の変化量よりも大きくなる。これにより、発振部 3 0 では、周波数制御ワード C T M に基づいて周波数  $f_0$  の粗調整を行うとともに、周波数制御ワード F T M に基づいて周波数  $f_0$  の微調整を行うことができるようになっている。40

#### 【 0 0 5 3 】

ここで、発振回路 1 5 は、本開示における「発振回路」の一具体例に対応する。制御回路 4 0 、加算回路 2 1 、および減算回路 2 5 は、本開示における「演算部」の一具体例に対応する。周波数制御ワード F B I N の値は、本開示における「第 1 の入力コード値」の50

一具体例に対応し、周波数制御ワード C B I N の値は、本開示における「第 2 の入力コード値」の一具体例に対応する。周波数制御ワード F L M T 1 の値は、本開示における「第 1 のコード値」の一具体例に対応し、周波数制御ワード C B I N 2 の値は、本開示における「第 2 のコード値」の一具体例に対応する。

#### 【 0 0 5 4 】

##### [ 動作および作用 ]

続いて、本実施の形態の周波数シンセサイザ 1 の動作および作用について説明する。

#### 【 0 0 5 5 】

##### ( 全体動作概要 )

まず、図 1 , 3 , 4などを参照して、周波数シンセサイザ 1 の全体動作概要を説明する 10 。基準位相生成回路 1 1 は、分周比ワード F C W およびクロック信号 C L K に基づいて、基準位相ワード P W 1 を生成する。位相比較回路 1 2 は、基準位相ワード P W 1 および位相ワード P W 2 に基づいて、位相誤差ワード P E W を生成する。ループフィルタ 1 3 は、位相誤差ワード P E W およびクロック信号 C L K に基づいて、位相誤差ワード P E W 2 を生成する。利得調整回路 1 4 は、位相誤差ワード P E W 2 に基づいて、周波数制御ワード C B I N , F B I N を生成する。発振回路 1 5 は、周波数制御ワード C B I N , F B I N およびクロック信号 C L K に基づいて、クロック信号 D C O C L K , D C O C L K B を生成する。具体的には、発振回路 1 5 では、制御部 2 0 が、周波数制御ワード C B I N , F B I N およびクロック信号 C L K に基づいて、周波数制御ワード C B I N , F B I N を周波数制御ワード C T M , F T M に変換し、発振部 3 0 が、周波数制御ワード C T M , F T M に基づいて、周波数制御ワード C T M , F T M に応じた周波数  $f_0$  のクロック信号 D C O C L K , D C O C L K B を生成する。位相検出回路 1 6 は、クロック信号 D C O C L K , D C O C L K B 、基準クロック信号 R E F C L K 、およびクロック信号 C L K に基づいて、位相ワード P W 2 を生成する。リタイミング回路 1 7 は、基準クロック信号 R E F C L K をクロック信号 D C O C L K , D C O C L K B に基づくタイミングでリタイミングして、クロック信号 C L K として出力する。 20

#### 【 0 0 5 6 】

制御部 2 0 では、加算回路 2 1 が、周波数制御ワード C B I N が示す値と補正ワード C C F が示す値を加算して、その加算結果を示す周波数制御ワード C B I N 2 を生成する。リミッタ 2 2 は、周波数制御ワード C B I N 2 が示す値が所定の範囲外である場合に、その値をその所定の範囲の下限値または上限値に制限することにより、周波数制御ワード C L M T を生成する。エンコーダ 2 3 は、周波数制御ワード C L M T に基づいてサーモメータコードを生成する。フリップフロップ 2 4 は、エンコーダ 2 3 が生成したサーモメータコードをクロック信号 C L K に基づくタイミングでリタイミングして、周波数制御ワード C T M として出力する。 30

#### 【 0 0 5 7 】

減算回路 2 5 は、周波数制御ワード F B I N が示す値から補正ワード F C F が示す値を減算して、その減算結果を示す周波数制御ワード F L M T 1 を生成する。制御回路 4 0 は、周波数制御ワード F L M T 1 およびクロック信号 C L K に基づいて、補正ワード C C F , F C F を生成する。リミッタ 2 6 は、周波数制御ワード F L M T 1 が示す値が所定の範囲 R l i m の範囲外である場合に、その値をその所定の範囲 R l i m の下限値または上限値に制限することにより、周波数制御ワード F L M T 2 を生成する。符号変換回路 2 7 は、符号付き数値を示す周波数制御ワード F L M T 2 を、符号なし数値を示す周波数制御ワード F U に変換する。エンコーダ 2 8 は、周波数制御ワード F U に基づいてサーモメータコードを生成する。フリップフロップ 2 9 は、エンコーダ 2 8 が生成したサーモメータコードをクロック信号 C L K に基づくタイミングでリタイミングして、周波数制御ワード F T M として出力する。 40

#### 【 0 0 5 8 】

##### ( 詳細動作 )

次に、周波数シンセサイザ 1 の詳細動作について説明する。周波数シンセサイザ 1 は、

例えば、電源投入直後などの初期状態では、微調整用の周波数制御ワード F B I N を所定の値（例えば“0”）に固定し、粗調整用の周波数制御ワード C B I N を変化させることにより負帰還動作を行う。その際、補正ワード C C F , F C F が示す値は“0”を維持するため、制御部 20 は、粗調整用の周波数制御ワード C B I N が示す値をサーモメータコードに変換することにより周波数制御ワード C T M を生成する。そして、周波数シンセサイザ 1 は、この負帰還動作により、周波数  $f_o$  を目標周波数  $f_{target}$  に近付ける（動作 P 1）。

#### 【0059】

そして、その後に、周波数シンセサイザ 1 は、粗調整用の周波数制御ワード C B I N を固定し、微調整用の周波数ワード F B I N を変化させることにより負帰還動作を行う。その際、制御回路 40 は、周波数制御ワード F L M T 1 の値が範囲 R l i m の範囲内（この例では -32 ~ +31 の範囲内）に収まるように、補正ワード F C F を生成するとともに、その補正ワード F C F に対応する補正ワード C C F を生成する。そして、周波数シンセサイザ 1 は、この負帰還動作により、周波数  $f_o$  を目標周波数  $f_{target}$  により近付け、位相同期状態を実現する（動作 P 2）。

#### 【0060】

以下に、この動作 P 2 について、詳細に説明する。まず最初に、周波数制御ワード F L M T 1 が範囲 R l i m の上限値付近の値を示す場合における動作を説明し、次に、周波数制御ワード F L M T 1 が範囲 R l i m の下限値付近の値を示す場合における動作を説明する

#### 【0061】

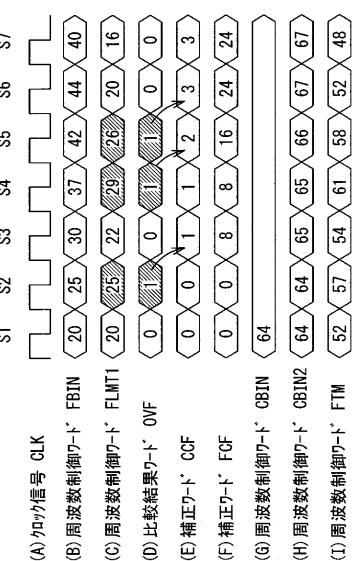

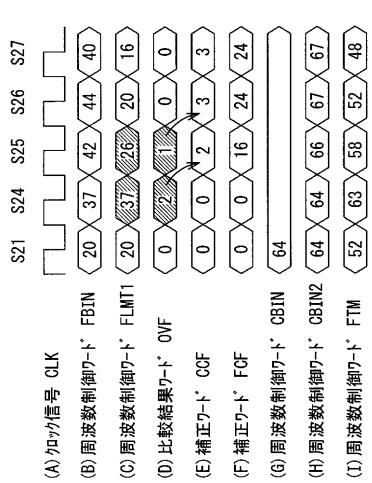

図 10 は、周波数制御ワード F L M T 1 が範囲 R l i m の上限値付近の値を示す場合における、発振回路 15 の動作のタイミング図を表すものであり、(A) はクロック信号 C L K の波形を示し、(B) は周波数制御ワード F B I N を示し、(C) は周波数制御ワード F L M T 1 を示し、(D) は比較結果ワード O V F を示し、(E) は補正ワード C C F を示し、(F) は補正ワード F C F を示し、(G) は周波数制御ワード C B I N を示し、(H) は周波数制御ワード C B I N 2 を示し、(I) は周波数制御ワード F T M を示す。この例では、粗調整用の周波数制御ワード C B I N は“64”に固定され、周波数制御ワード F B I N が過渡的に変化している。これにより、発振回路 15 の状態が、状態 S 1 ~ S 7 のように変化している。

#### 【0062】

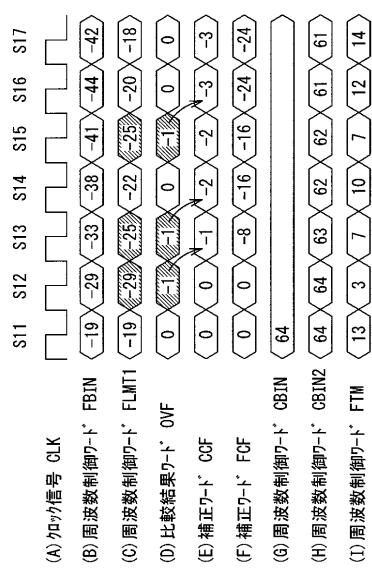

図 11 は、図 10 に示した状態 S 1 ~ S 7 を、発振部 30 の周波数制御特性を用いて表すものである。この図 11 では、横軸は周波数制御ワード F L M T 1 の値を示し、縦軸は周波数  $f_o$  を示している。

#### 【0063】

状態 S 1において、粗調整用の周波数制御ワード C B I N の値は“64”であり（図 10 (G)）、微調整用の周波数制御ワード F B I N の値は“20”である（図 10 (B)）。また、補正ワード C C F の値が“0”であるため（図 10 (E)）、加算回路 21 は、周波数制御ワード C B I N 2 の値を“64”（= 64 + 0）にし（図 10 (H)）、その結果、制御部 20 は、粗調整用の周波数制御ワード C T M の値を“64”にする。同様に、補正ワード F C F の値が“0”であるため（図 10 (F)）、減算回路 25 は、周波数制御ワード F L M T 1 の値を“20”（= 20 + 0）にし（図 10 (C)）、その結果、制御部 20 は、微調整用の周波数制御ワード F T M の値を“52”（= 20 + 32）にする（図 10 (I)）。この周波数制御ワード F L M T 1 の値“20”は、しきい値 T L 1 (-24) 以上でありかつしきい値 T H 1 (23) 以下であるため、比較回路 41 は、比較結果ワード O V F の値を“0”にする（図 10 (D)）。

#### 【0064】

このようにして、状態 S 1 では、図 11 に示したように、粗調整用の周波数制御ワード C T M の値“64”（C T M = 64）に対応した周波数制御特性が選択され、発振部 30 は、周波数制御ワード F L M T 1 の値“20”に応じた周波数  $f_o$  で発振する。

#### 【0065】

10

20

30

40

50

次に、状態 S 2において、微調整用の周波数制御ワード F B I N の値が“25”に変化する（図 10（B））。また、一つ前の状態 S 1において、比較結果ワード O V F の値が“0”であったため、累積加算回路 4 2 および乗算回路 4 3 は、補正ワード C C F , F C F の値をともに“0”にする（図 10（E），（F））。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“64”（= 64 + 0）にし（図 10（H））、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“64”にする。減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“25”（= 25 + 0）にし（図 10（C））、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“57”（= 25 + 32）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“25”は、しきい値 T H 1 (= 23) より大きくかつしきい値 T H 2 (31) 以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“1”にする（図 10（D））。

#### 【0066】

このようにして、状態 S 2 では、図 11 に示したように、粗調整用の周波数制御ワード C T M の値“64”（C T M = 64）に対応した周波数制御特性が引き続き選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“25”に応じた周波数 f o で発振する。

#### 【0067】

次に、状態 S 3 において、微調整用の周波数制御ワード F B I N の値が“30”に変化する（図 10（B））。また、一つ前の状態 S 2 において、比較結果ワード O V F の値が“1”であったため、累積加算回路 4 2 は、補正ワード C C F の値を“1”にするとともに（図 10（E））、乗算回路 4 3 は、補正ワード F C F の値を“8”にする（図 10（F））。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“65”（= 64 + 1）にし（図 10（H））、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“65”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“22”（= 30 - 8）にし（図 10（C））、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“54”（= 22 + 32）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“22”は、しきい値 T L 1 (-24) 以上でありかつしきい値 T H 1 (23) 以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“0”にする（図 10（D））。

#### 【0068】

このようにして、状態 S 3 では、図 11 に示したように、粗調整用の周波数制御ワード C T M の値“65”（C T M = 65）に対応した周波数制御特性が選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“22”に応じた周波数 f o で発振する。

#### 【0069】

次に、状態 S 4 において、微調整用の周波数制御ワード F B I N の値が“37”に変化する（図 10（B））。また、一つ前の状態 S 3 において、比較結果ワード O V F の値が“0”であったため、累積加算回路 4 2 は、補正ワード C C F の値“1”を維持するとともに（図 10（E））、乗算回路 4 3 は、補正ワード F C F の値“8”を維持する（図 10（F））。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“65”（= 64 + 1）にし（図 10（H））、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“65”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“29”（= 37 - 8）にし（図 10（C））、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“61”（= 29 + 32）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“29”は、しきい値 T H 1 (23) より大きくかつしきい値 T H 2 (31) 以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“1”にする（図 10（D））。

#### 【0070】

このようにして、状態 S 4 では、図 11 に示したように、粗調整用の周波数制御ワード C T M の値“65”（C T M = 65）に対応した周波数制御特性が引き続き選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“29”に応じた周波数 f o で発振する。

#### 【0071】

10

20

30

40

50

次に、状態 S 5において、微調整用の周波数制御ワード F B I N の値が“42”に変化する（図 10（B））。また、一つ前の状態 S 4において、比較結果ワード O V F の値が“1”であったため、累積加算回路 4 2は、補正ワード C C F の値を“2”にするとともに（図 10（E））、乗算回路 4 3は、補正ワード F C F の値を“16”にする（図 10（F））。これにより、加算回路 2 1は、周波数制御ワード C B I N 2 の値を“66”（ $= 64 + 2$ ）にし（図 10（H））、その結果、制御部 2 0は、粗調整用の周波数制御ワード C T M の値を“66”にする。また、減算回路 2 5は、周波数制御ワード F L M T 1 の値を“26”（ $= 42 - 16$ ）にし（図 10（C））、その結果、制御部 2 0は、微調整用の周波数制御ワード F T M の値を“58”（ $= 26 + 32$ ）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“26”は、しきい値 T H 1（23）より大きくなつしきい値 T H 2（31）以下であるため、比較回路 4 1は、比較結果ワード O V F の値を“1”にする（図 10（D））。

#### 【0072】

このようにして、状態 S 5では、図 11に示したように、粗調整用の周波数制御ワード C T M の値“66”（C T M = 66）に対応した周波数制御特性が選択され、発振部 3 0は、周波数制御ワード F L M T 1 の値“26”に応じた周波数 f oで発振する。

#### 【0073】

次に、状態 S 6において、微調整用の周波数制御ワード F B I N の値が“44”に変化する（図 10（B））。また、一つ前の状態 S 5において、比較結果ワード O V F の値が“1”であったため、累積加算回路 4 2は、補正ワード C C F の値を“3”にするとともに（図 10（E））、乗算回路 4 3は、補正ワード F C F の値を“24”にする（図 10（F））。これにより、加算回路 2 1は、周波数制御ワード C B I N 2 の値を“67”（ $= 64 + 3$ ）にし（図 10（H））、その結果、制御部 2 0は、粗調整用の周波数制御ワード C T M の値を“67”にする。また、減算回路 2 5は、周波数制御ワード F L M T 1 の値を“20”（ $= 44 - 24$ ）にし（図 10（C））、その結果、制御部 2 0は、微調整用の周波数制御ワード F T M の値を“52”（ $= 20 + 32$ ）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“20”は、しきい値 T L 1（-24）以上でありかつしきい値 T H 1（23）以下であるため、比較回路 4 1は、比較結果ワード O V F の値を“0”にする（図 10（D））。

#### 【0074】

このようにして、状態 S 6では、図 11に示したように、粗調整用の周波数制御ワード C T M の値“67”（C T M = 67）に対応した周波数制御特性が選択され、発振部 3 0は、周波数制御ワード F L M T 1 の値“20”に応じた周波数 f oで発振する。

#### 【0075】

次に、状態 S 7において、微調整用の周波数制御ワード F B I N の値が“40”に変化する（図 10（B））。また、一つ前の状態 S 6において、比較結果ワード O V F の値が“0”であったため、累積加算回路 4 2は、補正ワード C C F の値“3”を維持するとともに（図 10（E））、乗算回路 4 3は、補正ワード F C F の値“24”を維持する（図 10（F））。これにより、加算回路 2 1は、周波数制御ワード C B I N 2 の値を“67”（ $= 64 + 3$ ）にし（図 10（H））、その結果、制御部 2 0は、粗調整用の周波数制御ワード C T M の値を“67”にする。また、減算回路 2 5は、周波数制御ワード F L M T 1 の値を“16”（ $= 40 - 24$ ）にし（図 10（C））、その結果、制御部 2 0は、微調整用の周波数制御ワード F T M の値を“48”（ $= 16 + 32$ ）にする（図 10（I））。この周波数制御ワード F L M T 1 の値“16”は、しきい値 T L 1（-24）以上でありかつしきい値 T H 1（23）以下であるため、比較回路 4 1は、比較結果ワード O V F の値を“0”にする（図 10（D））。

#### 【0076】

このようにして、状態 S 7では、図 11に示したように、粗調整用の周波数制御ワード C T M の値“67”（C T M = 67）に対応した周波数制御特性が引き続き選択され、発振部 3 0は、周波数制御ワード F L M T 1 の値“16”に応じた周波数 f oで発振する。

10

20

30

40

50

## 【0077】

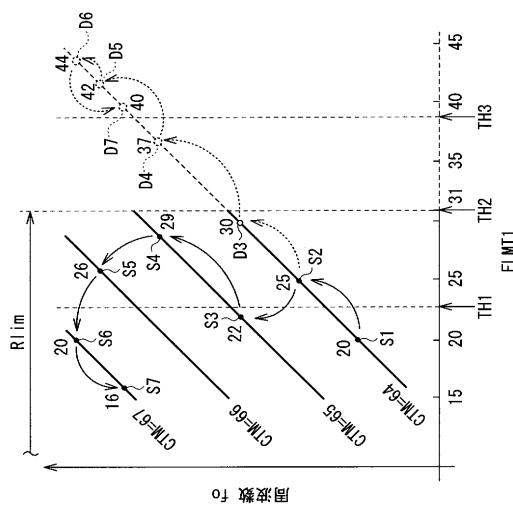

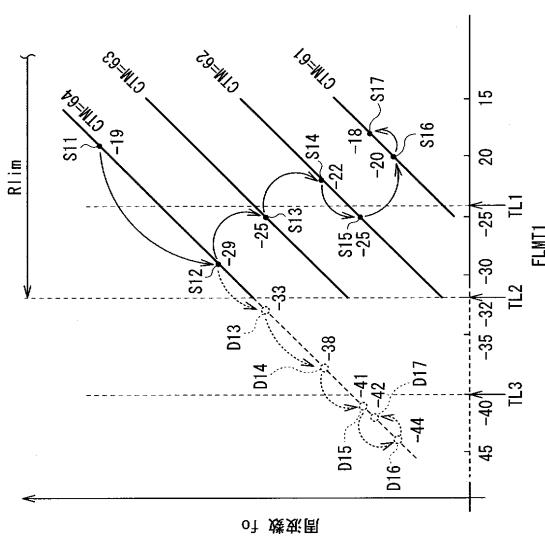

図12は、周波数制御ワードFLMT1が範囲Rlimの下限値付近の値を示す場合における、発振回路15の動作のタイミング図を表すものであり、(A)はクロック信号CLKの波形を示し、(B)は周波数制御ワードFBINを示し、(C)は周波数制御ワードFLMT1を示し、(D)は比較結果ワードOVFを示し、(E)は補正ワードCCFを示し、(F)は補正ワードFCFを示し、(G)は周波数制御ワードCBINを示し、(H)は周波数制御ワードCBIN2を示し、(I)は周波数制御ワードFTMを示す。この例では、粗調整用の周波数制御ワードCBINは“64”に固定され、周波数制御ワードFBINが過渡的に変化している。これにより、発振回路15の状態が、状態S11～S17のように変化している。

10

## 【0078】

図13は、図12に示した状態S11～S17を、発振部30の周波数制御特性を用いて表すものである。

## 【0079】

状態S11において、粗調整用の周波数制御ワードCBINの値は“64”であり(図12(G))、微調整用の周波数制御ワードFBINの値は“-19”である(図12(B))。また、補正ワードCCFの値が“0”であるため(図12(E))、加算回路21は、周波数制御ワードCBIN2の値を“64”( $= 64 + 0$ )にし(図12(H))、その結果、制御部20は、粗調整用の周波数制御ワードCTMの値を“64”にする。同様に、補正ワードFCFの値が“0”であるため(図12(F))、減算回路25は、周波数制御ワードFLMT1の値を“-19”( $= -19 + 0$ )にし(図12(C))、その結果、制御部20は、微調整用の周波数制御ワードFTMの値を“13”( $= -19 + 32$ )にする(図12(I))。この周波数制御ワードFLMT1の値“-19”は、しきい値TL1(-24)以上でありかつしきい値TH1(23)以下であるため、比較回路41は、比較結果ワードOVFの値を“0”にする(図12(D))。

20

## 【0080】

このようにして、状態S11では、図13に示したように、粗調整用の周波数制御ワードCTMの値“64”( $CTM = 64$ )に対応した周波数制御特性が選択され、発振部30は、周波数制御ワードFLMT1の値“-19”に応じた周波数 $f_0$ で発振する。

## 【0081】

30

次に、状態S12において、微調整用の周波数制御ワードFBINの値が“-29”に変化する(図12(B))。また、一つ前の状態S11において、比較結果ワードOVFの値が“0”であったため、累積加算回路42および乗算回路43は、補正ワードCCF, FCFの値をともに“0”にする(図12(E), (F))。これにより、加算回路21は、周波数制御ワードCBIN2の値を“64”( $= 64 + 0$ )にし(図12(H))、その結果、制御部20は、粗調整用の周波数制御ワードCTMの値を“64”にする。減算回路25は、周波数制御ワードFLMT1の値を“-29”( $= -29 + 0$ )にし(図12(C))、その結果、制御部20は、微調整用の周波数制御ワードFTMの値を“3”( $= -29 + 32$ )にする(図12(I))。この周波数制御ワードFLMT1の値“-29”は、しきい値TL2(-32)以上でありかつしきい値TL1(-24)より小さいため、比較回路41は、比較結果ワードOVFの値を“-1”にする(図12(D))。

40

## 【0082】

このようにして、状態S12では、図13に示したように、粗調整用の周波数制御ワードCTMの値“64”( $CTM = 64$ )に対応した周波数制御特性が引き続き選択され、発振部30は、周波数制御ワードFLMT1の値“-29”に応じた周波数 $f_0$ で発振する。

## 【0083】

次に、状態S13において、微調整用の周波数制御ワードFBINの値が“-33”に変化する(図12(B))。また、一つ前の状態S12において、比較結果ワードOVF

50

の値が“ - 1 ”であったため、累積加算回路 4 2 は、補正ワード C C F の値を“ - 1 ”にするとともに(図 12 (E))、乗算回路 4 3 は、補正ワード F C F の値を“ - 8 ”にする(図 12 (F))。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“ 6 3 ”( $= 64 - 1$ )にし(図 12 (H))、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“ 6 3 ”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“ - 2 5 ”( $= - 33 + 8$ )にし(図 12 (C))、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“ 7 ”( $= - 25 + 32$ )にする(図 12 (I))。この周波数制御ワード F L M T 1 の値“ - 2 5 ”は、しきい値 T L 2 (-32)以上でありかつしきい値 T L 1 (-24)より小さいため、比較回路 4 1 は、比較結果ワード O V F の値を“ - 1 ”にする(図 12 (D))。

10

#### 【0084】

このようにして、状態 S 1 3 では、図 13 に示したように、粗調整用の周波数制御ワード C T M の値“ 6 3 ”( $C T M = 63$ )に対応した周波数制御特性が選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“ - 2 5 ”に応じた周波数  $f_0$  で発振する。

#### 【0085】

次に、状態 S 1 4 において、微調整用の周波数制御ワード F B I N の値が“ - 3 8 ”に変化する(図 12 (B))。また、一つ前の状態 S 1 3 において、比較結果ワード O V F の値が“ - 1 ”であったため、累積加算回路 4 2 は、補正ワード C C F の値を“ - 2 ”にするとともに(図 12 (E))、乗算回路 4 3 は、補正ワード F C F の値を“ - 1 6 ”にする(図 12 (F))。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“ 6 2 ”( $= 64 - 2$ )にし(図 12 (H))、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“ 6 2 ”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“ - 2 2 ”( $= - 38 + 16$ )にし(図 12 (C))、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“ 1 0 ”( $= - 22 + 32$ )にする(図 12 (I))。この周波数制御ワード F L M T 1 の値“ - 2 2 ”は、しきい値 T L 1 (-24)以上でありかつしきい値 T H 1 (23)以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“ 0 ”にする(図 12 (D))。

20

#### 【0086】

このようにして、状態 S 1 4 では、図 13 に示したように、粗調整用の周波数制御ワード C T M の値“ 6 2 ”( $C T M = 62$ )に対応した周波数制御特性が選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“ - 3 8 ”に応じた周波数  $f_0$  で発振する。

30

#### 【0087】

次に、状態 S 1 5 において、微調整用の周波数制御ワード F B I N の値が“ - 4 1 ”に変化する(図 12 (B))。また、一つ前の状態 S 1 4 において、比較結果ワード O V F の値が“ 0 ”であったため、累積加算回路 4 2 は、補正ワード C C F の値“ - 2 ”を維持するとともに(図 12 (E))、乗算回路 4 3 は、補正ワード F C F の値“ - 1 6 ”を維持する(図 12 (F))。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“ 6 2 ”( $= 64 - 2$ )にし(図 12 (H))、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“ 6 2 ”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“ - 2 5 ”( $= - 41 + 16$ )にし(図 12 (C))、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“ 7 ”( $= - 25 + 32$ )にする(図 12 (I))。この周波数制御ワード F L M T 1 の値“ - 2 5 ”は、しきい値 T L 2 (-32)以上でありかつしきい値 T L 1 (-24)より小さいため、比較回路 4 1 は、比較結果ワード O V F の値を“ - 1 ”にする(図 12 (D))。

40

#### 【0088】

このようにして、状態 S 1 5 では、図 13 に示したように、粗調整用の周波数制御ワード C T M の値“ 6 2 ”( $C T M = 62$ )に対応した周波数制御特性が引き続き選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“ - 2 5 ”に応じた周波数  $f_0$  で発振する。

#### 【0089】

50

次に、状態 S 1 6において、微調整用の周波数制御ワード F B I N の値が“ - 4 4 ”に変化する(図 1 2 (B))。また、一つ前の状態 S 1 5において、比較結果ワード O V F の値が“ - 1 ”であったため、累積加算回路 4 2 は、補正ワード C C F の値を“ - 3 ”にするとともに(図 1 2 (E))、乗算回路 4 3 は、補正ワード F C F の値を“ - 2 4 ”にする(図 1 2 (F))。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“ 6 1 ”( $= 6 4 - 3$ )にし(図 1 2 (H))、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“ 6 1 ”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“ - 2 0 ”( $= - 4 4 + 2 4$ )にし(図 1 2 (C))、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“ 1 2 ”( $= - 2 0 + 3 2$ )にする(図 1 2 (I))。この周波数制御ワード F L M T 1 の値“ - 2 0 ”は、しきい値 T L 1 (- 2 4)以上でありかつしきい値 T H 1 (2 3)以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“ 0 ”にする(図 1 2 (D))。

#### 【0090】

このようにして、状態 S 1 6 では、図 1 3 に示したように、粗調整用の周波数制御ワード C T M の値“ 6 1 ”( $C T M = 6 1$ )に対応した周波数制御特性が選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“ - 2 0 ”に応じた周波数  $f_o$  で発振する。

#### 【0091】

次に、状態 S 1 7 において、微調整用の周波数制御ワード F B I N の値が“ - 4 2 ”に変化する(図 1 2 (B))。また、一つ前の状態 S 1 6 において、比較結果ワード O V F の値が“ 0 ”であったため、累積加算回路 4 2 は、補正ワード C C F の値“ - 3 ”を維持するとともに(図 1 2 (E))、乗算回路 4 3 は、補正ワード F C F の値“ - 2 4 ”を維持する(図 1 2 (F))。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を“ 6 1 ”( $= 6 4 - 3$ )にし(図 1 2 (H))、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を“ 6 1 ”にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を“ - 1 8 ”( $= - 4 2 + 2 4$ )にし(図 1 2 (C))、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を“ 1 4 ”( $= - 1 8 + 3 2$ )にする(図 1 2 (I))。この周波数制御ワード F L M T 1 の値“ - 1 8 ”は、しきい値 T L 1 (- 2 4)以上でありかつしきい値 T H 1 (2 3)以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を“ 0 ”にする(図 1 2 (D))。

#### 【0092】

このようにして、状態 S 1 7 では、図 1 3 に示したように、粗調整用の周波数制御ワード C T M の値“ 6 1 ”( $C T M = 6 1$ )に対応した周波数制御特性が引き続き選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値“ - 1 8 ”に応じた周波数  $f_o$  で発振する。

#### 【0093】

発振回路 1 5 では、図 1 1 に示したように、ある状態において、周波数制御ワード F L M T 1 の値がしきい値 T H 1 よりも大きくなった場合(例えば状態 S 2 , S 4 , S 5)には、その次の状態において、粗調整用の周波数制御ワード C T M の値を高くし、粗調整用の可変容量バンク 3 3 の設定を切り替える。また、同様に、発振回路 1 5 では、図 1 3 に示したように、ある状態において、周波数制御ワード F L M T 1 の値がしきい値 T L 1 よりも小さくなった場合(例えば状態 S 1 2 , S 1 3 , S 1 5)には、その次の状態において、粗調整用の周波数制御ワード C T M の値を低くし、粗調整用の可変容量バンク 3 3 の設定を切り替える。これにより、周波数制御ワード F L M T 1 の値を範囲 R l i m の範囲内(この例では - 3 2 ~ + 3 1 の範囲内)に収めつつ、周波数制御範囲を広くすることができる。

#### 【0094】

すなわち、例えば、粗調整用の可変容量バンク 3 3 の設定を切り替えない場合には、図 1 1 において、状態 S 3 ~ S 7 は状態 D 3 ~ D 7 に示したようになり、図 1 3 において、状態 S 1 3 ~ S 1 7 は状態 D 1 3 ~ D 1 7 に示したようになる。すなわち、この場合、微調整用の周波数制御ワード F L M T 1 の値をより広い範囲で変化させる必要がある。また

10

20

30

40

50

、周波数制御範囲の上限近くまたは下限近くで動作させる場合には、周波数制御ワードの値が上限値または下限値を超えてしまい、周波数  $f_o$  が飽和してしまうおそれがある。

#### 【0095】

一方、発振回路 15 では、粗調整用の可変容量バンク 33 の設定を切り替えるようにしている。これにより、微調整用の周波数制御ワード F L M T 1 の値を狭い範囲内で変化させつつ、周波数制御範囲を広くすることができ、周波数  $f_o$  が飽和するおそれを低減することができる。

#### 【0096】

また、発振回路 15 では、周波数制御ワード F L M T 1 の値がしきい値 T H 1 よりも大きくなった場合やしきい値 T L 1 よりも小さくなった場合に、粗調整用の可変容量バンク 33 の設定を切り替えるようにしたので、可変容量バンク 33 の設定を切り替える頻度を少なくすることができる。

10

#### 【0097】

すなわち、例えば、図 11 に示したように、状態 S5 から状態 S6 に遷移する場合には、発振回路 15 では、周波数  $f_o$  を上げる制御が行われ、粗調整用の可変容量バンク 33 の設定が切り替わる。一方、状態 S6 から状態 S7 に遷移する場合には、発振回路 15 では、周波数  $f_o$  を下げる制御が行われるが、粗調整用の可変容量バンク 33 の設定は維持されている。すなわち、状態 S6 では、周波数制御ワード F L M T 1 の値をしきい値 T H 1 以下に維持したまま、周波数制御ワード C T M の値を大きくすることにより高い周波数  $f_o$  を実現している。よって、状態 S6 から状態 S7 に遷移する場合において、粗調整用の周波数制御ワード C T M の値を維持したまま、微調整用の周波数制御ワード F L M T 1 の値を小さくすることにより、周波数  $f_o$  を下げることができる。

20

#### 【0098】

同様に、例えば図 13 に示したように、状態 S15 から状態 S16 に遷移する場合には、発振回路 15 では、周波数  $f_o$  を下げる制御が行われ、粗調整用の可変容量バンク 33 の設定が切り替わる。一方、状態 S16 から状態 S17 に遷移する場合には、発振回路 15 では、周波数  $f_o$  を上げる制御が行われるが、粗調整用の可変容量バンク 33 の設定は維持されている。すなわち、状態 S16 では、周波数制御ワード F L M T 1 の値をしきい値 T L 1 以上に維持したまま、周波数制御ワード C T M の値を小さくすることにより低い周波数  $f_o$  を実現している。よって、状態 S16 から状態 S17 に遷移する場合において、粗調整用の周波数制御ワード C T M の値を維持したまま、微調整用の周波数制御ワード F L M T 1 の値を大きくすることにより、周波数  $f_o$  を上げることができる。

30

#### 【0099】

このように、粗調整用の可変容量バンク 33 の設定を変化させることにより周波数  $f_o$  を一旦変化させたのちに、元の周波数  $f_o$  に戻す場合には、粗調整用の可変容量バンク 33 の設定を維持し、微調整用の可変容量バンク 34 の設定を変化させる。これにより、粗調整用の可変容量バンク 33 の設定を切り替える頻度を少なくすることができ、以下に説明するように、可変容量バンク 33 の設定を切り替えに起因する位相雑音を低減することができる。

#### 【0100】

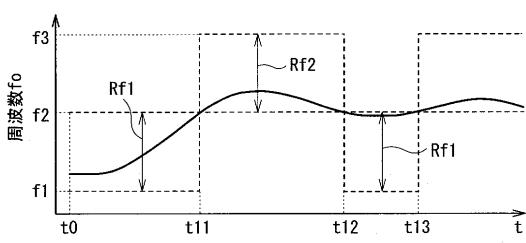

40

図 14 は、発振回路 15 の動作のタイミング図を表すものである。図 14 において、周波数範囲 R f は、微調整用の周波数制御ワード F T M により制御可能な周波数範囲である。

#### 【0101】

タイミング  $t_0 \sim t_2$  の期間において、前段の利得調整回路 14 は、周波数制御ワード C B I N, F B I N を介して、発振回路 15 に対して周波数  $f_o$  を徐々に高くするように指示する。

#### 【0102】

タイミング  $t_0 \sim t_1$  の期間において、発振回路 15 では、微調整用の周波数制御ワード F T M が変化し、周波数  $f_o$  が徐々に高くなる。この期間では、周波数制御ワード F L

50

M T 1 の値はしきい値 T L 1 以上でありかつしきい値 T H 1 以下であるため、制御部 2 0 は、粗調整用の周波数制御ワード C T M を変化させない。これにより、粗調整用の可変容量バンク 3 3 の設定の切り替えは生じず、周波数範囲 R f は固定される。

#### 【 0 1 0 3 】

そして、タイミング t 1 ~ t 2 の期間において、発振回路 1 5 では、粗調整用の周波数制御ワード C T M が徐々に変化し、周波数 f o が引き続き高くなる。この期間では、周波数制御ワード F L M T 1 の値がしきい値 T H 1 より大きくなるため、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を徐々に高くする。これにより、粗調整用の可変容量バンク 3 3 の設定が切り替わり、周波数範囲 R f が徐々に移動する。

#### 【 0 1 0 4 】

そして、タイミング t 2 以降において、前段の利得調整回路 1 4 は、周波数制御ワード C B I N , F B I N を介して、発振回路 1 5 に対して周波数 f o をやや下げるよう指示する。発振回路 1 5 では、微調整用の周波数制御ワード F T M が変化し、周波数 f o がやや下がる。このタイミング t 2 以降では、周波数制御ワード F L M T 1 の値はしきい値 T H 1 以下になるため、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を維持する。これにより、粗調整用の可変容量バンク 3 3 の設定の切り替えは生じず、周波数範囲 R f は固定される。

#### 【 0 1 0 5 】

以上のように、発振回路 1 5 では、周波数制御ワード F L M T 1 の値がしきい値 T H 1 よりも大きくなった場合やしきい値 T L 1 よりも小さくなった場合に、粗調整用の可変容量バンク 3 3 の設定を切り替えるようにしたので、可変容量バンク 3 3 の設定を切り替える頻度を少なくすることができる。すなわち、例えば、前段の利得調整回路から供給される周波数制御ワードの値と所定のしきい値とを比較し、その大小関係により粗調整用の可変容量バンク 3 3 の設定を切り替えるように構成した場合には、図 1 5 に示したように、粗調整用の可変容量バンク 3 3 の設定が頻繁に切り替わるおそれがある。この例では、タイミング t 1 0 ~ t 1 1 の期間、およびタイミング t 1 2 ~ t 1 3 の期間では、周波数 f 1 ~ f 2 の周波数範囲 R f 1 が設定され、タイミング t 1 1 ~ t 1 2 の期間、およびタイミング t 1 3 以降では、周波数 f 2 ~ f 3 の周波数範囲 R f 2 が設定されている。これにより、タイミング t 1 1 , t 1 2 , t 1 3 において、粗調整用の可変容量バンク 3 3 の設定が切り替わる。特に、目標周波数 f target が、周波数範囲 R f 1 , R f 2 の境界の周波数 f 2 付近である場合には、さらに可変容量バンク 3 3 の設定が頻繁に切り替わるおそれがある。このように、粗調整用の可変容量バンク 3 3 の設定が切り替わると、位相雑音が生じてしまうおそれがある。

#### 【 0 1 0 6 】

一方、発振回路 1 5 では、周波数制御ワード F L M T 1 の値がしきい値 T H 1 よりも大きくなった場合やしきい値 T L 1 よりも小さくなった場合に、粗調整用の可変容量バンク 3 3 の設定を切り替えるようにした。これにより、図 1 4 に示したように、粗調整用の可変容量バンク 3 3 の設定の切り替えが生じる頻度を下げることができ、可変容量バンク 3 3 の設定の切り替えに起因する位相雑音を低減することができる。

#### 【 0 1 0 7 】

次に、前段の利得調整回路 1 4 が、周波数制御ワード F B I N をより大きなステップで変化させた場合の発振回路 1 5 の動作について説明する。

#### 【 0 1 0 8 】

図 1 6 は、周波数制御ワード F L M T 1 が範囲 R l i m の上限値付近の値を示す場合における、発振回路 1 5 の動作のタイミング図を表すものであり、( A ) はクロック信号 C L K の波形を示し、( B ) は周波数制御ワード F B I N を示し、( C ) は周波数制御ワード F L M T 1 を示し、( D ) は比較結果ワード O V F を示し、( E ) は補正ワード C C F を示し、( F ) は補正ワード F C F を示し、( G ) は周波数制御ワード C B I N を示し、( H ) は周波数制御ワード C B I N 2 を示し、( I ) は周波数制御ワード F T M を示す。この例では、粗調整用の周波数制御ワード C B I N は “ 6 4 ” に固定され、周波数制御ワード C B I N 2 は “ 6 5 ” に固定される。

10

20

30

40

50

D F B I N が過渡的に変化している。これにより、発振回路 1 5 の状態が、状態 S 2 1 , S 2 4 ~ S 2 7 のように変化している。

#### 【 0 1 0 9 】

図 1 7 は、図 1 6 に示した状態 S 2 1 , S 2 4 ~ S 2 7 を、発振部 3 0 の周波数制御特性を用いて表すものである。

#### 【 0 1 1 0 】

状態 S 2 1 では、図 1 0 , 1 1 の状態 S 1 と同様に、粗調整用の周波数制御ワード C B I N の値は “ 6 4 ” であり ( 図 1 6 ( G ) ) 、微調整用の周波数制御ワード F B I N の値は “ 2 0 ” である ( 図 1 6 ( B ) ) 。補正ワード C C F の値が “ 0 ” であるため ( 図 1 6 ( E ) ) 、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を “ 6 4 ” にし ( 図 1 6 ( H ) ) 、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を “ 6 4 ” にする。補正ワード F C F の値が “ 0 ” であるため ( 国 1 6 ( F ) ) 、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を “ 2 0 ” にし ( 国 1 6 ( C ) ) 、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を “ 5 2 ” にする ( 国 1 6 ( I ) ) 。そして、比較回路 4 1 は、この周波数制御ワード F L M T 1 の値 “ 2 0 ” に基づいて、比較結果ワード O V F の値を “ 0 ” にする ( 国 1 6 ( D ) ) 。これにより、状態 S 2 1 では、国 1 7 に示したように、粗調整用の周波数制御ワード C T M の値 “ 6 4 ” ( C T M = 6 4 ) に対応した周波数制御特性が選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値 “ 2 0 ” に応じた周波数 f o で発振する。

10

#### 【 0 1 1 1 】

次に、状態 S 2 4 において、微調整用の周波数制御ワード F B I N の値が “ 3 7 ” に変化する ( 国 1 6 ( B ) ) 。また、一つ前の状態 S 2 1 において、比較結果ワード O V F の値が “ 0 ” であったため、累積加算回路 4 2 は、補正ワード C C F , F C F の値をともに “ 0 ” にする ( 国 1 6 ( E ) , ( F ) ) 。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を “ 6 4 ” ( = 6 4 + 0 ) にし ( 国 1 6 ( H ) ) 、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を “ 6 4 ” にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を “ 3 7 ” ( = 3 7 - 0 ) にし ( 国 1 6 ( C ) ) 、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を “ 6 3 ” にする ( 国 1 6 ( I ) ) 。すなわち、周波数制御ワード F L M T 1 の値 “ 3 7 ” がリミッタ 2 6 により上限値 ( 3 1 ) に制限されるため、微調整用の周波数制御ワード F T M の値が “ 6 3 ” ( = 3 1 + 3 2 ) になる。この周波数制御ワード F L M T 1 の値 “ 3 7 ” は、しきい値 T H 2 ( 3 1 ) より大きくかつしきい値 T H 2 ( 3 9 ) 以下であるため、比較回路 4 1 は、比較結果ワード O V F の値を “ 2 ” にする ( 国 1 6 ( D ) ) 。

20

30

#### 【 0 1 1 2 】

このようにして、状態 S 2 4 では、国 1 7 に示したように、粗調整用の周波数制御ワード C T M の値 “ 6 4 ” ( C T M = 6 4 ) に対応した周波数制御特性が引き続き選択され、発振部 3 0 は、周波数制御ワード F L M T 1 の値 “ 3 1 ” に応じた周波数 f o で発振する。

。

#### 【 0 1 1 3 】

次に、状態 S 2 5 において、微調整用の周波数制御ワード F B I N の値が “ 4 2 ” に変化する ( 国 1 6 ( B ) ) 。また、一つ前の状態 S 2 4 において、比較結果ワード O V F の値が “ 2 ” であったため、累積加算回路 4 2 は、補正ワード C C F の値を “ 2 ” にするとともに ( 国 1 6 ( E ) ) 、乗算回路 4 3 は、補正ワード F C F の値を “ 1 6 ” にする ( 国 1 6 ( F ) ) 。これにより、加算回路 2 1 は、周波数制御ワード C B I N 2 の値を “ 6 6 ” ( = 6 4 + 2 ) にし ( 国 1 6 ( H ) ) 、その結果、制御部 2 0 は、粗調整用の周波数制御ワード C T M の値を “ 6 6 ” にする。また、減算回路 2 5 は、周波数制御ワード F L M T 1 の値を “ 2 6 ” ( = 4 2 - 1 6 ) にし ( 国 1 6 ( C ) ) 、その結果、制御部 2 0 は、微調整用の周波数制御ワード F T M の値を “ 5 8 ” ( = 2 6 + 3 2 ) にする ( 国 1 6 ( I ) ) 。この周波数制御ワード F L M T 1 の値 “ 2 6 ” は、しきい値 T H 1 ( 2 3 ) より大きくかつしきい値 T H 2 ( 3 1 ) 以下であるため、比較回路 4 1 は、比較結果ワード O V 40

50

Fの値を“1”にする(図16(D))。

**【0114】**

このようにして、状態S25では、図17に示したように、粗調整用の周波数制御ワードCTMの値“66”(CTM=66)に対応した周波数制御特性が選択され、発振部30は、周波数制御ワードFLMT1の値“26”に応じた周波数 $f_0$ で発振する。

**【0115】**

すなわち、この例では、図10, 11の場合と異なり、状態S24から状態S25に変化する際、粗調整用の周波数制御ワードCTMの値を、2つ変化させている。これにより、粗調整用の可変容量バンク33の設定をより早く変えることができる。

**【0116】**

その後の状態S26, S27の動作は、図10, 11に示した状態S6, S7と同様である。

**【0117】**

このように、発振回路15では、図6に示したように、比較回路41が、周波数制御ワードFLMT1の値と複数のしきい値とを比較するようにした。これにより、周波数制御ワードFBINが大きなステップで変化した場合には、補正ワードCCFを大きく変化させることができるために、粗調整用の可変容量バンク33の設定をより早く変えることができる。

**【0118】**

**[効果]**

10

以上のように本実施の形態では、周波数制御ワードFLMT1の値がしきい値TH1よりも大きくなった場合やしきい値TL1よりも小さくなった場合に、粗調整用の可変容量バンクの設定を切り替えるようにしたので、粗調整用の可変容量バンクの設定を切り替える頻度を少なくすることができ、位相雑音を低減することができる。

**【0119】**

**[変形例1]**

周波数シンセサイザの構成は、図1の構成に限定されるものではない。以下に、他の構成について詳細に説明する。

**【0120】**

図18は、本変形例に係る周波数シンセサイザ2の一構成例を表すものである。この周波数シンセサイザ2は、アナログPLLと類似の構成を有するものである。周波数シンセサイザ2は、位相検出回路51と、分周回路56とを有している。

20

**【0121】**

位相検出回路51は、基準クロック信号REFCLKおよびクロック信号DIVCLKに基づいて、これらの信号の位相誤差値を求め、位相誤差値を位相誤差ワードPEWとして出力するものである。位相検出回路51は、例えば、TDC(Time To Digital Converter)を用いて構成されるものである。

**【0122】**

分周回路56は、クロック信号DCOCLK, DCOKLKBにより構成される差動信号を、分周比ワードFCWが示す分周比で分周し、クロック信号DIVCLKとして出力するものである。そして、分周回路56は、このクロック信号DIVCLKを、位相検出回路51に加え、ループフィルタ13および発振回路15にも供給する。

30

**【0123】**

この構成でも、上記実施の形態に係る周波数シンセサイザ1と同様の効果を得ることができる。

40

**【0124】**

以上、実施の形態および変形例を挙げて本技術を説明したが、本技術はこれらの実施の形態等には限定されず、種々の変形が可能である。

**【0125】**

例えば、上記の実施の形態等では、例えば、可変容量素子グループ36における可変容

50

量素子 35 の素子数を“8”にするとともに、乗算回路 43 における乗算値を“8”にしたが、これに限定されるものではなく、この素子数と乗算値とが互いに等しければ、どのような数であってもよい。乗算回路 43 における演算をビットのシフトにより実現する場合には、この素子数および乗算値を2のべき乗（例えば4や16など）にすることが望ましい。

**【0126】**

また、上記の実施の形態では、周波数制御ワード C B I N , F B I N , C T M , F T M などのビット数をそれぞれ例示したが、これに限定されるものではなく、所望の性能を発揮できる範囲で変更してもよい。

**【0127】**

なお、本明細書に記載された効果はあくまで例示であって限定されるものでは無く、また他の効果があってもよい。

**【0128】**

なお、本技術は以下のような構成とすることができます。

**【0129】**

(1) 第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に基づいて第1の感度で発振信号の周波数が変化し、前記第2のコード値に基づいて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を備えた発振回路。

**【0130】**

(2) 前記第1の入力コード値の補正による前記発振信号の周波数の変化方向と、前記第2の入力コード値の補正による前記発振信号の周波数の変化方向とは、互いに反対方向である

前記(1)に記載の発振回路。

**【0131】**

(3) 前記第2の入力コード値の補正量は、前記第1の感度と前記第2の感度との感度比、および前記第1の入力コード値の補正量に応じた量である

前記(1)または(2)に記載の発振回路。

**【0132】**

(4) 前記演算部は、

前記第1のコード値と、前記第1の所定の範囲よりも狭い第2の所定の範囲の上限値および下限値とを比較して比較結果値を生成する比較部と、

前記比較結果値を累積加算して累積値を求める累積加算部と、

前記累積値に基づいて前記第1の入力コード値を補正するとともに前記第2の入力コード値を補正する補正部と

を有する

前記(1)から(3)のいずれかに記載の発振回路。

**【0133】**

(5) 前記比較部は、さらに、前記第1のコード値と、前記第1の所定範囲の上限値および下限値とを比較して、前記比較結果値を生成する

前記(4)に記載の発振回路。

**【0134】**

(6) 前記比較結果値は、前記第1のコード値が前記第2の所定の範囲の上限値よりも大きい場合には正の値であり、前記第1のコード値が前記第2の所定の範囲の下限値よりも小さい場合には負の値であり、

前記補正部は、前記第2の入力コード値を前記累積値の分だけ増やすことにより前記第2の入力コードを補正し、前記第1の入力コード値を、前記第1の感度を前記第2の感度

10

20

30

40

50

で除算した値と前記累積値との積の分だけ減らすことにより前記第1の入力コード値を補正する

前記(4)または(5)に記載の発振回路。

**【0135】**

(7) 前記発振部は、

インダクタと

前記インダクタと並列接続され、前記第1のコード値に基づいて容量値が変化する第1の可変容量バンクと、

前記インダクタと並列接続され、前記第2のコード値に基づいて容量値が変化する第2の可変容量バンクと

10

を有する

前記(1)から(6)のいずれかに記載の発振回路。

**【0136】**

(8) 前記第1の可変容量バンクは、前記第1の感度に対応する変化率で容量値が変化する第1の可変容量素子を複数有し、

前記第2の可変容量バンクは、前記第2の感度に対応する変化率で容量値が変化する第2の可変容量素子を複数有する

前記(7)に記載の発振回路。

**【0137】**

(9) 基準位相信号を生成する基準位相生成回路と、

20

前記基準位相信号と帰還位相信号との位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号の位相を求めて前記帰還位相信号として出力する位相検出回路とを備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

30

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有する

周波数シンセサイザ。

**【0138】**

(10) 入力クロック信号と帰還クロック信号との間の位相差を検出する位相比較回路と、

前記位相比較回路における検出結果に基づいて第1の入力コード値および第2の入力コード値を生成する周波数制御回路と、

40

前記第1の入力コード値および前記第2の入力コード値に基づいて発振信号を生成する発振回路と、

前記発振信号を分周して前記帰還クロック信号を生成する分周回路とを備え、

前記発振回路は、

前記第1の入力コード値を補正することにより、前記第1の入力コード値のとりうる範囲より狭い第1の所定の範囲内の第1のコード値を生成し、前記第1の入力コード値の補正量に応じて前記第2の入力コード値を補正して第2のコード値を生成する演算部と、

前記第1のコード値に応じて第1の感度で発振信号の周波数が変化し、前記第2のコード

50

ド値に応じて前記第1の感度よりも高い第2の感度で前記発振信号の周波数が変化する発振部と

を有する

周波数シンセサイザ。

【符号の説明】

【0139】

1, 2 ... 周波数シンセサイザ、11...基準位相生成回路、12...位相比較回路、13...ループフィルタ、14...利得調整回路、15...発振回路、16...位相検出回路、17...リタイミング回路、20...制御部、21...加算回路、22...リミッタ、23...エンコーダ、24...フリップフロップ、25...減算回路、26...リミッタ、27...符号変換回路、28...エンコーダ、29...フリップフロップ、30...発振部、31...負性抵抗、32...インダクタ、33, 34...可変容量バンク、35...可変容量素子、36...可変容量素子グループ、40...制御回路、41...比較回路、42...累積加算回路、43...乗算回路、51...位相検出回路、57...分周回路、CBIN, CBIN2, CLMT, CTM, FBIN, FLM

T1, FLM2, FTM, FU...周波数制御ワード、CCF...FCF...補正ワード、CLK...クロック信号、DCOCLK, DCOLKB...クロック信号、FCW...分周比ワード、 $f_o$ ...周波数、OVF...比較結果ワード、PEW, PEW2...位相誤差ワード、PW1...基準位相ワード、PW2...位相ワード、REFCLK...基準クロック信号、Rlim...範囲、TH1, TH2, TH3, TL1, TL2, TL3...しきい値。

10

【図1】

【図2】

【 义 3 】

【 図 4 】

【図5】

【 図 6 】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 5】

【図 1 4】

【図 1 6】

【図 17】

【図 18】

---

フロントページの続き

(56)参考文献 国際公開第2011/161860(WO,A1)

特開2009-010599(JP,A)

特開2011-130047(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03L1/00 - 9/00