(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-80553

(P2013-80553A)

(43) 公開日 平成25年5月2日(2013.5.2)

(51) Int.Cl.

G 11 B 5/09 (2006.01)

G 11 B 20/10 (2006.01)

F 1

G 11 B 5/09 321 A

G 11 B 20/10 321 A

テーマコード(参考)

5 D 031

5 D 044

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 57 頁)

(21) 出願番号 特願2012-215775 (P2012-215775)

(22) 出願日 平成24年9月28日 (2012.9.28)

(31) 優先権主張番号 13/250,246

(32) 優先日 平成23年9月30日 (2011.9.30)

(33) 優先権主張国 米国(US)

(71) 出願人 508243639

エルエスアイ コーポレーション

アメリカ合衆国 95131 カリフォルニア, サンホセ, リッダー パーク ドライヴ 1320

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128657

弁理士 三山 勝巳

(74) 代理人 100160967

弁理士 ▲濱▼口 岳久

(74) 代理人 100170601

弁理士 川崎 孝

最終頁に続く

(54) 【発明の名称】磁気記録システムにおけるトラック間干渉の軽減のためのハードウェアに基づく方法および装置

## (57) 【要約】

【課題】磁気記録システムにおけるトラック間干渉の軽減のためのハードウェアに基づく方法および装置を提供すること。

【解決手段】トラック間干渉(ITT)は、ITTキャンセル・データを取得することと、ITTキャンセル・データを、磁気記録システムの書き込みデータ経路を用いてITT軽減回路に提供することによって磁気記録システムにおいて軽減される。任意的に、書き込みデータ経路は、読み取りデータ経路が読み取り動作を実行するとの実質的に同時に動作することができる。ITTキャンセル・データは、例えば、ユーザ・データおよび/または媒体データを含む。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

磁気記録システムにおけるトラック間干渉(ITT)の軽減のための方法であって、

トラック間干渉キャンセル・データを取得することと、

前記トラック間干渉キャンセル・データを、前記磁気記録システムの書き込みデータ経路の少なくとも一部を用いてトラック間干渉軽減回路に提供することとを含む、方法。

## 【請求項 2】

前記トラック間干渉キャンセル・データは、ユーザ・データ、媒体データ、ADCデータ、およびY-データのうちの1つまたは複数を含む請求項1に記載の方法。

## 【請求項 3】

前記書き込みデータ経路は、読み取りデータ経路が読み取り動作を実行するのと実質的に同時に動作する請求項1に記載の方法。

## 【請求項 4】

前記トラック間干渉の軽減は、所与の読み取り動作に対して、1つまたは複数の隣接するセクタに関して選択的に実行される請求項1に記載の方法。

## 【請求項 5】

前記提供するステップは、読み取り動作中に実行される請求項1に記載の方法。

## 【請求項 6】

磁気記録システムにおけるトラック間干渉(ITT)の軽減のための装置であって、

読み取りデータ経路と、

トラック間干渉キャンセル・データを、前記磁気記録システムのトラック間干渉軽減回路に提供するための書き込みデータ経路とを含む、装置。

## 【請求項 7】

前記書き込みデータ経路は、前記読み取りデータ経路が読み取り動作を実行するのと実質的に同時に動作する請求項6に記載の装置。

## 【請求項 8】

前記トラック間干渉の軽減を開始するための、リード・ゲート信号と実質的に同時にアサートされる第1の制御信号を生成するための手段をさらに含む請求項6に記載の装置。

## 【請求項 9】

前記トラック間干渉の軽減のための、前の読み取り動作からのデータおよび後処理されたデータのうちの1つまたは複数の使用を示す第2の制御信号を生成するための手段をさらに含む請求項6に記載の装置。

## 【請求項 10】

読み取りデータ経路と、

前記読み取りデータ経路による前の読み取り動作からの記憶されたデータおよび記憶された後処理されたデータのうちの1つまたは複数の使用を示す再試行制御信号を生成するための手段とを含む、磁気記録システム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、概して、磁気記録システムに関し、より具体的には、そのような磁気記録システムにおけるトラック間干渉の影響を軽減するための改善された技術に関する。

## 【背景技術】

## 【0002】

磁気記録(MR)システムにおいて、データは、通常、一連の小さな磁気領域として、磁気媒体上の同心円状のトラックに記録される。所与のトラックに隣接するトラックに書き込まれたデータは、所与のトラックの媒体から読み出される信号に影響を与える。1つまたは複数の隣接するトラックの結果として所与のトラックの読み取り中に引き起こされる信号は、クロストークまたはトラック間干渉(ITT)と呼ばれる。所与のトラックの読み出される信号内の、隣接するトラックによって引き起こされたITT雑音の軽減は、

10

20

30

40

50

概して、ITI軽減回路またはプロセスに与えられる隣接するトラックからのデータパターンについての情報に頼る。

#### 【0003】

ITIは、データの同心円状のまたはらせん状のトラックが、媒体に、ヘッドのサイズに比して互いにごく近くに記録されるハードディスクドライブ(HDD)において特に問題である。ディスクドライブの容量は、トラックをより近くにまとめて配置することによって増やされる。しかし、ITIは、テクノロジーの微細化とともに増大することが知られており、トラックの分離距離が短くなるにつれて重大な雑音源になる。トラックがより近くにまとめて配置されるにつれて、隣接するトラックは、所与のトラックが媒体から読み出されるときにその所与のトラックの信号により影響を与えやすくなり、全体的な信号対雑音比を低下させる。したがって、ITIは、磁気媒体の所与の領域に信頼性高く記憶され得るトラックの数を制限する。ITIは、トラックが一部のケースでは互いに接触するほど近くに配置され、その他のケースではデータを書き込まれたときに互いに重なる可能性さえあるシングルド磁気記録(Single Magnetic Record ining)(SMR)システムにおいては一層大きな問題である。

#### 【0004】

磁気記録システムにおけるITIの影響を軽減するためのいくつかの技術が、提案されている。例えば、既存のSMRの実装においては、軽減プロセスが、通常、ハードディスクコントローラ(HDC)のソフトウェアによって実行される。しかし、ITIの軽減が有効化されるとき、HDCは、ディスクの3~6回転ごとに数セクタ(および典型的には1セクタのみ)よりも多いセクタを再生するのに十分なほど速くデータを処理することができないことが分かっている。しかし、ディスクの各回転は、(例えば、使用される特定のディスクドライブ、プラッタのサイズ、およびディスク上の各トラックの半径方向の位置に応じて)例えば、500以上のセクタを含む可能性がある。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

#### 【特許文献1】米国特許出願第13/186,174号

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

したがって、ITIの影響を軽減するための改善された技術に対するニーズが、存在する。ITIの影響を軽減するためのハードウェアに基づく技術に対するさらなるニーズが、存在する。ハードディスクコントローラがITIの計算を実行することを要求しない、ITIの影響を軽減するためのハードウェアに基づく技術に対するさらに別のニーズが、存在する。

#### 【課題を解決するための手段】

#### 【0007】

概して、磁気記録システムにおけるトラック間干渉の軽減のためのハードウェアに基づく方法および装置が、提供される。本発明の一態様によれば、トラック間干渉(ITI)が、ITIキャンセル・データを取得することと、ITIキャンセル・データを、読み取り動作中に、磁気記録システムの書き込みデータ経路を用いてITI軽減回路に提供することによって磁気記録システムにおいて軽減される。任意的に、書き込みデータ経路は、読み取りデータ経路が読み取り動作を実行するのと実質的に同時に動作することができる。

#### 【0008】

ITIキャンセル・データは、例えば、書き込みデータ経路の外部にあるメモリから得られる可能性がある。ITIキャンセル・データは、例えば、ユーザ・データおよび/または媒体データを含む。一実施形態において、書き込みデータ経路は、ユーザ・データをITIの軽減のための媒体データに変換する。

10

20

30

40

50

## 【0009】

ITIの軽減は、データの所与のセクタに対して選択的に有効化されることができる。加えて、ITIの軽減は、1つまたは複数の隣接するトラックに関する所与の読み取り動作に対して選択的に実行され得る。任意的に、ITIの軽減は、ITIを補正されたデータを後処理するための後処理手順と組み合わせて実行される可能性があり、および/または後処理されたデータに対してITIの軽減を実行する可能性がある。

## 【0010】

本発明、ならびに本発明のさらなる特徴および利点のより完全な理解が、以下の詳細な説明および図面を参照することによって得られる。

## 【図面の簡単な説明】

10

## 【0011】

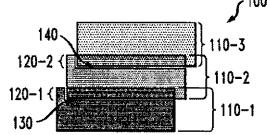

【図1】シングルド磁気記録(SMR)システムの磁気媒体上のいくつかの例示的なトラックの一部を示す図である。

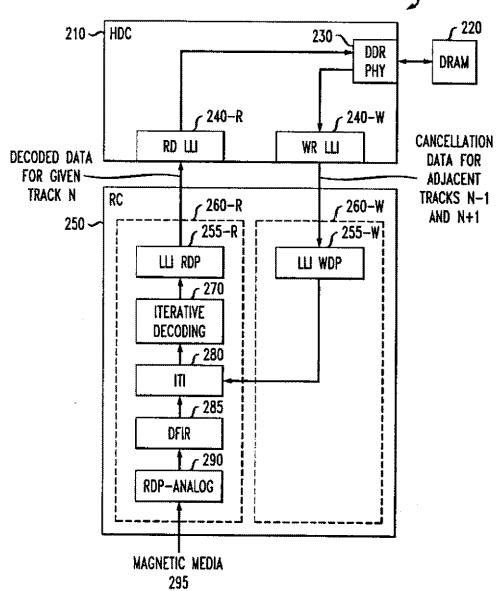

【図2】本発明によるITIの軽減を組み込む磁気記録システムの概略構成図である。

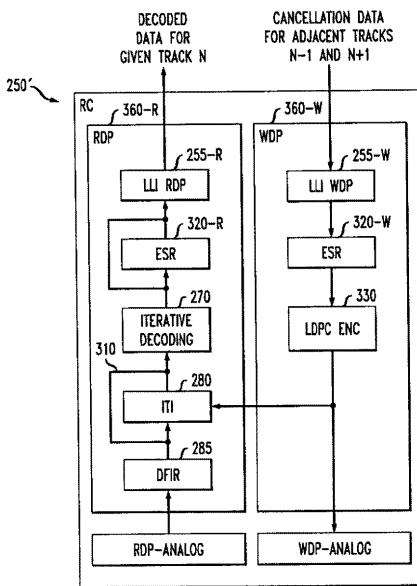

【図3】図2の一部として示されたリード・チャネルの代替的な実装の概略構成図である。

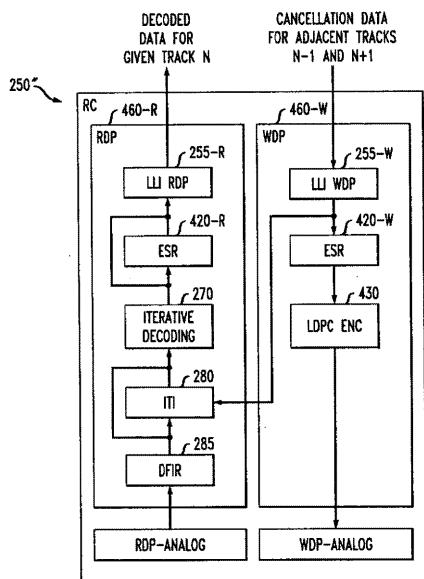

【図4】図2の一部として示されたリード・チャネルの代替的な実装の概略構成図である。

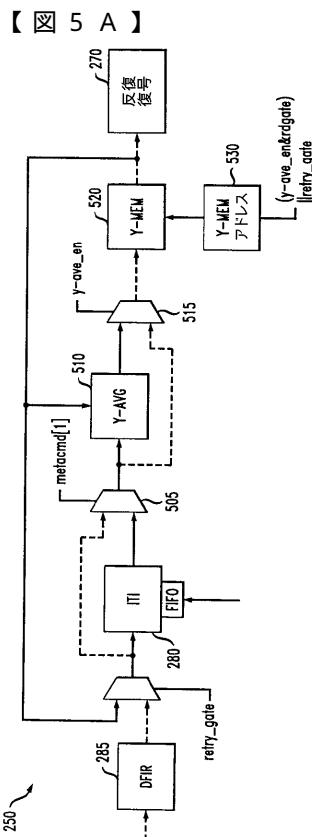

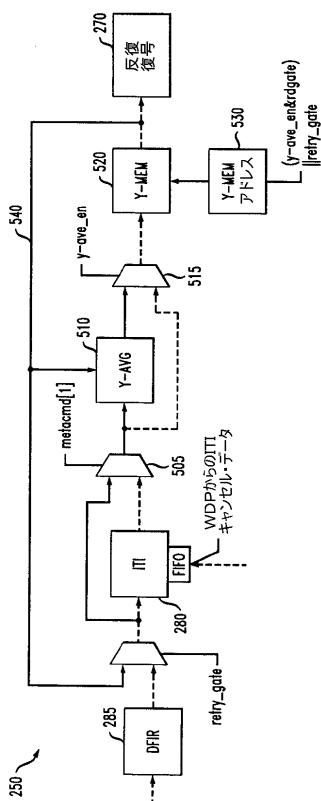

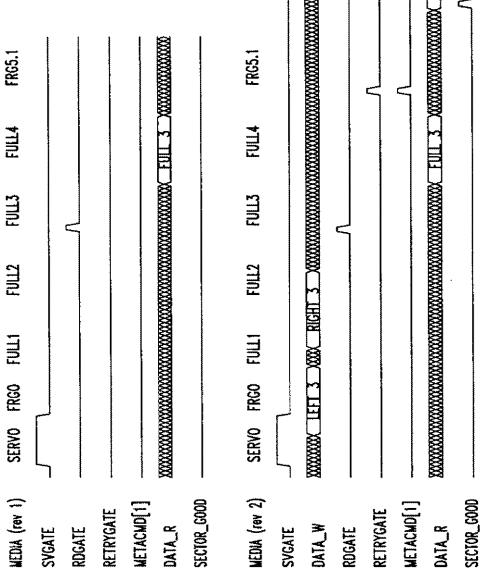

【図5A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

20

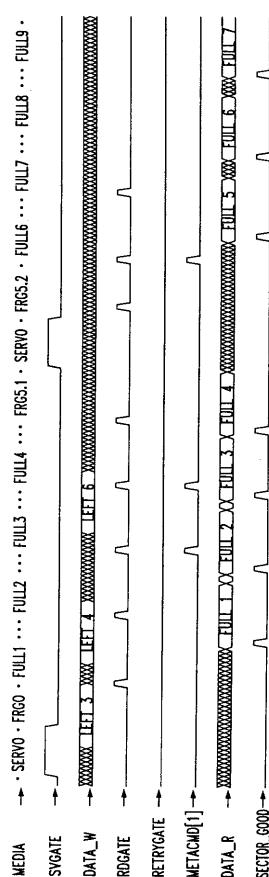

【図5B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

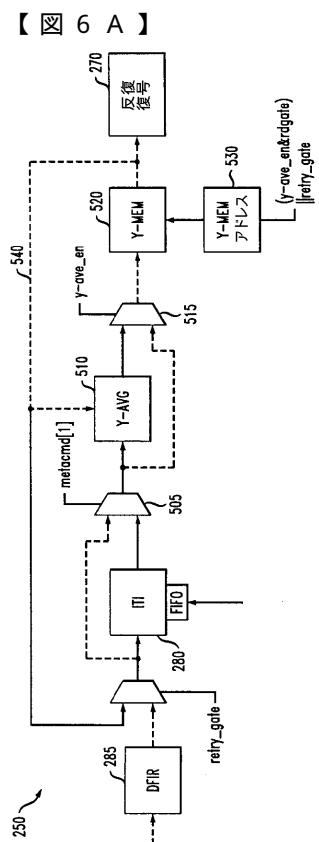

【図6A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図6B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

30

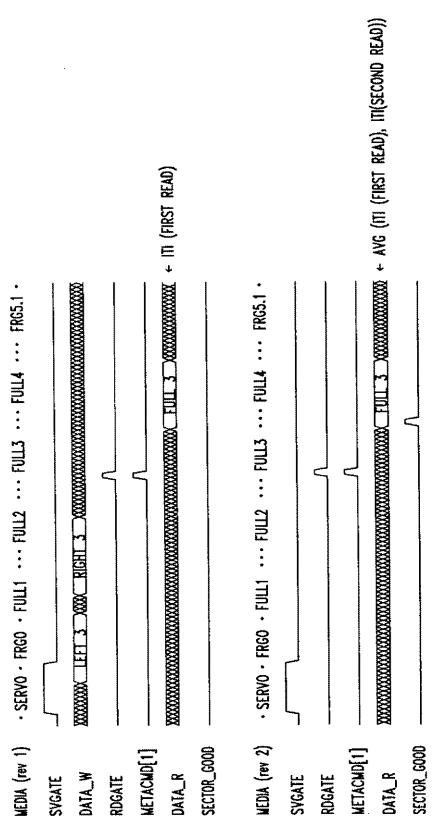

【図7A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図7B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図8A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

40

【図8B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図8C】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

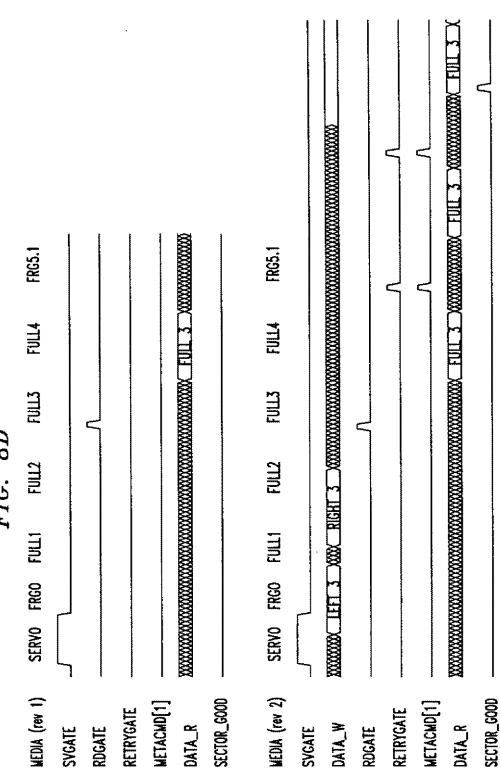

【図8D】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図9A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

50

。【図9B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図10A】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図10B】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

【図10C】いくつかの例示的な動作モードおよび各モードに関する対応するインターフェース信号を実装するためのさまざまな構成の図2～4のリード・チャネルを示す図である。

#### 【発明を実施するための形態】

##### 【0012】

本発明は、磁気記録システムにおけるトラック間干渉の軽減のためのハードウェアに基づく方法および装置を提供する。ITIの軽減は、正しいデータ再生の見込みを高めるために、媒体から読み取られるデータを追加的なデータ（以降、「キャンセル・データ」と呼ばれる）と組み合わせる。キャンセル・データは、ITI軽減回路またはプロセスに供給されなければならない。キャンセル・データは、当業者に明らかであろうように、ディスク媒体から読み取られるか、または別のソースから取得され得る。

##### 【0013】

本発明の一態様によれば、開示されたトラック間干渉の軽減のためのハードウェアに基づく技術は、HDCからキャンセル・データを取得するが、HDCの処理ユニットがITIの計算を実行することを要求しない。本発明の別の態様によれば、後のデジタル信号処理（DSP）のために読み取りデータ経路に示すためのキャンセル・データを記憶し、供給し、操作し、それによって、書き込まれたデータを正しく再生する可能性を高めるためのシステムが、開示された。

##### 【0014】

リード・チャネルは、通常、所与の時間に読み取りモードかまたは書き込みモードのいずれかであるスレーブ・デバイスである。各モードで、データは、通常、一方向にしか流れない。例えば、データは、書き込みモードにおいては、ハードディスクコントローラ（HDC）から、媒体へのリード・チャネル（RC）に流れ、読み取りモードにおいては、媒体からRCへ流れ、次いでHDCへと流れる。本発明は、書き込みデータ経路（WDP）の少なくとも一部が、リード・チャネルが読み取りモードで読み取り動作を実行しているときに通常はアイドル状態であることを認識する。

##### 【0015】

したがって、本発明のさらなる態様によれば、（読み取り動作中、通常はアイドル状態であるか、または休止状態である）書き込みデータ経路が、読み取りデータ経路のITI軽減回路にキャンセル・データを伝達するために使用される。このように、書き込みデータ経路が、キャンセル・データをリード・チャネルに送信するために、読み取り動作中に使用される。キャンセル・データは、磁気媒体から読み取りデータ経路によって取得される媒体データと実質的に同時にITI軽減回路に与えられる。その他の利点として、書き込みデータ経路は、通常、データを符号化し、スクランブルし、バッファリングし、（後で媒体に書き込まれる）誤り訂正データを計算するための機能を含み、この機能が、ITIの軽減のために本発明にしたがって利用されることができる。このようにして、開示されたITI軽減システムは、書き込み経路のそうでなければアイドル状態であるハードウェアおよび既存のバッファリング能力を利用して、最小限の設計の労力、領域の消費、および電力のコストでITIの軽減を可能にする。

##### 【0016】

10

20

30

40

50

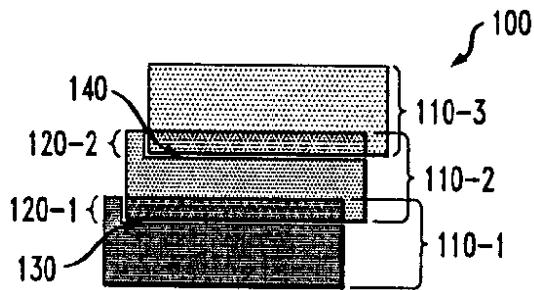

図1は、例示的なシングルド磁気記録(SMR)システムの磁気媒体100上のいくつかの例示的なトラック110-1から110-3の一部を示す。トラック110-1から110-3は、通常、(図1において下から上に示されるような)数が大きくなる順序で書き込まれる。本明細書に記載のいくつかの例は、左右のトラックに言及し、それらは、所与のトラックに対してそれぞれ左および右に隣接するトラックについての言及である。図1に示されるように、例示的なトラック110-1、110-2、および110-3は、トラック110-1と110-2の間の第1の重なる領域120-1を有し、トラック110-2と110-3の間の第2の重なる領域120-2を有するように書き込まれる。例えば、トラック110-2から読み取られる信号は、トラック110-3が、既に書き込まれたトラック110-2に重ねて書き込まれるので、トラック110-3から読み取られる信号によって大きく影響される。トラック110-2から読み取られる信号は、トラック110-2の左端が、トラック110-1の右端の上に書き込まれるので、トラック110-1に既に書き込まれたデータによってやはり影響される。トラック110-2に関するリード信号は、記録されたデータを読むためにトラック上に位置付けられる読み取りヘッドの位置およびサイズに大きく依存する。読み取りヘッドが、例えば、端140などのその他のトラック110-3の端よりも、端130などのトラック110-2の一端に近く位置付けられる場合、端130に隣接する対応するトラック110-1は、端140に隣接するトラック110-3よりもトラック110-2のリード信号に影響を与える。読み取りヘッドが110-2の重ねられていない領域と同じか、またはそれよりも大きい場合、トラック110-1と110-3の両方が、ITI雑音を引き起こす可能性が高い。

#### 【0017】

一方の隣接するトラックは、他方の隣接するトラックよりも重大なITIの影響を有する可能性があることが留意される。例えば、隣接するトラックの位置に対する真ん中のトラック110-2上の読み取りヘッドの位置は、真ん中のトラックに対する、それぞれの隣接するトラックによって寄与されるITIの量に影響する可能性がある。したがって、任意的に、ITIの軽減は、より重大なITIの寄与を有する隣接するトラックに対して最初に実行され得る。以下でさらに検討されるように、本明細書に記載の例示的な実施形態は、一方の側のトラックを使用するかもしくは反対側のトラックを使用するかについて、または両側のITIの軽減が実行されている場合には側面のトラックの順序についていかなる制限も課さない。開示されたITI軽減メカニズムは、正常な再生が行われるとITI軽減プロセスが終了することを許すように、(事前に知られている場合)最も重要なキャンセルが最初に実行されることを可能にする。

#### 【0018】

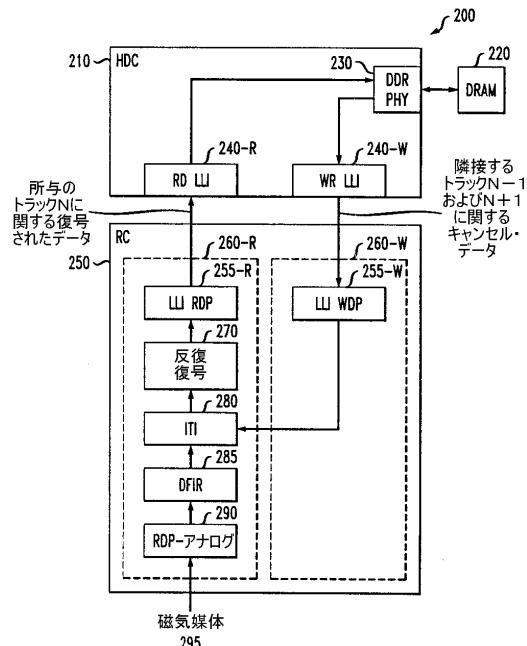

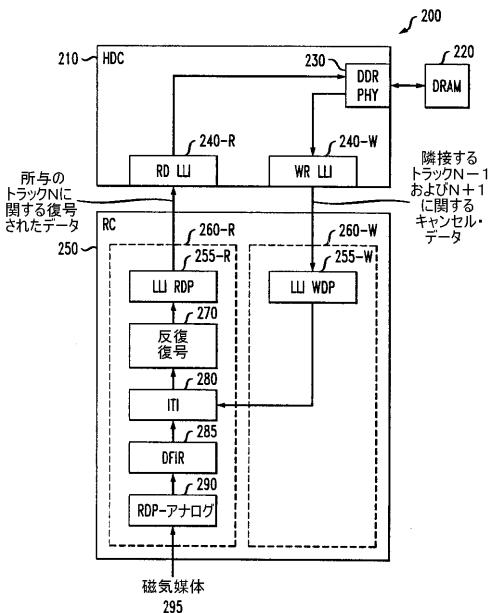

図2は、本発明によるITIの軽減を組み込む磁気記録システム200の一部の概略構成図である。図2は、読み取り動作中のITIの軽減のための磁気記録システム200の構成を示す。図2に示されるように、磁気記録システム200は、ハードディスクコントローラ(HDC)210およびリード・チャネル(RC)250を含む。リード・チャネル250は、読み取りデータ経路(RDP)260-Rおよび書き込みデータ経路(WDP)260-Wを含む。既に示されたように、書き込みデータ経路260-Wは、所与のトラックNに隣接するトラックN-1およびN+1などの1つまたは複数の隣接するトラックに関するキャンセル・データを、読み取りデータ経路260-RのITI軽減回路280に伝達するために本発明によって使用される。キャンセル・データは、磁気媒体から読み取りデータ経路260-Rによって取得される媒体データと実質的に同時にITI軽減回路280に与えられる。

#### 【0019】

概して、RDP-アナログ・ブロック290は、交流結合減衰器(ac-coupling, attenuator)(ACC)、適応制御、ベースライン補償(base line compensation)、磁気抵抗非対称(MRA)補償(magneto-resist asymmetric(MRA) compensation)、サーマ

10

20

30

30

40

50

ル・アスペリティ (thermal asperity) (TA) 検出を備える可変利得増幅器 (VGA)、デジタル信号処理のための適応制御を備える連続時間フィルタ (CTF)、およびアナログ・デジタル・コンバータ (ADC) などのいくつかのアナログ・コンポーネントを含む。概して、サーマル・アスペリティは、読み取りヘッドが、磁気材料が存在するディスク・プラッタの平面の上に隆起しているその磁気材料の一部に衝突するときに発生し、信号の振幅を実質的に大きくする。サーマル・アスペリティ検出ブロックは、知られている方法で、そのような磁気材料部分を特定し、それらを補償するように試みる。

【0020】

次いで、デジタル化された信号が、信号を等化するデジタル有限インパルス応答 (DFIR) フィルタ 285 によってフィルタリングされる。DFIR 285 は、フィルタリングされた出力を ITI 軽減回路 280 に提供する。次に、ITI 軽減回路 280 によって生成された ITI が打ち消された信号が、ビタビ検出器と、低密度パリティ検査復号器などの復号器とを含む反復復号ブロック 270 に与えられる。読み取りデータ経路 260-R は、所与のトラック N に関する復号されたデータをハードディスクコントローラ 210 に提供する。

【0021】

既に示されたように、書き込みデータ経路 260-W は、概して、誤り訂正が後のデータの読み取りに対して実行され得るように、媒体に書き込まれるべきデータを符号化する機能を含む。加えて、書き込みデータ経路 260-W は、さらに、データをスクランブルし、バッファリングし、この機能は、ITI の軽減のために本発明によって利用されることができる。

【0022】

例示的な ITI 軽減回路 280 のより詳細な検討については、例えば、参照により本明細書に援用される、「Systems and Methods for Inter-Track Interference Compensation」と題された、2011年7月19日に出願された米国特許出願第13/186,174号（代理人整理番号AGERE-022110）を参照されたい。本発明による ITI の軽減のためのいくつかの例示的な技術が、図 5～10 に関連して以下でさらに検討される。例えば、本発明のさまざまな実装は、ITI の軽減を用いるかまたは用いない、磁気媒体 295 の直接読み取りをサポートする。加えて、本発明の別の実装は、少なくとも片側の ITI の軽減を用いるオンザフライ (OTF) またはリアルタイムの読み取りをサポートする。本発明のさらに別の実装は、両側の ITI の軽減まで用いたオフラインの読み取りをサポートする。

【0023】

本発明は、Y-平均された (Y-Averaged) データなどの後処理された DFIR データの ITI の軽減、および / または ITI を軽減されたデータの Y-平均などの、ITI を軽減された DFIR データの後処理もサポートする。例えば、Y-平均されたデータの ITI の軽減は、複数の読み取りにわたる Y-平均を取得することと、次いで、Y-平均されたサンプルを用いて ITI の軽減および復号を実行することとを含む。同様に、ITI を軽減されたデータの Y-平均は、セクタを読み取ることと、現在の読み取ったセクタを用いて ITI の軽減および任意的に復号を実行することと、複数の読み取りからの ITI を軽減されたサンプルを用いて Y-平均を得ることとを含み、その後に次のセクタの読み取りが続き、以下同様である。

【0024】

図 2 に示されるように、ハードディスクコントローラ 210 は、それぞれ、読み取りデータ経路 (RDP) 260-R および書き込みデータ経路 (WDP) 260-W の対応する長レイテンシ・インターフェース (long latency interface) (LLI) 255-R、255-W と通信するための例示的な長レイテンシ・インターフェース (LLI) 240-R、240-W を含む。

【0025】

10

20

30

40

50

ハードディスクコントローラ 210 は、ダイナミックランダムアクセスメモリ (D R A M ) 220 などの外部ダブルデータレート (D D R ) デバイスと通信するためのダブルデータレート (D D R ) P H Y インターフェース 230 も含む。キャンセル・データは、例えば、外部 D R A M 220 、またはスタティックランダムアクセスメモリ (S R A M ) もしくはフラッシュメモリなどの別の不揮発性メモリに記憶され得る。例示的な D R A M 220 は、磁気媒体 100 (図 1 ) または磁気媒体 295 (図 2 ) の 1 つまたは複数のトラックに関するキャンセル・データを記憶することができる。例えば、記憶されるキャンセル・データの量は、現在読み取られているトラックに関するトラック間隔 ( t r a c k s p a c i n g ) に応じて決まる可能性がある。例示的な D R A M 220 は、D R A M に記憶される必要があるデータの量を削減するために 1 つまたは複数のセクタ ( 例えば、以前の読み取り動作中に正常に再生されることができなかつたセクタ ) だけに関するキャンセル・データを記憶することもできる。

10

## 【 0026 】

サイドトラック・データとも呼ばれるキャンセル・データは、当業者に明らかであろうように、いくつかの例示的なフォーマットを有する可能性がある。概して、例示的なキャンセル・データは、書き込まれた媒体の波形に対応する符号化された媒体データ、またはハードディスクコントローラ 210 によって通常供給される符号化されていないユーザ・データを含み得る。概して、例示的な媒体データ・フォーマットは、低密度パリティ検査 ( L D P C ) オーバヘッド、ランレンジス制限 ( r u n - l e n g t h \_ l i m i t e d ) ( R L L ) 符号化オーバヘッド、および誤り検出符号 ( E D C ) オーバヘッドを含む符号化されたデータを含む。図 3 および 4 は、媒体データを処理するための異なる実施形態を組み込むリード・チャネル 250 の代替的な実装 250 ' および 250 '' をそれぞれ示す。図 3 および 4 において、ランレンジス制限および誤り検出符号符号器および復号器機能ならびにスクランブル機能は、「 E S R 」 ( すなわち、誤り検出符号、スクランブル、および R L L ) とラベル付けされる。

20

## 【 0027 】

例示的な実施形態において、 I T I 軽減回路 280 は、「 Y - データ ( Y - D a t a ) 」と呼ばれる等化されたアナログ・デジタル・コンバータ ( A D C ) サンプルを処理することができる。代替的な実施形態において、 I T I 軽減回路 280 は、本明細書では「 A D C データ」と呼ばれる生の ( 等化されていない ) A D C サンプルを処理することができる。 Y - データまたは A D C データは、例えば、媒体に書き込まれた各媒体ビット ( m e d i a \_ b i t ) に関する 6 ビットのデータである可能性がある。 A D C - データまたは Y - データは、磁気媒体 295 から読み取られ、それぞれ、 A D C または D F I R 等化器の出力で利用可能である。反復復号ブロック 270 は、各 Y - データ・サンプルを検出された媒体データの単一のビットに、ならびに ( パリティおよびその他のオーバヘッド・ビットの除去の後 ) 検出されたユーザ・データの単一のビットに変換する。反復復号ブロック 270 は、例えば、よく知られている L D P C 復号器を用いて具現化され得る。

30

## 【 0028 】

例示的な実施形態において、書き込みデータ経路 260 - W は、 I T I キャンセル・データをユーザまたは媒体データ・フォーマットで表す。代替的な実施形態において、書き込みデータ経路 260 - W は、 I T I キャンセル・データを A D C または Y - データ・フォーマットで表し、その場合、媒体ビットごとの複数のビットが、 D R A M に記憶され、 H D C から書き込みデータ経路 260 - W に供給される。 I T I 軽減回路 280 は、書き込みデータ経路 260 - W が何を供給するかに応じて媒体データ、 A D C データ、または Y - データに基づいて I T I を軽減する。 H D C が I T I キャンセル・データをリード・チャネルにユーザ・データ・フォーマットで提供する場合、書き込みデータ経路は、図 3 および 4 に示されるように、ユーザ・データを媒体データに変換する。

40

## 【 0029 】

D D R P H Y 230 が追加的な費用およびシステム設計の修正なしに Y - データまた

50

は A D C データ・フォーマット（例えば、記憶された媒体ビットごとに 6 ビット）をサポートするのに十分な帯域幅を持たない場合、本発明のユーザまたは媒体データ・フォーマットの実装である単一ビット・フォーマットは、それでもサポートされることができることが留意される。単一ビット・フォーマットを用いると、1 ビット単位の帯域幅が追加される必要があるだけである。読み取りデータは、既存の非 I T I ドライブのメモリに書き込まれることがさらに留意される。したがって、D D R からデータを読み取り、開示された I T I キャンセル手順で使用するためにリード・チャネルにキャンセル・データを送るために 1 帯域幅ビット単位が追加されるだけである。単一ビット・フォーマットを使用することによって、D R A M で I T I キャンセル・データのために必要とされるストレージの量が、やはり大幅に削減される。

10

### 【 0 0 3 0 】

1 つの例示的な実施形態において、磁気記録システム 2 0 0 は、I T I キャンセル・データが所与の読み取り動作のために使用されるべきかどうかを示す、例えば、M E T A C M D [ 1 ] または I T I \_ G A T E と呼ばれる I T I 制御信号またはレジスタを含む。I T I 制御信号が I T I キャンセル・データが所与の読み取り動作のために使用されるべきでないことを示す場合、I T I 軽減回路 2 8 0 は、図 3 ~ 4 で以下にさらに示されるように（I T I の軽減のために使用されるべきデータが存在しないので）任意的に迂回することができる。加えて、例示的な磁気記録システム 2 0 0 は、例示的な実施形態において、I T I のキャンセルが 1 つの隣接するトラックのみに対して実行されるべきか（例えば、I T I \_ S I D E S が I T I \_ S I D E S = 0 に設定される）、または 2 つの隣接するトラックに対して実行されるべきか（例えば、I T I \_ S I D E S が I T I \_ S I D E S = 1 に設定される）を示すための、例えば、I T I \_ S I D E S と呼ばれるモード制御信号またはレジスタを含む。概して、任意の数 N のトラックが、真ん中のトラックに I T I の影響を有する可能性がある。当業者に明らかであろうように、追加的に、N 個の側面の I T I の軽減が、本発明にしたがって N ステップで実行され得る。

20

### 【 0 0 3 1 】

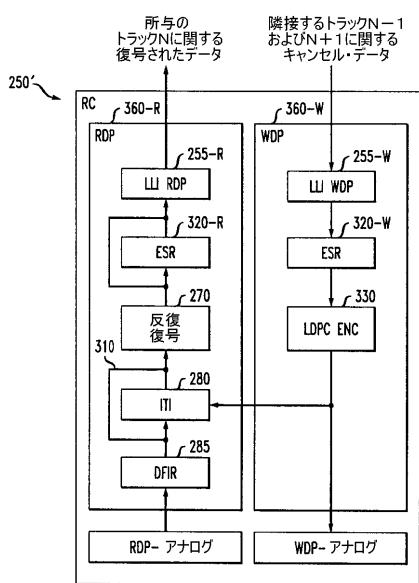

図 3 は、書き込みデータ経路が I T I 軽減回路 2 8 0 に示すための媒体データを生成する、図 2 のリード・チャネル 2 5 0 の代替的な実装 2 5 0 ' の概略構成図である。図 3 に示されるように、例示的なリード・チャネル 2 5 0 ' は、図 2 と同様にして、読み取りデータ経路 3 6 0 - R と、書き込みデータ経路 3 6 0 - W を含む。読み取りデータ経路 3 6 0 - R は、図 2 の読み取りデータ経路 2 6 0 - R と同様にして実装され得る。既に示されたように、書き込みデータ経路 3 6 0 - W は、キャンセル・データを、読み取りデータ経路 3 6 0 - R の I T I 軽減回路 2 8 0 に伝達するために本発明によって使用される。キャンセル・データは、磁気媒体から読み取りデータ経路 3 6 0 - R によって取得される媒体データと実質的に同時に I T I 軽減回路 2 8 0 に与えられる。別の例示的な実施形態において、キャンセル・データは、磁気媒体から読み取りデータ経路 3 6 0 - R によって取得される対応する媒体データの前または後に I T I 軽減回路 2 8 0 に与えられる。

30

### 【 0 0 3 2 】

読み取りデータ経路 ( R D P ) 3 6 0 - R および書き込みデータ経路 3 6 0 - W の長レインシ・インターフェース ( L L I ) 2 5 5 - R 、 2 5 5 - W は、それぞれ、図 2 と同様にして実装され得る。さらに、反復復号ブロック 2 7 0 および I T I 軽減回路 2 8 0 は、図 2 と同様にして実装され得る。

40

### 【 0 0 3 3 】

図 3 の例示的な実施形態において、符号化された媒体データは、書き込みデータ経路 3 6 0 - W によって生成される。H D C は、I T I キャンセル・データを書き込みデータ経路にユーザ・データ・フォーマットで提供する。図 3 に示されるように、例示的な書き込みデータ経路 3 6 0 - W は、ユーザ・データを、I T I キャンセル・データとして I T I 軽減回路に提供される符号化された媒体データに符号化する E S R 符号器 3 2 0 - W および L D P C 符号器 3 3 0 を含む。書き込みデータ経路は、媒体への書き込み動作中と同様の方法でユーザ・データを符号化する。

50

## 【0034】

図3に示されるように、読み取りデータ経路360-RのITI軽減回路280は、ITIのキャンセルが所与の読み取り動作に関して有効化されないとき、任意的に迂回され得る。さらに、読み取りデータ経路360-RのESR符号器320-Rは、媒体データ・フォーマットが再生されるべきであるとき、任意的に迂回され得る。

## 【0035】

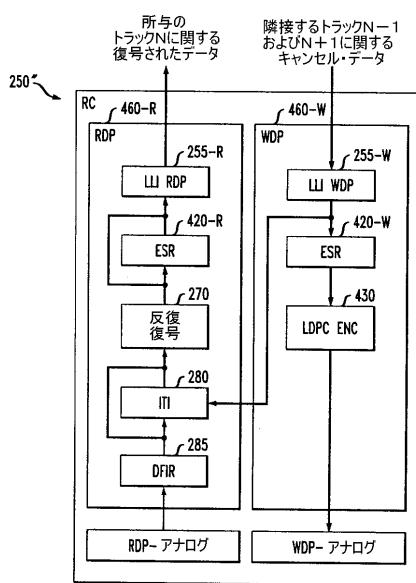

図4は、書き込みデータ経路がユーザ・データをITI軽減回路280に提供し、ITI軽減回路280がユーザ・データから媒体データを生成する、図2のリード・チャネル250の代替的な実装250'の概略構成図である。図4に示されるように、例示的なリード・チャネル250'は、図2と同様にして、読み取りデータ経路460-Rと、書き込みデータ経路360-Wとを含む。読み取りデータ経路460-Rは、図2の読み取りデータ経路260-Rと同様にして実装され得る。既に示されたように、書き込みデータ経路460-Wは、キャンセル・データを、読み取りデータ経路460-RのITI軽減回路280に伝達するために本発明によって使用される。キャンセル・データは、磁気媒体から読み取りデータ経路460-Rによって取得される媒体データと実質的に同時にITI軽減回路280に与えられる。別の例示的な実施形態または動作モードにおいて、キャンセル・データは、磁気媒体から読み取りデータ経路460-Rによって取得される媒体データの前または後にITI軽減回路280に与えられる。

10

## 【0036】

読み取りデータ経路(RDP)460-Rおよび書き込みデータ経路460-Wの長ライエンシ・インターフェース(LLI)255-R、255-Wは、それぞれ、図2と同様にして実装され得る。さらに、反復復号ブロック270およびITI軽減回路280は、図2と同様にして実装され得る。

20

## 【0037】

図4の例示的な実施形態において、符号化された媒体データは、書き込みデータ経路460-Wによって提供されるユーザ・データからITI軽減回路280により生成される。したがって、図4に示されるように、例示的な書き込みデータ経路460-WのESR符号器420-WおよびLDPD符号器430は、ITI軽減回路280に与えられるユーザ・データによって迂回される。書き込みデータ経路460-WのESR符号器420-WおよびLDPD符号器430は、ユーザ・データが媒体に書き込まれる前に媒体データに符号化されるときは、書き込み動作中にユーザ・データによって迂回されない。

30

## 【0038】

図4に示されるように、読み取りデータ経路460-RのITI軽減回路280は、ITIのキャンセルが所与の読み取り動作に関して有効化されないとき、任意的に迂回され得る。さらに、読み取りデータ経路460-RのESR符号器420-Rは、媒体データ・フォーマットが再生されるべきであるとき、任意的に迂回され得る。

40

## 【0039】

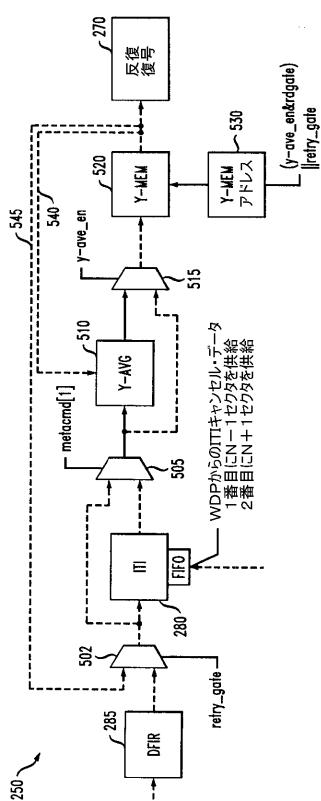

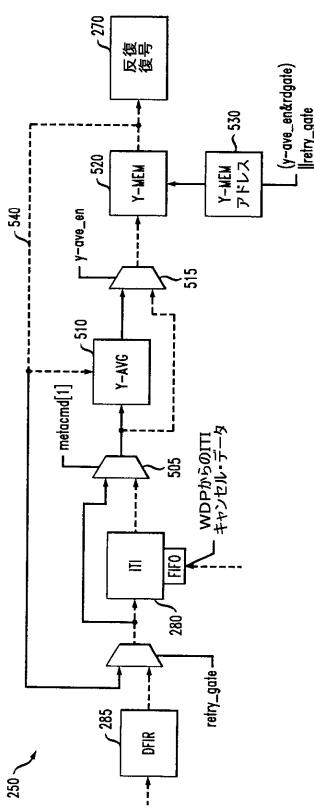

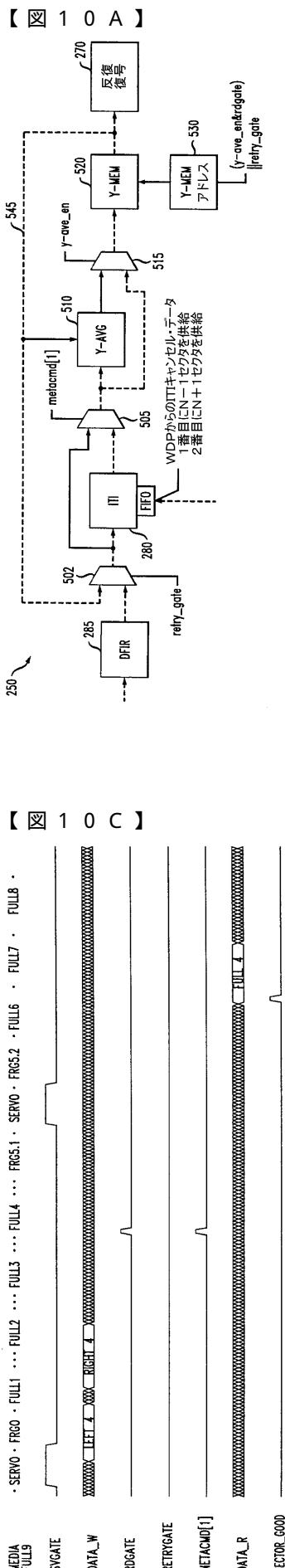

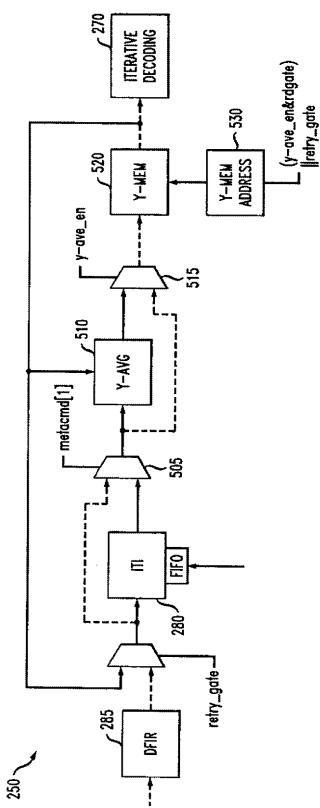

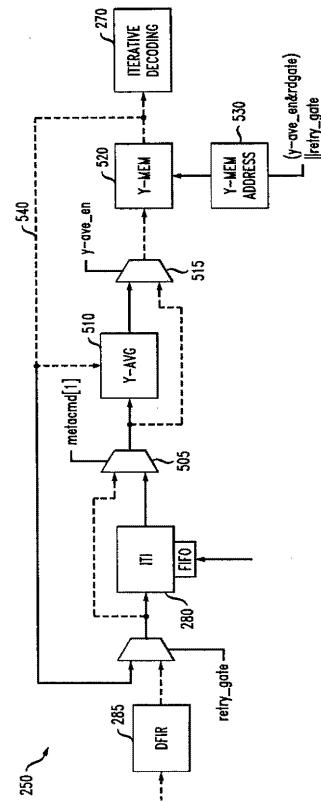

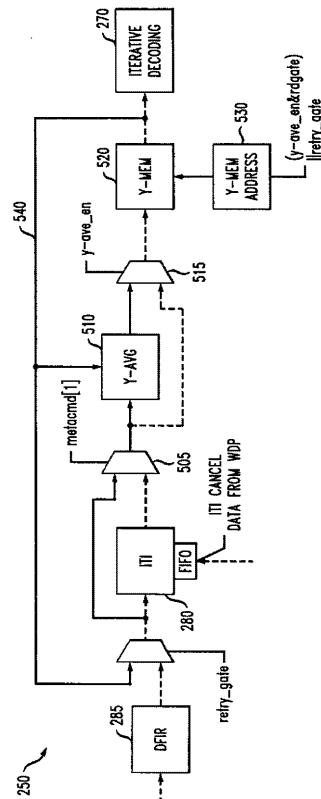

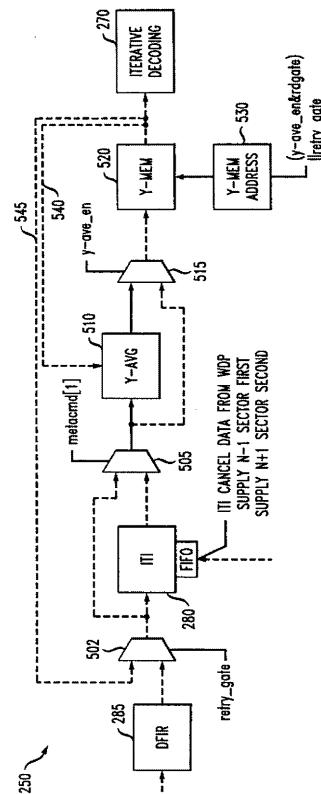

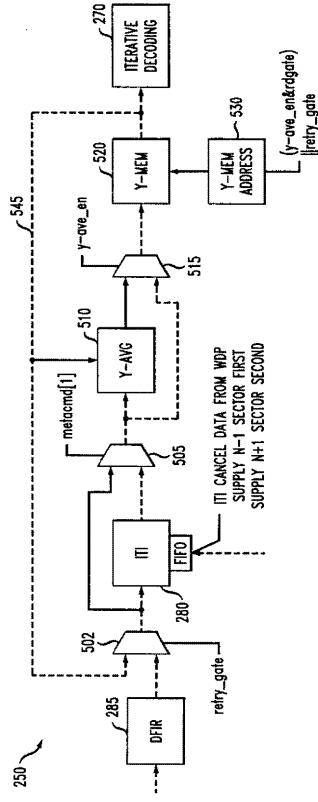

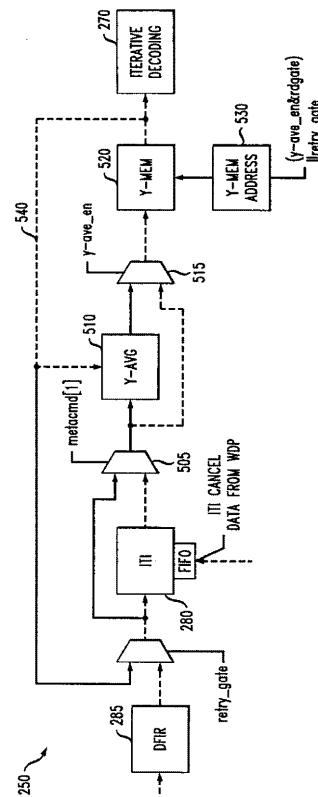

図5～10は、いくつかの例示的な動作モードを実装するためのさまざまな構成のリード・チャネル250を示す。図5～10において、アクティブな信号経路は、太字破線矢印を用いて示される。図5～10に示されるように、および上で検討されたように、リード・チャネル250は、デジタル有限インパルス応答フィルタ285、ITI軽減回路280、および反復復号ブロック270を含む。

## 【0040】

加えて、図5～10に関連して以下でさらに検討されるように、リード・チャネル250は、マルチプレクサ505、515、Y-AVG後処理ブロック510、Y-MEMメモリ・ブロック520、およびY-データを処理するためのY-MEMアドレス・ブロック530をさらに含む。

## 【0041】

図5Aは、例示的な非ITI動作モードのリード・チャネル250を示す。概して、非ITIモードは、ITIの軽減が必要とされないときに（例えば、トラックの分離が十分

50

であるときに)選択的に無効化されることを可能にし、さらに、リード・チャネル250がITIの軽減がサポートされない可能性があるレガシーシステムで使用されることを可能にする。図5Aに示されるように、ITI軽減回路280は、マルチプレクサ505を用いて迂回され、Y-AVGブロック510は、マルチプレクサ515を用いて迂回される。したがって、非ITIモードのためのアクティブな信号経路は、DFIRフィルタ285、Y-MEMブロック520、および反復復号ブロック270を含む。概して、Y-データは、Y-MEMブロック520に記憶され、次いで、復号のために反復復号ブロック270に適用される。

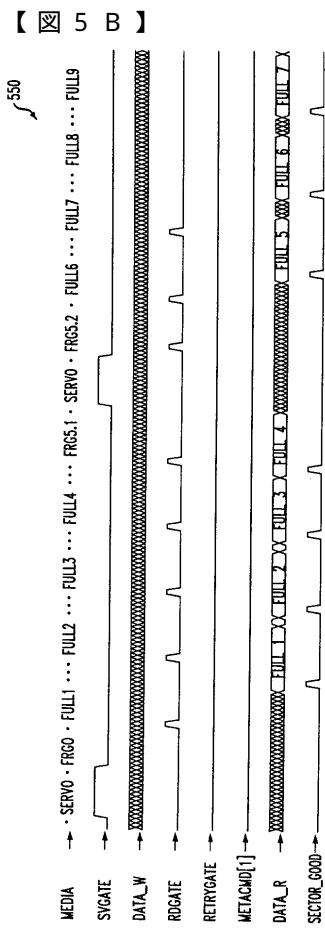

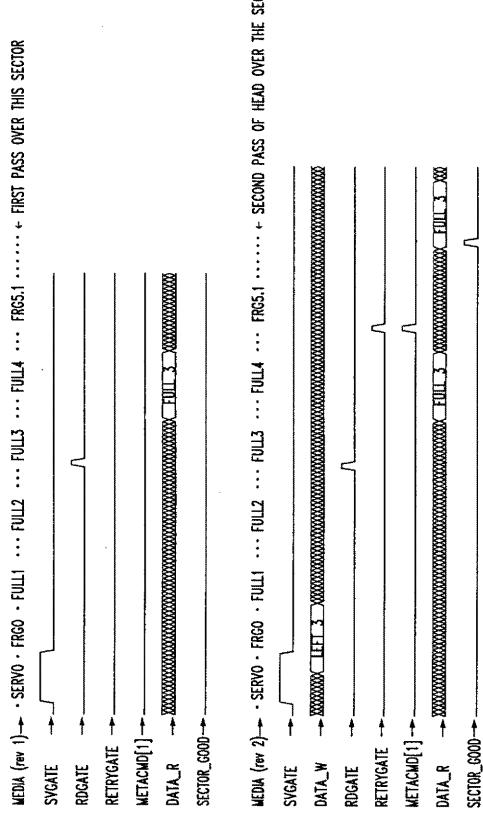

#### 【0042】

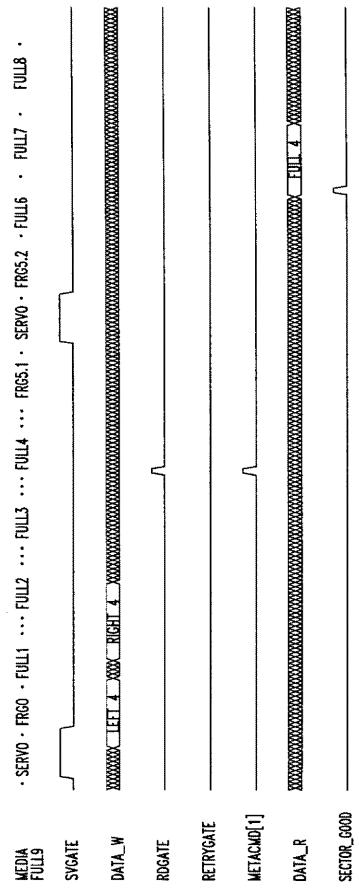

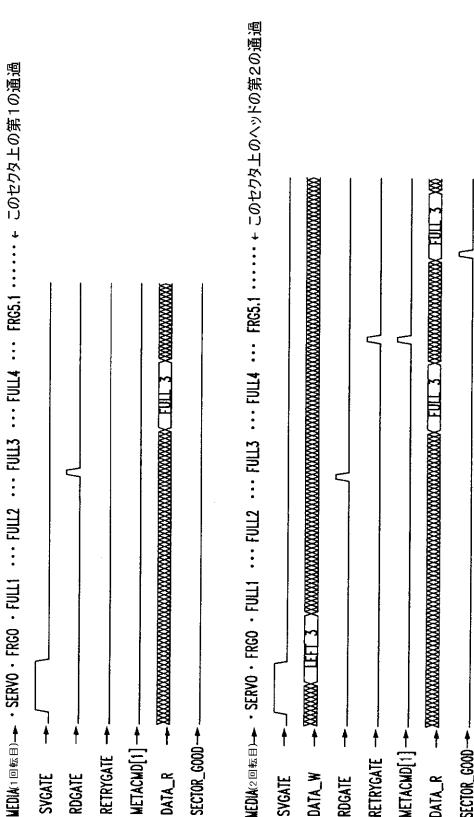

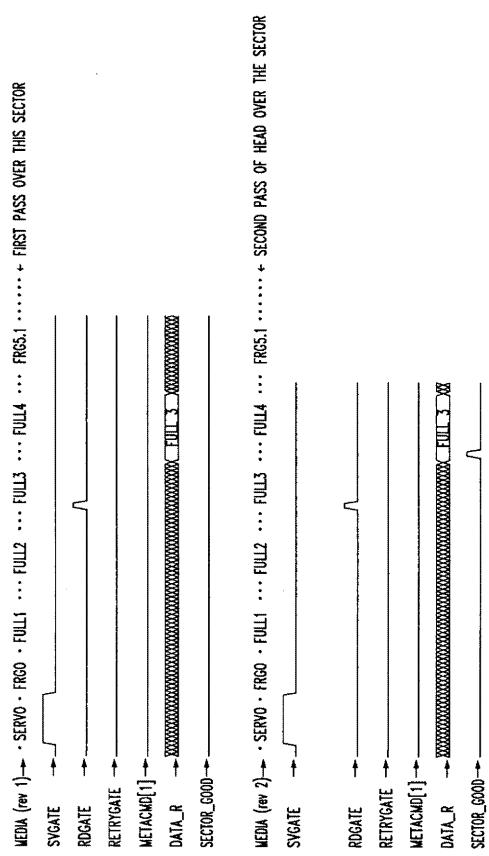

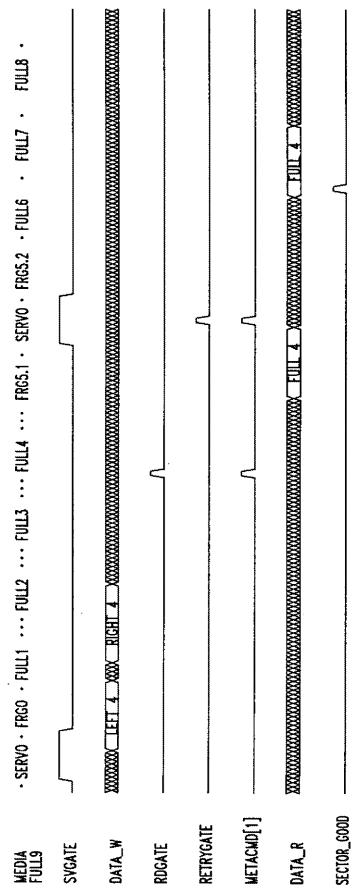

図5Bは、図5Aの例示的な非ITI動作モードに関して、いくつかのインターフェース信号を時間の関数として示す。概して、以下の図において、MEDIA信号は、何が媒体上にあるか(サーボ(servo)、フラグメント(fragment)、またはフル・セクタ(full sector))を示す。図の用語「FRG」は、セクタのフラグメントを示し、用語「FULL」は、完全なセクタを示し、用語「SERVO」は、分割セクタ(split sector)を示す(例えば、FRG5.1は、左のセクタのフラグメントであり、FRG5.2は、右のセクタのフラグメントであり、それらは、「SERVO」ラベルによって示されるように分割される)。したがって、FRG5.1とFRG5.2とが一緒にFULLを構成する(フル・セクタが2つに分割される)。加えて、2つのRDGATEパルスが、各部分を読み取るために使用され、チャネルが、組み合わせてfullセクタを再生する。一部の図において、用語「MEDIA(1回転目)」および「MEDIA(2回転目)」は、同じセクタが2回読まれる(ディスクが、ヘッドをもう一度そのセクタの上に持ってくるために一周しなければならない)ことを示す。

#### 【0043】

SVGA信号は、(単に参照のために)サーボ・ゲート(servo gate)を示す(および、媒体上のあらゆるSERVOの上でhighである)。DARA\_W信号は、(ITIキャンセル・データがチャネルに入る)書き込み経路データを示す。LEFT#は、同じ番号を有するセクタに関する左キャンセル・データを示し、つまり、LEFT#は、左のトラックに書き込まれた隣接するデータに対応する。RIGHT#は、同じ番号を有するセクタに関する右キャンセル・データを示し、つまり、RIGHT#は、右のトラックに書き込まれた隣接するデータに対応する。図1を参照すると、トラック2がデータが再生される現在のトラックである場合、トラック1およびトラック3が、それぞれ、隣接する左トラックおよび右トラックである。

#### 【0044】

RDGATE信号は、リード・ゲート(read gate)に対応し、媒体からの読み取りを示す。RDGATE信号は、各セクタおよびセクタのフラグメントの始まりにおいてアクティブである。RETRYGATE信号は、記憶されたサンプルからの(y-memor y)からの)再試行を示す。RETRYGATE信号は本明細書においてはITIの軽減との関連で示されるが、当業者に明らかであろうように、RETRYGATE信号は、その他の用途でも使用され得ることが留意される。

#### 【0045】

本明細書において検討されるように、信号METACMD[1]は、(RDGATEまたはRETRYGATEに合わせられた)読み取りまたは再試行と一緒にITIの軽減をトリガする。図5Bは軽減を用いない通常の読み取り動作に対応するので、METACMD[1]はアクティブではない。

#### 【0046】

DATA-R信号は、再生されたセクタ・データを示す(FULL#は、同じ名前の媒体のセクタに関する再生されたデータを意味する)。加えて、SECTOR\_GOOD信号は、良好なセクタが再生されたことを示す(セクタが良好でないときは、追加的な処理が、セクタを再生するために実行される)。

10

20

30

30

40

50

## 【0047】

さらに、以下の図のうちの1つまたは複数において、以下の表記が使用される。

`avg(data1, data2)` は、同じデータの2回の読み取り動作からのデータのビットごとの平均を示し、媒体上に記憶された各ビットに関して、対応するY-サンプル(`Y-sample`)`data1`および`data2`が平均される。代替的な実装においては、ADCサンプルが平均される。

`decode(data)` は、L D P C復号動作(Y-データから媒体またはユーザ・ビットに変換されるデータ再生)を示し、Y-データは、例えば、6ビットを用いて表される。

`iti(left, data)` は、「`data`」内の主トラック信号から左の隣接するトラックによってもたらされたITIを除去することを示す。 10

`iti(left, right, data)` は、「`data`」内の主トラック信号から左右両方の隣接するトラックによってもたらされたITIを除去することを示す。

## 【0048】

図6Aは、例示的な後処理(非ITI)動作モードのリード・チャネル250を示す。図6Aに示されるように、ITI軽減回路280は、マルチブレクサ505を用いて迂回される。したがって、非ITIモードのためのアクティブな信号経路は、DFIRフィルタ285、(マルチブレクサ515を用いて選択される)Y-AVGブロック510、Y-MEMブロック520、および反復復号ブロック270を含む。Y-MEMアドレス・ブロック530は、知られている方法でY-MEMブロック520の選択を制御する。概して、所与のセクタからの記憶されたデータの最初の読み取りに関するY-データが、Y-MEMブロック520に記憶され、次に、そのセクタからのデータのその後の再読み取りに関するすべてのサンプルが、Y-AVGブロック510によってフィードバック経路540を用いてY-MEMブロック520の内容と合併される、つまり、平均される。所与のセクタは、その所与のセクタからの記憶されたデータが正常な復号動作によって示されるように正常に読み取られるまで、Y-MEMブロック520の内容が繰返しのたびに更新されるようにして複数回読み取られる可能性がある。Y-MEMブロック520の出力は、復号のために反復復号ブロック270にやはり適用される。 20

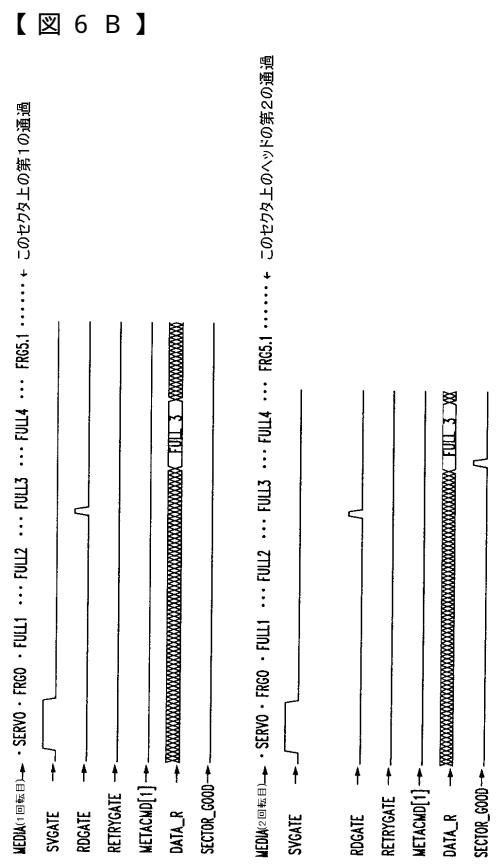

## 【0049】

図6Bは、図6Aの例示的な後処理(非ITI)動作モードについて、いくつかのインターフェース信号を時間の関数として示す。例示的な実施形態において実行される後処理は、記憶されたデータを2回読み取り、図6Bに示される2回の読み取り動作で読み取られたデータのビットごとの平均を実行することなどによる、ITIの軽減を用いない平均読み取り(Average Read)を含む。当業者に明らかであろうように、平均は、任意の回数の読み取り動作に対して実行され得る。第2の読み取りおよび平均が、データが再生され得るように雑音を十分に削減するので、ITIの軽減が必要とされないことが留意される。図6Bに示されるように、`SECTOR_GOOD`信号が、第3のセクタ上の第1の通過に関しては存在しないが、第3のセクタ上の第2の通過の後には存在する。セクタFULL3は、第1の読み取り中に読み取られ、次いで、反復復号器に渡され、復号されたセクタが、`DATA_R`バスに渡されることが留意される。セクタが誤りなしに正常に復号されなかったので、`SECTOR_GOOD`信号は、アサートされない。第2の回転で、第2の読み取りの後、2つの読み取りのY-データが平均され、Y-平均されたデータが、反復復号ブロックに渡され、反復復号ブロックが、セクタを正常に復号する。 40

## 【0050】

図7Aは、例示的なリアルタイムITI動作モードのリード・チャネル250を示す。概して、ITIの軽減が、データ転送速度で実行され、あらゆるセクタに対して任意的に実行され得る。図7Aの実施形態において、ITIの軽減は、スループットへの影響を少なくするために(例えば、例示的なモード制御信号またはレジスタ、`ITI_SIDE`によって示されるように)1つの隣接するトラックに対してのみ実行される。ITIキャ

10

20

30

40

50

ンセル・データは、図2に関連して上で検討されたように、書き込みデータ経路260-W(図2)から得られる。図7Aに示されるように、ITI軽減回路280は、マルチプレクサ505によってアクティブな信号経路に置かれ、Y-AVGブロック510は、マルチプレクサ515によって迂回される。したがって、リアルタイムITIモードのためのアクティブな信号経路は、DFIRフィルタ285、ITI軽減回路280、Y-MEMブロック520、および反復復号ブロック270を含む。概して、ITI軽減回路280のITIを補正された出力は、Y-MEMブロック520に記憶され、次いで、復号のために反復復号ブロック270に適用される。

#### 【0051】

図7Bは、図7Aの例示的なリアルタイムITI動作モードに関して、いくつかのインターフェース信号を時間の関数として示す。本明細書において検討されるように、例示的なリアルタイムITI動作モードは、ITIの軽減が、RDGATE信号と同時にMETACMD[1]信号をアサートすることによって選択的に有効化されることを可能にする。(OTFまたは再試行動作のいずれかに関してITI\_SIDES=0)。

10

#### 【0052】

RDGATE信号はセクタ1、2、3、4、5、6、7が媒体から読み取られることを示す。DATA\_W信号は、ITIの軽減がセクタ3、4、および6に対して左側のトラックを用いて実行されることを示す。METACMD[1]信号は、(RDGATEまたはRETRYGATEに合わせられた)読み取りまたは再試行と一緒にITIの軽減をトリガする。セクタ1、2、5、および7は、METACMD[1]信号が関連するRDGATEとともにアサートされないので、通常通りに処理されることが留意される。

20

#### 【0053】

両側のITI動作モードは、図10Aから10Cに関連して以下でさらに検討されることが留意される。

#### 【0054】

図8Aは、例示的なITI軽減付きの後処理動作モードのリード・チャネル250を示す。概して、ITI軽減付きの後処理モードは、後処理されたY-データに対してITIの軽減を実行する。図8Aに示されるように、ITI軽減回路280は、マルチプレクサ505を用いて選択的にアクティブな信号経路に置かれ、Y-AVGブロック510は、マルチプレクサ515を用いてアクティブな信号に置かれる。したがって、ITI軽減付きの後処理モードのためのアクティブな信号経路は、DFIRフィルタ285、ITI軽減回路280、Y-AVGブロック510、Y-MEMブロック520、および反復復号ブロック270を含む。Y-MEMアドレス・ブロック530は、知られている方法でY-MEMブロック520の選択を制御する。

30

#### 【0055】

概して、所与のセクタの最初の読み取りに関して、ITI軽減回路280およびY-AVGブロック510は迂回され、Y-データがY-MEMブロック520に記憶される。そのセクタのその後のM回の再読み取りに関して、個々の読み取りからの新しいYサンプルは、Y-AVGブロック510によってフィードバック経路540を用いてY-MEMブロック520の内容と合併される(すなわち、平均される)。所与のセクタは、そのセクタが正常に読み取られるまで、Y-MEMブロック520の内容が繰返しのたびに更新されるようにして複数回読み取られる可能性がある。M+1回目の読み取り動作およびY-平均動作の完了の後、Y-MEMブロック520は、同じセクタのM+1回の読み取り動作からのY-データの平均を含む。Y-MEMブロック520の出力は、復号のために反復復号ブロック270にやはり適用される。

40

#### 【0056】

後処理されたY-データを用いて、事前に定義された回数(M+1回)の再読み取りの後でセクタが正常に読み取れない場合、後処理されたデータに対してITIの軽減を実行するために、ITIの軽減が有効化され得る。ITIの軽減を実行するための指示が、RETRYGATEとMETACMD[1]の組み合わされたシグナリングによって(また

50

は、RETRY GATEとITI\_GATEの組み合わされたシグナリングによって)開始される。このモードにおいては、Y-データが、マルチプレクサ502の制御の下で、フィードバック経路545を用いてY-MEMブロック520からITI軽減回路280に適用される。RETRY GATE信号は、Y-データが、媒体のセクタを読み取ることによって得られないが、前の読み取り動作からのYサンプルを含むY-MEMブロックを読み取ることによって得られることを示す。(例示的なITI\_SIODES制御語の値に基づいて片側または両側の)ITIキャンセル・データは、図2に関連して上で検討されたように、書き込みデータ経路260-W(図2)から得られる。加えて、Y-AVGブロック510は、そのとき、マルチプレクサ515を用いて迂回され、したがって、後処理され、次いで打ち消されたデータが、反復復号ブロック270による復号の前にY-MEMブロック520に記憶されることができる。

10

## 【0057】

さらなる変形形態において、平均の再読み取り動作の回数は、動的に決定され得る(または事前に定義された条件が発生すると終了され得る)。平均動作のたびに、平均されたデータが復号器にプッシュされるときに、データが復号され、復号の品質に関する1つまたは複数の測定基準が生成される。例えば、1つの例示的な品質の測定基準は、ビット誤りの数を含み得る。1つの例示的な実装において、平均手順は、ビット誤りの数が減少するまで継続され得る。ビット誤りの数が横ばいになる(すなわち、さらなる平均がもはや助けにならない可能性がある)場合、ITIの軽減が実行されることがある。同様に、ITIの軽減のその後の使用も、動的に決定され得る。ITIの軽減動作が実行されると、(潜在的に、ビット誤りに関して上で検討された同じ例を用いて)データおよび測定基準が計算され、コントローラに送信され、コントローラが、再生が実現されると直ちに終了する可能性がある。この場合、信号ITI\_SIODESが片側のキャンセルのみを実行するように調整され、それぞれの側が、再生が成功するまで、各ステップの後に分析された測定基準/データを用いて1つずつ実行される。

20

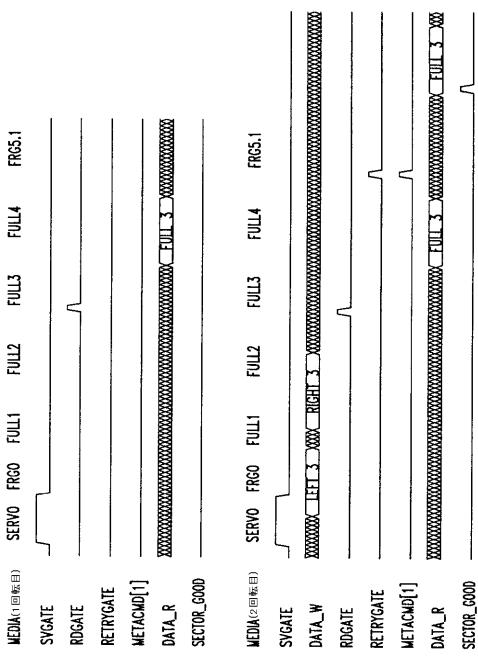

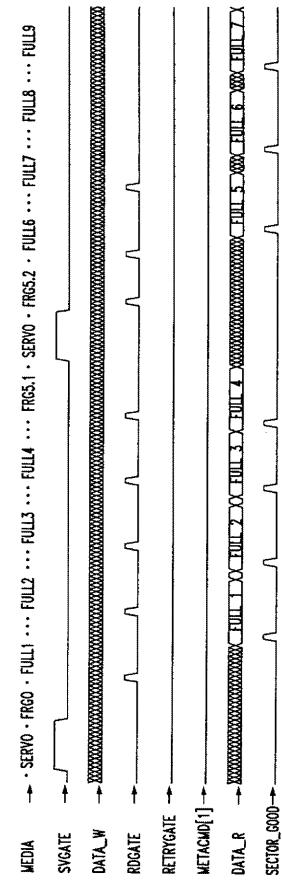

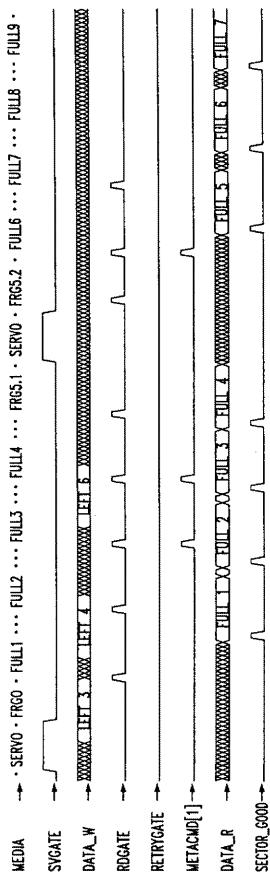

## 【0058】

図8Bは、図8Aの例示的な片側のITI軽減付きの後処理動作モード(ITI\_SIODES=0)に関して、いくつかのインターフェース信号を時間の関数として示す。例示的な実施形態において実行される後処理は、図8Bに示される2回の読み取りの平均などの、片側のITIの軽減を用いる平均読み取りを含む。当業者に明らかであろうように、平均は、任意の回数の読み取り動作に対して実行され得る。読み取りは、第1の読み取り動作または第2の読み取り動作がSECTOR\_GOOD信号を有する場合、停止され得ることが留意される。DATA\_R信号に関して、図8Bの第1の「FULL3」は、decode(avg(read1, read2))を含み、第2の「FULL3」は、decode(itii(left, avg(read1, read2)))を含むことがさらに留意される。セクタFULL3は、第1の読み取り中に読み取られ、次いで、反復復号器に渡され、復号されたセクタが、DATA\_Rバスに渡されることが留意される。セクタが誤りなしに正常に復号されなかったので、SECTOR\_GOOD信号は、アサートされない。第2の回転で、第2の読み取りの後、2つの読み取りのY-データが平均され、Y-平均されたデータが、反復復号ブロックに渡され、復号されたセクタが、DATA\_Rバスに渡される。セクタが誤りなしに正常に復号されなかったので、SECTOR\_GOOD信号は、アサートされない。次に、RETRY GATEおよびMETACMD[1]信号が、本発明によるITIのキャンセルを開始して、Y-平均されたデータを処理し、主トラックのセクタ3に隣接する左トラック(LEFT3)に関するキャンセル・データを用いてITIを軽減する。このキャンセル・データLEFT3は、DATA\_Wバスを用いて書き込みデータ経路で前もって与えられた。結果が、反復復号ブロックに渡され、反復復号ブロックが、復号されたセクタを生成する。復号されたセクタは、DATA\_Rバスに渡される。このセクタが誤りなしに正常に復号されたので、SECTOR\_GOOD信号が、アサートされる。

30

40

## 【0059】

50

図 8 C は、図 8 A の例示的な自動的な両側の I T I 軽減付きの後処理動作モード ( I T I \_ S I D E S = 1 ) について、いくつかのインターフェース信号を時間の関数として示す。例示的な実施形態において実行される後処理は、図 8 C に示される 2 回の読み取りの平均などの、自動的な両側の I T I の軽減を用いる平均読み取りを含む。当業者に明らかであろうように、平均は、任意の回数の読み取り動作に対して実行され得る。読み取りは、第 1 の読み取り動作または第 2 の読み取り動作が S E C T O R \_ G O O D 信号を有する場合、または第 1 の I T I \_ R E T R Y が S E C T O R \_ G O O D 信号を有するとき、停止され得ることが留意される。D A T A \_ R 信号に関して、図 8 C の第 1 の「F U L L 3」は、d e c o d e ( a v g ( r e a d 1 , r e a d 2 ) ) を含み、第 2 の「F U L L 3」は、d e c o d e ( i t i ( l e f t , r i g h t , a v g ( r e a d 1 , r e a d 2 ) ) ) を含むことがさらに留意される。セクタ F U L L 3 は、第 1 の読み取り中に読み取られ、次いで、反復復号器に渡されることが留意される。復号されたセクタが、D A T A \_ R バスに渡される。セクタが誤りなしに正常に復号されなかったので、S E C T O R \_ G O O D 信号は、アサートされない。第 2 の回転で、第 2 の読み取りの後、2 つの読み取りの Y - データが平均され、Y - 平均されたデータが、反復復号ブロックに渡される。復号されたセクタが、D A T A \_ R バスに渡される。セクタが誤りなしに正常に復号されなかったので、S E C T O R \_ G O O D 信号は、アサートされない。次に、( I T I \_ S i d e s = 1 として) R E T R Y G A T E および M E T A C M D [ 1 ] 信号が、自動的な両側の I T I 軽減動作モードを開始して、Y - 平均されたデータを処理し、主トラックのセクタ 3 に隣接する左トラック ( L E F T 3 ) と右トラック ( R I G H T 3 ) の両方にに関するキャンセル・データを用いて I T I を軽減する。このキャンセル・データ L E F T 3 および R I G H T 3 は、D A T A \_ W バスを用いて書き込みデータ経路で前もって与えられた。組み合わされた結果が、反復復号ブロックに渡され、反復復号ブロックが、復号されたセクタを生成する。復号されたセクタが、D A T A \_ R バスに渡される。このセクタが誤りなしに正常に復号されたので、S E C T O R \_ G O O D 信号が、アサートされる。

【 0 0 6 0 】

図 8 D は、I T I の軽減が片側ずつ実行される ( I T I \_ S I D E S = 0 ) 、図 8 A の例示的な両側の I T I 軽減付きの後処理動作モードについて、いくつかのインターフェース信号を時間の関数として示す。例示的な実施形態において実行される後処理は、図 8 D に示される 2 回の読み取りの平均などの、両側の I T I の軽減を ( 片側ずつ ) 用いる平均読み取りを含む。当業者に明らかであろうように、やはり、平均は、任意の回数の読み取り動作に対して実行され得る。読み取りは、いつでも S E C T O R \_ G O O D 信号が検出されるときに停止され得ることが留意される。D A T A \_ R 信号に関して、図 8 D の下半分の第 1 の「F U L L 3」は、d e c o d e ( r e a d 1 ) を含み、第 2 の F U L L 3 は、d e c o d e ( a v g ( r e a d 1 , r e a d 2 ) ) を含み、第 3 の「F U L L 3」は、d e c o d e ( i t i ( l e f t , a v g ( r e a d 1 , r e a d 2 ) ) ) を含み、第 4 の「F U L L 3」は、d e c o d e ( i t i ( l e f t , r i g h t , a v g ( r e a d 1 , r e a d 2 ) ) ) を含むことがさらに留意される。セクタ F U L L 3 は、第 1 の読み取り中に読み取られ、次いで、反復復号器に渡されることが留意される。復号されたセクタが、D A T A \_ R バスに渡される。セクタが誤りなしに正常に復号されなかったので、S E C T O R \_ G O O D 信号は、アサートされない。第 2 の回転で、第 2 の読み取りの後、2 つの読み取りの Y - データが平均され、Y - 平均されたデータが、反復復号ブロックに渡される。復号されたセクタが、D A T A \_ R バスに渡される。セクタが誤りなしに正常に復号されなかったので、S E C T O R \_ G O O D 信号は、アサートされない。次に、( I T I \_ S i d e s = 0 として) 第 1 の R E T R Y G A T E および M E T A C M D [ 1 ] 信号が、両側の I T I 軽減動作モード ( ただし片側ずつ ) を開始して、Y - 平均されたデータを処理し、主トラックのセクタ 3 に隣接する左トラック ( L E F T 3 ) に関するキャンセル・データを用いて I T I を軽減する。このキャンセル・データ L E F T 3 は、D A T A \_ W バスを用いて書き込みデータ経路で前もって与えられた。I T I のキャンセルの結果が、反復復号ブロックに渡され、反復復号ブロックが、復号されたセクタを生成

10

20

30

40

50

する。復号されたセクタが、DATA\_Rバスに渡される。このセクタが誤りなしに正常に復号されなかったので、SECTOR\_GOOD信号は、アサートされない。（ITI\_Sides = 0として）RETRYGATEおよびMETACMD[1]信号の第2の組が、主トラックのセクタ3に隣接する右トラック（RIGHT3）に関するキャンセル・データを用いてITIの軽減を開始する。このキャンセル・データRIGHT3は、DATA\_Wバスを用いて書き込みデータ経路で前もって与えられた。次に、組み合わされた結果が、反復復号ブロックに渡され、反復復号ブロックが、復号されたセクタを生成する。復号されたセクタが、DATA\_Rバスに渡される。このセクタが誤りなしに正常に復号されたので、SECTOR\_GOOD信号が、アサートされる。

【0061】

10

図9Aは、例示的な後処理付きのITI軽減動作モードのリード・チャネル250を示す。この構成において、後処理付きのITI軽減モードは、最初にITIの軽減を実行し、次にY-データの後処理を実行する。図9Aに示されるように、ITI軽減回路280は、マルチブレクサ505を用いて選択的にアクティブな信号経路に置かれ、Y-AVGブロック510は、マルチブレクサ515を用いてアクティブな信号に置かれる。したがって、後処理付きのITI軽減モードのためのアクティブな信号経路は、DFIRフィルタ285、ITI軽減回路280、Y-AVGブロック510、Y-MEMブロック520、および反復復号ブロック270を含む。Y-MEMアドレス・ブロック530は、知られている方法でY-MEMブロック520の選択を制御する。

【0062】

20

図9Aの実施形態において、ITIの軽減は、例えば、例示的なモード制御信号またはレジスタ、ITI\_SIDESと、（ITIの軽減をバイパスする、すなわち「まったく実行しない」ための）METACMD[1]とによって示されるように、所与の読み取り動作に対して、どちらかの隣接するトラックもしくは両方の隣接するトラックに対して実行されるか、またはまったく実行されない。ITIキャンセル・データは、図2に関連して上で検討されたように、書き込みデータ経路260-W（図2）から得られる。図9Aに示されるように、サンプルの第1の組に関して、ITI軽減回路280は、マルチブレクサ505によってアクティブな信号経路に置かれ、Y-AVGブロック510は、マルチブレクサ515によって迂回され、ITIを補正されたデータが、Y-MEMブロック520および反復復号ブロック270に送信される。

30

【0063】

加えて、すべての残りのITIを補正されたサンプルが、Y-AVGブロック510によってフィードバック経路540を用いてY-MEMブロック520の内容と合併される（すなわち、平均される）。所与のセクタは、そのセクタが正常に読み取られるまで、Y-MEMブロック520の内容が繰返しのたびに更新されるようにして複数回読み取られる可能性がある。Y-MEMブロック520の出力は、復号のために反復復号ブロック270にやはり適用される。

【0064】

40

図9Bは、図9Aの例示的な後処理付きのITI軽減動作モードに関して、いくつかのインターフェース信号を時間の関数として示す。例示的な実施形態において実行される後処理は、ITIを軽減されたデータの平均を含む。当業者に明らかであろうように、やはり、平均は、任意の回数の読み取り動作に対して実行され得る。概して、このプロセスは、媒体を2回読み取ることを含む。媒体を読み取るたびに、ITIが軽減され、その結果が、前に計算された／記憶された結果と平均される。例えば、2回の読み取り動作に対する平均について、プロセスは、媒体から目標のセクタを読み取ることと、読み取られたデータに対してITIの軽減を実行すること（例えば、左の隣接するトラックからのITIが軽減される）と、結果を記憶すること（すなわち、1組のサンプルの平均を記憶する）と、媒体295から同じ目標のセクタを再び読み取ることと、読み取られたデータに対してITIの軽減を実行すること（例えば、右の隣接するトラックからのITIが軽減される）と、第2のITIを軽減されたデータを記憶されたデータと平均すること（ITIが

50

打ち消されたデータの平均を生じる)とを含む。これは、`avg(iti(first_read),iti(second_read)) = (iti(read1) + iti(read2)) / 2.0`と表され得る。2回の読み取り中に、同じ隣接するトラックからのITIが代替的な動作モードで軽減された可能性があることが留意される。

#### 【0065】

図9Aおよび9Bの例示的な後処理付きのITI軽減動作モードは片側のITIの軽減に関して示されているが、本明細書において検討されるように、および当業者に明らかであろうように、N個の側面のITIの軽減が可能であることが留意される。

#### 【0066】

図10Aは、例示的な両側のITI動作モードのリード・チャネル250を示す。ITIキャンセル・データは、図2に関連して上で検討されたように、書き込みデータ経路260-W(図2)から得られる。最初に、片側のITIの軽減が、図7Aと同様にして実行される(すなわち、1つの隣接するトラックに対するITIの軽減)。図10Aに示されるように、ITI軽減回路280は、マルチブレクサ505によってアクティブな信号経路に置かれ、Y-AVGブロック510は、マルチブレクサ515によって迂回される。したがって、リアルタイムITIモードのためのアクティブな信号経路は、DFIRフィルタ285、ITI軽減回路280、Y-MEMブロック520、および反復復号ブロック270を含む。概して、ITI軽減回路280のITIを補正された出力は、Y-MEMブロック520に記憶され、次いで、復号のために反復復号ブロック270に適用される。

10

20

#### 【0067】

第2の隣接するトラックに対するITIの軽減を実行するために、Y-MEMブロック520からのY-データが、`retrygate`信号の制御の下でかまたは自動的にかのいずれかで、フィードバック経路545と、マルチブレクサ502による適切な選択とを用いてITI軽減ブロック280に適用される。このようにして、データは、(側面の数に関わらず)媒体の1回の読み取りがデータの1つのセクタを生成するように、復号器270に一度だけ渡される。したがって、`retrygate`信号によって制御されるとき、2つのイベント(1回の媒体の読み取りおよび1回の再試行)が、データの2つのセクタを生成するか、または(自動モードにおいて)1つのイベント(媒体の読み取り)が、データの1つのセクタを生成する。ITIキャンセル・データが、他方の隣接するトラックに関して、図2に関連して上で検討されたように書き込みデータ経路260-W(図2)から得られる。ITI軽減回路280は、マルチブレクサ505によってアクティブな信号経路に残り、Y-AVGブロック510は、マルチブレクサ515によってやはり迂回される。したがって、リアルタイムITIモードのためのアクティブな信号経路は、DFIRフィルタ285、ITI軽減回路280、Y-MEMブロック520、および反復復号ブロック270を含む。概して、ITI軽減回路280のITIを補正された出力は、Y-MEMブロック520に記憶され、次いで、復号のために反復復号ブロック270に適用される。このようにして、両側のITI動作モードは、磁気媒体の単一の読み取りのみによって両方の隣接するトラックに関するITIの軽減を可能にする。

30

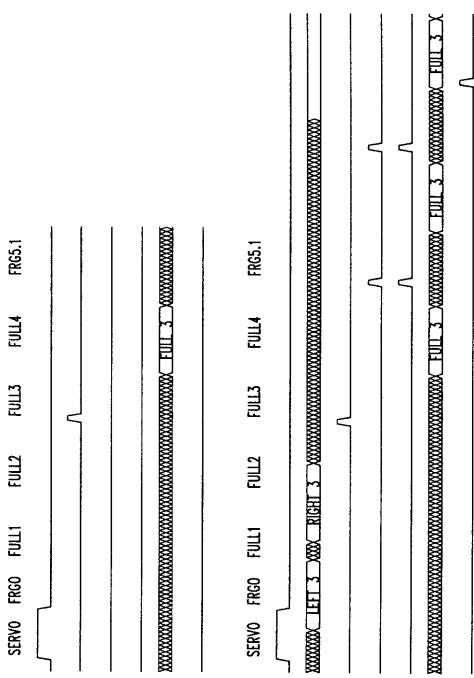

#### 【0068】

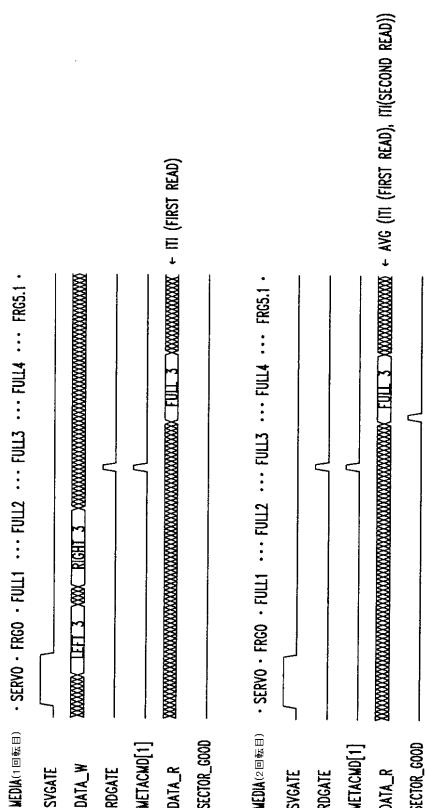

図10Bは、2つの片側のITIのキャンセルが続けてトリガされる、図10Aの例示的な両側のITI動作モードに関して、いくつかのインターフェース信号を時間の関数として示す。例示的な両側のITI動作モードは、ITIの軽減が2つの隣接するトラックに対して実行されることを可能にする(`ITI_SIDES = 0`、`RETRY`動作のみ)。図10Bにおいて、例示的な両側のITIモードに関して、ITIの軽減は、片側ずつ実行される。したがって、`ITI_SIDES = 0`である。例示的なDATA\_W信号は、ITIの軽減がセクタ4に対して左側のトラックおよび右側のトラックを用いて実行されることを示す。METACMD[1]信号は、(`RDGATE`または`RETRYGATE`に合わせられた)再試行と一緒にITIの軽減をトリガする。図10BはITIの軽減を用いた読み取り動作に対応するので、METACMD[1]は、セクタ4に関するRD

40

50

G A T E 信号およびR E T R Y 信号に合わせられるとときにアクティブである。D A T A \_ R 上の第1のF U L L 4 は「不良」であり、したがって、第2の側面の軽減が試みられ、S E C T O R \_ G O O D 信号に至ることが留意される。図10Bの第1の「F U L L 4」は、d e c o d e ( i t i ( l e f t , r e a d 1 ) ) を含み、第2の「F U L L 4」は、d e c o d e ( i t i ( l e f t , r i g h t , r e a d 1 ) ) [ I T I \_ S I D E S = 0 ] を含むことが留意される。

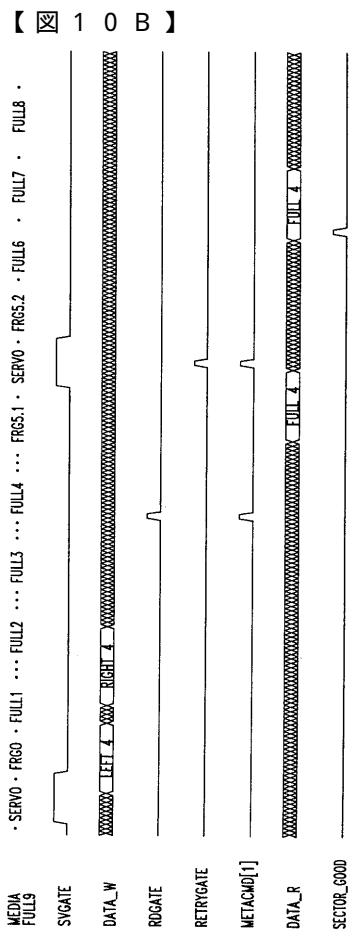

#### 【0069】

図10Cは、図10Aの例示的な自動的な両側のI T I動作モードに関して、いくつかのインターフェース信号を時間の関数として示す。例示的な自動的な両側のI T I動作モードは、I T Iの軽減が2つの隣接するトラックに対して実行されることを可能にする。図10Cにおいて、例示的な自動的な両側のI T Iモードに関して、I T Iの軽減は、一度に2つの隣接するトラックに対して実行される。したがって、I T I \_ S I D E S = 1 、R E T R Y モードのみである。例示的なD A T A \_ W 信号は、I T Iの軽減がセクタ4に対して左側のトラックおよび右側のトラックを用いて実行されることを示す。M E T A C M D [ 1 ] 信号は、( R D G A T E に合わせられた) 読み取りと一緒にI T Iの軽減をトリガする。図10CはI T Iの軽減を用いた読み取り動作に対応するので、M E T A C M D [ 1 ] は、セクタ4に関するR D G A T E 信号に合わせられるとときにアクティブである。図10Cの「F U L L 4」は、d e c o d e ( i t i ( l e f t , r i g h t , r e a d 1 ) ) [ I T I \_ S I D E S = 1 ] を含むことが留意される。

#### 【0070】

##### 軽減のアーキテクチャおよび実装

D F I R フィルタ285(例えば、図2～4)の出力の信号は、符号間干渉とトラック間干渉の両方を含む。I T Iは、隣接するトラックに記憶されたデータに関する硬判定を用いて本発明にしたがって軽減される。片側のI T Iの軽減に関しては、どちらかの隣接するトラックに関するデータが使用され、一方、両側のI T Iの軽減に関しては、両方の隣接するトラックに関するデータが使用される。

#### 【0071】

隣接するトラック110-1および110-3(図1)に関するデータは、前の読み取り動作で隣接するトラック110-1および110-3を読み取ることによって取得され、例えば、D R A M 220(図2)に記憶された。隣接するトラックのデータは、D F I R 285の出力の信号に含まれるI T Iを推定し、軽減するために使用される。

#### 【0072】

次いで、任意的に、I T Iを軽減された信号が、トラックNのデータを再生するために、雑音予測最尤( n o i s e - p r e d i c t i v e m a x i m u m l i k e l i h o o d ) ( N P M L ) 検出器(図示せず)および復号器270を通される。I T Iの軽減を容易にするために、S M R ハードディスクドライブ( H D D )は、隣接するトラックのセクタがそれらのトラック内の位置に関して揃えられている揃えられたセクタ・データ・フォーマットを使用することが期待される。通常の非シングルドH D D( n o n - s h i n g l e d H D D )は、概して、隣接するトラックのセクタが通常は揃えられていない、揃えられていないセクタ・データ・フォーマットを使用する。揃えられたセクタ・データ・フォーマットの利点は、トラックNのセクタに対するI T Iを軽減するために、トラックN-1およびN+1の1つの隣接するセクタに関するデータだけが考慮される必要があることである。揃えられていないセクタ・データ・フォーマットの場合、トラックN-1およびN+1のそれぞれの2つの隣接するセクタに関するデータが考慮される必要がある。

#### 【0073】

揃えられたセクタ・データ・フォーマットを用いても、隣接するトラックのセクタは、書き込みプロセスが理想的でないために数ビット期間ずらされる可能性がある。また、異なるトラックにデータを書き込む間のディスクの回転数( f r e q u e n c y )の変動が、隣接するトラックに書き込まれたデータ間のわずかな回転数のずれを引き起こす可能性

10

20

30

40

50

がある。この回転数のずれが、トラックNから読み取られる信号内のN-1およびN+1のITIの応答の位相ドリフトを引き起こす可能性がある。良好なビット誤り率(BER)性能のために、ITI軽減アルゴリズムは、理想的でない書き込みプロセスが原因の隣接するセクタ間の位相差と、隣接するトラック間の回転数のずれが原因のITIの応答の位相ドリフトの両方を考慮すべきである。

#### 【0074】

SMRハードディスクドライブは、オフラインの誤り回復のためにITIの軽減を使用する可能性がある。ITIの軽減を用いないトラックNの目標のセクタの復号が通常の読み取り動作中に失敗するときにはいつでも、HDDは、隣接するトラックのセクタを読み取り(または再試行動作中に、トラックNの失敗するセクタを再読み取りし)、ITIの軽減を用いてこのセクタの復号を再開する。したがって、本明細書に記載のITIの軽減のために使用される隣接するトラックに関する硬判定を再生するために、片側のITIの軽減は余分な1回転を引き起こし、両側のITIの軽減は余分な2回転を引き起こす。

10

#### 【0075】

サイドトラックN-1およびN+1に関する硬判定は、例えば、DRAM220(図2)に記憶され得る。オフラインの単一のセクタのITIの軽減に関して、トラックN-1およびN+1に関する1つのセクタだけ(合計で、片側のITIの軽減のために1セクタ、および両側のITIの軽減のために2セクタ)が、DRAM220に記憶される必要がある。通常のHDDと比較して、HDDコントローラ210とリード・チャネル250の間の追加的なデータ経路が、ITIの軽減のためのトラックN-1およびN+1に対応するデータを転送するために必要とされる。開示された実施形態においては、書き込みデータ経路が、ITIの軽減のためのトラックN-1およびN+1に対応するキャンセル・データを転送するために使用される。

20

#### 【0076】

トラックのランダムな読み取りは隣接するトラックのデータを読み取るために追加的な回転を必要とするので、通常の読み取り動作中のオンザフライ(OTF)のTTIの軽減は、トラックの連続的な読み取りを必要とする。連続的な読み取りを用いる片側のOTFのITIの軽減においては、トラック1、2、3などが、ITIの軽減のために順番に読み取られ、ITIは、前の読み取られたトラックからの記憶された硬判定を用いてトラックNから軽減される。片側のOTFのITIの軽減に関して、トラックは、逆順で順番に読み取られ、ITIは、前の読み取られたトラックからの記憶された硬判定を用いてトラックNから軽減される。したがって、片側のOTFのITIの軽減は、トラック全体の分の硬判定がDRAM220に記憶されることを必要とする。

30

#### 【0077】

OTFのITIの軽減は、リード・チャネル250からコントローラ210への2つの同時のデータストリーム、すなわち、リード・チャネル250からコントローラ210への復号されたセクタの転送と、コントローラ210からリード・チャネル250への隣接するトラックのセクタに関するデータの転送とがサポートされる必要があるので、HDDのDRAMメモリの追加的な帯域幅も必要とする。

40

#### 【0078】

当業者に明らかであろうように、3つの側面のITIの軽減などの追加的なトラックを用いるITIの軽減が本発明にしたがって実行され得ることが留意される。

#### 【0079】

既に示されたように、本明細書に記載の磁気記録システムおよびリード・チャネルの構成は、従来の構成に比していくつかの利点をもたらす。再度、本発明の上述の実施形態は、単に例示的であるように意図されていることが強調されるべきである。概して、例示的な磁気記録システムは、当業者に明らかであろうように、書き込みデータ経路を用いてITI軽減データを提供するITI軽減方式を組み込むように修正され得る。加えて、ITIの軽減のための開示された技術は、独立したディスクの冗長アレイ(RAID)システムなどの仮想ストレージ・システム/ストレージ仮想化システムのような任意の磁気記録

50

システムで使用され得る。

【0080】

本明細書に記載のインターフェースおよびデータフロー・メカニズムは、当業者に明らかであろうように、修正なしに追加的な動作モードおよび構成をサポートする。例えば、開示されたITI軽減技術は、示されたように干渉する複数のサイドトラックを有する通常のドライブ( N 個の側面の軽減のための潜在的な使用)と、揃えられたセクタまたは揃えられていないセクタを有するシングルド・ドライブ(shingled drive)または通常のドライブ(知られているデータの潜在的な使用)と、意図しない詰め込み(squeezing)を有する通常のドライブ(したがって、そのドライブは、シングルド・ドライブではないにもかかわらずITIの再生を必要とする)とで実装され得る。概して、揃えられていないセクタは、隣接するセクタのデータが揃えられていないときに発生する。例えば、図1を参照すると、真ん中のトラック110-2は隣接するトラック110-1、110-3のうちの1つまたは複数と揃っていなかったので、トラックは、揃えられていないと言われる。揃えられていないトラックがある場合、本発明は、隣接するトラックの揃えられた部分が属するセクタに無関係に、所与のトラックのセクタに揃えられている隣接するトラックの部分を用いる、所与のトラックのセクタのITIの軽減を可能にする。

10

【0081】

本発明の例示的な実施形態がデジタル論理ブロックに関して説明されたが、当業者に明らかであろうように、さまざまな機能は、ソフトウェアプログラムの、回路要素もしくは状態機械によるハードウェアの、またはソフトウェアとハードウェアの両方の組み合わせの処理ステップとしてデジタル領域で実装され得る。そのようなソフトウェアは、例えば、デジタル信号プロセッサ、特定用途向け集積回路、マイクロコントローラ、または多目的コンピュータで使用され得る。そのようなハードウェアおよびソフトウェアは、集積回路内に実装された回路内に具現化され得る。

20

【0082】

本発明の集積回路の実装においては、通常、複数の集積回路ダイが、ウェハの表面上の繰返しパターンで形成される。それぞれのそのようなダイは、本明細書に記載のデバイスを含むことができ、その他の構造または回路を含み得る。ダイは、ウェハから切断またはダイシングされ、次いで、集積回路としてパッケージングされる。当業者は、パッケージングされた集積回路を製造するためにウェハをどのようにダイシングすべきか、およびダイをどのようにパッケージングすべきかを知っているであろう。そのように製造された集積回路は、本発明の一部とみなされる。

30

【0083】

したがって、本発明の機能は、方法、およびそれらの方法を実施するための装置の形態で具現化され得る。本発明の1つまたは複数の態様は、例えば、ストレージ媒体に記憶され、機械にロードされるおよび/もしくは機械によって実行されるのか、または何らかの伝送媒体を介して送信されるのかに関わらずプログラムコードの形態で具現化することができ、そのプログラムコードがコンピュータなどの機械にロードされ、機械によって実行されるとき、当該機械は本発明を実施するための装置になる。汎用プロセッサで実装されるとき、プログラムコードのセグメントは、特定の論理回路と同様に動作するデバイスを提供するためにプロセッサと連携する。本発明は、集積回路、デジタル信号プロセッサ、マイクロプロセッサ、およびマイクロコントローラのうちの1つまたは複数で実装されることもできる。

40

【0084】

本明細書において示され、説明された実施形態および変更形態は、本発明の原理を例示するに過ぎず、さまざまな修正が、本発明の範囲および精神を逸脱することなく当業者によって実施され得ることを理解されたい。

【図1】

【図2】

【図3】

【図4】

【図 7 A】

【図 7 B】

【図 8 A】

【図 8 B】

【 図 8 C 】

【 図 8 D 】

【 図 9 A 】

【図9B】

---

フロントページの続き

(72)発明者 カート ジェー・ウォレル

アメリカ合衆国 80513 コロラド, パーソード, グレン ドライヴ 5200

(72)発明者 エリック エフ・ハラッチ

アメリカ合衆国 18017 ペンシルヴァニア, ベスレヘム, バーバリー ストリート 510

5

(72)発明者 チャンユー スー

アメリカ合衆国 94539 カリフォルニア, フレモント, デニス ストリート 41335

(72)発明者 ジェファーソン イー・シングルトン

アメリカ合衆国 80021 コロラド, ウエストミンスター, ウエスト ワンハンドレッドセヴ

ンス ドライヴ 9707

(72)発明者 クリパ ヴェンカタチャラム

アメリカ合衆国 01742 マサチューセッツ, コンコード, ピー・ボディ コート 20

(72)発明者 ディヴィッド ジー・スプリングバーグ

アメリカ合衆国 80525 コロラド, フォート コリンズ, ダートマウス トレイル 717

F ターム(参考) 5D031 AA04 DD05 HH08 HH11

5D044 BC01 CC05 FG05

【外國語明細書】

## HARDWARE-BASED METHODS AND APPARATUS FOR INTER-TRACK INTERFERENCE MITIGATION IN MAGNETIC RECORDING SYSTEMS

### Field of the Invention

The present invention relates generally to magnetic recording systems and, more particularly, to improved techniques for mitigating the effect of inter-track interference in such magnetic recording systems.

### Background of the Invention

In magnetic recording (MR) systems, data is typically recorded on concentric circular tracks on a magnetic media as a sequence of small magnetic domains. Data written onto the tracks that neighbor a given track will affect the signal read back from the media of the given track. The signal induced during the read of the given track as a result of one or more neighboring tracks is referred to as crosstalk or inter-track interference (ITI). The mitigation of the ITI noise caused by the neighboring tracks in the read back signal of the given track typically relies on information about the data pattern from the neighboring tracks supplied to an ITI mitigation circuit or process.

ITI is of particular concern in hard disk drives (HDD) where concentric or spiral tracks of data are recorded on the media in close proximity to one another, relative to the size of the head. The capacity of the disk drive is increased by placing the tracks closer together. ITI is known to increase with technology scaling, however, and becomes a significant source of noise as track separation distances become smaller. As the tracks are placed closer together, the neighboring tracks are more likely to influence the signal of the given track when it is read back from the media, reducing the overall signal-to-noise ratio. ITI thus limits the number of tracks that can reliably be stored in a given area of a magnetic medium. ITI is of even greater concern in Shingled Magnetic Recording (SMR) systems, where the tracks are placed close enough that the tracks touch one another in some cases, and in other cases can even overlap one another when written with data.

A number of techniques have been proposed for mitigating the effect of ITI in magnetic recording systems. In existing SMR implementations, for example, the mitigation process is typically performed by software in the hard disk controller (HDC). It has been found, however, that when ITI mitigation is enabled, the HDC cannot process data fast enough to recover more than a few sectors (and typically only one sector) for every 3-6

revolutions of the disk. Each revolution of the disk, however, may contain, for example, 500 or more sectors (depending on, e.g., the particular disk drive that is employed, the size of the platter and the radial position of each track on the disk).

A need therefore exists for improved techniques for mitigating the effect of ITI. A further need exists for hardware-based techniques for mitigating the effect of ITI. Yet another need exists for hardware-based techniques for mitigating the effect of ITI that do not require a hard disk controller to perform the ITI computations.

### Summary of the Invention

Generally, hardware-based methods and apparatus are provided for inter-track interference mitigation in magnetic recording systems. According to one aspect of the invention, inter-track interference (ITI) is mitigated in a magnetic recording system by obtaining ITI cancellation data; and providing the ITI cancellation data during a read operation to an ITI mitigation circuit using a write data path in the magnetic recording system. The write data path can optionally operate substantially simultaneously with the read data path performing the read operation.

The ITI cancellation data can be obtained, for example, from a memory that is external to the write data path. The ITI cancellation data comprises, for example, user data and/or media data. In one embodiment, the write data path converts user data to media data for the ITI mitigation.

The ITI mitigation can be selectively enabled for a given sector of data. In addition, the ITI mitigation can be selectively performed for a given read operation for one or more neighboring tracks. The ITI mitigation can optionally be performed in combination with a post-processing procedure to post-process ITI corrected data and/or perform ITI mitigation on post-processed data.

A more complete understanding of the present invention, as well as further features and advantages of the present invention, will be obtained by reference to the following detailed description and drawings.

### Brief Description of the Drawings

FIG. 1 illustrates a portion of a number of exemplary tracks on a magnetic medium of a Shingled Magnetic Recording (SMR) system;

FIG. 2 is a schematic block diagram of a magnetic recording system incorporating ITI mitigation in accordance with the present invention

FIGS. 3 and 4 are schematic block diagrams of alternative implementations of the read channel illustrated as part of FIG. 2; and

FIGS. 5-10 illustrate the read channel of FIGS. 2-4 in various configurations, to implement a number of exemplary modes of operation, as well as corresponding interface signals for each mode.

### Detailed Description

The present invention provides hardware-based methods and apparatus for inter-track interference mitigation in magnetic recording systems. ITI mitigation combines the data read from the media with additional data (hereafter referred to as "cancellation data") in order to improve the likelihood of correct data recovery. The cancellation data must be supplied to the ITI mitigation circuit or process. The cancellation data may be read from the disk media, or obtained from another source, as would be apparent to a person of ordinary skill in the art.

According to one aspect of the invention, the disclosed hardware-based techniques for inter-track interference mitigation obtain the cancellation data from the HDC but do not require the processing unit in the HDC to perform the ITI computations. According to another aspect of the invention, a system is disclosed for storing, supplying and manipulating the cancellation data for presentation to the read data path for subsequent digital signal processing (DSP), thereby improving the chances for correctly recovering the written data.

Read channels are typically slave devices that are in either a read mode or a write mode at a given time. In each mode, data typically flows only in one direction. For example data flows from a hard disk controller (HDC) to the read channel (RC) to the media in a write mode and from the media to the RC and then the HDC in a read mode. The present invention recognizes that at least a portion of the write data path (WDP) is normally idle when the read channel is executing a read operation in a read mode.

Thus, according to a further aspect of the invention, the write data path (which is normally idle or dormant during read operations) is employed to deliver the cancellation data to an ITI mitigation circuit in the read data path. Thus, the write data path is used during

read operations to transmit cancellation data into the read channel. The cancellation data is provided to the ITI mitigation circuit substantially simultaneously with the media data that is obtained by the read data path from the magnetic media. Among other benefits, the write data path typically includes functionality to encode, scramble and buffer data, and calculate error correction data (which is subsequently written to the media), and this functionality can be leveraged in accordance with the present invention for ITI mitigation. In this manner, the disclosed ITI mitigation system makes use of otherwise idle hardware and existing buffering capabilities in the write path to enable ITI mitigation, at very minimal design effort, area expense and power costs.

FIG. 1 illustrates a portion of a number of exemplary tracks 110-1 through 110-3 on a magnetic medium 100 of an exemplary Shingled Magnetic Recording (SMR) system. The tracks 110-1 through 110-3 are typically written in increasing numerical order (such as illustrated from bottom to top in FIG. 1). A number of examples described herein make reference to left and right tracks, which are references to the tracks that are adjacent to the left and right, respectively, to a given track. As shown in FIG. 1, the exemplary tracks 110-1, 110-2 and 110-3 are written with a first overlap region 120-1 between tracks 110-1 and 110-2, and with a second overlap region 120-2 between tracks 110-2 and 110-3. The signal read from track 110-2, for example, is heavily influenced by the signal read from track 110-3 since track 110-3 is written overlapping the previously written track 110-2. The signal read from track 110-2 is also influenced by the data previously written on track 110-1 since the left edge of track 110-2 is written over the right edge of track 110-1. The read signal for track 110-2 depends heavily on the position and size of the read head that is positioned over the tracks to read the recorded data. If the read head is positioned closer to one edge of track 110-2, such as edge 130, than the edge of the other track track 110-3, such as edge 140, for example, then the corresponding track 110-1 that is adjacent to edge 130 will affect the read signal of track 110-2 more than the track 110-3 that is adjacent to edge 140. If the read head is the same size or larger than the non-overlapped region of 110-2, both tracks 110-1 and 110-3 are likely to induce ITI noise.

It is noted that one adjacent track can have a more significant ITI effect than the other adjacent track. For example, the position of the read head over the center track 110-2 relative to the position of the adjacent tracks may influence the amount of ITI contributed by each adjacent track to the center track. Thus, ITI mitigation can optionally be performed

first for the adjacent track having the more significant ITI contribution. As discussed further below, the illustrative embodiments described herein do not place any restrictions on using one side track or the other side track, or the order of side tracks if two-sided ITI mitigation is being performed. The disclosed ITI mitigation mechanisms allow for the most important cancellation (if known a priori) to be performed first so as to allow the ITI mitigation process to terminate once successful recovery is achieved.

FIG. 2 is a schematic block diagram of portions of a magnetic recording system 200 incorporating ITI mitigation in accordance with the present invention. FIG. 2 illustrates the configuration of the magnetic recording system 200 for ITI mitigation during a read operation. As shown in FIG. 2, the magnetic recording system 200 comprises a hard disk controller (HDC) 210 and a read channel (RC) 250. The read channel 250 comprises a read data path (RDP) 260-R and a write data path (WDP) 260-W. As previously indicated, the write data path 260-W is employed by the present invention to deliver the cancellation data for one or more adjacent tracks, such as tracks N-1 and N+1, that are adjacent to a given track N to an ITI mitigation circuit 280 in the read data path 260-R. The cancellation data is provided to the ITI mitigation circuit 280 substantially simultaneously with the media data that is obtained by the read data path 260-R from the magnetic media.

Typically, the RDP-Analog block 290 comprises a number of analog components, such as an ac-coupling, attenuator (ACC); a variable gain amplifier (VGA) with adaptive control, baseline compensation, magneto-resist asymmetric (MRA) compensation, thermal asperity (TA) detection; continuous time filter (CTF) with adaptive control for digital signal processing; and an analog to digital converter (ADC). Generally, thermal asperity occurs when the read head encounters a portion of magnetic material that is raised above the plane of the disk platter on which the magnetic material resides, causing the signal amplitude to substantially increase. The thermal asperity detection block identifies such magnetic material portions and attempts to compensate for them, in a known manner.

The digitized signal is then filtered by a Digital Finite Impulse Response (DFIR) filter 285, which equalizes the signal. The DFIR 285 provides a filtered output to the ITI mitigation circuit 280. The ITI-cancelled signals generated by the ITI mitigation circuit 280 are then provided to the iterative decoding block 270 that includes a Viterbi detector and a decoder, such as a low-density parity check decoder. The read data path 260-R provides decoded data for a given track N to the hard disk controller 210.

As previously indicated, the write data path 260-W typically includes functionality to encode the data that is to be written onto the media, such that error correction can be performed on a subsequent read of the data. In addition, the write data path 260-W also scrambles and buffers the data, and this functionality can be leveraged in accordance with the present invention for ITI mitigation.

For a more detailed discussion of an exemplary ITI mitigation circuit 280, see, for example, United States Patent Application Serial No. 13/186,174, filed July 19, 2011, entitled "Systems and Methods for Inter-Track Interference Compensation," (Attorney Docket No. AGERE-022110), incorporated by reference herein. A number of exemplary techniques for ITI mitigation in accordance with the present invention are discussed further below in conjunction with FIGS. 5-10. For example, various implementations of the present invention support direct reads of the magnetic media 295, with or without ITI mitigation. In addition, another implementation of the present invention supports on-the-fly (OTF) or real-time reads with at least one-sided ITI mitigation. Yet another implementation of the present invention supports offline reads with up to two-sided ITI mitigation.

The present invention also supports ITI mitigation of post-processed DFIR data, such as Y-Averaged data and/or post-processing of ITI mitigated DFIR data, such as Y-Averaging of ITI mitigated data. For example, ITI mitigation of Y-Averaged data comprises obtaining a Y-Average over multiple reads and then performing ITI mitigation and decoding using the Y-averaged samples. Similarly, Y-Averaging of ITI mitigated data comprises reading a sector, performing ITI mitigation and optionally decoding using the current read sector, and obtaining a Y-Average using the ITI-mitigated samples from multiple reads, followed by a read of a next sector, and so forth.

As shown in FIG. 2, the hard disk controller 210 comprises exemplary long latency interfaces (LLI) 240-R, 240-W for communicating with corresponding long latency interfaces (LLI) 255-R, 255-W in the read data path (RDP) 260-R and write data path (WDP) 260-W, respectively.

The hard disk controller 210 also includes a double data rate (DDR) PHY interface 230 for communicating with external DDR devices, such as a dynamic random access memory (DRAM) 220. The cancellation data can be stored, for example, in the external DRAM 220 or another non-volatile memory, such as a static random access memory (SRAM) or flash memory. The exemplary DRAM 220 can store cancellation data for one

or more tracks of the magnetic media 100 (FIG. 1) or magnetic media 295 (FIG. 2). For example, the amount of cancellation data that is stored can be a function of the track spacing for the track currently being read. The exemplary DRAM 220 may also store cancellation data for just one or multiple sectors (for example, the sectors that could not be successfully recovered during a prior read operation) to reduce the amount of data that needs to be stored in DRAM.

The cancellation data, also referred to as side-track data, can have a number of exemplary formats, as would be apparent to a person of ordinary skill in the art. Generally, the exemplary cancellation data can comprise coded media data that corresponds to the written media waveform, or un-encoded user data which would normally be supplied by the hard disk controller 210. Generally, the exemplary media data format comprises encoded data including Low Density Parity Check (LDPC) overhead, run-length limited (RLL) encoding overhead and error detection code (EDC) overhead. FIGS. 3 and 4 present alternative implementations 250' and 250", respectively, of the read channel 250 that incorporate different embodiments for processing the media data. In FIGS. 3 and 4, the run-length limited and error detection code encoder and decoder functions and the scrambler functions are labeled as "ESR" (i.e., Error Detection Code, Scrambler and RLL).

It is further noted that in the exemplary embodiment, the ITI mitigation circuit 280 processes equalized analog-to-digital converter (ADC) samples, referred to as "Y-Data." In an alternative embodiment, the ITI mitigation circuit 280 may process raw (unequalized) ADC samples, referred to herein as "ADC data." The Y-Data or ADC data, for example, may be 6 bits of data for each media bit that was written on the media. The ADC-data or Y-Data is read from the magnetic media 295 and is available at the output of the ADC or DFIR equalizer, respectively. The iterative decoding block 270 converts each Y-Data sample to a single bit of detected media data (and after removal of parity and other overhead bits) to a single bit of detected user data. The iterative decoding block 270 may be embodied, for example, using a well-known LDPC decoder.

In an exemplary embodiment, the write data path 260-W represents the ITI cancellation data in user or media data format. In an alternative embodiment, the write data path 260-W represents the ITI cancellation data in ADC or Y-data format, in which case multiple bits per media bit are stored in the DRAM and supplied from the HDC to the write data path 260-W. The ITI mitigation circuit 280 mitigates ITI based on media data, ADC data

or Y-data depending on what the write data path 260-W supplies. If the HDC provides ITI cancellation data to the read channel in user data format, the write data path converts the user data to media data as described in FIGS. 3 and 4.

It is noted that if the DDR PHY 230 does not have sufficient bandwidth without added expense and system design modifications to support the Y-Data or ADC data format (for example, 6 bits per stored media bit) format, the single bit format, that is user or media data format implementation of the present invention can still be supported. With the single bit format, only one bit unit of bandwidth needs to be added. It is further noted that read data is written to memory in existing non-ITI drives. Thus, only one bandwidth bit unit is added for reading the data from the DDR and sending the cancellation data to the read channel for use in the disclosed ITI cancellation procedure. By using the single bit format, the required storage amount for ITI cancellation data in the DRAM is greatly reduced as well.

In one exemplary embodiment, the magnetic recording system 200 includes an ITI control signal or register, referred to, for example, as METACMD[1] or ITI\_GATE, to indicate whether ITI cancellation data should be used for a given read operation. If the ITI control signal indicates that the ITI cancellation data should not be used for a given read operation, then the ITI mitigation circuit 280 can optionally be bypassed (as there is no data to be used for ITI mitigation), as shown further below in FIGS. 3-4. In addition, the exemplary magnetic recording system 200 includes a mode control signal or register, referred to, for example, as ITI\_SIDES, to indicate whether ITI cancellation is to be performed for only one adjacent track (for example, ITI\_SIDES is set to ITI\_SIDES=0) or two adjacent tracks (for example, ITI\_SIDES is set to ITI\_SIDES=1) in the exemplary embodiment. In general, any number, N, of tracks can have an ITI influence on the center track. In addition, N-sided ITI mitigation can be performed in accordance with the present invention in N steps, as would be apparent to a person of ordinary skill in the art.

FIG. 3 is a schematic block diagram of an alternative implementation 250' of the read channel 250 of FIG. 2, where the write data path generates the media data for presentation to the ITI mitigation circuit 280. As shown in FIG. 3, the exemplary read channel 250' comprises a read data path 360-R and a write data path 360-W, in a similar manner to FIG. 2. The read data path 360-R may be implemented in a similar manner to the read data path 260-R of FIG. 2. As previously indicated, the write data path 360-W is employed by the present invention to deliver the cancellation data to an ITI mitigation circuit

280 in the read data path 360-R. The cancellation data is provided to the ITI mitigation circuit 280 substantially simultaneously with the media data that is obtained by the read data path 360-R from the magnetic media. In another exemplary embodiment, the cancellation data is provided to the ITI mitigation circuit 280 before or after the corresponding media data that is obtained by the read data path 360-R from the magnetic media.

The long latency interfaces (LLI) 255-R, 255-W in the read data path (RDP) 360-R and write data path 360-W, respectively, may be implemented in a similar manner to FIG. 2. In addition, the iterative decoding block 270 and ITI mitigation circuit 280 may be implemented in a similar manner to FIG. 2.

In the exemplary embodiment of FIG. 3, the coded media data is generated by the write data path 360-W. The HDC provides ITI cancellation data to the write data path in user data format. As shown in FIG. 3, the exemplary write data path 360-W comprises an ESR encoder 320-W and an LDPC encoder 330, which encode the user data to coded media data, which is provided to the ITI mitigation circuit as ITI cancellation data. The write data path encodes the user data in a similar fashion as during a write operation to the media.

As shown in FIG. 3, the ITI mitigation circuit 280 in the read data path 360-R can optionally be bypassed when ITI cancellation is not enabled for a given read operation. Furthermore, the ESR encoder 320-R in the read data path 360-R can optionally be bypassed when a media data format is to be recovered.

FIG. 4 is a schematic block diagram of an alternative implementation 250" of the read channel 250 of FIG. 2, where the write data path provides user data to the ITI mitigation circuit 280, and the ITI mitigation circuit 280 generates the media data from the user data. As shown in FIG. 4, the exemplary read channel 250" comprises a read data path 460-R and a write data path 360-W, in a similar manner to FIG. 2. The read data path 460-R may be implemented in a similar manner to the read data path 260-R of FIG. 2. As previously indicated, the write data path 460-W is employed by the present invention to deliver the cancellation data to an ITI mitigation circuit 280 in the read data path 460-R. The cancellation data is provided to the ITI mitigation circuit 280 substantially simultaneously with the media data that is obtained by the read data path 460-R from the magnetic media. In another exemplary embodiment or mode of operation, the cancellation data is provided to the ITI mitigation circuit 280 before or after the media data that is obtained by the read data path 460-R from the magnetic media.

The long latency interfaces (LLI) 255-R, 255-W in the read data path (RDP) 460-R and write data path 460-W, respectively, may be implemented in a similar manner to FIG. 2. In addition, the iterative decoding block 270 and ITI mitigation circuit 280 may be implemented in a similar manner to FIG. 2.

In the exemplary embodiment of FIG. 4, the coded media data is generated by the ITI mitigation circuit 280 from the user data provided by the write data path 460-W. Thus, as shown in FIG. 4, the ESR encoder 420-W and an LDPC encoder 430 in the exemplary write data path 460-W are bypassed by the user data that is provided to the ITI mitigation circuit 280. The ESR encoder 420-W and an LDPC encoder 430 in write data path 460-W are not bypassed by the user data during a write operation, when the user data is encoded to media data before being written to the media.

As shown in FIG. 4, the ITI mitigation circuit 280 in the read data path 460-R can optionally be bypassed when ITI cancellation is not enabled for a given read operation. Furthermore the ESR encoder 420-R in the read data path 460-R can optionally be bypassed when a media data format is to be recovered.

FIGS. 5-10 illustrate the read channel 250 in various configurations, to implement a number of exemplary modes of operation. In FIGS. 5-10, the active signal path is shown using boldface, dashed arrows. As shown in FIGS. 5-10, and as discussed above, the read channel 250 comprises a Digital Finite Impulse Response filter 285, the ITI mitigation circuit 280, and an iterative decoding block 270.

In addition, as discussed further below in conjunction with FIGS. 5-10, the read channel 250 further comprises multiplexers 505, 515, a Y-AVG post processing block 510, a Y-MEM memory block 520 and a Y-MEM address block 530 for processing the Y-data.

FIG. 5A illustrates the read channel 250 in an exemplary non-ITI mode of operation. Generally, the non-ITI mode allows the ITI mitigation to be selectively disabled when not needed (for example, when the track separation is sufficient), and also allows the read channel 250 to be used with legacy systems where ITI mitigation may not be supported. As shown in FIG. 5A, the ITI mitigation circuit 280 is bypassed using the multiplexer 505 and the Y-AVG block 510 is bypassed using the multiplexer 515. Thus, the active signal path for the non-ITI mode comprises the DFIR filter 285, Y-MEM block 520 and the iterative

decoding block 270. Generally, the Y-data is stored in the Y-MEM block 520 and then applied to the iterative decoding block 270 for decoding.

FIG. 5B illustrates a number of interface signals as a function of time for the exemplary non-ITI mode of operation of FIG. 5A. Generally, in the following figures, the MEDIA signal illustrates what is on the media (a servo, a fragment, or a full sector). The term "FRG" in the figures indicates a fragment of a sector, the term "FULL" indicates a complete sector, and the term "SERVO" indicates a split sector (for example, FRG5.1 is a left sector fragment, FRG5.2 is a right sector fragment, and they are split, as indicated by the "SERVO" label). Thus, FRG5.1 and FRG5.2 together make up FULL5 (a full sector is split into two pieces). In addition, two RDGATE pulses are used to read each part and the channel combines and recovers the full5 sector. In some figures, the terms "MEDIA (rev 1)" and "MEDIA (rev 2)" indicate that the same sector is read twice (the disk has to go all the way around to get the head over the sector again).

The SVGATE signal indicates the servo gate (just for reference, and is high over any SERVO on the media). The DATA\_W signal indicates the write path data (where ITI cancellation data will go into the channel). LEFT# indicates left cancellation data for the sector with the same number, that is it corresponds to adjacent data written in the left track. RIGHT# indicates right cancellation data for the sector with the same number that is it corresponds to adjacent data written in the right track. Referring to FIG. 1, if track 2 is the current track from which data is recovered, tracks 1 and 3 are the adjacent left and right tracks, respectively.

The RDGATE signal corresponds to the read gate and initiates a read from the media. The RDGATE signal is active at the start of each sector and sector fragment. The RETRYGATE signal initiates a retry from stored samples (from y-memory). It is noted that while the RETRYGATE signal is illustrated herein in the context of ITI mitigation, the RETRYGATE signal can be employed in other applications as well, as would be apparent to a person of ordinary skill in the art.

As discussed herein, the signal METACMD[1] triggers an ITI mitigation with the read or retry (aligned to RDGATE or RETRYGATE). Since FIG. 5B corresponds to a normal read operation, without mitigation, the METACMD[1] is not active.

The DATA\_R signal indicates the recovered sector data (FULL# means the recovered data for the media sector of the same name). In addition, the SECTOR\_GOOD

signal indicates a good sector has been recovered (when the sector is not good, additional work is performed to recover the sector).

In addition, in one or more of the following figures, the following notation is employed:

avg(data1,data2) indicates a bitwise average of data from two read operations of the same data, where for each bit stored on the media, the corresponding Y-samples data1 and data2 are averaged. In an alternative implementation, the ADC samples are averaged;

decode(data) indicates an LDPC decode operation (data recovery, converted from Y-data to media or user bits), where Y-data is, for example, represented using 6 bits.;

iti(left, data) indicates a removal of ITI caused by the left adjacent track from the main track signal in “data”; and

iti(left, right, data) indicates a removal of ITI caused by both the left and right adjacent tracks from the main track signal in “data”.

FIG. 6A illustrates the read channel 250 in an exemplary post-processing (non-ITI) mode of operation. As shown in FIG. 6A, the ITI mitigation circuit 280 is bypassed using the multiplexer 505. Thus, the active signal path for the non-ITI mode comprises the DFIR filter 285, the Y-AVG block 510 (selected using the multiplexer 515), Y-MEM block 520 and the iterative decoding block 270. The Y-MEM address block 530 controls the selection of the Y-MEM block 520, in a known manner. Generally, the Y-data for the first read of stored data from a given sector is stored in the Y-MEM block 520 and then all samples for subsequent re-reads of data from the sector are merged, that is averaged by the Y-AVG block 510 with the contents of the Y-MEM block 520 using the feedback path 540. A given sector can be read multiple times, with the contents of the Y-MEM block 520 updated on each iteration, until the stored data from the given sector is successfully read as indicated by a successful decoding operation. The output of the Y-MEM block 520 is also applied to the iterative decoding block 270 for decoding.

FIG. 6B illustrates a number of interface signals as a function of time for the exemplary post-processing (non-ITI) mode of operation of FIG. 6A. The post-processing performed in the exemplary embodiment comprises an Average Read without ITI mitigation, such as by reading the stored data twice and performing a bitwise average of the data read in the two read operations shown in FIG. 6B. The averaging could be performed for any number of read operations, as would be apparent to a person of ordinary skill in the art. It is

noted that ITI mitigation is not needed because the second read and averaging sufficiently reduces the noise so that the data can be recovered. As shown in FIG. 6B, a SECTOR\_GOOD signal is not present for the first pass over the third sector, but is present following the second pass over the third sector. It is noted that sector FULL3 is read during the first read and is then passed to the iterative decoder and the decoded sector is passed to the DATA\_R bus. Since the sector was not decoded successfully without errors, the SECTOR\_GOOD signal is not asserted. On the second revolution, after the second read, the Y-data of the two reads is averaged, and the Y-averaged data is passed to the iterative decoding block, which decodes the sector successfully.

FIG. 7A illustrates the read channel 250 in an exemplary real-time ITI mode of operation. Generally, ITI mitigation is performed at the data rate and can optionally be performed on every sector. In the embodiment of FIG. 7A, ITI mitigation is performed for only one adjacent track to reduce the impact on throughput (for example, as indicated by the exemplary mode control signal or register, ITI\_SIDES). The ITI cancellation data is obtained from the write data path 260-W (FIG. 2), as discussed above in conjunction with FIG. 2. As shown in FIG. 7A, the ITI mitigation circuit 280 is placed in the active signal path by the multiplexer 505, and the Y-AVG block 510 is bypassed by the multiplexer 515. Thus, the active signal path for the real-time ITI mode comprises the DFIR filter 285, the ITI mitigation circuit 280, the Y-MEM block 520 and the iterative decoding block 270. Generally, the ITI corrected output of the ITI mitigation circuit 280 is stored in the Y-MEM block 520 and is then applied to the iterative decoding block 270 for decoding.

FIG. 7B illustrates a number of interface signals as a function of time for the exemplary real-time ITI mode of operation of FIG. 7A. As discussed herein, the exemplary real-time ITI mode of operation allows ITI mitigation to be selectively enabled by asserting the METACMD[1] signal simultaneously with the RDGATE signal. (ITI\_SIDES=0, either for OTF or retry operation).

The RDGATE signal indicates that sectors 1, 2, 3, 4, 5, 6, 7 are read from the media. The DATA\_W signal indicates that ITI mitigation will be performed using the left side track for sectors 3, 4 and 6. The METACMD[1] signal triggers an ITI mitigation with the read or retry (aligned to RDGATE or RETRYGATE). It is noted that sectors 1, 2, 5 and 7 are processed normally, since the METACMD[1] signal is not asserted with the associated RDGATE.

It is noted that a two-sided ITI mode of operation is discussed further below in conjunction with FIGS. 10A through 10C.

FIG. 8A illustrates the read channel 250 in an exemplary post-processing with ITI Mitigation mode of operation. Generally, the post-processing with ITI Mitigation mode performs ITI mitigation on post-processed Y-data. As shown in FIG. 8A, the ITI mitigation circuit 280 is selectively placed in the active signal path using the multiplexer 505 and the Y-AVG block 510 is placed in the active signal using the multiplexer 515. Thus, the active signal path for the post-processing with ITI Mitigation mode comprises the DFIR filter 285, ITI mitigation circuit 280, the Y-AVG block 510, Y-MEM block 520 and the iterative decoding block 270. The Y-MEM address block 530 controls the selection of the Y-MEM block 520, in a known manner.

Generally, for the first read of a given sector, the ITI mitigation circuit 280 and Y-AVG block 510 are bypassed and the Y-data is stored in the Y-MEM block 520. For subsequent M re-reads of the sector, the new Y samples from the individual reads are merged (i.e., averaged) by the Y-AVG block 510 with the contents of the Y-MEM block 520 using the feedback path 540. A given sector can be read multiple times, with the contents of the Y-MEM block 520 updated on each iteration, until the sector is successfully read. After the M+1-th read operation and completion of the Y-average operation, the Y-MEM block 520 contains the average of the Y-data from the M+1 read operations of the same sector. The output of the Y-MEM block 520 is also applied to the iterative decoding block 270 for decoding.

If the sector is not successfully read after a predefined number (M+1) of re-reads, using post-processed Y-Data, then ITI mitigation can be enabled, to perform ITI mitigation on the post-processed data. The direction to perform ITI mitigation is initiated by the combined signaling of RETRYGATE and METACMD[1] (or by the combined signaling of RETRYGATE and ITI\_GATE). In this mode, Y-Data is applied from the Y-MEM block 520 to the ITI mitigation circuit 280 using the feedback path 545, under control of multiplexer 502. The RETRYGATE signal indicates that the Y-data is not obtained by reading a sector from the media, but by reading the Y-MEM block that contains Y samples from a previous read operation. The ITI cancellation data (one sided or two-sided, based on the value of the exemplary ITI\_SIDES control word) is obtained from the write data path 260-W (FIG. 2), as discussed above in conjunction with FIG. 2. In addition, the Y-AVG

block 510 block is now bypassed using the multiplexer 515, so that the post-processed, then cancelled data can be stored in the Y-MEM block 520 prior to decoding by the iterative decoding block 270.

In a further variation, the number of average re-read operations can be dynamically determined (or terminated upon the occurrence of a predefined condition). Upon each averaging operation, as the averaged data is pushed to the decoder, the data is decoded and one or more metrics on the quality of decoding are generated. For example, one exemplary quality metric can include a number of bit errors. In one exemplary implementation, the averaging procedure can be continued until the number of bit errors decreases. If the number of bit errors plateaus (i.e., additional averaging may no longer help), then ITI mitigation can be performed. Similarly, the subsequent use of ITI mitigation can also be dynamically determined. As the ITI mitigation operations are performed, the data and metrics are computed and sent to the controller which can terminate immediately once recovery has been achieved (potentially using the same example discussed above relating to bit errors). In this case, the signal ITI\_SIDES is adjusted to perform only one-sided cancellation and each side is performed one at a time with the metrics/data analyzed after each step until recovery is successful.

FIG. 8B illustrates a number of interface signals as a function of time for the exemplary post-processing with single-sided ITI Mitigation mode of operation of FIG. 8A (ITI\_SIDES=0). The post-processing performed in the exemplary embodiment comprises an Average Read with single-sided ITI mitigation, such as an average of two reads shown in FIG. 8B. The averaging could be performed for any number of read operations, as would be apparent to a person of ordinary skill in the art. It is noted that the reading can be stopped if the first or second read operation has a SECTOR\_GOOD signal. Relating to the DATA\_R signal, it is further noted that the first "FULL3" in FIG. 8B comprises a decode(avg(read1, read2)) and the second "FULL3" comprises a decode(iti(left,avg(read1, read2))). It is noted that sector FULL3 is read during the first read and is then passed to the iterative decoder, and the decoded sector is passed to the DATA\_R bus. Since the sector was not decoded successfully without errors, the SECTOR\_GOOD signal is not asserted. On the second revolution, after the second read, the Y-data of the two reads is averaged, and the Y-averaged data is passed to the iterative decoding block, and the decoded sector is passed to the DATA\_R bus. Since the sector was not decoded successfully without errors, the

SECTOR\_GOOD signal is not asserted. Then, the RETRYGATE and METACMD[1] signals initiate the ITI cancellation in accordance with the present invention to process the Y-averaged data and mitigate the ITI using the cancellation data for the left track (LEFT3) that is adjacent to sector 3 in the main track. This cancellation data LEFT3 was provided earlier on the write data path using the DATA\_W bus. The result is passed to the iterative decoding block, which generates the decoded sector. The decoded sector is passed to the DATA\_R bus. Since this sector was decoded successfully without errors, the SECTOR\_GOOD signal is asserted.