(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6257726号

(P6257726)

(45) 発行日 平成30年1月10日(2018.1.10)

(24) 登録日 平成29年12月15日(2017.12.15)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/369 (2011.01)

F 1

H01L 27/146

H04N 5/369

F

請求項の数 13 (全 11 頁)

(21) 出願番号 特願2016-194768 (P2016-194768)

(22) 出願日 平成28年9月30日 (2016.9.30)

(62) 分割の表示 特願2011-266274 (P2011-266274)

の分割

原出願日 平成23年12月5日 (2011.12.5)

(65) 公開番号 特開2017-11300 (P2017-11300A)

(43) 公開日 平成29年1月12日 (2017.1.12)

審査請求日 平成28年10月28日 (2016.10.28)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 固体撮像装置およびカメラ

## (57) 【特許請求の範囲】

## 【請求項 1】

画素アレイ内に第1回路が形成された第1半導体領域を有する第1半導体基板と、前記画素アレイ内に第2回路が形成された第2半導体領域を有する第2半導体基板とを備え、前記第1半導体基板と前記第2半導体基板とが重なって配置され、前記第1回路と前記第2回路とが電気的に接続された固体撮像装置であって、

前記第1半導体基板は、前記第1半導体領域と接続した1つ以上の第1コントラクトプラグと、前記第1半導体基板の正面に露出し、前記第1コントラクトプラグに電気的に接続された第1接続部と、を前記画素アレイ内に有し、

前記第2半導体基板は、前記第2半導体領域と接続した1つ以上の第2コントラクトプラグと、前記第2半導体基板の正面に露出し、前記第2コントラクトプラグに電気的に接続された第2接続部と、を前記画素アレイ内に有し、

前記第1接続部と前記第2接続部は互いに接触しており、

前記画素アレイ内にある前記第2コントラクトプラグの数は前記画素アレイ内にある前記第1コントラクトプラグの数よりも多いことを特徴とする固体撮像装置。

## 【請求項 2】

前記第1回路は、フローティングディフュージョンと、光電変換部で発生した電荷を前記フローティングディフュージョンへ転送するためのトランジスタとを更に含み、

前記第2回路は、前記フローティングディフュージョンをリセットするためのトランジスタと、前記フローティングディフュージョンからの信号を増幅するためのトランジスタ

10

20

との内の少なくとも一方を含むことを特徴とする請求項 1 に記載の固体撮像装置。

【請求項 3】

前記第 1 半導体領域と前記第 2 半導体領域とは同じ導電型であることを特徴とする請求項 1 又は 2 に記載の固体撮像装置。

【請求項 4】

前記第 1 半導体領域と前記第 2 半導体領域とは互いに異なる導電型であることを特徴とする請求項 1 又は 2 に記載の固体撮像装置。

【請求項 5】

前記第 1 コンタクトプラグは、前記第 1 半導体領域に第 1 定電圧を供給するためのプラグであり、前記第 2 コンタクトプラグは、前記第 2 半導体領域に第 2 定電圧を供給するためのプラグであることを特徴とする請求項 1 乃至 4 の何れか 1 項に記載の固体撮像装置。 10

【請求項 6】

前記第 2 半導体基板は前記第 2 定電圧が供給される導電パターンを更に有し、

前記第 2 コンタクトプラグ及び前記第 2 接続部はそれぞれ、前記導電パターンに電気的に接続され、

前記導電パターンから供給される前記第 2 定電圧が前記第 1 コンタクトプラグを通じて前記第 1 定電圧として前記第 1 半導体基板に供給されることを特徴とする請求項 5 に記載の固体撮像装置。

【請求項 7】

前記第 1 定電圧と前記第 2 定電圧は、同じ値であることを特徴とする請求項 5 又は 6 に記載の固体撮像装置。 20

【請求項 8】

前記第 1 回路は、光電変換部を含み、

前記第 1 半導体領域は、第 1 ウエル領域であり、前記光電変換部は、前記第 1 ウエル領域に設けられており、

前記第 2 半導体領域は、第 2 ウエル領域であり、フローティングディフュージョンからの信号を增幅するためのトランジスタは、前記第 2 ウエル領域に設けられていることを特徴とする請求項 1 乃至 7 の何れか 1 項に記載の固体撮像装置。

【請求項 9】

前記第 2 回路は、光電変換部を含み、

前記第 2 半導体領域は、第 2 ウエル領域であり、前記光電変換部は、前記第 2 ウエル領域に設けられており、

前記第 1 半導体領域は、第 1 ウエル領域であり、フローティングディフュージョンからの信号を增幅するためのトランジスタは、前記第 1 ウエル領域に設けられていることを特徴とする請求項 1 に記載の固体撮像装置。

【請求項 10】

前記第 2 半導体基板内に設けられた接地線を更に有し、

前記接地線は、前記第 2 コンタクトプラグと前記第 2 接続部とのそれぞれに電気的に接続する

ことを特徴とする請求項 1 乃至 9 の何れか 1 項に記載の固体撮像装置。 40

【請求項 11】

前記 1 つ以上の第 1 コンタクトプラグは、前記第 1 半導体基板の正面に対する平面視において前記第 1 接続部に重なる位置にあるコンタクトプラグを含むことを特徴とする請求項 1 乃至 10 の何れか 1 項に記載の固体撮像装置。

【請求項 12】

前記 1 つ以上の第 2 コンタクトプラグは、前記第 2 半導体基板の正面に対する平面視において前記第 2 接続部に重なる位置にあるコンタクトプラグを含むことを特徴とする請求項 1 乃至 11 の何れか 1 項に記載の固体撮像装置。

【請求項 13】

請求項 1 乃至 12 の何れか 1 項に記載の固体撮像装置と、

50

前記固体撮像装置によって得られた信号を処理する信号処理部と、

を備えることを特徴とするカメラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は固体撮像装置およびカメラに関する。

【背景技術】

【0002】

固体撮像装置において、複数の回路を別の基板に分けて形成し、その複数の電気的に接続する構成が知られている。特許文献1に記載された固体撮像装置では、センサ基板にフォトダイオード、転送トランジスタ、リセットトランジスタ、および増幅トランジスタが形成され、周辺回路基板に選択トランジスタおよび周辺回路が形成される。10

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009-170448号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

固体撮像装置では、回路素子が形成される半導体領域に電源電圧または接地電位を供給するために、電源線または接地線と半導体領域とがコンタクトプラグで接続される。特許文献1には画素アレイにおいてコンタクトプラグをどのように配置するかについて何ら提案されていない。そこで、本発明は、画素アレイを構成する回路が別の基板に分けて形成される固体撮像装置において、半導体領域に定電圧を供給するコンタクトプラグの有利な配置を提供することを目的とする。20

【課題を解決するための手段】

【0005】

上記課題に鑑みて、本発明の1つの実施形態は、画素アレイ内に第1回路が形成された第1半導体領域を有する第1半導体基板と、前記画素アレイ内に第2回路が形成された第2半導体領域を有する第2半導体基板とを備え、前記第1半導体基板と前記第2半導体基板とが重なって配置され、前記第1回路と前記第2回路とが電気的に接続された固体撮像装置であって、前記第1半導体基板は、前記第1半導体領域と接続した1つ以上の第1コンタクトプラグと、前記第1半導体基板の主面に露出し、前記第1コンタクトプラグに電気的に接続された第1接続部と、を前記画素アレイ内に有し、前記第2半導体基板は、前記第2半導体領域と接続した1つ以上の第2コンタクトプラグと、前記第2半導体基板の主面に露出し、前記第2コンタクトプラグに電気的に接続された第2接続部と、を前記画素アレイ内に有し、前記第1接続部と前記第2接続部は互いに接触しており、前記画素アレイ内にある前記第2コンタクトプラグの数は前記画素アレイ内にある前記第1コンタクトプラグの数よりも多いことを特徴とする固体撮像装置を提供する。30

【発明の効果】

【0006】

上記手段により、画素アレイを構成する回路が別の基板に分けて形成される固体撮像装置において、半導体領域に定電圧を供給するコンタクトプラグの有利な配置が提供される。40

【図面の簡単な説明】

【0007】

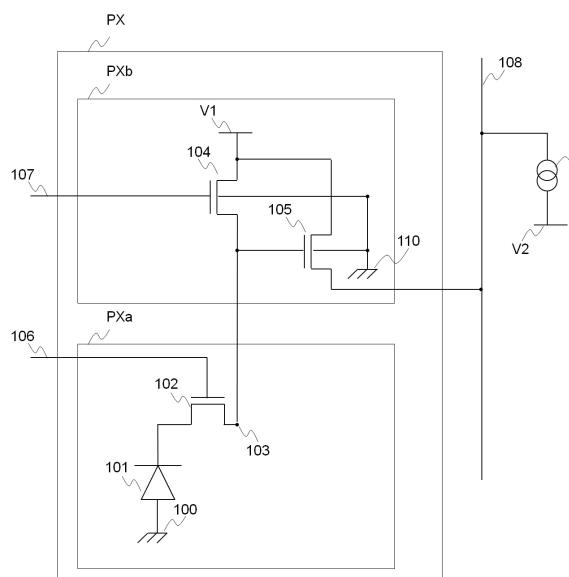

【図1】本発明の第1実施形態の固体撮像装置の1つの画素の等価回路の一例を説明する図。

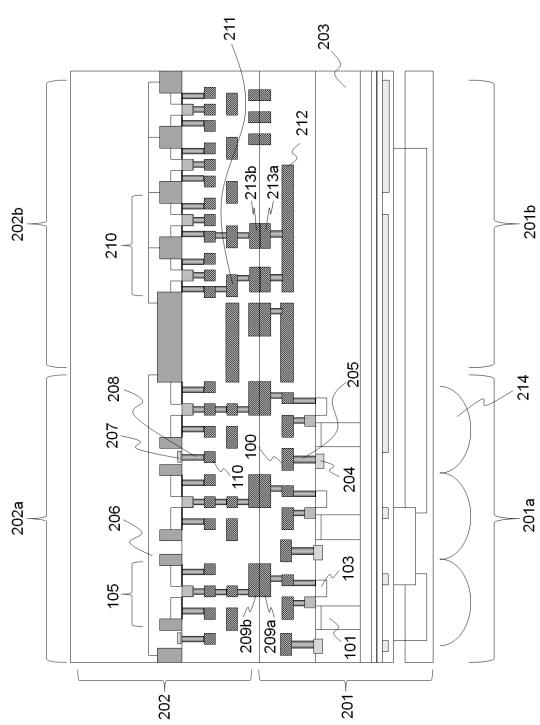

【図2】本発明の第1実施形態の固体撮像装置の例示の概略断面図。

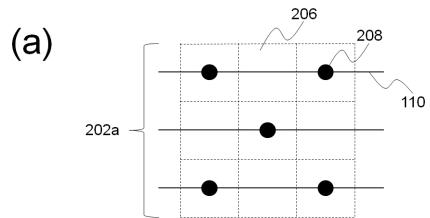

【図3】本発明の第1実施形態の固体撮像装置におけるコンタクトプラグの配置例を模式50

的に説明する図。

【図4】本発明の第1実施形態の変型例の固体撮像装置の例示の概略断面図。

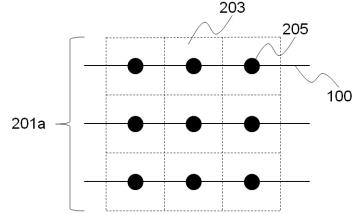

【図5】本発明の第2実施形態の固体撮像装置におけるコンタクトプラグの配置例を模式的に説明する図。

【発明を実施するための形態】

【0008】

添付の図面を参照しつつ本発明の実施形態について以下に説明する。様々な実施形態を通じて同様の要素には同一の参照符号を付して重複する説明を省略する。以下に説明する実施形態は、本発明の一部の実施形態であって、本発明はこれらに限定されるものではない。本明細書で特に図示または記載されない部分に関しては、当該技術分野の公知技術を適用しうる。

10

【0009】

図1から図3を参照しつつ、本発明の第1実施形態の固体撮像装置を説明する。図1は本発明の第1実施形態の固体撮像装置の1つの画素の等価回路の一例を説明する図である。本実施形態に係る固体撮像装置は2枚の半導体基板を有し、画素アレイを構成する回路はそれぞれの半導体基板に分かれて形成される。図1に示す画素PXは、第1半導体基板に形成される回路PXa(第1回路)と第2半導体基板に形成される回路PXb(第2回路)とを有する。

【0010】

回路PXaは光電変換部101と、転送トランジスタ102と、フローティングディフュージョン(FD)102とを含みうる。光電変換部101は例えばフォトダイオードで構成され、光電変換により正孔と電子とが発生する。本実施形態では信号電荷として電子を用いる。光電変換部101には接地線100からウェル領域およびコンタクトプラグを介して接地電位(第1定電圧)が供給される。転送トランジスタ102は光電変換部101で発生した電荷をフローティング状態のFD103へ転送する転送部として機能し、例えばNMOStランジスタが用いられる。転送トランジスタ102のゲートへは制御線106を通じて垂直走査回路(不図示)から駆動パルスが供給される。光電変換部101および転送トランジスタ102はP型のウェル領域(第1半導体領域)内に形成される。

20

【0011】

回路PXbはリセットトランジスタ104と増幅トランジスタ105とを含みうる。リセットトランジスタ104は少なくともFD103の電位を基準電位にリセットする画素リセット部として機能し、例えばNMOStランジスタが用いられる。リセットトランジスタ104の一方の主電極はFD103に電気的に接続され、他方の主電極は電圧源V1に電気的に接続される。これにより、リセットトランジスタ104は増幅トランジスタ105の入力ノードの電圧をリセットする。リセットトランジスタ104がオン状態にある間に転送トランジスタ102がオン状態になると、光電変換部101の電位も基準電位にリセットされる。リセットトランジスタ104のゲートへは制御線107を通じて垂直走査回路(不図示)から駆動パルスが供給される。増幅トランジスタ105は光電変換部101で発生した電子に基づく信号を増幅して信号線108へ出力する信号増幅部として機能し、例えばNMOStランジスタが用いられる。増幅トランジスタ105のゲートはFD103に電気的に接続される。増幅トランジスタ105の一方の主電極は電圧源V1に接続される。また、増幅トランジスタ105の他方の主電極へは信号線108を通じて電流源109からバイアス電流が供給され、このバイアス電流により増幅トランジスタ105はソースフォロアとして動作する。電流源109は電圧源V2に接続される。リセットトランジスタ104および増幅トランジスタ105はP型のウェル領域(第2半導体領域)内に形成される。リセットトランジスタ104および増幅トランジスタ105のそれぞれのバックゲートには接地線110からウェル領域およびコンタクトプラグを介して接地電位が供給される。

30

【0012】

上述の例ではリセットトランジスタ104および増幅トランジスタ105としてNMO

40

50

Sトランジスタを用いるが、PMOSトランジスタを用いてもよい。この場合に、リセットトランジスタ104および増幅トランジスタ105はN型のウェル領域内に形成される。リセットトランジスタ104および増幅トランジスタ105のバックゲートには電圧線から電源電圧（第2定電圧）が供給される。増幅トランジスタ105としてPMOSトランジスタが用いられる場合に、増幅トランジスタ105は信号電荷（上述の例では電子）と逆極性を有する。そのため、光電変換部101への入射光量が大きくなると、増幅トランジスタ105のゲート電位が下がり、これに応じて、増幅トランジスタ105のソース電位が上昇する。これにより、リセット時と比較して信号振幅が大きい場合の信号線108の駆動を駆動レベルが高い状態で行うことができ、増幅トランジスタ105としてPMOSトランジスタを用いる場合と比べて読み出し速度が向上しうる。

10

#### 【0013】

上述の例では信号電荷として電子を用いるが、正孔が用いられてもよい。この場合に、転送トランジスタ102としてPMOSトランジスタが用いられ、転送トランジスタ102はN型のウェル領域内に形成される。光電変換部101には電源地線からウェル領域およびコンタクトプラグを介して電源電圧が供給される。フォトダイオードのシリコン／酸化膜界面で発生する暗電流抑制のためにピニング層を形成する場合に、ピニング層の導電型もウェルと同様にN型としてもよい。この場合に、ピニング層としてシリコン／酸化膜界面の近傍に急峻な不純物プロファイルを形成することが可能な砒素や燐を用いることができるため、ピニング層にP型を用いた場合よりも暗電流を効果的に抑制できる。信号電荷として正孔が用いられる場合に、リセットトランジスタ104および増幅トランジスタ105として逆極性のNMOSトランジスタを用いることで、上述の読み出し速度が向上するという効果が得られうる。

20

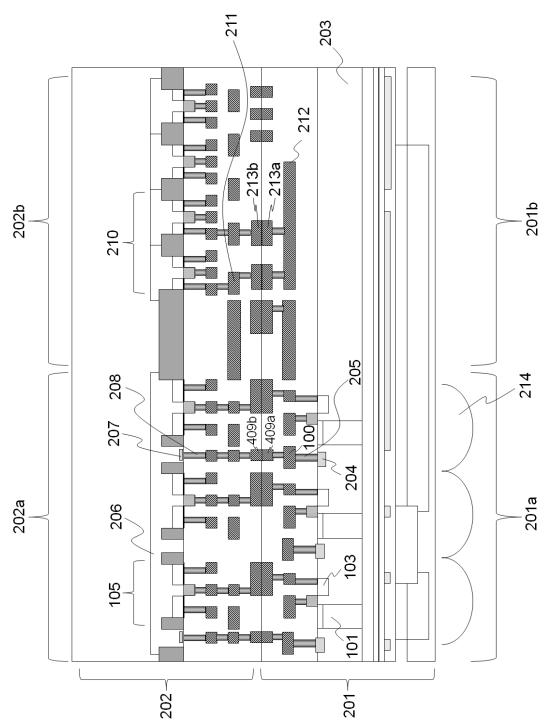

#### 【0014】

図2は本発明の第1実施形態の固体撮像装置の例示の概略断面図である。固体撮像装置は半導体基板201および半導体基板202を有する。半導体基板201の主面（回路が形成された表面）と半導体基板202の主面とは対向して配置される。半導体基板201の領域201aに形成された回路と半導体基板202の領域202aに形成された回路によって固体撮像装置の画素アレイが形成される。この画素アレイには、図1を用いて説明された画素PXが3行3列に配置されるが、画素数はこれに限られない。半導体基板201の領域201aに各画素PXの回路PXaが形成され、半導体基板202の領域202aに各画素PXの回路PXbが形成される。また、半導体基板201の領域201bに形成された回路と半導体基板202の領域202bに形成された回路によって固体撮像装置の周辺回路が形成される。周辺回路は例えば画素アレイから出力された信号を処理する回路や画素アレイに制御信号を供給する回路などを含みうる。図2では図1で説明されたリセットトランジスタ104を省略しているが、例えば半導体基板202の領域202aに形成されうる。

30

#### 【0015】

半導体基板201はウェル領域203を含み、ウェル領域203内に光電変換部101やFD103が形成される。光電変換部101で発生する電子を信号電荷として用いる場合にウェル領域203はP型の半導体領域であり、正孔を信号電荷として用いる場合にウェル領域203はN型の半導体領域である。すなわち、ウェル領域203は信号電荷と反対の導電型を有する。図2ではすべての画素の光電変換部101が1つのウェル領域203に形成されるが、光電変換部101ごとに個別のウェル領域を有してもよい。ウェル領域203内のウェルコンタクト領域204にはコンタクトプラグ205の一端が接続され、コンタクトプラグ205の他端は接地線100に接続される。これにより、コンタクトプラグ205を介してウェルコンタクト領域204に接地線100から接地電位が供給される。ウェルコンタクト領域204はウェル領域203と同じ導電型を有する半導体領域であり、ウェル領域203よりも不純物濃度が高く、これによりウェル領域203に任意の電圧を供給する。半導体基板201の領域201aの裏面にはマイクロレンズ214が形成され、このマイクロレンズ214を通じて光電変換部101へ光が照射される。

40

50

## 【0016】

半導体基板 202 はウェル領域 206 を含み、ウェル領域 206 内に増幅トランジスタ 105 のソース領域およびドレイン領域が形成される。増幅トランジスタ 105 がN M O Sトランジスタの場合にウェル領域 206 はP型の半導体領域であり、P M O Sトランジスタの場合にウェル領域 206 はN型の半導体領域である。すなわち、ウェル領域 203 は増幅トランジスタのソース電極およびドレイン電極と反対の導電型を有する。図2ではすべての画素の増幅トランジスタ 105 が1つのウェル領域 206 に形成されるが、増幅トランジスタ 105 ごとに個別のウェル領域を有してもよい。ウェル領域 206 内のウェルコンタクト領域 207 にはコンタクトプラグ 208 の一端が接続され、コンタクトプラグ 208 の他端は接地線 110 に接続される。これにより、コンタクトプラグ 208 を介してウェルコンタクト領域 207 に接地線 110 から接地電位が供給される。ウェルコンタクト領域 207 はウェル領域 206 と同じ導電型を有する半導体領域であり、ウェル領域 206 よりも不純物濃度が高く、これによりウェル領域 206 に任意の電圧を供給する。

## 【0017】

半導体基板 201 は接続部 209a を有し、接続部 209a の一部が半導体基板 201 の正面から露出する。また、半導体基板 202 は接続部 209b を有し、接続部 209b の一部が半導体基板 202 の正面から露出する。半導体基板 201 の正面と半導体基板 202 の正面とが対向して配置された場合に、接続部 209a と接続部 209b とが接続され、半導体基板 201 内の回路と半導体基板 202 内の回路とが電気的に接続される。例えば、接続部 209a および接続部 209b を介して F D 103 と増幅トランジスタ 105 のゲートとが電気的に接続される。接続部 209a と接続部 209b とは物理的に接続されてもよいし、導電性接着剤を介して接続されてもよい。接続部 209a および接続部 209b は各半導体基板の最上位配線層による導電パターンとして形成されてもよい。

## 【0018】

半導体基板 202 の領域 202b には、例えば読み出し回路の一部を構成するM O Sトランジスタ 210 が形成される。読み出し回路の一例として、複数の画素列ごとに読み出された信号を並列に処理する並列処理回路が挙げられる。このような並列処理回路として、列増幅器、列アナログ・デジタル変換器などがある。周辺回路は並列処理回路以外の回路も含みうる。

## 【0019】

半導体基板 202 の領域 202b は並列処理回路を構成するM O Sトランジスタ 210 に定電圧を供給する電圧線を含む導電パターン 211 を有する。導電パターン 211 は、紙面奥行き方向に延在して、各並列処理回路のM O Sトランジスタ 210 に共通に定電圧を供給する。また、半導体基板 201 の領域 201b は導電パターン 212 を有する。半導体基板 201 は接続部 213a を有し、半導体基板 202 は接続部 213b を有する。導電パターン 211 と導電パターン 212 とは接続部 213a および接続部 213b を介して電気的に接続される。接続部 213a および接続部 213b は、接続部 209a および接続部 209b と同様に最上位配線層の導電パターンにより形成されてもよい。半導体基板 201 の領域 201b は半導体基板 202 の領域 202b に比べて配置される回路素子の個数が少ない。場合によっては、半導体基板 201 の領域 201b には回路素子が全く配置されない。従って、領域 201b に導電パターン 212 を配置することによって、領域 202b に配置する場合よりも導電パターン 212 を自由にレイアウトできるとともに、導電パターン 212 の面積を大きくすることができ、抵抗値を低下させることができる。

## 【0020】

上述の例では増幅トランジスタ 105 としてM O Sトランジスタを用いたが、接合型電界効果型トランジスタ ( J F E T ) を用いてもよい。また、複数の光電変換部 101 で増幅トランジスタ 105 およびリセットトランジスタ 104 を共有してもよい。また、リセットトランジスタ 104 および増幅トランジスタ 105 のうちの少なくとも一方を半導体

基板 201 に形成してもよい。また、画素アレイ内にリセットトランジスタ 104 および増幅トランジスタ 105 を形成せずに、光電変換部 101 の電荷を直接に信号線を介して周辺回路へ出力してもよい。

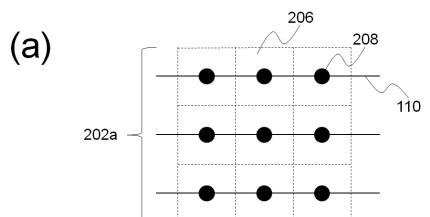

#### 【0021】

図 3 は本発明の第 1 実施形態の固体撮像装置におけるコンタクトプラグの配置例を模式的に説明する図である。図 3 (a) は半導体基板 202 の画素アレイが形成された領域 202a におけるコンタクトプラグ 208 の配置例を示し、図 3 (b) は半導体基板 201 の画素アレイが形成された領域 201a におけるコンタクトプラグ 205 の配置例を示す。図 3 において、参考のために画素 PX の境界を概念的に点線で示す。上述のように、画素アレイは 3 行 3 列に配置された 9 個の画素 PX を有する。図 3 ではコンタクトプラグの配置を説明するために必要な要素だけを示し、光電変換部 101 などの他の要素は省略する。

#### 【0022】

従来は画素アレイを構成する回路素子が同一の半導体基板に形成されるため、同一のウェル領域内に形成される複数の回路素子に対して同一のコンタクトプラグから接地電位が供給される。そのため、コンタクトプラグの配置の自由度が制限されていた。これに対して、本実施形態の固体撮像装置では、半導体基板 201 と半導体基板 202 とのそれぞれに画素アレイを構成する回路素子が分離して配置される。そのため、本実施形態では半導体基板 201 の画素アレイ内のウェル領域 203 に接地電位を供給するコンタクトプラグ 205 と半導体基板 202 の画素アレイ内のウェル領域 206 に接地電位を供給するコンタクトプラグ 208 とを独立して形成できる。そこで、本実施形態では、それぞれの半導体基板に形成される回路素子の特性に合わせてコンタクトプラグの配置を決定する。

#### 【0023】

設計方法として、まずそれぞれの半導体基板に形成する回路素子を決定する。本実施形態では、半導体基板 201 に光電変換部 101 と転送トランジスタ 102 と FD103 とが形成され、半導体基板 202 にリセットトランジスタ 104 と増幅トランジスタ 105 とが形成される。続いて、それぞれの半導体基板に形成するコンタクトプラグの配置を決定する。

#### 【0024】

本実施形態では、半導体基板 201 の画素アレイ内にある 1 つ以上のコンタクトプラグ 205 (第 1 コンタクトプラグ) の数が半導体基板 202 の画素アレイ内にある 1 つ以上のコンタクトプラグ 208 (第 2 コンタクトプラグ) の数よりも多い。具体的には半導体基板 201 では 1 画素ごとに 1 個の割合でコンタクトプラグ 205 が配され、半導体基板 202 では 2 画素ごとに 1 個の割合でコンタクトプラグ 208 が配されている。光電変換部 101 ごとにコンタクトプラグ 205 を配置することにより、光電変換部 101 の信号電荷が飽和状態を超えた際の溢れだしを抑制できる。また、カラーフィルタを用いた単板センサにおいて、光電変換部 101 の信号電荷が飽和状態を超えて溢れだした際に信号電荷が隣接する他の色の画素にそれぞれ不均等に混入することを抑制でき、高照度撮影時の画像における色再現性の劣化を防止できる。さらに、半導体基板 202 の画素アレイ内のウェル領域 206 へ接地電位を供給するコンタクトプラグ 208 の数を少なくすることによって、増幅トランジスタ 105 のゲート面積を大きくでき、ゲート面積に反比例する 1/f ノイズの発生を抑制できる。これにより、本実施形態では高照度撮影時の色再現性の向上と低照度撮影時のノイズ低減との両立を図ることができる。

#### 【0025】

図 3 の例では各画素行に 1 本の接地線 110 を配置しているが、ウェル領域 206 に所望の電圧を供給できれば複数の接地線 110 ごとに 1 本の接地線 110 を配置してもよい。また、半導体基板 202 においてコンタクトプラグ 208 を有する画素と有しない画素とが交互に配置されているが、このように周期的に配置するのではなく、ランダムに配置してもよい。また、半導体基板 201 において 1 つの画素に 1 つのコンタクトプラグ 205 が配置されているが、1 つの画素に複数のコンタクトプラグ 205 が配置されてもよい

10

20

30

40

50

し、複数の画素に対して1つのコンタクトプラグ205が配置されてもよい。

【0026】

続いて、図4を用いて第1実施形態の変型例を説明する。図4は本発明の第1実施形態の変型例の固体撮像装置の例示の概略断面図である。この変型例では、半導体基板201は接続部409aを有し、接続部409aの一部が半導体基板201の正面から露出する。また、半導体基板202は接続部409bを有し、接続部409bの一部が半導体基板202の正面から露出する。半導体基板201の正面と半導体基板202の正面とが対向して配置された場合に、接続部409aと接続部409bとが接続され、半導体基板201内の接地線100と半導体基板202内のウェル領域206とが電気的に接続される。接続部409aおよび接続部409bは、接続部209aおよび接続部209bと同様に最上位配線層の導電パターンにより形成されてもよい。このように、半導体基板201にのみ接地線100を形成し、半導体基板202には接地線110を形成しないことによって、半導体基板202のレイアウトの自由度を高めることができる。

10

【0027】

半導体基板201、202を貼り合わせる際に僅かなずれがある場合や貼り合わせ面の平滑性が良くない場合に、接続部409aと接続部409bとの間に接続不良が発生することがある。その結果、ウェル領域206に接地電位を供給できなくなる。本変型例では、コンタクトプラグの本数が少ない半導体基板202のウェル領域206へ接続部409a、409bを介して接地電位を供給するため、接続部409a、409bの数を少なくすることができ、接続不良が発生する確率を低減できる。第1実施形態について説明されてきた複数の変型例は組み合わせて適用することも可能である。

20

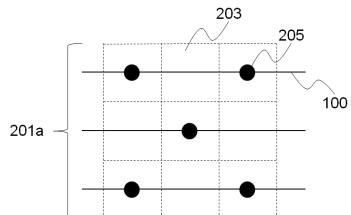

【0028】

続いて、図5を参照しつつ、本発明の第2実施形態の固体撮像装置を説明する。図5は本発明の第2実施形態の固体撮像装置におけるコンタクトプラグの配置例を模式的に説明する図である。以下では第1実施形態との相違点を中心に説明し、特に言及しない点は第1実施形態に準ずる。また、第1実施形態で説明した変型例は本実施形態にも適用可能である。

【0029】

本実施形態では、半導体基板201の画素アレイ内にあるコンタクトプラグ205の数が半導体基板202の画素アレイ内にあるコンタクトプラグ208の数よりも少ない。具体的には半導体基板201では2画素ごとに1個の割合でコンタクトプラグ205が配され、半導体基板202では1画素ごとに1個の割合でコンタクトプラグ208が配されている。增幅トランジスタ105およびリセットトランジスタ104が形成されるウェル領域206の電位は各トランジスタの動作特性を決める上で重要である。このウェル領域206の電位が画素アレイ内の場所によって電位の分布が生じると、画素アレイごとに異なるオフセットとして信号にシェーディングが生じる場合がある。そのため、半導体基板202の画素アレイ内のウェル領域206に多くのコンタクトプラグ208を配置して、ウェル領域206に接地電位を供給することによってシェーディングを抑制できる。一方、光電変換部101が配置される半導体基板201のウェル領域203に多くのコンタクトプラグ205を配置すると、コンタクトプラグ205を介して光電変換部101へ暗電流が多く発生してしまう場合がある。光電変換部101への暗電流の発生は、特に暗時の画像に悪影響を与える。また、コンタクトプラグ205により光電変換部101の面積が圧迫され、受光できる光電変換部101の面積が減ってしまい、感度が低下する場合がある。そのため、半導体基板201の画素アレイ内のコンタクトプラグ205を間引いて配置することによって、光電変換部101の面積を圧迫することを抑えることができるとともに、暗電流の発生を抑制できる。これにより、本実施形態では暗電流の抑制および感度の向上、すなわち高いS/N比の実現と、シェーディングの抑制との両立を図ることができる。また、第1実施形態で説明した変型例と同様に、半導体基板202内の接地線100から半導体基板201内のウェル領域203へ接地電位を供給してもよい。

30

40

【0030】

以下、上記の各実施形態に係る固体撮像装置の応用例として、この固体撮像装置が組み込まれたカメラについて例示的に説明する。カメラの概念には、撮影を主目的とする装置のみならず、撮影機能を補助的に備える装置（例えば、パーソナルコンピュータ、携帯端末等）も含まれる。カメラは、上記の実施形態として例示された本発明に係る固体撮像装置と、この固体撮像装置から出力される信号を処理する信号処理部とを含む。この信号処理部は、例えば、A / D 変換器と、このA / D 変換器から出力されるデジタルデータを処理するプロセッサとを含みうる。

【符号の説明】

【0031】

100 接地線、101 光電変換部、102 転送トランジスタ、201 半導体基板 10

、202 半導体基板、209 接続部、213 接続部

【図1】

【図2】

【図3】

(b)

【図4】

【図5】

(b)

---

フロントページの続き

(72)発明者 曽田 岳彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 肇

(56)参考文献 特開2009-170448 (JP, A)

特開2011-119946 (JP, A)

特開2010-219339 (JP, A)

特開2001-230400 (JP, A)

特開2011-129784 (JP, A)

特開2007-081139 (JP, A)

特開2005-093555 (JP, A)

特開2001-332714 (JP, A)

特開2009-206941 (JP, A)

特開2010-073906 (JP, A)

特開2011-151375 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/369