(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4115727号

(P4115727)

(45) 発行日 平成20年7月9日(2008.7.9)

(24) 登録日 平成20年4月25日(2008.4.25)

(51) Int.Cl.

G01R 19/165 (2006.01)

H03K 5/08 (2006.01)

F 1

G01R 19/165

H03K 5/08M

Z

請求項の数 2 (全 11 頁)

(21) 出願番号 特願2002-83004 (P2002-83004)

(22) 出願日 平成14年3月25日 (2002.3.25)

(65) 公開番号 特開2003-279603 (P2003-279603A)

(43) 公開日 平成15年10月2日 (2003.10.2)

審査請求日 平成17年3月15日 (2005.3.15)

(73) 特許権者 000001960

シチズンホールディングス株式会社

東京都西東京市田無町六丁目1番12号

(74) 代理人 100126583

弁理士 宮島 明

(74) 代理人 100100871

弁理士 土屋 繁

(72) 発明者 下鶴 雅士

東京都西東京市田無町六丁目1番12号

シチズン時計株式会社内

審査官 武田 知晋

(56) 参考文献 特開平04-175095 (JP, A)

実開平03-002267 (JP, U)

最終頁に続く

(54) 【発明の名称】電源電圧検出回路

## (57) 【特許請求の範囲】

## 【請求項 1】

判定電圧と電源電圧とを比較して、その比較結果に基づいて電圧信号を出力する電圧判定回路と、

前記電圧判定回路が~~出力した~~電圧信号を保持して出力するラッチ回路部と、

前記ラッチ回路部から前記比較結果をフィードバックされる動作制御部と、

を具備する電源電圧検出回路であって、

前記ラッチ回路部は、第一のラッチ回路と第二のラッチ回路とを有してなり、

前記第一のラッチ回路は、前記電圧判定回路と前記第二のラッチ回路との間に接続され、入力された前記電圧判定回路の出力を保持して前記第二のラッチ回路に出力および前記動作制御部にフィードバックし、

前記動作制御部は、前記電圧判定回路を動作させる信号が入力されると前記電圧判定回路を非動作状態から動作状態に切り換える制御を行い、前記フィードバックされた信号が変化すると、前記電圧判定回路を非動作状態にし、前記電圧判定回路を非動作にする信号が入力されると、前記第一のラッチ回路をリセットし、前記第二のラッチ回路に前記第一のラッチ回路の出力を保持させ、前記電圧判定回路を非動作状態にする

ことを特徴とする電源電圧検出回路。

## 【請求項 2】

前記第一のラッチ回路は、回路動作を開始するための信号を入力するクロック入力端子を有し、

前記電圧判定回路の出力を前記クロック入力端子に入力し、該出力の変化に基づいて回路動作を開始し、該出力を保持することを特徴とする請求項1に記載の電源電圧検出回路。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は電源電圧検出回路、更に詳しくは一次電池あるいは二次電池を電源電圧として動作する電子時計等の小型携帯機器に用いるのに適した電源電圧検出回路に関するものである。

【0002】

10

【従来の技術】

従来より、一次電池あるいは二次電池を電源電圧として動作する電子時計等の小型携帯機器では電源電圧の低下による誤動作を防ぐために電源電圧検出回路を搭載している。

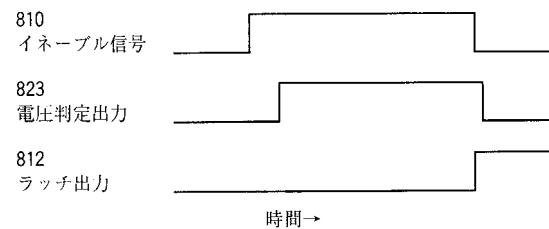

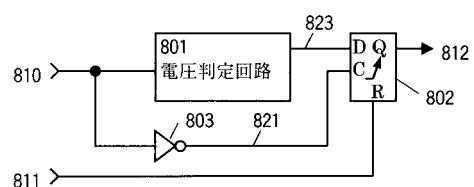

図8は従来の電源電圧検出回路の一例の構成を示す図である。

従来の電源電圧検出回路は図8に示すように、電源電圧が判定電圧よりも高いとハイレベルを出力する電圧判定回路801とクロック信号の立ち上がりに同期してデータをラッチするラッチ回路802と、インバータ803とを有している。

【0003】

20

図8において、電圧判定回路801の入力端子とインバータ803の入力端子とイネーブル信号810とを接続し、インバータ803の出力端子とラッチ回路802のクロック入力端子Cとを接続し、電圧判定出力823と電圧判定回路801の出力端子とラッチ回路802のデータ入力端子Dとを接続し、ラッチ回路802のリセット入力端子Rとリセット信号811とを接続してラッチ回路802のラッチ出力812を電源電圧検出回路の出力信号として構成している。

【0004】

図9は従来の電源電圧検出回路の動作を示すタイミングチャートであり、電源電圧が電源電圧検出回路の判定電圧よりも高い場合の例である。

【0005】

30

図9においてイネーブル信号810はハイレベルの期間電源電圧検出回路の動作を許可する制御信号である。

イネーブル信号810がハイレベルになると電圧判定回路が動作を開始して電圧判定回路の出力遅延時間だけ遅れて電圧判定出力823はハイレベルになり、その後でイネーブル信号810をローレベルにするとイネーブル信号810の立下りに同期して電圧判定出力823をラッチしてラッチ出力812はハイレベルになり、電圧判定回路の出力遅延時間だけ遅れて電圧判定出力823はローレベルになるがラッチ出力812はハイレベルを維持する。

なお、以上の動作の際に、イネーブル信号810は、動作温度範囲、動作電圧範囲で確実に電圧判定出力823が出力されるだけの充分な時間ハイレベルにしておく必要がある。以上の動作により、電源電圧が判定電圧以上であるかどうかをラッチ出力である電圧検出信号812のレベルで判定することができる。

40

【0006】

【発明が解決しようとする課題】

しかしながら従来の電源電圧検出回路ではイネーブル信号810は、動作温度範囲、動作電圧範囲で確実に電圧判定出力812が出力されるだけの充分な時間ハイレベルにしておく必要があるために、電圧判定出力812がすみやかに出力される条件においても図8における電圧判定回路801を長い期間動作させることにより多大な消費電力を費やしていた。

そこで本発明は、上記課題を解決して電源電圧検出回路の消費電力を低減することを目的としたものである。

【0007】

50

**【課題を解決するための手段】**

上記課題を解決するために、本発明に係る電源電圧検出回路は、判定電圧と電源電圧とを比較して、その比較結果に基づいて電圧信号を出力する電圧判定回路と、電圧判定回路が出力した電圧信号を保持して出力するラッチ回路部と、ラッチ回路部から比較結果をフィードバックされる動作制御部と、を具備する電源電圧検出回路であって、

ラッチ回路部は、第一のラッチ回路と第二のラッチ回路とを有してなり、第一のラッチ回路は、電圧判定回路と第二のラッチ回路との間に接続され、入力された電圧判定回路の出力を保持して第二のラッチ回路に出力および動作制御部にフィードバックし、動作制御部は、電圧判定回路を動作させる信号が入力されると電圧判定回路を非動作状態から動作状態に切り換える制御を行い、フィードバックされた信号が変化すると、電圧判定回路を非動作状態にし、電圧判定回路を非動作にする信号が入力されると、第一のラッチ回路をリセットし、第二のラッチ回路に第一のラッチ回路の出力を保持させ、電圧判定回路を動作状態から非動作状態にすることを特徴としている。

**【0008】**

上記発明において、第一のラッチ回路は、回路動作を開始するための信号を入力するクロック入力端子を有し、前記電圧判定回路の出力を前記クロック入力端子に入力し、該出力の変化に基づいて回路動作を開始し、該出力を保持することを特徴としている。

**【0010】**

**【発明の実施の形態】**

本発明の実施の形態は、イネーブル信号を入力し、電圧判定回路で電源電圧を判定した後に入出力制御回路で電圧検出信号を出力してなる電源電圧検出回路であって、前記入出力制御回路は動作制御部とラッチ回路部よりなり、前記電源電圧判定回路は電源電圧と判定電圧とを比較した結果を前記ラッチ回路に出力してなることを特徴としている。前記イネーブル信号に従って電圧判定回路が動作を開始し、電圧判定回路の出力が変化することを入出力制御回路が判断して電圧判定回路の動作を終了させる。

**【0011】**

**(第一実施例)**

以下、図面を参照して本発明の実施例について説明する。

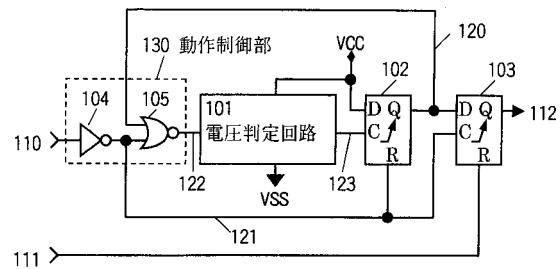

図1は本発明の第一実施例に係る電源電圧検出回路の構成を示す図である。

図1において、動作制御部130と、第一のラッチ回路102と第二のラッチ回路103からなるラッチ回路部とで入出力制御回路を構成する。また、前記動作制御部130は、電圧判定回路101の動作非動作を制御するようにインバータ104とノアゲート105とで構成する。

**【0012】**

イネーブル信号110とインバータ104の入力端子とを接続し、イネーブル信号110の反転信号121はノアゲート105の第一の入力端子と第一のラッチ回路102のリセット端子Rと第二のラッチ回路103のクロック端子Cとに接続し、電圧判定回路101の入力信号122はノアゲート105の出力端子と電圧判定回路101の入力端子とに接続する。

**【0013】**

電圧判定出力123は電圧判定回路101の出力端子と第一のラッチ回路102のクロック入力端子Cに接続し、第一のラッチ回路102のデータ入力端子Dと電源電圧VCCとを接続し、第一のラッチ回路102の出力信号120と第一のラッチ回路102の出力端子Qと第二のラッチ回路103のデータ入力端子Dとノアゲート105の第二の入力端子とを接続し、リセット信号111と第二のラッチ回路103のリセット端子Rとを接続することにより第二のラッチ回路103のラッチ出力112を本発明の第一実施例に係る電源電圧検出回路の出力信号とする。リセット信号111はリセット信号111がハイレベルの期間に第二のラッチ回路103のラッチ出力112をローレベルにリセットする信号で、出力の初期化時以外はリセット信号111はローレベルに固定する。

**【0014】**

10

20

30

40

50

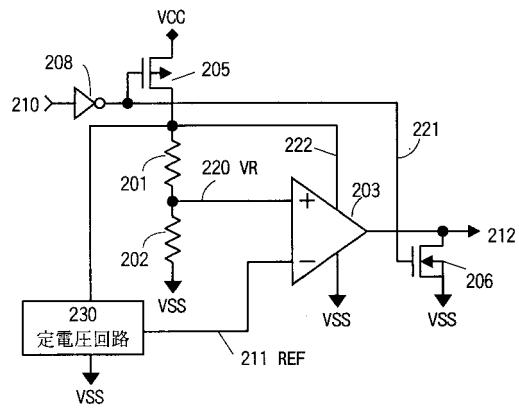

図2は図1に示した電源電圧検出回路を構成する電圧判定回路101の一例を示す回路図である。

図2において、イネーブル信号210とインバータ208の入力端子とを接続しイネーブル信号210の反転信号221とインバータ208の出力端子とソースを電源電圧VCCと接続したPチャネル電界効果トランジスタ(以下PMOSと記す)205のゲート端子とソースを接地電圧VSSと接続したNチャネル電界効果トランジスタ(以下NMOSと記す)206のゲート端子とを接続する。

#### 【0015】

第一の抵抗201の第一の端子と第一の端子を接地電圧VSSに接続する第二の抵抗202の第二の端子とコンパレータ203の正入力端子と電源電圧分割電圧VR220とを接続する。前記第一の抵抗201と第二の抵抗202とで抵抗分割回路を構成する。

10

#### 【0016】

コンパレータ203のマイナス電源端子には接地電圧VSSを供給し、コンパレータ203の負入力端子と定電圧回路230の出力である基準電圧REF211とを接続する。コンパレータ203の出力端子とNMOS206のドレインとを接続し電圧判定回路の出力端子212とする。NMOS206とコンパレータ203とで電圧比較回路を構成する。

#### 【0017】

PMOS205のドレインは、定電圧回路230のプラス電源端子と接続して定電圧回路230に電源を供給し、且つ第一の抵抗201の第二の端子と接続し抵抗分割回路に電源を供給し、且つコンパレータ203のプラス電源端子と接続し電圧比較回路に電源を供給する。前記PMOS205は、定電圧回路230および抵抗分割回路および電圧比較回路への電源供給あるいは電源遮断を制御するスイッチ回路とする。

20

#### 【0018】

次に図2の電圧判定回路の動作について説明する。

イネーブル信号210がローレベルの期間は、PMOS205がオフとなることで定電圧回路230および抵抗分割回路および電圧比較回路には電源が供給されず低消費電力となり、且つNMOS206がオンとなることで電圧判定回路の出力端子212はローレベルに固定される。

#### 【0019】

イネーブル信号210がハイレベルの期間は、PMOS205がオンとなることで定電圧回路230および抵抗分割回路および電圧比較回路に電源が供給され、定電圧回路230の出力である基準電圧REF211は設定した定電圧を出し、電源電圧分割電圧VR220は電源電圧を第一の抵抗201と第二の抵抗202とで抵抗分割した電圧を出し、且つNMOS206がオフとなることで電圧判定回路の出力端子212は電源電圧が判定電圧よりも高ければハイレベル、電源電圧が判定電圧よりも低ければローレベルを出力する。

30

#### 【0020】

ここで、基準電圧REF211と電源電圧分割電圧VR220と判定電圧との関係は、第一の抵抗201の抵抗値をR1とし第二の抵抗202の抵抗値をR2とし判定電圧をVxとすると以下の関係式で示される。

40

$$Vx = REF \times (R1 / (R1 + R2)) \quad \dots \quad 式1$$

例えば、REF = 1V、R1 = 5K、R2 = 10Kとした場合には判定電圧Vxは式1より1.5Vとなり、電源電圧が1.5Vよりも高ければ電圧判定回路の出力はハイレベル、電源電圧が1.5Vよりも低ければ電圧判定回路の出力はローレベルとなる。

#### 【0021】

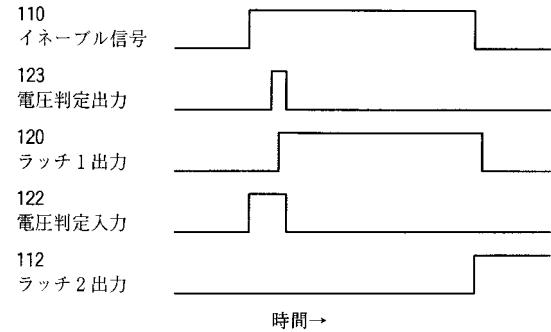

図3は本発明の第一実施例に係る電源電圧検出回路の動作を示すタイミングチャートであり、電源電圧が判定電圧よりも高い場合の例を示している。

図3において、最初にイネーブル信号110がローレベルの時は電圧判定回路は非動作となり電圧判定出力123、ラッチ1出力120、電圧判定入力122、及びラッチ2出力112はすべてローレベルである。次に、イネーブル信号110をハイレベルにして電源

50

電圧検出回路を動作させると、電圧判定入力 122 はハイレベルとなり電圧判定回路が動作を開始し、電圧判定回路の出力遅延時間分遅れて電圧判定出力 123 がハイレベルになることでラッチ 1 出力 120 はハイレベルになり、ラッチ 1 出力 120 がハイレベルになることで電圧判定入力 122 がローレベルになり、電圧判定入力 122 がローレベルになることで電圧判定回路が非動作となり電圧判定出力 123 はローレベルに変化するが、ラッチ 1 出力 120 はハイレベルを維持する。

#### 【 0022 】

電源電圧検出回路の動作温度範囲、動作電圧範囲で確実に電圧判定出力 123 が出力されるだけの充分な時間イネーブル信号 110 をハイレベルにした後で、イネーブル信号 110 をローレベルにするとラッチ 2 出力 112 がハイレベルになり、以後再びイネーブル信号 110 がハイレベルになり電源電圧検出回路を動作させるか第二のラッチ回路をリセット信号をハイレベルにして初期化するまでラッチ 2 出力 112 はハイレベルを維持する。前述の動作により電圧判定回路 101 は電圧判定入力 122 がハイレベルの期間しか動作しないのでイネーブル信号 110 のハイレベルの期間が長くても消費電力を低減することができる。

#### 【 0023 】

上記説明のように本発明の電源電圧検出回路は電源電圧が判定電圧よりも高いことを検出すると速やかに電圧判定回路を非動作にするので電源電圧検出回路の消費電力を低減することが可能である。

#### 【 0024 】

##### ( 第二実施例 )

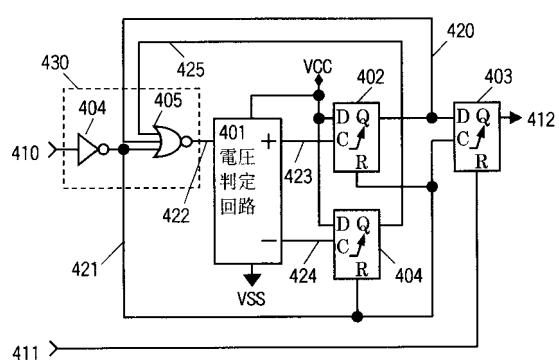

図 4 は本発明の第二実施例に係る電源電圧検出回路の構成を示す図である。

図 4 において、動作制御部 430 と、第一のラッチ回路 402 と第二のラッチ回路 403 と第三のラッチ回路 404 からなるラッチ回路部とで入出力制御回路を構成する。また、動作制御部 430 は、電圧判定回路 401 の動作非動作を制御するように、インバータ 404 とノアゲート 405 とで構成する。

#### 【 0025 】

イネーブル信号 410 とインバータ 404 の入力端子とを接続し、イネーブル信号 410 の反転信号 421 はノアゲート 405 の第一の入力端子と第一のラッチ回路 402 のリセット端子 R と第三のラッチ回路 404 のリセット端子 R と第二のラッチ回路 403 のクロック端子 C とに接続し、電圧判定回路 401 の入力信号 422 はノアゲート 405 の出力端子と電圧判定回路 401 の入力端子とに接続する。

#### 【 0026 】

電源電圧が判定電圧よりも高いと出力がハイレベルに変化する電圧判定正出力 423 は電圧判定回路 401 の正出力端子と第一のラッチ回路 402 のクロック入力端子 C に接続し、第一のラッチ回路 402 のデータ入力端子 D と電源電圧 VCC とを接続し、第一のラッチ回路 402 の出力信号 420 と第一のラッチ回路 402 の出力端子 Q と第二のラッチ回路 403 のデータ入力端子 D とノアゲート 405 の第二の入力端子とを接続する。電源電圧が判定電圧よりも高いと出力がローレベルに変化する電圧判定負出力 424 は電圧判定回路 401 の負出力端子と第三のラッチ回路 404 のクロック入力端子 C に接続し、第三のラッチ回路 404 のデータ入力端子 D と電源電圧 VCC とを接続し、第三のラッチ回路 404 の出力信号 425 と第三のラッチ回路 404 の出力端子 Q とノアゲート 405 の第三の入力端子とを接続する。

#### 【 0027 】

リセット信号 411 と第二のラッチ回路 403 のリセット端子とを接続することにより第二のラッチ回路 403 のラッチ出力 412 を本発明の第二実施例に係る電源電圧検出回路の出力信号とする。リセット信号 411 はリセット信号 411 がハイレベルの期間に第二のラッチ回路 403 のラッチ出力 412 をローレベルにリセットする信号で、出力の初期化時以外はリセット信号 411 はローレベルに固定する。

#### 【 0028 】

10

20

30

40

50

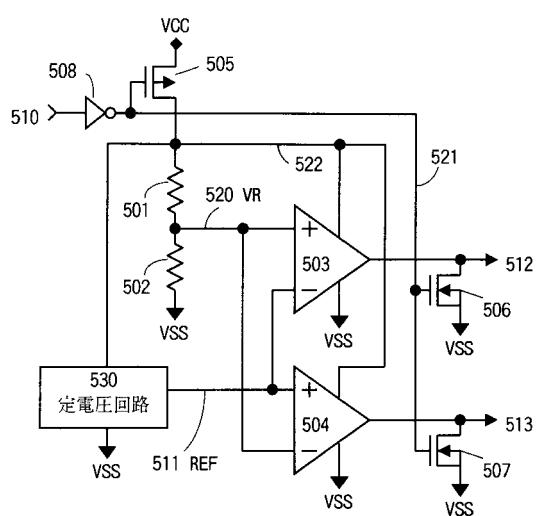

図5は図4に示した電源電圧検出回路を構成する電圧判定回路401の一例を示す回路図である。

図5において、イネーブル信号510とインバータ508の入力端子を接続しイネーブル信号510の反転信号521とインバータ508の出力端子とソースを電源電圧VCCと接続したPMOS505のゲート端子とソースを接地電圧VSSと接続した第一のNMOS506のゲート端子とソースを接地電圧VSSと接続した第二のNMOS507のゲート端子とを接続する。

#### 【0029】

第一の抵抗501の第一の端子と第一の端子を接地電圧VSSに接続する第二の抵抗502の第二の端子と第一のコンパレータ503の正入力端子と第二のコンパレータ504の負入力端子と電源電圧分割電圧VR520とを接続する。第一の抵抗501と第二の抵抗502とで抵抗分割回路を構成する。10

#### 【0030】

第一のコンパレータ503のマイナス電源端子と第二のコンパレータ504のマイナス電源端子には接地電圧VSSを供給し、第一のコンパレータ503の負入力端子と第二のコンパレータ504の正入力端子と定電圧回路530の出力である基準電圧REF511とを接続する。第一のコンパレータ503の出力端子と第一のNMOS506のドレインとを接続し電圧判定回路の正出力端子512とし、第二のコンパレータ504の出力端子と第二のNMOS507のドレインとを接続し電圧判定回路の負出力端子513とする。第一のコンパレータ503と第一のNMOS506とで第一の電圧比較回路を構成し、第二のコンパレータ504と第二のNMOS507とで第二の電圧比較回路を構成する。20

#### 【0031】

PMOS505のドレインは、定電圧回路530のプラス電源端子と接続して定電圧回路530に電源を供給し、且つ第一の抵抗501の第二の端子と接続し抵抗分割回路に電源を供給し、且つコンパレータ503のプラス電源端子と接続し第一の電圧比較回路に電源を供給し、且つコンパレータ504のプラス電源端子と接続し第二の電圧比較回路に電源を供給する。

前記PMOS505は、定電圧回路530および抵抗分割回路および第一の電圧比較回路および第二の電圧比較回路への電源供給あるいは電源遮断を制御するスイッチ回路とする。30

#### 【0032】

次に図5の電圧判定回路の動作について説明する。

イネーブル信号510がローレベルの期間は、PMOS505がオフとなることで定電圧回路530および抵抗分割回路および第一の電圧比較回路および第二の電圧比較回路には電源が供給されず低消費電力となり、且つNMOS506がオンとなることで電圧判定回路の正出力端子512はローレベルに固定され、且つNMOS507がオンとなることで電圧判定回路の負出力端子513はローレベルに固定される。

#### 【0033】

イネーブル信号510がハイレベルの期間は、PMOS505がオンとなることで定電圧回路530および抵抗分割回路および第一の電圧比較回路および第二の電圧比較回路に電源が供給され、定電圧回路530の出力である基準電圧REF511は設定した定電圧を出力し、電源電圧分割電圧VR520は電源電圧を第一の抵抗501と第二の抵抗502とで抵抗分割した電圧を出力し、且つNMOS506がオフとなることで電圧判定回路の正出力端子512は電源電圧が判定電圧よりも高ければハイレベル、電源電圧が判定電圧よりも低ければローレベルを出力し、且つNMOS507がオフとなることで電圧判定回路の負出力端子513は電源電圧が判定電圧よりも高ければローレベル、電源電圧が判定電圧よりも低ければハイレベルを出力する。40

#### 【0034】

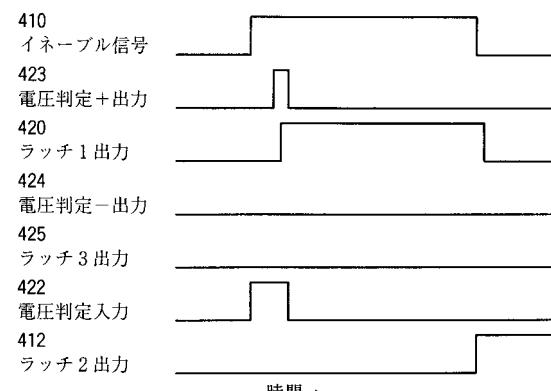

図6は本発明の第二実施例に係る電源電圧検出回路の第一の動作を示すタイミングチャートであり、電源電圧が判定電圧よりも高い場合の例を示している。50

図6において、最初にイネーブル信号410がローレベルの時は電圧判定回路は非動作となり電圧判定正出力423、ラッチ1出力420、電圧判定負出力424、ラッチ3出力425、電圧判定入力422、及びラッチ2出力412はすべてローレベルである。次に、イネーブル信号410をハイレベルにして電源電圧検出回路を動作させると、電圧判定入力422はハイレベルとなり電圧判定回路が動作を開始し、電圧判定回路の出力遅延時間分遅れて電圧判定正出力423がハイレベルになることでラッチ1出力420はハイレベルになり、ラッチ1出力420がハイレベルになることで電圧判定入力422がローレベルになり、電圧判定入力422がローレベルになることで電圧判定回路が非動作となり電圧判定正出力423はローレベルに変化するが、ラッチ1出力420はハイレベルを維持する。

10

#### 【0035】

電源電圧検出回路の動作温度範囲、動作電圧範囲で確実に電圧判定正出力423が出力されるだけの充分な時間イネーブル信号410をハイレベルにした後で、イネーブル信号410をローレベルにするとラッチ2出力412がハイレベルになり、以後再びイネーブル信号410がハイレベルになり電源電圧検出回路を動作させるか第二のラッチ回路をリセット信号をハイレベルにして初期化するまでラッチ2出力412はハイレベルを維持する。前記動作の期間中、電圧判定負出力424及びラッチ3出力425はローレベルを維持して変化しない。

前述の動作により電圧判定回路401は電圧判定入力422がハイレベルの期間しか動作しないのでイネーブル信号410のハイレベルの期間が長くても消費電力を低減することができる。

20

#### 【0036】

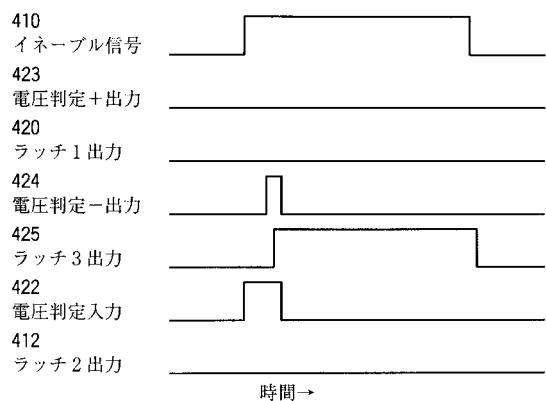

図7は本発明の第二実施例に係る電源電圧検出回路の第二の動作を示すタイミングチャートであり、電源電圧が判定電圧よりも低い場合の例を示している。

図7において、最初にイネーブル信号410がローレベルの時は電圧判定回路は非動作となり電圧判定正出力423、ラッチ1出力420、電圧判定負出力424、ラッチ3出力425、電圧判定入力422、及びラッチ2出力412はすべてローレベルである。

#### 【0037】

次に、イネーブル信号410をハイレベルにして電源電圧検出回路を動作させると、電圧判定入力422はハイレベルとなり電圧判定回路が動作を開始し、電圧判定回路の出力遅延時間分遅れて電圧判定負出力424がハイレベルになることでラッチ3出力425はハイレベルになり、ラッチ3出力425がハイレベルになることで電圧判定入力422がローレベルになり、電圧判定入力422がローレベルになることで電圧判定回路が非動作となり電圧判定負出力424はローレベルに変化するが、ラッチ3出力425はハイレベルを維持する。

30

#### 【0038】

電源電圧検出回路の動作温度範囲、動作電圧範囲で確実に電圧判定負出力424が出力されるだけの充分な時間イネーブル信号410をハイレベルにした後で、イネーブル信号410をローレベルにするとラッチ2出力412はローレベルのまま変化しない。前記動作の期間中、電圧判定正出力423及びラッチ1出力420はローレベルを維持して変化しない。

40

前述の動作により電圧判定回路401は電圧判定入力422がハイレベルの期間しか動作しないのでイネーブル信号410のハイレベルの期間が長くても消費電力を低減することができる。

#### 【0039】

上記説明のように本発明の電源電圧検出回路は電源電圧が判定電圧よりも高いことを検出すると速やかに電圧判定回路を非動作にし、また電源電圧が判定電圧よりも低いことを検出すると速やかに電圧判定回路を非動作にするので電源電圧検出回路の消費電力を低減することが可能である。

#### 【0040】

50

**【発明の効果】**

以上説明したように、本発明の電源電圧検出回路では電圧判定出力が変化すると速やかに電圧判定回路を非動作とすることにより電源電圧検出回路の消費電力を低減することができる。

**【図面の簡単な説明】**

【図 1】本発明の第一実施例に係る電源電圧検出回路の構成を示す図である。

【図 2】図 1 に示した電源電圧検出回路を構成する電圧判定回路の回路図である。

【図 3】本発明の第一実施例に係る電源電圧検出回路の動作を示すタイミングチャートである。

【図 4】本発明の第二実施例に係る電源電圧検出回路の構成を示す図である。 10

【図 5】図 4 に示した電源電圧検出回路を構成する電圧判定回路の回路図である。

【図 6】本発明の第二実施例に係る電源電圧検出回路の第一の動作を示すタイミングチャートである。

【図 7】本発明の第二実施例に係る電源電圧検出回路の第二の動作を示すタイミングチャートである。

【図 8】従来の電源電圧検出回路の構成を示す図である。

【図 9】従来の電源電圧検出回路の動作を示すタイミングチャートである。

**【符号の説明】**

1 0 1 . . . 電圧判定回路

1 3 0 . . . 動作制御部

1 0 2 、 1 0 3 . . . ラッチ回路

2 0 1 、 2 0 2 . . . 抵抗

2 0 3 . . . コンパレータ

2 3 0 . . . 定電圧回路

2 0 5 . . . P M O S

2 0 6 . . . N M O S

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図9】

時間→

【図8】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

G01R 19/00-19/32

H03K 5/08