(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6153471号

(P6153471)

(45) 発行日 平成29年6月28日(2017.6.28)

(24) 登録日 平成29年6月9日(2017.6.9)

|                          |                    |

|--------------------------|--------------------|

| (51) Int.Cl.             | F 1                |

| HO 1 L 23/12 (2006.01)   | HO 1 L 23/12 501 C |

| HO 1 L 21/60 (2006.01)   | HO 1 L 21/60 311 Q |

| HO 1 L 23/522 (2006.01)  | HO 1 L 21/88 T     |

| HO 1 L 21/768 (2006.01)  | HO 1 L 21/88 J     |

| HO 1 L 21/3205 (2006.01) |                    |

請求項の数 13 (全 30 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2013-543298 (P2013-543298)  |

| (86) (22) 出願日 | 平成23年12月7日(2011.12.7)         |

| (65) 公表番号     | 特表2014-504451 (P2014-504451A) |

| (43) 公表日      | 平成26年2月20日(2014.2.20)         |

| (86) 国際出願番号   | PCT/US2011/063653             |

| (87) 国際公開番号   | W02012/078709                 |

| (87) 国際公開日    | 平成24年6月14日(2012.6.14)         |

| 審査請求日         | 平成26年12月4日(2014.12.4)         |

| (31) 優先権主張番号  | 12/962,806                    |

| (32) 優先日      | 平成22年12月8日(2010.12.8)         |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                          |

|-----------|------------------------------------------------------------------------------------------|

| (73) 特許権者 | 504142411<br>テッセラ、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア州 95<br>134, サン・ノゼ、オーチャード・<br>パークウェイ 3025 |

| (74) 代理人  | 100099623<br>弁理士 奥山 尚一                                                                   |

| (74) 代理人  | 100096769<br>弁理士 有原 幸一                                                                   |

| (74) 代理人  | 100107319<br>弁理士 松島 鉄男                                                                   |

| (74) 代理人  | 100114591<br>弁理士 河村 英文                                                                   |

| (74) 代理人  | 100125380<br>弁理士 中村 純子                                                                   |

最終頁に続く

(54) 【発明の名称】超小型電子ユニット、積層アセンブリ、システム、及びモジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

超小型電子ユニットであって、該超小型電子ユニットは、

基板であって、該基板は本質的に、半導体材料と、凹部を有する主面であって、該凹部は該半導体材料の中へ延在し、該凹部は該主面の下方に延在し、かつ該凹部が該基板を完全に通っては延在していないものである主面と、該凹部内に配置され、弾性係数が10 GPa未満である材料と、を有し、前記凹部は、場所によって変化する勾配を有する内面を画定し、該内面が前記主面とは反対側の前記基板の第2の面に向かって更に延在するに従い、前記主面に対する該内面の角度の大きさが減少するようになっている、基板と、

導電性素子であって、該導電性素子は、前記凹部の上に重なり、かつ前記基板によって支持されたアンカー部分から、前記凹部に重なり前記基板によって支持されない端部分に延在している接合部分を備え、前記端部分は前記アンカー部分に対して片持ち梁であり、前記凹部は前記主面に平行な横方向においては前記凹部の外側境界の下方に延在せず、該接合部分は、該超小型電子ユニットの外部のコンポーネントに接続するために前記主面において少なくとも部分的に露出しており、前記導電性素子は、前記基板の前記主面とは反対側の第2の面に向かって延在している導電性ビアに電気的に結合されている、導電性素子と、

前記基板の前記主面と前記導電性素子の前記アンカー部分との間に配置された誘電体層と

を具備し、

10

20

前記基板は、複数の能動半導体デバイスを備え、前記導電性素子は、該複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続されている、超小型電子ユニット。

【請求項2】

前記接合部分は、前記超小型電子ユニットの動作又は製造又は試験中に、該接合部分に対する応力を低減するように移動可能である、請求項1に記載の超小型電子ユニット。

【請求項3】

前記凹部内に配置された前記材料は、ポリイミド、シリコーン及びエポキシからなる群から選択された少なくとも1つの材料を含む、請求項1に記載の超小型電子ユニット。

【請求項4】

前記接合部分は、前記基板の前記主面に対して実質的に平行な方向に延在している、請求項1に記載の超小型電子ユニット。 10

【請求項5】

前記アンカー部分及び前記接合部分は同じ方向に延在している、請求項1に記載の超小型電子ユニット。

【請求項6】

前記導電性ビアは前記第2の面において露出している、請求項1に記載の超小型電子ユニット。

【請求項7】

前記導電性ビアは、前記基板において前記第2の面から前記主面まで延在している孔内に延在している、請求項1に記載の超小型電子ユニット。 20

【請求項8】

前記孔は、前記主面から前記第2の面に向かって延在している第1の開口部と、該第1の開口部から前記第2の面まで延在している第2の開口部と、を含み、前記第1の開口部及び前記第2の開口部の内面は、前記主面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定している、請求項1に記載の超小型電子ユニット。

【請求項9】

少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備える積層アセンブリであって、該第1の超小型電子ユニットは請求項1に記載の超小型電子ユニットであり、前記第2の超小型電子ユニットは、該第1の超小型電子ユニットと積層されており、該積層アセンブリ内の前記第1の超小型電子ユニットの前記基板は、前記第2の超小型電子ユニットの基板と電気的に接続されている、積層アセンブリ。 30

【請求項10】

前記第1の超小型電子ユニットの前記接合部分と前記第2の超小型電子ユニットの導電性素子とに電気的に結合されている導体塊を更に具備する、請求項1に記載の積層アセンブリ。

【請求項11】

請求項1に記載の超小型電子ユニットを少なくとも1つ含む構造体を具備するシステムであって、該構造体に1つ又は複数の他の電子コンポーネントが電気的に接続される、システム。

【請求項12】

ハウジングを更に具備し、前記構造体及び前記他の電子コンポーネントは前記ハウジングに実装されている、請求項1に記載のシステム。 40

【請求項13】

請求項1に記載の前記超小型電子ユニットを複数備えるモジュールであって、前記複数の前記超小型電子ユニットの各々にかつ各々から信号を伝送するための共通の電気的インターフェースを有している、モジュール。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層型超小型電子アセンブリ及びこうしたアセンブリを作製する方法と、こ 50

うしたアセンブリにおいて有用なコンポーネントと、に関する。

【0002】

[関連出願の相互参照]

本出願は、2010年12月8日に出願された米国特許出願第12/962,806号の継続出願であり、その開示内容は引用することにより本明細書の一部をなすものとする。

【背景技術】

【0003】

半導体チップは、一般に、個々のパッケージングされたユニットとして提供される。標準的なチップは、平坦な矩形本体を有し、その表面にチップの能動回路部に接続されたコンタクトがある。通常、各個々のチップは、パッケージに実装され、次にパッケージは、プリント回路基板等の回路パネルに実装され、チップのコンタクトを回路パネルの導体に接続する。多くの従来の設計では、チップパッケージは、チップ自体の面積よりも大幅に広い回路パネルの面積を占有する。本開示において表面を有するフラットチップに関して使用するとき、「チップの面積」は、表面の面積を指すものと理解するべきである。

【0004】

「フリップチップ」設計では、チップの表面はパッケージ基板の面に対面し、すなわち、チップキャリア及びチップ上のコンタクトは、はんだボール又は他の接続素子によってチップキャリアのコンタクトに直接接合される。そして、チップキャリアを、チップの表面の上に重なる端子を介して回路パネルに接合することができる。「フリップチップ」設計は、比較的小型の構成を可能にし、各チップは、例えば、その開示を引用することにより本明細書の一部をなすものとする本願と同一の譲受人に譲渡された米国特許第5,148,265号、米国特許第5,148,266号及び米国特許第5,679,977号の或る特定の実施形態に開示されているように、チップの表面の面積に等しいか又はそれよりわずかに広い回路パネルの面積を占有する。

【0005】

超小型電子アセンブリが占有する回路パネルの平面面積を最小限にすることに加えて、回路パネルの平面に対して垂直な高さ又は寸法全体が小さいチップパッケージを製造することも望ましい。こうした薄い超小型電子パッケージにより、隣接する構造体に近接してパッケージが実装されている回路パネルの配置が可能になり、これにより、回路パネルを組み込んだ製品の全体的なサイズが低減する。

【0006】

複数のチップを「積層体」構成で、すなわち複数のチップが重なり合って配置される構成でパッケージングすることも提案された。積層型構成では、幾つかのチップを、チップの総面積よりも小さい回路パネルの面積に実装することができる。或る特定の積層型チップ構成は、例えば、その開示を引用することにより本明細書の一部をなすものとする、上述した米国特許第5,148,265号、米国特許第5,679,977号及び米国特許第5,347,159号の或る特定の実施形態に開示されている。同様に引用することにより本明細書の一部をなすものとする米国特許第4,941,033号は、チップが積み重なり合って、チップに関連するいわゆる「配線フィルム」上の導体によって互いに相互接続される構成を開示している。

【0007】

従来のチップコンタクトには、コンタクトにおける非最適な応力分布と、例えば半導体チップとチップが結合される構造体との間の熱膨張係数(CTE)の不整合と、のために、信頼性の問題がある可能性がある。例えば、半導体チップの面において導電性コンタクトが比較的薄くかつ堅い誘電材料によって絶縁されている場合、コンタクトにおいて著しい応力が存在する可能性がある。さらに、半導体チップがポリマ基板の導電性素子に結合されている場合、チップと基板のCTEがより高い構造との間の電気的接続が、CTE不整合のために応力を受けることになる。

【0008】

10

20

30

40

50

チップのいかなる物理的構成においても、サイズは重要な考慮事項である。チップのより小型の物理的構成に対する要求は、携帯型電子デバイスの急速な発展により、更に強くなっている。単に例として、一般に「スマートフォン」と呼ばれるデバイスは、携帯電話の機能を、強力なデータプロセッサ、メモリ、並びに全地球測位システム受信機、電子カメラ及びローカルエリアネットワーク接続等の補助デバイスを、高解像度ディスプレイ及び関連する画像処理チップと一体化している。こうしたデバイスは、完全なインターネット接続、最大解像度の映像を含むエンターテイメント、ナビゲーション、電子銀行等の機能を、全てポケットサイズのデバイスで提供することができる。複雑な携帯型デバイスでは、多数のチップを小さい空間に詰め込む必要がある。さらに、チップのうちの幾つかは、一般に「I/O」と呼ばれる多くの入出力接続を有している。これらのI/Oを、他のチップのI/Oと相互接続しなければならない。相互接続は、短くあるべきであり、信号伝播遅延を最小限にするために低インピーダンスであるべきである。相互接続を形成するコンポーネントは、アセンブリのサイズを大幅に増大させるべきではない。同様の必要性は、例えばインターネット検索エンジンで使用されるもののようなデータサーバにおける用途等の、他の用途でも発生する。例えば、複雑なチップ間に多数の短い低インピーダンス相互接続を提供する構造により、検索エンジンの帯域幅を増大させ、その電力消費量を低減することができる。10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

20

半導体コンタクト形成及び相互接続において進歩があったにも関わらず、電気的相互接続の信頼性を向上させるとともに半導体チップのサイズを最小限にするために、依然として改善が必要である。本発明のこれらの属性は、以下に説明するように超小型電子パッケージの構造によって達成される。

#### 【課題を解決するための手段】

#### 【0010】

30

本発明の一態様によれば、超小型電子ユニットは、基板及び導電性素子を備えることができる。基板は、10 ppm / 未満のCTEと、基板を通って延在していない凹部を有する主面と、凹部内に配置された弾性係数が10 GPa未満の材料と、を有することができる。導電性素子は、凹部の上に重なりかつ基板によって支持されるアンカー部分から延在している、接合部分を備えることができる。接合部分を、超小型電子ユニットの外部のコンポーネントに接続するために、主面において少なくとも部分的に露出させることができる。

#### 【0011】

一実施の形態では、前記基板は、7 ppm / 未満のCTEを有することができる。特定の実施の形態では、前記接合部分は、前記超小型電子ユニットの動作、製造又は試験中に存在する可能性がある応力等の、該接合部分に対する応力を低減するように、移動可能とすることができます。例示的な実施の形態では、前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなることができる。一実施の形態では、前記基板は、複数の能動半導体デバイスを備えることができ、前記導電性素子は、前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続することができる。特定の実施の形態では、前記凹部内に配置された前記材料は、ポリイミド、シリコーン及びエポキシからなる群から選択された少なくとも1つの材料を含むことができる。40

#### 【0012】

例示的な実施の形態では、前記凹部は、前記基板を通って延在していなくてもよい。一実施の形態では、前記接合部分は、前記基板の前記主面に対して実質的に平行な方向に延在することができる。特定の実施の形態では、前記アンカー部分及び前記接合部分は同じ方向に延在することができる。例示的な実施の形態では、前記導電性素子は、前記基板の前記主面とは反対側の第2の面に向かって延在している導電性ビアに電気的に結合することができる。一実施の形態では、前記導電性ビアは前記第2の面において露出することができる50

できる。特定の実施の形態では、前記導電性ピアは、前記基板において前記第2の面から前記主面まで延在している孔(hole)内に延在することができる。

#### 【0013】

一実施の形態では、前記孔は、前記主面から前記第2の面に向かって延在している第1の開口部(opening)と、該第1の開口部から前記第2の面まで延在している第2の開口部と、を含むことができる。前記第1の開口部及び前記第2の開口部の内面は、前記主面に對してそれぞれ第1の方向及び第2の方向に延在して、實質的な角度を画定することができる。例示的な実施の形態では、積層アセンブリが、少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備えることができ、前記第2の超小型電子ユニットは、前記第1の超小型電子ユニットと積層されており、該積層アセンブリ内の前記第1の超小型電子ユニットの前記基板は、前記第2の超小型電子ユニットの基板と電気的に接続されている。特定の実施の形態では、前記積層アセンブリは、前記第1の超小型電子ユニットの前記接合部分と前記第2の超小型電子ユニットの導電性素子とに電気的に結合されている導体塊を更に具備することができる。10

#### 【0014】

本発明の別の態様によれば、超小型電子ユニットは、基板及び導電性素子を備えることができる。基板は、10 ppm / 未満のCTEと、基板を通って延在していない凹部を有する主面と、凹部内に配置された弾性係数が10 GPa未満の材料と、を有することができる。導電性素子は、基板に対して固定されたアンカー部分と、少なくとも部分的に凹部の上に重なる接合部分と、接合部分からアンカー部分まで下方に延在する接続部分と、を有することができる。接合部分は、アンカー部分から離れる方向に延在することができ、超小型電子ユニットの外部のコンポーネントに接続するために主面において露出することができます。接続部分は、凹部の内面の輪郭に沿わない輪郭を有することができる。20

#### 【0015】

例示的な実施の形態では、前記基板は、7 ppm / 未満のCTEを有することができる。一実施の形態では、前記接合部分は、前記超小型電子ユニットの動作、製造又は試験中に存在する可能性がある応力等の、該接合部分に対する応力を低減するように、移動可能とすることができる。特定の実施の形態では、前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなることができる。一実施の形態では、前記基板は、複数の能動半導体デバイスを備えることができ、前記導電性素子は、前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続することができる。例示的な実施形態では、前記接続部分は凹部内へ延在することができる。30

#### 【0016】

特定の実施形態では、前記導電性素子は、前記基板の前記主面とは反対側の第2の面に向かって延在している導電性ピアに電気的に結合することができる。一実施形態では、導電性ピアは前記第2の面において露出することができる。例示的な実施形態では、前記導電性ピアは、前記基板において前記第2の面から前記主面まで延在している孔内に延在することができる。特定の実施形態では、前記孔は、前記主面から前記第2の面に向かって延在している第1の開口部と、該第1の開口部から前記第2の面まで延在している第2の開口部と、を含むことができる。前記第1の開口部及び前記第2の開口部の内面は、前記主面に對してそれぞれ第1の方向及び第2の方向に延在して、實質的な角度を画定することができる。一実施形態では、前記アンカー部分は、前記孔の内面の輪郭に沿う輪郭を有することができる。例示的な実施形態では、前記接合部分は内部穴(aperture)を画定することができる。40

#### 【0017】

一実施形態では、前記穴は、前記接合部分を通って前記接続部分内に延在することができる。特定の実施形態では、前記穴の少なくとも一部を、誘電材料で充填することができる。例示的な実施形態では、積層アセンブリが、少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備えることができ、前記第2の超小型電子ユニットは、前記第1の超小型電子ユニットと積層されており、該積層アセンブリ内の前記第1の超小型50

電子ユニットの前記基板は、前記第2の超小型電子ユニットの基板と電気的に接続されている。特定の実施の形態では、前記積層アセンブリ前記第1の超小型電子ユニットの前記接合部分と前記第2の超小型電子ユニットの導電性素子とに電気的に結合されている導体塊を更に具備することができる。

【0018】

本発明の更に別の態様によれば、超小型電子ユニットを製造する方法が、CTEが10 ppm/未満である基板の正面に支持される導電性素子を形成するステップと、前記正面から、少なくとも導電性素子の接合部分を支持する材料を除去するステップであって、それにより前記基板を通じて延在しない凹部を形成する、除去するステップと、弾性係数が10 GPa未満である材料を前記凹部内に堆積させるステップと、を含むことができる。前記接合部分は、基板によって支持されなくてもよく、一方で、前記接合部分に隣接する前記導電性素子のアンカー部分は前記基板によって支持することができる。前記接合部分は、前記超小型電子ユニットの外部のコンポーネントに接続するために、前記基板の正面において少なくとも部分的に露出することができる。

10

【0019】

一実施形態では、前記基板は、7 ppm/未満のCTEを有することができる。例示的な実施形態では、前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなることができる。特定の実施形態では、前記基板は、複数の能動半導体デバイスを含むことができ、前記導電性素子を形成する前記ステップは、前記導電性素子を、前記複数の半導体デバイスのうちの少なくとも1つに電気的に接続することができる。例示的な実施形態では、導電性素子を形成するステップを、前記接合部分が前記正面に対して実質的に平行に配置されるように行うことができる。一実施形態では、本方法は、基板から材料を除去し、前記正面から該正面とは反対側の基板の第2の面まで延在する孔を形成するステップと、前記孔内に延在する導電性ビアを、該導電性ビアが前記導電性素子に電気的に結合されかつ前記第2の面向かって延在するように形成するステップと、を更に含むことができる。

20

【0020】

特定の実施形態では、前記基板から材料を除去し、孔を形成する前記ステップは、前記正面から前記第2の面向かって延在する第1の開口部と、該第1の開口部から前記第2の面まで延在する第2の開口部と、を形成するステップを含むことができる。前記第1の開口部及び前記第2の開口部の内面は、前記正面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定することができる。一実施形態では、少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備える積層アセンブリを製造する方法は、前記第1の超小型電子ユニットの前記基板を前記第2の超小型電子ユニットの基板に電気的に接続するステップを更に含むことができる。

30

【0021】

本発明の更に別の態様によれば、超小型電子ユニットを製造する方法が、CTEが10 ppm/未満である基板から材料を除去するステップであって、それにより、該基板の正面から、該正面とは反対側の第2の面まで延在する孔を形成する、基板から材料を除去するステップと、前記正面の上方に延在しあつ該正面に支持される接合部分と、前記基板に対して固定されたアンカー部分と、前記接合部分から前記アンカー部分まで下方に延在する接続部分と、を有する導電性素子形成するステップと、前記正面から、少なくとも前記導電性素子の接合部分を支持する材料を除去するステップであって、それにより、凹部を、前記接合部分が少なくとも部分的に該凹部の上に重なるように形成する、前記正面から材料を除去するステップと、弾性係数が10 GPa未満である材料を前記凹部内に堆積させるステップと、を含むことができる。前記接続部分の表面は、前記孔の内面の輪郭に沿う輪郭を有することができる。前記接続部分の前記表面の輪郭は、前記凹部の内面の輪郭に沿わなくてもよい。前記接合部分は、前記超小型電子ユニットの外部のコンポーネントに接続するために、前記基板の前記正面において少なくとも部分的に露出することができる。

40

50

## 【0022】

特定の実施形態では、基板は、7 ppm / 未満のCTEを有することができる。例示的な実施形態では、前記超小型電子ユニットを製造する方法は、前記導電性素子を形成する前記ステップの前に、前記孔内に延在しかつ前記第2の面に向かって延在する導電性ピアを形成するステップを更に含むことができ、それにより、前記導電性素子を形成する前記ステップは、該導電性素子を前記導電性ピアに電気的に結合する。一実施形態では、前記導電性素子を形成する前記ステップを、前記接合部分が前記接続部分に対して中心合わせされないように行うことができる。特定の実施形態では、前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択された1つの材料からなることができる。例示的な実施形態では、前記基板は、複数の能動半導体デバイスを備えることができ、前記導電性素子を形成する前記ステップは、該導電性素子を前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続することができる。一実施形態では、前記導電性素子を形成する前記ステップを、前記接合部分が内部穴を画定するよう行うことができる。特定の実施形態では、前記導電性素子を形成する前記ステップを、前記穴が前記接合部分を通って前記接続部分内へ延在するよう行うことができる。10

## 【0023】

一実施形態では、前記超小型電子ユニットを製造する方法は、前記穴の少なくとも一部分内に誘電材料を堆積させるステップを更に含むことができる。特定の実施形態では、前記基板から材料を除去する前記ステップであって、それにより孔を形成する前記ステップは、前記主面から前記第2の面に向かって延在する第1の開口部と、該第1の開口部から前記第2の面まで延在する第2の開口部と、を形成するステップを含むことができる。前記第1の開口部及び前記第2の開口部の内面は、前記主面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定することができる。例示的な実施形態では、少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備える積層アセンブリを製造する方法は、前記第1の超小型電子ユニットの前記基板を前記第2の超小型電子ユニットの基板に電気的に接続するステップを更に含むことができる。20

## 【0024】

本発明の更なる態様は、他の電子デバイスとともに、本発明の上述した態様による超小型電子構造体、本発明の上述した態様による複合チップ、又は両方を組み込んだシステムを提供する。例えば、本システムを、携帯型ハウジングとすることができる単一ハウジング内に配置することができる。本発明のこの態様の好ましい実施の形態によるシステムを、同等の従来のシステムよりも小型にすることができる。30

## 【0025】

本発明の更なる態様は、本発明の上述した態様による複数の超小型電子アセンブリを備えることができるモジュールを提供する。各モジュールは、前記超小型電子アセンブリの各自にかつ各自から信号を伝送するための共通の電気的インターフェースを有することができる。

## 【図面の簡単な説明】

## 【0026】

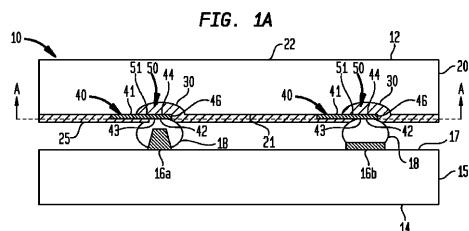

【図1A】本発明の一実施形態によるコンタクト構造体を有する積層アセンブリを示す側面図である。40

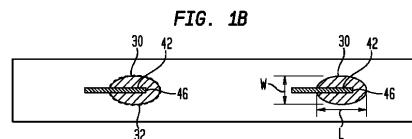

【図1B】線A-Aに沿って取り出された図1Aの積層アセンブリの対応する下から上への断面図の一実施形態の図である。

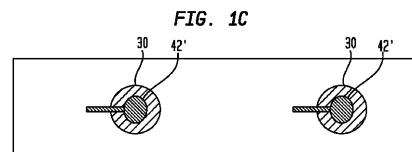

【図1C】線A-Aに沿って取り出された図1Aの積層アセンブリの対応する下から上への断面図の別の実施形態の図である。

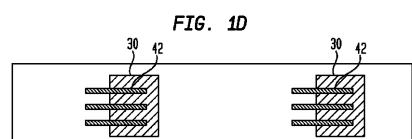

【図1D】線A-Aに沿って取り出された図1Aの積層アセンブリの対応する下から上への断面図の更に別の実施形態の図である。

【図2A】図1Aに示す本発明の実施形態による製造の段階を示す断面図である。

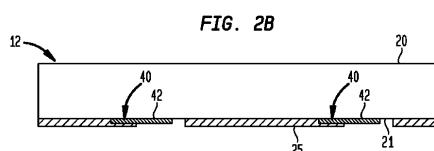

【図2B】図1Aに示す本発明の実施形態による製造の段階を示す断面図である。

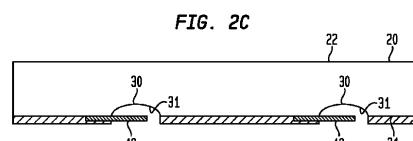

【図2C】図1Aに示す本発明の実施形態による製造の段階を示す断面図である。50

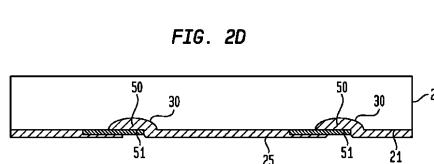

【図 2 D】図 1 A に示す本発明の実施形態による製造の段階を示す断面図である。

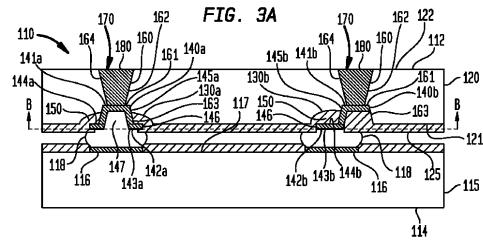

【図 3 A】本発明の一実施形態によるコンタクト構造体を有する積層アセンブリを示す側面図である。

【図 3 B】線 B - B に沿って取り出された図 3 A の積層アセンブリの対応する下から上への断面図の一実施形態の図である。

【図 3 C】線 B - B に沿って取り出された図 3 A の積層アセンブリの対応する下から上への断面図の別の実施形態の図である。

【図 3 D】線 B - B に沿って取り出された図 3 A の積層アセンブリの対応する下から上への断面図の更に別の実施形態の図である。

【図 4 A】図 3 A に示す本発明の実施形態による製造の段階を示す断面図である。 10

【図 4 B】図 3 A に示す本発明の実施形態による製造の段階を示す断面図である。

【図 4 C】図 3 A に示す本発明の実施形態による製造の段階を示す断面図である。

【図 4 D】図 3 A に示す本発明の実施形態による製造の段階を示す断面図である。

【図 4 E】図 3 A に示す本発明の実施形態による製造の段階を示す断面図である。

【図 5】本発明による、チップに電気的に接続されたパッドを有する基板の上面斜視図である。

【図 6】本発明の別の実施形態によるコンタクト構造体を有する基板を示す側断面図である。

【図 7】本発明の 1 つの実施形態によるモジュールの概略図である。

【図 8】本発明の 1 つの実施形態によるシステムの概略図である。 20

#### 【発明を実施するための形態】

##### 【0027】

図 1 A を参照すると、本発明の一実施形態による積層型超小型電子アセンブリ 10 は、第 1 の超小型電子素子 12 及び第 2 の超小型電子素子 14 を備えている。幾つかの実施形態では、第 1 の超小型電子素子 12 及び第 2 の超小型電子素子 14 を、半導体チップ、ウェハ、誘電体基板等とすることができます。例えば、第 1 の超小型電子ユニット 12 及び第 2 の超小型電子ユニット 14 の一方又は両方は、メモリ記憶素子を備えることができる。本明細書で用いるとき、「メモリ記憶素子」は、電気的インターフェースによってデータを伝送するため等のために、メモリセルにデータを格納しつつそこからデータを検索するように使用可能な回路とともにアレイで配置された多数のメモリセルを指す。 30

##### 【0028】

第 1 の超小型電子ユニット 12 は、基板 20 であって、主面 21 から部分的にその基板を通って主面とは反対側の第 2 の面 22 に向かって延在している凹部 30 を有する基板 20 と、導電性素子 40 であって、基板によって支持されるアンカー部分 41、アンカー部分から延在している接合部分 42 であって、少なくとも部分的に凹部 30 の上に重なり、かつ第 1 の超小型電子ユニットの外部のコンポーネントと相互接続するために主面において少なくとも部分的に露出している接合部分 42、及び端部分 46 を有する導電性素子 40 と、を備えている。図示するように、端部分 46 は、接合部分 42 の端部に位置している。誘電体領域 50 が、少なくとも凹部 30 内の内面 31 の上に重なっている。

##### 【0029】

図 1 A において、主面 21 に対して平行な方向を、本明細書では「水平」方向又は「横」方向と呼ぶのに対し、表面に直交する方向を、本明細書では上方向又は下方向と呼び、本明細書ではまた「垂直」方向とも呼ぶ。本明細書で言及する方向は、言及する構造体の基準系にある。したがって、これらの方向は、標準の基準系又は重力基準系に対する任意の向きに位置することができる。1 つの特徴が「面の上方」に別の特徴よりも高い高さに配置されていると言う場合、それは、その 1 つの特徴が、その面から離れる同じ直交方向において他方の特徴よりも遠い距離にあることを意味する。逆に、1 つの特徴が「面の上方」に別の特徴よりも低い高さに配置されていると言う場合、それは、その 1 つの特徴が、その面から離れる同じ直交方向において他方の特徴よりも近い距離にあることを意味する。 40

## 【0030】

基板20は、好ましくは、熱膨張係数（「CTE」）が $10 \times 10^{-6}$ /（すなわち $\text{ppm}/$ ）未満である。特定の実施形態では、基板20は、 $7 \times 10^{-6}$ /（すなわち $\text{ppm}/$ ）未満の熱膨張係数（「CTE」）を有することができる。基板20は、好ましくは、本質的に半導体、ガラス又はセラミック等の材料からなる。基板20が、シリコン等の半導体から作製される実施形態では、複数の能動半導体デバイス（例えばトランジスタ、ダイオード等）を、主面21又は第2の面22及び/又はその下方に位置する基板20の能動半導体領域に配置することができる。基板20の主面21と第2の面22との間の厚さは、通常、 $200 \mu\text{m}$ 未満であり、著しく小さく、例えば $130 \mu\text{m}$ 、 $70 \mu\text{m}$ 又は更にはそれより小さくすることができる。

10

## 【0031】

基板20は、主面21と少なくとも1つの導電性素子40との間に配置された誘電体層を更に備えることができる。誘電体層が、第2の面22の上に重なることができる。こうした誘電体層は、基板20から導電性素子を電気的に絶縁することができる。これらの誘電体層のうちの一方又は両方を、第1の超小型電子ユニット12の「パッシベーション層」と呼ぶことができる。誘電体層は、無機誘電材料若しくは有機誘電材料又は両方を含むことができる。誘電体層は、電着したコンフォーマルコーティング又は他の誘電材料、例えば光画像形成可能なポリマ材料、例えばはんだマスク材料を含むことができる。

## 【0032】

超小型電子素子12は、基板20の主面21において露出している1つ又は複数の導電性素子40を備えることができる。各導電性素子40の接合部分42を、第2の超小型電子素子14のように、第1の超小型電子素子12の外部のコンポーネントと相互接続するために主面21において露出させることができる。特に図には示さないが、基板20の能動半導体デバイスを、接合部分42に導電接続することができる。したがって、能動半導体デバイスを、基板20の1つ又は複数の誘電体層内に又はその上方に延在している、組み込まれた配線を介して、導電的にアクセス可能とすることができる。導電性素子40（及び本明細書に記載する他の導電性素子のうちの任意のもの）を、例えば銅又は金を含む任意の導電性金属から作製することができる。

20

## 【0033】

例えば図1Cに図示するように、接合部分42'は、導電性ボンドパッド、例えば薄い平坦な部材の下面図形状を有することができる。各接合部分42は、例えば、図1Bに示すような矩形トレース形状、図1Cに示すように円形パッド形状、橢円形状、正方形形状、三角形状、又はより複雑な形状を含む任意の下面図形状を有することができる。他の実施形態では、接合部分42を、例えば導電性ポストを含む他の任意のタイプの導電性コンタクトとすることができる。

30

## 【0034】

接合部分42を、凹部30と位置合せすることができ、凹部によって画定される基板20の領域内に完全に又は部分的に配置することができる。図1Aに見られるように、接合部分42は、凹部30によって画定される領域内に完全に配置されている。図示するように、接合部分42の上面43によって画定される平面は、基板20の主面21によって画定される平面に対して実質的に平行である。図示するように、接合部分42の底面44は、基板20の主面21によって画定される平面に位置している。他の実施形態では、接合部分42の底面44を、主面21によって画定される平面の上方又は下方に配置することができる。導電性素子40の端部分46は、基板20によって支持されておらず、それにより、端部分を、アンカー部分41に対して片持ちにすることができる。主面21の上に重なりかつ誘電体領域50に隣接して位置する接合部分42のこうした支持されていない端部分46は、支持されているアンカー部分41に対して自由に移動することができ、それにより、接合部分42は片持ち梁として機能することができる。

40

## 【0035】

本開示において用いられるとき、導電性素子が基板又は基板の面の上に重なる誘電体素

50

子の面「において露出して」いるという記述は、導電性素子が、誘電体素子の表面に直交する方向において、誘電体素子の外側から誘電体素子の表面に向かって移動している理論的な点に接触することができることを示す。したがって、誘電体素子の表面において露出している端子又は他の導電性素子は、こうした表面から突出することができるか、こうした表面と同一平面とすることができるか、又はこうした表面に対して凹状とし、誘電体における孔又は窪みを通して露出させることができる。

#### 【0036】

導電性素子を形成するために使用可能な本質的に任意の技法を使用して、本明細書に記載する導電性素子を形成することができるが、2010年7月23日に出願された、本願と同一の所有者によって所有される米国特許出願第12/842,669号においてより詳細に説明されているような特定の技術を採用することができる。この特許出願は、参照することにより本明細書の一部をなすものとする。こうした技法は、例えば、表面をレーザにより、又はフライス加工若しくはサンドブラスト加工等の機械的プロセスにより、導電性素子が表面の他の部分とは異なるように形成されるべきである経路に沿って表面のそれらの部分を処理するように、選択的に処理することを含むことができる。例えば、レーザ又は機械的プロセスを使用して、特定の経路のみに沿って表面から犠牲層等の材料を取り除き又は除去し、それによりその経路に沿って延在する溝を形成することができる。そして、溝内に触媒等の材料を堆積させることができ、溝内に1つ又は複数の金属層を堆積させることができる。

#### 【0037】

導電性素子40の端部分46は、図では、凹部30の外側境界32(図1B)を越えて横方向に(すなわち、基板20の主面21に対して平行な方向に)延在していないものとして示されている。本明細書に開示する実施形態のうちの任意のものにおいて、導電性素子の端部分及び/又は接合部分は、凹部の外側境界を越えて横方向に延在することができる。一実施形態では、接合部分の端部を、対応する凹部の外側境界を越えて横方向に延在する導電性トレース(図示せず)に結合することができるが、接合部分を、依然として、後述するように対応する基板に対して移動可能とすることができます。

#### 【0038】

凹部30は、主面21から部分的に基板20を通って第2の面22に向かって延在している。凹部30の内面31は、主面21から基板20を通って任意の角度で延在することができる。好ましくは、内面31は、主面21から、主面21によって画定される水平面に対して0度と90度との間の角度で延在している。内面31は、一定の勾配又は可変の勾配を有することができる。例えば、主面21によって画定される水平面に対する内面31の角度又は勾配は、内面31が第2の面22に向かって深く貫入するに従い、大きさが減少する(すなわち、正又は負の大きさが小さくなる)ことができる。

#### 【0039】

凹部30は、例えば、図1Bに示すような橢円形、又は図1Cに示すような円形を含む、任意の底面図形状を有することができる。図1Bに示す実施形態では、凹部30は、主面21に沿って第1の横方向に幅Wを有し、凹部は、第1の横方向に対して横切る主面に沿った第2の横方向に長さLを有しており、長さは幅より大きい。幾つかの例では、凹部30は、特に、例えば円柱、立方体、角柱又は円錐台形状を含む、任意の3次元形状を有することができる。

#### 【0040】

特定の実施形態では、図1Dに示すように、凹部30を矩形溝とし、複数の接合部分42が少なくとも部分的に凹部の上に重なるようにすることができます。任意の数の接合部分42が单一の凹部30の上に重なることができ、接合部分を、单一の凹部の上に重なる任意の幾何学的構成で配置することができる。例えば、図1Dに示すように、3つの接合部分42を、单一の凹部30の上に重なる共通軸に沿って配置することができる。

#### 【0041】

図示する実施形態では、誘電体領域50は、誘電体領域の輪郭が凹部の輪郭(すなわち

10

20

30

40

50

、凹部の内面 3 1 の形状)に沿うように凹部 3 0 を充填する。誘電体領域 5 0 は、基板 2 0 に対して優れた誘電体分離を提供することができる。誘電体領域 5 0 をコンプライアントとし、弾性係数及び厚さを、その係数及び厚さの積がコンプライアンシ(compliancy)を提供するように十分低くかつ厚くすることができる。好ましくは、導電性素子 4 0 の接合部分 4 2 は、少なくとも部分的に誘電体領域 5 0 の上に重なる。コンプライアントな誘電体領域 5 0 により、導電性素子 4 0 の接合部分 4 2 が、接合部分に外部負荷が加えられたとき、基板 2 0 及びその上に支持されている導電性素子のアンカー部分 4 1 に対して幾分か撓曲又は移動することができる。そのように、第 1 の超小型電子ユニット 1 2 の接合部分 4 2 と第 2 の超小型電子素子 1 4 の端子との間の結合は、第 1 の超小型電子ユニットと第 2 の超小型電子ユニットとの間の熱膨張係数(「CTE」)の不整合による熱歪みに対してより優れた耐性を有することができる。10

#### 【0042】

本明細書において導電性素子の接合部分に関連して用いるとき、「移動可能」とは、接合部分が、それに加えられる外部負荷によって基板の主面に対して、以下のような程度まで変位することができることを意味するものとし、すなわち、こうした変位がない場合に導電性素子との電気的接続において存在することになる、超小型電子ユニットの動作、製造又は試験中に熱膨張差によってもたらされるもの等の機械的応力を、変位が相当に緩和又は低減する程度である。

#### 【0043】

誘電体領域 5 0 の厚さとその弾性係数との積によって提供されるコンプライアンシの程度を、第 1 の超小型電子ユニット 1 2 と、第 1 の超小型電子ユニットが接合部分を介して実装される第 2 の超小型電子ユニット 1 4 と、の間の熱膨張不整合に起因して接合部分 4 2 に加えられる歪みを補償するのに十分とすることができる。誘電体領域 5 0 の露出した外面 5 1 とこうした第 2 の超小型電子ユニット 1 4 との間にアンダーフィル(図示せず)を設けて、CTE 不整合による熱応力を向上させることができる。20

#### 【0044】

図示する実施形態では、誘電体領域 5 0 の外面 5 1(図 1A)は、基板 2 0 の主面 2 1 によって画定される平面内に位置している。代替的に、誘電体領域 5 0 の外面 5 1 は、基板 2 0 の主面 2 1 によって画定される平面の上方に延在することができ、又は、誘電体領域の外面を、基板の主面によって画定される平面の下方に窪ませることができる。30

#### 【0045】

誘電体層 2 5 が、基板 2 0 の主面 2 1 と接合部分 4 2 ではない導電性素子 4 0 の部分との上に重なることにより、基板と接合部分ではない導電性素子の部分とに対して優れた誘電体分離を提供することができる。誘電体層 2 5 は、無機誘電材料若しくは有機誘電材料又は両方を含むことができる。特定の実施形態では、誘電体領域 2 5 は、誘電体領域 5 0 と同じコンプライアント誘電材料を含むことができる。例示的な実施形態では、誘電体層 2 5 を、誘電体領域 5 0 と連続して形成することができる。

#### 【0046】

第 2 の超小型電子素子 1 4 は、基板 1 5 と、第 1 の超小型電子ユニット 1 2 の接合部分 4 2 と相互接続するために基板の主面 1 7 において少なくとも部分的に露出している導電性コンタクト 1 6 a 及び 1 6 b と、を備えることができる。第 1 の超小型電子ユニット 1 2 に接合部分 4 2 を設け、第 2 の超小型電子素子 1 4 に裏面導電性コンタクト 1 4 を設けることにより、複数の超小型電子ユニットを上下に積層して、積層超小型電子アセンブリ 1 0 を形成することができる。こうした配置では、接合部分 4 2 は、導電性コンタクト 1 6 a 及び 1 6 b と位置合せされる。40

#### 【0047】

図 1 A に示すように、導電性コンタクト 1 6 a は導電性ポストである。導電性ポスト 1 6 a は、任意のタイプの導電性ポストとすることができます、円錐台形状を含む任意の形状を有することができる。各導電性ポスト 1 6 a の基部及び先端は、実質的に円形であるか、又は異なる形状、例えば橢円形を有することができる。2010年7月8日に出願された50

、本願と同一の所有者によって所有される米国特許出願第12/832,376号に示し記載されているように、導電性ポストの他の例を使用することができる。導電性コンタクト16bは、導電性パッドとして示されている。導電性パッド16bは、円形、正方形、橢円形、矩形又はより複雑な形状を含む、任意の形状を有することができる。

#### 【0048】

第1の超小型電子ユニット12と第2の超小型電子ユニット14との間の接続は、導体塊18を介することができる。基板20の主面21の誘電体層25及び誘電体領域50と基板15の主面17の上に重なる誘電体層(例えばパッシベーション層)とは、相互接続が設けられる場所を除き、第1の超小型電子ユニット12と第2の超小型電子ユニット14との間に電気的絶縁を提供することができる。

10

#### 【0049】

導体塊18は、比較的溶融温度が低い可溶金属、例えば、はんだ、錫、又は複数の金属を含む共晶混合物(eutectic mixture)を含むことができる。代替的に、導体塊18は、湿潤性金属、例えば銅、又ははんだ若しくは別の可溶金属よりも溶融温度の高い他の貴金属若しくは非貴金属を含むことができる。こうした湿潤性金属を、対応する特徴、例えば第2の超小型電子ユニット14等の相互接続素子の可溶金属の特徴と接合して、第1の超小型電子ユニット12をこうした相互接続素子に外部で相互接続することができる。特定の実施形態では、導体塊18は、媒体内に散在する導電性材料、例えば導電性ペースト、例えば金属充填ペースト、はんだ充填ペースト、又は等方性導電性接着剤若しくは異方性導電性接着剤を含むことができる。

20

#### 【0050】

ここで、図2A～図2Dを参照して、超小型電子アセンブリ10(図1A～図1D)を製造する方法について説明する。図2Aに示すように、第1の超小型電子ユニット12は、基板20と主面21の上に重なる1つ又は複数の導電性素子40とを備えている。導電性素子40を、パッシベーション層(図示せず)等の誘電体層によって基板20から絶縁することができる。

#### 【0051】

図2Bに示す製造の段階では、誘電体層25が、基板20の主面21の上に形成され、主面の残りの部分を保存することが望まれる場所でエッチングマスク層としての役割を果たす。例えば、誘電体層25を、堆積し主面21の一部のみを覆うようにパターニングされる、光画像形成可能層、例えばフォトレジスト層とすることができます、その後、時限エッチングプロセスを行うことによって凹部30を形成することができる。各導電性素子40の接合部分42を、第1の超小型電子ユニット12の外部のコンポーネントに接続するために、主面21において少なくとも部分的に露出した(すなわち、誘電体層25によって覆わない)ままにすることができる。

30

#### 【0052】

様々な方法を使用して、誘電体層25を形成することができる。一例では、流動性誘電材料を、基板20の主面21に施すことができ、その後、流動性材料は、「スピンドコーディング」操作中に、主面にわたってより均一に分散され、次いで、加熱を含むことができる乾燥サイクルが続く。別の例では、誘電材料の熱可塑性フィルムを、主面21に施すことができ、その後、アセンブリは加熱されるか、又は真空環境で、すなわち周囲圧力未満の環境に配置されて加熱される。別の例では、蒸着を用いて、誘電体層25を形成することができる。

40

#### 【0053】

更に別の例では、基板20を誘電体堆積浴(bath)に浸漬して、コンフォーマル誘電体コーティング又は誘電体層25を形成することができる。本明細書において用いられるとき、「コンフォーマルコーティング」は、誘電体層25が主面21の輪郭に沿う場合等、コーティングされている表面の輪郭に沿う特定の材料のコーティングである。例えば電気泳動堆積法又は電解堆積法を含む電気化学堆積法を使用して、コンフォーマル誘電体層25を形成することができる。

50

**【 0 0 5 4 】**

一例では、電気泳動堆積法を用いてコンフォーマル誘電体コーティングを形成することができ、それにより、コンフォーマル誘電体コーティングは、アセンブリの露出した導電性面及び半導性面上にのみに堆積する。堆積中、半導体デバイスウェハは所望の電位で保持され、浴を異なる望ましい電位で保持するために、浴内に電極が浸漬される。そして、限定されないが主面 21 に沿って、導電性又は半導性である基板の露出面に、電着したコンフォーマル誘電体層 25 を形成するために十分な時間、アセンブリは、適切な条件下で浴内に保持される。電気泳動堆積は、それによってコーティングされるべき表面と浴との間に十分に強力な電場が維持される限り発生する。電気泳動的に堆積したコーティングは、その堆積物のパラメータ、例えば電圧、濃度等によって決まる或る厚さに達した後に堆積を停止するという点で自己限定期である。

10

**【 0 0 5 5 】**

電気泳動堆積は、アセンブリの導電性及び / 又は半導性外面に連続的かつ均一な厚さのコンフォーマルコーティングを形成する。加えて、電気泳動コーティングは、その誘電(非導電)特性に起因して、主面 21 の上に重なる残りのパッシベーション層の上に生じないように堆積することができる。言い換えれば、電気泳動堆積の特性は、その誘電特性が与えられると、誘電材料の層に十分な厚さがある場合、電気泳動堆積が、導体の上に重なる誘電材料の層の上に生じないということである。通常、電気泳動堆積は、約 10 ミクロンを超える数 10 ミクロンまでの厚さの誘電体層の上では発生しない。コンフォーマル誘電体層 25 を、陰極エポキシ堆積前駆体から形成することができる。代替的に、ポリウレタン又はアクリル堆積前駆体を使用することができる。以下の表 1 に、種々の電気泳動コーティング前駆体組成及び供給業者を列挙する。

20

**【 0 0 5 6 】**

【表1】

| 電気泳動コーティング名                   | POWERCRON 645       | POWERCRON 648      | CATHOGUARD 325     |

|-------------------------------|---------------------|--------------------|--------------------|

| <b>製造業者</b>                   |                     |                    |                    |

| MFG                           | PPG                 | PPG                | BASF               |

| タイプ                           | 陰極                  | 陰極                 | 陰極                 |

| ポリマ基材                         | エポキシ                | エポキシ               | エポキシ               |

| 住所                            | ペンシルバニア州ピット<br>バーグ  | ペンシルバニア州ピット<br>バーグ | ミシガン州 サウスフィー<br>ルド |

| <b>適用データ</b>                  |                     |                    |                    |

| PB/Pf フリー                     | PB フリー              | PB 又は Pf フリー       | PB フリー             |

| 有害大気汚染物質(HAPs),<br>G/L        |                     | 60-84              | 適合                 |

| 揮発性有機化合物(VOC),<br>G/L (マイナス水) |                     | 60-84              | <95                |

| 硬化                            | 20 分/175C           | 20 分/175C          |                    |

| <b>フィルム特性</b>                 |                     |                    |                    |

| 色                             | 黒                   | 黒                  | 黒                  |

| 厚さ、μm                         | 10-35               | 10-38              | 13-36              |

| ペンシル硬度                        |                     | 2H+                | 4H                 |

| <b>浴特性</b>                    |                     |                    |                    |

| 固体、%wt.                       | 20(18-22)           | 20(19-21)          | 17.0-21.0          |

| pH(25C)                       | 5.9(5.8-6.2)        | 5.8(5.6-5.9)       | 5.4-6.0            |

| 導電率(25C)μS                    | 1000-1500           | 1200-1500          | 1000-1700          |

| P/B 比                         | 0.12-0.14           | 0.12-0.16          | 0.15-0.20          |

| 動作温度、C                        | 30-34               | 34                 | 29-35              |

| 時間、秒                          | 120-180             | 60-180             | 120+               |

| 陽極                            | SS316               | SS316              | SS316              |

| 電圧                            |                     | 200-400            | >100               |

| 電気泳動コーティング名                   | ELECTROLAC          | LECTRASEAL DV494   | LECTROBASE 101     |

| <b>製造業者</b>                   |                     |                    |                    |

| MFG                           | MACDERMID           | LVH COATINGS       | LVH COATINGS       |

| タイプ                           | 陰極                  | 陽極                 | 陰極                 |

| ポリマ基材                         | ポリウレタン              | ウレタン               | ウレタン               |

| 住所                            | コネチカット州ウォーター<br>ベリー | 英國バーミンガム           | 英國バーミンガム           |

| <b>適用データ</b>                  |                     |                    |                    |

| PB/Pf フリー                     |                     | PB フリー             | PB フリー             |

| 有害大気汚染物質(HAPs),<br>G/L        |                     |                    |                    |

| 揮発性有機化合物(VOC),<br>G/L (マイナス水) |                     |                    |                    |

| 硬化                            | 20 分/149C           | 20 分/175C          | 20 分/175C          |

| <b>フィルム特性</b>                 |                     |                    |                    |

| 色                             | 透明(+染色)             | 黒                  | 黒                  |

| 厚さ、μm                         |                     | 10-35              | 10-35              |

| ペンシル硬度                        | 4H                  |                    |                    |

| <b>浴特性</b>                    |                     |                    |                    |

| 固体、%wt.                       | 7.0(6.5-8.0)        | 10-12              | 9-11               |

| pH(25C)                       | 5.5-5.9             | 7-9                | 4.3                |

| 導電率(25C)μS                    | 450-600             | 500-800            | 400-800            |

| P/B 比                         |                     |                    |                    |

| 動作温度、C                        | 27-32               | 23-28              | 23-28              |

| 時間、秒                          |                     |                    | 60-120             |

| 陽極                            | SS316               | 316SS              | 316SS              |

| 電圧                            | 40、最大               |                    | 50-150             |

【0057】

別の例では、誘電体層を電解で形成することができる。このプロセスは、電気泳動堆積法に類似しているが、堆積した層の厚さが、それが形成される導電性又は半導性面に近接していることによって制限されない。このように、電解堆積誘電体層を、要件に基づいて選択される厚さになるように形成することができ、処理時間は、達成される厚さの係数で

10

20

30

40

50

ある。

**【 0 0 5 8 】**

その後、図 2 C に示す製造の段階では、基板 2 0 の主面 2 1 から第 2 の面 2 2 に向かって下方に延在する凹部 3 0 を形成することができる。例えば、主面 2 1 の残りの部分を保存することが望まれる場所においてマスク層（例えば、誘電体層 2 5）を形成した後、基板の材料を除去するように基板 2 0 を選択的にエッティングすることにより、凹部 3 0 を形成することができる。凹部 3 0 を、少なくとも接合部分 4 2 を支持する基板 2 0 の材料が除去されるように形成することができる。

**【 0 0 5 9 】**

主面 2 1 から第 2 の面 2 2 に向かって下方に延在している凹部 3 0 の内面 3 1 は、図 2 C に示すように、傾斜させることができ、すなわち主面に対して垂直角（直角）以外の角度で延在することができる。ウェットエッティングプロセス、例えば特に等方性エッティングプロセス及びテーパ刃を使用するのに引きを使用して、傾斜した内面 3 1 を有する凹部 3 0 を形成することができる。特に、レーザアブレーション、機械的フライス加工、化学エッティング、プラズマエッティング、基板 2 0 に向かって微細研磨粒子の噴射を向けることを使用して、傾斜した内面 3 1 を有する凹部 3 0（又は本明細書に記載する他の任意の孔若しくは開口部）を形成することもできる。

**【 0 0 6 0 】**

代替的に、凹部 3 0 の内面は、傾斜している代りに、主面 2 1 から下方に、主面 2 1 に対して実質的に直角に、垂直方向に又は実質的に垂直方向に延在することができる。特に、異方性エッティングプロセス、レーザアブレーション、機械的除去プロセス、例えばフライス加工、超音波加工、基板 2 0 に向かって微細研磨粒子の噴流を向けることを使用して、本質的に垂直な内面を有する凹部 3 0 を形成することができる。

**【 0 0 6 1 】**

その後、図 2 D に示す製造の段階では、凹部 3 0 の内側に誘電体領域 5 0 が形成される。誘電体領域 5 0 は、無機材料、ポリマ材料又は両方を含むことができる。任意選択的に、誘電体領域 5 0 を、その領域の露出した外面 5 1 が、基板 2 0 の主面 2 1 又は誘電体層 2 5 の露出面と同一平面上であるか又は実質的に同一平面上であるように形成することができる。例えば、凹部 3 0 に、例えば分配プロセス又はステンシル印刷プロセスによって自己平坦化誘電体材料を堆積させることができる。別の例では、誘電体領域 5 0 を形成した後に、基板 2 0 の主面 2 1 又は誘電体層 2 5 の露出面に、研削プロセス、ラップ仕上げプロセス又は研磨プロセスを施すことにより、誘電体領域 5 0 の表面を、主面 2 1 又は誘電体層 2 5 の露出した表面に対して平坦化することができる。

**【 0 0 6 2 】**

その後、再び図 1 A を参照すると、第 1 の超小型電子ユニット 1 2 を第 2 の超小型電子ユニット 1 4 の上に積層することができ、それにより、積層超小型電子アセンブリ 1 0 を形成することができる。上述したように、第 1 の超小型電子ユニット 1 2 と第 2 の超小型電子ユニット 1 4 との間の接続は、導体塊 1 8 を介することができる。導体塊 1 8 は、第 1 の超小型電子ユニット 1 2 の接合部分 4 2 と、第 2 の超小型電子ユニット 1 4 の導電性コンタクト 1 6 a 及び 1 6 b と、の間の電気的接続を提供することができる。こうした配置では、接合部分 4 2 は、導電性コンタクト 1 6 a 及び 1 6 b と位置合せされる。

**【 0 0 6 3 】**

ここで図 3 A を参照すると、本発明の別の実施形態による積層超小型電子アセンブリ 1 0 は、第 1 の超小型電子ユニット 1 1 2 及び第 2 の超小型電子ユニット 1 1 4 を備えている。超小型電子ユニット 1 1 2 及び 1 1 4 は、上述した超小型電子ユニット 1 2 及び 1 4 と同様の機能を有することができる。

**【 0 0 6 4 】**

第 1 の超小型電子ユニット 1 1 2 は、基板 1 2 0 であって、主面 1 2 1 から部分的にその基板を通って、主面と反対側の第 2 の面 1 2 2 に向かって延在している凹部 1 3 0 a 及び 1 3 0 b を有する基板 1 2 0 と、導電性素子 1 4 0 a 及び 1 4 0 b であって、各々が、

10

20

30

40

50

基板によって支持されるそれぞれのアンカー部分 141a 又は 141b、少なくとも部分的にそれぞれの凹部 130a 又は 130b の上に重なり、かつ第 1 の超小型電子ユニットの外部のコンポーネントと相互接続するために主面において少なくとも部分的に露出している、それぞれの接合部分 142a 又は 142b、アンカー部分と接合部分との間に延在している 1つ又は複数のそれぞれの接続部分 145a 又は 145b、並びに端部分 146 を有する、導電性素子 140a 及び 140b と、を備えている。図示するように、端部分 146 は、各接合部分 142a 及び 142b の端部に位置している。誘電体領域 150 が、少なくとも凹部 130a 又は 130b 内の内面 131 の上に重なっている。

#### 【0065】

基板 120 は、開口部 130 から第 2 の面 122 まで延在している孔 160 と、孔内においてそれぞれのアンカー部分 141a 又は 141b から第 2 の面まで延在している導電性ビア 170 と、を更に備えている。導電性ビア 170 は、積層超小型電子アセンブリ 110 の外部のコンポーネントと相互接続するために第 2 の面 122 において露出しているコントラクト部分 180 を備えている。

10

#### 【0066】

基板 120 は、図 1A ~ 図 2D を参照して上述した基板 20 と同様の特性を有している。例えば、基板 120 は、好ましくは、CTE が 10 ppm / 未満であり、基板 120 は、好ましくは、本質的に、半導体、ガラス又はセラミック等の材料からなる。基板 120 がシリコン等の半導体から作製される実施形態では、その基板の中に複数の能動半導体デバイスを配置することができる。基板 120 は、主面 121 及び / 又は第 2 の面 122 の上に重なる誘電体層（例えば「パッシベーション層」）を更に備えることができる。

20

#### 【0067】

超小型電子素子 112 は、基板 120 の主面 121 において露出している 1つ又は複数の導電性素子 140a 及び 140b を備えることができる。それぞれの導電性素子 140a 及び 140b の接合部分 142a 及び 142b を、第 2 の超小型電子素子 114 等、第 1 の超小型電子素子 112 の外部のコンポーネントと相互接続するために、主面 121 において露出させることができる。基板 120 における能動半導体デバイスを、接合部分 142a 及び 142b に導電接続することができる。

#### 【0068】

各接合部分 142a 及び 142b は、任意の下面図形状を有することができる。例えば図 3B に示すように、接合部分 142a 及び 142b は、導電性ボンドパッド、例えば薄い平坦な部材、又は導電性ボンドパッドの一部の形状を有することができる。例えば、図 3B 及び図 3C に示す接合部分 142B は、円形の中実下面図形状を有している。図 3B に示す接合部分 142a は、円形の下面図形状を有し、そこを通って穴 147 が延在している。図 3C に示す接合部分セグメント 142a' は合わせて円形下面図形状を有し、穴 147 がそこを通って延在し、間隙 148 が隣接する接合部分セグメントの間に延在している。

30

#### 【0069】

接合部分 142a 及び 142b は、例えば矩形トレース形状又は矩形トレース形状部分を含む、他の下面図形状を有することができる。例えば、図 3D に示す接合部分 142b' は、矩形トレース形状を有している。図 3D に示す接合部分 142a' は、間に穴 147 が位置している矩形トレース形状部分である。接合部分 142a 及び 142b は、代替的に、より複雑な形状を有することができる。他の実施形態では、接合部分 142a 及び 142b を、例えば導電性ポストを含む、他の任意のタイプの導電性コントラクトとすることができる。

40

#### 【0070】

接合部分 142a 及び 142b を、それぞれの凹部 130a 又は 130b と位置合せすることができ、凹部によって画定される基板 120 の領域内に完全に又は部分的に配置することができる。図 3A に見られるように、接合部分 142a 及び 142b は、それぞれの凹部 130a 又は 130b によって画定される領域内に完全に配置されている。図示す

50

るよう、それぞれの接合部分 142a 又は 142b の上面 143a 及び 143b によって画定される平面は、基板 120 の主面 121 によって画定される平面に対して実質的に平行である。図示するように、それぞれの接合部分 142a 又は 142b の底面 144a 及び 144b は、基板 120 の主面 121 によって画定される平面に位置している。他の実施形態では、底面 144a 及び 144b を、主面 121 によって画定される平面の上方又は下方に配置することができる。

#### 【0071】

接続部分 145a 及び 145b は、それぞれの接合部分 142a 又は 142b からそれぞれのアンカー部分 141a 又は 141b まで下方に延在している。接続部分 145a 及び 145b の少なくとも一部は、それぞれの凹部 130a 又は 130b の内面 131 の輪郭に沿わない輪郭を有している。特定の実施形態では、単一トレース形状の接続部分 145b がアンカー部分 141b から接合部分 142b まで延在することができる。代替実施形態では、任意の数の接続部分がアンカー部分から延在することができる。例えば、一実施形態では、接続部分 145a は、図 3B に示す実施形態におけるように、内部穴 147 を備える中空円錐台形状を有することができる。別の実施形態では、4 つの個々の接続部分が、単一のアンカー部分 141a と、図 3C に示す接合部分 142a' 等のそれぞれの接合部分との間に延在することができる。更に別の実施形態では、2 つの個々の接続部分が、単一のアンカー部分 114a と、図 3D に示す接合部分 142a'' 等のそれぞれの接合部分と、の間に延在することができる。接合部分 142a 及び 142b は、好ましくは、それぞれの接続部分 145a 又は 145b に対して中心合わせされておらず、それにより、それぞれの導電性素子 140a 又は 140b の端部分 146 を、それぞれのアンカー部分 141a 又は 141b に対して片持ちにすることができる。

#### 【0072】

凹部 130a 及び 130b は、図 1A ~ 図 2D を参照して上に示し説明した凹部 30 と同様である。凹部 130a 及び 130b は、主面 121 から部分的に基板 120 を通って第 2 の面 122 まで延在している。凹部 130a 及び 130b の内面 131 は、主面 121 から基板 120 を通って任意の角度で延在することができる。好ましくは、内面 131 は、主面 121 から、主面 121 によって画定される水平面に対して 0 度と 90 度との角度で延在する。

#### 【0073】

凹部 130a 及び 130b は、例えば、図 1B ~ 図 1D に示す凹部 130b 等、橢円形、又は図 1B 及び図 1C に示す凹部 130a 等、円形を含む、任意の下面図形状を有することができる。幾つかの例では、凹部 130a 及び 130b は、特に、例えば円柱、立方体、角柱又は円錐台形状を含む、任意の 3 次元形状を有することができる。特定の実施形態では、凹部 130a 及び 130b を矩形溝とし、図 1D に示す接合部分 42 の構成に類似する構成で、複数のそれぞれの接合部分 142a 及び 142b が少なくとも部分的に凹部の上に重なるようにすることができる。

#### 【0074】

誘電体領域 150 は、図 1A ~ 図 2D を参照して上に示し説明した誘電体領域 50 と同様のあり得る構成及び特性を有している。例えば、図 3A ~ 図 3D に示す実施形態では、誘電体領域 150 は、誘電体領域の輪郭が凹部の輪郭（すなわち、凹部の内面 131 の形状）に沿うように、凹部 130a 及び 130b を充填している。誘電体領域 150 をコンプライアントとし、弾性係数及び厚さを、その係数及び厚さの積がコンプライアンスを提供するように十分低くかつ厚くすることができる。好ましくは、接合部分 142a 及び 142b は、基板 120 に対して移動可能とすることができるように、少なくとも部分的に誘電体領域 150 の上に重なっている。

#### 【0075】

図 1A ~ 図 2D を参照して上述した誘電体層 25 と同様に、誘電体層 125 は、基板 120 の主面 121 と接合部分 142a 及び 142b ではない導電性素子 140a 及び 140b の部分との上に重なることにより、基板と接合部分ではない導電性素子の部分とに対

10

20

30

40

50

して優れた誘電体分離を提供することができる。

**【0076】**

図3A～図3Dに示すように、孔160は段状であり、開口部130から第2の面122に向かって延在している第1の開口部161と、第1の開口部から第2の面まで延在している第2の開口部162と、を含む。段状孔160は、2010年7月23日に出願された、本願と同一の所有者によって所有される米国特許出願第12/842,717号と、本願と同一の所有者によって所有される米国特許出願公開第2008/0246136号とにおいてより詳細に示し記載されている構造のうちの任意のものを有することができ、上記出願は、引用することにより本明細書の一部をなすものとする。他の実施形態では、図6を参照して示し説明する孔60b等、孔はより単純な非段状構造を有することができる。10

**【0077】**

第1の開口部161は、凹部130から部分的に基板120を通って第2の面122に向かって延在している。第1の開口部161は、凹部130から基板120を通って、主面121によって画定される水平面に対して0度と90度との間の角度で延在する、内面163を有している。内面163は、一定の勾配又は可変の勾配を有することができる。例えば、主面121によって画定される水平面に対する内面163の角度又は勾配は、内面163が第2の面122に向かって深く貫入するに従い、大きさが減少する（すなわち、正又は負の大きさが小さくなる）ことができる。例えば図4Dに示すように、第1の開口部161は、凹部130において幅W1を有し、第1の開口部が第2の開口部162に接觸する場所において、W1より小さい幅W2を有し、それにより、第1の開口部は、主面121から第2の面122に向かう方向において先細りになっている。他の例では、第1の開口部は一定の幅を有することができ、又は第1の開口部を、第2の面から表面に向かう方向に先細りにすることができます。第1の開口部161は、特に、例えば立方体、円柱、円錐台又は角柱を含む、任意の3次元形状を有することができる。20

**【0078】**

第2の開口部162は、第1の開口部161から部分的に基板120を通って第2の基板122に向かって延在している。第2の開口部162は、第1の開口部161から基板120を通って、主面121によって画定される水平面に対して0度と90度との角度で延在する内面164を有している。上述した内面163と同様に、内面164は、一定の勾配又は可変の勾配を有することができる。例えば図4Dに示すように、第2の開口部162は、第1の開口部161と接觸する場所において幅W3を有し、第2の面122において、W3より大きい幅W4を有し、それにより、第1の開口部は、第2の面122から主面121に向かう方向において先細りになっている。他の例では、第2の開口部は一定の幅を有することができ、又は、第2の開口部を、表面から第2の面に向かう方向において先細りにすることができます。第2の開口部162は、特に、例えば立方体、円柱、円錐台又は角柱を含む、任意の3次元形状を有することができる。30

**【0079】**

特定の実施形態では、内面163及び164は、主面121に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定することができる。任意の数の第1の開口部161が单一の第2の開口部162から延在することができ、任意の数の第2の開口部が单一の第1の開口部から延在することができる。第1の開口部161及び第2の開口部162を、各々に対しあつ基板120に対し任意の幾何学的構成で配置することができる。様々な第1の及び第2の開口部形態並びにこれらの形態を形成する方法の特定の例は、上述の、本願と同一の譲受人が所有する米国特許出願第12/842,717号及び米国特許出願公開第2008/0246136号に記載されている。40

**【0080】**

それぞれの導電性素子140a及び140bのアンカー部分141a及び141bは、好ましくは、それぞれの第1の開口部161の輪郭に沿う輪郭を有し、それにより、アンカー部分は、基板120に対して固定された位置を有している。アンカー部分141a又50

は 141b は、支点としての役割を果たすことができ、取り付けられた超小型電子ユニットに対する熱膨張差によってもたらされるもの等の機械的応力下に置かれたときに、取り付けられた接合部分 142a 又は 142b が、その支点を中心に枢動することができる。

#### 【0081】

導電性ピア 170 は、それぞれのアンカー部分 141a 又は 141b と第 2 の面 122 との間の孔 160 を通って延在している。図 3A に示すように、導電性ピア 170 は、導電性ピアから基板 120 を電気的に絶縁することができる任意選択的な誘電体層（図示せず）の内側の第 2 の開口部 162 内の容積の全てを充填することができる。導電性ピア 170 は、第 2 の開口部 162 の輪郭に沿うことができる。導電性ピア 170 は、円柱形状又は円錐台形状を有することができる。導電性ピア 170 を、例えば銅又は金を含む、金属又は金属の導電性化合物から作製することができる。10

#### 【0082】

他の実施形態（図示せず）では、導電性ピア 170 の輪郭（すなわち、導電性ピアの外面の形状）は、第 2 の開口部 162 の輪郭（すなわち、第 2 の開口部の内面 164 の形状）に沿わない。こうした非コンフォーマルな導電性ピアの実施形態では、導電性ピア 170 は、例えば、円柱形状、円錐台形状、又は第 2 の面 122 から異なる距離における円柱形状及び円錐台形状の組合せを含む、任意の形状を有することができる。

#### 【0083】

導電性ピア 170 を、中実又は中空とすることができる。幾つかの実施形態では、導電性ピアは、誘電体材料で充填される内部空間を有することができる。例えば、導電性ピア 170 を、第 2 の開口部 162 の内面 164 の上に重なる金属を堆積させることによって形成することができ、それにより、第 2 の開口部の内面の上に重なる導電性層を生成することができる。様々な導電性ピア形態及びこれらの形態を形成する方法の特定の例は、上述の、本願と同一の譲受人が所有する米国特許出願第 12/842,717 号及び米国特許出願公開第 2008/0246136 号に記載されている。20

#### 【0084】

導電性ピア 170 は、各々、積層超小型電子アセンブリ 110 の外部のコンポーネントと相互接続するよう、第 2 の面 122 において露出しているコンタクト部分 180 を備えている。幾つかの実施形態では、各導電性ピア 170 を、第 2 の面 122 において露出している別個の導電性コンタクトに電気的に結合することができる。30

#### 【0085】

第 2 の超小型電子ユニット 114 は、図 1A を参照して上に示し説明した第 2 の超小型電子ユニット 14 と同様である。第 2 の超小型電子ユニット 114 は、基板 115 と、第 1 の超小型電子ユニット 112 の接合部分 142a 及び 142b と相互接続するために基板の主面 117 において少なくとも部分的に露出している導電性コンタクト 116 と、を備えることができる。

#### 【0086】

図 3A に示すように、導電性コンタクト 116 は導電性パッドである。導電性パッド 116 は、円形、正方形、橢円形、矩形、又はより複雑な形状を含む、任意の形状を有することができる。特定の実施形態では、導電性コンタクト 116 を、例えば、図 1A に示す導電性ポスト 16a 等の導電性ポストを含む、任意のタイプの導電性コンタクトとすることができる。2010 年 7 月 8 日に出願された、本願と同一の所有者によって所有される米国特許出願第 12/832,376 号に示し記載されているように、導電性ポストの他の例を使用することができる。40

#### 【0087】

第 1 の超小型電子ユニット 112 と第 2 の超小型電子ユニット 114 との間の接続は、図 1A ~ 図 2D を参照して説明したものと同様に、導体塊 118 を介することができる。基板 120 の主面 121 における誘電体層 125 及び誘電体領域 150 と、基板 115 の主面 117 の上に重なる誘電体層（例えばパッシベーション層）とは、相互接続が設けられている場所を除き、第 1 の超小型電子ユニット 112 と第 2 の超小型電子ユニット 111 50

4との間に電気的絶縁を提供することができる。

#### 【0088】

ここで、図4A～図4Dを参照して、超小型電子アセンブリ110(図3A～図3D)を製造する方法について説明する。図4Aに示す製造の段階では、第1の超小型電子ユニット112は基板120を備えている。基板から材料を除去することにより、正面121から基板120の第2の面122まで延在する孔160を形成することができる。特定の実施形態では、正面121から内側に延在する第1の開口部161を形成することができ、第2の面122から内側に延在する第2の開口部を形成することができる。他の実施形態では、正面121又は第2の面122のいずれから、第1の開口部161及び第2の開口部162のいずれか又は両方を形成することができる。

10

#### 【0089】

孔160を、凹部30を形成することに関して上述したものと同様の方法でかつ同様のプロセスを用いて形成することができる。例えば、正面121の残りの部分を保存することが望まれる場所にマスク層を形成した後、基板の材料を除去するように基板120を選択的にエッチングすることにより、孔160を形成することができる。凹部30と同様に、第1の開口部161の内面163及び第2の開口部162の内面164は、正面121に対して任意の一定の角度又は可変の角度で延在することができる。

#### 【0090】

図示しないが、基板120の正面121に、及び／又は第1の開口部161の内面163及び第2の開口部162の内面164の上に重ねて、誘電体層を任意選択的に形成することにより、導電性素子140a及び140b並びに導電性ビア170の基板からの電気的絶縁を可能にすることができる。こうした誘電体層を、図2Bに示す誘電体層25を参照して上述した様々な方法のうちの任意のものを用いて形成することができる。こうした誘電体層を、基板120の正面121の上に既に重なっている可能性があるパッシベーション層に加えるか又はその代りとすることができる。

20

#### 【0091】

図4Bに示す製造の段階において、アンカー部分141a及び141bと、導電性素子140a及び140bのそれぞれの接続部分145a及び145bとを、第1の開口部161内に形成することができ、正面121の上に重なる接合部分142a及び142bを形成することができ、コンタクト部分180を第2の面122において露出させて、導電性ビア170を第2の開口部162内に形成することができる。アンカー部分141a及び141bの各々、接続部分145a及び145b、接合部分142a及び142b、並びに導電性ビア170を、单一金属堆積プロセス又は別個のプロセスで形成することができる。導電性ビア170が、第2の面122において露出している別個の導電性コンタクトに電気的に結合される実施形態では、こうした導電性コンタクトを、導電性素子140a及び140b並びに導電性ビアとともに单一金属堆積プロセスで形成することができ、又はこうした導電性コンタクトを別個のプロセスで形成することができる。

30

#### 【0092】

導電性素子140a及び140b並びに導電性ビア170を形成する例示的な方法は、基板120の露出面上への主金属層のスパッタリング、めっき又は機械的堆積のうちの1つ又は複数により、金属層を堆積させることを含む。機械的堆積は、コーティングされる表面上に加熱された金属粒子の流れを高速で向けることを含むことができる。このステップを、例えばプランケット堆積により、正面121、並びに内面163及び164に対して行うことができる。一実施形態では、主金属層は、アルミニウムを含むか又は本質的にアルミニウムからなる。別の特定の実施形態では、主金属層は、銅を含むか又は本質的に銅からなる。更に別の実施形態では、主金属層は、チタンを含むか又は本質的にチタンからなる。導電性素子140a及び140b並びにビア170を形成するプロセスにおいて、1つ又は複数の他の例示的な金属を用いることができる。特定の例では、複数の金属層を含む積層体を上述した面のうちの1つ又は複数の上に形成することができる。例えば、こうした積層金属層としては、例えば、チタンの層及びそれに続くチタンの上に重なる銅

40

50

の層 (Ti - Cu)、ニッケルの層及びそれに続くニッケル層の上に重なる銅の層 (Ni - Cu)、同様に設けられるニッケル - チタン - 銅の積層体 (Ni - Ti - Cu)、又はニッケル - バナジウムの積層体 (Ni - V) を挙げることができる。

#### 【0093】

特定の実施形態では、図2Aに示す製造の段階に示すように、例えば基板から任意の材料を除去する前に、接合部分142a及び142bを基板120の主面121の上に堆積させることができる。こうした実施形態では、例えば、接合部分142a及び/又は142bを通してエッチングし、その後、基板120内にエッチングすることにより、孔160を形成することができる。接合部分142a及び/又は142bを通して孔160が形成された後、上述したように、接続部分145a及び145b、アンカー部分141a及び141b並びに導電性ビア170を形成することができる。

10

#### 【0094】

図4Cに示す製造の段階では、誘電体層125は、基板120の主面121に形成され、主面の残りの部分を保存することが望まれる場所においてエッチングマスク層としての役割を果たす。誘電体層125を、図2Bに示す誘電体層25に関して上述した様々な方法のうちの任意のものを用いて形成することができる。接合部分142a及び142bを、第1の超小型電子ユニット112の外部のコンポーネントと接続するために、主面121において少なくとも部分的に露出させた(すなわち、誘電体層125によって覆わない)まとまることができる。

20

#### 【0095】

その後、図4Dに示す製造の段階では、凹部30を形成することに関する上述したものと同様にかつ同様のプロセスを用いて、凹部130を形成することができる。例えば、主面121の残りの部分を保存することが望まれる場所にマスク層(例えば誘電体層25)を形成した後、基板の材料を除去するように基板120を選択的にエッチングすることにより、凹部130を形成することができる。少なくとも接合部分142a及び142bを支持する基板120の材料が除去されるよう、凹部130を形成することができる。凹部30と同様に、凹部130の内面131は、主面121に対して任意の一定の角度又は可変の角度で延在することができる。

30

#### 【0096】

図4Dに示すように、凹部130を、第1の開口部161ほど主面121から遠くに延在しないように形成することができ、それにより、アンカー部分141a及び141bの輪郭は、第1の開口部の内面163の残りの部分の輪郭に沿う。特定の実施形態では、凹部130を、少なくとも第1の開口部121程度に主面121から遠くに延在するように形成することができ、それにより、アンカー部分141a及び141bの輪郭は、基板120の任意の内面の輪郭に沿わない。こうした実施形態では、アンカー部分141a及び141bを、アンカー部分と、第2の開口部162の内面164の輪郭に沿う輪郭を有することができる導電性ビア170と、の間の取付物(attachment)を介して、基板120に固定することができる。

30

#### 【0097】

その後、図4Eに示す製造の段階において、凹部30の内側に誘電体領域50を形成することに関する上述したものと同様にかつ同様のプロセスを用いて、凹部130の内側に誘電体領域150を形成することができる。例えば、誘電体領域150の領域の露出した外面151が、(図4Eに示すように)基板120の主面121又は誘電体層125の露外面と同一平面状であるか又は実質的に同一平面であるように、誘電体領域150を形成することができる。

40

#### 【0098】

その後、再び図3Aを参照すると、第1の超小型電子ユニット112を第2の超小型電子ユニット114の上に積層することができ、それにより、積層超小型電子アセンブリ110が形成される。上述したように、第1の超小型電子ユニット112と第2の超小型電子ユニット114との間の接続は、導体塊118を介することができる。導体塊118は

50

、第1の超小型電子ユニット112の接合部分142a及び142bと、第2の超小型電子ユニット114の導電性コンタクト16との間の電気的接続を提供することができる。こうした配置では、接合部分142a及び142bは、それぞれの導電性コンタクト16に位置合せされる。

#### 【0099】

図5に示すように、図1A～図4Eを参照して上述した実施形態のうちの任意のものにおいて使用するのに適している、導電性素子240の基礎部分241及び接合部分242が示されている。接合部分242は、導電性素子240の基礎部分241から延在している。基礎部分241を、例えば、図3Aに示す第1の超小型電子ユニット112に関して上述した接合部分142a又は142bの一部、又は図1Aに示す第1の超小型電子ユニット12に関して上述したアンカー部分41の一部とすることができます。基礎部分241を、基板220の主面221の真下に、又は誘電体領域250の外面251の真下に配置された他の導電性素子に接続することができる。図5に示す実施形態では、基礎部分241は、コンプライアントであるか、又は主面221によって画定される平面の方向に移動可能であるセグメント243を備え、それにより、セグメントは、加えられる外部負荷によって主面221に沿う方向に変位することができる。

10

#### 【0100】

ここで図6を参照すると、別の実施形態による第1の超小型電子アセンブリ12'は、図1Aに示す第1の超小型電子アセンブリ12に類似しているが、導電性素子40'は、基板20'の主面21と第2の面22との間に延在している導電性ビア70a及び70bに電気的に接続されている点が異なる。

20

#### 【0101】

基板20'は、主面21及び第2の面22から延在している孔60a及び60bを備え、導電性ビア70a及び70bは、それぞれの孔内で、導電性素子40'のそれぞれのアンカー部分41'から第2の面まで延在している。各導電性ビア70a及び70bは、第1の超小型電子ユニット12'の外部のコンポーネントと相互接続するために第2の面22において露出しているコンタクト部分80を備えている。孔60aは、開口部30が孔60a又は60bのいずれともオーバラップしない点を除いて、図3Aに示す孔160と同様の段状孔であり、そのため、孔60a及び60bは、第2の面からそれぞれの開口部までではなく、第2の面22から主面21まで延在している。孔60bは段状ではなく、すなわち、孔60bを、例えば、基板20'から材料を除去する單一エッチングプロセス又は他のプロセスで形成することができる。

30

#### 【0102】

図1Aに示す第1の超小型電子アセンブリ12と同様に、各導電性素子40は、第1の超小型電子素子12'の外部のコンポーネントと相互接続するために主面21において露出させることができる接合部分42を備えている。また第1の超小型電子アセンブリ12と同様に、誘電体領域50をコンプライアントとすることができます、それにより、各接合部分42を基板20'に対して移動可能とすることができる。

#### 【0103】

図7は、超小型電子アセンブリ310の各々にかつ各々から信号を伝送するための電気的インタフェース320を有している、合わせて1つのユニットに配置された少なくとも2つの超小型電子アセンブリ310を備えたモジュール300を示す。電気的インタフェースは、超小型電子アセンブリ310内の超小型電子素子の各々に共通である、信号の伝送又は基準電位、例えば電源及び接地に使用可能な1つ又は複数のコンタクトを含むことができる。超小型電子アセンブリ310を、上述したアセンブリのうちの任意のものとすることができる。特定の例では、モジュール300を、デュアルインラインメモリモジュール(「DIMM」)又はシングルインラインメモリモジュール(「SIMM」)とすることができ、その1つ又は複数の部分が、マザーボード上に設けることができるような、システムの他のコネクタの対応するスロットに挿入されるようなサイズである。こうしたDIMM又はSIMMでは、電気的インタフェースは、こうしたスロットコネクタ内の複

40

50

数の対応するばね接点と嵌合するのに適しているコンタクト 330 を有することができる。こうしたばね接点を、対応するモジュールコンタクトと嵌合するように各スロットの单一の側部又は複数の側部に配置することができる。モジュールが非積層超小型電子アセンブリ又は積層超小型電子アセンブリを有することができ、又は、並列若しくは直列の電気的インタフェース、若しくはモジュールにかつモジュールから電気信号を伝送するための並列の電気的インタフェース及び直列の電気的インタフェースの組合せを有することができる、様々な他のモジュール及び相互接続配置が可能である。本発明により、モジュール 300 と更なるシステムインターフェースとの間の任意の種類の電気的相互接続配置が企図されている。

## 【0104】

10

図 8 に示すように、上述した超小型電子アセンブリを多様な電子システムの構成で利用することができる。例えば、本発明の更なる実施形態によるシステム 400 は、他の電子コンポーネント 408 及び 410 とともに上述したような超小型電子アセンブリ 406 を含む。説明した例では、コンポーネント 408 は半導体チップであり、コンポーネント 410 が表示画面であるが、他の任意のコンポーネントを使用することができる。当然ながら、例示を明確にするために図 8 には 2 つの追加のコンポーネントのみを示すが、本システムは、任意の数のこうしたコンポーネントを含むことができる。超小型電子アセンブリ 406 を、上述したような超小型電子アセンブリのうちの任意のものとすることができる。更なる変形形態では、任意の数のこうした超小型電子アセンブリを使用することができる。

20

## 【0105】

超小型電子アセンブリ 406 並びにコンポーネント 408 及び 410 は、破線で概略的に示す共通ハウジング 401 内に取り付けられ、必要に応じて互いに電気的に相互接続されて所望の回路を形成する。図示する例示的なシステムでは、システムは、可撓性印刷回路基板等の回路パネル 402 を含み、回路パネルは、コンポーネントを互いに相互接続する多数の導体 404 を含み、それらのうちの 1 つのみを図 8 に示す。しかしながら、これは単に例示的なものであり、電気接続をもたらす任意の適切な構造を使用することができる。

## 【0106】

30

ハウジング 401 は、例えば携帯電話又は携帯情報端末における使用可能なタイプの携帯型ハウジングとして示されており、画面 410 は、ハウジングの表面において露出している。構造体 406 が、撮像チップ等の感光素子を含む場合、光を構造体に誘導するために、レンズ 411 又は他の光学デバイスも提供することができる。この場合もまた、図 8 に示す簡略化システムは単に例示的なものであり、上述した構造体を用いて、デスクトップコンピュータ、ルータ等、一般に固定構造体とみなされるシステムを含む他のシステムを作製することができる。

## 【0107】

本明細書に開示されているビア及びビア導電体は、2010年7月23日に出願された、同時係属の本願と同一の譲受人に譲渡された米国特許出願第 12/842,587 号、同第 12/842,612 号、同第 12/842,651 号、同第 12/842,669 号、同第 12/842,692 号及び同第 12/842,717 号に、かつ米国特許出願公開第 2008/0246136 号により詳細に開示されているもの等のプロセスによって形成することができ、それらの開示内容は、引用することにより本明細書の一部をなすものとする。

40

## 【0108】

本発明は特定の実施形態を参照しながら本明細書において説明されてきたが、これらの実施形態は本発明の原理及び応用形態を例示するにすぎないことは理解されたい。それゆえ、添付の特許請求の範囲によって規定されるような本発明の趣旨及び範囲から逸脱することなく、例示的な実施形態に数多くの変更を加えることができること、及び他の構成を考案することを理解されたい。

50

## 【0109】

本明細書において記述される種々の従属請求項及び特徴は、初期の請求項において提示されるのとは異なる方法において組み合わせることができることは理解されよう。また、個々の実施形態との関連で説明された特徴は、記述される実施形態のうちの他の実施形態と共に用できることも理解されよう。

## [実施形態例]

## [実施形態1]

基板であって、10 ppm / 未満のCTEと、該基板を通って延在していない凹部を有する主面と、該凹部内に配置された、弾性係数が10 GPa未満である材料と、を有する基板と、

10

前記凹部の上に重なり、かつ前記基板によって支持されるアンカー部分から延在している接合部分を備える導電性素子であって、該接合部分は、該超小型電子ユニットの外部のコンポーネントに接続するために前記主面において少なくとも部分的に露出している、導電性素子と、

を具備する、超小型電子ユニット。

## [実施形態2]

前記基板は、CTEが7 ppm / 未満である、実施形態1に記載の超小型電子ユニット。

20

## [実施形態3]

前記接合部分は、前記超小型電子ユニットの動作、製造又は試験中に存在する可能性がある応力等の、該接合部分に対する応力を低減するように移動可能である、実施形態1に記載の超小型電子ユニット。

## [実施形態4]

前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなる、実施形態1に記載の超小型電子ユニット。

## [実施形態5]

前記基板は、複数の能動半導体デバイスを備え、前記導電性素子は、前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続されている、実施形態1に記載の超小型電子ユニット。

30

## [実施形態6]

前記凹部内に配置された前記材料は、ポリイミド、シリコーン及びエポキシからなる群から選択された少なくとも1つの材料を含む、実施形態1に記載の超小型電子ユニット。

## [実施形態7]

前記凹部は、前記基板を通って延在していない、実施形態1に記載の超小型電子ユニット。

## [実施形態8]

前記接合部分は、前記基板の前記主面に対して実質的に平行な方向に延在している、請求項1に記載の超小型電子ユニット。

## [実施形態9]

前記アンカー部分及び前記接合部分は同じ方向に延在している、実施形態1に記載の超小型電子ユニット。

40

## [実施形態10]

前記導電性素子は、前記基板の前記主面とは反対側の第2の面に向かって延在している導電性ビアに電気的に結合されている、実施形態9に記載の超小型電子ユニット。

## [実施形態11]

前記導電性ビアは前記第2の面において露出している、実施形態10に記載の超小型電子ユニット。

## [実施形態12]

前記導電性ビアは、前記基板において前記第2の面から前記主面まで延在している孔内に延在している、実施形態10に記載の超小型電子ユニット。

50

[実施形態 13]

前記孔は、前記主面から前記第2の面に向かって延在している第1の開口部と、該第1の開口部から前記第2の面まで延在している第2の開口部と、を含み、前記第1の開口部及び前記第2の開口部の内面は、前記主面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定している、実施形態12に記載の超小型電子ユニット。

[実施形態 14]

少なくとも第1の超小型電子ユニット及び第2の超小型電子ユニットを備える積層アセンブリであって、該第1の超小型電子ユニットは実施形態1に記載の超小型電子ユニットであり、前記第2の超小型電子ユニットは、該第1の超小型電子ユニットと積層されており、該積層アセンブリ内の前記第1の超小型電子ユニットの前記基板は、前記第2の超小型電子ユニットの基板と電気的に接続されている、積層アセンブリ。

10

[実施形態 15]

前記第1の超小型電子ユニットの前記接合部分と前記第2の超小型電子ユニットの導電性素子とに電気的に結合されている導体塊を更に具備する、実施形態14に記載の積層アセンブリ。

[実施形態 16]

実施形態1に記載の構造体と、該構造体に電気的に接続された1つ又は複数の他の電子コンポーネントと、を具備するシステム。

[実施形態 17]

ハウジングを更に具備し、前記構造体及び前記他の電子コンポーネントは前記ハウジングに実装されている、実施形態16に記載のシステム。

20

[実施形態 18]

実施形態1のいずれか一項に記載の複数の超小型電子アセンブリを備えるモジュールであって、前記超小型電子アセンブリの各々にかつ各々から信号を伝送するための共通の電気的インターフェースを有している、モジュール。

[実施形態 19]

C T E が 1 0 p p m / 未満である基板の主面に支持される導電性素子を形成するステップと、

前記主面から、少なくとも前記導電性素子の接合部分を支持する材料を除去するステップであって、それにより前記基板を通って延在しない凹部を形成し、前記接合部分が前記基板によって支持されず、一方で、前記接合部分に隣接する前記導電性素子のアンカー部分が前記基板によって支持されるようにする、除去するステップと、

30

弾性係数が 1 0 G P a 未満である材料を前記凹部内に堆積させるステップと、

を含み、

前記接合部分は、前記超小型電子ユニットの外部のコンポーネントに接続するために前記基板の前記主面において少なくとも部分的に露出する、超小型電子ユニットを製造する方法。

[実施形態 20]

前記基板は、C T E が 7 p p m / 未満である、実施形態19に記載の方法。

40

[実施形態 21]

前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなる、実施形態19に記載の方法。

[実施形態 22]

前記基板は、複数の能動半導体デバイスを備え、前記導電性素子を形成する前記ステップは、前記導電性素子を、前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続する、実施形態19に記載の方法。

[実施形態 23]

前記導電性素子を形成する前記ステップは、前記接合部分が前記主面に対して実質的に平行に配置されるように行われる、実施形態19に記載の方法。

[実施形態 24]

50

前記基板から材料を除去し、前記主面から該主面とは反対側の前記基板の第2の面まで延在する孔を形成するステップと、

前記孔内に延在する導電性ビアを、該導電性ビアが前記導電性素子に電気的に結合されかつ前記第2の面に向かって延在するように形成するステップと、

を更に含む、実施形態19に記載の方法。

[実施形態25]

前記基板から材料を除去し、孔を形成する前記ステップは、前記主面から前記第2の面に向かって延在する第1の開口部と、該第1の開口部から前記第2の面まで延在する第2の開口部と、を形成するステップを含み、前記第1の開口部及び前記第2の開口部の内面は、前記主面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定する、実施形態24に記載の方法。

10

[実施形態26]

少なくとも第1の超小型電子素子及び第2の超小型電子素子を備える積層アセンブリを製造する方法であって、該第1の超小型電子素子は実施形態19に記載の通りに製造され、該方法は、前記第1の超小型電子ユニットの前記基板を前記第2の超小型電子ユニットの基板に電気的に接続するステップを更に含む、方法。

[実施形態27]

C T E が 10 ppm / 未満である基板から材料を除去するステップであって、それにより、該基板の主面から該主面とは反対側の第2の面まで延在する孔を形成する、基板から材料を除去するステップと、

20

前記主面の上方に延在しかつ該主面上に支持される接合部分と、前記基板に対して固定されたアンカー部分と、前記接合部分から前記アンカー部分まで下方に延在する接続部分と、を有する導電性素子を形成するステップであって、前記接続部分の表面は、前記孔の内面の輪郭に沿う輪郭を有する、導電性素子を形成するステップと、

前記主面から、少なくとも前記導電性素子の接合部分を支持する材料を除去するステップであって、それにより、凹部を、前記接合部分が少なくとも部分的に該凹部の上に重なるように、かつ前記接続部分の前記表面の前記輪郭が前記凹部の内面の輪郭に沿わないよう形成する、前記主面から材料を除去するステップと、

弾性係数が 10 GPa 未満である材料を前記凹部内に堆積させるステップと、

を含み、

30

前記接合部分は、前記超小型電子ユニットの外部のコンポーネントに接続するために前記基板の前記主面において少なくとも部分的に露出する、超小型電子ユニットを製造する方法。

[実施形態28]

前記基板は、C T E が 7 ppm / 未満である、実施形態27に記載の方法。

[実施形態29]

前記導電性素子を形成する前記ステップの前に、前記孔内に延在しかつ前記第2の面に向かって延在する導電性ビアを形成するステップを更に含み、それにより、前記導電性素子を形成する前記ステップは、該導電性素子を前記導電性ビアに電気的に結合する、請求項27に記載の方法。

40

[実施形態30]

前記導電性素子を形成する前記ステップは、前記接合部分が前記接続部分に対して中心合わせされないよう行われる、実施形態27に記載の方法。

[実施形態31]

前記基板は、本質的に、半導体、ガラス及びセラミックからなる群から選択される1つの材料からなる、実施形態27に記載の方法。

[実施形態32]

前記基板は、複数の能動半導体デバイスを備え、前記導電性素子を形成する前記ステップは、該導電性素子を前記複数の能動半導体デバイスのうちの少なくとも1つに電気的に接続する、実施形態27に記載の方法。

50

[ 実施形態 3 3 ]

前記導電性素子を形成する前記ステップは、前記接合部分が内部穴を画定するよう行われる、実施形態 27 に記載の方法。

〔 實施形態 3 4 〕

前記導電性素子を形成する前記ステップは、前記穴が前記接合部分を通って前記接続部分内へ延在するように行われる、実施形態33に記載の方法。

〔 實施形態 35 〕

前記穴の少なくとも一部分内に誘電材料を堆積させるステップを更に含む、実施形態3

4に記載の方法。

「寒施形態 36」

前記基板から材料を除去する前記ステップであって、それにより孔を形成する前記ステップは、前記正面から前記第2の面に向かって延在する第1の開口部と、該第1の開口部から前記第2の面まで延在する第2の開口部と、を形成するステップを含み、前記第1の開口部及び前記第2の開口部の内面は、前記正面に対してそれぞれ第1の方向及び第2の方向に延在して、実質的な角度を画定する、実施形態27に記載の方法。

「寒施形態 37」

少なくとも第1の超小型電子素子及び第2の超小型電子素子を備える積層アセンブリを製造する方法であって、該第1の超小型電子素子は実施形態27に記載の通りに製造され、該方法は、前記第1の超小型電子ユニットの前記基板を前記第2の超小型電子ユニットの基板に電気的に接続するステップを更に含む、方法。

## 【産業上の利用可能性】

[0110]

本発明は、限定はしないが、超小型電子ユニット及び超小型電子ユニットを製造する方法を含む、広範な産業上の利用可能性を有する。

【 1 A 】

【 図 1 B 】

【図1C】

【 図 1 D 】

〔 囮 2 A 〕

〔 図 2 B 〕

〔图2C〕

【図2D】

【図3A】

---

フロントページの続き

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100166268

弁理士 田中 祐

(74)代理人 100170379

弁理士 徳本 浩一

(74)代理人 100161001

弁理士 渡辺 篤司

(72)発明者 オガネシアン, ヴァーゲ

アメリカ合衆国カリフォルニア州 94086, サニーベイ, ペリウインクル・テラス 889

(72)発明者 ハーバ, ベルガセム

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド内

(72)発明者 モハメド, イリヤス

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド内

(72)発明者 サヴァリア, ピューシュ

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド内

(72)発明者 ミッセル, クレイグ

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド内

審査官 麻川 倫広

(56)参考文献 特開2005-354120 (JP, A)

国際公開第2009/104668 (WO, A1)

米国特許第06507113 (US, B1)

米国特許第06638352 (US, B2)

特開2007-250712 (JP, A)

特開2007-096198 (JP, A)

特開2000-299408 (JP, A)

特開2003-198069 (JP, A)

特開2007-005403 (JP, A)

特開2010-157215 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L21/3205-21/3213

21/447-21/449

21/60-21/607

21/768

23/12-23/15

23/522

23/532

25/00-25/07

25/10-25/11

(30)

JP 6153471 B2 2017.6.28

25 / 16 - 25 / 18