(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5611571号

(P5611571)

(45) 発行日 平成26年10月22日(2014.10.22)

(24) 登録日 平成26年9月12日(2014.9.12)

|                        |                  |

|------------------------|------------------|

| (51) Int.Cl.           | F 1              |

| HO 1 L 27/12 (2006.01) | HO 1 L 27/12 B   |

| HO 1 L 21/02 (2006.01) | HO 1 L 21/02 B   |

| HO 1 L 31/18 (2006.01) | HO 1 L 31/04 460 |

請求項の数 3 (全 22 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2009-262954 (P2009-262954)  |

| (22) 出願日     | 平成21年11月18日 (2009.11.18)      |

| (65) 公開番号    | 特開2010-153823 (P2010-153823A) |

| (43) 公開日     | 平成22年7月8日 (2010.7.8)          |

| 審査請求日        | 平成24年11月15日 (2012.11.15)      |

| (31) 優先権主張番号 | 特願2008-302169 (P2008-302169)  |

| (32) 優先日     | 平成20年11月27日 (2008.11.27)      |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 井坂 史人<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 加藤 翔<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 有田 祐<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 下村 明久<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

最終頁に続く

(54) 【発明の名称】半導体基板の作製方法及び半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に第1の単結晶半導体層を設ける工程と、

前記第1の単結晶半導体層上に、シラン系ガスに対する水素の流量比が4倍以上10倍以下の条件で気相エピタキシャル成長法を用いて第2の単結晶半導体層を設ける工程と、

前記第1の基板と第2の基板とを絶縁膜を介して貼り合わせ、前記第1の基板と第2の基板との間に前記第1の単結晶半導体層及び前記第2の単結晶半導体層を設ける工程と、

前記第1の基板と前記第2の基板とを前記第1の単結晶半導体層と前記第2の単結晶半導体層との界面で分離して、前記第1の基板上に前記第1の単結晶半導体層を設け且つ前記第2の基板上に前記第2の単結晶半導体層を設ける工程と、

を有し、

前記第1の基板がガラス基板であることを特徴とする半導体基板の作製方法。

## 【請求項 2】

第1の基板と所定の深さに脆化層が形成された単結晶半導体基板とを絶縁膜を介して貼り合わせる工程と、

前記単結晶半導体基板と前記第1の基板とを前記脆化層から分離して、前記第1の基板上に第1の単結晶半導体層を設ける工程と、

前記第1の単結晶半導体層上に、シラン系ガスに対する水素の流量比が4倍以上10倍以下の条件で気相エピタキシャル成長法を用いて第2の単結晶半導体層を設ける工程と、

前記第1の基板と第2の基板とを絶縁膜を介して貼り合わせ、前記第1の基板と第2の

10

20

基板との間に前記第1の単結晶半導体層及び前記第2の単結晶半導体層を設ける工程と、

前記第1の基板と前記第2の基板とを前記第1の単結晶半導体層と前記第2の単結晶半導体層との界面で分離して、前記第1の基板上に前記第1の単結晶半導体層を設け且つ前記第2の基板上に前記第2の単結晶半導体層を設ける工程と、

を有し、

前記第1の基板がガラス基板であることを特徴とする半導体基板の作製方法。

**【請求項3】**

第1の基板上に単結晶半導体層を設ける工程と、

前記単結晶半導体層上に、シラン系ガスに対する水素の流量比が4倍以上10倍以下の条件で気相エピタキシャル成長法を用いて、光電変換層を設ける工程と、

10

前記光電変換層上に第1の導電膜を設ける工程と、

前記第1の基板と第2の基板とを絶縁膜を介して貼り合わせ、前記第1の基板と第2の基板との間に、前記単結晶半導体層、前記光電変換層、及び前記第1の導電層を設ける工程と、

前記第1の基板と前記第2の基板とを前記単結晶半導体層と前記光電変換層との界面で分離して、前記第1の基板上に前記単結晶半導体層を設け且つ前記第2の基板上に前記第1の導電層及び前記光電変換層を設ける工程と、

前記光電変換層上に第2の導電層を設ける工程と、を有し、

前記第1の基板がガラス基板であることを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

単結晶半導体層の作製方法に関する。また、単結晶半導体膜を有する半導体基板の作製方法、及び半導体基板の再生方法に関する。

**【背景技術】**

**【0002】**

バルク状のシリコンウエハに代わり、絶縁表面に薄い単結晶半導体層が存在するSOI基板を使った集積回路が開発されている。SOI基板を使うことで、トランジスタのドレインと基板間における寄生容量が低減されるため、SOI基板は半導体集積回路の性能を向上させるものとして注目されている。

30

**【0003】**

SOI基板を製造する方法の1つに、スマートカット法が知られている（例えば、特許文献1参照）。スマートカット法によるSOI基板の作製方法概要を以下に説明する。シリコンウエハに水素イオンを注入することによって表面から所定の深さに微小気泡層を形成する。酸化シリコン膜を介して、水素イオンを注入したシリコンウエハを別のシリコンウエハに接合させる。しかる後熱処理を行うことで、該微小気泡層が劈開面となり、水素イオンを注入したウエハが薄膜状に剥離する。スマートカット法は水素イオン注入剥離法と呼ぶこともある。

**【0004】**

特許文献1では、単結晶シリコン層表面の平坦性向上や、単結晶シリコン層の欠陥修復のため、単結晶シリコン層の形成の後に、CMP処理や高温（1200以下程度）の熱処理を施している。

40

**【0005】**

また、スマートカット法を用いてシリコンウエハから単結晶シリコン層を剥離・転載した後、該シリコンウエハを再利用する方法が知られている（例えば、特許文献2参照）。特許文献2では、単結晶シリコン層をシリコンウエハから剥離した後、シリコンウエハをCMP処理等をすることで平坦化している。

**【先行技術文献】**

**【特許文献】**

**【0006】**

50

【特許文献 1】特開 2003 - 017671 号公報

【特許文献 2】特開平 11 - 097379 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献 1 のような方法で単結晶半導体層を形成する場合には、CMP 处理や高温の熱処理が必須となるため、大型の半導体基板（SOI 基板）を安価に提供することは困難である。例えば、大面積を実現するための現実的な選択肢としては、単結晶半導体層の貼り合わせ先の基板にガラス基板を用いることが挙げられるが、このようなガラス基板は耐熱性の面で上記の要求を満たすことができない。また、CMP 处理は、表面研磨処理であるため、大面積を均一に処理することは極めて困難である。

10

【0008】

上記問題に鑑み、CMP 处理や高温の熱処理を必須とせず、特性の良好な単結晶半導体層を作製することを目的の一とする。又は、このような単結晶半導体層を有する半導体基板（又は SOI 基板）を提供することを目的の一とする。

【0009】

また、特許文献 2 のような方法でシリコンウエハを再利用する場合には、半導体層の剥離・転載工程を経るたびに CMP 处理により研磨されるため、徐々にシリコンウエハの厚さが薄くなり再生が不可能になってしまう。

【0010】

上記問題に鑑み、半導体基板の再生回数を増やして、生産性を向上させることを目的の一とする。

20

【課題を解決するための手段】

【0011】

本発明の一態様は、第 1 の単結晶半導体層をシード層として気相エピタキシャル成長を行うことで、第 1 の単結晶半導体層上に第 2 の単結晶半導体層を形成し、両層の界面で分離を行うものである。この際、第 1 の単結晶半導体層に対する第 2 の単結晶半導体層の圧縮応力が高いことを利用して両層を分離している。

【0012】

また、上記分離後の第 1 の単結晶半導体層を、再度気相エピタキシャル成長させシード層として再利用する。この際、第 1 の単結晶半導体層にレーザー処理を行うことが好ましい。

30

【0013】

半導体基板の作製方法の一は、第 1 の基板上に第 1 の単結晶半導体層を設ける工程と、前記第 1 の単結晶半導体層上に、気相エピタキシャル成長法を用いて第 2 の単結晶半導体層を設ける工程と、前記第 1 の基板と第 2 の基板とを絶縁層を介して貼り合わせ、前記第 1 の基板と第 2 の基板との間に前記第 1 の単結晶半導体層及び前記第 2 の単結晶半導体層を設ける工程と、前記第 1 の基板と前記第 2 の基板とを前記第 1 の単結晶半導体層と前記第 2 の単結晶半導体層との界面で分離して、前記第 1 の基板上に前記第 1 の単結晶半導体層を設け且つ前記第 2 の基板上に前記第 2 の単結晶半導体層を設ける工程と、を有することを特徴とする。

40

【0014】

また、半導体基板の作製方法の他の一態様は、第 1 の基板と所定の深さに脆化層が形成された単結晶半導体基板とを絶縁層を介して貼り合わせる工程と、前記単結晶半導体基板と前記第 1 の基板とを前記脆化層から分離して、前記第 1 の基板上に第 1 の単結晶半導体層を設ける工程と、前記第 1 の単結晶半導体層上に、気相エピタキシャル成長法を用いて第 2 の単結晶半導体層を設ける工程と、前記第 1 の基板と第 2 の基板とを絶縁層を介して貼り合わせ、前記第 1 の基板と第 2 の基板との間に前記第 1 の単結晶半導体層及び前記第 2 の単結晶半導体層を設ける工程と、前記第 1 の基板と前記第 2 の基板とを前記第 1 の単結晶半導体層と前記第 2 の単結晶半導体層との界面で分離して、前記第 1 の基板上に前記

50

第1の単結晶半導体層を設け且つ前記第2の基板上に前記第2の単結晶半導体層を設ける工程と、を有することを特徴とする。

【0015】

また、半導体装置の作製方法の一態様は、第1の基板上に単結晶半導体層を設ける工程と、前記単結晶半導体層上に、気相エピタキシャル成長法を用いて、光電変換層を設ける工程と、前記光電変換層上に第1の導電膜を設ける工程と、前記第1の基板と第2の基板とを絶縁層を介して貼り合わせ、前記第1の基板と第2の基板との間に、前記単結晶半導体層、前記光電変換層、及び前記第1の導電層を設ける工程と、前記第1の基板と前記第2の基板とを前記単結晶半導体層と前記光電変換層との界面で分離して、前記第1の基板上に前記単結晶半導体層を設け且つ前記第2の基板上に前記第1の導電層及び前記光電変換層を設ける工程と、前記光電変換層上に第2の導電層を設ける工程と、を有することを特徴とする。 10

【0016】

また、半導体装置の作製方法の他の一態様は、第1の基板上に第1の単結晶半導体層を設ける工程と、前記第1の単結晶半導体層上に、気相エピタキシャル成長法を用いて、一導電型を有する第2の単結晶半導体層、真性な第3の単結晶半導体層、前記一導電型と反対の導電型を有する第4の単結晶半導体層を順に形成することで、光電変換層を設ける工程と、前記光電変換層上に第1の導電膜を設ける工程と、前記第1の基板と第2の基板とを絶縁層を介して貼り合わせ、前記第1の基板と第2の基板との間に、前記第1の単結晶半導体層、前記光電変換層、及び前記第1の導電層を設ける工程と、前記第1の基板と前記第2の基板とを前記第1の単結晶半導体層と前記第2の単結晶半導体層との界面で分離して、前記第1の基板上に前記第1の単結晶半導体層を設け且つ前記第2の基板上に前記第1の導電層及び前記光電変換層を設ける工程と、前記光電変換層上に第2の導電層を設ける工程と、を有することを特徴とする。 20

【0017】

なお、第2の単結晶半導体層として単結晶シリコン層を形成する場合、原料ガスにおいて、シラン系ガスの流量に対する水素の流量を4倍以上10倍以下（好ましくは5倍以上7倍以下）として気相エピタキシャル成長を行うことが好ましい。

【0018】

また、第1の基板及び第2の基板として、ガラス基板を用いると良い。 30

【0019】

なお、本明細書において単結晶とは、ある結晶軸に注目した場合、その結晶軸の方向が試料のどの部分においても同じ方向を向いている結晶のことをいい、かつ結晶と結晶との間に結晶粒界が存在しない結晶である。なお、本明細書では、結晶欠陥やダングリグボンドを含んでいても、上記のように結晶軸の方向が揃っており、粒界が存在していない結晶であるものは単結晶とする。

【0020】

また、本明細書において半導体基板とは、バルク状のシリコンウエハに薄い単結晶半導体層が設けられた基板や、絶縁基板に薄い単結晶半導体層が設けられた基板を含む。

【0021】

また、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路及び電子機器は全て半導体装置に含まれる。 40

【0022】

また、本明細書中において光電変換装置とは、光エネルギーと電気エネルギーとを変換する装置全般を指し、例えば太陽電池等がある。

【0023】

また、本明細書中において表示装置とは、発光装置や液晶表示装置を含む。発光装置は発光素子を含み、液晶表示装置は液晶素子を含む。発光素子は、電流または電圧によって輝度が制御される素子をその範疇に含んでおり、具体的には無機EL（Electro Luminescence）、有機EL等がある。 50

**【発明の効果】****【0024】**

気相エピタキシャル成長法によって形成された第2の単結晶半導体層の圧縮応力を利用して、第2の単結晶半導体層を第1の単結晶半導体層から分離している。これにより、第2の単結晶半導体層において欠陥等の発生を防止できるため、高温の熱処理を必須としない。また、分離後の第2の単結晶半導体層は平坦性が高いため、C M P処理などの平坦化処理が必須としない。このように、半導体基板（SOI基板）の大面積化が容易となる。

**【0025】**

また、第1の単結晶半導体層と、気相エピタキシャル成長法によって形成された第2の単結晶半導体層との界面において分離する方法を用いている。これにより、第1の単結晶半導体層をシード層として繰り返し利用することで、再生処理が効率化され、半導体基板（SOI基板）の生産性を向上させることができる。

10

**【図面の簡単な説明】****【0026】**

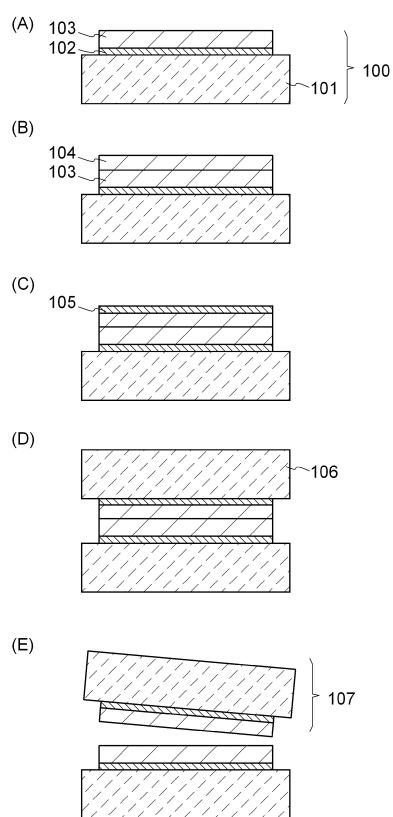

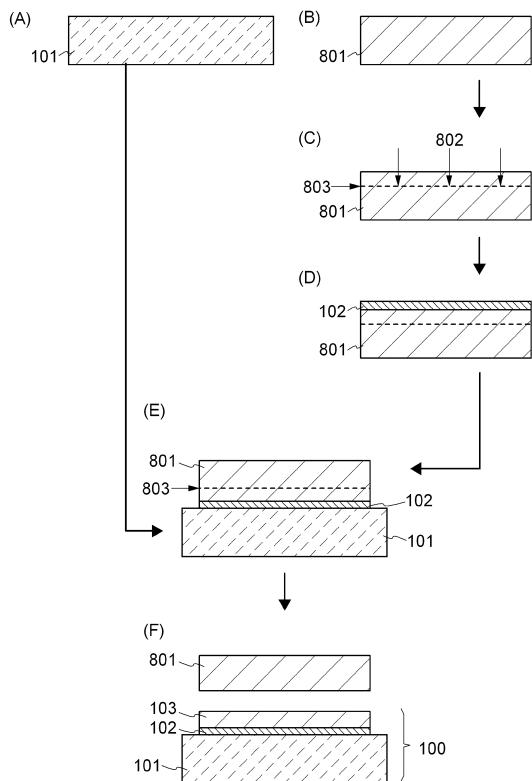

【図1】半導体基板の作製方法の一例を示す図である。

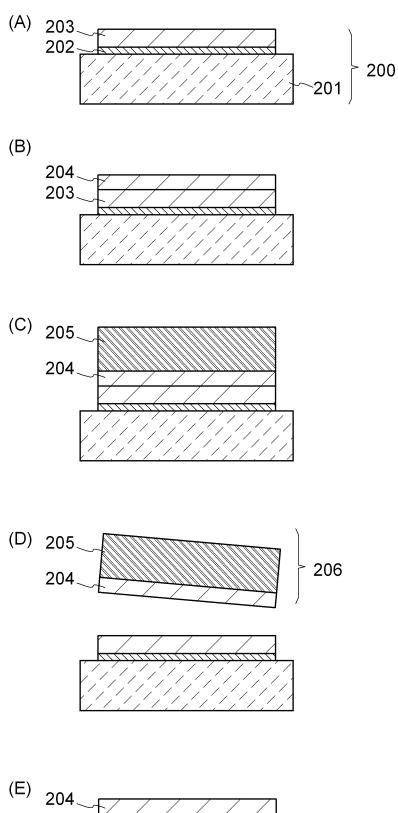

【図2】単結晶半導体層の作製方法の一例を示す図である。

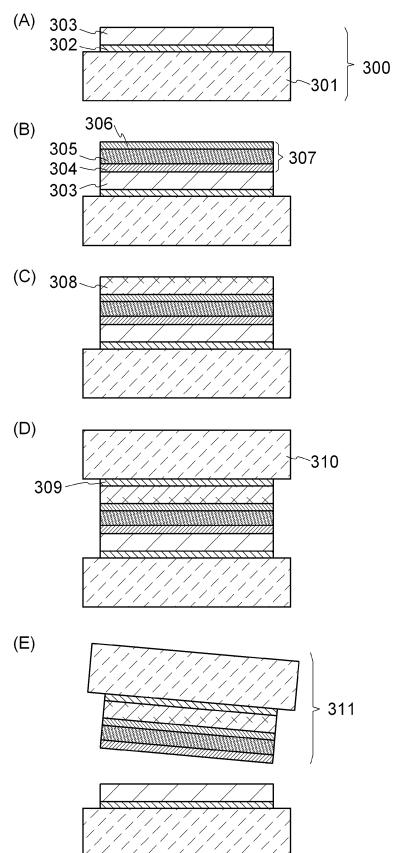

【図3】半導体装置の作製方法の一例を示す図である。

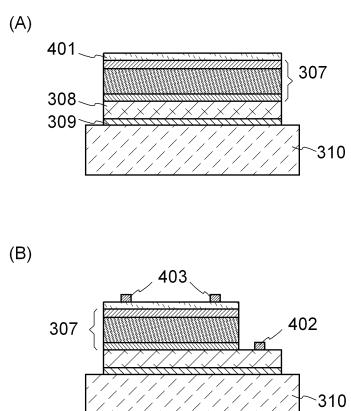

【図4】半導体装置の作製方法の一例を示す図である。

【図5】半導体装置を用いた電子機器を示す図である。

20

【図6】半導体装置を用いた電子機器を示す図である。

【図7】分離の様子を示すTEM像である。

【図8】半導体基板の作製方法の一例を示す図である。

**【発明を実施するための形態】****【0027】**

本明細書中に開示する発明の実施の形態について、図面を用いて以下に説明する。但し、本明細書中に開示する発明は、以下の説明に限定されず、趣旨及びその範囲から逸脱することなくその形態および詳細を変更し得ることは当業者であれば容易に理解される。従って、本明細書中に開示する発明は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

30

**【0028】****(実施の形態1)**

本実施の形態では、半導体基板（SOI基板とも呼ぶ）の作製方法の一例に関して図面を参照して説明する。

**【0029】**

まず、第1のSOI基板100（シード基板とも呼ぶ）を準備する（図1（A）参照）。

。

**【0030】**

第1のSOI基板100は、第1の基板101上に絶縁層102を介して第1の単結晶半導体層103（シード層とも呼ぶ）が設けられたものを用いることができる。

40

**【0031】**

第1のSOI基板100の作製方法の一例を図8に示す。第1の基板101及びシリコンウエハ等の単結晶半導体基板801を準備する（図8（A）、（B）参照）。単結晶半導体基板801の表面から電界で加速されたイオンでなるイオンビーム802を照射して、所定の深さの領域にイオンを導入することで脆化層803を形成する（図8（C）参照）。次に絶縁層102を介して第1の基板101と貼り合わせる（図8（D）、（E）参照）。そして熱処理を行い脆化層803から分離することで第1の基板101上に第1の単結晶半導体層103を形成する（図8（F）参照）。第1の単結晶半導体層103の平坦性を高めるためにレーザー光の照射処理を施すことも効果的である。このようにして、

50

第1のS O I基板100を作製する。

**【0032】**

ここで第1の基板101としては、絶縁体でなる基板を用いることができる。具体的には、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイア基板が挙げられる。なお、上記ガラス基板においては、一般に、ホウ酸( $B_2O_3$ )を多く含有させることでガラスの耐熱性が向上するが、ホウ酸と比較して酸化バリウム( $BaO$ )を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ より $BaO$ を多く含むガラス基板を用いると良い。他にも、第1の基板101として単結晶半導体基板(例えば、単結晶シリコン基板等)を用いてもよい。本実施の形態では、第1の基板101としてガラス基板を用いる場合について説明する。第1の基板101として大面積化が可能で安価なガラス基板を用いることにより、低コスト化を図ることができる。

10

**【0033】**

更に、上記第1の基板101に関しては、その表面をあらかじめ洗浄しておくことが好み。具体的には、第1の基板101に対して、塩酸過水(HPM)、硫酸過水(SPM)、アンモニア過水(APM)、希フッ酸(DHF)等を用いて超音波洗浄を行う。このような洗浄処理を行うことによって、第1の基板101表面の平坦性向上や、第1の基板101表面に残存する研磨粒子の除去などが可能である。

**【0034】**

また、絶縁層102は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜等の単層、又はこれらを積層させた膜を用いることができる。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、濃度範囲として酸素が55～65原子%、窒素が1～20原子%、Siが25～35原子%、水素が0.1～10原子%の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、濃度範囲として酸素が15～30原子%、窒素が20～35原子%、Siが25～35原子%、水素が15～25原子%の範囲で含まれるものという。

20

**【0035】**

なお、ここで分離した単結晶半導体基板801は、CMP処理、高温熱処理を行い繰り返し利用することで、第1のS O I基板100を複数枚作製することができる。この単結晶半導体基板の再生処理を第1の再生処理工程と呼ぶ。

30

**【0036】**

次に、第1の単結晶半導体層103上に、気相エピタキシャル成長法によって第2の単結晶半導体層104を形成する(図1(B)参照)。

**【0037】**

第2の単結晶半導体層104は、第1の単結晶半導体層103と同様の材料を用いて形成すれば良いが、例えば、単結晶シリコン層を形成する場合には、シラン系ガス(珪素の水素化合物を含むガス、代表的にはモノシランやジシラン)と水素との混合ガスを原料ガスとする気相成長法(CVD法などを含む)を用いて形成することができる。

40

**【0038】**

上記気相エピタキシャル成長に用いる原料ガスは、シラン系ガスに対して、流量比で4倍以上10倍以下、好ましくは5倍以上7倍以下の水素を含むガスを用いることが好み。つまり、シラン系ガスの水素希釈比(水素/シラン系ガス)を4倍以上10倍以下、好ましくは5倍以上7倍以下とする。シラン系ガスは代表的にはシランであり、その他ジシラン( $Si_2H_6$ )などを用いることもできる。また、原料ガスに、希ガスを添加してもよい。

**【0039】**

エピタキシャル成長に使用するプラズマCVD装置としては、電力周波数が10MHz以上200MHz以下、代表的には13.56MHz或いは60MHzの高周波(RF)

50

プラズマCVD装置や、電力周波数が1GHz以上5GHz以下、代表的には2.45GHzのマイクロ波プラズマCVD装置などを用いることができる。

#### 【0040】

エピタキシャル成長の条件は適宜設定することができるが、一例としては、原料ガスとしてシランと水素の混合ガスを用い、シランと水素の流量(ccm)比をSiH<sub>4</sub>:H<sub>2</sub>=25(ccm):150(ccm)、基板温度を280°C、高周波電源の出力を30W、電力周波数を27MHzとすればよい。このような条件(特に流量比)で形成した第2の単結晶半導体層104は圧縮応力が高く、第1の単結晶半導体層103との界面で容易に分離することができるようになる。なお、成膜の際の基板温度を200°C以上300°C以下程度とした場合には、欠陥の少ない良好な第2の単結晶半導体層104を得ることができる。また、原料ガスの総流量を増大させることにより、成膜に掛かる時間を低減し、結晶性を向上させることが可能である。10

#### 【0041】

第2の単結晶半導体層104の膜厚は、適宜必要な大きさとすればよいが、膜厚を増大させた場合にはそれに従って圧縮応力が大きくなる傾向にあるため、第1の単結晶半導体層103と第2の単結晶半導体層104との界面での分離をより容易なものとすることができる。例えば、第2の単結晶半導体層104の厚さは、100nm以上10μm以下程度とすればよい。

#### 【0042】

なお、第2の単結晶半導体層104のエピタキシャル成長を行う前には、第1の単結晶半導体層103表面に形成されている自然酸化膜などは除去しておくことが好ましい。第1の単結晶半導体層103表面に酸化膜などが存在する場合には、エピタキシャル成長の進行を妨げ、第2の単結晶半導体層104の結晶性が低下する可能性があるためである。このような酸化膜の除去は、フッ酸系の溶液を用いて行うことができる。具体的には、フッ酸(又は希フッ酸)により第1の単結晶半導体層103の表面が撥水性を示すまで処理すればよい。同様に、汚染物除去の観点からは、硫酸過水(SPM)、アンモニア過水(APM)、塩酸過水(HPM)、希フッ酸(DHF)などを用いて第1の単結晶半導体層103の表面を洗浄しておくことが好ましい。20

#### 【0043】

次に、第2の単結晶半導体層104上に、絶縁層105を形成する(図1(C)参照)30

。

#### 【0044】

絶縁層105は、酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、窒化酸化シリコン膜等の絶縁層を単層で、又は積層させて形成することができる。これらの膜は、熱酸化法、CVD法、スパッタリング法等を用いて形成することができる。

#### 【0045】

本明細書中において、酸化窒化シリコンとは、その組成において、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が50原子%以上70原子%以下、窒素が0.5原子%以上15原子%以下、珪素が25原子%以上35原子%以下、水素が0.1原子%以上10原子%以下の範囲で含まれるものという。また、窒化酸化シリコンとは、その組成において、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が5原子%以上30原子%以下、窒素が20原子%以上55原子%以下、珪素が25原子%以上35原子%以下、水素が10原子%以上30原子%以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)や、水素前方散乱法(HFS: Hydrogen Forward Scattering)を用いて測定した場合のものである。また、構成元素の含有比率の合計は、100原子%を超えない。40

#### 【0046】

その後、絶縁層105を介して第1の基板101と第2の基板106とを貼り合わせる(図1(D)参照)。絶縁層105は、第2の単結晶半導体層104と第2の基板10650

とを接合させる接合層として機能する。

#### 【0047】

第2の基板106は、第1の基板101と同様の基板を用いればよい。本実施の形態では、第2の基板106としてガラス基板を用いる場合について説明する。第2の基板106として大面積化が可能で安価なガラス基板を用いることにより、低コスト化を図ることができる。第2の基板106に対して第1の基板101と同様に、塩酸過水(HPM)、硫酸過水(SPM)、アンモニア過水(APM)、希フッ酸(DHF)等を用いて表面を洗浄するとよい。

#### 【0048】

なお、第1の基板101と第2の基板106との貼り合わせを行う前に、絶縁層105の表面処理を行ってもよい。表面処理としては、プラズマ処理、オゾン処理、メガソニック洗浄、2流体洗浄(純水や水素添加水等の機能水を窒素等のキャリアガスとともに吹き付ける方法)又はこれらを組み合わせて用いることで、絶縁層105の表面の有機物等のゴミを除去し親水化することができる。その結果、第1の基板101と第2の基板106との接合強度を向上させることができる。特に、絶縁層105の表面にプラズマ処理を行った後、オゾン処理、メガソニック洗浄、2流体洗浄等を行うと効果的である。

#### 【0049】

また、第1の基板101と第2の基板106とを貼り合わせる前に、第2の基板106上に、窒素含有層(例えば、窒化シリコン膜や窒化酸化シリコン膜等の窒素を含有する絶縁膜)を形成してもよい。窒素含有層は、第2の基板106に含まれるナトリウム等の元素が第2の単結晶半導体層104に拡散することを防ぐためのバリア層として機能する。窒素含有層に対して絶縁層105と同様に、プラズマ処理、オゾン処理、メガソニック洗浄、2流体洗浄等の表面処理を行うと接合強度を向上させることができる。

#### 【0050】

また、第1の基板101と第2の基板106と貼り合わせた後に、接合強度を増加させるための熱処理を行っても良い。熱処理の温度は、適宜設定することができるが、高温(例えば600以上)の熱処理を行う場合には第1の単結晶半導体層103と第2の単結晶半導体層104との密着性が強化されてしまい、界面での分離が困難となることがある点に留意すべきである。上記熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA(瞬間熱アニール、Rapid Thermal Anneal)装置、マイクロ波加熱装置などを用いることができる。

#### 【0051】

次に、第1の基板101と第2の基板106とを、第1の単結晶半導体層103と第2の単結晶半導体層104との界面で分離して、第1の基板101上に第1の単結晶半導体層103を設け、第2の基板106上に第2の単結晶半導体層104を設ける(図1(E)参照)。この際、第1の単結晶半導体層103に対する第2の単結晶半導体層104の圧縮応力が高いため、容易に分離することができる。

#### 【0052】

上記分離の方法として、基板分離装置などによる力学的方法(単純に引き剥がす方法)を用いることができる。また、ウォータージェットのように第1の単結晶半導体層103と第2の単結晶半導体層104との界面に分離を促進させる処理を施す方法などを用いても良い。

#### 【0053】

また、第2の単結晶半導体層104の薄膜化のための処理や、平坦性をより一層向上させるための処理を行っても良い。該処理としては、ドライエッティングまたはウェットエッティングの一方、または双方を組み合わせて用いることができる。

#### 【0054】

以上の工程により、半導体基板(第2のSOI基板107)を作製することができる。

#### 【0055】

本実施の形態では、気相エピタキシャル成長法によって形成された第2の単結晶半導体

10

20

30

40

50

層 104 の応力を利用して、第 1 の S O I 基板 100 から第 2 の単結晶半導体層 104 を分離している。これにより、第 2 の単結晶半導体層 104 中において欠陥等の発生を防止できるため、高温の熱処理を必須としない。また、分離後の第 2 の単結晶半導体層 104 は平坦性が高いため、C M P 処理などの平坦化処理も必須としない。このように、本実施の形態の作製方法を用いることで、特性が良好で且つ大面積な半導体基板（第 2 の S O I 基板 107）を提供することができる。

#### 【 0056 】

そして、得られた半導体基板（第 2 の S O I 基板 107）を用いることで、特性が良好な薄膜トランジスタ等の半導体装置を作製することができる。薄膜トランジスタを作製する場合は、第 2 の単結晶半導体層 104 を用いて島状の半導体層を形成し、ゲート絶縁膜、ゲート電極を形成すればよい。そして層間絶縁膜、電極等を形成して素子としての形状を整える。n 型の薄膜トランジスタ又は p 型の薄膜トランジスタを作製する場合は、島状の半導体層に対して導電性を付与する元素の添加を行えばよい。

#### 【 0057 】

また、本実施の形態では、第 1 の単結晶半導体層 103 と、気相エピタキシャル成長法により形成した第 2 の単結晶半導体層 104 との界面で分離する方法を用いている。これにより、第 1 の単結晶半導体層 103 は、厚さが減少しないため、シード層として繰り返し利用することができる。すなわち、第 1 の S O I 基板 100 をシード基板として繰り返し利用して第 2 の S O I 基板 107 を作製することができ、半導体基板の生産性を大幅に向上させることができる。ここで第 1 の S O I 基板 100 の再生処理を第 2 の再生処理工程と呼ぶ。

#### 【 0058 】

第 2 の再生処理工程を行う際、第 1 の単結晶半導体層 103 にレーザー光の照射処理を行ってもよい。レーザー光の照射により、第 1 の単結晶半導体層 103 中の欠陥を低減し、表面の平坦性を高めることができる。レーザー光の照射処理は、C M P 処理や高温の熱処理に比べて処理時間を短縮させ、また歩留まりを向上させることができる。

#### 【 0059 】

また、第 1 の S O I 基板 100 をシード基板として第 2 の再生処理行程を繰り返し行うことで第 1 の単結晶半導体層 103（シード層）の劣化が懸念される場合は、第 2 の S O I 基板 107 の方をシード基板として用い、第 2 の単結晶半導体層 104 をシード層としてエピタキシャル成長を行うことでシード層の劣化を防止することが可能である。

#### 【 0060 】

また、第 2 の再生処理と、上述した第 1 の再生処理とを合わせて用いることで、生産性が相乗的に向上し、得られる半導体基板の枚数を飛躍的に増大させることができる。

#### 【 0061 】

本実施の形態で示した構成は、本明細書の他の実施の形態又は実施例で示す構成と適宜組み合わせて用いることができる。

#### 【 0062 】

##### （実施の形態 2）

本実施の形態では、単結晶半導体層の作製方法の一例に関して図面を参照して説明する。

#### 【 0063 】

まず、S O I 基板 200（シード基板とも呼ぶ）を準備する（図 2（A）参照）。

#### 【 0064 】

S O I 基板 200 は、実施の形態 1 で示した第 1 の S O I 基板 100 と同様の方法を用いて作製し、基板 201 上に絶縁層 202 を介して第 1 の単結晶半導体層 203（シード層とも呼ぶ）が設けられた構造とすればよい。

#### 【 0065 】

すなわち、単結晶半導体基板の一部を基板 201 上に転載することで第 1 の単結晶半導体層 203 を形成することができる。ここで用いた単結晶半導体基板は、実施の形態 1 と

10

20

30

40

50

同様に第1の再生処理工程を行い繰り返し利用することができる。

【0066】

次に、第1の単結晶半導体層203上に、実施の形態1と同様に気相エピタキシャル成長法を用いて第2の単結晶半導体層204を形成する(図2(B)参照)。

【0067】

次いで、SOI基板200及び第2の単結晶半導体層204を加熱し、所定の温度に保持した状態で、第2の単結晶半導体層204上に金属を含有する材料を塗布(又はスクリーン印刷)して、金属層205を形成する(図2(C)参照)。加熱温度は、金属層205を形成することができる温度であれば特に限定されない。金属層205は、アルミニウムや銅などの材料を用いて形成することができる。なお、スパッタリング法などの方法を用いて金属層205を形成しても良い。10

【0068】

その後、SOI基板200、第2の単結晶半導体層204及び金属層205を冷却することで、SOI基板200と第2の単結晶半導体層204とを、第1の単結晶半導体層203と第2の単結晶半導体層204との界面において分離して、金属層205と第2の単結晶半導体層204の積層構造体206を形成する(図2(D)参照)。冷却温度は特に限定されないが、例えば、室温程度とすることができる。もちろん、室温より低い温度にまで冷却しても良い。

【0069】

上記の方法でSOI基板200から第2の単結晶半導体層204を分離することができる原因是、単結晶半導体材料と金属材料の熱膨張係数が大きく異なるためである。この原理により、金属層205を形成する際の温度と冷却後の温度との差が大きいほど、良好な分離が実現できると言える。20

【0070】

その後、金属層205を除去することで第2の単結晶半導体層204(自立膜)を形成することができる(図2(E)参照)。

【0071】

なお、本実施の形態においては、最終的に金属層205を除去する構成を採用しているが、本実施の形態はこれに限定されない。例えば、金属層205を電極などに利用する場合には、金属層205を除去せずに残存させる構成としても良い。30

【0072】

また、形成された第2の単結晶半導体層204は、そのまま用いても良いし、何らかの基板に貼り合わせて用いても良い。

【0073】

なお、上記分離の際に、基板分離装置などによる力学的方法(単純に引き剥がす方法)や、ウォータージェットのような分離を促進させる方法などを併用しても良い。

【0074】

また、得られた第2の単結晶半導体層204に対して、レーザー光の照射処理を行っても良い。これにより、第2の単結晶半導体層204中の欠陥をさらに低減し、表面の平坦性を向上させた半導体層を得ることができる。また、第2の単結晶半導体層204に対して熱処理を施して、その欠陥を低減させても良い。40

【0075】

また、第2の単結晶半導体層204の薄膜化のための処理や、平坦性をより一層向上させるための処理を行っても良い。該処理としては、ドライエッチングまたはウェットエッティングの一方、または双方を組み合わせて用いることができる。

【0076】

本実施の形態では、気相エピタキシャル成長法によって形成された第2の単結晶半導体層204の応力をを利用して、SOI基板200から第2の単結晶半導体層204を分離している。これにより、第2の単結晶半導体層204自体には欠陥などがほとんど発生しないため、高温の熱処理を必須としない。また、分離後の第2の単結晶半導体層204は平50

坦性が高いため、C M P処理などの平坦化処理も必須としない。このように、本実施の形態の作製方法を用いることで、特性が良好で且つ大面積な単結晶半導体層を提供することができる。

#### 【0077】

一方、SOI基板200は、実施の形態1と同様に、第2の再生処理工程を行うことで繰り返しシード基板として利用することができ、単結晶半導体層の生産性を向上させることができる。

#### 【0078】

また、第2の再生処理と、上述した第1の再生処理とを合わせて用いることで、生産性が相乗的に向上し、得られる単結晶半導体層の数を飛躍的に増大させることができることである。

#### 【0079】

本実施の形態で示した構成は、本明細書の他の実施の形態又は実施例で示す構成と適宜組み合わせて用いることができる。

#### 【0080】

##### (実施の形態3)

本実施の形態では、半導体装置の作製方法の一例として、光電変換装置の作製方法について図面を参照して説明する。

#### 【0081】

まず、SOI基板300(シード基板とも呼ぶ)を準備する(図3(A)参照)。

#### 【0082】

SOI基板300は、実施の形態1で示した第1のSOI基板100と同様の方法を用いて作製し、第1の基板301上に絶縁層302を介して第1の単結晶半導体層303(シード層とも呼ぶ)が設けられた構造とすればよい。

#### 【0083】

すなわち、単結晶半導体基板の一部を第1の基板301上に転載することで第1の単結晶半導体層303を形成することができる。ここで用いた単結晶半導体基板は、実施の形態1と同様に第1の再生処理工程を行い繰り返し利用することができる。

#### 【0084】

次に、第1の単結晶半導体層303上に第2の単結晶半導体層304を形成する(図3(B)参照)。第2の単結晶半導体層304は、例えば、気相エピタキシャル成長法を用いて形成する。

#### 【0085】

第2の単結晶半導体層304は、第1の単結晶半導体層303をシード層とし、第1の単結晶半導体層303の結晶性の影響を受けた半導体層となる。

#### 【0086】

第2の単結晶半導体層304としてシリコン層を形成する場合には、シラン系ガス(珪素の水素化合物を含むガス、代表的にはモノシランやジシラン)と水素との混合ガスと、p型を付与する元素を含んだガス(例えばジボラン)とを原料ガスとする気相成長法(CVD法などを含む)を用いて形成することができる。これにより、第2の単結晶半導体層304は、p型シリコン層となり、光電変換装置のp型半導体層とすることができます。

#### 【0087】

エピタキシャル成長は、シラン系ガスに対する水素の流量比が、4倍以上10倍以下(好ましくは5倍以上7倍以下)とすることが好ましい。つまり、シラン系ガスの水素希釈比(水素/シラン系ガス)を4倍以上10倍以下、好ましくは5倍以上7倍以下とする。シラン系ガスは代表的にはシランであり、その他ジシラン(Si<sub>2</sub>H<sub>6</sub>)などを用いることもできる。また、原料ガスに、希ガスを添加してもよい。

#### 【0088】

エピタキシャル成長に使用するプラズマCVD装置としては、電力周波数が10MHz以上200MHz以下、代表的には13.56MHz或いは60MHzの高周波(RF)

プラズマCVD装置や、電力周波数が1GHz以上5GHz以下、代表的には2.45GHzのマイクロ波プラズマCVD装置などを用いることができる。

#### 【0089】

エピタキシャル成長の条件は適宜設定することができるが、一例としては、原料ガスとしてシランと水素の混合ガスを用い、シランと水素の流量(ccm)比をSiH<sub>4</sub>:H<sub>2</sub>=25(ccm):150(ccm)、基板温度を280°C、高周波電源の出力を30W、電力周波数を27MHzとすればよい。このような条件(特に流量比)で形成した第2の単結晶半導体層304は圧縮応力が高く、第1の単結晶半導体層303との界面で容易に分離することができるようになる。なお、成膜の際の基板温度を200°C以上300°C以下程度とした場合には、欠陥の少ない良好な第2の単結晶半導体層304を得ることができる。また、原料ガスの総流量を増大させることにより、成膜に掛かる時間を低減し、結晶性を向上させることができると10。

#### 【0090】

第2の単結晶半導体層304の膜厚は、1nm以上100nm以下程度(好ましくは10nm以上80nm以下程度)とすればよい。

#### 【0091】

なお、第2の単結晶半導体層304のエピタキシャル成長を行う前に、第1の単結晶半導体層303の表面に形成されている自然酸化膜などは除去しておくことが好ましい。第1の単結晶半導体層303の表面に酸化膜が存在する場合には、エピタキシャル成長の進行を妨げ、第2の単結晶半導体層304の結晶性が低下する可能性がある。酸化膜の除去は、フッ酸系の溶液などを用いて行うことができる。

#### 【0092】

次に、第2の単結晶半導体層304上に、第3の単結晶半導体層305を形成する(図3(B)参照)。第3の単結晶半導体層305は、例えば気相エピタキシャル成長法を用いて形成する。

#### 【0093】

第3の単結晶半導体層305としてシリコン層を形成する場合には、シラン系ガス(珪素の水素化合物を含むガス、代表的にはモノシランやジシラン)と水素との混合ガスとを原料ガスとする気相成長法(CVD法などを含む)を用いて形成することができる。これにより、第3の単結晶半導体層305は、真性シリコン層となり、光電変換装置の真性半導体層とすることができます。

#### 【0094】

第3の単結晶半導体層305の膜厚は、0.1μm以上程度(好ましくは1μm以上程度)とすればよい。

#### 【0095】

なお、ここでいう真性半導体層とは、半導体層に含まれるp型もしくはn型を付与する不純物が $1 \times 10^{20} \text{ cm}^{-3}$ 以下の濃度であり、酸素及び窒素が $9 \times 10^{19} \text{ cm}^{-3}$ 以下の濃度であり、暗伝導度に対して光伝導度が1000倍以上である半導体層を指す。また本明細書では、真性半導体層をi型半導体層とも呼ぶ。

#### 【0096】

また、第3の単結晶半導体層305のエピタキシャル成長を行う前に、第2の単結晶半導体層304の表面に形成された自然酸化膜などは除去しておくことが好ましい。

#### 【0097】

次に、第3の単結晶半導体層305上に、第4の単結晶半導体層306を形成する(図3(B)参照)。第4の単結晶半導体層306は、例えば気相エピタキシャル成長法を用いて形成する。

#### 【0098】

第4の単結晶半導体層306としてシリコン層を形成する場合には、シラン系ガス(珪素の水素化合物を含むガス、代表的にはモノシランやジシラン)と水素との混合ガスと、n型を付与する元素を含んだガス(例えばフォスフィン)とを原料ガスとする気相成長法

10

20

30

40

50

(CVD法などを含む)を用いて形成することができる。これにより、第4の単結晶半導体層306は、n型シリコン層となり、光電変換装置のn型半導体層とすることができます。

#### 【0099】

第4の単結晶半導体層306の膜厚は、1nm以上100nm以下程度(好ましくは10nm以上80nm以下程度)とする。

#### 【0100】

また、第4の単結晶半導体層306のエピタキシャル成長を行う前に、第3の単結晶半導体層305の表面に形成された自然酸化膜などは除去しておくことが好ましい。

#### 【0101】

以上のようにして、光電変換装置の光電変換層307(p型半導体層、i型半導体層、及びn型半導体層)を形成することができる。

#### 【0102】

なお、本実施の形態では、第2の単結晶半導体層304をp型半導体層とし、第4の単結晶半導体層306をn型半導体層としたが、これに限定されず、第2の単結晶半導体層304をn型半導体層とし、第4の単結晶半導体層306をp型半導体層としてもよい。第2の単結晶半導体層304と第4の単結晶半導体層306とが反対の導電型を示すようになる。

#### 【0103】

次いで、第4の単結晶半導体層306上に、光電変換装置の第1の電極となる第1の導電層308を形成する(図3(C)参照)。

#### 【0104】

第1の導電層308は、アルミニウム、銀、チタン、タンタル、タンゲステン、モリブデン、銅から選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料を用いることができる。また、これらの材料を積層して用いてもよい。本実施の形態では、低抵抗かつ低成本のアルミニウムを用い、アルミニウムの上面と下面に窒化チタンを設ける構造とした。第4の単結晶半導体層306とアルミニウムとの間に窒化チタンを設けることで、アルミニウムが第4の単結晶半導体層306に拡散することを防止できる。

#### 【0105】

次に、第1の導電層308上に、絶縁層309を形成する(図3(D)参照)。

#### 【0106】

絶縁層309は、酸化シリコン、窒化シリコン、酸化窒化シリコン、または酸化アルミニウムなどを、熱酸化法、CVD法、スパッタリング法等を用いて形成することができる。本実施の形態では、絶縁層309を酸化アルミニウムによって形成した。そのため、第1の導電層308と絶縁層309とをスパッタリング法を用いて連続成膜することが可能である。

#### 【0107】

その後、絶縁層309を介して第1の基板301と第2の基板310と貼り合わせる(図3(D)参照)。絶縁層309は、光電変換層307と第2の基板310とを接合させる接合層として機能する。

#### 【0108】

ここで、絶縁層309とアルミニウムとの間には窒化チタンが設けられているため、絶縁層309が酸化アルミニウムのように酸素を含む場合にも、アルミニウムの酸化を防ぐことができる。

#### 【0109】

なお、第1の基板301と第2の基板310との貼り合わせを行う前に、絶縁層309の表面処理を行ってもよい。表面処理としては、プラズマ処理、オゾン処理、メガソニック洗浄、2流体洗浄(純水や水素添加水等の機能水を窒素等のキャリアガスとともに吹き付ける方法)又はこれらを組み合わせて用いることで、絶縁層309の表面の有機物等のゴミを除去し親水化することができる。その結果、第1の基板301と第2の基板310

10

20

30

40

50

との接合強度を向上させることができる。特に、絶縁層309の表面にプラズマ処理を行った後、オゾン処理、メガソニック洗浄、2流体洗浄等を行うと効果的である。

#### 【0110】

また、第1の基板301と第2の基板310とを貼り合わせる前に、第2の基板310上に、窒素含有層（例えば、窒化シリコン膜や窒化酸化シリコン膜等の窒素を含有する絶縁膜）を形成してもよい（図示せず）。窒素含有層は、第2の基板310に含まれるナトリウム等の元素が第2の単結晶半導体層304に拡散することを防ぐためのバリア層として機能する。窒素含有層に対して絶縁層309と同様に、プラズマ処理、オゾン処理、メガソニック洗浄、2流体洗浄等の表面処理を行うと接合強度を向上させることができる。

#### 【0111】

また、第1の基板301と第2の基板310とを貼り合わせた後に、接合強度を増加させるための熱処理を行っても良い。熱処理の温度は、適宜設定することができるが、高温（例えば600以上）の熱処理を行う場合には第1の単結晶半導体層303と第2の単結晶半導体層304との密着性が強化されてしまい、界面での分離が困難となることがある点に留意すべきである。上記熱処理には、拡散炉、抵抗加熱炉などの加熱炉、RTA（瞬間熱アニール、Rapid Thermal Anneal）装置、マイクロ波加熱装置などを用いることができる。

10

#### 【0112】

次に、第1の基板301と第2の基板310とを、第1の単結晶半導体層303と第2の単結晶半導体層304との界面で分離して、第1の基板301上に第1の単結晶半導体層303を設け、第2の基板310上に光電変換層307を設ける（図3（E）参照）。この際、第1の単結晶半導体層303に対する第2の単結晶半導体層304の圧縮応力が高いため、容易に分離することができる。

20

#### 【0113】

また、実施の形態2で示した方法を適用し、SOI基板300、光電変換層307、及び第1の導電層308を冷却してもよい。第1の導電層308が実施の形態2の金属層205と同様の効果を奏し、分離が促進される。

#### 【0114】

上記分離の方法として、基板分離装置などによる力学的方法（単純に引き剥がす方法）を用いることができる。また、ウォータージェットのように第1の単結晶半導体層303と第2の単結晶半導体層304との界面に分離を促進させる処理を施す方法などを用いても良い。

30

#### 【0115】

ここまで工程により、第2の基板310上に第1の導電層308及び光電変換層307が設けられた積層構造体311を得ることができる。

#### 【0116】

次いで、第2の単結晶半導体層304上に、光電変換装置の第2の電極として第2の導電層401を形成する（図4（A）参照）。第2の導電層401は、光電変換装置の受光面電極層として機能する。

#### 【0117】

40

第2の導電層401は透光性を有する導電膜を用いて形成することができ、酸化インジウム・スズ合金（ITO）膜、酸化インジウム・酸化亜鉛合金膜、酸化亜鉛膜、又は酸化スズ膜、などの酸化物金属膜を用いればよい。第2の導電層401はスパッタリング法や真空蒸着法を用いて形成することができる。

#### 【0118】

次に、第2の導電層401及び光電変換層307をエッチングして、第1の導電層308の一部を露出させる（図4（B）参照）。

#### 【0119】

エッチングはレーザー光の照射処理により行うことができる。レーザー光を用いると新たにマスクを設けること必要がない。また、第2の導電層401を選択的に形成し第2の

50

導電層 401 をマスクとしてエッチングを行ってもよく、この場合も新たにマスクを設ける必要がない。もちろん、レジストや絶縁層を用いてマスクを形成しエッチングを行ってもよい。

#### 【 0120 】

その後、第1の導電層 308 に電気的に接続する第1の補助電極として第3の導電層 402、第2の導電層 401 に電気的に接続する第2の補助電極として第4の導電層 403 を形成する（図4（B）参照）。

#### 【 0121 】

第3の導電層 402 及び第4の導電層 403 は、銀インクをスクリーン印刷することにより形成ができる。第4の導電層 403（上部電極側）は、上方から見て格子状（或いは櫛状、櫛形、櫛歯状）となるように形成する。このような形状とすることで、光電変換層 307 に十分な光を照射することができ、光吸収効率を向上させることができる。10

#### 【 0122 】

以上の工程により、光電変換装置を作製することができる。

#### 【 0123 】

本実施の形態では、気相エピタキシャル成長法によって形成された第2の単結晶半導体層 304 の応力をを利用して、SOI 基板 300 から光電変換層 307 を分離している。これにより、光電変換層 307 中において欠陥等の発生を防止できるため、高温の熱処理を必須としない。また、分離後の第2の単結晶半導体層 304 は平坦性が高いため、CMP 处理などの平坦化処理を必須としない。このように、本実施の形態の作製方法を用いることで、特性が良好で且つ大面積な単結晶半導体層を備えた光電変換装置を提供することができる。20

#### 【 0124 】

一方、SOI 基板 300 は、実施の形態 1 と同様に、第2の再生処理工程を行うことで繰り返しシード基板として利用することができ、光電変換装置の生産性を大幅に向上させることができる。

#### 【 0125 】

また、第2の再生処理と、上述した第1の再生処理とを合わせて用いることで、生産性が相乗的に向上し、得られる光電変換装置の数を飛躍的に増大させることができある。

#### 【 0126 】

本実施の形態で示した構成は、本明細書の他の実施の形態又は実施例で示す構成と適宜組み合わせて用いることができる。

#### 【 0127 】

##### （実施の形態 4 ）

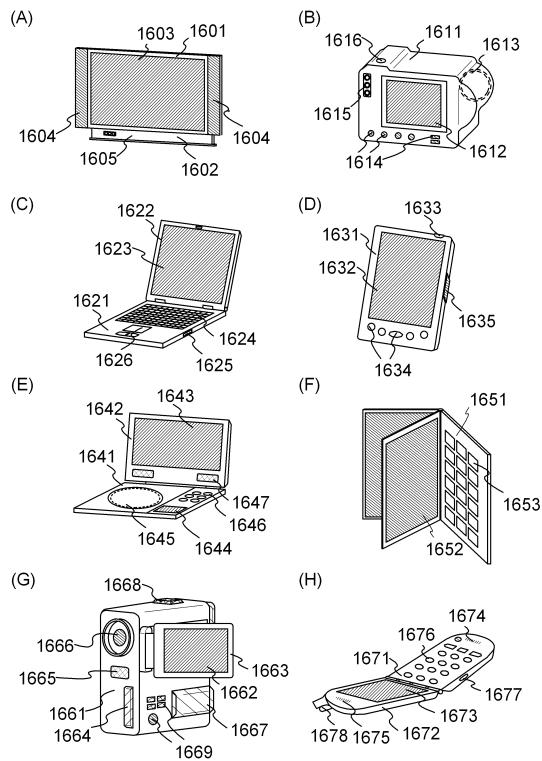

本実施の形態では、上記の実施の形態にて作製した半導体装置、特に表示装置を用いた電子機器について、図5及び図6を参照して説明する。

#### 【 0128 】

半導体装置（特に表示装置）を用いて作製される電子機器としては、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。40

#### 【 0129 】

図5（A）はテレビ受像器又はパーソナルコンピュータのモニタである。筐体 1601、支持台 1602、表示部 1603、スピーカー部 1604、ビデオ入力端子 1605 等を含む。表示部 1603 には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能なテレビ受像器又はパーソナルコンピュータのモニタを低価格で提供することができる。50

**【 0 1 3 0 】**

図5( B )はデジタルカメラである。本体1611の正面部分には受像部1613が設けられており、本体1611の上面部分にはシャッターボタン1616が設けられている。また、本体1611の背面部分には、表示部1612、操作キー1614、及び外部接続ポート1615が設けられている。表示部1612には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能なデジタルカメラを低価格で提供することができる。

**【 0 1 3 1 】**

図5( C )はノート型パーソナルコンピュータである。本体1621には、キーボード1624、外部接続ポート1625、ポインティングデバイス1626が設けられている。また、本体1621には、表示部1623を有する筐体1622が取り付けられている。表示部1623には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能なノート型パーソナルコンピュータを低価格で提供することができる。

10

**【 0 1 3 2 】**

図5( D )はモバイルコンピュータであり、本体1631、表示部1632、スイッチ1633、操作キー1634、赤外線ポート1635等を含む。表示部1632にはアクティブマトリクス表示装置が設けられている。表示部1632には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能なモバイルコンピュータを低価格で提供することができる。

20

**【 0 1 3 3 】**

図5( E )は画像再生装置である。本体1641には、表示部1644、記録媒体読み込み部1645及び操作キー1646が設けられている。また、本体1641には、スピーカー部1647及び表示部1643それぞれを有する筐体1642が取り付けられている。表示部1643及び表示部1644それぞれには、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能な画像再生装置を低価格で提供することができる。

**【 0 1 3 4 】**

図5( F )は電子書籍である。本体1651には操作キー1653が設けられている。また、本体1651には複数の表示部1652が取り付けられている。表示部1652には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能な電子書籍を低価格で提供することができる。

30

**【 0 1 3 5 】**

図5( G )はビデオカメラであり、本体1661には外部接続ポート1664、リモコン受信部1665、受像部1666、バッテリー1667、音声入力部1668、操作キー1669が設けられている。また、本体1661には、表示部1662を有する筐体1663が取り付けられている。表示部1662には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能なビデオカメラを低価格で提供することができる。

**【 0 1 3 6 】**

40

図5( H )は携帯電話であり、本体1671、筐体1672、表示部1673、音声入力部1674、音声出力部1675、操作キー1676、外部接続ポート1677、アンテナ1678等を含む。表示部1673には、本明細書で開示した半導体装置が用いられている。本明細書で開示した半導体装置により、信頼性が高く高性能な携帯電話を低価格で提供することができる。

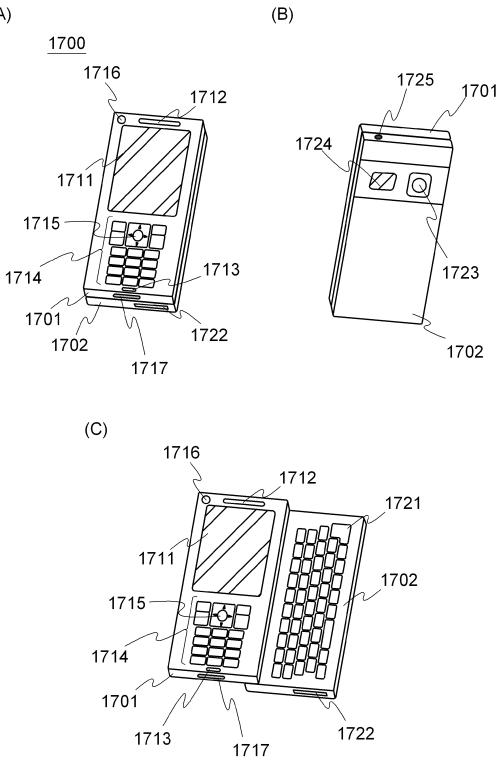

**【 0 1 3 7 】**

図6は、電話としての機能と、情報端末としての機能を併せ持った携帯電子機器1700の構成の一例である。ここで、図6( A )は正面図、図6( B )は背面図、図6( C )は展開図である。携帯電子機器1700は、電話と情報端末の双方の機能を備えており、音声通話以外にも様々なデータ処理が可能な、いわゆるスマートフォンと呼ばれる電子機

50

器である。

**【0138】**

携帯電子機器1700は、筐体1701及び筐体1702で構成されている。筐体1701は、表示部1711、スピーカー1712、マイクロフォン1713、操作キー1714、ポインティングデバイス1715、カメラ用レンズ1716、外部接続端子1717等を備え、筐体1702は、キーボード1721、外部メモリスロット1722、カメラ用レンズ1723、ライト1724、イヤフォン端子1725等を備えている。また、アンテナは筐体1701内部に内蔵されている。上記構成に加えて、非接触ICチップ、小型記録装置等を内蔵していてもよい。

**【0139】**

表示部1711には、本明細書で開示した半導体装置が組み込まれている。なお、表示部1711に表示される映像（及びその表示方向）は、携帯電子機器1700の使用形態に応じて様々に変化する。また、表示部1711と同一面にカメラ用レンズ1716を備えているため、映像を伴う音声通話（いわゆるテレビ電話）が可能である。なお、スピーカー1712及びマイクロフォン1713は音声通話に限らず、録音、再生等に用いることが可能である。カメラ用レンズ1723（及び、ライト1724）を用いて静止画及び動画の撮影を行う場合には、表示部1711はファインダーとして用いられることになる。操作キー1714は、電話の発信・着信、電子メール等の簡単な情報入力、画面のスクロール、カーソル移動等に用いられる。

**【0140】**

重なり合った筐体1701と筐体1702（図6（A））は、スライドし、図6（C）のように展開し、情報端末として使用できる。この場合には、キーボード1721、ポインティングデバイス1715を用いた円滑な操作が可能である。外部接続端子1717はACアダプタやUSBケーブル等の各種ケーブルと接続可能であり、充電やコンピュータ等とのデータ通信を可能にしている。また、外部メモリスロット1722に記録媒体を挿入し、より大容量のデータの保存及び移動に対応できる。上記機能に加えて、赤外線などの電磁波を用いた無線通信機能や、テレビ受信機能等を有していても良い。本明細書で開示した半導体装置により、信頼性が高く高性能な携帯電子機器を低価格で提供することができる。

**【0141】**

以上の様に、本明細書で開示した半導体装置の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は、他の実施の形態又は実施例と適宜組み合わせて用いることができる。

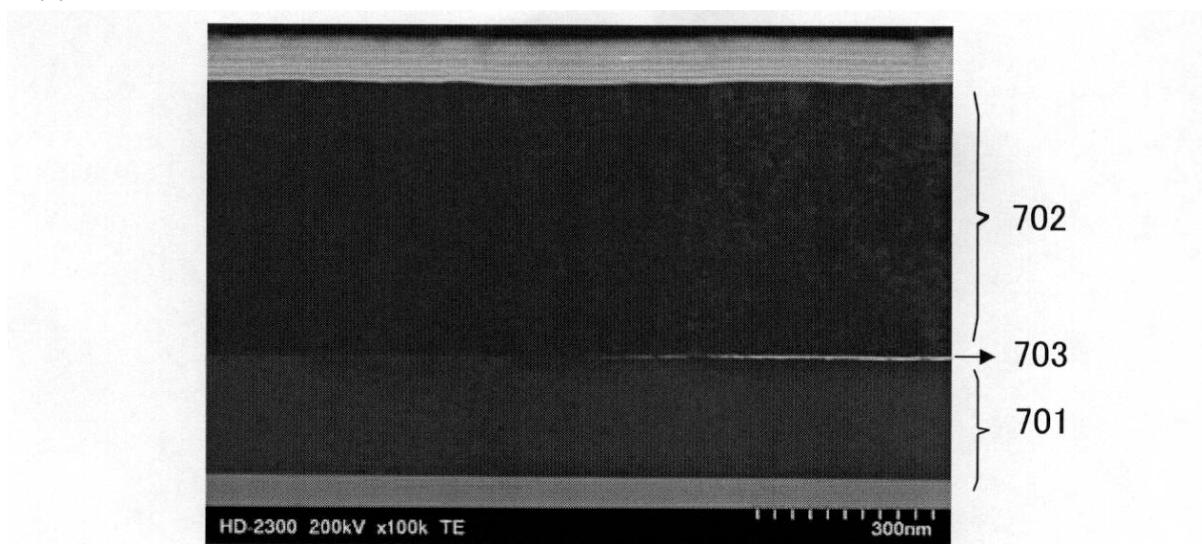

**【実施例1】**

**【0142】**

本実施例では、第1の単結晶半導体層と第2の単結晶半導体層との界面において、第1の基板と第2の基板とが分離される様子を示す。第1の単結晶半導体層及び第2の単結晶半導体層としてシリコン層を用いてサンプルを作製した。そして、第2の単結晶半導体層は、シランと水素の流量（sccm）比をSiH<sub>4</sub> : H<sub>2</sub> = 25 : 150 (sccm)、基板温度を280°C、高周波電源の出力を30W、電源周波数を27MHzとしたプラズマCVD法によって成膜した。

**【0143】**

また、第1の基板と第2の基板とを貼り合わせる前に、第1の単結晶半導体層に、窒素を吹き付けながらレーザー光の照射処理を施している。レーザー光は、照射エネルギー密度を794mJ/cm<sup>2</sup>とした。

**【0144】**

図7は、分離の様子を示すTEM像の断面図である。第1の単結晶半導体層701と第2の単結晶半導体層702との界面703において剥離が生じ、分離が良好に行われる様子が確認できた。

**【0145】**

10

20

30

40

50

本実施例で示した構成は、本明細書の実施の形態と適宜組み合わせて用いることができる。

【符号の説明】

【0 1 4 6】

|       |            |    |

|-------|------------|----|

| 1 0 0 | 第1のSOI基板   |    |

| 1 0 1 | 第1の基板      |    |

| 1 0 2 | 絶縁層        |    |

| 1 0 3 | 第1の単結晶半導体層 |    |

| 1 0 4 | 第2の単結晶半導体層 |    |

| 1 0 5 | 絶縁層        | 10 |

| 1 0 6 | 第2の基板      |    |

| 1 0 7 | 第2のSOI基板   |    |

| 2 0 0 | SOI基板      |    |

| 2 0 1 | 基板         |    |

| 2 0 2 | 絶縁層        |    |

| 2 0 3 | 第1の単結晶半導体層 |    |

| 2 0 4 | 第2の単結晶半導体層 |    |

| 2 0 5 | 金属層        |    |

| 2 0 6 | 積層構造体      |    |

| 3 0 0 | SOI基板      | 20 |

| 3 0 1 | 第1の基板      |    |

| 3 0 2 | 絶縁層        |    |

| 3 0 3 | 第1の単結晶半導体層 |    |

| 3 0 4 | 第2の単結晶半導体層 |    |

| 3 0 5 | 第3の単結晶半導体層 |    |

| 3 0 6 | 第4の単結晶半導体層 |    |

| 3 0 7 | 光電変換層      |    |

| 3 0 8 | 第1の導電層     |    |

| 3 0 9 | 絶縁層        |    |

| 3 1 0 | 第2の基板      | 30 |

| 3 1 1 | 積層構造体      |    |

| 4 0 1 | 第2の導電層     |    |

| 4 0 2 | 第3の導電層     |    |

| 4 0 3 | 第4の導電層     |    |

| 7 0 1 | 第1の単結晶半導体層 |    |

| 7 0 2 | 第2の単結晶半導体層 |    |

| 7 0 3 | 界面         |    |

| 8 0 1 | 単結晶半導体基板   |    |

| 8 0 2 | イオンビーム     |    |

| 8 0 3 | 脆化層        | 40 |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図8】

【図7】

---

フロントページの続き

審査官 綿引 隆

(56)参考文献 特開平10-326883(JP,A)

特表2006-527478(JP,A)

特表2004-517472(JP,A)

特開2008-001540(JP,A)

特開2006-012986(JP,A)

特開2006-216896(JP,A)

特開2008-277805(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 27/12

H01L 31/04 - 078

H01L 31/18