(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3850625号

(P3850625)

(45) 発行日 平成18年11月29日(2006.11.29)

(24) 登録日 平成18年9月8日(2006.9.8)

(51) Int.C1.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/28</b> | <b>(2006.01)</b> | G09G | 3/28 | H    |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/28 | E    |

|             |             |                  | G09G | 3/20 | 622Q |

|             |             |                  | G09G | 3/20 | 632Z |

|             |             |                  | G09G | 3/20 | 641E |

請求項の数 8 (全 29 頁)

(21) 出願番号 特願2000-99162 (P2000-99162)

(22) 出願日 平成12年3月31日 (2000.3.31)

(65) 公開番号 特開2000-347616 (P2000-347616A)

(43) 公開日 平成12年12月15日 (2000.12.15)

審査請求日 平成16年8月11日 (2004.8.11)

(31) 優先権主張番号 特願平11-96816

(32) 優先日 平成11年4月2日 (1999.4.2)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人 100078134

弁理士 武 顯次郎

(72) 発明者 中 一隆

神奈川県横浜市戸塚区吉田町292番地

株式会社 日立製作所 情報メディア事業

本部内

(72) 発明者 大沢 通孝

神奈川県横浜市戸塚区吉田町292番地

株式会社 日立製作所 情報メディア事業

本部内

最終頁に続く

(54) 【発明の名称】表示装置および表示方法

## (57) 【特許請求の範囲】

## 【請求項1】

表示部の画素をサブフィールド方式で点灯させて映像を表示する表示装置であって、

入力映像信号を複数のサブフィールドのサブフィールドデータに変換する入力信号処理手段と、

該表示部の画素をアドレスするタイミングを制御する制御手段と、

該入力信号処理手段と該制御手段とからの出力に基づいて、該表示部の該画素をアドレスし、点灯させる駆動手段と

を有し、

該入力信号処理手段は、隣り合う複数のラインでのデジタル化した該入力映像信号を複数の周波数成分に変換する手段と、変換された該周波数成分のうちの所定の周波数成分の所定個数の下位ビットを0とした後に逆変換する手段とを含む構成をして、少なくとも1つの下位側サブフィールドで該複数のラインのサブフィールドデータを同一にし、

該制御手段により、サブフィールドデータが同一とされた該下位側サブフィールドで該複数のラインの点灯すべき該画素を同時にアドレスするように動作させることにより、アドレス制御時間を短くし、

該駆動手段で表示部を駆動して該入力映像信号に対応する映像を表示するようにしたことを特徴とする表示装置。

## 【請求項2】

請求項1において、

前記入力信号処理手段は、最も発光重みの小さい最下位サブフィールドを含む下位側サブフィールドの複数のラインのアドレス信号を同一とするようにしたことを特徴とする表示装置。

**【請求項3】**

請求項1または2において、

前記下位側サブフィールドの数を外部から設定できるように構成したことを特徴とする表示装置。

**【請求項4】**

請求項1, 2または3において、

前記入力信号処理手段は、前記少なくとも1つの下位側サブフィールドの隣接する2ラインのアドレス信号を同一とするようにしたことを特徴とする表示装置。

10

**【請求項5】**

表示部の画素をサブフィールド方式で点灯させて映像を表示する表示方法であって、少なくとも1つの下位側サブフィールドで、隣り合う複数のラインでのディジタル化された入力映像信号を複数の周波数成分に変換し、変換された該周波数成分のうちの所定の周波数成分の所定個数の下位ビットを0とした後に逆変換することにより、少なくとも1つの下位側サブフィールドで該複数のラインのサブフィールドデータを同一にするよう、該入力映像信号を複数のサブフィールドのサブフィールドデータに変換する入力信号処理を行ない、

該表示部の画素をアドレスするタイミングを制御する制御処理を行ない、

20

該入力信号処理と該制御処理との出力に基づいて、該表示部の該画素をアドレスして点灯させ、

該制御処理により、サブフィールドデータが同一とされた該下位側サブフィールドで該複数のラインの点灯すべき該画素を同時にアドレスするように動作させることによりアドレス制御時間を短くするようにし、

該表示部を駆動して該入力映像信号に対応する映像を表示するようにしたことを特徴とする表示方法。

**【請求項6】**

請求項5において、

前記入力信号処理は、最も発光重みの小さい最下位サブフィールドを含む下位側サブフィールドの複数のラインのアドレス信号を同一とするようにしたことを特徴とする表示方法。

30

**【請求項7】**

請求項5または6において、

前記下位側サブフィールドの数を外部から設定できるように構成したことを特徴とする表示方法。

**【請求項8】**

請求項5, 6または7において、

前記入力信号処理は、前記少なくとも1つの下位側サブフィールドの隣接する2ラインのアドレス信号を同一とするようにしたことを特徴とする表示方法。

40

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、表示装置および表示方法に係わり、特に、サブフィールド方式により階調表現を行ない、夫々のサブフィールドでライン毎のデータを順次出力して表示する表示装置および表示方法に関する。

**【0002】**

**【従来の技術】**

近年、従来から用いられているブラウン管(CRT)表示装置に代わって、薄型軽量で、画面歪みが少なく地磁気の影響を受けにくい、液晶やプラズマを用いたフラットパネルデ

50

イスプレイが用いられるようになってきた。特に、自発光型による広い視野角を有し、大型パネルが比較的容易に作成可能なプラズマディスプレイが映像信号の表示装置として注目されている。

#### 【0003】

一般に、プラズマディスプレイは、発光と非発光の中間の階調表示が困難であるので、中間階調を表示するためには、サブフィールド方式と呼ばれる方式が用いられている。このサブフィールド方式では、1フィールドの時間幅を複数のサブフィールドに分割し、夫々のサブフィールドに固有の発光重みを割り当て、各サブフィールドの発光と非発光を制御することにより、1フィールドの輝度の階調を表現している。

#### 【0004】

10

#### 【発明が解決しようとする課題】

現在、プラズマディスプレイの主流となっているアドレス・サステイン分離方式では、1つのサブフィールドが放電セルの状態を初期化するリセット期間、放電セルの点灯・不点灯を制御するアドレス制御期間及びその発光量を決定するサステイン期間などを制御する制御パルスから構成されている。これらの制御パルスは、安定した発光制御を実現するために、所定の時間幅より短くすることはできない。このアドレス制御期間では、ライン毎に点灯・非点灯を制御するデータに基づいてアドレス処理が行なわれるため、高解像度のパネルでは、ライン数の増加により多くの時間が必要となる。このため、1フィールド期間内に構成可能なサブフィールドの数が制限されたり、十分な輝度が得られないという問題があった。例えば、アドレス制御処理に1ライン当たり $2\text{ }\mu\text{ s}$ 要する表示パネルを用いて垂直解像度1000ラインの高精細パネルを実現しようとする際には、1サブフィールド当たり $2\text{ ms}$  ( $= 2\text{ }\mu\text{ s} \times 1000\text{ ライン}$ ) のアドレス制御期間が必要となる。一般に、映像信号を劣化することなく表示するためには、256階調(8ビット)程度必要とされているが、約 $16.6\text{ ms}$ の1フィールド期間に8サブフィールドを構成しようとすると、サステイン期間に割り当てる時間はほとんどなくなってしまう。このように、1フィールドの期間のほとんどをサブフィールド毎のアドレス制御期間に割り当ててしまうことになるため、パネル発光に寄与するサステイン期間を十分確保できないという問題があった。

20

#### 【0005】

また、サブフィールド数を制限した場合、例えば、6サブフィールド64階調に制限したような場合には、十分な階調数が表現できず、高画質の表示装置を実現することが困難であった。

30

#### 【0006】

さらに、サブフィールド方式による階調表示固有の問題として、動画像の画質を劣化させてしまう擬似輪郭妨害がある。この擬似輪郭妨害を低減させるためには、サブフィールド数を増加させて1フィールド内の発光分布や発光の重心を制御する手法が用いられている。表現可能な階調数が同一の条件では、サブフィールド数が多いほど制御可能な発光パターンが増加するため、擬似輪郭妨害を低減する効果は大きくなる。従って、十分なサブフィールド数が得られない場合には、この擬似輪郭妨害によって動画像表示時の画質が著しく劣化してしまうという問題があった。

また、従来の表示装置では、基本的には、入力された信号を忠実に表示することに終始しており、一部に階調数の不足を補うためのディザや誤差拡散処理、あるいは平均輝度の制御など人間の視覚特性を考慮して高画質を得る手法も用いられているが、信号の振幅を制御する程度のものであった。

40

さらに、特開平11-24628号公報に示されるように、下位ビットに相当するサブフィールドでは、飛び越し走査によってアドレス制御時間を短縮する手法や、飛び越し走査の代わりに、走査電極を2本同時に選択して書き込み動作を行なう方式も開示されているが、具体的な信号の生成方法が示されていない。

#### 【0007】

映像信号の各ラインは1画面の垂直方向にサンプリングしたデータであり、飛び越し走査によってサンプリングデータを間引く際には、折り返し妨害低減のため、事前に垂直解像

50

度を半減させておく必要がある。これにより、垂直解像度は半減することになり、解像度感の欠落した画像となってしまう。また、事前に垂直解像度を半減させずにサンプリングデータを間引いた場合には、折り返し妨害により、高い周波数成分の信号が低い周波数に変換され、大きな画質劣化の要因となることが知られている。

#### 【0008】

本発明の目的は、人間の視覚特性や映像信号の統計的な性質を積極的に利用して、必要に応じて表示画像の解像度情報量を制限し、総合的な画質を向上させた表示装置および表示方法を提供することにある。

#### 【0009】

本発明の他の目的は、フィールドの時間内に占める総アドレス制御期間を改善して、十分なサブフィールド数を確保し、階調表現、擬似輪郭妨害の対策、さらには、高輝度表示の実現を可能にした高解像度の表示装置および表示方法を提供することにある。

10

#### 【0010】

##### 【課題を解決するための手段】

本発明は、上記の課題を解決するために、次のような手段を採用した。

#### 【0011】

第1の手段として、入力信号に基づいて、点灯画素及び発光輝度を制御する表示装置において、設定に応じて表示解像度情報を制限し、点灯画素を制御する時間を短くすることを特徴とする。

#### 【0012】

また、第2の手段として、サブフィールド方式により階調表現を行なう表示装置において、所定のサブフィールドにおいて、表示解像度情報を制限し、アドレス制御期間を短縮化することを特徴とする。

20

#### 【0013】

また、第3の手段として、第2の手段において、前記アドレス制御期間を短縮化するサブフィールドが、最も発光重みの小さい最下位サブフィールドを含む1つ以上のサブフィールドであることを特徴とする。

#### 【0014】

また、第4の手段として、第2の手段において、前記アドレス制御期間を短縮化するサブフィールドが、最も発光重みの小さい最下位サブフィールドを除いた1つ以上の下位サブフィールドであることを特徴とする。

30

#### 【0015】

また、第5の手段として、第2の手段において、前記アドレス制御期間を短縮化するサブフィールドの数が、当該表示装置の外部からの設定により変化することを特徴とする。

#### 【0016】

また、第6の手段として、サブフィールド方式により階調表現を行ない、夫々のサブフィールドの点灯・非点灯の制御をライン単位で行なう表示装置において、所定のサブフィールドにおいて、隣接する複数ラインを同一データで同時に制御することを特徴とする。

#### 【0017】

また、第7の手段として、第6の手段において、前記同一データで同時に制御するサブフィールドが、最も発光重みの小さい最下位サブフィールドを含む1つ以上のサブフィールドであることを特徴とする。

40

#### 【0018】

また、第8の手段として、第6の手段において、前記同一データで同時に制御するサブフィールドが、最も発光重みの小さい最下位サブフィールドを除いた1つ以上の下位サブフィールドであることを特徴とする。

#### 【0019】

また、第9の手段として、第6の手段において、前記同一データで制御するラインの組み合わせがフィールドあるいはフレーム単位で変化する構成であることを特徴とする。

#### 【0020】

50

また、第10の手段として、第6の手段において、前記同一データで制御するラインの組み合わせが1フィールド内のサブフィールドで互いに異なる組み合わせであることを特徴とする。

【0021】

また、第11の手段として、第6の手段において、前記同一データで同時に制御するサブフィールドの数が、当該表示装置の外部からの設定により、変化することを特徴とする。

【0022】

また、第12の手段として、第6の手段において、前記同一データで同時に制御するラインの数が、当該表示装置の外部からの設定により、変化することを特徴とする。

【0023】

また、第13の手段として、第6の手段において、前記同一データで同時に制御するラインが隣接する2ラインであることを特徴とする。

【0024】

また、第14の手段として、入力信号に基づいて点灯画素及び発光輝度を制御して画像表示する表示方法において、設定に応じて表示解像度情報を制限して点灯画素を制御する時間を短くすることを特徴とする。

【0025】

また、第15の手段として、サブフィールド方式により階調表現を行なって画像表示する表示方法において、所定のサブフィールドにおいて、表示解像度情報を制限し、アドレス制御期間を短縮化することを特徴とする。

【0026】

また、第16の手段として、第15の手段において、前記アドレス制御期間を短縮化するサブフィールドの数が、外部からの設定により、変化することを特徴とする。

【0027】

また、第17の手段として、サブフィールド方式により階調表現を行ない、夫々のサブフィールドの点灯・非点灯の制御をライン単位で行なって画像表示する表示方法において、所定のサブフィールドにおいて、隣接する複数ラインを同一データで同時に制御することを特徴とする。

【0028】

また、第18の手段として、第17の手段において、前記同一データで同時に制御するサブフィールドの数が、外部からの設定により、変化することを特徴とする。

【0029】

【発明の実施の形態】

以下に、本発明に係る実施形態を図面を用いて説明する。

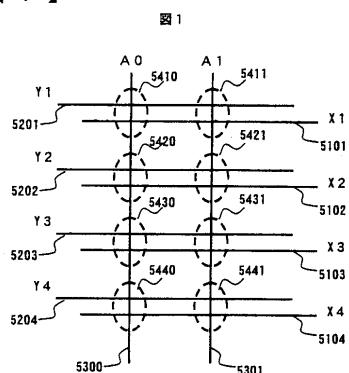

【0030】

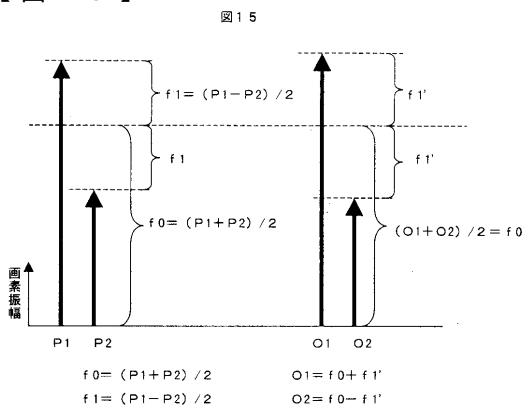

図1は一般的なAC3電極型プラズマディスプレイの放電セルと電極の配置を模式的に示したものである。

【0031】

同図において、5101, 5102, 5103, 5104はXサステイン電極、5201, 5202, 5203, 5204はYサステイン電極、5300, 5301はアドレス電極である。各アドレス電極5300, 5301は背面板、Xサステイン電極5101～5104及びYサステイン電極5201～5204は前面板上に形成されており、Xサステイン電極及びYサステイン電極の電極対とアドレス電極の交点に画素が形成される。これらの電極間の放電により、同図に示すように、パネル上に画素5410, 5411, 5420, 5421, 5430, 5431, 5440, 5441が形成される。

【0032】

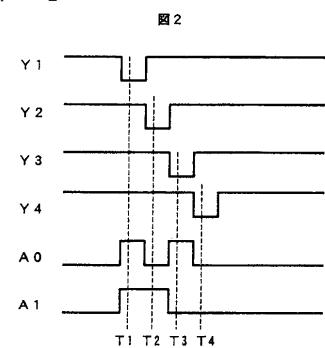

図2は本発明と対比するために示した従来技術でのアドレス制御期間におけるYサステイン電極5201～5204及びアドレス電極5300～5301の印加電圧を示す図である。

【0033】

10

20

30

40

50

同図に示すように、Y1サステイン電極5201、Y2サステイン電極5202、Y3サステイン電極5203、Y4サステイン電極5204の順にスキャンパルスが印加され、ライン毎に点灯・非点灯を制御するアドレスパルスがA0アドレス電極5300、A1アドレス電極5301に印加される。

#### 【0034】

ここで、時刻T1では、Y1サステイン電極5201にスキャンパルスが印加されているので、第1ラインの画素5410、5411の点灯・非点灯が制御される。この例では、A0アドレス電極5300及びA1アドレス電極5301にはともにアドレス電圧が印加されているので、A0アドレス電極-Y1サステイン電極間、A1アドレス電極-Y1サステイン電極間でアドレス放電が生じ、これに続くサステイン期間での発光可能なように壁電荷が形成される。以降、時刻T2では、第2ラインの画素5420と画素5421、時刻T3では、第3ラインの画素5430と画素5431、時刻T4では、画素5440と画素5441の点灯・非点灯を制御するアドレス処理が夫々行なわれる。このようなライン毎のアドレス処理により、必要に応じてセル内の壁電荷が形成され、これに続くサステイン期間において、発光が制御される。

#### 【0035】

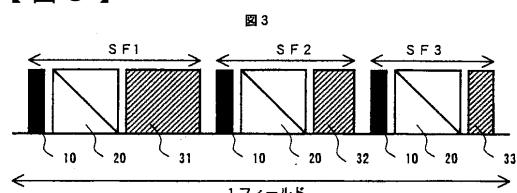

図3は本発明と対比するために示した従来技術での1フィールドが3つのサブフィールド(SF1、SF2、SF3)から構成されたフィールド構成を示す図である。

#### 【0036】

同図において、10は各サブフィールドにおいて放電セルの状態を初期化するリセット期間、20は各サブフィールドにおいて各画素の点灯・非点灯を制御するアドレス制御期間、31、32、33は夫々のサブフィールドにおける発光量を決定するサステイン期間である。このサステイン期間31～33では、アドレス制御期間20で発光可能なように壁電荷が形成された放電セルについて、サステインパルス数に応じた発光が行なわれる。サブフィールド方式では、階調表現を実現するために、各サブフィールドSF1～SF3には、夫々に対応した発光重みが割り当てられている。ここでは、各サブフィールドSF1～SF3のサステイン期間31、32、33におけるサステインパルス数は概略4：2：1の発光重みとなるように構成されている。これにより、サブフィールドSF1～SF3のいずれも発光しない階調0から、全てのサブフィールドSF1～SF3が発光する階調7(=3+2+1)までの階調を表現することができる。ここで、表示可能な最大輝度(階調7)は、サブフィールドSF1～SF3の各サステイン期間31、32、33におけるサステインパルス数の合計で決定されるために、1フィールド内のアドレス制御期間20などの発光に寄与しない時間が長くなると、輝度が十分確保できず、良好な画質を得ることができない。また、アドレス制御期間20は表示ライン数に比例した時間を必要とし、また、1サブフィールドに1つのアドレス制御期間が必要となるものである。このため、高解像度の表示パネルを実現しようとする場合には、十分なサブフィールド数が確保できず、表示階調数が不足したり、輝度が低下したりして画質が劣化してしまうという問題がある。

#### 【0037】

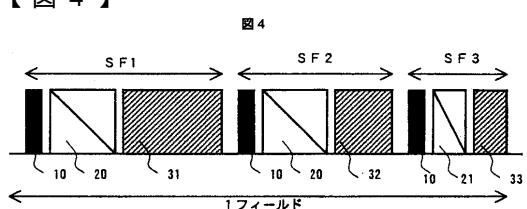

図4は本発明の第1の実施形態に係わり、図3に示す従来のフレーム構成に比べて、サブフィールド(SF1、SF2、SF3)のうち、発光重みの少ない下位サブフィールドSF3のアドレス制御期間を半分に設定したフィールド構成を示す図である。

#### 【0038】

同図において、21はサブフィールドSF3のアドレス制御期間が図3に示すものと比べて半分の期間に設定されたアドレス制御期間である。なお、その他の構成は図3に示す同符号の構成に対応する。

#### 【0039】

同図において、サブフィールドSF1、SF2では、図3に示す場合と同様に、リセット期間10で放電セルを初期化し、アドレス制御期間20でライン毎に点灯・非点灯画素が選択処理される。サステイン期間31、32では、アドレス制御期間20で選択された画

10

20

30

40

50

素を夫々の発光重みに応じて発光させる。サブフィールド S F 3 では、リセット期間 10 に続くアドレス制御期間 21 で隣接する 2 ライン同時にアドレス処理を行なうようすることにより、データ間引きによりアドレス制御期間 20 が短縮化されて 1 ライン当たり半分の時間でアドレス制御処理を行なうことができる。

#### 【0040】

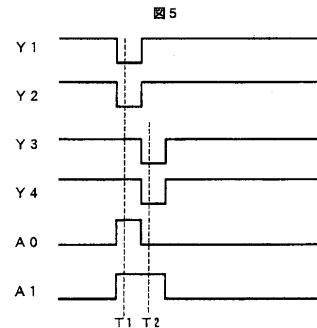

図 5 は本実施形態でのアドレス制御期間における Y サステイン電極 5201 ~ 5204 及びアドレス電極 5300 ~ 5301 の印加電圧を示す模式図である。

#### 【0041】

同図に示すように、Y1 サステイン電極 5201 及び Y2 サステイン電極 5202 が同時にスキャンパルスが印加されることにより、2 ライン同時に同一データによりアドレス処理が行なわれる。Y1 サステイン電極 5201, Y2 サステイン電極 5202 に引き続い 10 て、Y3 サステイン電極 5203 及び Y4 サステイン電極 5204 が同時にアドレス処理される。このように 2 ラインづつ同時にスキャンパルスを印加してアドレス処理を行なうことにより、1 画面の総ラインのスキャンに要する時間を半分に短縮することができる。

#### 【0042】

なお、図 5 に示す例では、2 ライン同時のアドレス処理としたが、2 ラインに限ることなく、3 ラインあるいは 4 ライン同時の処理としてもよく、この際に必要なアドレス時間は 1 / 3 あるいは 1 / 4 に短縮することができる。また、このアドレス短縮化の処理は、最も発光重みの少ない最下位サブフィールド S F 3 に限ることなく、サブフィールド S F 2 あるいはサブフィールド S F 2 とサブフィールド S F 3 の両方に適応するものであってもよい。また、サブフィールド S F 2 は 2 ラインの同時アドレス処理によりアドレス処理期間を 1 / 2 にし、サブフィールド S F 3 は 3 ラインの同時アドレス処理によりアドレス処理期間を 1 / 3 に短縮化するように構成してもよい。このような処理を行なうことにより、発光重みの小さい下位サブフィールドの垂直解像度情報は失われてしまうが、画像平坦部の滑らかな表示は問題なく表示することができ、また、発光重みの大きな上位サブフィールドによりエッジ部の信号は再現されるため、ほとんど画質の劣化はなく、高輝度の画像表示が可能となる。 20

#### 【0043】

このように、本実施形態によれば、特定のサブフィールドでアドレス制御データ数を減らすことにより、1 フィールド内での直接発光に寄与しないアドレス制御期間を短縮し、その分、サステイン期間 31, 32, 33 に割り当てて高輝度化したり、または、サブフィールド数を増加させて高画質化を図ることが可能となる。 30

#### 【0044】

また、本実施形態によれば、常に隣接する 2 ラインが同一のデータでアドレス処理されるが、隣接画素間では、画像の相關性によって類似したデータとなりやすく、また、発光重みの小さいサブフィールド S F 3 に対してこの処理を行なうことにより、ほとんど画質を劣化させることなく、アドレス処理期間を短縮することができる。

#### 【0045】

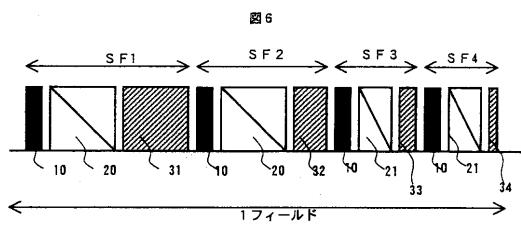

図 6 は本発明の第 2 の実施形態に係わり、図 3 に示す従来のフレーム構成に比べて、サブフィールド S F 4 を増やし、サブフィールド S F 1 ~ S F 4 のうち発光重みの少ない下位サブフィールド S F 3 ~ S F 4 のアドレス制御期間を半分にしたフィールド構成を示す図である。 40

同図において、21 はサブフィールド S F 3, S F 4 のアドレス制御期間が図 3 に示すものと比べて半分の期間に設定したアドレス制御期間、34 は増加したサブフィールド S F 4 のサステイン期間である。その他の構成は図 3 に示す同符号の構成に対応する。

#### 【0046】

同図において、サブフィールド S F 1, S F 2 では、図 3 の場合と同様に、リセット期間 10 で放電セルを初期化し、アドレス制御期間 20 でライン毎に点灯・非点灯画素の選択処理を行なう。サステイン期間 31, 32 では、アドレス制御期間で選択された画素を夫々の発光重みに応じて発光させる。サブフィールド S F 3 では、リセット期間 10 に続く 50

アドレス制御期間 2 1 で 2 ライン同時にアドレス処理を行なうことにより、半分の時間でアドレス処理を行ない、2 ラインづつ等しいデータにより点灯・非点灯の制御が行なわれる。これに続くサステイン期間 3 3 では、アドレス処理で選択されたラインの発光が行なわれる。また、サブフィールド S F 4 も同様に、リセット期間 1 0 に続くアドレス制御期間 2 1 で 2 ライン同時にアドレス処理を行なうことにより、半分の時間でアドレス制御処理を行ない、サステイン期間 3 4 において、アドレス処理で選択されたセルを発光させる。

#### 【 0 0 4 7 】

このように、本実施形態によれば、サブフィールド S F 3 , S F 4 のアドレス制御期間 2 1 を半分の時間にすることにより、1 フィールド期間内に 4 つのサブフィールド S F 1 ~ S F 4 を構成することができ、サステイン期間 3 1 , 3 2 , 3 3 , 3 4 の発光比率を 8 : 4 : 2 : 1 に設定することにより、16 階調の表示を行なうことができる。なお、本実施形態では、サブフィールド S F 4 のアドレス制御期間が新たに増加するが、サブフィールド S F 3 , S F 4 のアドレス制御期間を半分の時間で処理するため、1 フィールド期間内の全てのサブフィールド S F 1 ~ S F 4 のアドレス制御期間の合計は、図 3 に示した従来の構成とほぼ等しくすることができる。これにより、従来の方式とほぼ等しい輝度を保った状態で表示階調数を増加させることができ、高画質な表示装置を実現することができる。

#### 【 0 0 4 8 】

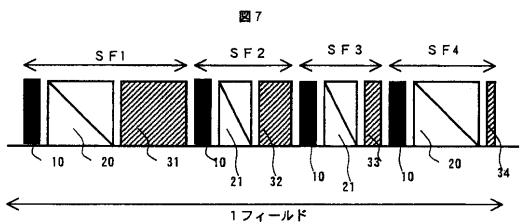

図 7 は本発明の第 3 の実施形態に係わり、図 3 に示す従来のフレーム構成と比べて、サブフィールド S F 4 を増やし、サブフィールド S F 1 ~ S F 4 のうち最下位のサブフィールド S F 4 を除く下位のサブフィールド S F 2 ~ S F 3 のアドレス制御期間を半分にしたフィールド構成を示す図である。

#### 【 0 0 4 9 】

2 1 はサブフィールド S F 2 , S F 3 のアドレス制御期間が半分の期間にしたアドレス制御期間、3 4 は増加したサブフィールド S F 4 のサステイン期間である。その他の構成は図 3 に示す同符号の構成に対応する。

#### 【 0 0 5 0 】

同図に示すように、サブフィールド S F 1 とサブフィールド S F 4 は、図 3 に示すものと同様に、全てのラインに対してアドレス処理を行ない、サブフィールド S F 2 , S F 3 は、2 ラインづつ同一データにより、アドレス処理を行なう。

#### 【 0 0 5 1 】

本実施形態によれば、サブフィールド S F 2 , S F 3 のアドレス制御期間 2 1 は通常のアドレス制御期間 2 0 の約半分となり、第 2 の実施形態と同様に、1 フィールド期間内の総アドレス制御期間は図 3 に示す従来技術の 3 サブフィールドの構成とほぼ等しく、従来とほぼ等しい輝度を保った状態で表示階調数を増加させることができる。

#### 【 0 0 5 2 】

また、本実施形態は、第 2 の実施形態と比べて、最下位サブフィールド S F 4 がライン毎に点灯・非点灯を制御できるので、ディザや誤差拡散方式といった擬似中間階調表現と併用した際の画質妨害を低減させることができる。

#### 【 0 0 5 3 】

ここで、ディザや誤差拡散方式とは、最小の階調ステップを ON · OFF させることによって平均的な輝度を擬似的に表現するものであり、例えば、最小の階調ステップを 1 とした場合に、この最小ステップを交互に ON · OFF させることにより、擬似的に 0 . 5 の階調を表現し、この ON · OFF の比率を変えることにより、細かな中間階調を表現しようとすることができる。この擬似中間階調を適用することにより、実際の表示階調よりもより多くの階調が擬似的に表現可能となるが、最小ステップ階調の ON · OFF パターンが粒状性のノイズとして目に付く問題が知られている。

#### 【 0 0 5 4 】

サブフィールド方式に基づく階調表現では、この最小ステップ階調は最下位サブフィール

10

20

30

40

50

ドの発光量に相当する。また、プラズマディスプレイなどでは、従来のCRTのようなガンマ特性を持たないため、低輝度側の表示階調が粗くなる傾向がある。そのため、擬似中間階調を適用した際には、黒レベルと最下位サブフィールドがONする最小ステップ階調の間の階調を擬似的に表現しようとした際に生ずる粒状性ノイズによる妨害が目につきやすい。

#### 【0055】

第1及び第2の実施形態では、夫々の最下位サブフィールドSF3, SF4が2ライン同一データで制御されているため、この粒状性ノイズの粒が大きくなつて画質劣化要因となるが、本実施形態では、最下位サブフィールドSF4は1ドット毎に制御でき、粒状性ノイズによる妨害を従来と同等にすることができる。

10

#### 【0056】

一般的な自然画像を対象とした場合、隣接画素の差分情報の振幅発生分布はラプラス分布になることが知られている。これはゼロ近傍の小さな振幅の発生頻度が極めて高く集中しており、振幅の大きな差分情報が発生する頻度は小さいという特徴を有している。即ち、上下の隣接する2つの画素に着目した場合には、2つの差分がゼロ（同じレベル）であるか、わずかな差である場合が多いことを示している。第1, 第2の実施形態では、夫々の最下位サブフィールドSF3, SF4を2ライン同一データで発光制御するため、2つの差分がゼロ（同じレベル）である場合には、画質が劣化することなく、画像の表示が可能である。さらに、本実施形態では、振幅の小さな最下位サブフィールドSF4をライン単位に独立制御するため、2つの画素の差分がゼロ（同じレベル）である場合に加えて、階調の最小ステップ以内であれば、画質が劣化することなく、画像の表示が可能となる。

20

#### 【0057】

このように、本実施形態によれば、最下位サブフィールドSF4を含めた下位サブフィールドSF2, SF3を独立に制御することにより、発生頻度の極めて高い隣接画素差分が小さな領域における画質劣化を低減させることができる。

#### 【0058】

また、本実施形態では、発生頻度は低いが情報量の多いエッジ部の信号は、最上位サブフィールドを含む上位サブフィールドをライン毎に独立に制御することにより、正しく表現するので、全体としてアドレス制御期間を短縮したことによる画質劣化をより少なくすることができる。これを高階調表現の場合に適用すると、例えば、256階調表現可能な128:64:32:16:8:4:2:1の発光比率を有するSF1~SF8の8つのサブフィールドにおいて、SF5, SF6の2つのサブフィールドを2ライン同一データにより表示し、残りの最下位サブフィールドを含めた下位サブフィールドSF7, SF8及び最上位サブフィールドを含む上位サブフィールドSF1, SF2, SF3, SF4は、従来と同様に、ライン毎にアドレス制御を行なう構成とすればよい。あるいはSF4, SF5, SF6のアドレス制御期間を短縮化する構成や、SF5, SF6, SF7のアドレス制御期間を短縮化する構成であってもよい。

30

#### 【0059】

また、本実施形態の応用例として、必要に応じてアドレス制御期間を全く短縮化しない高解像度であるが低輝度の表示モードと、より多くのサブフィールドに対してアドレス制御期間を短縮化するために解像度は低いが高輝度な表示モードとを必要に応じて切り換えるように構成してもよい。例えば、コンピュータなどのモニタとして使用する際には、アドレス制御期間を全く短縮化しない高解像度な表示とし、ビデオ信号の表示の際には、サブフィールドSF1~SF8の8つのサブフィールドのうち、2つのサブフィールドSF5, SF6を2ライン同一データにより表示させて高輝度表示を行なえるように切り換える構成とする。

40

さらにまた、表示装置が置かれている周辺の輝度やユーザ設定、映像信号のレベルに応じて、2つのサブフィールドのアドレス制御期間を短縮化するモードから3つのサブフィールドのアドレスの短縮化、4つ、5つと短縮化するサブフィールドを増加させて輝度調整の範囲を拡大する構成としてもよい。

50

**【0060】**

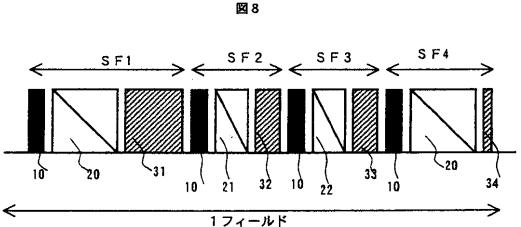

図8は本発明の第4の実施形態に係わり、図3に示す従来のフレーム構成と比べて、サブフィールドSF4を増やし、サブフィールドSF1～SF4のうち最下位のサブフィールドSF4を除く下位のサブフィールドSF2，SF3のアドレス制御期間を半分にするとともに、そのサステイン期間の発光比率を同じにしたフィールド構成を示す図である。

**【0061】**

21はサブフィールドSF2の第1の位相でデータ間引きを行なって短縮化したアドレス制御期間、22はサブフィールドSF3の第2の位相でデータ間引きを行なって短縮化したアドレス制御期間、32，33は互いに同一の発光比率を有するサブフィールドSF2，SF3のサステイン期間、34は増加したサブフィールドSF4のサステイン期間である。その他の構成は図3に示すものと同じである。

10

**【0062】**

本実施形態では、各サブフィールドSF1～SF4の発光比率を1：2：4：…のような2のべき乗の値でなく、サブフィールドSF2とサブフィールドSF3の発光量を等しくなるように構成する。具体的には、4：2：2：1のような発光重みである。2のべき乗と異なる発光比率とすることにより、同一サブフィールド数で表現可能な階調数は減ることになるが、サブフィールド方式固有の問題である擬似輪郭妨害を低減させる手法として用いることができる。

**【0063】**

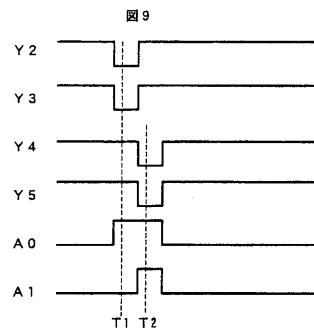

本実施形態では、発光重みの等しい2つのサブフィールドSF2，SF3に対してアドレス制御期間21，22を圧縮するが、これらサブフィールドSF2，SF3では、異なる位相でデータを間引くように構成している。サブフィールドSF2のアドレス制御期間21では、図5に示すように、Y1サステイン電極とY2サステイン電極とに等しいスキャンパルスを与えて第1ラインと第2ラインとを等しいデータでアドレスし、Y3サステイン電極とY4サステイン電極とに同時にスキャンパルスを与えて第3ラインと第4ラインとを等しいデータでアドレスするが、サブフィールドSF3のアドレス制御期間22では、図9に示すように、Y2サステイン電極とY3サステイン電極とに等しいスキャンパルスを与えて第2ラインと第3ラインとを等しいデータでアドレスし、Y4サステイン電極とY5サステイン電極とに同時にスキャンパルスを与えて第4ラインと第5ラインとを等しいデータでアドレスするように構成する。このように構成することにより、例えば、Y2サステイン電極のデータに関してY1サステイン電極と同一データでアドレス処理するか、Y3サステイン電極と同一データでアドレス処理するかの選択範囲が広がり、最適な処理を選択することにより、アドレス制御期間の短縮に伴う画質劣化を低減させることができる。

20

30

**【0064】**

また、本実施形態によれば、他の実施形態のような常に同一ペアの2ラインが同一データで処理される方式では、2ラインのデータが類似な値となりやすく、ラインペアリングと呼ばれる妨害が生じてしまう可能性があるが、同一データで処理するラインペアが2通りあることにより、ラインペアリングを目立ちにくくする効果がある。

**【0065】**

このように、本実施形態によれば、従来の擬似輪郭妨害低減の効果を保持したままアドレス制御期間を圧縮することができ、高輝度あるいは階調特性の優れた表示装置を実現することができる。また、アドレス制御期間を圧縮することによって生じる時間を使ってサブフィールド数を増加させ、擬似輪郭妨害を低減させることもできる。

40

**【0066】**

なお、このようなラインペアリングを低減するために、第2，第3の実施形態における発光重みの異なるサブフィールドの場合でも、間引くラインの位相を互いに変えるように構成してもよい。また、フィールド単位で間引くラインの位相を変化させるものであってもよい。例えば、奇数フィールドと偶数フィールドとでペアとなるラインを変化させる構成とすればよい。

50

**【0067】**

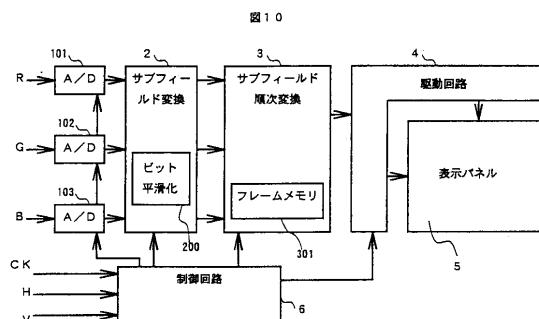

次に、上記の各実施形態に係わるサブフィールド構成を適用した表示装置の構成を図10を用いて説明する。

**【0068】**

同図において、101, 102, 103は夫々R, G, Bのアナログ映像信号をデジタル信号に変換するA/D変換回路、2はA/D変換された2進のデジタル信号をサブフィールドの発光・非発光を表わすサブフィールドデータに変換するサブフィールド変換回路、200はサブフィールド変換回路2内に設けられており、アドレス制御期間の圧縮を行なうサブフィールドに対応する制御ビットの平滑化処理を行なう制御ビット平滑化回路、3は画素単位で表わされるサブフィールドデータをサブフィールド単位の面順次の形に変換するサブフィールド順次変換回路、301はサブフィールド順次変換回路3内に設けられたビット単位での面順次を実現するためのフレームメモリ、4はサブフィールド単位の面順次形式に変換された信号を駆動に必要なパルスを追加挿入して表示デバイスを駆動するための電圧（あるいは電流）に変換する駆動回路、5はサブフィールド方式で階調表現が行なわれる表示パネル、6は入力映像信号のタイミング情報であるドットクロックCK, 水平同期信号H, 垂直同期信号Vなどから各ブロックに必要な制御信号を生成する制御回路である。

10

**【0069】**

ここで、入力されたR, G, Bの各信号は、A/D変換回路101, 102, 103により、デジタル信号に変換される。このデジタル信号は一般の2進数表記に基づくものであり、各ビットが2のべき乗の重みを有している。具体的には、b0, b1, ..., b6, b7の8ビットの信号に量子化する際には、最下位ビットb0が1の重みを有し、b1が2、b2が4、b3が8、... b7が128の重みを有している。これらのデジタル信号は、サブフィールド変換回路2により、サブフィールドの発光・非発光を示すサブフィールドデータに変換される。このサブフィールドデータは表示を行なうサブフィールドの数に対応したビット数の情報からなり、8サブフィールドにより表示を行なう際には、S0, S1, ..., S7の8ビットの信号で構成される。さらに、ビットS0は先頭のサブフィールドSF1の発光期間にその画素が発光するか否かを示しており、同様に、S1, S2, ... の順でサブフィールドSF2, SF3の発光・非発光に対応している。

20

**【0070】**

さらに、制御ビット平滑化回路200では、アドレス制御期間の圧縮を行なうサブフィールドに対応する制御ビットの平滑化処理を行なう。これは、2ライン同時に同一の制御ビットでアドレスを行なうため、ペアとなる1ライン上のサブフィールドデータあるいは1ライン下のサブフィールドデータとで該当する制御ビットが同じデータとなるよう変換する処理である。なお、このサブフィールド制御ビット平滑化処理の説明は後述する。

30

**【0071】**

次に、このサブフィールドデータはサブフィールド順次変換回路3に供給され、このサブフィールド順次変換回路3内に設けられたフレームメモリ301に画素単位で書き込まれる。フレームメモリ301からの読み出しが、サブフィールド単位で面順次に読み出しが行なわれる。即ち、サブフィールドSF1での発光の有無を示すビットS0が1フィールド分読み出された後、サブフィールドSF2の発光の有無を示すビットS1が読み出され、以下順に、S2, S3, ..., S7の順で読み出され、アドレスデータとして出力されることにより、各サブフィールドが構成される。この際、アドレス制御期間の圧縮を行なうサブフィールドでは、2ラインに1ラインが間引かれて半分のライン数のデータがアドレスデータとして読み出される。この後、駆動回路4で表示素子を駆動するのに必要な信号変換やパルスの挿入などが行なわれ、マトリックスディスプレイパネル5が駆動される。

40

**【0072】**

なお、アドレス制御期間のアドレスデータと同時に出力されるスキャンパルスは、通常の

50

ライン単位でアドレス処理を行なうサブフィールドでは、図2に示したタイミングであり、2ライン同時にアドレス処理してアドレス制御期間を圧縮したサブフィールドでは、図5あるいは図9に示したタイミングで出力される。

#### 【0073】

上記のように構成することにより、所定のサブフィールドのアドレス制御期間を短縮化させることができ、従来に比べて高輝度あるいは高画質の表示装置を実現することができる。

#### 【0074】

なお、フレームメモリ301では、全てのデータが書き込まれ、読み出しの段階でアドレス制御期間の圧縮を行なう際に2ラインに1ラインが間引かれる構成としたが、書込みの段階で間引く構成であってもよい。これにより、メモリ容量を低減でき、同一容量のメモリであっても、より高解像度あるいは多階調の表示ができる。10

#### 【0075】

また、サブフィールド数を増加させる、あるいは2のべき乗と異なる発光重みを割り当てて擬似輪郭妨害低減の処理を行なう場合には、サブフィールド変換回路2において、入力映像信号レベルからサブフィールド発光パターンへの変換が行なわれる。例えば、8ビットで入力される映像信号を10サブフィールドで表示を行なう場合には、8ビットの入力信号から10ビットのサブフィールドデータへの変換が組み合わせ論理回路あるいはルックアップテーブルなどにより行なわれる。

#### 【0076】

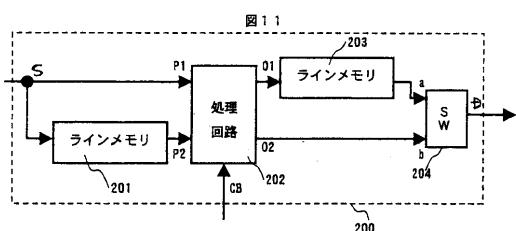

次に、制御ビット平滑化回路200の構成について図11を用いて説明する。20

同図において、201はサブフィールドデータを1ライン遅延させるためのラインメモリ、202は2つの入力P1, P2に対して制御信号CBで指定されたビットデータが等しくなるように変換して出力O1, O2として出力する処理回路、203は処理回路202の出力O1を1ライン遅延させるためのラインメモリ、204はライン単位で2つの入力a, bを切り換えて出力する切換回路である。

#### 【0077】

ここで、各サブフィールドの発光・非発光をビットデータに対応させたサブフィールドデータSは、ラインメモリ201と、入力P1として処理回路202とに供給される。ラインメモリ201で1ライン遅延したサブフィールドデータSは、入力P2として処理回路202に供給される。処理回路202では、入力P1としてのサブフィールドデータと入力P2としての1ライン遅延したサブフィールドデータとにより、現在のラインと1ライン前との上下に隣接する2つの画素のサブフィールドデータに対して所定のビットデータが等しくなるように変換が行なわれる。このような変換処理を施されたサブフィールドデータは、出力O1, O2として、処理回路202から出力される。処理回路202の出力O1, O2は画面上で垂直に隣接する画素のサブフィールドデータであるため、出力O1をラインメモリ203で1ライン遅延させ、切換回路204をライン毎に切り換えて2ラインの信号を順次化することにより、所定のビットデータが2ライン同一値をとるサブフィールドデータDに変換することができる。30

#### 【0078】

なお、この処理回路202で等しいビットデータとなるように処理するビットの位置は制御信号CBによって決定されており、どのサブフィールドのアドレス制御期間を短縮化するかが設定できるようになっている。また、アドレス制御期間の短縮化を全く行なわない場合の設定も、この制御信号CBにより行なわれ、この際には、処理回路202は入力P1をそのまま出力O1として出力し、入力P2をそのまま出力O2として出力する。40

#### 【0079】

処理回路202の最も簡単な構成は、入力P1の所定のビットデータをそのまま、入力P2の同一位置のビットデータとして、出力するものである。これにより、両者のビットデータを等しくすることができる。あるいは入力P2のビットデータを、入力P1の同一位置のビットデータとして、出力してもよく、入力信号との誤差が少なくなるようにいすれ

かの方法を選択するものであってもよい。これ以外の構成であっても、制御信号 C B で指定されたビットデータが output O 1 , O 2 で等しくなり、かつ変換に伴う入力信号との差が小さくなるように考慮されたものであればよい。この際に、必要に応じて制御信号 C B で指定されたビット以外の信号を変換に伴う入力信号との差が小さくなるように変更する構成であってもよい。

#### 【 0 0 8 0 】

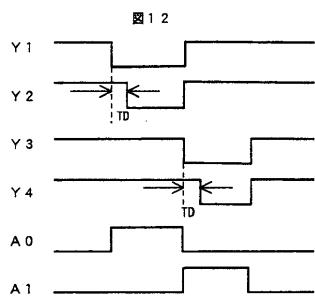

なお、上記の各実施形態では、特定のサブフィールドのアドレス制御期間を短縮するため、図 5 あるいは図 9 に示したように、スキャンパルスを 2 ライン同時に印加して同時に 2 ラインのアドレス処理を行なったが、このような処理を施すことにより、アドレス制御期間の短縮は可能となるが、アドレス処理時に同時に 2 ラインで放電が発生するため、アドレス放電電流のピーク値が増加してしまう問題がある。

10

#### 【 0 0 8 1 】

このような問題を避けるために、図 12 に示すように、Y 1 サステイン電極及び Y 2 サステイン電極、あるいは Y 3 サステイン電極及び Y 4 サステイン電極のペアとなる 2 つのラインに時間的にずれたパルスを印加する構成としてもよい。このように構成することにより、放電のピーク電流の増加を抑えることができ、ドライバ回路の小面積化や小型化など経済的効果がある。この際には、通常のアドレスタイミングに比較して、期間 T D だけ長い時間のアドレス処理周期として構成すればよい。あるいは、Y 2 サステイン電極及び Y 4 サステイン電極の後半のラインのアドレス放電は、Y 1 サステイン電極及び Y 3 サステイン電極の隣接画素放電に伴うプライミング効果により、放電発生のタイミングが早まる効果が期待されるため、通常のアドレス処理周期のまま、後半ラインのスキャンパルス幅が狭くなるように構成してもよい。このように構成することにより、従来並みの放電ピーク電流でアドレス制御期間の短縮化を実現できる。図 12 では、Y 1 サステイン電極と Y 2 サステイン電極、及び Y 3 サステイン電極と Y 4 サステイン電極を 2 ラインづつペアにした場合を示しているが、2 ラインに限らず、3 ラインあるいは 4 ライン同時の処理としてもよく、この際にも、アドレス放電が重複して発生しないように、スキャンパルスのタイミングをずらして与える構成とすればよい。また、Y 2 サステイン電極と Y 3 サステイン電極、及び Y 4 サステイン電極と Y 5 サステイン電極のようにペアとなるラインがずれた場合でも同様であり、後半のラインのスキャンパルスが遅れて印加されるように構成すればよい。

20

#### 【 0 0 8 2 】

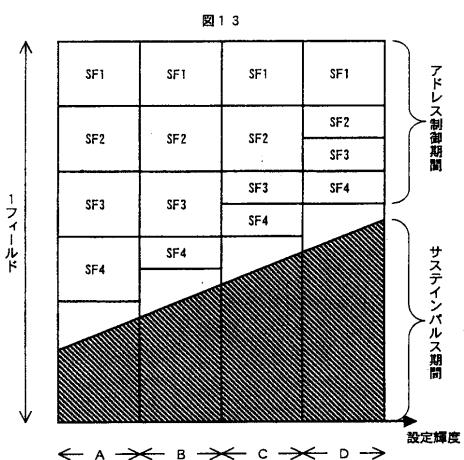

次に、本発明の表示装置において、アドレス制御期間を全く短縮化しない高解像度であるが低輝度の表示モードと、より多くのサブフィールドに対してアドレス制御期間を短縮化させる解像度は低いが高輝度な表示モードとの関係を図 13 を用いて説明する。

30

#### 【 0 0 8 3 】

同図において、縦軸は時間軸を示し、1 フィールド期間内をどのような処理を割り当てるかの時間配分を表わし、横軸は最高輝度の設定値を示し、この最高輝度の設定範囲によってサブフィールド S F 1 ~ S F 4 の時間配分が A , B , C , D の 4 つのモードで切り換わる様子を示す。

#### 【 0 0 8 4 】

40

ここで、S F 1 , S F 2 , S F 3 , S F 4 は夫々のサブフィールド S F 1 ~ S F 4 のアドレス制御期間を表わし、斜線で示した領域はサステイン期間内の総サステインパルス数を表わしている。

#### 【 0 0 8 5 】

同図に示すように、最高輝度の設定が低い A 領域では、全てのサブフィールドをアドレス制御期間の短縮化をせずに表示を行なう。設定輝度がやや高い B 領域では、サブフィールド S F 4 のアドレス制御期間を短縮化し、これによる空き時間をサステイン期間に割り当てて高輝度を実現している。最高輝度の設定を増加させた C 領域及び D 領域の場合には、最下位サブフィールド S F 4 に加えて、サブフィールド S F 3 , サブフィールド S F 2 のアドレス制御期間を順次 1 / 2 に短縮化し、設定輝度を実現するためのサステイン期間を

50

得る構成となっている。

【0086】

なお、この例では、アドレス制御期間を1/2に短縮化する場合を示しているが、これを1/3あるいは1/4に短縮化するものであってもよい。また、一旦1/2に短縮化した後、さらにサステイン期間を伸ばして輝度向上を図るために、1/3あるいは1/4と設定を変化するものであってもよい。

【0087】

本発明によれば、従来の表示装置では、アドレス制御期間の短縮化を全く行なわないため、図13に示すA領域に該当する場合しか使用することができなかつたが、必要に応じて表示解像度情報を領域B、領域C、領域Dのように制限することより、高輝度の設定が可能となる。

10

【0088】

また、本発明では、使用目的などに応じてより広範囲な輝度設定が可能となり、表示装置が置かれている周辺の輝度やユーザ設定、映像信号のレベルに応じて設定することができ、高画質で高輝度の表示装置を実現することができる。そのため、それほど高輝度を必要としないが高解像度が要求されるコンピュータ等のモニタや、それほど解像度は要求されないが高輝度でメリハリのある表示が望まれる映画やビデオ表示に応じて、画像内容や使用者の目的に適した画質を自在に実現することができる。

【0089】

なお、上記の各実施形態では、全てアドレス・サステイン分離方式に関するものであったが、アドレスとサステインの時間がフィールド内で重なり合う多重駆動方式であっても、アドレス制御期間が短縮化されることにより、同様の効果が得られる。

20

【0090】

また、インターレース(飛び越し走査)形式の入力信号(インターレース信号)に対して、フィールド毎に異なる位置のラインを発光ラインとすることにより、インターレース表示をする特開平9-160525号公報に記載のプラズマ表示装置にも、本発明式を適用することができる。

【0091】

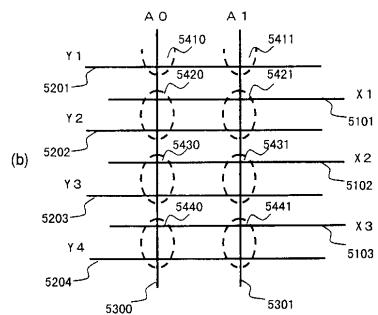

図14はインターレース表示を行なうプラズマディスプレイの放電セルと電極の配置を模式的に示す図であって、同図(a)は奇数フィールドの表示の場合を、同図(b)は偶数フィールドの表示の場合を夫々示しており、5101～5104はXサステイン電極、5201～5204はYサステイン電極、5300、5301はアドレス電極である。ここで、アドレス電極5300、5301は背面板上に、Xサステイン電極5101～5104及びYサステイン電極5201～5204は前面板上に夫々形成されている。

30

【0092】

インターレース表示を実現するために、奇数フィールドの表示の際には、図14(a)に示すように、Yサステイン電極5201-Xサステイン電極5101間、Yサステイン電極5202-Xサステイン電極5102間、Yサステイン電極5203-Xサステイン電極5103間夫々に放電発光による画素が形成される。また、偶数フィールドの表示の際には、図14(b)に示すように、Xサステイン電極5101-Yサステイン電極5200間、Xサステイン電極5102-Yサステイン電極5203間、Xサステイン電極5103-Yサステイン電極5204間夫々に放電発光による画素が形成される。このように、インターレース信号の奇数、偶数のフィールドで発光画素の位置をずらすことにより、インターレース表示を実現している。

40

【0093】

この奇数、偶数フィールドでの発光画素の位置制御は、Xサステイン電極とYサステイン電極とに印加するサステインパルスの位相によって行なわれるものであって、該当するサブフィールドでの画素の発光・非発光は、アドレス電極5300、5301とYサステイン電極5201、5202、5203、5204との間のアドレス放電によって制御されている。即ち、奇数フィールドと偶数フィールドとのいずれの場合も、画素5410の発

50

光・非発光の制御はYサステイン電極5201とアドレス電極5300との間のアドレス放電によって決定され、その後のサステインパルスの印加条件によって図14(a)に示す位置で画素5410が形成されるか、図14(b)に示す位置で画素5410が形成されるかする。従って、アドレス制御期間での動作は、偶数、奇数フィールドとともに、図2に示した従来のプラズマディスプレイと同様に、Yサステイン電極に順次スキャンパルスが印加され、画素の発光・非発光に応じてアドレス電極A0,A1を制御する動作は全く同様である。

#### 【0094】

従って、特開平9-160525号公報に記載されるようなインターレース表示のプラズマディスプレイであっても、順次走査のプラズマディスプレイと同様に、本発明を適用することができる。10

#### 【0095】

上記のように、複数ラインを同一データで同時にアドレスすることにより、アドレス制御期間を短縮化することも、従来のプラズマディスプレイと同様に、インターレース表示に適用可能であり、この際には、インターレース信号のフィールド内で隣接する複数ラインでの下位サブフィールドのデータを共通化することになる。ところで、1フレームに合成された映像信号では、同じフィールドでの隣接ライン間での垂直方向の距離が離れ、これらライン間の画像の相関性は低くなる。このため、従来の順次走査のプラズマディスプレイと比較して、アドレス処理のデータを同一とするライン数は2ライン程度に少なくし、また、アドレス処理を同一データとするサブフィールドを発光重みが小さいものに制限することが必要となり、これにより、画質劣化を目立ちにくくすることができる。20

#### 【0096】

ところで、画面上の上下に隣接する画素の下位nビットのデータを無条件に同一にすると、これら画素のデータが大きく異なるようになり、大幅な画質劣化を生じる場合があり、何らかの処理が必要である。例えば、上下に隣接する2つの画素のうちの上側の画素がレベル16、下側の画素データがレベル15である場合、2のべき乗の発光重みによるサブフィールド表現では、レベル16は[1, 0, 0, 0, 0]（左側が最上位ビット（最上位サブフィールドに対するもの）、右側が最下位ビット（最下位サブフィールドに対するもの）であり、“1”は発光サブフィールド、“0”は消灯サブフィールドを表わす）で表わされ、レベル15は[0, 1, 1, 1, 1]で表わされる。この際、下位4ビットに相当するサブフィールドを飛び越し走査の要領に従って2ラインに1ラインの割合で間引いて同一データとする場合を想定する。この場合、上側の画素のレベル16[1, 0, 0, 0, 0]の下位4ビット[0, 0, 0, 0]で、下側の画素のレベル15[0, 1, 1, 1, 1]の下位4ビット[1, 1, 1, 1]を置き換えるものとすると、下側の画素のレベルは0[0, 0, 0, 0]となる。即ち、かかる処理により、上側の画素のレベルはそのまま16「1, 0, 0, 0, 0」であるが、下側の画素は、そのレベルが15「0, 1, 1, 1, 1」から0「0, 0, 0, 0, 0」に大きく変化してしまう。また、その逆に、レベル16の上側の画素の下位4ビット「0, 0, 0, 0」を下側の画素のレベル15[0, 1, 1, 1, 1]の下位4ビット[1, 1, 1, 1]と書き替えると、この上側の画素のレベルは31[1, 1, 1, 1, 1]となり、下側の画素のレベルがそのまま15「0, 1, 1, 1, 1」であるのに対し、これら画素間のレベル差が大きくなる。3040

#### 【0097】

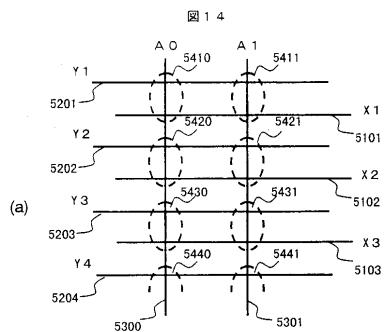

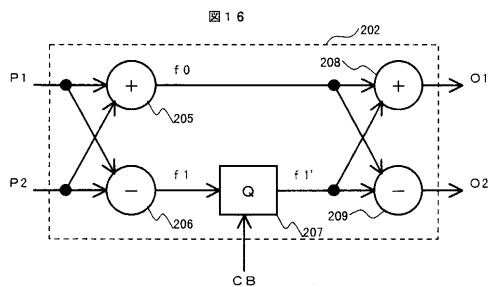

そこで、かかる問題を解消できるようにした図11における処理回路202の動作及び構成の一具体例について、図15及び図16を用いて説明する。

#### 【0098】

図15は処理回路202に入力される画面上で上下に隣接する2つの画素P1, P2（以下では、入力画素P1, P2という）の振幅と処理出力O1, O2（以下では、出力画素O1, O2という）の振幅とを模式的に示す図である。

#### 【0099】

同図において、上記の入力画素データとの変換による誤差が最も少なく、かつ所望の下位50

$n$  ビット（但し、 $n$  は 1 以上の整数であって、上記のように、この下位  $n$  ビットに最下位ビットが含まれるとは限らない）を隣接する画素間で共通にするために、画面上で上下に隣接する画素  $P_1$ ,  $P_2$  のデータの平均値  $f_0$  と、これら入力画素  $P_1$ ,  $P_2$  のデータの差分値  $f_1$  を次の式(1), (2)で算出する。

$$f_0 = (P_1 + P_2) / 2 \quad \dots \dots (1)$$

$$f_1 = (P_1 - P_2) / 2 \quad \dots \dots (2)$$

この演算は、入力画素  $P_1$ ,  $P_2$  を直交変換（2 行 × 2 列のアダマール変換）するものである。

#### 【0100】

次に、差分値  $f_1$  を、その下位  $n$  ビットが“0”となるように、変換（量子化）し、量子化差分値  $f_1'$  とする。この量子化差分値  $f_1'$  を用いて、出力画素  $O_1$ ,  $O_2$  を次の式(3), (4)で算出する。

$$O_1 = f_0 + f_1' \quad \dots \dots (3)$$

$$O_2 = f_0 - f_1' \quad \dots \dots (4)$$

この演算は、上記式(1), (2)による直交変換の逆変換である。

#### 【0101】

ここで、量子化差分値  $f_1'$  の下位  $n$  ビットは“0”であるため、差分値  $f_0$  をこれと加算あるいは減算して得られる出力画素  $O_1$ ,  $O_2$  の下位  $n$  ビットは、差分値  $f_0$  の下位  $n$  ビットと等しいデータとなっている。即ち、出力画素  $O_1$  と出力画素  $O_2$  との下位  $n$  ビットを等しいデータとすることができます。厳密には、かかる加算、減算によって下位  $n$  ビットのデータからキャリーやボローがない状態では、差分値  $f_0$  と量子化差分値  $f_0'$  との加算と減算とは等しい算出結果（2を法とする演算）となるため、上記式(3), (4)で得られる出力画素  $O_1$ ,  $O_2$  で下位  $n+1$  ビットのデータも等しくすることができます。

#### 【0102】

この際の出力画素  $O_1$ ,  $O_2$  の平均値  $(O_1 + O_2) / 2$  は常に入力画素  $P_1$ ,  $P_2$  の平均値  $f_0$  と等しくなり、常に隣接する 2 ラインの平均信号レベルを同一に保つことができる。また、下位  $n$  ビットを共通にすることによって生じる変換誤差は、出力画素  $O_1$ ,  $O_2$  ともに等しく、 $|f_1 - f_1'|$  づつ分散される。このため、特定の画素に変換誤差が集中せず、入力画像と変換後の画像との 2 乗平均誤差を最小にすることができます。なお、 $f_1 = f_1'$  の場合（即ち、差分値  $f_1$  の量子化対象とする下位  $n$  ビットが全て“0”）には、変換誤差がなく、 $P_1 = O_1$ ,  $P_2 = O_2$  となることは明らかであり、差分値  $f_1$  から量子化差分値  $f_1'$  への量子化回路 207 による量子化特性により、下位何ビットを共通化するかが決定される。

#### 【0103】

図 16 は処理回路 202 の一具体例を示すブロック図であって、205, 208 は加算回路、206, 209 は減算回路、207 は外部からの制御信号 CB によって特性の変化する量子化回路である。

なお、この図 16 では、画面の垂直方向に隣接する 2 つの画素の処理について説明する。従って、 $P_1$ ,  $P_2$  は入力画素、 $O_1$ ,  $O_2$  は出力画素である。

#### 【0104】

同図において、処理回路 202 に入力された画面上垂直方向に隣接した入力画素  $P_1$ ,  $P_2$  は、加算回路 205 と減算回路 206 とに供給される。加算回路 205 では、上記式(1)による入力画素  $P_1$ ,  $P_2$  の加算処理が行なわれ、平均値  $f_0$  が算出される。また、減算回路 206 では、上記式(2)による入力画素  $P_1$ ,  $P_2$  の減算処理が行なわれ、差分値  $f_1$  が算出される。この差分値  $f_1$  は量子化回路 207 に供給され、量子化差分値  $f_1'$  に変換される。量子化回路 207 では、制御信号 CB によって指定される下位  $n$  ビットが“0”となるように、差分値  $f_1$  が量子化処理される。このようにして得られた所望の下位  $n$  ビットが“0”的量子化差分値  $f_1'$  は、一方では、加算回路 205 で生成された平均値  $f_0$  と加算回路 208 で加算されて、上記式(3)で表わされる変換出力  $O_1$ 、即ち、出力画素  $O_1$  として出力され、また、他方では、減算回路 209 で加算回路 205 50

で生成された平均値  $f_0$  から減算されて、上記式(4)で表わされる変換出力  $O_2$ 、出力画素  $O_2$  として出力される。

#### 【0105】

一例として、画面上の上下に隣接する2つの画素が上記のレベル、即ち、上側の入力画素  $P_1$  がレベル16「1, 0, 0, 0, 0」であり、下側の入力画素  $P_2$  のレベルが15「0, 1, 1, 1, 1」である場合について説明する。

#### 【0106】

上記式(1), (2)により、

$$\begin{aligned} f_0 &= ('1, 0, 0, 0, 0' + '0, 1, 1, 1, 1') / 2 \\ &= '0, 1, 1, 1, 1' \end{aligned}$$

10

$$\begin{aligned} f_1 &= ('1, 0, 0, 0, 0' - '0, 1, 1, 1, 1') / 2 \\ &= '0, 0, 0, 0, 0' \end{aligned}$$

であり、差分値  $f_1$  を、その下位4ビットを“0”とする量子化によって得られる量子化差分値  $f_1'$  は「0, 0, 0, 0, 0」となる。従って、得られる出力画素  $O_1, O_2$  は、上記式(3), (4)により、

$$O_1 = '0, 1, 1, 1, 1' + '0, 0, 0, 0, 0'$$

$$O_2 = '0, 1, 1, 1, 1' - '0, 0, 0, 0, 0'$$

となり、いずれもレベル15「0, 1, 1, 1, 1」となって、下位4ビットが等しいものとなる。従って、上記の入力画素  $P_1$  の下位4ビットを入力画素  $P_2$  の下位4ビットと置き換えて夫々出力画素  $O_1, O_2$  とする場合に比べ、また、上記の入力画素  $P_2$  の下位4ビットを入力画素  $P_1$  の下位4ビットと置き換えて夫々出力画素  $O_1, O_2$  とする場合に比べ、出力画素  $O_1, O_2$  のレベルは入力画素  $P_1, P_2$  に近いものとなって画質の劣化がなくなり、また、これら出力画素  $O_1, O_2$  の下位4ビットが互いに等しいものとなって、アドレス制御期間の短縮化が可能となる。

#### 【0107】

以上のような構成により、画質劣化を最小に留め、しかも、垂直方向に隣接する2ラインの下位nビットのデータを共通化することができる。

#### 【0108】

なお、上記式(1), (2)での1/2の演算処理は、最下位ビットを切り捨てるこことによって実現可能であるため、明確に図示していないが、加算回路205及び減算回路206の出力を1/2とする形態とすればよい。また、かかる演算過程での丸め誤差などを低減するために、加算回路208及び減算回路209の出力部で1/2とする形態であってもよい。さらに、量子化回路207の量子化特性は制御信号CBによって制御されており、外部からのCBの設定により、下位何ビットを共通化するか制御することができる。

#### 【0109】

ところで、ここで示した画面上垂直方向に隣接した2つの画素の平均信号レベル(平均値)  $f_0$  は画像の垂直方向の低周波成分であり、また、それらの差分値  $f_1$  は垂直方向の高周波成分であると考えることができる。そして、量子化回路207により、下位nビットに相当するサブフィールドに対しては、垂直方向の高周波成分  $f_1$  が“0”となり、低周波成分  $f_0$  のみで構成されることになる。これにより、下位n個のサブフィールドでは、垂直解像度がこの平均信号レベル  $f_0$  のみの低周波成分に制限され、アドレス制御期間のデータ数を間引いて(同一データで同時にアドレス処理されて)表示することができる。

#### 【0110】

以上のように、入力信号を複数の垂直周波数成分に分割し、量子化手段により加減算するビットを選択して再合成することにより、所望のビットに相当する特定のサブフィールドの解像度情報を制限することができ、これにより、アドレス制御期間を短縮化するという点も本発明の特徴である。

10

20

30

40

50

**【0111】**

以上は垂直方向に隣接する2ラインに対する処理であったが、さらに、複数のラインについて、それらの下位nサブフィールドに相当するデータを共通化することができる。以下に4ラインに拡張した場合について説明する。

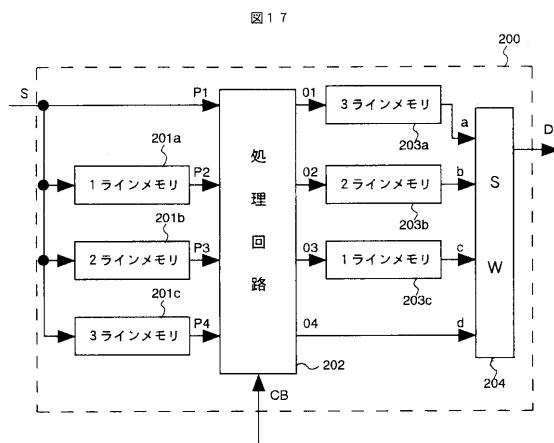

**【0112】**

図17は画面上垂直方向に順に隣接する4つの画素P1～P4の下位nビットを同時にアドレス処理する場合のビット平滑回路200の一具体例を示すブロック図であって、201aは1ライン分の遅延量をもつ1ラインメモリ、201bは2ライン分の遅延量をもつ2ラインメモリ、201cは3ライン分の遅延量をもつ3ラインメモリ、203aは3ライン分の遅延量をもつ3ラインメモリ、203bは2ライン分の遅延量をもつ2ラインメモリ、203cは1ライン分の遅延量をもつ1ラインメモリであり、図11に対応する部分には同一符号を付けている。10

**【0113】**

同図において、各サブフィールドの発光・非発光をビットデータに対応させたサブフィールドデータSは、直接、また、1ラインメモリ201aで1ライン期間遅延されて、また、2ラインメモリ201bで2ライン期間遅延され、また、3ラインメモリ201cで3ライン期間遅延されて、夫々処理回路202に供給される。従って、画面上垂直方向に順に隣接する入力画素P1, P2, P3, P4は、同時に処理回路202に供給される。処理回路202では、これら入力画素P1～P4が変換処理され、これら入力画素P1～P4に対して画面上垂直方向に順に隣接し、かつ互いに所望の下位nビットのデータが等しい出力画素O1, O2, O3, O4の信号が生成される。出力O1の信号は3ラインメモリ203aで3ライン期間分遅延されて入力aとして、出力O2の信号は2ラインメモリ203bで2ライン期間分遅延されて入力bとして、出力O3の信号は1ラインメモリ203cで1ライン期間分遅延されて入力cとして、出力O4の信号は入力dとして直接、夫々切換回路204に供給される。切換回路204はライン毎に所定の順序でこれら入力a～dを選択切り換えて順次化し、これにより、常に垂直方向に順に隣接した4つの画素で所望の下位nビットのデータが同一となるサブフィールドデータDが得られる。20

**【0114】**

なお、この処理回路202で等しいビットデータとなるように処理するビットの位置は制御信号CBによって決定されており、どのサブフィールドのアドレス制御期間を短縮化するかが設定できるようになっている。また、アドレス制御期間の短縮化を全く行なわない場合の設定も、この制御信号CBにより行なわれ、この際には、処理回路202は入力画素P1～P4を夫々そのまま出力画素O1～O4として出力する。30

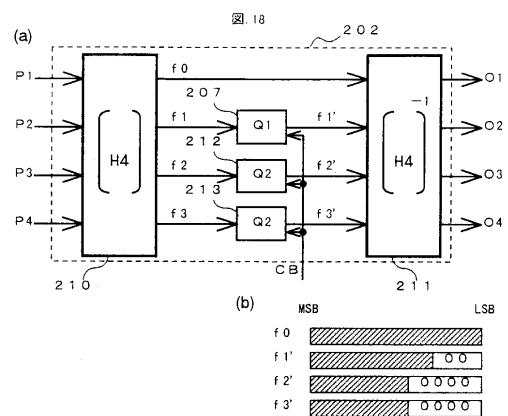

**【0115】**

図18(a)は図17での処理回路202の一具体例を示すブロック図であって、210は同一フィールド内の画面上垂直方向に順に隣接する入力画素P1, P2, P3, P4を4つの周波数成分f0, f1, f2, f3に変換する4次のアダマール変換回路、211はf0, f1', f2', f3'の4つの周波数成分から出力画素O1, O2, O3, O4に逆変換を行なう4次のアダマール逆変換回路、207は周波数成分f1を量子化して量子化周波数成分f1'に変換する量子化回路、212は周波数成分f2を量子化して量子化周波数成分f2'に変換する量子化回路、213は周波数成分f3を量子化して量子化周波数成分f3'に変換する量子化回路である。40

また、図18(b)は量子化回路207, 212, 213の量子化処理を示すものであり、斜線でハッチングした部分は量子化処理によって変換されないビットを示すものである。

なお、この具体例では、入力信号を周波数分割するために、直交行列の1種である4次のアダマール行列H<sub>4</sub>、即ち、

**【数1】**

$$H_4 = \begin{vmatrix} +1 & +1 & +1 & +1 \\ +1 & -1 & +1 & -1 \\ +1 & +1 & -1 & -1 \\ +1 & -1 & -1 & +1 \end{vmatrix}$$

による直交変換を用いるものであるが、他の直交変換方法を用いてもよい。

【0116】

同図において、画面上垂直方向に順に隣接した入力画素 P1, P2, P3, P4 はアダマール変換回路 210 に供給され、上記のアダマール行列を用いた直交変換により、

【数2】

$$\begin{array}{c|c|c} f_0 & \begin{vmatrix} +1 & +1 & +1 & +1 \\ +1 & -1 & +1 & -1 \\ +1 & +1 & -1 & -1 \\ +1 & -1 & -1 & +1 \end{vmatrix} & P_1 \\ f_3 & = & P_2 \\ f_1 & & P_3 \\ f_2 & & P_4 \end{array}$$

10

20

即ち、

$$f_0 = P_1 + P_2 + P_3 + P_4$$

$$f_1 = P_1 + P_2 - P_3 - P_4$$

$$f_2 = P_1 - P_2 - P_3 + P_4$$

$$f_3 = P_1 - P_2 + P_3 - P_4$$

の4個の周波数成分 f0, f1, f2, f3 に分解される。ここで、周波数成分 f0 は4つの入力画素 P1 ~ P4 の平均レベル(直流成分)である。また、周波数成分 f1, f2, f3 は夫々、4つの入力画素 P1 ~ P4 による周波数が異なる高周波数成分であって、画面の垂直方向の周波数成分であり、「+」から「-」や「-」から「+」への符号反転回数が多いほど周波数が高い。

30

【0117】

これら周波数成分 f0 ~ f3 のうちの周波数成分 f1, f2, f3 は夫々量子化回路 207, 212, 213 に供給され、制御信号 CB によって定められた量子化特性により、量子化される。図 18 (b) に示す例では、量子化回路 207 は周波数成分 f1 を量子化して、その下位 2 ビットが“0”となる量子化周波数成分 f1' を生成し、量子化回路 212, 213 は夫々、周波数成分 f2, f3 を量子化して、それらの下位 4 ビットが“0”となる量子化周波数成分 f2', f3' を生成する。勿論、周波数成分 f0 は量子化されていない。

【0118】

40

アダマール逆変換回路 211 では、上記数1の直交行列の逆行列  $H_4^{-1}$ 、即ち、

【数3】

$$H_4^{-1} = \begin{vmatrix} +1 & +1 & +1 & +1 \\ +1 & -1 & +1 & -1 \\ +1 & +1 & -1 & -1 \\ +1 & -1 & -1 & +1 \end{vmatrix}$$

50

を用いて(なお、この逆行列 $H_4^{-1}$ は直交行列 $H$ と等しい)これらの周波数成分 $f_0$ 及び量子化された $f_1'$ 、 $f_2'$ 、 $f_3'$ がアダマール逆変換され、出力画素を生成し出力する。

#### 【0119】

即ち、周波数成分 $f_0$ と量子化周波数成分 $f_1' \sim f_4'$ とはアダマール逆変換回路211に供給され、数3に示す逆行列 $H_4^{-1}$ を用いたアダマール逆変換により、

#### 【数4】

$$\begin{array}{c|c|c} O_1 & +1 & +1 & +1 & +1 \\ O_4 & +1 & -1 & +1 & -1 \\ O_2 & +1 & +1 & -1 & -1 \\ O_3 & +1 & -1 & -1 & +1 \end{array} = \begin{array}{c|c} f_0 & \\ f_1' & \\ f_2' & \\ f_3' & \end{array} \quad 10$$

即ち、

$$O_1 = (f_0 + f_1') + (f_2' + f_3') \dots (5)$$

$$O_2 = (f_0 + f_1') - (f_2' + f_3') \dots (6)$$

$$O_3 = (f_0 - f_1') - (f_2' - f_3') \dots (7)$$

$$O_4 = (f_0 - f_1') + (f_2' - f_3') \dots (8) \quad 20$$

の4つの出力画素 $O_1 \sim O_4$ が生成出力される。

#### 【0120】

この具体例では、周波数成分 $f_2$ に対する量子化回路212と周波数成分 $f_3$ に対する量子化回路213との量子化特性が等しく設定されており、これらから出力される量子化周波数成分 $f_2'$ 、 $f_3'$ は、ともに、下位4ビットが“0”となるように変換されている。これにより、上記式(5)、(6)の右辺第2項の $(f_2' + f_3')$ と式(7)、(8)の右辺第2項の $(f_2' - f_3')$ とでは、それらの下位4ビットが“0”となる。また、量子化周波数成分 $f_1'$ は下位2ビットが“0”である。これらの条件から、出力画素 $O_1 \sim O_4$ は周波数成分 $f_0$ と、量子化周波数成分 $f_1'$ と、 $(f_2' + f_3')$ あるいは $(f_2' - f_3')$ との上記式(5)～(8)に基づく加減算によって算出されるため、出力画素 $O_1 \sim O_4$ の少なくとも下位2ビットは周波数成分 $f_0$ の下位2ビットの値に等しく、垂直方向に順に隣接した4つの画素で下位2ビットのデータが等しくなる。30

#### 【0121】

次に、上記式(5)、(6)で示す出力画素 $O_1$ と出力画素 $O_2$ とを比較すると、出力画素 $O_1$ は $(f_0 + f_1')$ に下位4ビットが“0”である $(f_2' + f_3')$ を加算したものであり、出力画素 $O_2$ は $(f_0 + f_1')$ から $(f_2' + f_3')$ を減算したものであるから、出力画素 $O_1$ 、 $O_2$ の下位4ビットのデータは等しいが、さらに、下位5ビット目も等しくなる。上記式(5)、(6)において、 $(f_0 + f_1')$ 、 $(f_2' + f_3')$ の下位5ビット目のデータに対する出力画素 $O_1$ 、 $O_2$ の下位5ビット目は、

#### 【表1】

10

20

30

40

| $(f_0 + f_1')$ | $(f_2' + f_3')$ | 出力画素O1    | 出力画素O2   |

|----------------|-----------------|-----------|----------|

| “0”            | “0”             | “0”       | “0”      |

| “1”            | “0”             | “1”       | “1”      |

| “0”            | “1”             | “1”       | “1”(ボロー) |

| “1”            | “1”             | “0”(キャリー) | “0”      |

10

となり、出力画素O1, O2の下位5ビットのデータも等しくなる。但し、「ボロー」は下位6ビット目からのボロー、「キャリー」は下位6ビット目へのキャリーである。

#### 【0122】

同様に、上記式(7), (8)で表わされる出力画素O3と出力画素O4とを比較すると、これらは $(f_0 - f_1')$ と下位4ビットが“0”である $(f_2' - f_3')$ とを加算あるいは減算したものであるから、出力画素O1, O2の場合と同様、下位5ビット目までが同一のデータとなる。

#### 【0123】

即ち、上記数2のように入力画素P1～P4をアダマール変換して周波数成分 $f_0 \sim f_3$ を得、これら周波数成分 $f_1 \sim f_3$ を量子化した後、数4のようにアダマール逆変換することにより、垂直方向に隣接する2個の画素間で下位5ビットのデータを等しくすることができます。

20

#### 【0124】

以上のように、量子化回路207, 212, 213に図18(b)に示す量子化特性を設定することにより、下位5ビット目から下位3ビット目までは出力画素O1と出力画素O2、及び出力画素O3と出力画素O4の2ライン単位で等しいデータとなり、下位2ビット目と最下位ビットは垂直方向に順に隣接する4個の出力画素O1～O4全てで等しいデータとすることができる。

30

#### 【0125】

以上の処理により、下位2ビットに対応する2つの下位サブフィールドでは、同一データによる4ライン同時のアドレス処理を行なうことができ、下位5ビット目から下位3ビット目までに対応する3つのサブフィールドでは、同一データによる2ライン同時のアドレス処理を行なうことができる。これにより、下位5ビット目～下位3ビット目に対応するサブフィールドのアドレス制御期間を各ライン毎に順次アドレス処理を行なう場合の1/2の時間長に短縮することができ、下位2ビット目と最下位ビット(LSB)に対応する2つの下位サブフィールドのアドレス期間の時間長を同じく1/4に短縮することができる。

#### 【0126】

40

なお、入力画素P1～P4と出力画素O1～O4との振幅レンジを等しくするためには、式(5)～(8)に示す出力画素O1～O4に1/4の演算処理が必要であるが、これは下位2ビットを除く処理をすればよく、図16で示した処理回路202と同様に、これら演算データの有効ビットの設定により、特殊なハードウェアなく、これを実現できるため省略している。アダマール変換回路210の出力段で $f_0 \sim f_3$ を1/4にする構成であっても、出力画素O1～O4の振幅を1/4にする構成であってもよい。勿論、アダマール逆変換回路211に供給される周波数成分 $f_0$ や量子化回路207, 212, 213に供給される周波数成分 $f_1, f_2, f_3$ はこのように処理されたものである。

#### 【0127】

図19は図18に示した処理回路202を用いた図17に示したビット平滑回路200の

50

動作を示す図であって、図17に対応する信号には同一符号を付けています。

**【0128】**

図19(a)は処理回路202の入力P1～P4の時間関係を示すものであって、入力P2は入力P1を1ライン期間分遅延したもの、入力P3は入力P1を2ライン期間分遅延したもの、入力P4は入力P1を3ライン期間分遅延したものである。

**【0129】**

図19(b)は処理回路202の出力Q1～Q4の時間関係を示すものであって、括弧( )内は下位2ビットのデータを表わしている。括弧( )内の符号が等しいラインはそれらの下位2ビットのデータが等しいことを示している。例えば、(D)で表わされる出力O1のライン4と出力O2のライン3と出力O3のライン2と出力O4のライン1とは、下位2ビットのデータがDと等しいことになる。なお、ここでは、画面上垂直方向に隣接する2つの画素で下位5ビット目～下位3ビット目が等しいことは省いている。

10

**【0130】**

図19(c)は切換回路204の入力a, b, c, dを示すものであって、夫々で同じ順位のラインが同時刻となるが、同時刻のライン1では、入力a, b, c, dの順に下位2ビットのデータがA, B, C, Dの順に異なっており、次の同時刻のライン2では、入力a, b, c, dの順に下位2ビットのデータがB, C, D, Eの順に異なっており、次の同時刻のライン3では、入力a, b, c, dの順に下位2ビットのデータがC, D, E, Fの順に異なっており、……、最後に図示するライン7では、入力a, b, c, dの順に下位2ビットのデータがG, H, I, Jの順に異なっている。

20

**【0131】**

切換回路204は、図19の場合、ライン毎に入力d, c, b, aの順に繰り返し選択し、この結果、図19(d)に示すように、下位2ビットのデータが等しい順番の4個のラインがその順で選択され、連続する4ラインが同じ下位2ビットのデータをもつサブフィールドデータDが得られることになる。

**【0132】**

なお、かかるサブフィールドデータDにおいて、同じ下位2ビットのデータをもつ連続した4ラインのうち(例えば、図19(d)において、ライン1(D)～ライン4(D))、前半の2つのライン(ライン1(D)とライン2(D))は下位5ビット目～下位3ビット目が等しく、後半の2つのライン(ライン3(D)とライン4(D))も下位5ビット目～下位3ビット目が等しい。

30

**【0133】**

このようにして、アドレス制御期間を短縮化する所望のサブフィールドデータDが得られることになる。

**【0134】**

なお、図16に示した処理回路202を用いた図11に示すビット平滑回路200も、2入力P1, P2に対し、直交変換(ここでは、2行×2列のアダマール変換)を用いてサブフィールドデータDを得ていることになる。

**【0135】**

図16及び図18に示した処理回路202での処理は、直交変換(アダマール変換)を用いた画像データの圧縮・復号の過程と一致しており、直流成分に比較して高い周波数成分ほど粗く量子化する手法と極めて類似している。即ち、従来からの画像圧縮で蓄積された量子化ビット配分のノウハウを適用し、画質劣化をほとんど目立たないように変換することができる。

40

**【0136】**

また、直交変換を用いた画像圧縮方式により圧縮されて記録／伝送された映像信号を復号(圧縮された信号を伸張処理すること)して表示する場合には、予め本発明によるアドレス制御期間の圧縮処理によって欠落する情報が圧縮・記録／伝送の過程で低減されているため、実質的に画質劣化の少ない表示を実現することができる。

**【0137】**

50

以上のように、入力信号を複数の解像度情報に分割して、特定のサブフィールドの解像度情報を制限することにより、アドレス制御期間を短縮化することができる。

#### 【0138】

以上のように4つの垂直周波数成分に分割し、量子化手段により加減算するビットを選択し、再合成することにより、所望順位のビットに対応する特定のサブフィールドの解像度情報を制限することができ、これにより、そのサブフィールドでのアドレス制御期間を短縮化することができる。また、解像度情報を制限するサブフィールドや解像度の制限範囲は、制御信号CBでもってこれら周波数成分の量子化特性を変化させることにより、制御することができる。

#### 【0139】

この際に、複数に分割された周波数成分から画素を再合成する過程は、上記式(3)、(4)及び上記式(5)～(8)で示すように、係数が「1」と「-1」との線形結合による演算処理によって行なわれる。これにより、量子化手段によって選択したビットが直接出力画素に反映され、所望順位のビットに対応する特定のサブフィールドの解像度情報制限の設定を容易にすることができます。なお、実際には、出入力画素の振幅レンジを等しくするために、1/2あるいは1/4というような係数がかかるため、出力画素を合成する際の各周波数成分の係数が「+K」、「-K」の2種のみからなる線形結合で表わされれば、量子化特性の設定により、所望順位のビットに対応する特定のサブフィールドの解像度情報の制限の設定を容易にすることができます。従って、本発明は、上記の直交変換に限ることなく、逆変換の過程が「+K」、「-K」の2種のみの係数からなる線形結合であれば、他の直交変換を用いてもよい。

#### 【0140】

##### 【発明の効果】

以上説明したように、本発明によれば、必要な輝度に応じてアドレス制御期間を短縮化しこの時間を輝度・階調・擬似輪郭などの画質の改善に割り当てることができる。

#### 【0141】

また、比較的発光重みが小さい下位サブフィールドに対してデータ数を間引いて表示するよう構成することにより、画質劣化を低減させることができる。

#### 【0142】

また、最も発光重みが小さいサブフィールドを除いた、下位サブフィールドに対してデータ数を間引いて表示するよう構成することにより、ディザや誤差拡散処理などの擬似中間階調表現を行なうことができる。

#### 【0143】

また、高輝度表示を実現する場合にはより多くのサブフィールドに対してデータ数を間引いてサステイン期間を多く割り当てて表示し、低輝度であっても高精細の表示を行なう場合にはデータ間引きを行なうサブフィールドを減らす、あるいは全くなくすることにより、画像内容や使用者の目的に適した画質を実現することができる。

#### 【0144】

また、入力映像信号を垂直周波数成分に分割し、表示解像度情報を制限して点灯画素を制御する時間を短くすることにより、画質劣化の目立ちにくい高画質な表示を実現することができる。

##### 【図面の簡単な説明】

【図1】AC3電極型プラズマディスプレイの放電セルと電極の配置を示す模式図である。

【図2】従来技術に係るアドレス制御期間におけるYサステイン電極及びアドレス電極の印加電圧を示す図である。

【図3】従来技術に係る1フィールドが3つのサブフィールドから構成されたフィールド構成を示す図である。

【図4】本発明の第1の実施形態に係わり、サブフィールドのうち発光重みの少ない下位サブフィールドのアドレス制御期間を半分にしたフィールド構成を示す図である。

10

20

30

40

50

【図5】本発明の第1の実施形態に係わり、アドレス制御期間におけるYサステイン電極及びアドレス電極の印加電圧を示す図である。

【図6】本発明の第2の実施形態に係わり、最下位サブフィールドを増やし、発光重みの少ない下位サブフィールドのアドレス制御期間を半分にしたフィールド構成を示す図である。

【図7】本発明の第3の実施形態に係わり、最下位サブフィールドを増やし、最下位のサブフィールドを除く下位サブフィールドのアドレス制御期間を半分にしたフィールド構成を示す図である。

【図8】本発明の第4の実施形態に係わり、最下位サブフィールドを増やし、最下位のサブフィールドを除く下位のサブフィールドのアドレス制御期間を半分にするとともに、そのサステイン期間の発光比率を同じにしたフィールド構成を示す図である。 10

【図9】本発明の第4の実施形態に係わるアドレス制御期間のYサステイン電極及びアドレス電極の印加電圧を示す図である。

【図10】本発明の各実施形態に係わるサブフィールド構成を適用した表示装置の構成を示すブロック図である。

【図11】図10に示す制御ビット平滑化回路200の構成を示すブロック図である。

【図12】本発明の各実施形態に係わるアドレス制御期間のYサステイン電極及びアドレス電極の印加電圧の他の例を示す図である。

【図13】本発明における、アドレス制御期間を短縮化しない高解像度・低輝度の表示モードと、アドレス制御期間を短縮化した低解像度・高輝度の表示モードとの関係を説明するための図である。 20

【図14】インターレース表示に適したプラズマディスプレイの奇数フィールド表示と偶数フィールド表示との際の放電セルと電極の配置を示す模式図である。

【図15】図11における処理回路の動作を説明する模式図である。

【図16】図11における処理回路の一具体例を示すブロック図である。

【図17】図10におけるビット平滑化回路の他の具体例を示すブロック図である。

【図18】図17における処理回路の一具体例を示すブロック図である。

【図19】図18に示す処理回路を用いた図17に示すビット平滑回路の動作を示す図である。

#### 【符号の説明】

10 リセット期間

20 アドレス制御期間

21, 22 時間短縮されたアドレス制御期間

31~34 サステイン期間

101~103 A/D変換回路

2 サブフィールド変換回路

200 制御ビット平滑化回路

201, 203 ラインメモリ

202 処理回路

204 切換回路

205, 208 加算回路

206, 209 減算回路

207, 212, 213 量子化回路

210 アダマール変換回路

211 アダマール逆変換回路

3 サブフィールド順次変換回路

301 フレームメモリ

4 駆動回路

5 表示パネル

5101~5104 Xサステイン電極

30

40

50

- 5 2 0 1 ~ 5 2 0 4 Y サステイン電極

5 3 0 0 , 5 3 0 1 アドレス電極

5 4 1 0 , 5 4 1 1 放電セル

5 4 2 0 , 5 4 2 1 放電セル

5 4 3 0 , 5 4 3 1 放電セル

5 4 4 0 , 5 4 4 1 放電セル

6 制御回路

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

図19

**(a)**

|     |    |    |   |   |   |   |   |

|-----|----|----|---|---|---|---|---|

| P 1 | 1  | 2  | 3 | 4 | 5 | 6 | 7 |

| P 2 | 0  | 1  | 2 | 3 | 4 | 5 | 6 |

| P 3 | -1 | 0  | 1 | 2 | 3 | 4 | 5 |

| P 4 | -2 | -1 | 0 | 1 | 2 | 3 | 4 |

**(b)**

|     |       |       |      |      |      |      |      |

|-----|-------|-------|------|------|------|------|------|

| 0 1 | 1(A)  | 2(B)  | 3(C) | 4(D) | 5(E) | 6(F) | 7(G) |

| 0 2 | 0(A)  | 1(B)  | 2(C) | 3(D) | 4(E) | 5(F) | 6(G) |

| 0 3 | -1(A) | 0(B)  | 1(C) | 2(D) | 3(E) | 4(F) | 5(G) |

| 0 4 | -2(A) | -1(B) | 0(C) | 1(D) | 2(E) | 3(F) | 4(G) |

**(c)**

|   |      |      |      |      |      |      |      |

|---|------|------|------|------|------|------|------|

| a | 1(A) | 2(B) | 3(C) | 4(D) | 5(E) | 6(F) | 7(G) |

| b | 1(B) | 2(C) | 3(D) | 4(E) | 5(F) | 6(G) | 7(H) |

| c | 1(C) | 2(D) | 3(E) | 4(F) | 5(G) | 6(H) | 7(I) |

| d | 1(D) | 2(E) | 3(F) | 4(G) | 5(H) | 6(I) | 7(J) |

**(d)**

|   |      |      |      |      |      |      |      |

|---|------|------|------|------|------|------|------|

| D | 1(D) | 2(D) | 3(D) | 4(D) | 5(H) | 6(H) | 7(H) |

|---|------|------|------|------|------|------|------|

---

フロントページの続き

(72)発明者 鴻上 明彦

神奈川県横浜市戸塚区吉田町292番地 株式会社 日立製作所 情報メディア事業本部内

(72)発明者 大高 広

神奈川県横浜市戸塚区吉田町292番地 株式会社 日立製作所 情報メディア事業本部内

審査官 西島 篤宏

(56)参考文献 特開平11-024628(JP,A)

特開平09-305142(JP,A)

特開平10-207422(JP,A)

特開平10-301532(JP,A)

特開平05-273933(JP,A)

特開平10-066001(JP,A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00- 3/3