(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-164313

(P2012-164313A)

(43) 公開日 平成24年8月30日(2012.8.30)

(51) Int.Cl.

G05B 19/05 (2006.01)

F 1

G 05 B 19/05

テーマコード(参考)

L

5 H 2 2 O

審査請求 未請求 請求項の数 10 O L 外国語出願 (全 19 頁)

(21) 出願番号 特願2012-23564 (P2012-23564)

(22) 出願日 平成24年2月7日 (2012.2.7)

(31) 優先権主張番号 13/022,808

(32) 優先日 平成23年2月8日 (2011.2.8)

(33) 優先権主張国 米国(US)

(71) 出願人 390041542

ゼネラル・エレクトリック・カンパニイ

アメリカ合衆国、ニューヨーク州、スケネ

クタディ、リバーロード、1番

(74) 代理人 100137545

弁理士 荒川 智志

(74) 代理人 100105588

弁理士 小倉 博

(74) 代理人 100129779

弁理士 黒川 俊久

(74) 代理人 100113974

弁理士 田中 拓人

最終頁に続く

(54) 【発明の名称】インターフェースコネクタのデバイス、システムおよび方法

(57) 【要約】 (修正有)

【課題】機械監視システムをグレードアップするために、インターフェースコネクタを用いて第1の回路基板および第2の回路基板を接続するための、デバイス、システムおよび方法を提供する。

【解決手段】インターフェースコネクタ100を用いて第1の回路基板102および第2の回路基板104を接続するデバイス、方法およびシステムである。ある態様では、ケーシング内で互いに絶縁されている複数の導電性コネクタとを含む、インターフェースコネクタ100が説明される。各コネクタは、第1の端部および第2の端部を有し、第1の端部は第1の回路基板102に接続し、第2の端部は第2の回路基板104に接続する。複数のコネクタは、インターフェースコネクタ100の第1の列および第2の列を形成する。第1の列は偶数番号のコネクタを含み、第2の列は奇数番号のコネクタを含む。

【選択図】図1

FIG. 1

## 【特許請求の範囲】

## 【請求項 1】

2つの回路基板を接続するためのインターフェースコネクタであって、

ケーシング(202)と、

前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する導電性コネクタ(204)とを含み、前記第1の端部(302)が第1の回路基板(102)に接続し、前記第2の端部(304)が第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数のコネクタ(204)が、

コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、

コネクタ41、42、62～67、72～75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、

コネクタ5～12、19～40、76、82、83、85、87～91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供するように割り当てられる、インターフェースコネクタ。

## 【請求項 2】

コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78が、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続であり、

コネクタ1～4が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供し、

コネクタ63が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のクロック信号のための電気的な経路を提供し、

コネクタ48および56が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のトリップ乗算信号のための電気的な経路を提供し、

コネクタ24～39が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の管理データバス信号のための電気的な経路を提供する、請求項1記載のインターフェースコネクタ。

## 【請求項 3】

前記複数のコネクタ(204)の各々の前記第1の端部(302)が、前記第1の回路基板(102)に接続するためのメス型の端部を含み、前記複数のコネクタ(204)の各々の前記第2の端部(304)が、前記第2の回路基板(104)に接続するためのオス型の端部を含む、請求項1記載のインターフェースコネクタ。

## 【請求項 4】

前記複数のコネクタ(204)の各々の前記第1の端部(302)が、前記第1の回路基板(102)に接続するためのオス型の端部を含み、前記複数のコネクタ(204)の各々の前記第2の端部(304)が、前記第2の回路基板(104)に接続するためのメス型の端部を含む、請求項1記載のインターフェースコネクタ。

## 【請求項 5】

前記第1の回路基板(102)が、Bentley Nevada機械監視システムのための回路基板であり、前記インターフェースコネクタが、前記第2の回路基板(104)を、Bentley Nevada機械監視システムのための前記回路基板に電気的に接続するために使用される、請求項1記載のインターフェースコネクタ。

## 【請求項 6】

10

20

30

40

50

2つの回路基板を接続するための方法であって、

インターフェースコネクタ(100)を設けるステップであって、前記インターフェースコネクタ(100)が、ケーシング(202)と、前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する導電性コネクタ(204)とを含み、前記第1の端部(302)が第1の回路基板(102)に接続し、前記第2の端部(304)が第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数の導電性コネクタ(204)が、少なくとも120個のコネクタを含む、ステップと、

10

前記複数のコネクタ(204)が、

コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、

コネクタ41、42、62～67、72～75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、

コネクタ5～12、19～40、76、82、83、85、87～91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する

20

ように割り当てられるように、前記インターフェースコネクタ(100)を構成するステップと、

前記構成されたインターフェースコネクタ(100)を用いて、前記第1の回路基板(102)および前記第2の回路基板(104)を接続するステップと

を含む、方法。

#### 【請求項7】

コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供するように、前記インターフェースコネクタ(100)を構成するステップが、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78を、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続として構成するステップと、前記第1の回路基板と前記第2の回路基板との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供するように、コネクタ1～4を構成するステップと、前記第1の回路基板と前記第2の回路基板との間のトリップ乗算信号のための電気的な経路として、コネクタ48および56を構成するステップとを含み、

前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品が、ホストプロセッサおよびFPGAを含み、

コネクタ41、42、62～67、72～75および81が、前記第1の回路基板と前記第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供するように、前記インターフェースコネクタを構成するステップが、前記第1の回路基板と前記第2の回路基板との間のクロック信号のための電気的な経路を提供するようにコネクタ63を構成するステップを含み、

コネクタ5～12、19～40、76、82、83、85、87～91および93が、前記第1の回路基板と前記第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供するように、前記インターフェースコネクタを構成するステップが、前記第1の回路基板と前記第2の回路基板との間の管理データバス信号のための電気的な経路として、コネクタ24～39を構成するステップを含む、請求項6記載の方法。

20

30

40

50

## 【請求項 8】

前記構成されたインターフェースコネクタ(100)を用いて前記第1の回路基板(102)および前記第2の回路基板(104)を接続するステップが、前記第2の回路基板(104)を、Bentley Nevada機械監視システムのための回路基板に電気的に接続するステップを含む、請求項6記載の方法。

## 【請求項 9】

インターフェースコネクタ(100)と、

第1の回路基板(102)と、

第2の回路基板(104)と

を含むシステムであって、前記インターフェースコネクタ(100)が、前記第1の回路基板(102)を前記第2の回路基板(104)に接続するのに使用され、前記インターフェースコネクタ(100)が、

ケーシング(202)と、

前記ケーシング(202)内で互いに絶縁され、各コネクタ(204)が第1の端部(302)および第2の端部(304)を有する少なくとも120個の導電性コネクタ(204)とを含み、前記第1の端部(302)が前記第1の回路基板(102)に接続し、前記第2の端部(304)が前記第2の回路基板(104)に接続し、前記複数のコネクタ(204)が第1の列(404)および第2の列(406)を形成し、前期第1の列(404)が偶数番号のコネクタ(204)を含み、前記第2の列(406)が奇数番号のコネクタ(204)を含み、前記複数のコネクタ(204)が、

コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の一般的な回路の接続のための電気的な経路を提供し、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78が、前記第1の回路基板(102)または前記第2の回路基板(104)の上の電子部品のための電源の接続であり、コネクタ1～4が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供し、コネクタ48および56が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のトリップ乗算信号のための電気的な経路を提供し、

コネクタ41、42、62～67、72～75および81が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ63が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のクロック信号のための電気的な経路を提供し、

コネクタ5～12、19～40、76、82、83、85、87～91および93が、前記第1の回路基板(102)と前記第2の回路基板(104)との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供し、コネクタ24～39が、前記第1の回路基板(102)と前記第2の回路基板(104)との間の管理データバス信号のための電気的な経路を提供する

ように構成される、システム。

## 【請求項 10】

前記第1の回路基板(102)が、Bentley Nevada機械監視システムのための回路基板であり、前記インターフェースコネクタ(100)が、前記第2の回路基板(104)を、Bentley Nevada機械監視システムのための前記回路基板に電気的に接続するために使用される、請求項9記載のシステム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本出願は一般にインターフェースコネクタに関し、より詳細には、監視システムをグレードアップするために用いるインターフェースコネクタに関する。

## 【背景技術】

10

20

30

40

50

## 【0002】

既知の機械は、動作中に振動または別の異常な挙動を示すことがある。1つまたは複数のセンサを使用し、そのような挙動を測定および/または監視すること、また例えば、モータ駆動軸で発生する振動の量、モータ駆動軸の回転速度、および/または動作している機械もしくはモータの任意の他の適切な動作特性を決定することができる。センサは、しばしば、複数の監視装置を含む監視システムに結合される。少なくとも、一部の既知の監視システムでは、1つまたは複数のセンサから測定結果を表す信号を受信し、それに応答して、信号に対して少なくとも1つの処理ステップを実行し、その後、ユーザが使用できる形式でユーザに対して測定結果を表示する診断プラットフォームに、修正された信号を送信する。

10

## 【0003】

場合によっては、機械は交換または改良され、技術は進歩するので、そのような監視システムをグレードアップすることが望ましい。古いシステムを「ばらばらにする（rip and tear）」よりも、グレードアップ用部品によって既存の監視システムをグレードアップした方が、より効率的かつタイムリであることがある。場合によっては、監視システムが監視用に用いるモジュールは、プロセッサ、フィールドプログラマブルゲートアレイ（FPGA）、抵抗、コンデンサ、インダクタ、メモリなどの電子部品を追加することで改良することができる。場合によっては、新たな電子部品を含む第2の回路基板を追加することによって、監視モジュールの元の回路基板を拡張することが必要な場合がある。

20

## 【先行技術文献】

## 【特許文献】

## 【0004】

## 【特許文献1】米国特許第7188171号明細書

## 【発明の概要】

## 【0005】

したがって、その一部を上述した当技術分野における課題を克服する、デバイス、システムおよび方法が望まれている。具体的には、インターフェースコネクタを用いて第1の回路基板および第2の回路基板を接続するための、デバイス、システムおよび方法が望まれている。

30

## 【0006】

インターフェースコネクタを用いて2つの回路基板を接続するための、デバイス、方法およびシステムの実施形態が、本明細書で説明される。

## 【0007】

ある態様では、2つの回路基板を接続するためのインターフェースコネクタが説明される。ある実施形態のインターフェースコネクタは、ケーシングと、ケーシング内で互いに絶縁されている複数の導電性コネクタとを含む。それぞれのコネクタは、第1の端部および第2の端部を有する。第1の端部は第1の回路基板に接続し、第2の端部は第2の回路基板に接続する。インターフェースコネクタの複数のコネクタは、第1の列および第2の列を形成する。第1の列は偶数番号のコネクタを含み、前記第2の列は奇数番号のコネクタを含み、複数のコネクタは以下のように割り当てられる。コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120は、第1の回路基板と第2の回路基板との間の一般的な回路の接続のための電気的な経路を提供し、コネクタ41、42、62～67、72～75および81は、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ5～12、19～40、76、82、83、85、87～91および93は、第1の回路基板と第2の回路基板との間のフィールドプログラマブルゲートアレイ（FPGA）の接続のための電気的な経路を提供する。

40

## 【0008】

別の態様では、2つの回路基板を接続する方法が説明される。ある実施形態の方法は、

50

インターフェースコネクタを設けるステップを含む。その態様のインターフェースコネクタは、ケーシングと、ケーシング内で互いに絶縁されている複数の導電性コネクタとを含む。それぞれのコネクタは、第1の端部および第2の端部を有する。第1の端部は第1の回路基板に接続し、第2の端部は第2の回路基板に接続する。複数のコネクタは、第1の列および第2の列を形成し、第1の列は偶数番号のコネクタを含み、前記第2の列は奇数番号のコネクタを含む。インターフェースコネクタは、前記複数のコネクタが以下のように割り当てられるように構成される。コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120は、第1の回路基板と第2の回路基板との間の一般的な回路の接続のための電気的な経路を提供し、コネクタ41、42、62～67、72～75および81は、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ5～12、19～40、76、82、83、85、87～91および93は、第1の回路基板と第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する。第1の回路基板および第2の回路基板は、その構成されたインターフェースコネクタを用いて接続される。

10

## 【0009】

さらに別の態様では、システムが説明される。ある実施形態のシステムは、インターフェースコネクタ、第1の回路基板、および第2の回路基板を含む。インターフェースコネクタは、第1の回路基板を第2の回路基板に接続するために使用される。インターフェースコネクタは、ケーシングと、ケーシング内で互いに絶縁されている少なくとも120個の導電性コネクタとを含む。それぞれのコネクタは、第1の端部および第2の端部を有する。第1の端部は第1の回路基板に接続し、第2の端部は第2の回路基板に接続する。複数のコネクタは、第1の列および第2の列を形成し、第1の列は偶数番号のコネクタを含み、前記第2の列は奇数番号のコネクタを含む。複数のコネクタは、以下のように構成される。コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120は、第1の回路基板と第2の回路基板との間の一般的な回路の接続のための電気的な経路を提供し、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78は、第1の回路基板または第2の回路基板の上の電子部品のための電源の接続であり、コネクタ1～4は第1の回路基板と第2の回路基板との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供し、コネクタ41、42、62～67、72～75および81は、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ63は第1の回路基板と第2の回路基板との間のクロック信号のための電気的な経路を提供し、コネクタ5～12、19～40、76、82、83、85、87～91および93は、第1の回路基板と第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する。

20

## 【0010】

さらなる利点は、以下の説明で一部説明され、または実施することによって学習することができる。添付の特許請求の範囲で具体的に指摘される要素および組合せによって、利点を実現および達成することができるであろう。特許請求されているように、前述の全般的な説明、および以下の詳細な説明はともに、単に例示的かつ説明的なものであり、限定的なものではないことを理解されたい。

30

## 【0011】

本明細書に組み込まれ、本明細書の一部を構成する添付の図面は、実施形態を説明とともに例示し、方法およびシステムの原理を説明する役割を果たす。

40

## 【図面の簡単な説明】

## 【0012】

【図1】第1の回路基板を第2の回路基板に電気的に接続するためのインターフェースコネクタのある実施形態を示す図である。

## 【図2】第1の回路基板を第2の回路基板に電気的に接続するためのインターフェースコ

50

ネクタのある実施形態の平面図である。

【図3】第1の回路基板を第2の回路基板に電気的に接続するためのインターフェースコネクタのある実施形態の立面図である。

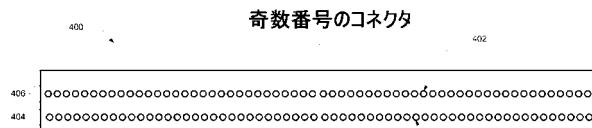

【図4】2列のコネクタを含むインターフェースコネクタのある実施形態を示す図である。

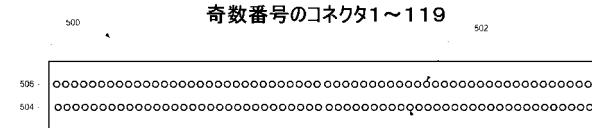

【図5】120個のコネクタを含むインターフェースコネクタのある実施形態を示す図である。

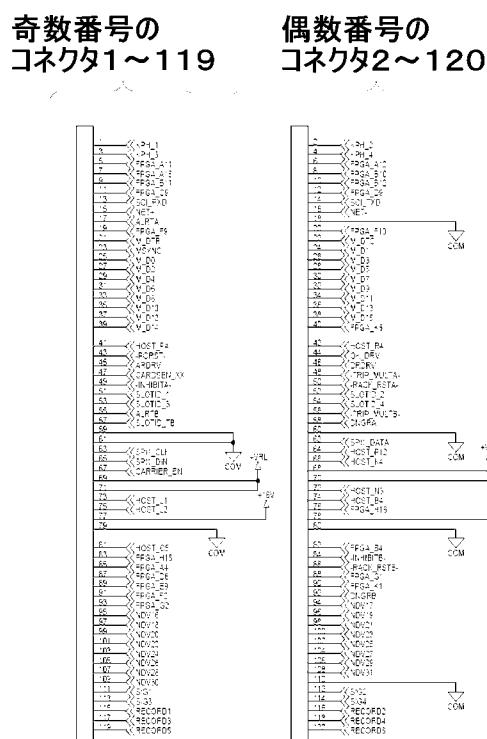

【図6】インターフェースコネクタのピン配列のある実施形態を示す図である。

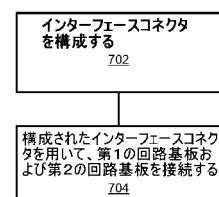

【図7】2つの回路基板を接続する方法のある実施形態を示す流れ図である。

【発明を実施するための形態】

【0013】

本方法および本システムについて開示し説明する前に、本方法および本システムは、具体的な合成方法、具体的な構成要素、または特定の構成に限定されないことを理解されたい。本明細書で使用される用語は具体的な実施形態を説明するためだけのものであり、限定することを意図していないことも理解されたい。

【0014】

本明細書および添付の特許請求の範囲で使用される場合、単数形の「a」、「a n」および「t h e」は、文脈から別段明らかではない限り複数形も指す。本明細書において、範囲は、「約」ある特定の値から、および/または「約」別の特定の値までのように表現されることがある。そのような範囲が表現される場合、別の実施形態は、そのある特定の値から、および/またはその別の特定の値までを含む。同様に、値が修飾語「約」を用いて概略的に表現される場合、その特定の値は別の実施形態を形成することが理解されるであろう。それぞれの範囲の終点は、別の終点に関連して、かつ別の終点とは独立に重要であることがさらに理解されるであろう。さらに、範囲の例が本明細書で提供される場合、別段述べられていない限り、与えられた範囲はその範囲内の全ての部分的な範囲も含むことを理解されたい。

【0015】

「任意選択の」または「任意選択で」は、その次に記述される事象または状況が起きても起きなくてもよいことを意味し、その記述は前記の事象または状況が起きる例と起きない例とを含む。

【0016】

本明細書の説明および特許請求の範囲の全体で、語「c o m p r i s e (備える、含む)」ならびに、「c o m p r i s i n g (備える、含む)」および「c o m p r i s e s (備える、含む)」などその語の変形は、「含んでいるが限定はされない」ことを意味し、例えば、別の追加要素、構成要素、整数またはステップを除外することを意図していない。「例示的な」は「のある例」を意味し、好適な実施形態または理想的な実施形態を示すことを意図していない。「など」は限定的な意味では使用されず、例示のためのものである。

【0017】

開示される方法およびシステムを実行するのに使用することができる、構成要素が開示される。これらおよび別の構成要素が本明細書で開示され、これらの構成要素の組合せ、サブセット、相互作用、グループなどが開示されるとき、様々な個々の組合せおよび集合的な組合せの各々への具体的な言及およびこれらの置換が明示的に開示されないことがあるが、全てのデバイス、方法およびシステムについて、各々が本明細書で具体的に考慮され説明される。これは、開示された方法におけるステップを含むが限定はされない、本出願の全ての態様に当てはまる。したがって、実行可能な様々な追加のステップが存在する場合、これらの追加のステップの各々が、あらゆる特定の実施形態または開示される方法の実施形態の組合せで実行されることを理解されたい。

【0018】

本方法およびシステムは、好適な実施形態の以下の詳細な説明およびそこに含まれる実

10

20

30

40

50

施例、ならびに図面および図面の前述の説明および以下の説明を参照することで、より容易に理解することができる。

【0019】

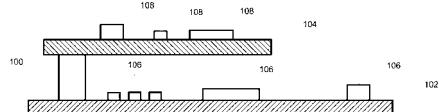

図1は、第1の回路基板102を第2の回路基板104に電気的に接続するためのインターフェースコネクタ100のある実施形態を示す。インターフェースコネクタ100は、第1の基板102上の電子部品106に関連する電子回路が、第2の基板上の電子部品108に関連する電子回路と接続するための、ブリッジを提供する。回路基板102、104は、当業者に知られているような回路基板であり、抵抗、コンデンサ、プロセッサ、フィールドプログラマブルゲートアレイ(FPGA)など電子部品106、108が導電性の経路を通じて取り付けられ相互接続される、非導電性の基部を一般に含む。一般にある態様では、インターフェースコネクタは、ケーシングと、ケーシング内で互いに絶縁されている複数の導電性コネクタを含む。ある態様では、インターフェースコネクタ100の実施形態は、ニューヨーク州スケネクタディのGeneral Electric社(GE)で製造されるような機械監視システムにおいて使用されうる。ある態様では、インターフェースコネクタの実施形態は、機械監視システムで使用される監視モジュールをグレードアップするために使用されうる。そのような機械監視システムおよびグレードアップ用監視モジュールは、2010年9月20日に出願された米国特許出願第12/885992号で説明されており、上記の出願は参照によって全体が本明細書に組み込まれ、本明細書の一部となる。ある態様では、第1の回路基板102は、Bentley-Nevada機械保護および監視システム用の補助基板である(Bentley NevadaはGeneral Electric社の商標である)。ある態様では、第2の回路基板104は、Bentley Nevadaモデル3300機械保護および監視システムをBentley Nevadaモデル3500機械保護および監視システムにグレードアップするために使用される移植可能なコアモジュール(PCM)である。ある態様では、PCMは、多くのプラットフォームに容易に移植可能でありうる、コア監視および保護機能を実行するマイクロプロセッサベースのモジュールである。ある態様では、インターフェースコネクタ100は、Bentley Nevada機械保護および監視システムのための、補助基板と移植可能なコアモジュールとの間の移植可能なコアモジュールのインターフェースコネクタとしての役割を果たす。しかし、別の使用法および応用が、本発明の実施形態の範囲内にあると考えられる。

【0020】

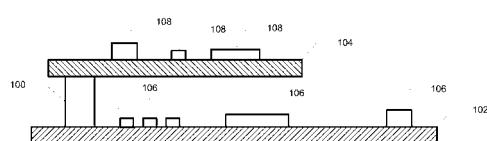

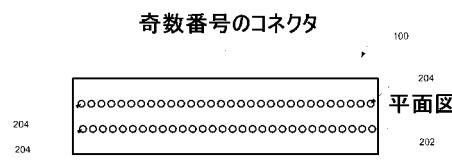

図2は、第1の回路基板102を第2の回路基板104に電気的に接続するためのインターフェースコネクタ100のある実施形態の平面図を示す。図2に示されるように、インターフェースコネクタ100のこの実施形態は、ケーシング202と、ケーシング202内で互いに絶縁されている複数の導電性コネクタ204とを含み、各コネクタ204は第1の端部および第2の端部を有する。ある態様では、コネクタ204の第1の端部は第1の回路基板102に接続し、コネクタ204の第2の端部は第2の回路基板104に接続する。図2に説明されるように、複数のコネクタ204は、第1の列および第2の列を形成する。ある態様では、第1の列は偶数番号のコネクタ204を含み、第2の列は奇数番号のコネクタを含む。例えば、偶数番号のコネクタは、2、4、6、8、10などであってよい。奇数番号のコネクタ204は、1、3、5、7、9、11などであってよい。

【0021】

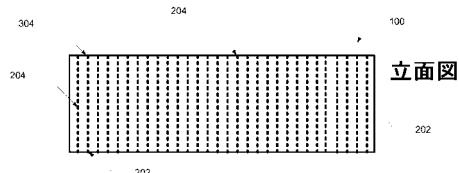

図3は、第1の回路基板102を第2の回路基板104に電気的に接続するためのインターフェースコネクタ100のある実施形態の立体図を示す。図3に示すように、コネクタ204はケーシング202を通じて延び、それぞれが導電性の経路を形成して、第1の回路基板102上の回路を第2の回路基板104の回路と接続する。上述のように、各コネクタ204は、第1の端部302および第2の端部304を有する。コネクタ204の第1の端部302および第2の端部304は、回路基板102、104とインターフェースするために必要とされるので、オス型またはメス型であってよい。ある態様では、複数のコネクタ204の各々の第1の端部302は、第1の回路基板102に接続するための

10

20

30

40

50

メス型端部を含む。別の態様では、複数のコネクタ204の各々の第1の端部302は、第1の回路基板102に接続するためのオス型端部を含む。ある態様では、複数のコネクタ204の各々の第2の端部304は、第2の回路基板104に接続するためのメス型端部を含む。別の態様では、複数のコネクタ204の各々の第2の端部304は、第2の回路基板104に接続するためのオス型端部を含む。別の種類のコネクタ端部も、本発明の実施形態の範囲内であると考えられる。

【0022】

図4は、2列のコネクタ402を含むインターフェースコネクタ400のある実施形態を示す。コネクタ402は、インターフェースコネクタ400の1つの列404の全てのコネクタ402が偶数番号となり、別の列406の全てのコネクタ402が全て奇数番号となるように、番号付けされる。

10

【0023】

図5は、120個のコネクタ502を含むインターフェースコネクタ500のある実施形態を示す。コネクタ502は、各列504、506内に60個のコネクタ502を有する2つの列504、506に分けられる。コネクタ502は、インターフェースコネクタ500の1つの列504内の全てのコネクタ502が偶数番号となり(2~120の番号を付けられる)、別の列506内の全てのコネクタ502が全て奇数の番号となる(1~119の番号を付けられる)ように、番号を付けられる。図6は、インターフェースコネクタのピン配置のある実施形態の図である。このピン配置の図は、機械保護および監視システムの補助基板を第2の回路基板に接続するためのものである。この実施形態では、第2の回路基板は、機械保護および監視システムをグレードアップするのに使用される、移植可能なコアモジュール(PCM)である。特に、図6のピン配置の図は、Bentley

Nevadaモデル3300機械保護および監視システムの補助基板を、モデル3300シリーズからモデル3500シリーズの機械保護および監視システムにグレードアップできるPCMに、接続するためのものである。図6に示されるように、少なくともコネクタ(本明細書では「ピン」とも呼ばれる)1~4、13~18、43~61、68~71、77、78、79、80、84、86、92および94~120は、第1の回路基板と第2の回路基板との間の一般的な回路接続のための電気的な経路を提供し、コネクタ41、42、62~67、72~75および81は、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供し、コネクタ5~12、19~40、76、82、83、85、87~91および93は、第1の回路基板と第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供する。より具体的には、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78は、第1の回路基板または第2の回路基板の上の電子部品のための電源の接続である。ある態様では、第1の回路基板または第2の回路基板の上の電子部品は、ホストプロセッサおよびFPGAを含む。コネクタ1~4は、第1の回路基板と第2の回路基板との間の複数のkeyphasor(General

20

Electric社の登録商標)信号のための電気的な経路を提供する。keyphasor(登録商標)信号は、機械監視および診断に使用される。この信号は、回転軸のある点から得られる、電子的パルス、またはトリガである。この信号は、回転子および機械に関係する別の測定値の、位相0の参照値としての役割を果たす。コネクタ63は、第1の回路基板と第2の回路基板との間のクロック信号のための、電気的な経路を提供する。

30

【0024】

以下の表1は、具体的に、Bentley Nevada補助基板を、一般的な回路接続、ホストプロセッサの接続、およびFPGAの接続を含むBentley Nevada PCMに接続するのに使用される、インターフェースコネクタの完全な接続情報を与える。

40

【0025】

【表1】

表I

| 回面上のノード名 | I/O | ピン番号 | 説明                                                                                       |

|----------|-----|------|------------------------------------------------------------------------------------------|

| 一般的な回路接続 |     |      |                                                                                          |

| ALRTA    | O   | 17   | 警告リレー状態および4つのリレーI/O のための<br>ドライバ。チャネル A。                                                 |

| GND      | PWR | 59   | シグナルコモン。                                                                                 |

| GND      | PWR | 61   | シグナルコモン。                                                                                 |

| GND      | PWR | 79   | シグナルコモン。                                                                                 |

| GND      | PWR | 18   | シグナルコモン。                                                                                 |

| DNGRA    | O   | 58   | 危険リレー状態および4つのリレーI/O のための<br>ドライバ。チャネル A。                                                 |

| GND      | PWR | 60   | シグナルコモン。                                                                                 |

| GND      | PWR | 80   | シグナルコモン。                                                                                 |

| DNGRB    | O   | 92   | 危険リレー状態および4つのリレーI/O のための<br>ドライバ。チャネル B。                                                 |

| GND      | PWR | 110  | シグナルコモン。                                                                                 |

| +VRL     | PWR | 69   | 未制御の正の電源。入力電圧は 6V~15V である。<br>最大の消費電力は 2.5W である。入力ピン当たりの最大電流は 0.25A である。                 |

| +VRL     | PWR | 71   | 未制御の正の電源。入力電圧は 6V~15V である。<br>最大の消費電力は 2.5W である。入力ピン当たりの最大電流は 0.25A である。                 |

| +VRL     | PWR | 68   | 未制御の正の電源。入力電圧は 6V~15V である。<br>最大の消費電力は 2.5W である。入力ピン当たりの最大電流は 0.25A である。                 |

| +VRL     | PWR | 70   | 未制御の正の電源。入力電圧は 6V~15V である。<br>最大の消費電力は 2.5W である。入力ピン当たりの最大電流は 0.25A である。                 |

| +16V     | PWR | 77   | 制御された正の電源。入力電圧の範囲は 15.50V<br>~17.50V である。最大の消費電力は 1.65W である。<br>入力ピン当たりの最大電流は 0.25A である。 |

| +16V     | PWR | 78   | 制御された正の電源。入力電圧の範囲は 15.50V<br>~17.50V である。最大の消費電力は 1.65W である。<br>入力ピン当たりの最大電流は 0.25A である。 |

| ALRTB    | O   | 55   | 警告リレー状態および4つのリレーI/O のための<br>ドライバ。チャネル B。                                                 |

| SIG1     | I   | 111  | 専用チャネル 1 のアナログ信号入力(+1~-24V)                                                              |

| SIG2     | I   | 112  | 専用チャネル 2 のアナログ信号入力(+1~-24V)                                                              |

| SIG3     | I   | 113  | 専用チャネル 3 のアナログ信号入力(+1~-24V)                                                              |

| SIG4     | I   | 114  | 専用チャネル 4 のアナログ信号入力(+1~-24V)                                                              |

| -PORST-  | O   | 43   | 専用のパワーオンリセットストローブ信号。Low<br>でリセット。High では通常動作。                                            |

| SCI_RXD  | I   | 13   | システム監視装置からの専用の SCI 受信信号。                                                                 |

| SCI_TXD  | O   | 14   | システム監視装置への専用の SCI 送信信号。                                                                  |

| NET+     | O   | 15   | システム監視装置への専用のニューロン通信線。                                                                   |

| NET-     | O   | 16   | システム監視装置への専用のニューロン通信線。                                                                   |

| OK_DRV   | O   | 44   | 専用の OK リレードライプ。オープンドライン。                                                                 |

| ARDRV    | O   | 45   | 専用の警告(第1の警告)リレードライプ信号。0=<br>警告なし。1=警告                                                    |

| DRDRV    | O   | 46   | 専用の危険(第2の警告)リレードライプ信号。0=                                                                 |

10

20

30

40

| 図面上のノード名      | I/O | ピン番号 | 説明                                                                                       |

|---------------|-----|------|------------------------------------------------------------------------------------------|

|               |     |      | 警告なし。1=警告                                                                                |

| CARDSEN_XX    | I   | 47   | 専用のカード感知線入力。システム監視装置はこの線を high に駆動する。High の場合、システム監視装置は SCI 応答を予測する。10k の抵抗がこの線をプルダウンする。 |

| SLOTID_1      | I   | 51   | スロット位置識別コードの 4 ビットのうちのビット 1。このピンの状態は外部回路によって定義される。このカードは、3.3V の電源線を提供することで外部回路を駆動する。     |

| SLOTID_2      | I   | 52   | スロット位置識別コードの 4 ビットのうちのビット 2。このピンの状態は外部回路によって定義される。このカードは、3.3V の電源線を提供することで外部回路を駆動する。     |

| SLOTID_3      | I   | 53   | スロット位置識別コードの 4 ビットのうちのビット 3。このピンの状態は外部回路によって定義される。このカードは、3.3V の電源線を提供することで外部回路を駆動する。     |

| SLOTID_4      | I   | 54   | スロット位置識別コードの 4 ビットのうちのビット 4。このピンの状態は外部回路によって定義される。このカードは、3.3V の電源線を提供することで外部回路を駆動する。     |

| SLOTID_TB     | I   | 57   | このビットはスロットの位置が上か下かを識別する。このピンの状態は外部回路によって定義される。このカードは、3.3V の電源線を提供することで外部回路を駆動する。         |

| KPH_1         | I   | 1    | 専用の調整された Keyphasor1 の入力。この線は FPGA に入る。                                                   |

| KPH_2         | I   | 2    | 専用の調整された Keyphasor2 の入力。この線は FPGA に入る。                                                   |

| KPH_3         | I   | 3    | 専用の調整された Keyphasor3 の入力。この線は FPGA に入る。                                                   |

| KPH_4         | I   | 4    | 専用の調整された Keyphasor4 の入力。この線は FPGA に入る。                                                   |

| -TRIP_MUL_TA- | I   | 48   | システム監視装置からの専用のトリップ乗算入力。この線は FPGA に入る。                                                    |

| -TRIP_MUL_TB- | I   | 56   | システム監視装置からの専用のトリップ乗算入力。この線は FPGA に入る。                                                    |

| -INHIBITA-    | I   | 49   | システム監視装置からの専用の抑止入力。この線は FPGA に入る。                                                        |

| -INHIBITB-    | I   | 84   | システム監視装置からの専用の抑止入力。この線は FPGA に入る。                                                        |

| -RACK_RST_A-  | I   | 50   | システム監視装置からの専用のラックリセット入力。この線は FPGA に入る。                                                   |

| -RACK_RST_B-  | I   | 86   | システム監視装置からの専用のラックリセット入力。この線は FPGA に入る。                                                   |

| NDV16         | I   | 95   | 外部ノード電圧の入力。入力電圧は、入力抵抗が $2.5k\Omega$ よりも小さい場合に直流電圧が $0\sim2.50V$                          |

10

20

30

| 図面上のノード名 | I/O | ピン番号 | 説明                                                           |

|----------|-----|------|--------------------------------------------------------------|

|          |     |      | の間でなければならない。                                                 |

| NDV17    | I   | 94   | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV18    | I   | 97   | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV19    | I   | 96   | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV20    | I   | 99   | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV21    | I   | 98   | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV22    | I   | 101  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV23    | I   | 100  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV24    | I   | 103  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV25    | I   | 102  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV26    | I   | 105  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV27    | I   | 104  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV28    | I   | 107  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV29    | I   | 106  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV30    | I   | 109  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| NDV31    | I   | 108  | 外部ノード電圧の入力。入力電圧は、入力抵抗が2.5kΩよりも小さい場合に直流電圧が0~2.50Vの間でなければならない。 |

| RECORD1  | O   | 115  | チャネル1、4~20mAのレコーダ出力。0~600Ωの負荷。                               |

| RECORD2  | O   | 116  | チャネル2、4~20mAのレコーダ出力。0~600Ωの負荷。                               |

10

20

30

| 図面上のノード名    | I/O | ピン番号 | 説明                                                                                      |

|-------------|-----|------|-----------------------------------------------------------------------------------------|

| RECORD3     | O   | 117  | チャネル3、4～20mAのレコーダ出力。0～600Ωの負荷。                                                          |

| RECORD4     | O   | 118  | チャネル4、4～20mAのレコーダ出力。0～600Ωの負荷。                                                          |

| RECORD5     | O   | 119  | チャネル5、4～20mAのレコーダ出力。0～600Ωの負荷。                                                          |

| RECORD6     | O   | 120  | チャネル6、4～20mAのレコーダ出力。0～600Ωの負荷。                                                          |

| ホストプロセッサの接続 |     |      |                                                                                         |

| HOST_P4     | I/O | 41   | SPI1_CS0, UART2_TXD, GP5_13.                                                            |

| HOST_R4     | I/O | 42   | SPI1_ENA, UART2_RXD, GP5_12.                                                            |

| SPI1_CLK    | O   | 63   | 44 SPI1 CLK。マスタークロック信号。内部で使用されるが、指定されたチップセレクト線とともに外部で使用されうる。49.9kΩの抵抗がこのピンとコモンの間に接続される。 |

| SPI1_DAT_A  | O   | 62   | SPI1 DATA。マスターデータ出力信号。内部で使用されるが、指定されたチップセレクト線とともに外部で使用されうる。                             |

| SPI1_DIN    | I   | 65   | SPI1 DATA。スレーブデータ入力信号。内部で使用されるが、指定されたチップセレクト線とともに外部で使用されうる。                             |

| CARRIER_EN  | O   | 67   | 専用の外部のSPIチップセレクト線。キャリア基板の識別子FLASHを選択するのに使用される。                                          |

| HOST_K4     | I/O | 66   | GP4_10.                                                                                 |

| HOST_L1     | I/O | 73   | GP4_11.                                                                                 |

| HOST_P12    | I/O | 64   | GP2_8.                                                                                  |

| HOST_N3     | I/O | 72   | GP5_10                                                                                  |

| HOST_C5     | I/O | 81   | ECAP0, GP2_12                                                                           |

| HOST_B4     | I/O | 74   | ECAP1, GP2_15                                                                           |

| HOST_L2     | I/O | 75   | ECAP2, GP4_12                                                                           |

| FPGAの接続     |     |      |                                                                                         |

| M_D0        | I/O | 25   | 管理データバスのビット0。管理データバスはFPGAの1つの機能である。                                                     |

| M_D1        | I/O | 24   | 管理データバスのビット1。管理データバスはFPGAの1つの機能である。                                                     |

| M_D2        | I/O | 27   | 管理データバスのビット2。管理データバスはFPGAの1つの機能である。                                                     |

| M_D3        | I/O | 26   | 管理データバスのビット3。管理データバスはFPGAの1つの機能である。                                                     |

| M_D4        | I/O | 29   | 管理データバスのビット4。管理データバスはFPGAの1つの機能である。                                                     |

| M_D5        | I/O | 28   | 管理データバスのビット5。管理データバスはFPGAの1つの機能である。                                                     |

| M_D6        | I/O | 31   | 管理データバスのビット6。管理データバスはFPGAの1つの機能である。                                                     |

| M_D7        | I/O | 30   | 管理データバスのビット7。管理データバスはFPGAの1つの機能である。                                                     |

| M_D8        | I/O | 33   | 管理データバスのビット8。管理データバスはFPGAの1つの機能である。                                                     |

| M_D9        | I/O | 32   | 管理データバスのビット9。管理データバスは                                                                   |

10

20

30

| 図面上のノード名 | I/O | ピン番号 | 説明                                              |

|----------|-----|------|-------------------------------------------------|

|          |     |      | FPGA の 1 つの機能である。                               |

| M_D10    | I/O | 35   | 管理データバスのビット 10。管理データバスは FPGA の 1 つの機能である。       |

| M_D11    | I/O | 34   | 管理データバスのビット 11。管理データバスは FPGA の 1 つの機能である。       |

| M_D12    | I/O | 37   | 管理データバスのビット 12。管理データバスは FPGA の 1 つの機能である。       |

| M_D13    | I/O | 36   | 管理データバスのビット 13。管理データバスは FPGA の 1 つの機能である。       |

| M_D14    | I/O | 39   | 管理データバスのビット 14。管理データバスは FPGA の 1 つの機能である。       |

| M_D15    | I/O | 38   | 管理データバスのビット 15。管理データバスは FPGA の 1 つの機能である。       |

| M_DTR    | I   | 21   | システム監視装置からの管理データ送受信信号。システム監視装置とのハンドシェイクに使用される。  |

| M_DTC    | O   | 22   | システム監視装置からの管理データ送信制御信号。システム監視装置とのハンドシェイクに使用される。 |

| MSYNC    | I   | 23   | システム監視装置からの管理同期線。                               |

| FPGA_A11 | I/O | 5    | FPGA への入力または出力。                                 |

| FPGA_A12 | I/O | 6    | FPGA への入力または出力。                                 |

| FPGA_A15 | I/O | 7    | FPGA への入力または出力。                                 |

| FPGA_B10 | I/O | 8    | FPGA への入力または出力。                                 |

| FPGA_B11 | I/O | 9    | FPGA への入力または出力。                                 |

| FPGA_B12 | I/O | 10   | FPGA への入力または出力。                                 |

| FPGA_C9  | I/O | 11   | FPGA への入力または出力。                                 |

| FPGA_D9  | I/O | 12   | FPGA への入力または出力。                                 |

| FPGA_F9  | I/O | 19   | FPGA への入力または出力。                                 |

| FPGA_F10 | I/O | 20   | FPGA への入力または出力。                                 |

| FPGA_A4  | I/O | 85   | FPGA への入力または出力。                                 |

| FPGA_B4  | I/O | 82   | FPGA への入力または出力。                                 |

| FPGA_D6  | I/O | 87   | FPGA への入力または出力。                                 |

| FPGA_H15 | I/O | 83   | FPGA への入力または出力。                                 |

| FPGA_H16 | I/O | 76   | FPGA への入力または出力。                                 |

| FPGA_E9  | I/O | 89   | FPGA への入力または出力。                                 |

| FPGA_F2  | I/O | 91   | FPGA への入力または出力。                                 |

| FPGA_G2  | I/O | 93   | FPGA への入力または出力。                                 |

| FPGA_G1  | I/O | 88   | FPGA への入力または出力。                                 |

| FPGA_K1  | I/O | 90   | FPGA への入力または出力。                                 |

| FPGA_K6  | I/O | 40   | FPGA への入力または出力。                                 |

10

20

30

40

50

ここで、E M I F A (拡張メモリインターフェース) は標準的なメモリおよび周辺インターフェースであり、E M I F B はS D R A M に専用のインターフェースであり、S C I は非同期式のシリアルインターフェースであり、S P I は同期式の周辺シリアルインターフェースであり、G P またはG P I O はホストプロセッサの標準的な入出力ロジックインターフェースを表し、E C A P は改良されたキャプチャポートを表し、汎用割り込みピンまたはパルス幅変調出力として使用されうる。T R I P \_ M U L T A およびT R I P \_ M U L T B (それぞれピン4 8 および5 6 ) は、保護システムのラックの中の各監視装置によって受信される、インジケータ信号である。保護システムは、システムラックの背面のトリップ乗算 (T r i p M u l t i p l y ) 接点入力を閉じることによって構成されうる。トリップ乗算接点が閉じると、警告トリップレベルを所定の大きさに上げるように各監視装置に通知する。例えば、監視装置が3 ミルの振動で警告するように構成されている場合、トリップ乗算は2 倍するように構成され、したがってT R I P \_ M U L T 入力が存在する場合 (すなわち閉じている場合) 、警告の設定は3 ミルから6 ミルに変化する。トリップ乗算は通常、機械に通常の振動よりも大きな振動が発生しうる、機械の始動時または

機械の停止時に使用することができる。これにより、振動の大きいそうした期間において、誤警告が防止される。2対のチャネル警告AおよびBが通常存在する。M\_D0からM\_D15(ピン24から39)は、管理データバス信号である。保護監視システムの各監視装置は、入来トランスデューサ信号をデジタル化する。デジタル化されたトランスデューサ信号は編成され、パケットに保存されて、システム監視装置に送られる。システム監視装置は各監視装置からの全てのパケットを編成し、サーバまたはパーソナルコンピュータ上に存在するソフトウェアにパケットを送る。このデータは、監視される資源を管理するのに役立つ、表示およびグラフを提供するのに使用される。このデータは、警告が必要になる突然の障害に対する保護ではなく、資源の管理に使用されるため、このデータは管理データと呼ばれ、各個別の監視装置からシステム監視装置にデータを移すのに使用されるバスは管理バスと呼ばれる。M\_D0からM\_D15は、管理データを移すのに使用される16ビット幅のバスであり、M\_D0が管理バスのビット0であり、M\_D15が管理バスの最終ビットすなわちビット15である。M\_DTC、M\_DTRおよびMSYNCは、管理データバスに関連して用いられデータを適切に同期および移動する、ハンドシェイキングまたは制御線である。

【0026】

図7は、2つの回路基板を接続する方法のある実施形態を示すフローチャートである。ステップ702において、インターフェースコネクタは以下のように構成される。コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120は、第1の回路基板と第2の回路基板との間の一般的な回路接続のための電気的な経路を提供するように割り当てられ、コネクタ41、42、62～67、72～75、および81は、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供するように割り当てられ、コネクタ5～12、19～40、76、82、83、85、87～91、および93は、第1の回路基板と第2の回路基板との間のフィールドプログラマブルゲートアレイ(FPGA)の接続のための電気的な経路を提供するように割り当てられる。インターフェースコネクタは、ケーシングと、ケーシング内で互いに絶縁されている複数の導電性コネクタとを含み、各コネクタは第1の端部および第2の端部を有する。第1の端部は第1の回路基板に接続し、第2の端部は第2の回路基板に接続する。複数のコネクタは第1の列および第2の列を形成し、第1の列は偶数番号のコネクタを含み、前記第2の列は奇数番号のコネクタで形成される。ある態様では、複数の導電性コネクタは、少なくとも120個のコネクタを含む。ある態様では、コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、第1の回路基板と第2の回路基板との間の一般的な回路接続のための電気的な経路を提供するように、インターフェースコネクタを構成するステップは、コネクタ59、61、79、18、60、80、110、69、71、68、70、77および78を、第1の回路基板または第2の回路基板の上の電子部品のための電源の接続として構成するステップを含む。ある態様では、第1の回路基板または第2の回路基板の上の電子部品は、ホストプロセッサおよびFPGAを含む。ある態様では、コネクタ1～4、13～18、43～61、68～71、77、78、79、80、84、86、92および94～120が、第1の回路基板と第2の回路基板との間の一般的な回路接続のための電気的な経路を提供するように、インターフェースコネクタを構成するステップは、第1の回路基板と第2の回路基板との間の複数のkeyphasor(登録商標)信号のための電気的な経路を提供するように、コネクタ1～4を構成するステップを含む。ある態様では、コネクタ41、42、62～67、72～75、および81が、第1の回路基板と第2の回路基板との間のホストプロセッサの接続のための電気的な経路を提供するように、インターフェースコネクタを構成するステップは、第1の回路基板と第2の回路基板との間でクロック信号のための電気的な経路を提供するようにコネクタ63を構成することを含む。ステップ704において、構成されたインターフェースコネクタは、第1の回路基板および第2の回路基板を接続するのに使用される。

【0027】

10

20

30

40

50

上述のように、かつ当業者には理解されるように、本発明の実施形態は、デバイス、システム、または方法として構成されうる。別段明示的に述べられない限り、本明細書で述べられたあらゆる方法は、そのステップがある特定の順序で実行されなければならないと解釈されることは決して意図されていない。したがって、方法の請求項が、方法のステップが従うべき順序を実際に記載しない場合、または、請求項または説明においてステップが特定の順序に限定されるべきであると別段具体的に述べられていない場合、あらゆる面において、ある順序が暗示されることは決して意図されていない。これは、ステップまたは動作の流れの構成に関する論理的な事項、文法的な構造または句読点から導かれる単純な意味、本明細書で説明される実施形態の数または種類を含む、解釈に関して可能性のあるあらゆる非明示的な原則に対して当てはまる。

10

## 【0028】

本出願全体を通じて、様々な刊行物が参照されることがある。これらの刊行物の開示の全体が、デバイス、方法およびシステムに関係する最新技術をより完全に説明するために、本明細書で参照によって本出願に組み込まれる。

## 【0029】

前述の説明および関連する図面に示される教示の利益を有し本発明のこれらの実施形態に関係する当業者には、本明細書で述べられた本発明の多くの修正および別の実施形態が想起されるであろう。したがって、本発明の実施形態は開示された特定の実施形態に限定されるべきではなく、修正および別の実施形態が添付の特許請求の範囲に含まれることが意図されることを、理解されたい。さらに、前述の説明および関連する図面は、要素および/または機能のある例示的な組合せに関する例示的な実施形態を説明するが、要素および/または機能の異なる組合せが、添付の特許請求の範囲から逸脱することなく、代替的な実施形態によって提供されうることを、理解されたい。この点において、例えば、上で明示的に説明された要素および/または機能の組合せとは異なる組合せも、添付の特許請求の範囲の一部で述べられることがある。特定の用語が本明細書で使用されたが、それらの用語は、限定するためではなく包括的かつ説明的な意味でのみ用いられる。

20

## 【符号の説明】

## 【0030】

- 100 インターフェースコネクタ

- 102 第1の回路基板

- 104 第2の回路基板

- 106 第1の回路基板 102 上の電子部品

- 108 第2の回路基板上の電子部品 108

- 202 ケーシング

- 204 複数の導電性コネクタ

- 302 (導電性コネクタ 204 の) 第1の端部

- 304 (導電性コネクタ 204 の) 第2の端部

- 400 インターフェースコネクタ

- 402 コネクタ

- 404 インターフェースコネクタの1つの列(偶数番号)

- 406 インターフェースコネクタの別の列(奇数番号)

- 500 インターフェースコネクタ

- 502 コネクタ

- 504 インターフェースコネクタ 500 の1つの列 504 内のコネクタ 502 は偶数番号である(2~120の番号を付けられる)

- 506 別の列 506 のコネクタ 502 は全て奇数番号である(1~119の番号を付けられる)

30

40

【図 1】

FIG. 1

【図 2】

偶数番号のコネクタ

FIG. 2

【図 3】

FIG. 3

【図 4】

FIG. 4 偶数番号のコネクタ

【図 5】

FIG. 5 偶数番号のコネクタ

2~120

【図 6】

FIG. 6

【図 7】

FIG. 7

---

フロントページの続き

(72)発明者 ミッケル・ディーン・コーヘン

アメリカ合衆国、ネバダ州・89423、ミンデン、ベントリー・パークウェイ・サウス、163

1番

F ターム(参考) 5H220 AA10 BB07 CC01 CX05 EE03 JJ04

【外國語明細書】

2012164313000001.pdf