## (12) 发明专利申请

(10) 申请公布号 CN 116895694 A

(43) 申请公布日 2023.10.17

(21) 申请号 202310310606.4

(22) 申请日 2023.03.27

### (30) 优先权数据

2022-053039 2022.03.29 JP

(71) 申请人 精工爱普生株式会社

地址 日本东京都

(72) 发明人 岛田浩行

(74) 专利代理机构 北京三友知识产权代理有限公司 11127

专利代理人 刘畅 欧阳柳青

### (51) Int.Cl.

H01L 29/78 (2006.01)

H01L 29/423 (2006.01)

H01L 29/06 (2006.01)

权利要求书2页 说明书9页 附图5页

### (54) 发明名称

半导体装置以及功率器件

### (57) 摘要

半导体装置以及功率器件，能够降低导通电阻。半导体装置具有：导电型彼此相同的第一半导体部以及第二半导体部，它们沿着第一方向配置；第三半导体部，其设置于第一半导体部与第二半导体部之间，杂质浓度比第一半导体部以及第二半导体部低；第四半导体部，其设置于第二半导体部与第三半导体部之间，杂质浓度比第一半导体部以及第二半导体部低；栅极绝缘层以及栅极电极，它们设置于第三半导体部的与第一方向交叉的第二方向；以及电介质部，其设置于第四半导体部的第二方向，电介质部由带隙比构成第四半导体部的材料大且相对介电常数比构成第四半导体部的材料大的材料构成，在对栅极电极施加了规定的电压的情况下，在第四半导体部形成耗尽层。

1.一种半导体装置,其具有:

导电型彼此相同的第一半导体部和第二半导体部,它们沿着第一方向配置;

第三半导体部,其设置于所述第一半导体部与所述第二半导体部之间,杂质浓度比所述第一半导体部和所述第二半导体部低;

第四半导体部,其设置于所述第二半导体部与所述第三半导体部之间,杂质浓度比所述第一半导体部和所述第二半导体部低;

栅极绝缘层和栅极电极,它们设置于所述第三半导体部的与所述第一方向交叉的第二方向;以及

电介质部,其设置于所述第四半导体部的所述第二方向,

所述电介质部由带隙比构成所述第四半导体部的材料大且相对介电常数比构成所述第四半导体部的材料大的材料构成,

在对所述栅极电极施加了规定的电压的情况下,在所述第四半导体部形成耗尽层。

2.根据权利要求1所述的半导体装置,其中,

所述第一半导体部、所述第三半导体部以及所述第四半导体部在所述第一方向上层叠而构成柱状部。

3.根据权利要求2所述的半导体装置,其中,

从所述第一方向观察,所述栅极绝缘层包围所述第三半导体部,

所述栅极电极包围所述栅极绝缘层。

4.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述第一半导体部构成源极区域,所述第二半导体部构成漏极区域。

5.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述电介质部的材质是过渡金属氧化物。

6.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述电介质部的材质是氧化铪。

7.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述栅极绝缘层由带隙比构成所述第三半导体部的材料大且相对介电常数比构成所述第三半导体部的材料大的材料构成。

8.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述栅极绝缘层的材质是过渡金属氧化物。

9.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述栅极绝缘层的材质是氧化铪。

10.根据权利要求1-3中的任意一项所述的半导体装置,其中,

所述半导体装置具有设置于所述第二半导体部的所述第一方向的电极,

所述第二半导体部还设置于所述电介质部的所述第一方向。

11.一种功率器件,其具有:

导电型彼此相同的第一半导体部和第二半导体部,它们沿着第一方向配置;

第三半导体部,其设置于所述第一半导体部与所述第二半导体部之间,杂质浓度比所述第一半导体部和所述第二半导体部低;

第四半导体部,其设置于所述第二半导体部与所述第三半导体部之间,杂质浓度比所

述第一半导体部和所述第二半导体部低；

栅极绝缘层和栅极电极，它们设置于所述第三半导体部的与所述第一方向交叉的第二方向；以及

电介质部，其设置于所述第四半导体部的所述第二方向，

所述电介质部由带隙比构成所述第四半导体部的材料大且相对介电常数比构成所述第四半导体部的材料大的材料构成，

在对所述栅极电极施加了规定的电压的情况下，在所述第四半导体部形成耗尽层。

## 半导体装置以及功率器件

### 技术领域

[0001] 本发明涉及半导体装置以及功率器件。

### 背景技术

[0002] 半导体纳米柱作为下一代纳米器件的结构,面向应用于晶体管、光源等各种半导体装置而受到关注。例如,通过采用由栅极电极在整个周向上包围半导体纳米柱的GAA (Gate All Around) 结构,能够由栅极电极包围半导体纳米柱的沟道形成区域,完全耗尽化,提高电流控制性。根据GAA结构,能够同时实现相对于时间急剧地导通/截止的切换特性和每单位面积的高密度化。

[0003] 例如在专利文献1中记载了一种晶体管器件,其具备纳米线、包围纳米线的栅极电介质、以及包围栅极电介质的栅极导电体。

[0004] 专利文献1:日本特表2014-503998号公报

### 发明内容

[0005] 在上述那样的晶体管器件中,期望降低导通电阻。

[0006] 本发明的半导体装置的一个方式具有:导电型彼此相同的第一半导体部以及第二半导体部,它们沿着第一方向配置;第三半导体部,其设置于所述第一半导体部与所述第二半导体部之间,杂质浓度比所述第一半导体部以及所述第二半导体部低;第四半导体部,其设置于所述第二半导体部与所述第三半导体部之间,杂质浓度比所述第一半导体部以及所述第二半导体部低;栅极绝缘层以及栅极电极,它们设置于所述第三半导体部的与所述第一方向交叉的第二方向;以及电介质部,其设置于所述第四半导体部的所述第二方向,所述电介质部由带隙比构成所述第四半导体部的材料大且相对介电常数比构成所述第四半导体部的材料大的材料构成,在对所述栅极电极施加了规定的电压的情况下,在所述第四半导体部形成耗尽层。

[0007] 本发明的功率器件的一个方式具有:导电型彼此相同的第一半导体部以及第二半导体部,它们沿着第一方向配置;第三半导体部,其设置于所述第一半导体部与所述第二半导体部之间,杂质浓度比所述第一半导体部以及所述第二半导体部低;第四半导体部,其设置于所述第二半导体部与所述第三半导体部之间,杂质浓度比所述第一半导体部以及所述第二半导体部低;栅极绝缘层以及栅极电极,它们设置于所述第三半导体部的与所述第一方向交叉的第二方向;以及电介质部,其设置于所述第四半导体部的所述第二方向,所述电介质部由带隙比构成所述第四半导体部的材料大且相对介电常数比构成所述第四半导体部的材料大的材料构成,在对所述栅极电极施加了规定的电压的情况下,在所述第四半导体部形成耗尽层。

### 附图说明

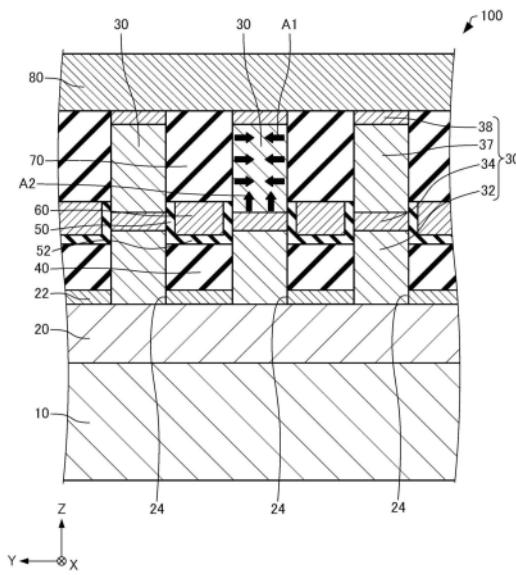

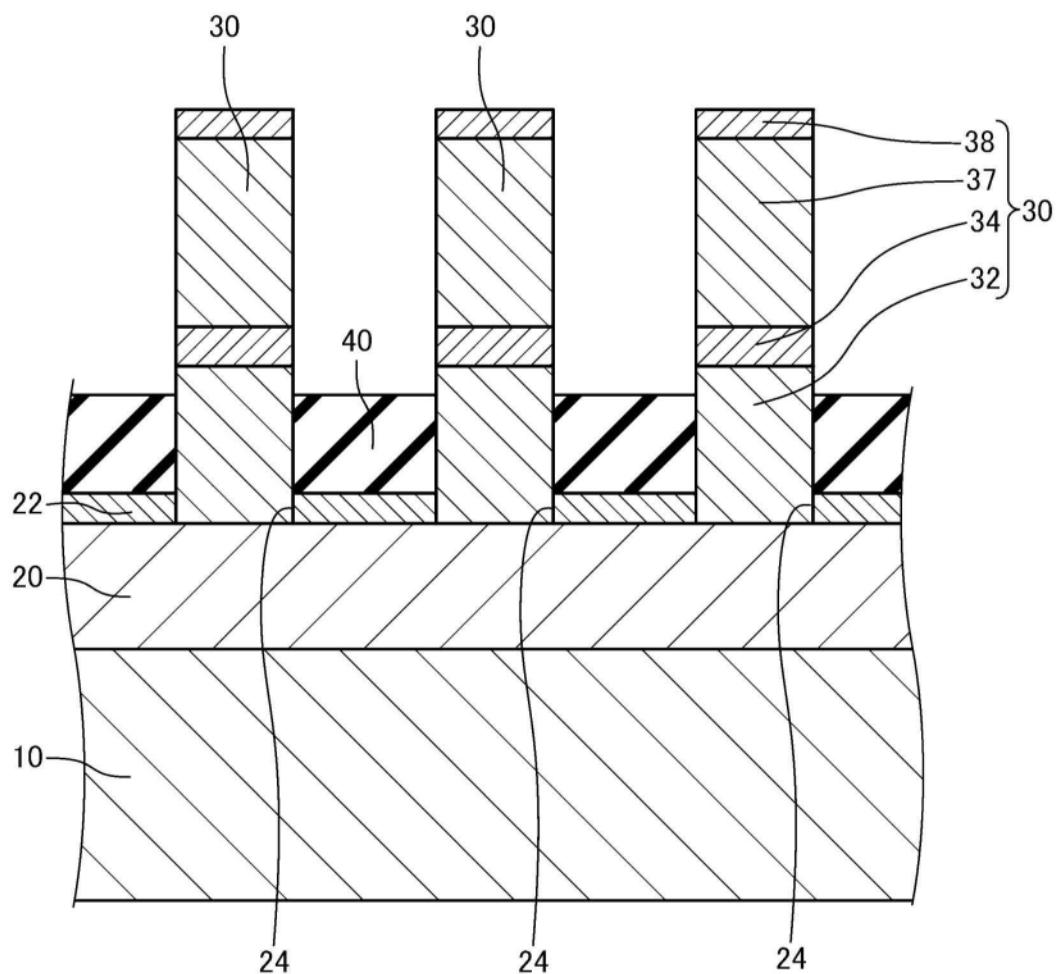

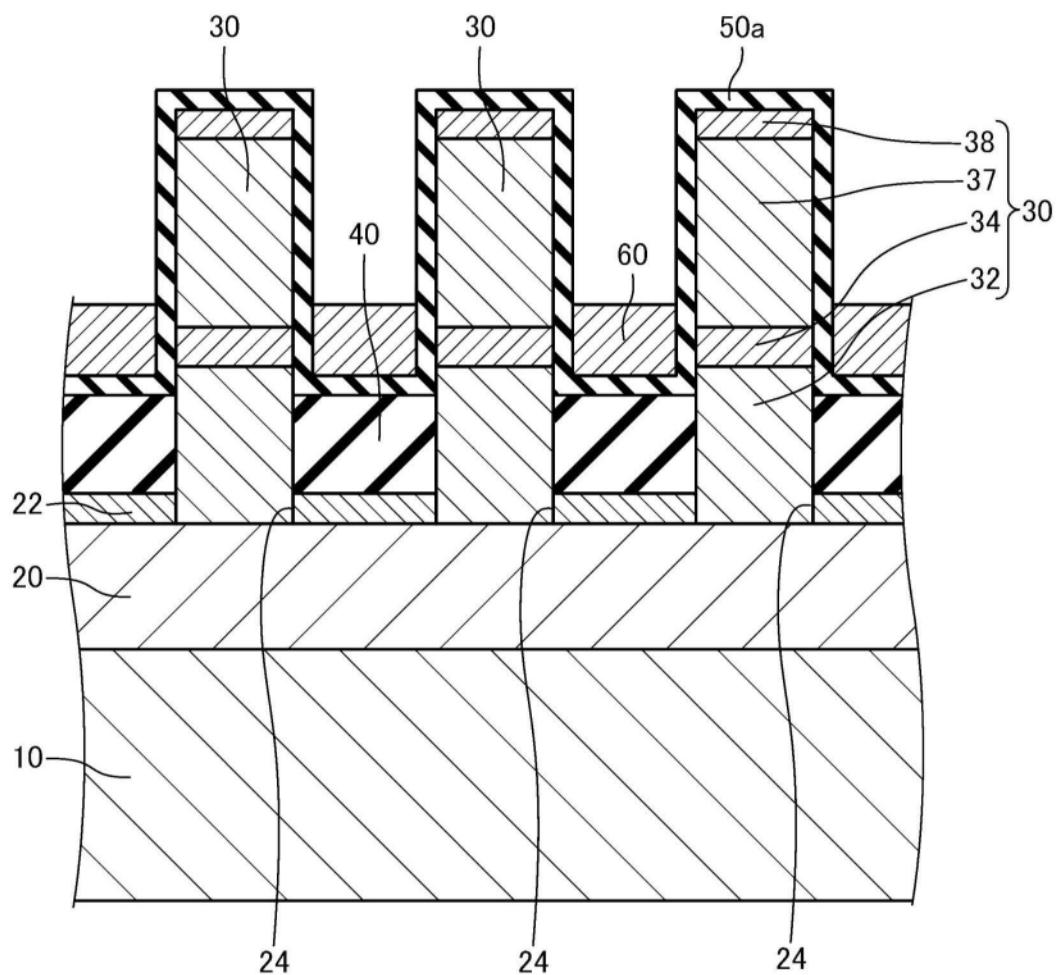

[0008] 图1是示意性地示出本实施方式的半导体装置的剖视图。

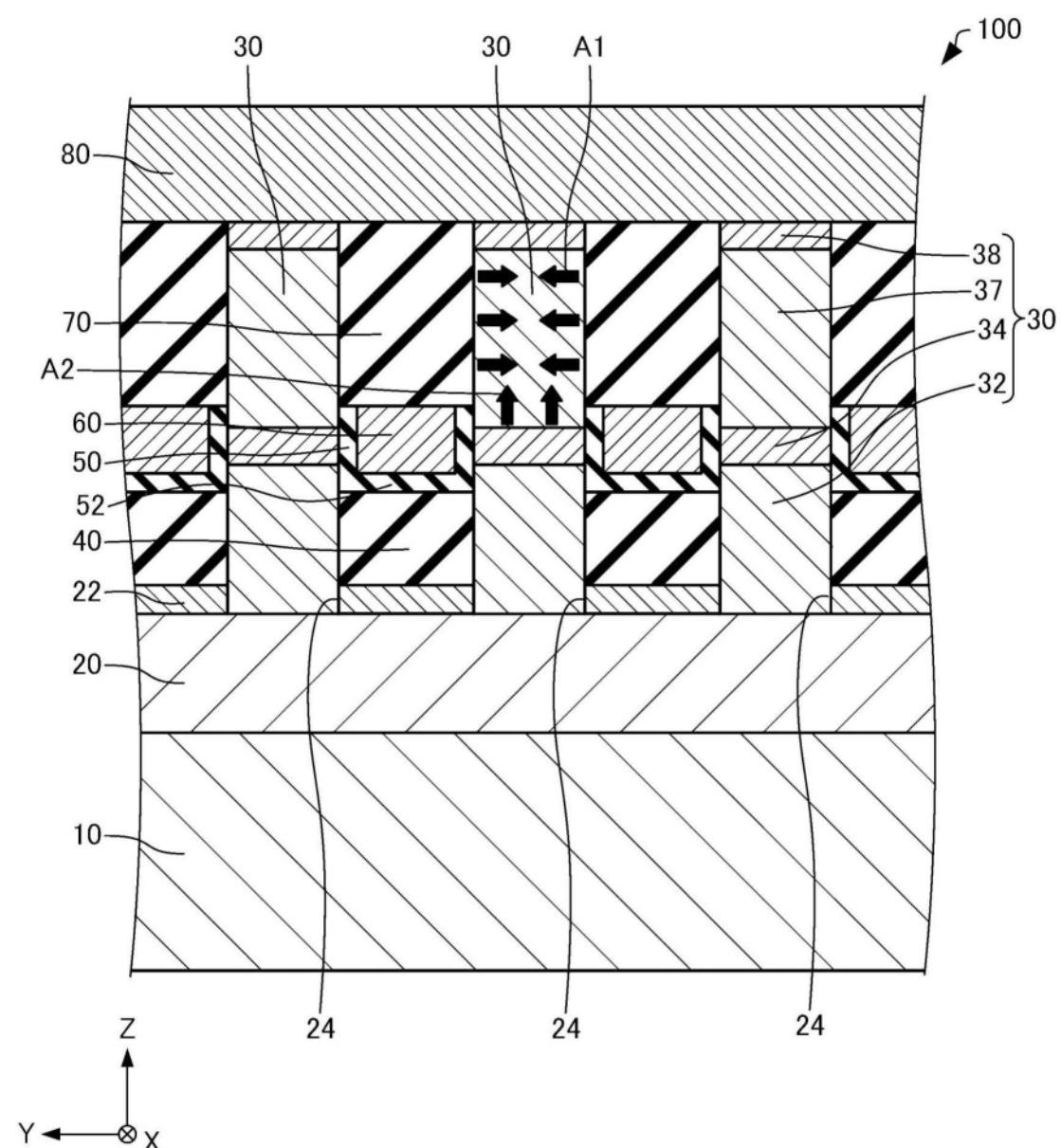

- [0009] 图2是示意性地示出本实施方式的半导体装置的俯视图。

- [0010] 图3是示意性地示出本实施方式的半导体装置的制造工序的剖视图。

- [0011] 图4是示意性地示出本实施方式的半导体装置的制造工序的剖视图。

- [0012] 图5是示意性地示出本实施方式的半导体装置的制造工序的剖视图。

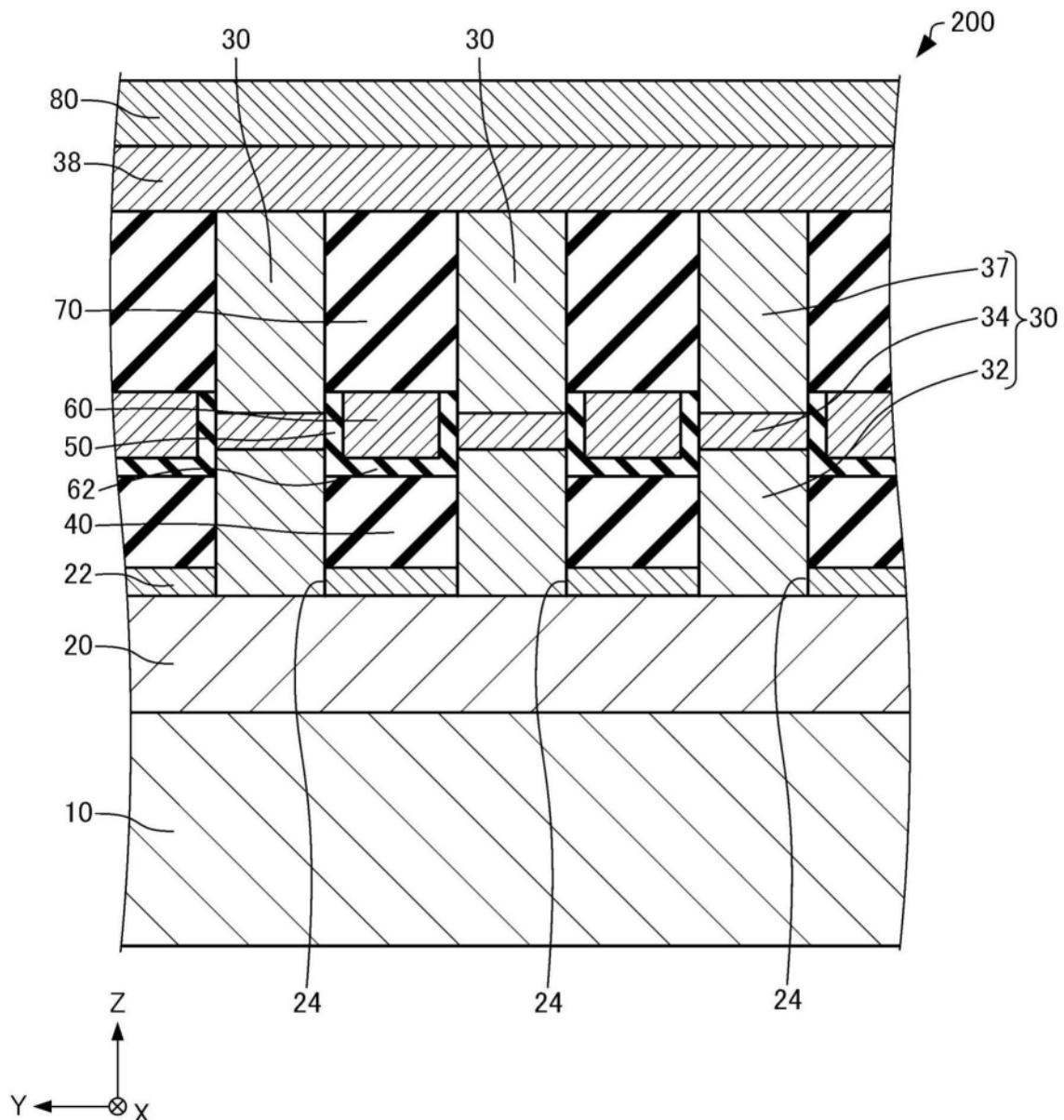

- [0013] 图6是示意性地示出本实施方式的第一变形例的半导体装置的剖视图。

- [0014] 标号说明

- [0015] 10:基板;20:缓冲层;22:掩模层;24:开口部;30:柱状部;32:源极区域;34:沟道形成区域;37:漂移区域;38:漏极区域;40:绝缘层;50:栅极绝缘层;50a、52:绝缘层;60:栅极电极;70:电介质层;80:漏极电极;100、200:半导体装置。

## 具体实施方式

[0016] 下面,使用附图对本发明的优选实施方式进行详细说明。另外,以下说明的实施方式并不对权利要求书中记载的本发明的内容进行不恰当的限定。并且,以下说明的结构不一定全部都是本发明必需结构要件。

### [0017] 1. 半导体装置

[0018] 首先,参照附图对本实施方式的半导体装置进行说明。图1是示意性地示出本实施方式的半导体装置100的剖视图。图2是示意性地示出本实施方式的半导体装置100的俯视图。另外,图1是沿图2的I-I线的剖视图。另外,在图1以及图2中,作为相互垂直的3个轴,图示了X轴、Y轴以及Z轴。

[0019] 如图1以及图2所示,半导体装置100具有基板10、缓冲层20、掩模层22、柱状部30、绝缘层40、栅极绝缘层50、栅极电极60、电介质层70以及漏极电极80。半导体装置100例如是功率器件。半导体装置100例如是纵型的金属氧化膜半导体场效应晶体管(MOSFET)。另外,为了方便,在图2中省略了漏极电极80的图示。

[0020] 基板10例如是Si基板、GaN基板、蓝宝石基板、SiC基板等。

[0021] 如图1所示,缓冲层20设置在基板10上。缓冲层20例如是掺杂有Si的n型的GaN层或AlGaN层。缓冲层20例如作为源极发挥功能。缓冲层20例如与未图示的源极焊盘电连接。源极焊盘经由缓冲层20与柱状部30的源极区域32电连接。

[0022] 此外,在本说明书中,在柱状部30的沟道形成区域34与漏极区域38的层叠方向上,在以沟道形成区域34为基准的情况下,将从沟道形成区域34朝向漏极区域38的方向设为“上”,将从沟道形成区域34朝向源极区域32的方向设为“下”来进行说明。在图示的例子中,沟道形成区域34与漏极区域38的层叠方向是Z轴方向。

[0023] 掩模层22设置在缓冲层20上。掩模层22设置在缓冲层20与绝缘层40之间。掩模层22例如是钛层、氧化硅层、氧化钛层、氧化铝层等。在掩模层22设置有多个开口部24。在图示的例子中,开口部24在Z轴方向上贯通掩模层22。柱状部30位于开口部24。掩模层22作为用于使柱状部30生长的掩模发挥功能。

[0024] 柱状部30设置在缓冲层20上。柱状部30隔着缓冲层20设置于基板10。柱状部30具有从缓冲层20向上方突出的柱状的形状。换言之,柱状部30从基板10经由缓冲层20向上方突出。柱状部30设置在缓冲层20与漏极电极80之间。柱状部30例如也被称为纳米柱、纳米线、纳米棒、纳米杆。柱状部30的平面形状例如是六边形等多边形、圆。在图2所示的例子中,

柱状部30的平面形状为正六边形。

[0025] 柱状部30的直径例如为50nm以上且500nm以下,优选为100nm以上且300nm以下。通过使柱状部30的直径为500nm以下,能够得到高品质的结晶的柱状部30。

[0026] 另外,“柱状部30的直径”在柱状部30的平面形状为圆的情况下是指直径,在柱状部30的平面形状不是圆的形状的情况下是指最小包含圆的直径。例如,在柱状部30的平面形状为多边形的情况下,柱状部30的直径是在内部包含该多边形的最小的圆的直径,在柱状部30的平面形状为椭圆的情况下,柱状部30的直径是在内部包含该椭圆的最小的圆的直径。

[0027] 柱状部30例如设置有多个。通过设置多个柱状部30,半导体装置100能够实现大电流化,适合用作功率器件。多个柱状部30相互隔离。相邻的柱状部30的间隔例如为10nm以上且1μm以下,优选为柱状部30的直径的0.5倍以上且1.5倍以下,即为25nm以上且750nm以下,更优选为400nm以上且600nm以下。从Z轴方向观察,多个柱状部30例如在规定的方向上以规定的间距排列。多个柱状部30例如呈三角格子状、正方格子状排列。在图示的例子中,多个柱状部30例如呈正三角格子状排列。

[0028] 此外,“柱状部30的间距”是指在规定的方向上相邻的柱状部30的中心间的距离。所谓“柱状部30的中心”,在柱状部30的平面形状为圆的情况下,为该圆的中心,在柱状部30的平面形状不是圆的形状的情况下,为最小包含圆的中心。例如,在柱状部30的平面形状为多边形的情况下,柱状部30的中心是在内部包含该多边形的最小的圆的中心,在柱状部30的平面形状为椭圆的情况下,柱状部30的中心是在内部包含该椭圆的最小的圆的中心。

[0029] 如图1所示,柱状部30具有源极区域32、沟道形成区域34、漂移区域37以及漏极区域38。

[0030] 源极区域32设置在缓冲层20上。源极区域32设置在缓冲层20与沟道形成区域34之间。源极区域32由半导体层构成。源极区域32的材质例如是掺杂有Si的n型的GaN、AlGaN。源极区域32的杂质浓度也可以与缓冲层20的杂质浓度相同。

[0031] 沟道形成区域34设置在源极区域32上。沟道形成区域34设置在源极区域32与漂移区域37之间。沟道形成区域34由半导体层构成。沟道形成区域34的杂质浓度比源极区域32的杂质浓度及漏极区域38的杂质浓度低。源极区域32、沟道形成区域34、漂移区域37以及漏极区域38的杂质浓度例如通过原子探针分析法来测定。

[0032] 沟道形成区域34的材质例如是有意未掺杂杂质的UID(unintentionally doped)型的GaN或AlGaN。由于柱状部30的直径较小,因此即使沟道形成区域34的导电型为UID型,也能够将沟道形成区域34完全耗尽化。在沟道形成区域34中,通过对栅极电极60施加规定的电压而形成沟道。在沟道形成区域34中,例如形成N沟道。

[0033] 漂移区域37设置在沟道形成区域34上。漂移区域37设置在沟道形成区域34与漏极区域38之间。漂移区域37由半导体层构成。漂移区域37的导电型例如与源极区域32相同。漂移区域37的材质例如为掺杂有Si的n型的GaN或AlGaN。

[0034] 漂移区域37的杂质浓度低于源极区域32的杂质浓度和漏极区域38的杂质浓度。此外,漂移区域37的杂质浓度可以与沟道形成区域34的杂质浓度相同。或者,漂移区域37的杂质浓度也可以高于沟道形成区域34的杂质浓度。即,漂移区域37的杂质浓度也可以在沟道形成区域34的杂质浓度与漏极区域38的杂质浓度之间。通过设置漂移区域37,能够提高半

半导体装置100的截止状态的耐压。

[0035] 漏极区域38设置在漂移区域37上。漏极区域38设置在漂移区域37与漏极电极80之间。漏极区域38由半导体层构成。漏极区域38的导电型与源极区域32相同。漏极区域38的材质例如是掺杂有Si的n型的GaN、AlGaN。

[0036] 漏极区域38的杂质浓度比漂移区域37的杂质浓度高。漏极区域38的杂质浓度可以与源极区域32的杂质浓度相同。源极区域32、沟道形成区域34、漂移区域37以及漏极区域38沿着第一方向配置。在图示的示例中，第一方向为+Z轴方向。源极区域32、沟道形成区域34、漂移区域37以及漏极区域38例如在+Z轴方向上层叠而构成柱状部30。

[0037] 绝缘层40设置在掩模层22上。绝缘层40设置在基板10与栅极电极60之间。绝缘层40设置在相邻的柱状部30的源极区域32之间。从Z轴方向观察，绝缘层40包围源极区域32。绝缘层40例如是SOG (spin on glass: 旋涂玻璃) 层。

[0038] 栅极绝缘层50设置于柱状部30的沟道形成区域34的侧面。沟道形成区域34的侧面例如由m面构成。栅极绝缘层50设置在沟道形成区域34的与第一方向交叉的第二方向上。在图示的示例中，第二方向为+Y轴方向，且与作为+Z轴方向的第一方向垂直。从Z轴方向观察，栅极绝缘层50包围沟道形成区域34。栅极绝缘层50设置在沟道形成区域34与栅极电极60之间。

[0039] 栅极绝缘层50例如由带隙比构成沟道形成区域34的材料大的材料构成。并且，栅极绝缘层50例如由相对介电常数比构成沟道形成区域34的材料大的材料构成。栅极绝缘层50的材质例如为氧化铪(HfO<sub>2</sub>)、氧化钽(Ta<sub>2</sub>O<sub>5</sub>)、氧化钇(Y<sub>2</sub>O<sub>3</sub>)、氧化锆(ZrO<sub>2</sub>)、氧化镧(La<sub>2</sub>O<sub>3</sub>)等过渡金属氧化物，优选为氧化铪。此外，栅极绝缘层50的材质也可以是氧化硅(SiO<sub>2</sub>)。

[0040] 栅极电极60设置于栅极绝缘层50。栅极电极60被设置在沟道形成区域34的+Y轴方向。在图示的例子中，从Z轴方向观察，栅极电极60包围栅极绝缘层50。栅极电极60例如隔着绝缘层52设置于绝缘层40。绝缘层52的材质与栅极绝缘层50相同。栅极电极60设置在绝缘层40与电介质层70之间。栅极电极60设置在相邻的柱状部30的沟道形成区域34之间。

[0041] 栅极电极60的材质例如是掺杂有磷、硼等杂质的多晶硅或金属。半导体装置100具有GAA结构。栅极电极60与未图示的栅极焊盘电连接。

[0042] 电介质层70设置在栅极绝缘层50上以及栅极电极60上。电介质层70设置在栅极绝缘层50及栅极电极60与漏极电极80之间。电介质层70被设置在漂移区域37的+Y轴方向。在图示的例子中，电介质层70包围漂移区域37。电介质层70设置在相邻的柱状部30的漂移区域37之间。

[0043] 电介质层70由带隙比构成漂移区域37的材料大的材料构成。并且，电介质层70由相对介电常数比构成漂移区域37的材料大的材料构成。电介质层70的材质例如为氧化铪、氧化钽、氧化钇、氧化锆、氧化镧等过渡金属氧化物，优选为氧化铪。

[0044] 电介质层70由带隙比构成漂移区域37的材料大且相对介电常数比构成漂移区域37的材料大的材料构成，由此在对栅极电极60施加了规定的电压的情况下，显现降低表面电场(Dielectric RESURF: Reduced Surface Field) 效应，借助由电介质层70产生的电场在漂移区域37形成耗尽层。在半导体装置100中，通过降低表面电场效应，能够具有伪超结结构。规定的电压是指用于使半导体装置100成为截止状态的电压。

[0045] 如图1的箭头A1所示，借助由电介质层70产生的电场所形成的耗尽层从柱状部30

的漂移区域37的侧面朝向柱状部30的中心扩展。此外,如箭头A2所示,还存在从沟道形成区域34侧朝向漂移区域37侧扩展的耗尽层。这样,在半导体装置100中,能够从纵向以及横向扩展耗尽层,因此显现降低表面电场效应。

[0046] 漏极电极80设置在漏极区域38上以及电介质层70上。漏极电极80设置在漏极区域38的+Z轴方向上。漏极区域38也可以与漏极电极80欧姆接触。

[0047] 漏极电极80的材质例如是掺杂有磷、硼等杂质的多晶硅或金属。漏极电极80与未图示的漏极焊盘电连接。漏极焊盘经由漏极电极80与漏极区域38电连接。

[0048] 半导体装置100例如用作功率器件,应用于逆变器、充电器、升压器、降压器、DC (Direct Current: 直流)/DC转换器、电动飞机、电动汽车等。此外,半导体装置100也可以不用作功率器件,而用作逻辑器件、高频器件等。

[0049] 半导体装置100例如具有以下的作用效果。

[0050] 在半导体装置100中,具有:作为第一半导体部的源极区域32以及作为第二半导体部的漏极区域38,它们的导电型彼此相同,沿着+Z轴方向配置;作为第三半导体部的沟道形成区域34,其设置在源极区域32与漏极区域38之间,杂质浓度比源极区域32以及漏极区域38低;作为第四半导体层的漂移区域37,其设置在沟道形成区域34与漏极区域38之间,杂质浓度比源极区域32以及漏极区域38低;设置在沟道形成区域34的+Y轴方向的栅极绝缘层50和栅极电极60;以及作为电介质部的电介质层70,其设置在漂移区域37的+Y轴方向。电介质层70由带隙比构成漂移区域37的材料大且相对介电常数比构成漂移区域37的材料大的材料构成,在对栅极电极60施加了规定的电压的情况下,借助由电介质层70产生的电场在漂移区域37形成耗尽层。

[0051] 因此,在半导体装置100中,例如与电介质层的介电常数为漂移区域的介电常数以下的情况相比,如上述的箭头A1那样,能够增大耗尽层从柱状部30的漂移区域37的侧面朝向柱状部30的中心扩展的降低表面电场效应。由此,能够提高耐受电压。其结果为,能够提高漂移区域37的杂质浓度,从而能够降低导通电阻。

[0052] 此外,在半导体装置100中,例如与电介质层的带隙为漂移区域的带隙以下的情况相比,能够提高电介质层70的绝缘性。因此,能够减少泄漏电流。

[0053] 此外,在半导体装置100中,沟道形成区域34的杂质浓度比源极区域32及漏极区域38的杂质浓度低,因此能够增大沟道形成区域34的载流子的迁移率。例如在沟道形成区域34形成N沟道的情况下,能够增大沟道形成区域34的电子迁移率。由此,能够降低导通电阻。

[0054] 此外,在半导体装置100中,与代替电介质层70而设置导电型与源极区域32及漏极区域38不同的p型半导体层的情况相比,能够容易地制造半导体装置100。例如,如果设置p型半导体层来代替电介质层70而形成超结结构,则需要高精度地控制p型半导体层的杂质浓度,制造工序变得复杂。

[0055] 此外,在半导体装置100中,在截止状态下,栅极电极60与漏极区域38之间的电位差大于栅极电极60与源极区域32之间的电位差。因此,与在源极区域的+Y轴方向设置电介质层的情况相比,能够增大降低表面电场效应。

[0056] 在半导体装置100中,源极区域32、沟道形成区域34以及漂移区域37在+Z轴方向上层叠而构成柱状部30。因此,在半导体装置100中,与源极区域、沟道形成区域以及漂移区域不构成柱状部的情况相比,由基板10与缓冲层20的晶格常数差引起的结晶缺陷在源极区域

32在柱状部30侧面弯折,由此能够减小到达沟道形成区域34以及漂移区域37的可能性。由此,沟道形成区域34以及漂移区域37能够具有高品质的结晶性。在图示的例子中,漏极区域38也构成柱状部30,因此漏极区域38也能够具有高品质的结晶性。

[0057] 在半导体装置100中,从Z轴方向观察,栅极绝缘层50包围沟道形成区域34,栅极电极60包围栅极绝缘层50。因此,在半导体装置100中,能够使沟道形成区域34完全耗尽化。

[0058] 在半导体装置100中,电介质层70的材质是过渡金属氧化物。因此,在半导体装置100中,易于实现带隙比漂移区域37大且相对介电常数比漂移区域37大的电介质层70。

[0059] 在半导体装置100中,电介质层70的材质是氧化铪。因此,在半导体装置100中,能够通过ALD(Atomic Layer Deposition:原子层沉积)法形成电介质层70。由此,例如在相邻的柱状部30之间不产生空隙就能够形成电介质层70。

[0060] 在半导体装置100中,栅极绝缘层50由带隙比构成沟道形成区域34的材料大且相对介电常数比构成沟道形成区域34的材料大的材料构成。因此,在半导体装置100中,例如与栅极绝缘层的介电常数为沟道形成区域的介电常数以下的情况相比,能够提高阈值电压的控制性。此外,例如与栅极绝缘层的带隙为沟道形成区域的带隙以下的情况相比,能够提高栅极绝缘层50的绝缘性。

[0061] 在半导体装置100中,栅极绝缘层50的材质是过渡金属氧化物。因此,在半导体装置100中,容易实现带隙比沟道形成区域34大且相对介电常数比沟道形成区域34大的栅极绝缘层50。

[0062] 在半导体装置100中,栅极绝缘层50的材质是氧化铪。因此,在半导体装置100中,能够通过ALD法形成栅极绝缘层50。由此,例如在相邻的柱状部30之间不产生空隙就能够形成栅极绝缘层50。

## [0063] 2. 半导体装置的制造方法

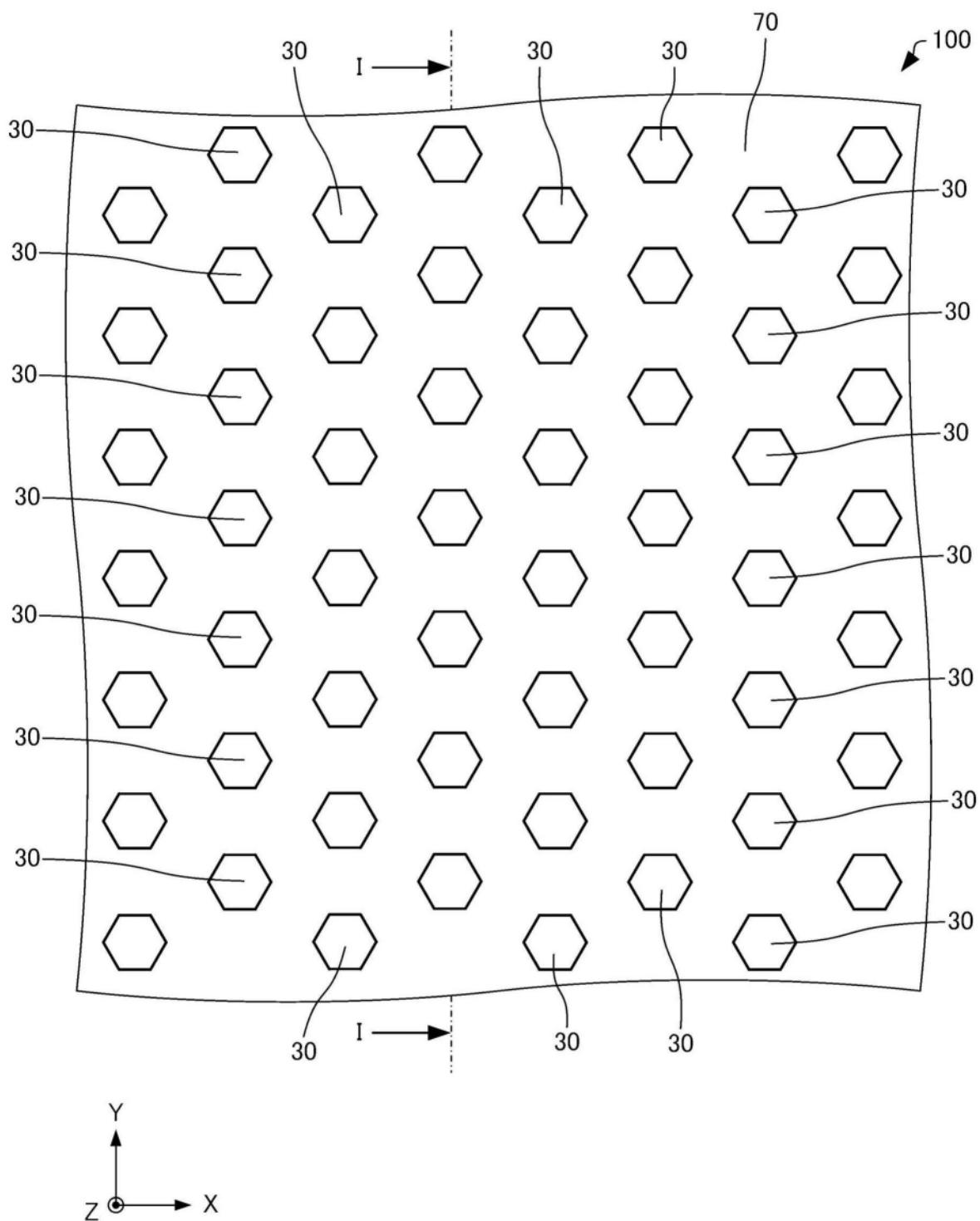

[0064] 接下来,参照附图对本实施方式的半导体装置100的制造方法进行说明。图3~图5是示意性地示出本实施方式的半导体装置100的制造工序的剖视图。

[0065] 如图3所示,在基板10上使缓冲层20外延生长。作为使其外延生长的方法,例如,能够列举MOCVD(Metal Organic Chemical Vapor Deposition:金属有机化学气相沉积)法、MBE(Molecular Beam Epitaxy:分子束外延)法。缓冲层20的生长一边掺杂杂质一边进行。

[0066] 接着,在缓冲层20上形成掩模层22。掩模层22例如通过电子束蒸镀法、溅射法等形成。

[0067] 接着,对掩模层22进行图案化,形成多个开口部24。图案化例如通过电子束光刻以及干式蚀刻来进行。

[0068] 如图4所示,在缓冲层20上,将掩模层22作为掩模,使源极区域32、沟道形成区域34、漂移区域37以及漏极区域38依次外延生长。作为使之外延生长的方法,例如能够列举MOCVD法、MBE法。源极区域32的生长及漏极区域38的生长是一边掺杂杂质一边进行的。通过本工序,能够形成多个柱状部30。

[0069] 接着,在掩模层22上且相邻的柱状部30的源极区域32之间形成绝缘层40。绝缘层40例如通过ALD法、CVD(Chemical Vapor Deposition:化学气相沉积)法、SOG(spin on glass:旋涂玻璃)法等形成。

[0070] 如图5所示,在绝缘层40上以覆盖柱状部30的方式形成绝缘层50a。绝缘层50a例如

通过ALD法、CVD法等形成。在图示的例子中，绝缘层50a形成于柱状部30的侧面和上表面。

[0071] 接着，在绝缘层50a上形成栅极电极60。栅极电极60例如通过CVD法、溅射法、真空蒸镀法形成。

[0072] 如图1所示，对绝缘层50a上的一部分进行蚀刻而去除。由此，在沟道形成区域34与栅极电极60之间形成栅极绝缘层50。通过该蚀刻，漏极区域38露出。

[0073] 接着，在栅极绝缘层50上以及栅极电极60上形成电介质层70。电介质层70例如通过ALD法、CVD法等形成。

[0074] 接着，在漏极区域38上以及电介质层70上形成漏极电极80。漏极电极80例如通过CVD法、溅射法、真空蒸镀法形成。

[0075] 通过以上的工序，能够制造出半导体装置100。

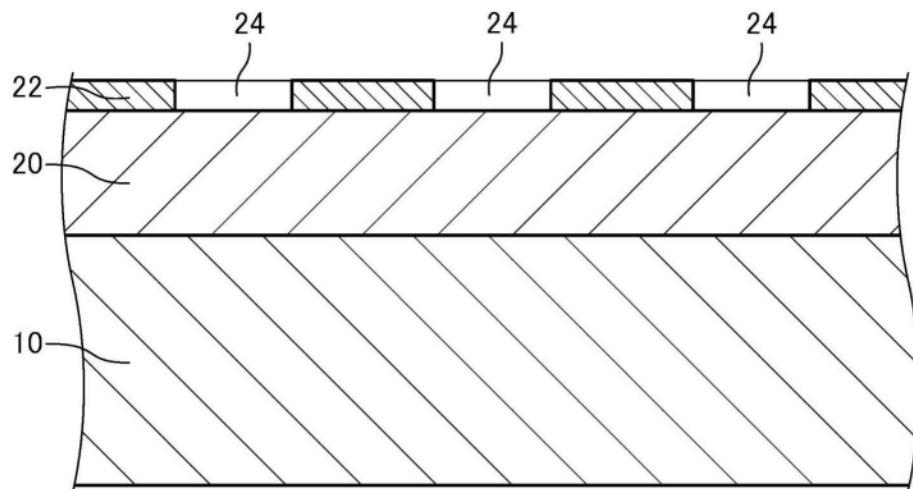

### [0076] 3. 半导体装置的变形例

[0077] 接下来，参照附图对本实施方式的变形例的半导体装置进行说明。图6是示意性地示出本实施方式的变形例的半导体装置200的剖视图。以下，在本实施方式的变形例的半导体装置200中，对于具有与上述的本实施方式的半导体装置100的结构部件相同的功能的部件标注相同标号，并省略对其详细的说明。

[0078] 在上述的半导体装置100中，如图1所示，漏极区域38构成柱状部30。

[0079] 与此相对，在半导体装置200中，如图6所示，漏极区域38不构成柱状部30。柱状部30由源极区域32、沟道形成区域34以及漂移区域37构成。

[0080] 漏极区域38还设置于电介质层70的+Z轴方向。漏极区域38设置在漂移区域37上以及电介质层70上。漏极区域38设置在漂移区域37及电介质层70与漏极电极80之间。漏极区域38遍及多个柱状部30而设置。从层叠方向观察，漏极区域38与多个柱状部30重叠。从层叠方向观察，漏极电极80与多个柱状部30重叠。

[0081] 在半导体装置200中，具有被设置于漂移区域37的+Z轴方向的漏极电极80，并且漏极区域38还被设置于电介质层70的+Z轴方向。因此，在半导体装置200中，与漏极区域未设置于电介质层的+Z轴方向的情况相比，能够增大漏极区域38与漏极电极80的接触面积。由此，能够降低漏极区域38与漏极电极80的接触电阻。通常，半导体层与金属电极之间的接触电阻高，因此增大该接触面积是重要的。

[0082] 上述的实施方式和变形例仅为一例，不应限定于此。例如，也能够对实施方式以及各个变形例进行适当组合。

[0083] 例如，本发明包含与在实施方式中说明的结构实质上相同的结构(例如，功能、方法和结果相同的结构，或目的和效果相同的结构)。另外，本发明包括置换了在实施方式中说明的结构的不是本质部分而得到的结构。另外，本发明包括与实施方式中说明的结构产生相同的作用效果的结构或能够达成相同目的的结构。另外，本发明包含在实施方式中说明的结构中附加了公知技术的结构。

[0084] 根据上述的实施方式以及变形例导出以下的内容。

[0085] 半导体装置的一个方式具有：导电型彼此相同的第一半导体部以及第二半导体部，它们沿着第一方向配置；第三半导体部，其设置在所述第一半导体部与所述第二半导体部之间，杂质浓度比所述第一半导体部以及所述第二半导体部低；第四半导体部，其设置在所述第二半导体部与所述第三半导体部之间，杂质浓度比所述第一半导体部以及所述第二

半导体部低；栅极绝缘层以及栅极电极，它们设置在所述第三半导体部的与所述第一方向交叉的第二方向；以及电介质部，其设置在所述第四半导体部的所述第二方向，所述电介质部由带隙比构成所述第四半导体部的材料大且相对介电常数比构成所述第四半导体部的材料大的材料构成，在对所述栅极电极施加了规定的电压的情况下，在所述第四半导体部形成耗尽层。

[0086] 根据这样的半导体层，能够降低导通电阻。

[0087] 在半导体装置的一个方式中，也可以是，所述第一半导体部、所述第三半导体部以及所述第四半导体部在所述第一方向上层叠而构成柱状部。

[0088] 根据这样的半导体层，能够减小结晶缺陷到达第三半导体部以及第四半导体部的可能性。

[0089] 在半导体装置的一个方式中，也可以是，从所述第一方向观察，所述栅极绝缘层包围所述第三半导体部，所述栅极电极包围所述栅极绝缘层。

[0090] 根据这样的半导体层，能够使第三半导体部完全耗尽化。

[0091] 在半导体装置的一个方式中，也可以是，所述第一半导体部构成源极区域，所述第二半导体部构成漏极区域。

[0092] 根据这样的半导体层，能够增大降低表面电场效应。

[0093] 在半导体装置的一个方式中，所述电介质部的材质可以是过渡金属氧化物。

[0094] 根据这样的半导体层，容易实现带隙比第四半导体部大且相对介电常数比第四半导体部大的电介质部。

[0095] 在半导体装置的一个方式中，所述电介质部的材质也可以是氧化铪。

[0096] 根据这样的半导体层，能够通过ALD法形成电介质部。

[0097] 在半导体装置的一个方式中，也可以是，所述栅极绝缘层由带隙比构成所述第三半导体部的材料大且相对介电常数比构成所述第三半导体部的材料大的材料构成。

[0098] 根据这样的半导体层，能够提高阈值电压的控制性。

[0099] 在半导体装置的一个方式中，也可以是，所述栅极绝缘层的材质为过渡金属氧化物。

[0100] 根据这样的半导体层，容易实现带隙比第三半导体部大且相对介电常数比第三半导体部大的栅极绝缘层。

[0101] 在半导体装置的一个方式中，也可以是，所述栅极绝缘层的材质为氧化铪。

[0102] 根据这样的半导体层，能够通过ALD法形成栅极绝缘层。

[0103] 在半导体装置的一个方式中，也可以是，具有设置在所述第二半导体部的所述第一方向的电极，所述第二半导体部还设置在所述电介质部的所述第一方向。

[0104] 根据这样的半导体层，能够降低第二半导体部与电极的接触电阻。

[0105] 功率器件的一个方式具有：导电型彼此相同的第一半导体部以及第二半导体部，它们沿着第一方向配置；第三半导体部，其设置于所述第一半导体部与所述第二半导体部之间，杂质浓度比所述第一半导体部以及所述第二半导体部低；栅极绝缘层以及栅极电极，它们设置于所述第三半导体部的与所述第一方向交叉的第二方向；以及电介质部，其设置于所述第二半导体部的所述第二方向，所述电介质部由带隙比构成所述第二半导体部的材料大且相对介电常数比构成所述第二半导体部的材料大的材料构成，在对所述栅极电极施

加了规定的电压的情况下,借助由所述电介质部产生的电场在所述第二半导体部形成耗尽层。

[0106] 根据这样的功率器件,能够降低导通电阻。

图1

图2

图3

图4

图5

图6