(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6461003号

(P6461003)

(45) 発行日 平成31年1月30日(2019.1.30)

(24) 登録日 平成31年1月11日(2019.1.11)

(51) Int.Cl.

F 1

|                    |                  |                    |

|--------------------|------------------|--------------------|

| <b>H01L 27/115</b> | <b>(2017.01)</b> | <b>H01L 27/115</b> |

| <b>H01L 27/10</b>  | <b>(2006.01)</b> | <b>H01L 27/10</b>  |

| <b>H01L 21/336</b> | <b>(2006.01)</b> | <b>H01L 29/78</b>  |

| <b>H01L 29/788</b> | <b>(2006.01)</b> | <b>371</b>         |

| <b>H01L 29/792</b> | <b>(2006.01)</b> |                    |

請求項の数 10 (全 23 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-547420 (P2015-547420)  |

| (86) (22) 出願日 | 平成25年12月5日 (2013.12.5)        |

| (65) 公表番号     | 特表2016-503960 (P2016-503960A) |

| (43) 公表日      | 平成28年2月8日 (2016.2.8)          |

| (86) 國際出願番号   | PCT/US2013/073327             |

| (87) 國際公開番号   | W02014/093126                 |

| (87) 國際公開日    | 平成26年6月19日 (2014.6.19)        |

| 審査請求日         | 平成28年12月2日 (2016.12.2)        |

| 審判番号          | 不服2017-11871 (P2017-11871/J1) |

| 審判請求日         | 平成29年8月8日 (2017.8.8)          |

| (31) 優先権主張番号  | 13/715, 565                   |

| (32) 優先日      | 平成24年12月14日 (2012.12.14)      |

| (33) 優先権主張国   | 米国 (US)                       |

早期審査対象出願

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364997<br>サイプレス セミコンダクター コーポレーション<br>アメリカ合衆国 カリフォルニア州 95134 サンノゼ チャンピオン コート 198 |

| (74) 代理人  | 100079108<br>弁理士 稲葉 良幸                                                             |

| (74) 代理人  | 100109346<br>弁理士 大貫 敏史                                                             |

| (74) 代理人  | 100117189<br>弁理士 江口 昭彦                                                             |

| (74) 代理人  | 100134120<br>弁理士 内藤 和彦                                                             |

最終頁に続く

(54) 【発明の名称】不揮発性メモリを有する集積回路及び製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の領域に形成され、かつ、選択ゲート誘電体の上に配置された選択ゲートと、前記選択ゲートの側壁上に形成され、かつ、1つ以上の誘電層を有する電荷トラップ誘電体の上に配置されたメモリゲートと、を含むメモリセルと、

第2の領域に形成され、かつ、前記電荷トラップ誘電体とは異なる第1の論理ゲート誘電体の上に配置された第1の論理ゲートを含む第1のトランジスタと、

第3の領域に形成され、かつ、前記電荷トラップ誘電体とは異なる第2の論理ゲート誘電体の上に配置された第2の論理ゲートを含む第2のトランジスタと、を備え、

前記メモリゲートは、前記第2の論理ゲートの厚さと実質的に同様の幅を有し、前記選択ゲート誘電体、前記第1の論理ゲート誘電体、及び前記第2の論理ゲート誘電体は、それぞれ互いに異なる厚さを有し、

前記第2の論理ゲート誘電体の厚さは、前記選択ゲート誘電体の厚さよりも小さく、かつ、前記選択ゲート誘電体の厚さは、前記第1の論理ゲート誘電体の厚さよりも小さい、半導体デバイス。

## 【請求項 2】

前記選択ゲート及び前記第1の論理ゲートが実質的に同じ厚さである、請求項1に記載の半導体デバイス。

## 【請求項 3】

10

20

前記電荷トラップ誘電体は、前記メモリゲートと前記選択ゲートの前記側壁との間に配置されている、請求項 1 に記載の半導体デバイス。

【請求項 4】

前記電荷トラップ誘電体が、2つの二酸化シリコン層の間に挟まれた窒化物層を含む、請求項 3 に記載の半導体デバイス。

【請求項 5】

前記第 2 の論理ゲートが前記第 1 の論理ゲートよりも薄い、請求項 1 に記載の半導体デバイス。

【請求項 6】

前記選択ゲート及び前記第 1 の論理ゲートが第 1 のゲート導体層を含む、請求項 1 に記載の半導体デバイス。 10

【請求項 7】

前記第 1 のゲート導体層が単一のポリ(多結晶)層を含む、請求項 6 に記載の半導体デバイス。

【請求項 8】

前記メモリゲート及び前記第 2 の論理ゲートが第 2 のゲート導体層を含む、請求項 1 に記載の半導体デバイス。

【請求項 9】

前記第 2 のゲート導体層が単一のポリ(多結晶)層を含む、請求項 8 に記載の半導体デバイス。 20

【請求項 10】

前記第 1 の領域は、メモリコア領域を備え、

前記第 2 の領域は、高電圧制御論理領域を備え、

前記第 3 の領域は、低電圧制御論理領域を備える、

請求項 1 に記載の半導体デバイス。

【発明の詳細な説明】

【技術分野】

【0001】

[0001] 本開示は一般に、改良された埋め込み半導体製品、並びにそのような半導体製品を生成するための方法及び装置に関する。 30

【背景技術】

【0002】

[0002] 不揮発性コアアレイにおける不揮発性メモリは、例えば、記憶層内に電荷を入れるホットキャリア注入を用いてプログラムされる。このプログラムプロセスを容易にするために高いドレイン電圧及びゲート電圧が用いられ、プログラムの間にメモリセルには比較的大きい電流が流れるが、これは低電圧又は低電力の用途には望ましくないことがある。

【0003】

[0003] スプリットゲート不揮発性メモリセルは、不揮発性メモリセルの一種であり、メモリゲートに隣接して選択ゲートが配置されたものである。スプリットゲート不揮発性メモリセルのプログラムの間、選択ゲートを比較的低い電圧にバイアスし、メモリゲートのみを高い電圧にバイアスして、ホットキャリア注入のために必要な垂直電界を得る。これによって、従来の非スプリットゲートメモリセルに比べ、プログラム動作中のホットキャリア注入は高効率となる。スプリットゲート不揮発性メモリセルは、ホットキャリア注入以外の技法を用いてプログラムすることも可能であり、その技法に応じて、プログラム動作中に得られる従来の不揮発性フラッシュメモリセルに対する利点は様々に異なる可能性がある。 40

【0004】

[0004] スプリットゲート不揮発性メモリセルのもう1つの利点は、高速の読み取り時間である。選択ゲートはメモリゲートと直列であるので、メモリゲートの消去された状態は 50

、空乏モード（すなわち閾値電圧  $V_t$  がゼロボルト未満である）に近いか又は空乏モードであり得る。消去されたメモリゲートがそのような空乏モードにある場合でも、オフ状態の選択ゲートが、チャネルに大きな電流が流れることを防ぐ。消去された状態の閾値電圧がゼロに近いか又はゼロ未満であるので、プログラムされた状態の閾値電圧が著しく高い必要はなく、それでも、消去された状態とプログラムされた状態との間に妥当な読み取りマージンが与えられる。これにより、読み取り動作において選択ゲート及びメモリゲートの双方に印加される電圧を供給電圧以下とすることができる。従って、供給電圧をもっと高いレベルまで上げる必要がないので、読み取り動作が高速となる。

### 【発明の概要】

#### 【発明が解決しようとする課題】

10

#### 【0005】

[0005] メモリセルと同一の基板上に、多くのタイプの電界効果デバイスをモノリシックに組み込むことは一般的である。それらのデバイスは、例えば符号化、電荷ポンピング、及びメモリ動作に関連した他の機能を実行する。また、基板は、メモリ動作に関連しない機能を提供するデバイスも含む場合がある。メモリセルと同一の基板上に組み込まれたそのような非メモリデバイスには、高速動作用に調整されたトランジスタが含まれ得るが、高い動作電圧を扱うように調整された他のトランジスタも存在する。スプリットゲート不揮発性メモリセル等のメモリセルの処理を、同一基板上にある1つ以上のタイプの非メモリトランジスタの処理と調和させることは困難である。これは、各々が異なる製造パラメータを必要とするからである。例えば、高速の性能要求のためには、非メモリトランジスタのゲート長を縮小して、処理を容易にするため必要なゲートスタックが薄くなるようにならなければならない。しかしながら、高い動作電圧を扱うための非メモリトランジスタでは、トランジスタの接合の傾斜を更に漸進的に（graded）しなければならない。これは通常、接合の形成中の注入エネルギーを増大することによって達成される。注入の貫通を防ぐために、ゲートスタックを厚くする必要がある。従って、異なる非メモリトランジスタのために異なるゲートスタックの厚さを有し、同一の半導体デバイス上の不揮発性メモリセルと調和させるための方法を有することが望ましい。このため、同一の基板上で異なる電気的要求を有するメモリセル及び他のデバイスを調和させて、コスト、性能、信頼性、又は製造性の向上を容易にするためのデバイス及び方法が必要とされている。

20

#### 【課題を解決するための手段】

30

#### 【0006】

[0006] 一実施形態によれば、第1の領域、第2の領域、及び第3の領域を含む半導体デバイスを製造する方法が提供される。この方法に従って、基板上に第1のゲート誘電体を形成する。第1の領域から第1のゲート誘電体を除去した後、第1の領域に選択ゲート誘電体を形成する。第1の領域に選択ゲートを形成することができ、第2の領域に第1の論理ゲートを形成する。第1の領域において選択ゲートによって覆われていない選択ゲート誘電体を除去した。次いで電荷トラップ誘電体を配置することができる。次いで、第3の領域から、電荷トラップ誘電体及び第1のゲート誘電体を除去し、ゲート導体層を配置することができる。ゲート導体層を除去（例えばエッティング）して、選択ゲートの側壁上のメモリゲート及び第3の領域における第2の論理ゲートを画定することができる。ゲート導体層の除去は、ゲート導体層を除去する前にハードマスクスタックを堆積してエッティングすることを含み得る。

40

#### 【0007】

[0007] 実施形態によれば、半導体デバイスが提供される。この半導体デバイスは、第1の領域に形成された選択ゲートと、第2の領域に形成された第1の論理ゲートと、第3の領域に形成された第2の論理ゲートと、を含む。第1の論理ゲートの厚さは、第2の論理ゲートと同じであるか又は異なる場合がある。第1の論理ゲートの厚さが第2の論理ゲートの厚さとは異なる場合、第1の論理ゲート及び第2の論理ゲートの各々は、単一のゲート材料層によって別個に形成されている。更に、デバイスは、選択ゲートの側壁上に形成されたメモリゲートを含む。メモリゲートは、第2の論理ゲートの厚さと実質的に同様の

50

幅を有する。

**【0008】**

[0008] 本発明の更に別の特徴及び利点、並びに本発明の様々な実施形態の構造及び動作について、添付図面を参照して以下で詳述する。本発明は、本明細書に記載する特定の実施形態に限定されないことに留意すべきである。そのような実施形態は、例示の目的のために本明細書に提示したに過ぎない。本明細書に包含される教示に基づいて、当業者には追加の実施形態が明らかであろう。

**【図面の簡単な説明】**

**【0009】**

[0009] 以下に、添付図面を参照して一例としてのみ本発明の実施形態について記載する。図面において、対応する参照番号は対応する部分を示す。更に、本明細書に組み込まれてその一部を形成する添付図面は本発明を例示し、記載と共に、本発明の原理を説明して、当業者に本発明の作成及び使用を可能とするように機能する。

**【0010】**

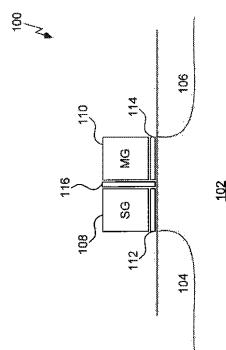

**【図1】[0010]** 様々な実施形態によるスプリットゲート不揮発性メモリセルの断面を示す。

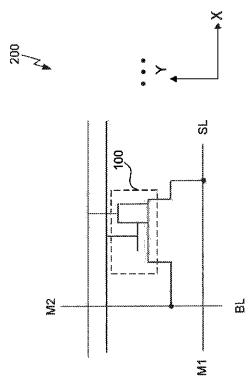

**【図2】[0011]** 様々な実施形態による、メモリアレイ内のメモリセルの回路図を示す。

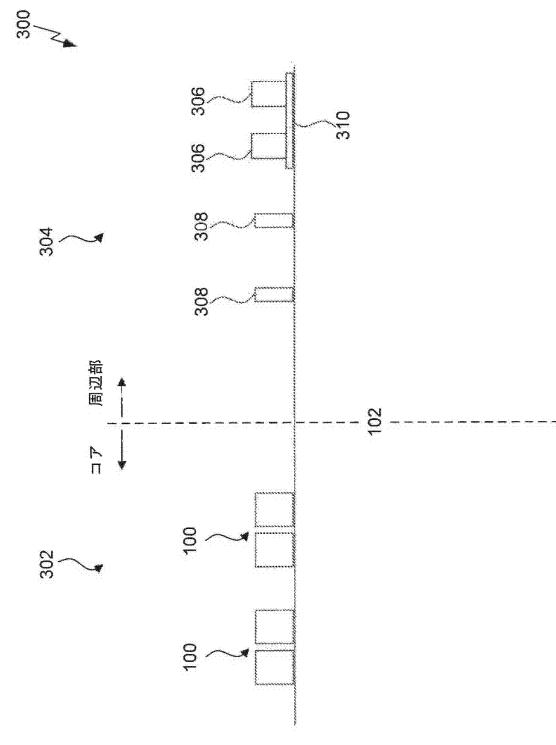

**【図3】[0012]** 様々な実施形態による半導体デバイスの断面を示す。

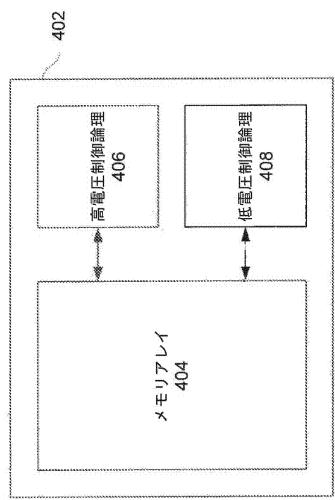

**【図4】[0013]** 様々な実施形態による半導体デバイスの機能ブロック図を示す。

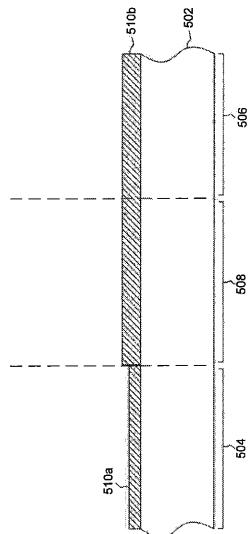

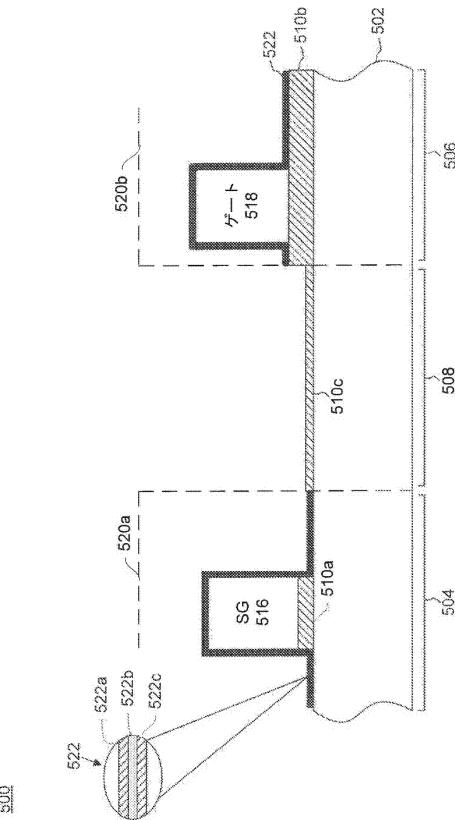

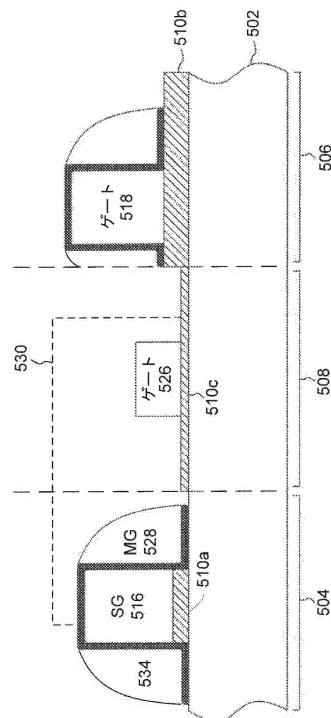

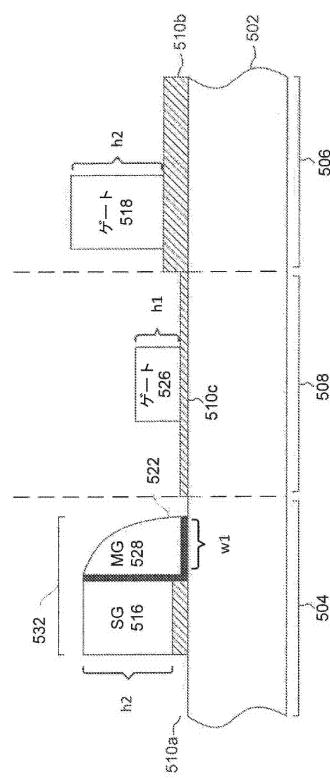

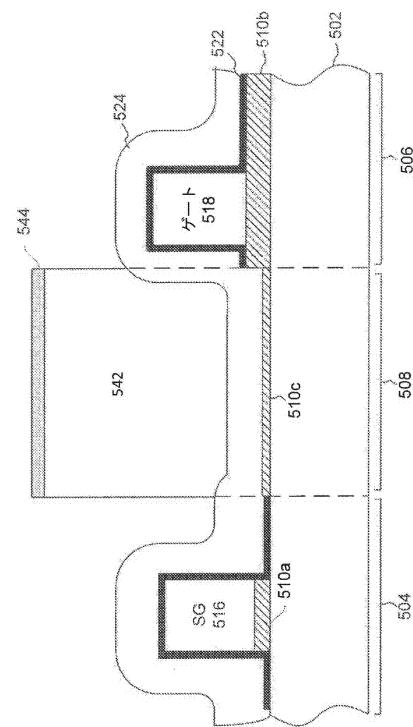

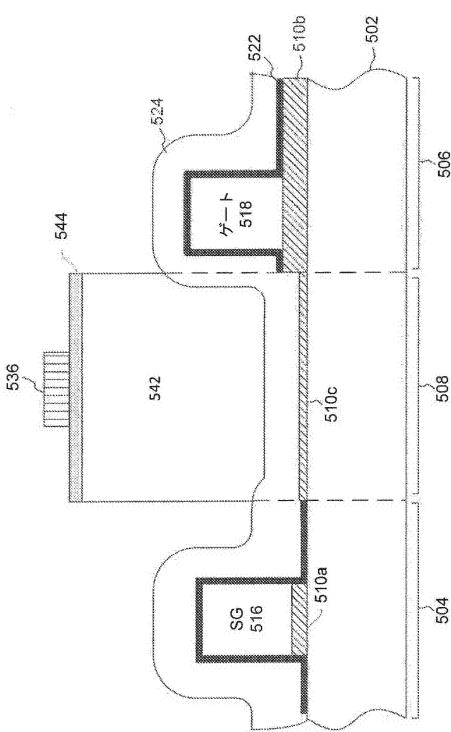

**【図5A】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

20

**【図5B】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5C】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5D】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5E】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5F】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5G】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5H】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5I】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図5J】[0014]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

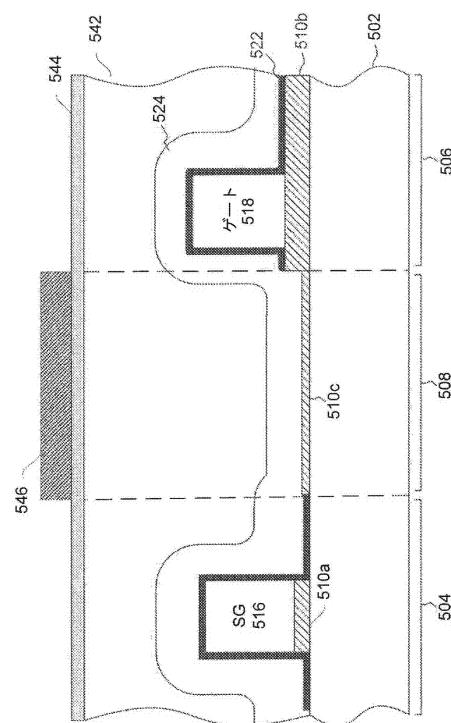

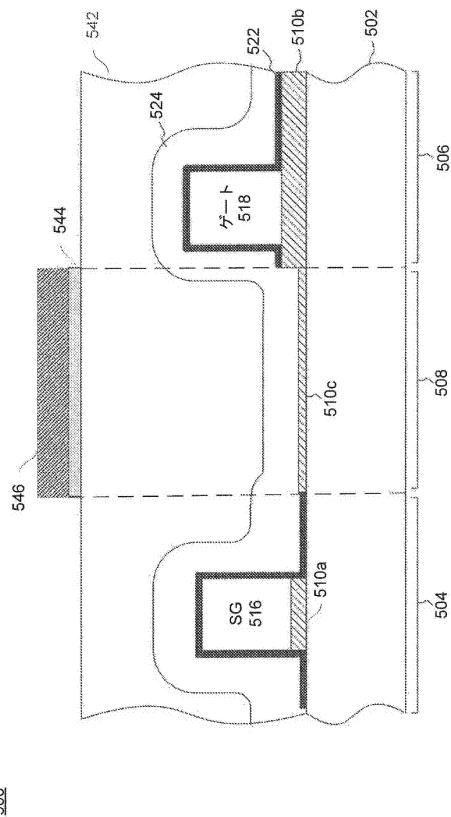

**【図6A】[0015]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

30

**【図6B】[0015]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図6C】[0015]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

**【図6D】[0015]** 実施形態による半導体デバイスの製造中のある時点の断面を示す。

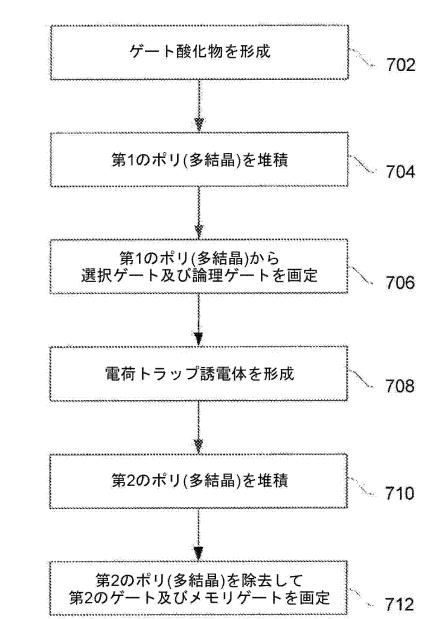

**【図7】[0016]** 実施形態による半導体デバイスの製造方法を示すフローチャートである。

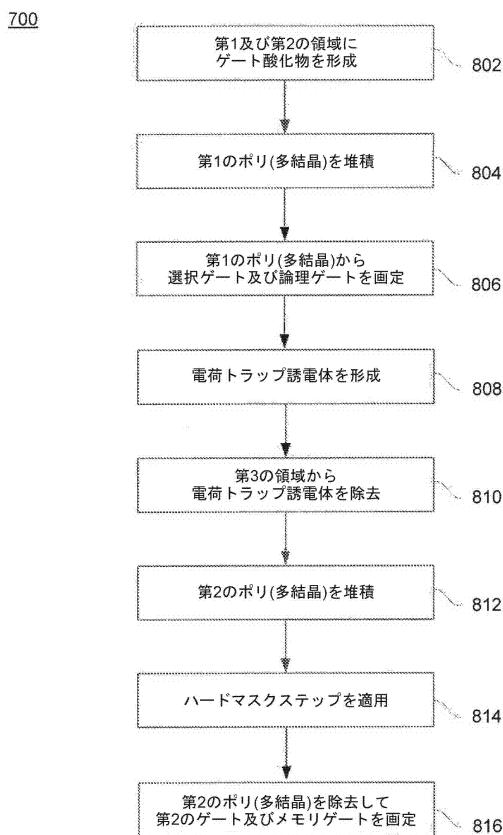

。 **【図8】[0017]** 実施形態による半導体デバイスの製造方法を示すフローチャートである。

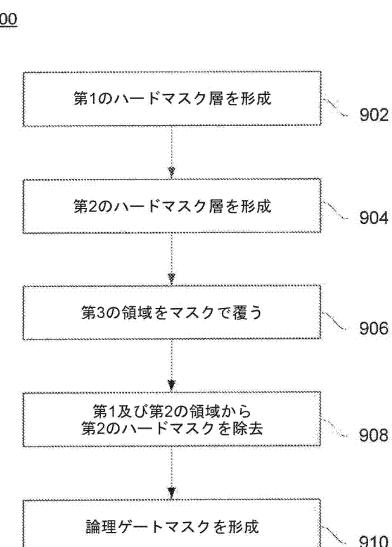

。 **【図9】[0018]** 実施形態による半導体デバイスの製造方法を示すフローチャートである。

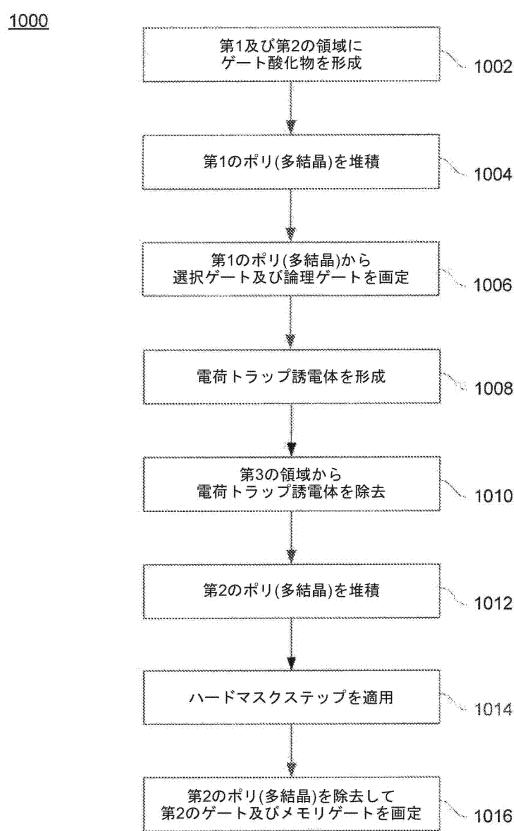

。 **【図10】[0019]** 実施形態による半導体デバイスの製造方法を示すフローチャートである。

40

**【0011】**

[0020] 本発明の特徴及び利点は、以下に示す詳細な説明を図面と関連付けて参照する場合にいっそう明らかとなろう。図面において、同様の参照番号は概ね、同一の要素、機能的に同様の要素、及び／又は構造的に同様の要素を示す。

**【発明を実施するための形態】**

**【0012】**

[0021] 本明細書は、本発明の特徴を組み込んだ1つ以上の実施形態を開示する。開示する実施形態（複数の実施形態）は、単に本発明を例示するに過ぎない。本発明の範囲は、開示した実施形態（複数の実施形態）に限定されない。本発明は、添付の特許請求の範囲

50

によって規定される。

【0013】

[0022] 記載される実施形態（複数の実施形態）、及び本明細書における「一実施形態」、「ある実施形態」、「例示的な実施形態」等に対する言及は、記載される実施形態（複数の実施形態）が特定の特徴、構造、又は特性を含むことができるが、全ての実施形態が必ずしもその特定の特徴、構造、又は特性を含むわけではないことを示す。また、そのようなフレーズは必ずしも同一の実施形態を指し示すものではない。更に、ある実施形態に関連付けて特定の特徴、構造、又は特性について記載する場合、明示的に記載されているか記載されていないかにかかわらず、そのような特徴、構造、又は特性を他の実施形態と関連付けて実行することは当業者の知識の範囲内であることは理解されよう。

10

【0014】

[0023] 様々な実施形態についていっそう詳細に記載する前に、この記載全体を通して用いることができるいくつかの言葉について更に説明を行うものとする。

【0015】

[0024] 「エッチ」又は「エッチング」という言葉は、本明細書において一般に、材料をパターニングする製造プロセスであって、エッチの完了後に材料の少なくとも一部が残っているようなものを記載するために用いられる。例えば、シリコンをエッチングするプロセスは、シリコンの上のマスキング層（例えばフォトレジスト又はハードマスク）をパターニングし、次いでマスキング層によって保護されなくなったシリコンのエリアを除去することを含むことは理解されよう。このため、マスクによって保護されたシリコンのエリアは、エッチプロセスが完了した後も残っている。しかしながら別の例では、エッチングは、マスクを用いないがエッチプロセスの完了後に材料の少なくとも一部が残っているプロセスのことも指す場合がある。

20

【0016】

[0025] 上述の記載は、「除去する」から「エッチングする」という言葉を区別するのに役立つ。材料をエッチングする場合、プロセスの完了後に材料の少なくとも一部は残っている。これに対して、材料を除去する場合は、プロセスにおいて実質的に全ての材料が除去される。しかしながらいくつかの実施形態においては、「除去する」は、エッチングを含み得る広義の言葉であると見なされる。

【0017】

30

[0026] 本明細書における説明中、電界効果デバイスが製造される基板の様々な領域について言及する。これらの領域は基板上のどこにでも存在することができ、更に、これらの領域は相互に排他的でない場合があることは理解されよう。すなわち、いくつかの実施形態において、1つ以上の領域の部分どうしが重複することがある。本明細書では3つまでの異なる領域について記載するが、いかなる数の領域も基板上に存在することができ、特定のタイプのデバイス又は材料を有するエリアを指定することは理解されよう。一般に、これらの領域は、同様のデバイスを含む基板のエリアを便利に記載するため用いられるが、記載する実施形態の範囲又は精神を限定するものではない。

【0018】

[0027] 「堆積する」又は「配置する」という言葉は、本明細書において、基板に材料の層を適用する動作を記載するために用いられる。そのような言葉は、限定ではないが熱成長、スペッタリング、蒸着、化学気相堆積、エピタキシャル成長、電気めっき等を含むいずれかの実行可能な層形成技法を記載するように意図されている。様々な実施形態によれば、例えば堆積は、いずれかの適切な周知の方法に従って実行することができる。例えば堆積は、基板上に材料を成長、被覆、又は転写させるいずれかのプロセスを含むことができる。いくつかの周知の技術には、とりわけ、物理気相堆積（PVD）、化学気相堆積（CVD）、電気化学堆積（ECD）、分子ビームエピタキシ（MBE）、原子層堆積（ALD）、及びプラズマエンハンスCVD（PECVD）が含まれる。

40

【0019】

[0028] この記載全体を通して、「基板」が用いられる場合、最も一般的にはシリコンで

50

あると考えられる。しかしながら基板は、ゲルマニウム、ガリウムヒ素、リン化インジウム等の幅広い半導体材料のいずれかであり得る。他の実施形態では、基板は、ガラス又はサファイアウェーハのように非導電性である場合がある。

#### 【0020】

[0029] 本明細書において用いる場合、「マスク」は、マスクで覆われていない材料部分の選択的な除去（例えばエッチング）を可能とするいずれかの適切な材料を含み得る。いくつかの実施形態によれば、マスキング構造は、ポリ（メチルメタクリレート）（PMM A）、ポリ（メチルグルタルイミド）（PMGI）、フェノールホルムアルデヒド樹脂、適切なエポキシ等のフォトレジストを含み得る。

#### 【0021】

[0030] そのような実施形態について更に詳しく記載する前に、本実施形態を実施することができる例示的なメモリセル及び環境を提示することが有益である。

#### 【0022】

[0031] 図1は、スプリットゲート不揮発性メモリセル100の一例を示す。メモリセル100は、シリコン等の基板102の上に形成されている。基板102は一般にp型又はp型ウェルであり、第1のドープソース／ドレイン領域104及び第2のドープソース／ドレイン領域106はn型である。しかしながら、基板102がn型であり、領域104及び106がp型であることも可能である。

#### 【0023】

[0032] メモリセル100は、2つのゲート、すなわち選択ゲート108及びメモリゲート110を含む。各ゲートは、例えばゲート構造を画定するための周知の堆積及びエッチ技法によって形成されたドープ多結晶シリコン（「poly（ポリ、多結晶）」）層等のゲート導体を備えることができる。選択ゲート108は、誘電層112の上に配置されている。メモリゲート110は、1つ以上の誘電層を有する電荷トラップ誘電体114の上に配置されている。一例において、電荷トラップ誘電体114は、2つの二酸化シリコン層の間に挟まれた電荷トラップ窒化シリコン層を含み、まとめて一般的に「ONO」と称される3層のスタックを生成する。他の電荷トラップ誘電体には、シリコンリッチ窒化物膜や、限定ではないがシリコン、酸素、及び窒素を様々な化学量論比で含むいずれかの膜が含まれ得る。また、選択ゲート108とメモリゲート110との間に、これら2つのゲート間を電気的に分離するために垂直誘電体116が配置されている。いくつかの例では、垂直誘電体116及び電荷トラップ誘電体114は同一の誘電体であるが、他の例では、一方の誘電体を形成した後に他方を形成する（例えばそれらは異なる誘電特性を有し得る）。このため、垂直誘電体116は必ずしも電荷トラップ誘電体114と同一の膜構造を含むわけではない。これらのゲートを画定した後に、領域104及び106が、例えばイオン注入技法を用いてドーパントを注入することによって生成される。領域104及び106は、各自にどのような電位が印加されるかに応じて、スプリットゲート不揮発性メモリセルのソース又はドレインを形成する。スプリットゲート不揮発性メモリセルにおいては、相対的なバイアスとは無関係に、便宜上、領域104を一般にドレインと称し、領域106を一般にソースと称する。この記載は一般的なスプリットゲートアーキテクチャの概要を示すことを意図しており、実施の際には多くのもっと詳細なステップ及び層を設けて最終的なメモリセル100を形成することは理解されよう。

#### 【0024】

[0033] ここで、メモリセル100に関連する例示的な書き込み、読み取り、及び消去の動作について説明する。メモリセル100に1ビットを書き込むには、例えば5ボルトのオーダーの正電圧を領域106に印加すると共に、領域104は接地するか又は0.5ボルト等の一定のバイアスをかけ、更に基板102を接地する。例えば1.5ボルトのオーダーの低い正電圧を選択ゲート108に印加すると共に、例えば8ボルトのオーダーの高い正電圧をメモリゲート110に印加する。ソースとドレインとの間のチャネル領域内で電子が加速されると、それらの一部は充分なエネルギーを得て上方に注入され、電荷トラップ誘電体114の内部にトラップされる。これはホットエレクトロン注入として知られて

10

20

30

40

50

いる。電荷トラップ誘電体 114 の一例において、電子は電荷トラップ誘電体 114 の窒化物層内にトラップされる。この窒化物層は一般に電荷トラップ層とも呼ばれる。電荷トラップ誘電体 114 内にトラップされた電荷は、様々な供給電圧が取り除かれた後も、メモリセル 100 内に「高」ビットを記憶する。

#### 【0025】

[0034] メモリセル 100 内に記憶された電荷を「消去」し、メモリセル 100 の状態を「低」ビットに戻すには、例えば 5 ボルトのオーダーの正電圧を領域 106 に印加すると共に、領域 104 はフローティング状態にするか又は一定のバイアスをかけ、選択ゲート 108 及び基板 102 は通常、接地する。例えば -8 ボルトのオーダーの大きい負電圧をメモリゲート 110 に印加する。メモリゲート 110 と領域 106 との間のバイアス状態が、バンド間トンネルによってホールを発生させる。発生したホールは、メモリゲート 110 の下の強い電界によって充分に励起され、上方の電荷トラップ誘電体 114 内へと注入される。注入されたホールは、メモリセル 100 を「低」ビット状態に効果的に消去させる。

#### 【0026】

[0035] メモリセル 100 の記憶されたビットを「読み取る」には、選択ゲート、メモリゲート、及び領域 104 の各々に、例えばゼロから 3 ボルトの範囲内の低い電圧を印加すると共に、領域 106 及び基板 102 は通常、接地する。メモリゲートに印加される低い電圧は、「高」ビットを記憶している場合にトランジスタをオンするために必要な閾値電圧と、「低」ビットを記憶している場合にトランジスタをオンするために必要な閾値電圧との間で、実質的に等距離にあるように選択して、これら 2 つの状態間を明確に区別する。例えば、「読み取り」動作中に低い電圧を印加すると大きな電流が領域 104 及び 106 間に流れた場合、メモリセルは「低」ビットを保持しており、「読み取り」動作中に低い電圧を印加すると大きな電流が領域 104 及び 106 間に流れない場合、メモリセルは「高」ビットを保持している。

#### 【0027】

[0036] 図 2 は、半導体デバイスにおける様々な金属層に対する接続を含むメモリセル 100 を備えた例示的な回路図 200 を示す。メモリセル 100 は 1 つだけ図示するが、X 方向及び Y 方向の双方に示す円により明らかであるように、X 方向及び Y 方向の双方に延びる様々なラインによってメモリセルのアレイを接続することができる。このように、用いるビットライン (BL) 及びソースライン (SL) に基づいて、ビットの読み取り、書き込み、及び消去のために 1 つ以上のメモリセル 100 を選択することができる。

#### 【0028】

[0037] 例示的なソースライン (SL) は、X 方向に沿って延び、第 1 の金属層 (M1) に形成されている。ソースライン (SL) を用いて、X 方向に延出する行に沿った各メモリセル 100 のドープ領域 106 との電気的接続を行うことができる。

#### 【0029】

[0038] 例示的なビットライン (BL) は、Y 方向に沿って延び、第 2 の金属層 (M2) に形成されている。ビットライン (BL) を用いて、Y 方向に延出する列に沿った各メモリセル 100 のドープ領域 104 との電気的接続を行うことができる。

#### 【0030】

[0039] 図 2 に示す回路接続は単なる例示であり、図示するものとは異なる金属層において様々な接続を行い得ることは理解されよう。更に、図示しないが、メモリセル 100 は、多数の積層した層内に形成されるように Z 方向に配列することも可能である。

#### 【0031】

[0040] 図 3 は、同一の基板 102 にメモリ回路 302 及び周辺回路 304 の双方を含む例示的な半導体デバイス 300 を示す。この例では、基板 102 はコア領域 302 及び周辺領域 304 を含む。コア領域 302 は、前述のものと同様に動作することができる複数のメモリセル 100 を含む。図 3 の断面図は単なる例示であり、コア領域 302 及び周辺領域 304 は基板 102 のいずれのエリアにも位置付けることができると共に、様々な異

10

20

30

40

50

なる領域から構成され得ることは理解されよう。更に、コア領域 302 及び周辺領域 304 は、基板 102 の概ね同一の領域に存在することができる。

### 【0032】

[0041] 基板 302、及び、この記載全体を通して一般に用いるような基板は、様々な実施形態に従って、シリコンとすることができます。しかしながら基板 302 は、ゲルマニウム、ガリウムヒ素、リン化インジウム等の幅広い半導体材料のいずれかとすればよい。他の実施形態では、基板 302 は、ガラス又はサファイアウェーハのように非導電性である場合がある。

### 【0033】

[0042] 周辺領域 304 は、トランジスタだけでなく、抵抗器、コンデンサ、インダクタ等の集積回路コンポーネントを含むことができる。図示する実施形態において、周辺領域 304 は、複数の高電圧トランジスタ 306 及び低電圧トランジスタ 308 を含む。一例において、高電圧トランジスタ 306 は、低電圧トランジスタ 308 とは別個の基板 102 の領域内に存在する。高電圧トランジスタ 306 は、例えば 20 ボルトまでの大きさの電圧に対応することができる。一方、低電圧トランジスタ 308 は、高電圧トランジスタ 306 に比べて高速で動作するが、同程度の高電圧で動作することはできない。一実施形態において、低電圧トランジスタ 308 は、高電圧トランジスタ 306 よりも短いゲート長を有するように設計されている。高電圧トランジスタ 306 は一般に、低電圧トランジスタ 308 のゲート誘電体よりも厚いゲート誘電体 310 を有するものとして特徴付けられる。図 3 に示すように、低電圧トランジスタ 308 は高電圧トランジスタ 306 よりも幅が狭いが、これは必須ではない。いくつかの実施形態によれば、低電圧トランジスタ 308 の方が高電圧トランジスタ 306 よりも幅が広い場合があり、あるいは、低電圧トランジスタ 308 及び高電圧トランジスタ 306 が同一の幅を有する場合もある。10 20

### 【0034】

[0043] 本明細書における説明中、電界効果デバイスが製造される基板の様々な領域について言及する。例えば図 3 を参照して、コア領域 302 及び周辺領域 304 について記載した。これらの領域は基板上のどこにでも存在することができ、更に、これらの領域は相互に排他的でない場合があることは理解されよう。すなわち、いくつかの実施形態において、1つ以上の領域の部分どうしが重複することがある。本明細書では3つまでの異なる領域について記載するが、いかなる数の領域も基板上に存在することができ、特定のタイプのデバイス又は材料を有するエリアを指定することは理解されよう。一般に、これらの領域は、同様のデバイスを含む基板のエリアを便利に記載するために用いられるが、記載する実施形態の範囲又は精神を限定するものではない。30

### 【0035】

[0044] 図 4 は、本発明の実施形態による半導体デバイス 402 の機能ブロック図である。図示のように、半導体デバイス 402 は、不揮発性メモリアレイ 404、高電圧制御論理 406、及び低電圧制御論理 408 を含む。様々な実施形態によれば、メモリアレイ 404 は多数のメモリセル 100 を備えることができ、半導体デバイス 402 のコア領域 302 に物理的に位置付けることができる。高電圧制御論理 406 は、多数の高電圧トランジスタ 306 を備えることができ、これらを用いてメモリアレイ 404 の部分の制御及び / 又は駆動を行うことができる。更に、高電圧制御論理 406 は、半導体デバイス 402 の周辺領域 304 に物理的に位置付けることができる。高電圧制御論理 406 と同様に、低電圧制御論理 408 は、多数の低電圧トランジスタ 308 を備えることができ、これらを用いてメモリアレイ 404 の部分の制御及び / 又は駆動を行うことができる。低電圧制御論理 408 も、半導体デバイスの周辺領域 304 に位置付けることができる。様々な実施形態によれば、高電圧制御論理 406 及び低電圧制御論理 408 は、周辺領域 304 の異なる部分に位置付けられている。更に、低電圧制御論理 408 は、半導体デバイス 402 の動作を制御するためにマイクロコントローラ及びアナログ回路を含むことができる。40

### 【0036】

[0045] 図 5A から図 5J は、本発明の実施形態による、半導体デバイス 500 の製造中50

の様々な時点における断面を示す。図 5 A は、いくつかの初期フィーチャを形成した後の半導体デバイス 500 を示す。図 5 A に示すように、デバイス 500 は、いくつかの領域に分割された基板層 502 を備えている。

#### 【0037】

[0046] 基板の第 1 の領域又はメモリ領域 504 は、メモリコンポーネントのために使用可能である。様々な実施形態によれば、第 1 の領域 504 は、複数のメモリセル 100 を形成することができるメモリコア領域を備えている。例えば、いくつかの実施形態によれば、第 1 の領域を用いて、多数の選択ゲート 108 / メモリゲート 110 の対を形成することができる。

#### 【0038】

[0047] 様々な実施形態に従って、第 2 及び第 3 の領域 506 及び 508 を含む周辺領域に、論理及び / 又は制御回路を形成することができる。第 2 の領域 506 は高電圧制御論理領域 406 を備えることができ、第 3 の領域 508 は低電圧制御論理領域 408 を備えることができる。

#### 【0039】

[0048] 図 5 A に示すように、第 1 の領域 504 にゲート誘電体 510a が形成され（例えば堆積され）、第 2 の領域 506 及び第 3 の領域 508 にゲート誘電体 510b が配置されている。様々な実施形態によれば、ゲート誘電体 510a 及び 510b は異なる厚さとすることができるが、これは必須ではない。ゲート誘電体 510a 及び 510b は、いずれかの周知の方法によって形成可能である。例えば、誘電体 510a 及び 510b は、20 基板 502 上に成長させることができる。第 1 の領域 504 の誘電体 510a は、第 2 及び第 3 の領域 506 及び 508 に配置された誘電体 510b とは独立して形成することができる。しかしながら、ゲート誘電体 510a 及び 510b は、基板上に配置して、基板 502 とは異なる材料の酸化物、又は基板 502 と同一の材料の酸化物を含むことも可能である。更に、様々な実施形態に従って、誘電体 510a 及び 510b は、同一の材料又は異なる材料を含むことができ、同時に又は異なる時点で形成することができる。

#### 【0040】

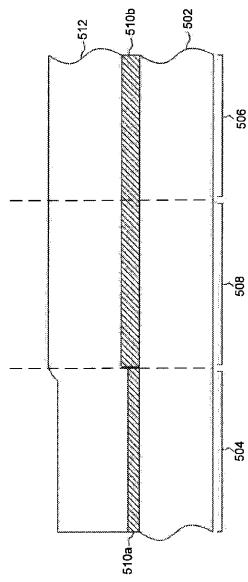

[0049] 図 5 B は、ゲート導体 512 の層を配置した後のデバイス 500 の断面を示す。ゲート導体 512 は、例えばポリ（多結晶）等のいずれかの適切な導体を含むことができる。図 5 B に示すように、ゲート導体 512 は、第 1 の領域 504 のゲート誘電体 510a の上に、並びに第 2 の領域 506 及び第 3 の領域 508 のゲート誘電体 510b の上に配置されている。

#### 【0041】

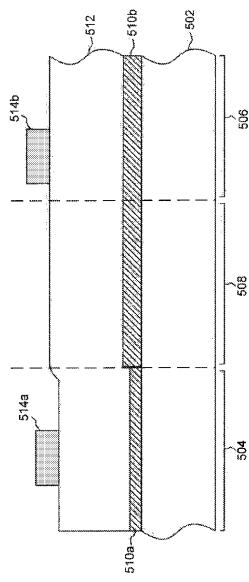

[0050] 図 5 C では、第 1 の領域 504 に配置されたゲート導体層 512 の一部の上で、マスク 514a が基板に適用されている。同様に、第 2 の領域 506 に配置されたゲート導体層 512 の一部の上に、マスク 514b が配置されている。第 3 の領域にはマスクが配置されていない。様々な実施形態によれば、マスク 514a 及び 514b を用いて、第 1 の領域 504 に選択ゲートを形成し、第 2 の領域 506 にトランジスタゲートを形成する。マスク 514a 及び 514b は、ゲート導体層 512 のマスクで覆われていない部分の選択的な除去（例えばエッチング）を可能とするいずれかの適切な材料を含むことができる。いくつかの実施形態によれば、マスキング構造は、ポリ（メチルメタクリレート）（PMMA）、ポリ（メチルグルタルイミド）（PMGI）、フェノールホルムアルデヒド樹脂、適切なエポキシ等のフォトレジストを含み得る。

#### 【0042】

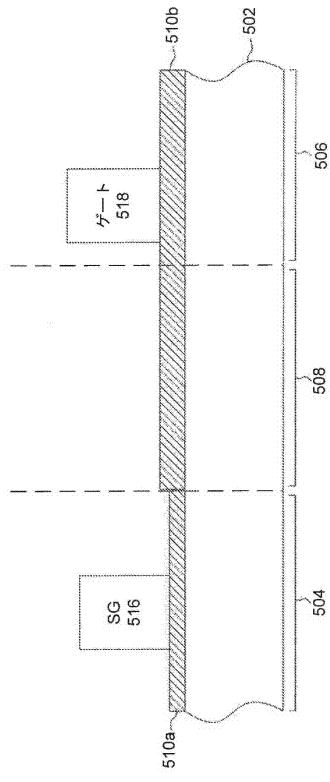

[0051] 図 5 D は、ゲート導体層 512 のマスクで覆われていない部分をマスク 514a 及び 514b と共に除去した後のデバイス 500 の断面を示す。図 5 D に見られるように、ゲート誘電体 510a の上の第 1 の領域 504 に選択ゲート 516 が形成されている。更に、ゲート誘電体 506 の上の第 2 の領域 506 に第 2 のゲート 518 が形成されている。様々な実施形態によれば、ゲート導体層 512 は、エッチング等のいずれかの適切な方法によって除去することができる。様々な実施形態によれば、ゲート導体層 512 の除

10

20

30

40

50

去部分は、周知のエッティング方法を用いて除去される。例えばゲート導体層 512 は、C<sub>12</sub>、KOH、TMAH（テトラ-メチル-アミノ-ヒドロキシル）を用いて、又は、例えばH<sub>2</sub>、HCl、O<sub>2</sub>、H<sub>2</sub>O（蒸気又は気体）、O<sub>3</sub>、HF、F<sub>2</sub>、並びにCl<sub>2</sub>及びXeF<sub>2</sub>を用いた炭素-フッ化物化合物による気相エッティングを用いて、エッティングすることができる。更に、いくつかの実施形態によれば、エッティング製品の組み合わせを用いることも可能である。

#### 【0043】

[0052] 図5Eは、様々な実施形態に従った、いくつかの追加の構造を形成した後のデバイス500の断面を示す。図5Eに示すように、まず、第1の領域においてSG516によって覆われていない誘電体510aの部分を除去し、デバイス500全体の上に電荷トラップ誘電体522を堆積した。様々な実施形態によれば、電荷トラップ誘電体は、上述のようなONO等の誘電体の1つ以上の層を含む。例えば電荷トラップ誘電体522は、第1の誘電層522a、窒化物層522b、及び第2の誘電層522cを含むことができる。様々な実施形態によれば、第1の誘電層522a及び第2の誘電層522cは、酸化物等のいずれかの適切な誘電体を含むことができる。電荷トラップ誘電体522は、その特定の組成とは無関係に、窒化物層522b等の少なくとも1つの電荷トラップ層を含むことが好ましい。電荷トラップ層は、窒化物、シリコンリッチ窒化物で形成することができ、いくつかの実施形態によれば、異なる窒化物から成る多数の層を含むことができる。また、第1の領域504及び第2の領域506を覆うようにマスキング層520が形成されている。第3の領域508における電荷トラップ誘電体522及び誘電体510bは、エッチ方法によって除去した。最後に、マスキング層520を除去した後、第3の領域508において基板502の部分の上にゲート誘電体510cが形成される。

10

20

#### 【0044】

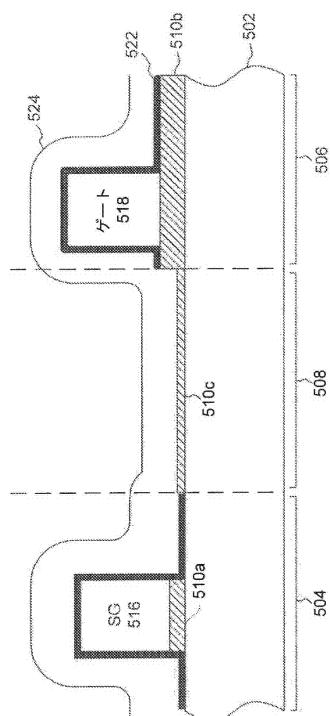

[0053] 図5Fは、製造プロセスの後半の段階におけるデバイス500の断面を示す。図5Fに示すように、デバイス500の3つの領域505、506、及び508の全てに第2のゲート導体層524が配置されている。いくつかの実施形態によれば、第2のゲート導体層524は、これより前に配置したゲート導体層512より薄い。更に、第2のゲート導体層524は、デバイス500と実質的にコンフォーマルとなる（conformal）ように配置することができる。

30

#### 【0045】

[0054] 図5Gは、様々な実施形態に従った製造プロセスの後半の段階におけるデバイス500の断面を示す。図5Gに示すように、第3の領域508に配置された第2のゲート導体層524の一部の上に、マスク536が配置されている。第1の領域504及び第2の領域506に配置された第2のゲート導体524の部分は、マスクで覆われないままである。

40

#### 【0046】

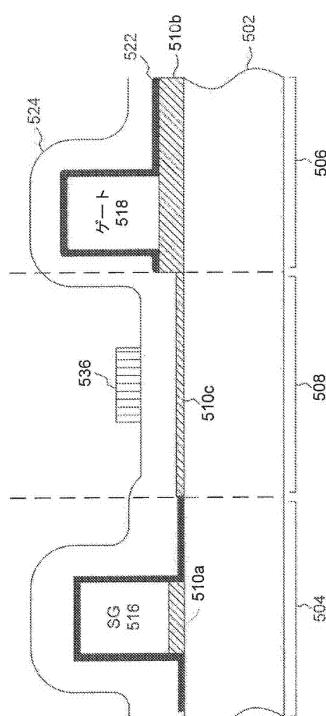

[0055] 図5Hは、第2のゲート導体層の一部が例えエッティングによって除去された後のデバイス500の断面を示す。図示のように、第2のゲート導体層524の除去によって、第3の領域508における誘電体510cの上にゲート526が形成されている。更に、選択ゲート516及びゲート518の側壁には、第2のゲート導体層524の一部528が配置されたままである。様々な実施形態によれば、部分528の一部は、第1の領域504においてメモリセル100のメモリゲートとして用いられる。

40

#### 【0047】

[0056] 図5Iは、生成プロセスの後半の段階におけるデバイス500の断面を示す。図5Iに示すように、選択ゲート516の右側の側壁に配置された部分528は、第1の領域504に配置されたメモリセル100のメモリゲートとして用いられる。このため、メモリゲート528は、第2のゲート導体から形成されたゲート526を含む第3の領域508の一部と共に、マスク530によって覆われている。このマスキングによって、（参照番号534によって示されるような）選択ゲート516の左側から、及びゲート518の側壁から、第2のゲート導体524を更に除去することができる。

50

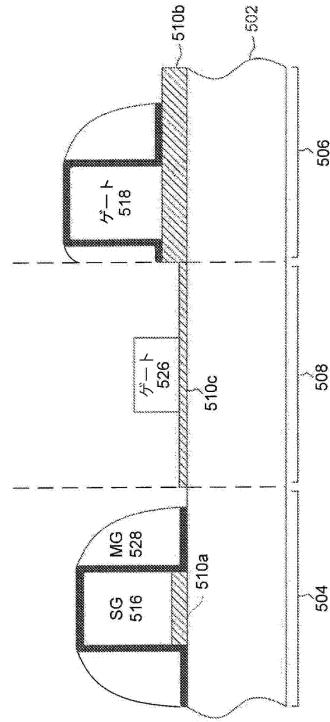

**【0048】**

[0057] 図5Jは、様々な実施形態によるデバイス500の断面を示す。図5Jに示すように、選択ゲート516の左側の側壁から、及びゲート518の双方の側壁から、第2のゲート導体524の残り部分528が除去（例えばエッチング）されている。更に、電荷トラップ誘電体522は、基板502及び選択ゲート516からメモリゲート528を分離するデバイスの部分を除いて、デバイスの全ての部分から除去されている。

**【0049】**

[0058] 図5Jに見られるように、デバイス500は、選択ゲート516、メモリゲート528、及び電荷トラップ誘電体を含むスプリットゲート不揮発性メモリセル532を含んでいる。先に説明したように、電荷トラップ誘電体はいくつかの誘電層を含むことができる。例えば電荷トラップ誘電体は、様々な実施形態によれば、2つの誘電層の間に挟まれた窒化物層を含むことができる。そのような状況においては、窒化物層が電荷トラップ層として機能することができる。すなわち、窒化物層は、メモリセルの値を記憶するため誘電体内に電荷をトラップするように機能することができる。

10

**【0050】**

[0059] ゲート526及びメモリゲート528は、同一のゲート導体層、すなわちこの場合は第2のゲート導体層524から形成されているので、様々な実施形態によれば、ゲート526の高さh1は、メモリゲート528の基部における幅w1と実質的に同一である。更に、選択ゲート516及びゲート518は同一のゲート導体層510から形成されているので、様々な実施形態によれば、それらは実質的に同じ高さh2を有し得る。ゲート導体層512及びゲート導体層524は異なる時点で堆積されたので、h1及びh2の厚さは同じであるか又は異なる場合がある。更に、各ゲート導体層512及び524は、単一のゲート導体堆積によって別々に形成される。

20

**【0051】**

[0060] いくつかの実施形態によれば、図5Fに示したプロセスステップに続いて、図5Gに示したプロセスステップに対する代替的なステップを実行することができる。この代替的な「ハードマスク」について、図6Aから図6Dを参照して説明する。図6Aは、図5Fを参照して説明したステップを実行した後のデバイス500を示す。更に、ゲート導体層524の上に第1のハードマスク層542が形成されている。第1のハードマスク層542の上に第2のハードマスク層544を形成することができる。ハード第1の及び第2のハードマスク層542及び544を、まとめて「ハードマスクスタック」と呼ぶことができる。第3の領域508を覆うようにマスク546が形成されている。図6Aに示すように、マスク546は第3の領域全体を覆っているが、これは必須ではない。

30

**【0052】**

[0061] 図6Bに、マスク546によって覆われなかった第2のハードマスク544の部分が例えばエッチングによって除去された後の、デバイス500の断面を示す。

**【0053】**

[0062] 図6Cは、マスク層546を除去した後のデバイス500の断面を示す。更に、第1及び第2の領域504及び506にあったハードマスクスタック542及び544の部分は除去されている。すなわち、ハードマスクスタック542及び544は第3の領域508にのみ残っている。

40

**【0054】**

[0063] 図6Dは、第3の領域508において残りのハードマスクスタック542及び544の上にマスク536を形成した後のデバイス500の断面を示す。第1の領域504及び第2の領域506に配置されている第2のゲート導体524の部分は、マスクで覆われていないままであり、図5Hに示す後のステップで除去することができる。

**【0055】**

[0064] 図7は、本発明の様々な実施形態に従って半導体デバイス500を製造する方法700を示すフローチャートである。理解を容易にするため、方法700について、図5Aから図5Jを同時に参照して説明する。しかしながら、方法600が図5Aから図5J

50

に示した実施形態に限定されることは理解されよう。

#### 【0056】

[0065] 図7に示すように、ステップ702においてゲート誘電体を形成する。様々な実施形態によれば、半導体デバイス500の全表面の上にゲート誘電体510bを形成する。マスキング及びエッチステップを実行して、第1の領域504からゲート誘電体510bを除去し、続いて第1の領域504にゲート誘電体成長510aを行う。このステップにおいて、第2の領域506及び第3の領域508は双方ともゲート誘電体510bを有するが、第1の領域504はゲート誘電体510aを有する。更に、各領域に形成されたゲート誘電体は、同一又は異なるものとすることができます。例えば、いくつかの実施形態によれば、第1の領域504に形成されたゲート誘電体510aは、ゲート誘電体510bより薄くすることができる。しかしながら、3つの領域504、506、及び508の全てを通して均一なゲート誘電体を形成することも可能である。10

#### 【0057】

[0066] ステップ704において、半導体デバイス500上にゲート導体512の第1の層を配置する。上記のように、ゲート導体512の第1の層は、堆積等のいずれかの適切な方法を用いて配置すればよい。いくつかの実施形態によれば、ゲート導体層512は、すでに形成されている構造を覆うようにコンフォーマルに配置することができる。例えばゲート導体層512は、第1の領域504のゲート誘電体510aの上に、並びに第2の領域506及び第3の領域508の510bの上に、コンフォーマルに配置することができる。20

#### 【0058】

[0067] ステップ706において、第1のゲート導体層512から選択ゲート516及び論理ゲート518を画定する。様々な実施形態によれば、これは、第1の領域504において第1のゲート導体層512の上にマスク514aを形成し、第1のゲート導体層512の上にマスク514bを形成することによって達成可能である。マスク514a及び514bを用いて、第1のゲート導体層512をマスクで覆った通りに、選択ゲート及び論理ゲートをそれぞれ画定することができる。

#### 【0059】

[0068] ステップ708において、デバイス500の上に電荷トラップ誘電体522を形成する。様々な実施形態によれば、電荷トラップ誘電体は、デバイス500の3つの領域504、506、及び508の全ての上に形成することができる。更に、電荷トラップ誘電体は1つ以上の誘電層で形成することができる。例えば電荷トラップ誘電体522は、第1の誘電層522a、窒化物層522b、及び第2の誘電層522cを含むことができる。電荷トラップ誘電体522は、その特定の組成には無関係に、窒化物層522b等の少なくとも1つの電荷トラップ層を含むことが好ましい。電荷トラップ層は、窒化物、シリコンリッチ窒化物から形成することができ、いくつかの実施形態によれば、異なる窒化物から成る多数の層を含むことができる。電荷トラップ誘電体522を形成する前に、第1の領域から、選択ゲート516で覆われていないままである誘電体510aの部分を除去することができる。30

#### 【0060】

[0069] ステップ710において、3つの領域504、506、及び508の全てに、例えば堆積によって第2のゲート導体層524を配置することができる。第2のゲート導体層524は、第1のゲート導体層512より薄くすることができる。次いでステップ712において、第2のゲート導体層524を除去（例えばエッティング）して、第3の領域508に第2の論理ゲート526を画定することができる。更に、第2のゲート導体層524からメモリゲート528を画定することができる。好ましくは、メモリゲート526は選択ゲート516の側壁に形成され、電荷トラップ誘電体522によって選択ゲート516から分離されている。更に、メモリゲート526は、電荷トラップ誘電体522によって基板502から分離されている。選択ゲート516、電荷トラップ誘電体、及びメモリゲート526が、共にスプリットゲート不揮発性メモリセル532を形成する。更に、メ4050

モリゲート 528 及び論理ゲート 526 は同一のゲート導体 524 の層から形成されたので、ゲート 526 の高さは、メモリゲート 528 の基部における幅と実質的に同一である。同様に、選択ゲート 516 及びゲート 518 は同一のゲート導体 512 の層から形成されたので、様々な実施形態によれば、それらは実質的に同じ高さを有する。また、ステップ 610 は、第 1 及び第 2 の領域を覆い、第 3 の領域から電荷トラップ誘電層 522 及びゲート誘電体 510b を除去するために、マスキング及びエッチステップを含むことができる。

#### 【0061】

[0070] 図 8 は、本発明の様々な実施形態による半導体デバイス 500 を製造する方法 800 を示すフローチャートである。方法 700 の説明と同様に、理解を容易にするため、方法 800 について、図 5A から図 5J を同時に参照して説明する。しかしながら、方法 800 が図 5A から図 5J に示した実施形態に限定されないことは理解されよう。

10

#### 【0062】

[0071] 図 8 に示すように、ステップ 802 において、半導体デバイス 500 の全表面の上にゲート誘電体 510b を形成する。マスキング及びエッチステップを実行して、第 1 の領域 504 からゲート誘電体 510b を除去し、続いて第 1 の領域 504 にゲート誘電体成長 510a を行う。このステップにおいて、第 2 の領域 506 及び第 3 の領域 508 は双方ともゲート誘電体 510b を有するが、第 1 の領域 504 はゲート誘電体 510a を有する。更に、各領域において形成されたゲート誘電体は、同一又は異なるものとすることができる。例えば、いくつかの実施形態によれば、第 1 の領域 504 に形成されたゲート誘電体 510a は、ゲート誘電体 510b より薄くすることができる。しかしながら、3 つの領域 504、506、及び 508 の全てを通して均一なゲート誘電体を形成することも可能である。

20

#### 【0063】

[0072] ステップ 804 において、半導体デバイス 500 上にゲート導体 512 の第 1 の層を配置する。上記のように、ゲート導体 512 の第 1 の層は、堆積等のいずれかの適切な方法を用いて配置すればよい。いくつかの実施形態によれば、ゲート導体層 512 は、すでに形成されている構造を覆うようにコンフォーマルに配置することができる。例えばゲート導体層 512 は、第 1 の領域 504 のゲート誘電体 510a の上に、並びに第 2 の領域 506 及び第 3 の領域 508 の 510b の上に、コンフォーマルに配置することができる。

30

#### 【0064】

[0073] ステップ 806 において、第 1 のゲート導体層 512 から選択ゲート 516 及び論理ゲート 518 を画定する。様々な実施形態によれば、これは、第 1 の領域 504 において第 1 のゲート導体層 512 の上にマスク 514a を形成し、第 1 のゲート導体層 512 の上にマスク 514b を形成することによって達成可能である。マスク 514a 及び 514b を用いて、第 1 のゲート導体層 512 をマスクで覆った通りに、選択ゲート及び論理ゲートをそれぞれ画定することができる。

#### 【0065】

[0074] ステップ 808 において、デバイス 500 の上に電荷トラップ誘電体 522 を形成する。様々な実施形態によれば、電荷トラップ誘電体は、デバイス 500 の 3 つの領域 504、506、及び 508 の全ての上に形成することができる。更に、電荷トラップ誘電体は 1 つ以上の誘電層で形成することができる。例えば電荷トラップ誘電体 522 は、第 1 の誘電層 522a、窒化物層 522b、及び第 2 の誘電層 522c を含むことができる。電荷トラップ誘電体 522 は、その特定の組成には無関係に、窒化物層 522b 等の少なくとも 1 つの電荷トラップ層を含むことが好ましい。電荷トラップ層は、窒化物、シリコンリッチ窒化物から形成することができ、いくつかの実施形態によれば、異なる窒化物から成る多数の層を含むことができる。電荷トラップ誘電体 522 を形成する前に、第 1 の領域から、選択ゲート 516 で覆われていないままである誘電体 510a の部分を除去することができる。

40

50

## 【0066】

[0075] ステップ810において、第3の領域508から電荷トラップ誘電体522を除去することができる。様々な実施形態によれば、除去される電荷トラップ誘電体522の部分は、マスキング及びエッチングによって第1及び第2の領域504及び508を覆うと共に第3の領域508から電荷トラップ誘電体522及びゲート誘電体510cを除去することによって、除去することができる。

## 【0067】

[0076] ステップ812において、3つの領域504、506、及び508の全てに、例えば堆積によって第2のゲート導体層524を配置することができる。第2のゲート導体層524は、第1のゲート導体層512より薄くすることができる。

10

## 【0068】

[0077] ステップ814において、ハードマスクを用いて第3の領域508を保護することができる。ハードマスクは、アモルファス炭素、SiN、SiON、SiO<sub>2</sub>、又はそれらの何らかの組み合わせ等、いずれかの適切な材料又は材料の組み合わせを含み得る。一例として、図6Aから図6Dに示すように、ゲート導体層542全体に第1のハードマスク層524としてのアモルファス炭素を堆積し、続いて第2のハードマスク層544としてSiONを堆積する。マスキングステップ546を用いて第3の領域を覆い、第1及び第2の領域504及び506におけるSiON544を除去する。第3の領域におけるSiON544をマスクとして用いて、第3の領域におけるアモルファス炭素542を保護すると共に、第1及び第2の領域におけるアモルファス炭素542をエッチングする。また、第1及び第2の領域におけるマスク542の除去中に、マスキング層546も除去する。このステップでは、第3の領域におけるアモルファス炭素542及びSiON544のみが残される。

20

## 【0069】

[0078] ステップ816において、第2のゲート導体層524を除去（例えばエッチング）し、マスキング層536を用いることによって第3の領域508に第2の論理ゲート526を画定することができる。更に、第2のゲート導体層524からメモリゲート528を画定することができる。好ましくは、メモリゲート528は選択ゲート516の側壁に形成され、電荷トラップ誘電体522によって選択ゲート516から分離されている。更に、メモリゲート528は、電荷トラップ誘電体522によって基板502から分離されている。選択ゲート516、電荷トラップ誘電体、及びメモリゲート528が、共にスプリットゲート不揮発性メモリセル532を形成する。更に、メモリゲート528及び論理ゲート526は同一のゲート導体524の層から形成されたので、ゲート526の高さは、メモリゲート528の基部における幅と実質的に同一である。同様に、選択ゲート516及びゲート518は同一のゲート導体512の層から形成されたので、様々な実施形態によれば、それらは実質的に同じ高さを有する。

30

## 【0070】

[0079] 図9は、様々な実施形態による半導体デバイス500を製造する方法900を示すフローチャートである。方法900について図6Aから図6Dを参照して説明する。図9に示すように、ステップ902において、ゲート導体層524の上に第1のハードマスク層542を形成することができる。ステップ904において、第2のハードマスク層544を形成することができる。ステップ906において、第3の領域508をマスク546で覆う。図6Aに示すように、マスク546は第3の領域の全体を覆っているが、これは必須ではない。

40

## 【0071】

[0080] ステップ908において、例えばエッチングによって、マスク546により覆われていない第2のハードマスク544の部分を除去する。続いてエッチングステップを適用して、第3の領域に残っているハードマスク544を用いることにより、第1及び第2の領域から第1のハードマスク542の部分を除去することができる。第1及び第2の領域における542の除去と同じステップにおいて又はそれより前に、マスク層546も除

50

去する。このステップでは、第3の領域のみにマスク542及び544が残っている。

【0072】

[0081] ステップ910において、第3の領域508に残っているハードマスク層542及び544の上に、論理ゲートマスク536を形成する。第1の領域504及び第2の領域506に配置された第2のゲート導体524の部分は、マスクで覆われないままであり、例えば図5Hに示す後のステップで除去することができる。

【0073】

[0082] 図10は、本発明の様々な実施形態による半導体デバイス500を製造する方法1000を示すフローチャートである。方法700及び800の説明と同様に、理解を容易にするため、方法1000について、図5Aから図5Jを同時に参照して説明する。しかしながら、方法1000が図5Aから図5Jに示した実施形態に限定されないことは理解されよう。

10

【0074】

[0083] 図10に示すように、ステップ1002においてゲート誘電体を形成する。様々な実施形態に従って、半導体デバイス500の全表面の上にゲート誘電体510bを形成する。マスキング及びエッチステップを実行して、第1の領域504からゲート誘電体510bを除去し、続いて第1の領域504にゲート誘電体成長510aを行う。このステップにおいて、第2の領域506及び第3の領域508は双方ともゲート誘電体510bを有するが、第1の領域504はゲート誘電体510aを有する。例えば、ゲート誘電体510aを半導体デバイス500の第1の領域504に形成し、ゲート誘電体510bを半導体デバイス500の第2の領域506に形成し、半導体デバイスの第3の領域508にはゲート誘電体を形成しないようにすることができる。しかしながら、いくつかの実施形態によれば、第1の領域504、第2の領域506、及び第3の領域508の全てにゲート誘電体を形成してもよい。

20

【0075】

[0084] ステップ1004において、半導体デバイス500上にゲート導体512の第1の層を配置する。上記のように、ゲート導体512の第1の層は、堆積等のいずれかの適切な方法を用いて配置すればよい。いくつかの実施形態によれば、ゲート導体層512は、すでに形成されている構造を覆うようにコンフォーマルに配置することができる。例えばゲート導体層512は、第1の領域504のゲート誘電体510aの上に、及び第2の領域506の510bの上に、コンフォーマルに配置することができる。第3の領域508にゲート誘電体を形成していない場合、第3の領域508では基板502の上に直接ゲート導体層512を配置することができる。しかしながら、第3の領域508にゲート誘電体510cが形成されている場合は、ゲート誘電体510cの上にゲート導体層512を配置する。

30

【0076】

[0085] ステップ1006において、第1のゲート導体層512から選択ゲート516及び論理ゲート518を画定する。様々な実施形態によれば、これは、第1の領域504において第1のゲート導体層512の上にマスク514aを形成し、第1のゲート導体層512の上にマスク514bを形成することによって達成可能である。マスク514a及び514bを用いて、第1のゲート導体層512をマスクで覆った通りに、選択ゲート及び論理ゲートをそれぞれ画定することができる。

40

【0077】

[0086] ステップ1008において、デバイス500の上に電荷トラップ誘電体522を形成する。様々な実施形態によれば、電荷トラップ誘電体は、デバイス500の3つの領域504、506、及び508の全ての上に形成することができる。更に、電荷トラップ誘電体は1つ以上の誘電層で形成することができる。例えば電荷トラップ誘電体522は、第1の誘電層522a、窒化物層522b、及び第2の誘電層522cを含むことができる。電荷トラップ誘電体522は、その特定の組成には無関係に、窒化物層522b等の少なくとも1つの電荷トラップ層を含むことが好ましい。電荷トラップ層は、窒化物、

50

シリコンリッチ窒化物から形成することができ、いくつかの実施形態によれば、異なる窒化物から成る多数の層を含むことができる。電荷トラップ誘電体522を形成する前に、第1の領域から、選択ゲート516で覆われていないままである誘電体510aの部分を除去することができる。

#### 【0078】

[0087] ステップ1010において、第3の領域508から電荷トラップ誘電体522を除去することができる。様々な実施形態によれば、除去される電荷トラップ誘電体522の部分は、マスキング及びエッチングによって第1及び第2の領域504及び508を覆うと共に第3の領域508から電荷トラップ誘電体522及びゲート誘電体510cを除去することによって、除去することができる。10

#### 【0079】

[0088] ステップ1012において、3つの領域504、506、及び508の全てに、例えば堆積によって第2のゲート導体層524を配置することができる。第2のゲート導体層524は、第1のゲート導体層512より薄くすることができる。

#### 【0080】

[0089] ステップ1014において、ハードマスクスタックを用いて第3の領域508を保護することができる。ハードマスクは、アモルファス炭素、SiN、SiON、SiO<sub>2</sub>、又はそれらの何らかの組み合わせ等、いずれかの適切な材料又は材料の組み合わせを含み得る。一例として、図6Aから図6Dに示すように、第2のゲート導体層524の全体に第1のハードマスク層542としてのSiNを堆積し、続いて第2のハードマスク層544としてSiO<sub>2</sub>を堆積する。マスキングステップ546を用いて第3の領域を覆い、第1及び第2の領域におけるSiO<sub>2</sub>544を除去する。マスク層546を除去した後、第3の領域に残っているハードマスク544を用いて覆うことによって、第1及び第2の領域504及び506のハードマスク542を除去することができる。このステップでは、ハードマスク542及び544のみが第3の領域にのみ残っている。20

#### 【0081】

[0090] ステップ1016において、第2のゲート導体層524を除去（例えばエッチング）して、第3の領域508に第2の論理ゲート526を画定することができる。実施形態によれば、第2の論理ゲート526は、第3の領域508に残っているハードマスク層542及び544の上に論理ゲートマスク536を形成することによって画定される。更に、第2のゲート導体層524からメモリゲート528を画定することができる。好ましくは、メモリゲート526は選択ゲート516の側壁に形成され、電荷トラップ誘電体522によって選択ゲート516から分離されている。更に、メモリゲート526は、電荷トラップ誘電体522によって基板503から分離されている。選択ゲート516、電荷トラップ誘電体、及びメモリゲート526が、共にスプリットゲート不揮発性メモリセル532を形成する。更に、メモリゲート528及び論理ゲート526は同一のゲート導体524の層から形成されたので、ゲート526の高さは、メモリゲート528の基部における幅と実質的に同一である。同様に、選択ゲート516及びゲート518は同一のゲート導体512の層から形成されたので、様々な実施形態によれば、それらは実質的に同じ高さを有する。30

#### 【0082】

[0091] 特許請求の範囲を解釈するために、「発明の概要」のセクション及び要約書でなく「発明を実施するための形態」のセクションの使用が意図されることには認められよう。「発明の概要」のセクション及び要約書では、本発明者らによって想定されるような本発明の例示的な実施形態の全てではないが1つ以上を記載することができ、従って、本発明及び添付の特許請求の範囲をいかなる点でも限定することは意図されない。40

#### 【0083】

[0092] 本発明の実施形態について、指定された機能及びそれらの関係の実施を示す機能的構成要素を利用して上述した。これらの機能的構成要素の境界は、説明の都合上、本明細書において任意に規定している。指定された機能及びそれらの関係が適切に実行される50

限り、代替的な境界を規定することも可能である。

**【0084】**

[0093] 前述の特定の実施形態についての記載は、本発明の全体的な実体を充分に明らかにし、他の者は、当業者の知識を適用することで、過度な実験を行うことなく、本発明の全体的な概念から逸脱することなく、そのような特定の実施形態を様々な用途のために容易に変更及び／又は適合させることができる。従って、そのような適合及び変形は、本明細書に提示する教示及び指導に基づき、開示する実施形態の均等物の意味及び範囲内にあることが意図される。本明細書における用語又は術語は、限定でなく記述の目的のためのものであるので、本明細書の用語又は術語が、教示及び指導に照らし合わせて当業者によつて解釈されることを理解されよう。

10

**【0085】**

[0094] 本発明の範囲は、上述の例示的な実施形態のいずれによつても限定されず、以下の特許請求の範囲及びそれらの均等物によってのみ規定されるものとする。

**【図1】**

FIG. 1

**【図3】**

**【図2】**

FIG. 2

【図4】

【図5A】

FIG. 5A

【図5B】

FIG. 5B

【図5C】

FIG. 5C

500

【図5D】

500

【図5E】

【図5F】

500

【図5G】

500

【図5H】

500

【図5I】

【図5J】

500

【図6A】

【図 6 B】

500

【図 6 C】

500

【図 6 D】

500

【図 7】

【図8】

【図9】

【図10】

---

フロントページの続き

(72)発明者 チャン , クオ トゥン

アメリカ合衆国 , カリフォルニア州 95070 , サラトガ , カントリー スクワイア レーン

12261

(72)発明者 チェン , チュン

アメリカ合衆国 , カリフォルニア州 95135 , サン ノゼ , キャマリロ コート 3232

(72)発明者 ファン , シエンチン

アメリカ合衆国 , カリフォルニア州 94539 , フリーモント , ナンザ コート 43740

合議体

審判長 加藤 浩一

審判官 深沢 正志

審判官 河合 俊英

(56)参考文献 特開2010-205791(JP,A)

特開2011-014920(JP,A)

米国特許出願公開第2012/0248523(US,A1)

米国特許出願公開第2006/0118857(US,A1)

(58)調査した分野(Int.Cl. , DB名)

H01L21/8247

H01L27/115

H01L21/336

H01L29/788

H01L29/792

H01L27/10