(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0086239

(43) 공개일자 2012년08월02일

(51) 국제특허분류(Int. Cl.)

*G11C 16/06* (2006.01) *G11C 29/42* (2006.01)

*G06F 11/10* (2006.01)

(21) 출원번호 10-2011-0138192

(22) 출원일자 2011년12월20일

심사청구일자 없음

(30) 우선권주장 JP-P-2011-012544 2011년01월25일 일본(JP)

(71) 출원인

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

나카니시 켄이치

일본국 도쿄도 미나토구 코난 1-7-1 소니 주식회사

(74) 대리인

최달용

전체 청구항 수 : 총 13 항

(54) 발명의 명칭 메모리 시스템 및 그 동작 방법

### (57) 요 약

메모리 시스템은: 블록 단위로 액세스될 데이터를 저장하는데 이용되는 제 1의 불휘발성 메모리와; 워드 단위로 랜덤하게 액세스될 데이터를 저장하는데 이용되는 제 2의 불휘발성 메모리; 및 상기 제 1 및 제 2의 불휘발성 메모리의 동작을 제어하도록 구성된 제어부를 포함하고, 상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용될 에러 정정 코드가 상기 제 1의 불휘발성 메모리에 보존된다.

**대 표 도** - 도1

## 특허청구의 범위

### 청구항 1

블록 단위로 액세스될 데이터를 저장하는데 이용되는 제 1의 불휘발성 메모리와;

워드 단위로 랜덤하게 액세스될 데이터를 저장하는데 이용되는 제 2의 불휘발성 메모리; 및

상기 제 1 및 제 2의 불휘발성 메모리의 동작을 제어하도록 구성된 제어부를 포함하고,

상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용될 여러 정정 코드가 상기 제 1의 불휘발성 메모리에 보존

되는 것을 특징으로 하는 메모리 시스템.

### 청구항 2

제 1항에 있어서,

상기 제어부는, 상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용될 여러 정정 코드를 상기 제 1의 불휘발성

메모리 내로부터 판독하여 보존하여 두기 위한 버퍼 영역을 갖는 것을 특징으로 하는 메모리 시스템.

### 청구항 3

제 2항에 있어서,

상기 제어부는, 상기 여러 정정 코드를 상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용하기에 앞서, 상기

제 2의 불휘발성 메모리에 저장된 상기 데이터에 필요한 상기 여러 정정 코드가 상기 버퍼 영역에 존재하지 않

는 경우, 상기 필요한 여러 정정 코드를 이용하기 이전에, 상기 필요한 여러 정정 코드를 상기 제 1의 불휘발성

메모리로부터 상기 버퍼 영역으로 판독하는 것을 특징으로 하는 메모리 시스템.

### 청구항 4

제 3항에 있어서,

상기 필요한 정정 코드를 상기 버퍼 영역으로 판독하기 이전에, 상기 제어부는 상기 버퍼 영역 내에 빈 영

역이 있는지의 여부를 판단하고,

상기 버퍼 영역 내에 상기 빈 영역이 있다고 판단한 경우, 상기 제어부는 상기 제 1의 불휘발성 메모리로부터

판독한 상기 필요한 판독 여러 정정 코드를 상기 빈 영역에 보존하고,

상기 빈 영역이 없다고 판단한 경우, 상기 제어부는 사용 빈도가 상대적으로 낮다고 상정되며 다른 여러 정정

코드를 보존하기 위해 사용되는 영역인 상기 버퍼 영역에 포함된 다른 영역을, 상기 필요한 여러 정정 코드를

보존하기 위해 사용될 상기 빈 영역으로 변경하는 것을 특징으로 하는 메모리 시스템.

### 청구항 5

제 4항에 있어서,

상기 다른 영역을 상기 빈 영역으로 변경하기 이전에, 상기 다른 여러 정정 코드가 변경된 경우, 상기 제어부는

상기 다른 여러 정정 코드를 상기 제 1의 불휘발성 메모리에 기록하는 것을 특징으로 하는 메모리 시스템.

### 청구항 6

제 3항에 있어서,

상기 제 2의 불휘발성 메모리에 저장된 데이터를 금후 액세스될 데이터로서 예상하기 위해, 상기 제 2의 불휘발

성 메모리에 저장된 데이터에 대한 이전 액세스의 기록을 이용하고;

상기 예상된 데이터에 필요한 여러 정정 코드를 상기 제 1의 불휘발성 메모리로부터 상기 버퍼 영역으로 미리

판독하여 두는 것을 메모리 시스템.

**청구항 7**

제 2항에 있어서,

상기 제어부는:

상기 제 2의 불휘발성 메모리로의 상기 데이터의 기록 동작 이전에, 상기 제 2의 불휘발성 메모리에 기록될 데이터에 상기 에러 정정 코드를 부가한 뒤 상기 기록 동작을 수행하고,

상기 제 2의 불휘발성 메모리로부터 상기 데이터를 판독하는 동작 이후 및 시스템 기동시에 상기 에러 정정 코드를 사용하는 것에 의해, 상기 제 2의 불휘발성 메모리로부터 판독된 데이터에 대해 비트 오류 검출 및 정정 처리를 수행하는 것을 특징으로 하는 메모리 시스템.

**청구항 8**

제 7항에 있어서,

상기 제어부는 상기 제 2의 불휘발성 메모리에 기록된 상기 데이터에 부가된 상기 에러 정정 코드를 사용하여 상기 기록 동작에서 상기 베파 영역의 컨텐츠를 갱신하는 것을 특징으로 하는 메모리 시스템.

**청구항 9**

제 1항에 있어서,

상기 제어부는, 상기 제 2의 불휘발성 메모리 내의 각 데이터의 어드레스와, 상기 제 1의 불휘발성 메모리 내의 각 데이터에 필요한 상기 에러 정정 코드의 어드레스를 대응시켜 관리하고 있는 것을 특징으로 하는 메모리 시스템.

**청구항 10**

제 1항에 있어서,

복수의 에러 정정 코드의 다발이, 상기 제 1의 불휘발성 메모리 내에서 상기 블록 단위로 보존되어 있는 것을 특징으로 하는 메모리 시스템.

**청구항 11**

제 1항에 있어서,

상기 제 1의 불휘발성 메모리에 저장된 데이터에 적용될 제 1의 에러 정정 코드와 상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용되며 상기 에러 정정 코드로서 사용되는 제 2의 에러 정정 코드는 상기 제 1의 불휘발성 메모리 내에 보존되는 것을 특징으로 하는 메모리 시스템.

**청구항 12**

제 1항에 있어서,

상기 제 1의 불휘발성 메모리는:

상기 블록으로서 각각 기능하는 페이지 단위로 액세스되는 데이터를 저장하기 위해 사용되는 플래시 메모리; 또는

상기 블록으로서 각각 기능하는 섹트 단위로 액세스되는 데이터를 저장하기 위해 사용되는 하드디스크인 것을 특징으로 하는 메모리 시스템.

**청구항 13**

메모리 시스템의 동작 방법에 있어서,

상기 메모리 시스템에서 사용되는 제 1의 불휘발성 메모리에 저장된 데이터를 블록 단위로 액세스를 수행하고;

상기 메모리 시스템에서 사용되는 제 2의 불휘발성 메모리에 저장된 데이터를 워드 단위로 랜덤 액세스를 수행하며;

상기 제 1의 불휘발성 메모리에 보존된 에러 정정 코드를 사용하는 것에 의해 상기 제 2의 불휘발성 메모리에 저장된 상기 데이터에 대해 비트 오류 검출 및 정정 처리를 수행하는 것을 특징으로 하는 메모리 시스템의 동작 방법.

## 명세서

### 기술 분야

- [0001] 본 발명은, 불휘발성 메모리를 이용한 메모리 시스템, 및 그와 같은 메모리 시스템의 동작 방법에 관한 것이다.

- [0002] 종래, 스토리지(보조 기억 장치)로서 기능하는 메모리상에 보존되어 있는 프로그램이나 데이터 등을, DRAM(Dynamic Random Access Memory) 등의 워크 메모리(주기억 장치)에 관통하여(로드하여) 실행하는 메모리 시스템(스토리지 시스템)이 사용되고 있다. 이와 같은 메모리 시스템에서, 고속 동작이 요구되는 스토리지로서는, 일반적으로 불휘발성 메모리(NVM : Non-Volatile Memory)가 사용되고 있다.

- [0003] 이 불휘발성 메모리는, 대용량이고 블록 단위로의 데이터 액세스에 대응하는 플래시 메모리와, 워드 단위로의 고속의 데이터 액세스(랜덤 액세스)가 가능한 불휘발성 랜덤 액세스 메모리(NVRAM : Non-Volatile Random Access Memory)로 대별된다. 플래시 메모리의 대표예에서는, NAND형 플래시 메모리를 들 수 있다. 한편, NVRAM의 예로서는, PCRAM(Phase-Change Random Access Memory), MRAM(Magnetoresistive Random Access Memory), ReRAM(Resistance Random Access Memory) 등을 들 수 있다.

- [0004] 전자의 플래시 메모리는, 비트 비용이 낮으면서 대용량이기 때문에, 고속의 스토리지 용도로서 채용되고 있다. 한편, 후자의 NVRAM은, 플래시 메모리에 비하여 비트 비용은 높지만, 이하의 이점을 갖고 있다. 즉, 워드 단위로의 고속 액세스 성능에 우수하고, 또한, CPU(Central Processing Unit)로부터 직접 액세스하는 것도 가능하기 때문에, 스토리지에 대한 불휘발성 캐시 메모리로서 채용함에 의해 메모리 시스템의 고속화를 담당하는 것이 기대되고 있다.

- [0005] 이와 같은 플래시 메모리 및 NVRAM을 이용한 메모리 시스템의 예는, 예를 들면, 일본 특표2004-506256호 공보(특허문헌1), 일본 특개2006-236304호 공보(특허문헌2), 및 『Shuhei Tanakamaru, 외 4명, "Post-manufacturing 17-times Acceptable Raw Bit Error Rate Enhancement, Dynamic Codeword Transition ECC scheme for Highly Reliable Solid-State Drives, SSDs", Memory Workshop (IMW), 2010 IEEE International, p. 1-4』에 개시되어 있다. 상기 메모리 시스템은 불휘발성 메모리 시스템으로도 칭해진다.

- [0006] 그런데, 이와 같은 메모리 시스템에서는, 각 불휘발성 메모리에서의 데이터 보존 특성을 향상시키고, 시스템의 신뢰성을 높이는 것이 중요하다. 이것은, 불휘발성 메모리는 일반적으로, 재기록 횟수의 증가와 함께 데이터의 보존 특성이 열화되는 경향이 있기 때문이다. 그래서, 예를 들면 상기 특허문헌1에서는, 에러 정정 코드(ECC : Error Correcting Code)를 이용하여 데이터의 비트 오류 검출 및 정정 처리를 행함에 의해, NAND형 플래시 메모리에서의 데이터 보존 특성을 향상시키고 있다.

- [0007] 한편, 상기한 NVRAM을 예를 들면 불휘발성 캐시 메모리로서 사용하는 경우, 스토리지로서 기능하는 NAND형 플래시 메모리 등에 비하여 액세스 빈도가 높아지기 때문에, NVRAM에서도 데이터 보존 특성을 향상시키는 것이 중요하다. 그러나, 상기 특허문헌1 등의 메모리 시스템에서는, NVRAM의 데이터에 대한 보존 특성 향상을 위한 수법(예를 들면, ECC를 이용하는 것 등)에 관해서는, 전혀 개시되어 있지가 않다.

- [0008] 그래서, 플래시 메모리와 NVRAM을 이용한 메모리 시스템에서, NVRAM의 데이터에 대해 ECC를 적용하고, 데이터의 보존 특성을 개선한 수법이 생각된다. 그러나, 단순하게 ECC를 적용하는 것만으로는, ECC 코드에의 액세스가 발생한 분만큼 NVRAM에서의 액세스 속도가 저하된다(NVRAM의 대역에 악영향을 미친다)는 부작용이 생겨 버려, 시스템 전체로서도 동작 속도가 저하되게 된다.

- [0009] 본 발명은 이러한 문제점을 감안하여 이루어진 것으로, 그 목적은, 동작 속도를 저하시키는 일 없이 시스템의 신뢰성을 향상시키는 것이 가능한 메모리 시스템 및 그 동작 방법을 제공하는 것에 있다.

## 과제의 해결 수단

- [0010] 본 발명의 메모리 시스템은:

- [0011] 블록 단위로 액세스될 데이터를 저장하는데 이용되는 제 1의 불휘발성 메모리와;

- [0012] 워드 단위로 랜덤하게 액세스될 데이터를 저장하는데 이용되는 제 2의 불휘발성 메모리; 및

- [0013] 상기 제 1 및 제 2의 불휘발성 메모리의 동작을 제어하도록 구성된 제어부를 포함한다.

- [0014] 상기 제 2의 불휘발성 메모리에 저장된 데이터에 적용될 에러 정정 코드가 상기 제 1의 불휘발성 메모리에 보존된다.

- [0015] 본 발명의 메모리 시스템의 동작 방법은:

- [0016] 상기 메모리 시스템에서 사용되는 제 1의 불휘발성 메모리에 저장된 데이터를 블록 단위로 액세스를 수행하고;

- [0017] 상기 메모리 시스템에서 사용되는 제 2의 불휘발성 메모리에 저장된 데이터를 워드 단위로 랜덤 액세스를 수행하며;

- [0018] 상기 제 1의 불휘발성 메모리에 보존된 에러 정정 코드를 사용하는 것에 의해 상기 제 2의 불휘발성 메모리에 저장된 상기 데이터에 대해 비트 오류 검출 및 정정 처리를 수행한다.

- [0019] 본 발명의 메모리 시스템 및 그 동작 방법에서는, 제 1의 불휘발성 메모리에 대해 블록 단위로 데이터의 액세스가 행하여짐과 함께, 제 2의 불휘발성 메모리에 대해 워드 단위로 데이터의 랜덤 액세스가 행하여진다. 이 때, 제 2의 불휘발성 메모리의 데이터에 대해 에러 정정 코드가 적용되고, 예를 들면 비트 오류 검출 및 정정 처리가 이루어짐에 의해, 제 2의 불휘발성 메모리에서의 데이터 보존 특성이 개선된다. 또한, 이 에러 정정 코드는 제 1의 불휘발성 메모리 내에 보존되어 있음에 의해, 예를 들면 제 2의 불휘발성 메모리 자신 내에 에러 정정 코드가 보존되는 경우와는 달리, 이 제 2의 불휘발성 메모리에서의 액세스 속도의 저하가 회피된다.

## 발명의 효과

- [0020] 본 발명의 메모리 시스템 및 그 동작 방법에 의하면, 워드 단위로 데이터의 랜덤 액세스가 행하여지는 제 2의 불휘발성 메모리의 데이터에 적용하는 에러 정정 코드를, 블록 단위로 데이터의 액세스가 행하여지는 제 1의 불휘발성 메모리 내에 보존하도록 하였기 때문에, 제 2의 불휘발성 메모리에서의 액세스 속도의 저하를 회피하면서, 이 제 2의 불휘발성 메모리에서의 데이터 보존 특성을 개선할 수 있다. 따라서, 동작 속도를 저하시키는 일 없이, 시스템의 신뢰성을 향상시키는 것이 가능해진다.

## 도면의 간단한 설명

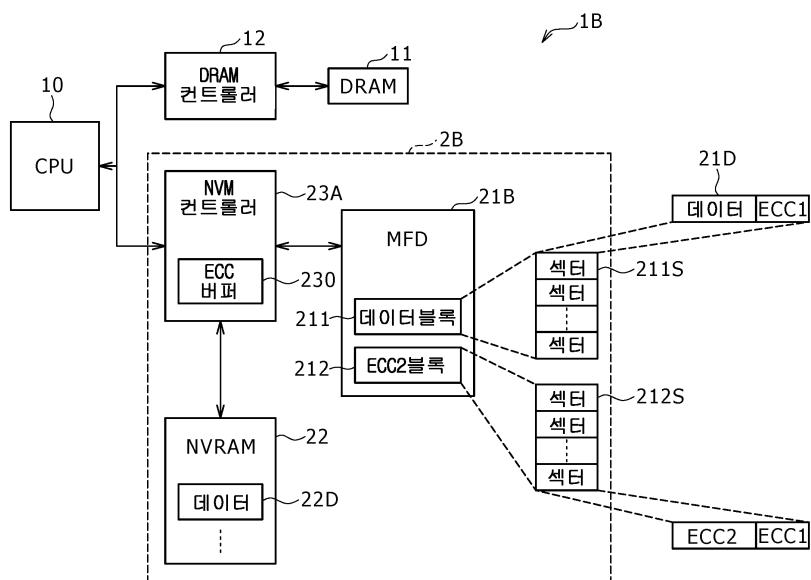

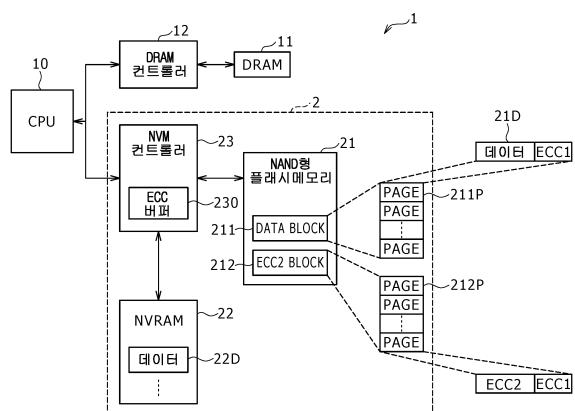

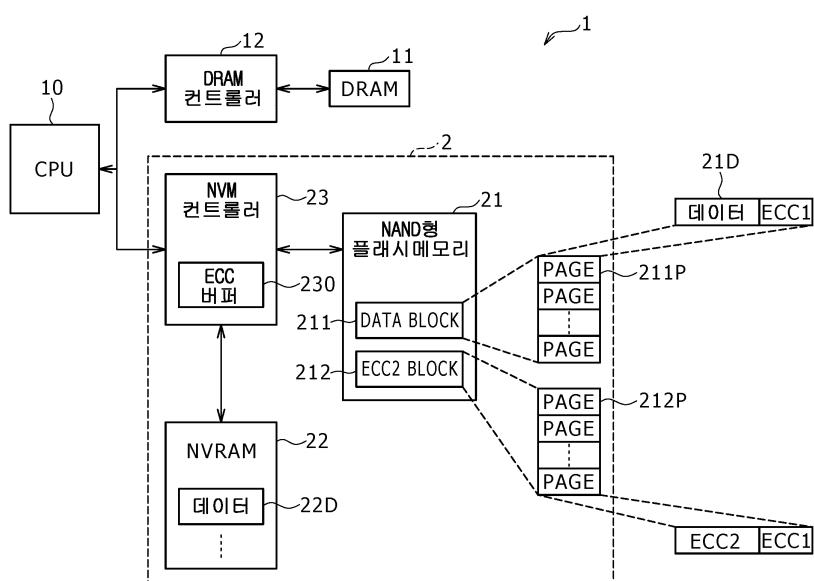

- [0021] 도 1은 본 발명의 한 실시의 형태에 관한 메모리 시스템을 구비한 데이터 기억 시스템의 구성예를 도시하는 블록도.

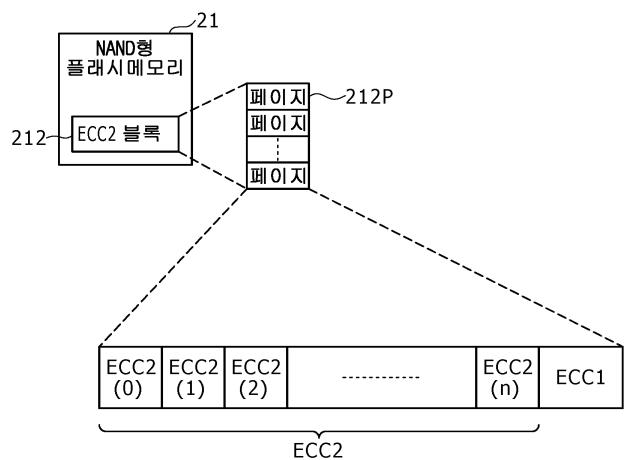

도 2는 도 1에 도시한 NAND형 플래시 메모리의 ECC2 블록에서의 상세한 데이터 구성예를 도시하는 블록도.

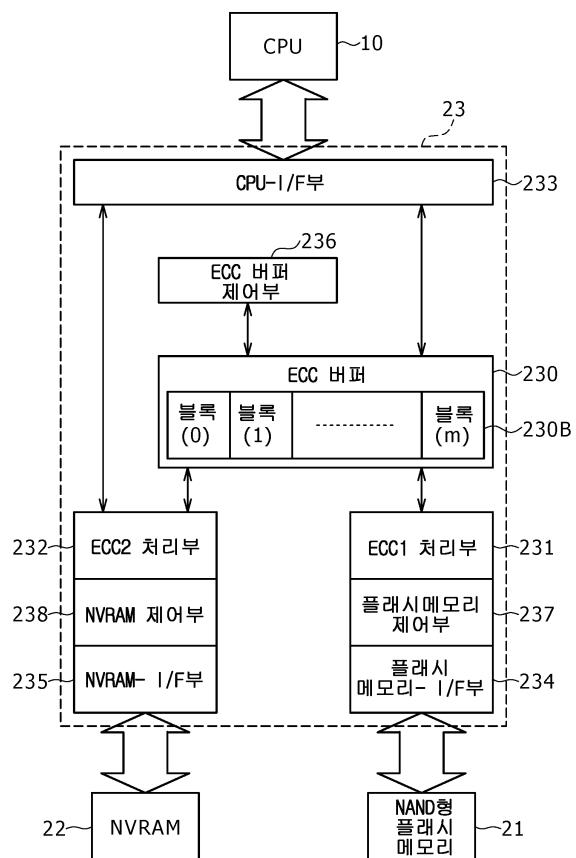

도 3은 도 1에 도시한 NVM 컨트롤러의 상세 구성예를 도시하는 블록도.

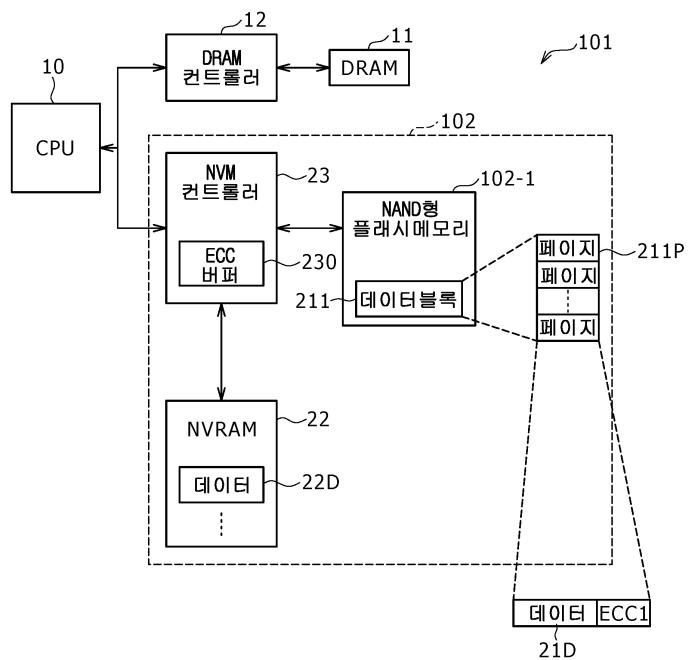

도 4는 비교예 1에 관한 메모리 시스템을 구비한 데이터 기억 시스템의 구성을 도시하는 블록도.

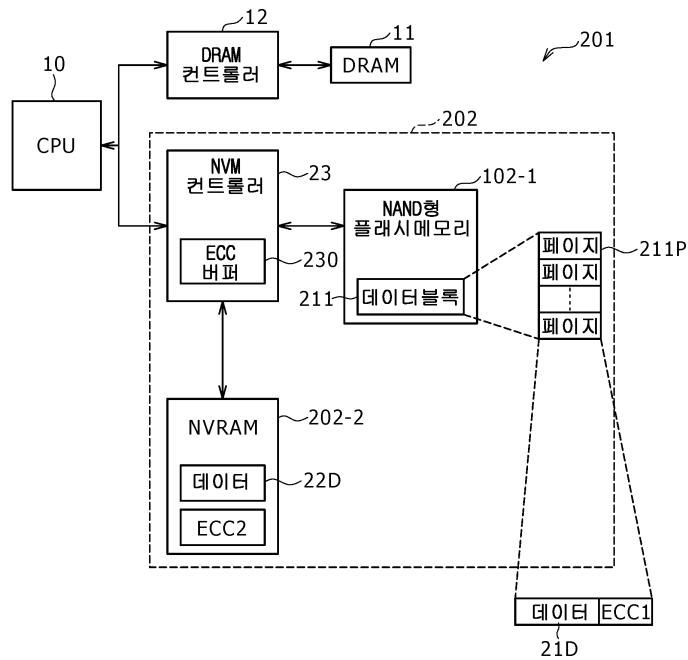

도 5는 비교예 2에 관한 메모리 시스템을 구비한 데이터 기억 시스템의 구성을 도시하는 블록도.

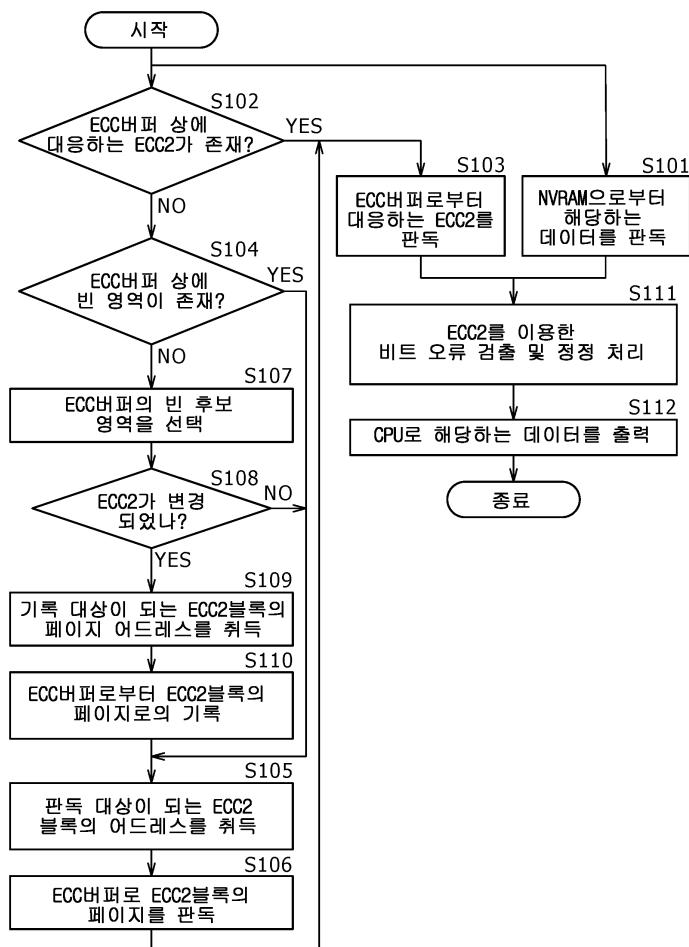

도 6은 에러 정정 코드(ECC2)를 이용한 NVRAM으로부터의 데이터 판독 처리의 한 예를 도시하는 흐름도.

도 7은 에러 정정 코드(ECC2)를 이용한 NVRAM에의 데이터 기록 처리의 한 예를 도시하는 흐름도.

도 8은 에러 정정 코드(ECC2)를 이용한 시스템 기동 처리의 한 예를 도시하는 흐름도.

도 9는 변형예 1에 관한 메모리 시스템을 구비한 데이터 기억 시스템의 구성예를 도시하는 블록도.

도 10은 변형예 2에 관한 메모리 시스템을 구비한 데이터 기억 시스템의 구성예를 도시하는 블록도.

## 발명을 실시하기 위한 구체적인 내용

- [0022] 이하, 본 발명의 실시의 형태에 관해, 도면을 참조하여 상세히 설명한다. 또한, 설명은 이하의 순서로 행한다.

- [0023] 1. 실시의 형태(제 1의 불휘발성 메모리로서 NAND형 플래시 메모리를 이용한 예)

- [0024] 2. 변형예

- [0025] 변형예 1(NAND형 플래시 메모리에 ECC 처리부를 내장한 예)

- [0026] 변형예 2(제 1의 불휘발성 메모리로서 MFD를 이용한 예)

- [0027] 그 밖의 변형예

#### [0028] 실시의 형태

##### [0029] 데이터 기억 시스템(1)의 구성

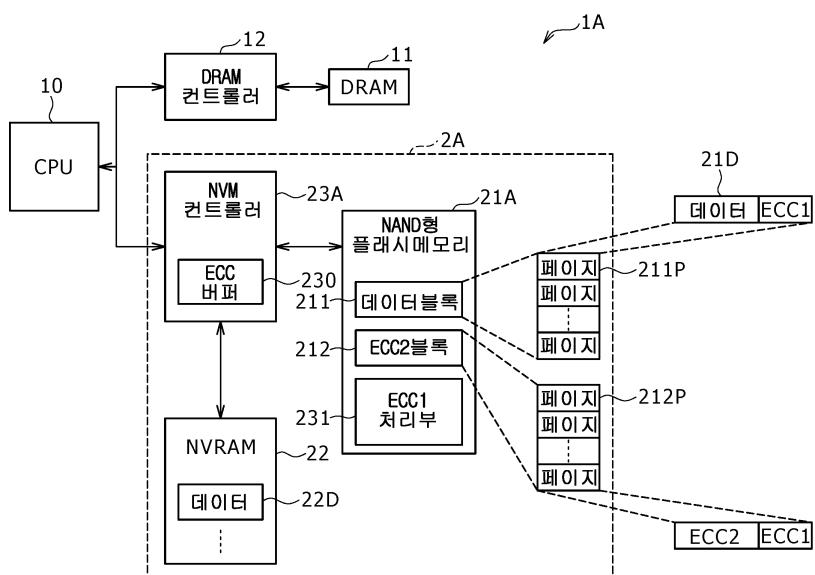

[0030] 도 1은, 본 발명의 한 실시의 형태에 관한 메모리 시스템(불휘발성 메모리 시스템(2))을 구비한 데이터 기억 시스템(데이터 기억 시스템(1))의 블록 구성을 도시하는 것이다. 이 데이터 기억 시스템(1)은, CPU(10), DRAM(11) 및 DRAM 컨트롤러(12)와, 본 실시의 형태의 불휘발성 메모리 시스템(2)을 구비하고 있다.

[0031] CPU(10)는, DRAM(11), DRAM 컨트롤러(12) 및 불휘발성 메모리 시스템(2)의 동작을 각각 제어하는 것이다. 구체적으로는, 후술하는 NVM 컨트롤러(23)를 통하여 NVRAM(22) 및 NAND형 플래시 메모리(21)에 보존(기억)되어 있는 각 데이터에 대해 액세스를 행하여, 예를 들면 워크 메모리(주 메모리)로서 기능하는 DRAM(11)에 데이터를 로드하거나, 역으로 DRAM(11)상의 데이터를 기록하거나 하는 기능을 갖고 있다.

[0032] DRAM(11)은, 상기한 바와 같이, 데이터 기억 시스템(1)에서의 워크 메모리로서 기능하는 휘발성의 메모리이다. DRAM 컨트롤러(12)는, CPU(10)로부터 수신되는 커맨드에 따라, DRAM(11)의 동작(예를 들면, 데이터의 기록 동작이나 판독 동작 등)을 제어하는 것이다.

##### [0033] 불휘발성 메모리 시스템(2)의 구성

[0034] 불휘발성 메모리 시스템(2)은, 불휘발성 메모리(NVM)인 NAND형 플래시 메모리(21)(제 1의 불휘발성 메모리) 및 NVRAM(22)(제 2의 불휘발성 메모리)과, NVM 컨트롤러(23)(제어부)를 구비하고 있다. 여기서는, 이들의 불휘발성 메모리중, NAND형 플래시 메모리(21)가 스토리지로서 기능함과 함께, NVRAM(22)이, 워크 메모리나 불휘발성의 캐시 메모리로서 기능하게 되어 있다. 이에 의해, 이 불휘발성 메모리 시스템(2)은, NAND형 플래시 메모리(21) 와의 조합으로 SnD(Store and Download) 모델에 대응함과 함께, NVRAM(22)과의 조합으로 XIP(execute In Plane) 모델에도 대응하는 것이 가능하게 되어 있다.

##### [0035] NAND형 플래시 메모리(21)

[0036] NAND형 플래시 메모리(21)는, 블록 단위(여기서는, 후술하는 페이지(211P, 212P) 단위)로 데이터의 액세스가 행하여지는 불휘발성 메모리(플래시 메모리)이다. 이 NAND형 플래시 메모리(21)는, 데이터 블록(211) 및 ECC2 블록(212)을 갖고 있다.

[0037] 데이터 블록(211)은, 페이지(211P) 단위로 데이터(21D)가 보존(기억)되어 있는 블록(데이터 영역)이다. 구체적으로는, 각 페이지(211P)에서는, 데이터(21D)가 그것을 보호하는 에러 정정 코드(ECC1)(제 1 에러 정정 코드)와 함께 보존되어 있다. 즉, 이 에러 정정 코드(ECC1)는, 후술하는 바와 같이, NAND형 플래시 메모리(21)의 데이터(21D)에 대해 적용되는 것이고, 이에 의해 NAND형 플래시 메모리(21)에서의 데이터의 보존 특성이 향상하도록 되어 있다.

[0038] ECC2 블록(212)은, NVRAM(22)을 보호하는 에러 정정 코드(ECC2)(제 2 에러 정정 코드)가 페이지(212P) 단위로 보존(기억)되어 있는 블록(데이터 영역)이다. 즉, 본 실시의 형태에서는, NVRAM(22)에 적용되는 에러 정정 코드(ECC2)가, NAND형 플래시 메모리(21) 내에 보존되어 있다. 구체적으로는, 각 페이지(212P)에서는, 이 에러 정정 코드(ECC2)가, 상기한 에러 정정 코드(ECC1)와 함께 보존되어 있다. 상세하게는, 예를 들면 도 2에 도시한 바와 같이, 복수의 에러 정정 코드(ECC2)의 다발(束)(여기서는, n(2 이상의 정수)개의 에러 정정 코드(ECC2(0) 내지 ECC2(n))가 통합된 다발)이, 각 페이지(212P) 단위로 에러 정정 코드(ECC1)와 함께 보존되어 있다. 환연하면, 각 페이지(212P)에서는, 데이터 영역에 에러 정정 코드(ECC2)가 보존됨과 함께, 용장 영역에는 페이지(211P)와 마찬가지로, 에러 정정 코드(ECC1)가 보존되어 있다.

[0039]

또한, 한 예로서 NVRAM(22)에 대한 액세스가 32비트 액세스인 경우, 이 NVRAM(22)의 데이터의 보호에 필요한 에러 정정 코드(ECC2)(예를 들면 해밍 부호(hamming code))는, 6비트가 된다. 또한, NAND형 플래시 메모리(21)에서의 페이지(211P, 212P)의 사이즈(데이터 영역)를, 일반적인 값인 약 32K비트(약 4K바이트)로 하면, 상기한 경우, NVRAM(22)에서의 약 5K워드분의 데이터에 필요한 에러 정정 코드(ECC2)가, 페이지(212P) 내에 보존되게 된다. 또한, 이 경우, NVM 컨트롤러(23)는 후술하는 바와 같이, 1회의 액세스로 5K워드분의 에러 정정 코드(ECC2)를 ECC 버퍼(230)에 판독할 수 있다. 이 때문에, NAND형 플래시 메모리(21)에서의 1페이지의 판독에 필요해지는 시간은, ONFI 2.1 mode 5(200MB/초)에 대응하는 MLC NAND형 플래시 메모리를 사용하는 경우에서 약 80 $\mu$ s가 되고, 하나의 에러 정정 코드(ECC2)당 16ns가 된다. 그러면 NVRAM(22)에서 연속한 어드레스에 대한 액세스가 발생한 경우라도, NVRAM(22)의 액세스 시간이 이 16ns보다도 길면, 액세스의 계속중에 있어서, ECC 버퍼(230)에 대해 다음의 페이지에 필요한 에러 정정 코드(ECC2)의 판독을 행하는 것이 가능해진다. 또한, NVRAM(22)에서 불연속의 어드레스에 대한 액세스가 발생한 경우에는, 후술하는 선판독(先讀) 기능을 이용함으로써, ECC 버퍼(230)에의 에러 정정 코드(ECC2)의 판독 시간을 단축할 수 있다. 또한, 상기한 16ns 정도의 액세스 시간은, NVRAM(22)에의 액세스 시간으로서는, 일반적으로 충분히 고속의 값이라고 말할 수 있다.

[0040]

#### NVRAM(22)

[0041]

NVRAM(22)은, 워드 단위로 데이터(데이터(22D))의 랜덤 액세스가 행하여지는 불휘발성 메모리이고, 상기한 NAND형 플래시 메모리(21)와는 달리, 데이터(22D)만이 보존되어 있다. 즉, 이 NVRAM(22) 내에는, 에러 정정 코드는 보존되어 있지 않다. 이와 같은 NVRAM(22)은, 예를 들면, PCRAM, MRAM, ReRAM 등으로 이루어진다.

[0042]

#### NVM 컨트롤러(23)

[0043]

NVM 컨트롤러(23)는, CPU(10)로부터 수신되는 커맨드에 따라, NAND형 플래시 메모리(21) 및 NVRAM(22)의 동작을 각각 제어하는 것이다. NAND형 플래시 메모리(21)의 통상의 동작은 NAND형 플래시 메모리(21)로 데이터(21D)를 기록하는 동작과 NAND형 플래시 메모리(21)로부터 데이터(21D)를 판독하는 동작을 포함한다. 마찬가지로, NVRAM(22)의 통상의 동작은 NVRAM(22)으로의 데이터(22D)의 기록 동작과, NVRAM(22)로부터 데이터(22D)를 판독하는 동작을 포함한다. NVM 컨트롤러(23)는 상기 언급된 ECC 버퍼(230)를 포함하도록 구성된다.

[0044]

본 실시의 형태에서는, 이 NVM 컨트롤러(23)는, NAND형 플래시 메모리(21) 내에 보존되어 있는 에러 정정 코드(ECC1, ECC2)를 이용하여, 소정의 비트 오류 검출 및 정정 처리(비트 오류 검출 및 정정 처리)를 행하는 기능을 갖고 있다. 구체적으로는, NAND형 플래시 메모리(21)에의 데이터(21D)의 기록시에, 에러 정정 코드(ECC1)를 부가하여 기록을 행하고, NAND형 플래시 메모리(21)로부터의 데이터(21D)의 판독시 또는 시스템의 기동시에, 에러 정정 코드(ECC1)를 이용하여 이 데이터(21D)에 대한 비트 오류 검출 및 정정 처리를 행한다. 또한, 에러 정정 코드(ECC2)를 이용하고, NVRAM(22)에의 데이터(22D)의 기록시에, 이 데이터(22D)에 대한 에러 정정 코드 생성 처리를 행하고, NVRAM(22)로부터의 데이터(22D)의 판독시 또는 시스템의 기동시에, 이 데이터(22D)에 대한 비트 오류 검출 및 정정 처리를 행한다.

[0045]

또한, NVM 컨트롤러(23)는, 데이터(22D)의 액세스 단위인 워드 단위로 에러 정정 코드(ECC2)를 계산하는 것과 병행하여, 데이터(21D)의 액세스 단위인 페이지(211P) 단위로 에러 정정 코드(ECC1)를 계산하도록 되어 있다. 또한, 이들의 에러 정정 코드(ECC1, ECC2)를 이용한 비트 오류 검출 및 정정 처리의 상세에 관해서는, 도 6 내지 도 8을 참조하여 후술한다.

[0046]

이 NVM 컨트롤러(23)는 또한, 상기한 NAND형 플래시 메모리(21) 내의 ECC2 블록(212)을 판독하여(로드하여) 일시적으로 보존하여 두기 위한 버퍼 영역인, ECC 버퍼(230)를 갖고 있다. 그리고, 상세는 후술하지만, NVM 컨트롤러(23)는, 이 ECC 버퍼(230) 내에 판독된 에러 정정 코드(ECC2)를 이용하여, 비트 오류 검출 및 정정 처리를 행하도록 되어 있다. 이에 의해, 비트 오류 검출 및 정정 처리를 고속으로 실행하는 것이 가능해진다.

[0047]

또한, 전술한 복수의 에러 정정 코드(ECC2)의 다발을 판독 단위로 하여, NAND형 플래시 메모리(21)로부터 ECC 버퍼(230)에의 에러 정정 코드(ECC2)의 판독을 행하는 경우에는, NVRAM(22)상의 연속한 어드레스에 대응시킴에 의해, NVRAM(22)상의 연속한 어드레스에의 액세스시에 고속의 처리가 가능해진다. 이와 같이 NVM 컨트롤러(23)는, ECC 버퍼(230)를 이용하여, 에러 정정 코드(ECC1, ECC2)의 캐싱 기능을 실현하고 있다.

[0048]

NVM 컨트롤러(23)는 또한, NVRAM(22) 내의 각 데이터(22D)의 어드레스와, 각 데이터(22D)에 필요한 에러 정정 코드(ECC2)의 NAND형 플래시 메모리(21) 내에서의 보존 어드레스를, 대응지어서 관리하는 기능(ECC 페이지 관리 기능)을 갖고 있다. 또한, 이와 같은 ECC 페이지 관리 기능을 이용한 비트 오류 검출 및 정정 처리의 상세에 관해서도, 도 6 내지 도 8을 참조하여 후술한다.

- [0049] 여기서, 도 3은, NVM 컨트롤러(23)의 블록 구성을 도시한 것이다. 이 NVM 컨트롤러(23)는, 상기한 ECC 버퍼(230)에 더하여, ECC1 처리부(231), ECC2 처리부(232), CPU-I/F부(233), 플래시 메모리-I/F부(234), NVRAM-I/F부(235), ECC 버퍼 제어부(236), 플래시 메모리 제어부(237) 및 NVRAM 제어부(238)를 갖고 있다.

- [0050] ECC1 처리부(231)는, 에러 정정 코드(ECC1)를 이용하여, NAND형 플래시 메모리(21)의 데이터(21D)에 대한 비트 오류 검출 및 정정 처리를 행하는 것이다. 또한, ECC2 블록(212)의 데이터(21D)에 대한 비트 오류 검출 및 정정 처리를 행한 결과는, ECC 버퍼(230)상에 일시적으로 보존되도록 되어 있다. 또한, 그 이외의 데이터 블록(211)의 데이터(21D)는, NVM 컨트롤러(23)로부터 CPU-I/F부(233)를 통하여 출력된다.

- [0051] ECC2 처리부(232)는, 상기한 바와 같이 하여 ECC2 버퍼(230)상에 일시적으로 보존된 에러 정정 코드(ECC2)를 이용하여, NVRAM(22)의 데이터(22D)에 대한 비트 오류 검출 및 정정 처리를 행하는 것이다. 또한, 이 때의 에러 정정 코드(ECC2)를 이용한 비트 오류 검출 및 정정 처리는, 예를 들면 일반적으로 이용되고 있는 허밍 부호 방식을 이용하여 행하여진다.

- [0052] CPU-I/F부(233)는, NVM 컨트롤러(23)와 CPU(10) 사이의 접속을 행하기 위한 인터페이스(I/F) 부분이다. 플래시 메모리-I/F부(234)는, NVM 컨트롤러(23)와 NAND형 플래시 메모리(21) 사이의 접속을 행하기 위한 인터페이스 부분이다. NVRAM-I/F부(235)는, NVM 컨트롤러(23)와 NVRAM(22) 사이의 접속을 행하기 위한 인터페이스 부분이다. 이와 같이, NVM 컨트롤러(23)는, 워드 단위로 랜덤 액세스를 행하는 워크 메모리(여기서는 NVRAM(22))용의 I/F 와, 블록(페이지) 단위로 액세스를 행하는 스토리지(여기서는 NAND형 플래시 메모리(21))용의 I/F의 쌍방을 갖고 있다.

- [0053] ECC 버퍼 제어부(236)는, ECC 버퍼(230)의 동작을 제어하는 것이다. 플래시 제어부(237)는, ECC1 처리부(231) 및 플래시 메모리-I/F부(234)의 동작을 각각 제어하는 것이다. NVRAM 제어부(238)는, ECC2 처리부(232) 및 NVRAM-I/F부(235)의 동작을 각각 제어하는 것이다.

- [0054] 데이터 기억 시스템(1)의 효과

- [0055] 1: 기본 동작

- [0056] 이 데이터 기억 시스템(1)에서는, CPU(10)로부터의 커맨드에 응한 DRAM 컨트롤러(12) 및 NVM 컨트롤러(23)의 제어에 의해, DRAM(11) 및 NVRAM(22)이 워크 메모리로서 기능함과 함께, NAND형 플래시 메모리(21)가 스토리지로서 기능한다. 이에 의해, CPU(10)로부터의 커맨드에 따라, 소정의 프로그램의 실행이나 데이터 처리가 행하여진다. 이때, 불휘발성 메모리 시스템(2)에서는, NAND형 플래시 메모리(21)에 대해 블록(페이지) 단위로 데이터(21D)의 액세스가 행하여지는 한편, NVRAM(22)에 대해 워드 단위로의 데이터(22D)의 랜덤 액세스가 행하여진다.

- [0057] 또한, 이때 NVM 컨트롤러(23)는, NAND형 플래시 메모리(21) 내에 보존되어 있는 에러 정정 코드(ECC1)를 이용하여, 이 NAND형 플래시 메모리(21)의 데이터(21D)에 대한 비트 오류 검출 및 정정 처리를 행한다. 구체적으로는, NVM 컨트롤러(23)는, NAND형 플래시 메모리(21)에의 데이터(21D)의 기록시에 생성한 에러 정정 코드(ECC1)를 사용하여, NAND형 플래시 메모리(21)로부터의 데이터(21D)의 관독시 또는 시스템(불휘발성 메모리 시스템(2))의 기동시에, 그와 같은 비트 오류 검출 및 정정 처리를 행한다. 또한, 이때의 에러 정정 코드(ECC1)를 이용한 비트 오류 검출 및 정정 처리는, 예를 들면 일반적으로 이용되고 있는 BCH 부호 방식을 이용하여 행하여진다. 이에 의해, NAND형 플래시 메모리(21)에서의 데이터(21D)의 보존 특성이 향상하고, 불휘발성 메모리 시스템(2)의 신뢰성의 향상이 도모되어 있다.

- [0058] 2: 에러 정정 코드(ECC2)를 이용한 비트 오류 검출 및 정정 처리)

- [0059] 다음에, 도 4 내지 도 8을 참조하여, 본 발명의 특징적 부분의 하나인, 에러 정정 코드(ECC2)를 이용한 비트 오류 검출 및 정정 처리 등에 관해, 비교예(비교예 1, 2)와 비교하면서 상세히 설명한다.

- [0060] 2-1: 비교예 1

- [0061] 도 4는, 비교예 1에 관한 메모리 시스템(불휘발성 메모리 시스템(102))을 구비한 데이터 기억 시스템(데이터 기억 시스템(101))의 블록 구성을 도시한 것이다. 이 비교예 1의 데이터 기억 시스템(101)은, CPU(10), DRAM(11), DRAM 컨트롤러(12) 및 불휘발성 메모리 시스템(102)을 구비하고 있다. 즉, 본 실시의 형태의 데이터 기억 시스템(1)에서, 본 실시의 형태의 불휘발성 메모리 시스템(2) 대신, 비교예 1의 불휘발성 메모리 시스템(102)을 마련한 것이고, 다른 구성은 마찬가지로 되어 있다.

- [0062] 불휘발성 메모리 시스템(102)은, 본 실시의 형태의 불휘발성 메모리 시스템(2)과는 달리, NAND형 플래시 메모리

(102-1)상에 에러 정정 코드(ECC2)를 보존하지 않기 때문에 ECC2 블록(212)을 구비하고 있지 않고, 다른 구성은 마찬가지로 되어 있다.

[0063] 즉, 이 불휘발성 메모리 시스템(102)에서는, 본 실시의 형태와 마찬가지로 에러 정정 코드(ECC1)를 이용하여 NAND형 플래시 메모리(102-1) 자신의 데이터 보존 특성의 개선을 도모하고 있지만, 본 실시의 형태와는 달리, NVRAM(22)용의 에러 정정 코드(ECC2)가 마련되어 있지 않다.

[0064] 따라서 이 비교예 1에서는, 에러 정정 코드(ECC2)를 이용한 NVRAM(22)의 데이터(22D)에 대한 비트 오류 검출 및 정정 처리가 행하여지지 않게 되기 때문에, NVRAM(22)에 대한 재기록 횟수가 증대해 보존 특성이 열화된 경우, 데이터 에러가 발생할 가능성이 있다. 특히, NVRAM(22)을 불휘발성의 캐시 메모리로서 사용한 경우, 스토리지로서 기능하는 NAND형 플래시 메모리(102-1)에 비하여 액세스 빈도가 높아진다. 이 때문에, NVRAM(22)은, NAND형 플래시 메모리(102-1) 이상으로 높은 데이터 보존 특성이 필요해진다. 그러나, 이 비교예 1에서는, 상기한 대로, NVRAM(22)에서의 데이터 에러의 발생을 막을 수가 없기 때문에, 불휘발성 메모리 시스템(102) 전체로서의 신뢰성도 저하되어 버리게 된다.

#### 2-2: 비교예 2

[0065] 뒤이어, 도 5는, 비교예 2에 관한 메모리 시스템(불휘발성 메모리 시스템(202))을 구비한 데이터 기억 시스템(데이터 기억 시스템(201))의 블록 구성을 도시한 것이다. 이 비교예 2의 데이터 기억 시스템(101)은, CPU(10), DRAM(11), DRAM 컨트롤러(12) 및 불휘발성 메모리 시스템(202)을 구비하고 있다. 즉, 본 실시의 형태의 데이터 기억 시스템(1)에서, 본 실시의 형태의 불휘발성 메모리 시스템(2) 대신에, 비교예 2의 불휘발성 메모리 시스템(202)을 마련한 것이고, 다른 구성은 마찬가지로 되어 있다.

[0066] 불휘발성 메모리 시스템(202)은, 본 실시의 형태의 불휘발성 메모리 시스템(2)과는 달리, NAND형 플래시 메모리(102-1)상에 에러 정정 코드(ECC2)를 보존하지 않기 때문에 ECC2 블록(212)을 구비하고 있지 않다. 그 대신에, 이 불휘발성 메모리 시스템(202)에서는, NVRAM(202-2)상에 에러 정정 코드(ECC2)를 보존하는 영역이 마련되어 있고, 다른 구성은 마찬가지로 되어 있다.

[0067] 즉, 이 비교예 2에서는, 에러 정정 코드(ECC2)를 이용하여, NVRAM(202-2)의 데이터(22D)에 대한 비트 오류 검출 및 정정 처리가 행하여지게 된다. 이에 의해, 상기 비교예 1과 비교하여, NVRAM(202-2)에서 데이터(22D)의 보존 특성의 개선이 도모되고, 불휘발성 메모리 시스템(202) 전체로서의 신뢰성도 향상한다.

[0068] 그런데, 이 비교예 2의 불휘발성 메모리 시스템(202)에서는, NVRAM(202-2)용의 에러 정정 코드(ECC2)가 NVRAM(202-2) 자신의 내부에서 보존되어 있는 것에 기인하여, 이하와 같은 문제가 생겨 버린다.

#### 액세스 속도의 저하의 문제

[0069] 우선, 첫번째의 문제로서, NVRAM(202-2)에서의 액세스 속도가 저하된다(NVRAM(202-2)의 대역에 악영향을 미친다)는 부작용이 생겨 버려, 불휘발성 메모리 시스템(202) 전체로서도 동작 속도가 저하되어 버린다는 것을 들 수 있다. 여기서, 비교예 2와 같이 NVRAM(202-2) 내에 에러 정정 코드(ECC2)가 보존되어 있는 경우에서의, 불휘발성 메모리 시스템(202)에의 액세스 수법으로서는, 이하의 2가지 수법이 생각된다.

[0070] 제 1의 수법은, 도 5에 도시한 바와 같이, NVRAM(202-2)상에서 데이터(22D)의 어드레스와는 다른 어드레스에, 에러 정정 코드(ECC2)를 보존한다는 것이다. 이 수법에서는, NVRAM(202-2)에 대한 1회의 액세스에 대해, 실제, 최저 2회(데이터(22D)에의 액세스와, 에러 정정 코드(ECC2)에의 액세스의 2회)의 액세스가 필요해진다. 이 때문에, 이 제 1의 수법에서는, NVRAM(202-2)에서의 고속의 액세스 속도가, 1/2로 저하되어 버리게 된다.

[0071] 제 2의 수법은, NVRAM(202-2)상에서 데이터(22D)의 일부의 비트에, 에러 정정 코드(ECC2)를 할당하여 보존하는 것이다. 이 수법에서는, NVRAM(202-2)에 대한 1회의 액세스에 의해, 데이터(22D)와 에러 정정 코드(ECC2)의 쌍방에 액세스할 수 있기 때문에, 상기한 제 1의 수법에 비하여, NVRAM(202-2)에서의 액세스 속도 저하의 영향은 작아지는 경향이 있다. 단, 1 회의 액세스에서 사용되는 데이터(22D)의 비트 사이즈가, 에러 정정 코드(ECC2)에 할당한 분만큼 작아지기 때문에, 이 제 2의 수법에서도, NVRAM(202-2)에서 고속의 액세스 속도가 저하되어 버리게 된다. 또한, 가령, 데이터(22D)에서 16비트중의 8비트분을 에러 정정 코드(ECC2)에 할당한 경우에는, 결국, 상기한 제 1의 수법과 마찬가지로, 액세스 속도가, 1/2로 저하되어 버린다.

[0072] 이와 같이, 상기한 2개의 수법의 어느 쪽에서도, 비교예 2에서는 NVRAM(202-2)에서의 액세스 속도가 저하되고 버리고, 불휘발성 메모리 시스템(202) 전체로서도 동작 속도가 저하되어 버리게 된다.

[0075] 비용 증가의 문제

[0076] 또한, 특히 2개의 불휘발성 메모리로서, NAND형 플래시 메모리(102-1)와 NVRAM(202-2)을 이용한 경우, 비교예 2의 불휘발성 메모리 시스템(202)에서는, 이하와 같은 비용 증가의 문제도 생긴다. 즉, 일반적으로, NVRAM은 NAND형 플래시 메모리에 비하여 비트 단가가 높기 때문에, 비교예 2와 같이, NVRAM(202-2)용의 에러 정정 코드(ECC2)를 NVRAM(202-2) 자신의 내부에서 보존한 경우, NVRAM(202-2)의 실질의 데이터 용량이 감소한다. 따라서 불휘발성 메모리(202) 전체로서, 불휘발성 메모리의 비용이 증대하여 버리게 된다.

[0077] 2-3: 본 실시의 형태

[0078] 이에 대해, 본 실시의 형태의 불휘발성 메모리 시스템(2)에서는, 도 1 내지 도 3에 도시한 바와 같이, NVRAM(22)의 데이터(22D)에 대해 에러 정정 코드(ECC2)가 적용되고, 이하 상세히 기술하는 바와 같이 하여 데이터(22D)에 대한 비트 오류 검출 및 정정 처리가 행하여진다. 이에 의해, 상기 비교예 1의 불휘발성 메모리 시스템(102)에 비하여, NVRAM(22)에서의 데이터 보존 특성이 개선된다.

[0079] 또한, 본 실시의 형태에서는, 도 1 및 도 2에 도시한 바와 같이, 이 에러 정정 코드(ECC2)가 NAND형 플래시 메모리(21) 내에 보존되어 있다. 이에 의해, 에러 정정 코드(ECC2)가 NVRAM(202-2) 내에 보존되어 있는 상기 비교예 2와는 달리, NVRAM(22)에서의 상술한 바와 같은 액세스 속도의 저하의 문제가 회피된다. 구체적으로는, NVRAM(22)상에는 데이터(22D)만이 보존되기 때문에, NVRAM(22)에서의 용량의 사용 효율이 보존된다. 또한, NVRAM-I/F부(235)의 대역(帶域)은, 전부 데이터 전송에 사용되게 되기 때문에, 에러 정정 코드(ECC2)를 이용함에 의한 대역의 감소도 발생하지 않고, NVRAM(22)에서의 퍼포먼스에의 영향도 최소한으로 억제된다. 또한, 전술한 바와 같이, 복수의 에러 정정 코드(ECC2)의 다발을 판독 단위로 하여, NAND형 플래시 메모리(21)로부터 ECC 베피(230)에의 에러 정정 코드(ECC2)의 판독을 행하는 경우에는, 이하의 이점도 얻어진다. 즉, NVRAM(22)상의 연속한 어드레스에 대응시킴에 의해, NVRAM(22)상의 연속한 어드레스에의 액세스시에 고속의 비트 오류 검출 및 정정 처리를 행하는 것이 가능해진다. 또한, 후술하는 바와 같이, ECC 베피(230)상에 필요하게 되는 에러 정정 코드(ECC2)가 존재하지 않은 경우에는, 재차 NAND형 플래시 메모리(21)에의 액세스가 발생하기 때문에, 일시적으로는 퍼포먼스가 저하되는 일이 된다. 단, ECC 베피(230)상에 한 번 판독된 에러 정정 코드(ECC2)중, 액세스 빈도가 높은 것이 우선하여 ECC 베피(230)에 보존되기 때문에, 전체로서는 NVRAM(22)에서의 고속의 데이터 액세스 성능은 유지된다고 말할 수 있다.

[0080] 또한, 본 실시의 형태에서는, 상기한 바와 같이, 비트 단가가 상대적으로 낮은 NAND형 플래시 메모리(21)측에 에러 정정 코드(ECC2)가 보존되어 있기 때문에, 상기 비교예 2와는 달리, 상술한 비용 증가의 문제도 회피된다(불휘발성 메모리의 비용이 억제된다).

[0081] 여기서, 이하 도 6 내지 도 8을 참조하여, 이와 같은 에러 정정 코드(ECC2)를 이용한 NVRAM(22)의 데이터(22D)에 대한 비트 오류 검출 및 정정 처리에 관해, 상세히 설명한다. 환언하면, NVM 컨트롤러(23)는 이하와 같이 하여, NVRAM(22)에의 데이터(22D)의 기록시에 에러 정정 코드(ECC2)를 기록함과 함께, NVRAM(22)으로부터의 데이터(22D)의 판독시 또는 시스템의 기동시에, 에러 정정 코드(ECC2)를 이용하여 이 데이터(22D)에 대한 비트 오류 검출 및 정정 처리를 행한다.

[0082] NVRAM(22)으로부터의 데이터 판독 처리

[0083] 도 6은, 에러 정정 코드(ECC2)를 이용한, NVRAM(22)으로부터 CPU(10)에의 데이터 판독 처리의 한 예를 흐름도로 도시한 것이다.

[0084] 이 데이터 판독 처리에서는, NVM 컨트롤러(23)는, ECC 베피(230)상에, NVRAM(22)으로부터 판독한 데이터(22D)에 대응하는(필요한) 에러 정정 코드(ECC2)가 존재하는(보존되어 있는)지의 여부를 판단한다(스텝 S102). 여기서, 필요한 에러 정정 코드(ECC2)가 ECC 베피(230)상에 존재하는 경우(스텝 S102 : Y)에는, NVM 컨트롤러(23)는 이하의 처리를 행한다. 즉, NVRAM(22)으로부터 해당하는(판독 대상으로 되어 있는) 데이터(22D)를 판독하는(스텝 S101) 것과 병행하여, 이 ECC 베피(230)로부터 필요한 에러 정정 코드(ECC2)를 판독한다(스텝 S103).

[0085] 한편, 필요한 에러 정정 코드(ECC2)가 ECC 베피(230)상에 존재하지 않는 경우(스텝 S102 : N)에는, 다음에 NVM 컨트롤러(23)는, 이 ECC 베피(230) 내에 빈 영역(available area)(에러 정정 코드(ECC2)가 보존되지 않은 영역)이 있는(존재하는)지의 여부를 판단한다(스텝 S104). 그리고, ECC 베피(230) 내에 빈 영역이 있다고 판단한 경우(스텝 S104 : Y)에는, 다음에 NVM 컨트롤러(23)는, 전술한 ECC 페이지 관리 기능을 이용하여, 필요한 에러 정정 코드(ECC2)를 포함하는 ECC2 블록(212)의 NAND형 플래시 메모리(21)상에서의 어드레스를 취득한다(스텝

S105). 계속해서, NVM 컨트롤러(23)는, NAND형 플래시 메모리(21)로부터 ECC 버퍼(230) 내의 상기한 빈 영역에 대해, 이 필요한 에러 정정 코드(ECC2)를 포함하는 ECC2 블록(212)의 페이지를 판독하여 보존시키고(스텝 S106), 전술한 스텝 S103으로 진행한다. 따라서, CPU(10)에 대해, 필요한 에러 정정 코드(ECC2)를 포함하는 ECC2 블록(212)을 NAND형 플래시 메모리(21)로부터 ECC 버퍼(230)로 판독하는데 걸리는 시간은 NVRAM(22)에 액세스하는데 걸리는 시간의 연장이다. 즉, NVRAM(22)에 대한 액세스는, 필요한 에러 정정 코드(ECC2)를 포함하는 ECC2 블록(212)을 NVM 컨트롤러(23)가 NAND형 플래시 메모리(21)로부터 ECC 버퍼(230)로 판독하는 동안, 일시적으로 정지될 필요가 있다.

[0086] 여기서, ECC 버퍼(230) 내에 빈 영역이 없다고 판단한 경우(스텝 S104 : N)에는, 다음에 NVM 컨트롤러(23)는, ECC 버퍼(230)상의 빈 후보 영역을 선택한다(스텝 S107). 구체적으로는, ECC 버퍼(230)상에서, 사용 빈도(액세스 빈도)가 상대적으로 낮다(바람직하게는 가장 낮다)고 상정되는 에러 정정 코드(ECC2)의 보존 영역을 빈 후보 영역으로서 선택하고, 빈 영역으로 변경하여 이용하도록(버퍼 영역의 재이용을 하도록) 한다.

[0087] 뒤이어, NVM 컨트롤러(23)는, 상기한 바와 같이 하여 에러 정정 코드(ECC2)의 보존 영역(빈 후보 영역)을 빈 영역으로 변경할 때에, NVM 컨트롤러(23)는, 우선, NAND형 플래시 메모리(21) 내의 해당하는 에러 정정 코드(ECC2)가 변경 끝남인지의 여부를 판단한다(스텝 S108). 여기서, 해당하는 에러 정정 코드(ECC2)가 이미 변경 끝남이 아니라고 판단한 경우(스텝 S108 : N)에는, 다음에 전술한 스텝 S105로 진행한다. 한편, 그 에러 정정 코드(ECC2)가 변경 끝남인 경우에는, NAND형 플래시 메모리(21) 내에 그 에러 정정 코드(ECC2)를 포함하는 ECC2 블록(212)의 페이지에 데이터(22D)를 기록한다. 구체적으로는, 해당하는 에러 정정 코드(ECC2)가 변경 끝남이라고 판단한 경우(스텝 S108 : Y)에는, 다음에 NVM 컨트롤러(23)는, 전술한 ECC 페이지 관리 기능을 이용하여, 에러 정정 코드(ECC2)의 기록 대상이 되는 ECC2 블록(212)의 NAND형 플래시 메모리(21)상에서의 어드레스를 취득한다(스텝 S109). 그리고, NVM 컨트롤러(23)는, ECC 버퍼(230)로부터 ECC2 블록(212)의 페이지에 대해, 해당한 에러 정정 코드(ECC2)를 기록하고(스텝 S110), 전술한 스텝 S105로 진행한다.

[0088] 여기서, 전술한 스텝 S103의 후에는, NVM 컨트롤러(23)는, 에러 정정 코드(ECC2)를 이용하여, NVRAM(22)에서 판독 대상으로 되어 있는 데이터(22D)에 대한 비트 오류 검출 및 정정 처리를 행한다(스텝 S111). 이 때, 에러 정정 코드(ECC2)를 이용한 비트 오류 검출 및 정정 처리는, 예를 들면, 일반적으로 이용되고 있는 허밍 부호 방식을 이용하여 행한다. 또한, 정정을 행하는 것이 불가능한 비트 오류가 검출된 경우에는, NVM 컨트롤러(23)는, 예를 들면 그 취지를 CPU(10)에 통지하도록 한다. 그리고, NVM 컨트롤러(23)는, 이와 같은 비트 오류 검출 및 정정 처리 후의 해당하는 데이터(22D)를, CPU(10)에 출력한다. 이상에 의해, 도 6에 도시한 NVRAM(22)으로부터 CPU(10)에의 데이터 판독 처리가 종료하게 된다.

[0089] 또한, 이와 같은 데이터 판독 처리(및, 이하의 데이터 기록 처리 및 시스템 기동 처리)할 때에는, NVM 컨트롤러(23)는, 이하와 같은 에러 정정 코드(ECC2)의 선판독 기능을 이용하는 것이 바람직하다. 이 에러 정정 코드(ECC2)의 선판독 기능을 이용하는 경우, 우선, NVM 컨트롤러(23)는, NVRAM(22) 내의 데이터(22D)에의 과거의 액세스 이력을 이용하여, 이 NVRAM(22) 내에서 금후 액세스가 행하여지는 데이터(22D)를 예상한다. 그리고, 그 예상한 데이터(22D)에 필요한 에러 정정 코드(ECC2)를, NVRAM(22)으로부터 ECC 버퍼(230)에 미리 판독하여 둔다. 이와 같은 에러 정정 코드(ECC2)의 선판독 기능을 이용하는 경우, NVRAM(22)에서의 액세스의 고속 성능의 유지가 용이해진다.

#### NVRAM(22)에의 데이터 기록 처리

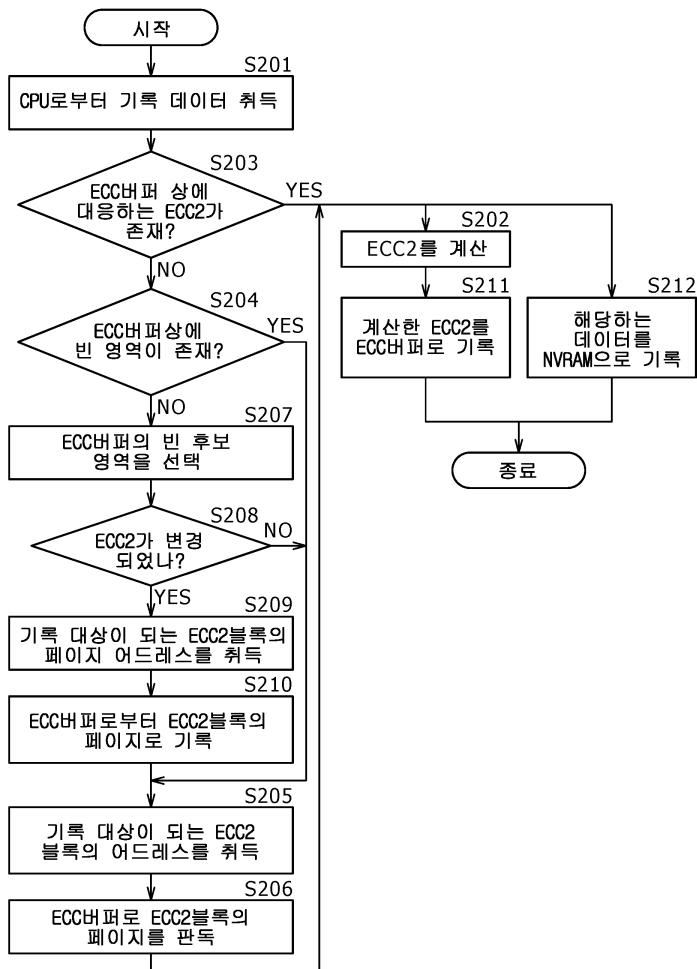

[0091] 도 7은, 에러 정정 코드(ECC2)를 이용한, CPU(10)로부터 NVRAM(22)에의 데이터 기록 처리의 한 예를 흐름도로 도시한 것이다.

[0092] 이 데이터 기록 처리에서는, 우선 NVM 컨트롤러(23)는, CPU(10)로부터 해당하는(기록 대상이 되는) 데이터(22D)를 취득한다(스텝 S201). 뒤이어, NVM 컨트롤러(23)는, 전술한 판독 처리할 때에 있어서의 스텝 S102, S104 내지 S110과 같은 처리를 행하고(스텝 S203 내지 S210), 다음에 이하의 스텝 S202로 진행한다.

[0093] 뒤이어, NVM 컨트롤러(23)는, 예를 들면 일반적으로 이용되고 있는 허밍 부호 방식을 이용하여, 취득한 데이터(22D)에 필요한 에러 정정 코드(ECC2)를, 연산(계산)함에 의해 생성한다(스텝 S202). 뒤이어 스텝 S211에서는, NVM 컨트롤러(23)는, 계산하여 얻어진 에러 정정 코드(ECC2)를, ECC 버퍼(230)에 기록한다(생성한다). 이 때, ECC 버퍼(230)상에서 에러 정정 코드(ECC2)를 포함한 페이지는, 생성 끝남 상태로서 등록된다. 또한, 그와 함께, NVM 컨트롤러(23)는, 해당하는 데이터(22D)를 NVRAM(22)에 기록한다(스텝 S212). 이상에 의해, 도 7에 도시한 CPU(10)로부터 NVRAM(22)에의 데이터 기록 처리가 종료하게 된다.

[0094] 시스템 기동 처리

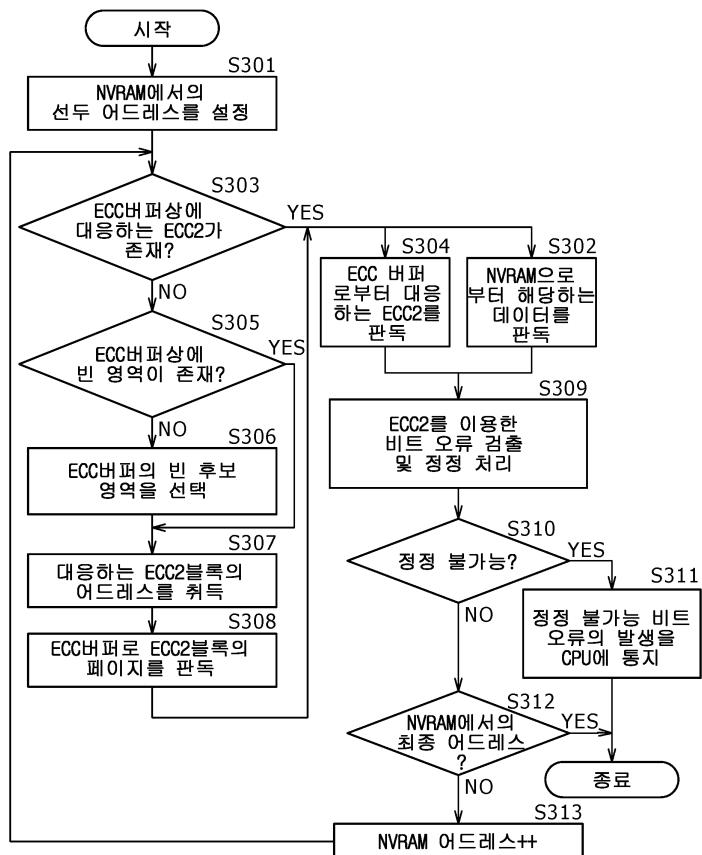

[0095] 도 8은, 에러 정정 코드(ECC2)를 이용한, 불휘발성 메모리 시스템(2)의 기동 처리(시스템 기동 처리)의 한 예를 흐름도로 도시한 것이다.

[0096] 이 시스템 기동 처리에서는, 우선, NVM 컨트롤러(23)는, NVRAM(22)에서 선두 어드레스를 설정한다(스텝 S301). 뒤이어, NVM 컨트롤러(23)는, 전술한 판독 처리할 때에 있어서의 스텝 S101 내지 S104, S107, S105, S106, S111과 같은 처리를 행하고(스텝 S302 내지 S309), 다음에 이하의 스텝 S310으로 진행한다.

[0097] 이 스텝 S310에서는, 스텝 S309에서 실행한 비트 오류 검출 및 정정 처리에서, 정정을 행하는 것이 불가능한 비트 오류가 검출된 것인지의 여부를 판단한다. 그리고, 정정을 행하는 것이 불가능한 비트 오류가 검출된 경우(스텝 S310 : Y)에는, 다음에 NVM 컨트롤러(23)는 그 취지를 CPU(10)에 통지함에 의해(스텝 S311), 도 8에 도시한 시스템 기동 처리가 종료하게 된다.

[0098] 한편, 정정을 행하는 것이 불가능한 비트 오류가 검출되지 않은 경우(스텝 S310 : N)에는, 다음에 NVM 컨트롤러(23)는, NVRAM(22)에서의 최종 어드레스가 대상으로 되어 있는지의 여부를 판단한다(스텝 S312). 여기서, 최종 어드레스가 대상으로 되어 있지 않은 경우(스텝 S312 : N)에는, NVM 컨트롤러(23)는, NVRAM(22)에서 대상 어드레스에 대해 「1」을 가산하고(스텝 S313), 전술한 스텝 S303으로 되돌아온다. 한편, 최종 어드레스가 대상으로 되어 있는 경우(스텝 S312 : Y)에는, 도 8에 도시한 시스템 기동 처리가 종료하게 된다.

[0099] 이와 같이, 불휘발성 메모리 시스템(2)이 (전원의 투입이 되어서) 기동한 때에, NVRAM(22)상의 모든 데이터(22D)에 대해 에러 정정 코드(ECC2)를 이용한 비트 오류 검출 및 정정 처리를 행함에 의해, 이하의 효과가 얻어진다. 즉, 불휘발성의 캐시 메모리로서 사용되는 NVRAM(22)상에, 데이터의 비트 오류가 존재하지 않는 것이 확인된 후에 불휘발성 메모리 시스템(2)이 동작 시작으로 되기 때문에, 시스템의 신뢰성을 향상시키는 것이 가능해진다.

[0100] 이상과 같이 본 실시의 형태에서는, 워드 단위로의 데이터의 랜덤 액세스가 행하여지는 NVRAM(22)의 데이터(22D)에 적용하는 에러 정정 코드(ECC2)를, 블록(페이지) 단위로 데이터의 액세스가 행하여지는 NAND형 플래시 메모리(21) 내에 보존하도록 하였기 때문에, NVRAM(22)에서의 액세스 속도의 저하를 회피하면서, 이 NVRAM(22)에서의 데이터 보존 특성을 개선(향상)할 수 있다. 따라서, 동작 속도를 저하시키는 일 없이, 불휘발성 메모리 시스템(2)의 신뢰성을 향상시키는 것이 가능해진다.

[0101] 또한, 특히 본 실시의 형태에서는, 비트 단자가 상대적으로 낮은 NAND형 플래시 메모리(21)측에 에러 정정 코드(ECC2)를 보존하도록 하였기 때문에, 불휘발성 메모리의 비용을 억제하는 것이 가능해진다.

[0102] 변형예

[0103] 계속해서, 상기 실시의 형태의 변형예(변형예 1, 2)에 관해 설명한다. 또한, 상기 실시의 형태에서의 구성 요소와 동일한 것에는 동일한 부호를 붙이고, 적절히 설명을 생략한다.

[0104] 변형예 1

[0105] 도 9는, 변형예 1에 관한 메모리 시스템(불휘발성 메모리 시스템(2A))을 구비하는 데이터 기억 시스템(데이터 기억 시스템(1A))의 블록 구성을 도시한 것이다. 본 변형예의 데이터 기억 시스템(1A)은, CPU(10), DRAM(11), DRAM 컨트롤러(12) 및 불휘발성 메모리 시스템(2A)을 구비하고 있다. 즉, 상기 실시의 형태의 데이터 기억 시스템(1)에서, 상기 실시의 형태의 불휘발성 메모리 시스템(2) 대신에, 본 변형예의 불휘발성 메모리 시스템(2A)을 마련한 것이고, 다른 구성은 마찬가지로 되어 있다.

[0106] 불휘발성 메모리 시스템(2A)은, ECC를 내장한 NAND형 플래시 메모리(21)와, NVRAM(22)과, NVM 컨트롤러(23A)를 구비하고 있다.

[0107] NAND형 플래시 메모리(21A)는, 전술한 ECC1 처리부(231)를 내장하는 것을 특징으로 하고 있다. 그 때문에, 본 변형예의 NVM 컨트롤러(23A)는, 에러 정정 코드(ECC1)를 이용하여 비트 오류 검출 및 정정 처리를 행하는 데이터를, NAND형 플래시 메모리(21A)로부터 수신하고, ECC 버퍼(230)에 일시적으로 보존한다. NAND형 플래시 메모리(21A)에 대해 기록을 행하는 경우에도, 데이터(21D)만을 송신한다. 이 NAND형 플래시 메모리(21A)는 또한, 페이지(211P) 단위로 구성되는 데이터 블록(211)과, 페이지(212P) 단위로 구성되는 ECC2 블록(212)을 갖고 있다. 또한, 페이지(211P, 212P)에서의 데이터 구성은, 상기 실시의 형태에서의 페이지(211P, 212P)에서의 데이터 구성과 마찬가지로 되어 있지만, 에러 정정 코드(ECC1)를 보존하는 영역에는 NVM 컨트롤러(23)로부터는 액세스할

수가 없다.

[0108] 근래, NAND형 플래시 메모리(21A)와 같이 ECC 처리부를 내장하도록 한 제품이 존재하는데, 본 변형예에서는 그와 같은 제품을 탑재한 불휘발성 메모리 시스템에서도, 상기 실시의 형태와 같은 작용에 의해 같은 효과를 얻는 것이 가능하다.

#### 변형예 2

[0110] 도 10은, 변형예 2에 관한 메모리 시스템(불휘발성 메모리 시스템(2B))을 구비하는 데이터 기억 시스템(데이터 기억 시스템(1B))의 블록 구성을 도시한 것이다. 본 변형예의 데이터 기억 시스템(1B)은, CPU(10), DRAM(11), DRAM 컨트롤러(12) 및 불휘발성 메모리 시스템(2B)을 구비하고 있다. 즉, 상기 실시의 형태의 데이터 기억 시스템(1)에서, 상기 실시의 형태의 불휘발성 메모리 시스템(2) 대신에, 본 변형예의 불휘발성 메모리 시스템(2B)을 마련한 것이고, 다른 구성은 마찬가지로 되어 있다.

[0111] 불휘발성 메모리 시스템(2B)은, MFD(Maneged Flash Drive)(21B), NVRAM(22) 및 NVM 컨트롤러(23A)를 구비하고 있다. 이 MFD(21B)로서는, 예를 들면, SSD(Solid State Drive), eMMC(Embedded Multi Media Card), SD 카드, USB(Universal Serial Bus) 메모리 등을 들 수 있다. 즉, 이 불휘발성 메모리 시스템(2B)은, 불휘발성 메모리 시스템(2)에서, NAND형 플래시 메모리(21) 대신에 MFD(21B)를 마련한 것이고, 다른 구성은 마찬가지로 되어 있다.

[0112] MFD(21B)는, 블록 단위(여기서는, 섹터(211S, 212S) 단위)로 데이터의 액세스가 행하여지는 NAND형 플래시를 탑재한 스토리지 디바이스이다. 이 MFD(21B)는, 전술한 ECC1 처리부(231)와 동등한 기능을 내장한 것을 특징으로 하고 있다. 그 때문에, 본 변형예의 NVM 컨트롤러(23A)는, 에러 정정 코드(ECC1)를 이용하여 비트 오류 검출 및 정정 처리를 행한 데이터를 MFD(21B)로부터 수신하고, ECC 베퍼(230)에 일시적으로 보존한다. MFD(21B)에 대해 기록을 행하는 경우에도, 데이터(21D)만을 송신한다. 이 MFD(21B)는 또한, 섹터(211S) 단위로 구성되는 데이터 블록(211)과, 섹터(212S) 단위로 구성되는 ECC2 블록(212)을 갖고 있다. 또한, 섹터(211S, 212S)에서의 데이터 구성은, 상기 실시의 형태에서의 페이지(211P, 212P)에서의 데이터 구성과 마찬가지로 되어 있지만, 에러 정정 코드(ECC1)를 보존하는 영역에는 NVM 컨트롤러(23)로부터는 액세스할 수가 없다.

[0113] 근래, MFD(21B)와 같은 기억 제품이 다수 존재하는데, 본 변형예에서는 그와 같은 제품을 탑재한 불휘발성 메모리 시스템에서도, 상기 실시의 형태와 같은 작용에 의해 같은 효과를 얻는 것이 가능하다.

[0114] 또한, 본 변형예에서는, NAND형 플래시 메모리(21) 대신에 MFD(21B)를 마련한 예에 관해 설명하였지만, 블록 단위(복수의 워드 단위)로 (일괄하여) 데이터 액세스를 행하는 기억 장치라면, 다른 디바이스라도 좋다. 즉, 예를 들면, 섹터 단위로 데이터의 액세스가 행하여지는 하드 디스크 등을 이용하도록 하여도 좋다.

#### 그 밖의 변형예

[0116] 이상, 실시의 형태 및 변형예를 들어서 발명을 설명하였지만, 본 발명은 이들의 실시의 형태 등으로 한정되지 않고, 여러가지의 변형이 가능하다.

[0117] 예를 들면, 상기 실시의 형태 등에서는, 데이터 기억 시스템에서의 워크 메모리의 한 예로서 DRAM을 들어서 설명하였지만, 이것으로는 한정되지 않고, DRAM 이외의 휘발성 메모리를 워크 메모리로서 이용하도록 하여도 좋다.

[0118] 또한, 상기 실시의 형태 등에서 설명한 NVM 컨트롤러(23, 23A)나 DRAM 컨트롤러(12)에서 기능(의 일부)을, CPU(10)측에서 담당하도록 하여도 좋다.

[0119] 또한, 상기 실시의 형태 등에서는, 데이터 기억 시스템이, CPU(10) 및 불휘발성 메모리 시스템(2)에 더하여 DRAM(11) 및 DRAM 컨트롤러(12)를 구비하고 있는 경우에 관해 설명하였지만, 경우에 따라서는, DRAM(11) 및 DRAM 컨트롤러(12)를 마련하지 않도록 하여도 좋다. 즉, CPU(10) 및 불휘발성 메모리 시스템에 의해서만 데이터 기억 시스템을 구성하도록 하여도 좋다.

[0120] 본 발명은 2011년 1월 25일자로 일본특허청에 특허출원된 일본특허원 제2011-12544호를 우선권으로 주장한다.

[0121] 당업자라면, 하기의 특허청구범위 또는 그 등가의 범위 내에서, 설계상의 필요 또는 다른 요인에 따라, 상기 실시의 형태에 대한 여러 가지 변형예, 조합예, 부분 조합예, 및 수정예를 실시할 수 있을 것이다.

#### 부호의 설명

[0122]

1, 1A, 1B : 데이터 기억 시스템 10 : CPU

11 : DRAM

12 : DRAM 컨트롤러

2 : 불휘발성 메모리 시스템

21, 21A : NAND형 플래시 메모리

211 : 데이터 블록

212 : ECC2 블록

211P, 212P : 페이지

21B : MFD

211S, 212S : 섹터

21D : 데이터

22 : NVRAM

22D : 데이터

23, 23A : NVM 컨트롤러

230 : ECC 버퍼

231 : ECC1 처리부

232 : ECC2 처리부

233 : CPU-I/F부

234 : 플래시 메모리-I/F부

235 : NVRAM-I/F부

236 : ECC 버퍼 제어부

237 : 플래시 메모리 제어부

238 : NVRAM 제어부

ECC1, ECC2 : 에러 정정 코드

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10