(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5064158号

(P5064158)

(45) 発行日 平成24年10月31日(2012.10.31)

(24) 登録日 平成24年8月17日(2012.8.17)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12 501P

請求項の数 10 (全 25 頁)

(21) 出願番号 特願2007-241375 (P2007-241375)

(22) 出願日 平成19年9月18日 (2007.9.18)

(65) 公開番号 特開2009-76497 (P2009-76497A)

(43) 公開日 平成21年4月9日 (2009.4.9)

審査請求日 平成22年7月12日 (2010.7.12)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 町田 洋弘

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 田代 吉成

最終頁に続く

(54) 【発明の名称】半導体装置とその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

電極パッドを備えた複数の半導体集積回路と、前記半導体集積回路を有する半導体チップが形成される半導体チップ形成領域を複数有する半導体基板と、前記電極パッドに配設された内部接続端子と、前記内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置の製造方法であって、

前記複数の半導体チップの前記電極パッドに前記内部接続端子を形成する内部接続端子形成工程と、

支持板に前記配線パターンの母材となる金属層が設けられた金属層付き支持板を準備する金属層付き支持板準備工程と、

前記半導体チップと対向する部分の前記金属層付き支持板にアライメントマーク形成用の樹脂の突出部を形成する位置に貫通部を形成する貫通部形成工程と、

前記内部接続端子と対向する部分の前記金属層に導電性端子を形成する導電性端子形成工程と、

前記内部接続端子と前記導電性端子とが対向するように、前記複数の半導体チップと前記金属層付き支持板とを対向配置させると共に、前記金属層付き支持板を押圧して、前記内部接続端子と前記金属層とを圧着する圧着工程と、

前記圧着工程後に、前記複数の半導体チップと前記金属層付き支持板との間、及び前記貫通部を前記樹脂で封止する封止工程と、

前記封止工程後に、前記支持板を除去して、前記支持板の前記貫通部に対応する部分の

10

20

前記樹脂に突出部を形成する突出部形成工程と、

前記突出部をアライメントマークとして用いて配線パターンを形成する配線パターン形成工程と、を含むことを特徴とする半導体装置の製造方法。

【請求項 2】

前記配線パターン形成工程は、

前記配線パターンの形成領域に対応する部分の前記金属層上を覆うレジスト膜を形成するレジスト膜形成工程と、

前記レジスト膜をマスクとして、前記金属層をエッチングして、前記配線パターンを形成する配線パターン形成工程と、を含むことを特徴とする請求項 1 記載の半導体装置の製造方法。

10

【請求項 3】

前記貫通部形成工程では、前記貫通部を少なくとも 2 つ以上形成することを特徴とする請求項 1 又は 2 記載の半導体装置の製造方法。

【請求項 4】

前記貫通部形成工程では、前記貫通部を前記配線パターンが形成される配線パターン形成領域以外の領域に対応する部分の前記金属層付き支持板に形成することを特徴とする請求項 1 ないし 3 のうち、いずれか一項記載の半導体装置の製造方法。

【請求項 5】

前記圧着工程では、前記金属層付き支持板に形成された前記貫通部をアライメントマークとして用いて、前記複数の半導体チップと前記金属層付き支持板を対向配置させることを特徴とする請求項 1 ないし 4 のうち、いずれか一項記載の半導体装置の製造方法。

20

【請求項 6】

前記封止工程では、前記樹脂をトランスマーモールド法により形成することを特徴とする請求項 1 ないし 5 のうち、いずれか一項記載の半導体装置の製造方法。

【請求項 7】

電極パッドを備えた複数の半導体集積回路と、前記半導体集積回路を有する半導体チップが形成される半導体チップ形成領域を複数有する半導体基板と、前記電極パッドに配設された内部接続端子と、前記内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置であって、

前記内部接続端子の上端部の側面を覆い、かつ、前記内部接続端子と前記配線パターンとを固定している導電性端子と、

30

前記半導体チップの上面を、前記内部接続端子及び前記導電性端子を除いて覆い、かつ、前記半導体基板と反対側の面に突出部を有する樹脂部材と、

前記樹脂部材の上面に設けられた前記配線パターンと、

前記配線パターンのパッド部を除いた部分と前記突出部とを覆うように、前記樹脂部材上に設けられたソルダーレジストと、を有することを特徴とする半導体装置。

【請求項 8】

前記突出部が、前記配線パターン作成用のアライメントマークであることを特徴とする請求項 7 記載の半導体装置。

40

【請求項 9】

前記樹脂部材本体は、平面視において四角形をなし、前記突出部は、前記樹脂部材本体の前記四角形の 4 つの角部の近傍に配置されていることを特徴とする請求項 7 又は 8 記載の半導体装置。

【請求項 10】

請求項 7 ないし 9 のうち、いずれか一項記載の半導体装置が切断され、個片化されて形成された、個片化された半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置とその製造方法に係り、電極パッドを備えた半導体チップと、電

50

極パッドに配設された内部接続端子と、内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置とその製造方法に関する。

【背景技術】

【0002】

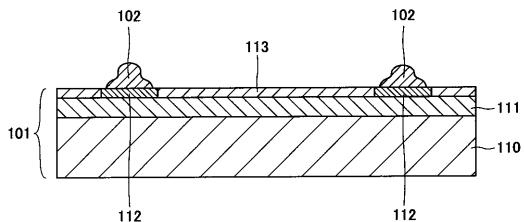

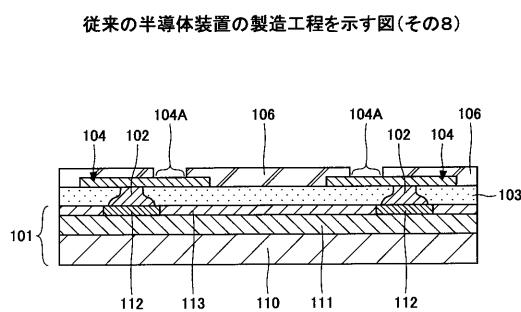

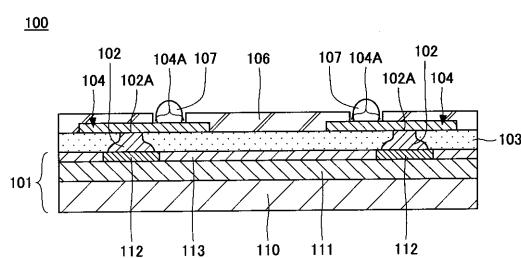

従来の半導体装置には、電極パッドを備えた半導体チップと、電極パッドに配設された内部接続端子と、内部接続端子と電気的に接続された配線パターンと、を備え、平面視した状態で半導体チップと略同じ大きさとされたチップサイズパッケージと呼ばれる半導体装置（例えば、図1参照）がある。

【0003】

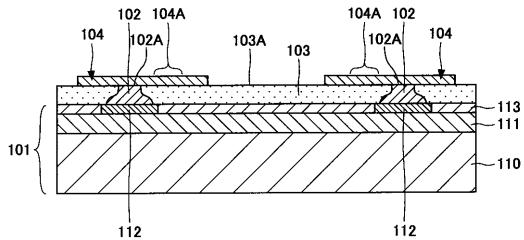

図1は、従来の半導体装置の断面図である。

10

【0004】

図1を参照するに、従来の半導体装置100は、半導体チップ101と、内部接続端子102と、樹脂層103と、配線パターン104と、ソルダーレジスト106と、外部接続端子107とを有する。

【0005】

半導体チップ101は、薄板化された半導体基板110と、半導体集積回路111と、複数の電極パッド112と、保護膜113とを有する。半導体集積回路111は、半導体基板110の表面側に設けられている。半導体集積回路111は、拡散層、絶縁層、及び配線パターン等（図示せず）から構成されている。複数の電極パッド112は、半導体集積回路111上に設けられている。複数の電極パッド112は、半導体集積回路111に設けられた配線パターンと電気的に接続されている。保護膜113は、半導体集積回路111上に設けられている。保護膜113は、半導体集積回路111を保護するための膜である。

20

【0006】

内部接続端子102は、電極パッド112上に設けられている。内部接続端子102の上端部は、樹脂層103から露出されている。内部接続端子102の上端部は、配線パターン104と接続されている。樹脂層103は、内部接続端子102が設けられた側の半導体チップ101を覆うように設けられている。

【0007】

配線パターン104は、樹脂層103上に設けられている。配線パターン104は、内部接続端子102と接続されている。配線パターン104は、内部接続端子102を介して、電極パッド112と電気的に接続されている。配線パターン104は、外部接続端子107が配設されるパッド104Aを有する。ソルダーレジスト106は、パッド104Aを除いた部分の配線パターン104を覆うように、樹脂層103上に設けられている。

30

【0008】

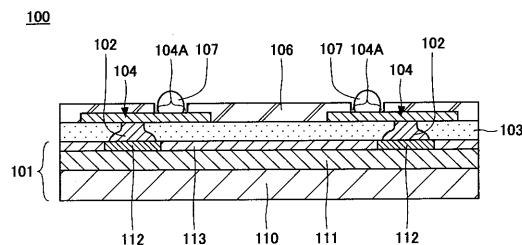

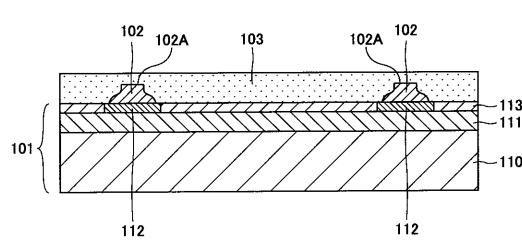

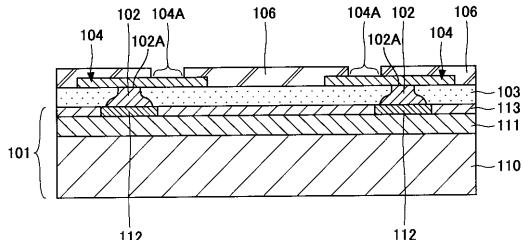

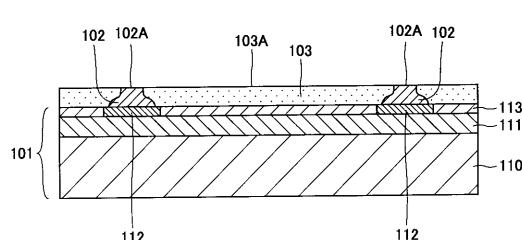

図2～図10は、従来の半導体装置の製造工程を示す図である。図2～図10において、図1に示す従来の半導体装置100と同一構成部分には同一符号を付す。

【0009】

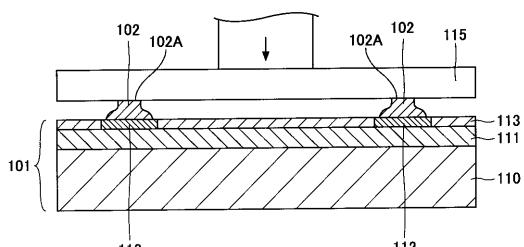

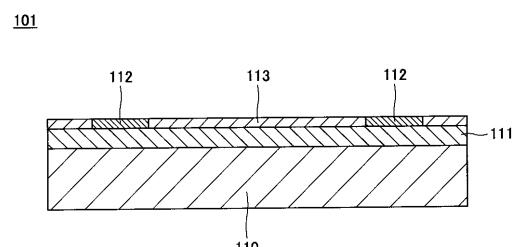

始めに、図2に示す工程では、薄板化される前の半導体基板110の表面側に、半導体集積回路111、複数の電極パッド112、及び保護膜113を有した半導体チップ101を形成する。次いで、図3に示す工程では、複数の電極パッド112上に内部接続端子102を形成する。この段階では、複数の内部接続端子102には、高さのばらつきがある。

40

【0010】

次いで、図4に示す工程では、複数の内部接続端子102に平坦な板115を押し当てて、複数の内部接続端子102の高さを揃える。これにより、複数の内部接続端子102の上面102Aは、略平坦な面とされる。次いで、図5に示す工程では、内部接続端子102が形成された側の半導体チップ101及び内部接続端子102を覆うように樹脂層103を形成する。

【0011】

50

次いで、図6に示す工程では、内部接続端子102の上面102Aが樹脂層103から露出するまで、樹脂層103を研磨する。このとき、樹脂層103の上面103Aが内部接続端子102の上面102Aと略面一となるように研磨を行う。これにより、図6に示す構造体の上面（具体的には、樹脂層103の上面103A及び内部接続端子102の上面102A）は、平坦な面になる。

【0012】

次いで、図7に示す工程では、平坦な面とされた図6に示す構造体の上面に配線パターン104を形成する。具体的には、配線パターン104は、例えば、図6に示す構造体の上面に金属箔（図示せず）を貼り付け、次いで、金属箔上を覆うようにレジスト（図示せず）を塗布し、次いで、このレジストを露光、現像することで配線パターン104の形成領域に対応する部分の金属箔上にレジスト膜（図示せず）を形成する。その後、上記レジスト膜をマスクとして金属箔をエッチングすることで、配線パターン104を形成する（サブトラクティブ法）。その後、レジスト膜を除去する。上記レジストの露光領域は、半導体集積回路111上に形成されたアライメントマーク（図示せず）の位置を赤外線又はX線透過機能を有した露光装置（図示せず）が検出することにより決定される。

10

【0013】

次いで、図8に示す工程では、樹脂層103上に、パッド104A以外の部分の配線パターン104を覆うソルダーレジスト106を形成する。

【0014】

次いで、図9に示す工程では、半導体基板110の裏面側から半導体基板110を研磨して、半導体基板110を薄板化する。次いで、図10に示す工程では、パッド104Aに外部接続端子107を形成する。これにより、半導体装置100が製造される（例えば、特許文献1参照。）。

20

【特許文献1】特許第3614828号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

しかしながら、従来の半導体装置100の製造方法では、複数の内部接続端子102の高さを揃える工程や、樹脂層103を研磨して複数の内部接続端子102の上面102Aを樹脂層103から露出させる工程が必要であるため、工程数の増加により、半導体装置100の製造コストが増加してしまうという問題があった。

30

【0016】

また、配線パターン104を形成するためのレジスト膜を形成する際に使用する赤外線又はX線透過機能を有した露光装置は、高価であるため、半導体装置100の製造コストが増加してしまうという問題があった。

【0017】

さらに、赤外線又はX線透過機能を有した露光装置を用いた場合、アライメントマークの検出精度が十分でないため、内部接続端子102に対する配線パターン104の位置精度が低下してしまうという問題があった。

【0018】

40

そこで本発明は、上述した問題点に鑑みなされたものであり、半導体装置の製造コストの低減を図ることができると共に、内部接続端子に対する配線パターンの位置精度を向上させることのできる半導体装置とその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0019】

本発明の一観点によれば、電極パッドを備えた複数の半導体集積回路と、前記半導体集積回路を有する半導体チップが形成される半導体チップ形成領域を複数有する半導体基板と、前記電極パッドに配設された内部接続端子と、前記内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置の製造方法であって、前記複数の半導体チップの前記電極パッドに前記内部接続端子を形成する内部接続端子形成工程と、支持板に前記配

50

線パターンの母材となる金属層が設けられた金属層付き支持板を準備する金属層付き支持板準備工程と、前記半導体チップと対向する部分の前記金属層付き支持板にアライメントマーク形成用の樹脂の突出部を形成する位置に貫通部を形成する貫通部形成工程と、前記内部接続端子と対向する部分の前記金属層に導電性端子を形成する導電性端子形成工程と、前記内部接続端子と前記導電性端子とが対向するように、前記複数の半導体チップと前記金属層付き支持板とを対向配置させると共に、前記金属層付き支持板を押圧して、前記内部接続端子と前記金属層とを圧着する圧着工程と、前記圧着工程後に、前記複数の半導体チップと前記金属層付き支持板との間、及び前記貫通部を前記樹脂で封止する封止工程と、前記封止工程後に、前記支持板を除去して、前記支持板の前記貫通部に対応する部分の前記樹脂に突出部を形成する突出部形成工程と、前記突出部をアライメントマークとして用いて配線パターンを形成する配線パターン形成工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

#### 【0020】

本発明によれば、複数の半導体チップの電極パッドに内部接続端子を形成し、支持板に配線パターンの母材となる金属層が設けられた金属層付き支持板に貫通部を形成し、その後、内部接続端子と対向する部分の金属層に導電性端子を形成し、次いで、内部接続端子と導電性端子とが対向するように、複数の半導体チップと金属層付き支持板とを対向配置させると共に、金属層付き支持板を押圧して、内部接続端子と金属層とを圧着した後、複数の半導体チップと金属層付き支持板との間及び貫通部を樹脂で封止することにより、複数の内部接続端子の高さを揃える工程、及び配線パターンと接続される部分の内部接続端子を樹脂から露出させるための樹脂研磨工程が不要となる。これにより、工程数を削減することができる。

#### 【0021】

また、封止工程後に支持板を除去して、支持板の貫通部に対応する部分の樹脂に突出部を形成し、その後、突出部をアライメントマークとして用いて配線パターンを形成することにより、内部接続端子に対する配線パターンの形成位置の精度を向上させることができる。

#### 【0022】

さらに、レジスト膜を形成する際、CCDカメラを備えた安価な露光装置を用いてアライメントマークである突出部の位置を検出することができるため、半導体装置の製造コストを低減することができる。

#### 【0023】

本発明の他の観点によれば、電極パッドを備えた複数の半導体集積回路と、前記半導体集積回路を有する半導体チップが形成される半導体チップ形成領域を複数有する半導体基板と、前記電極パッドに配設された内部接続端子と、前記内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置であって、前記内部接続端子の上端部の側面を覆い、かつ、前記内部接続端子と前記配線パターンとを固定している導電性端子と、前記半導体チップの上面を、前記内部接続端子及び前記導電性端子を除いて覆い、かつ、前記半導体基板と反対側の面に突出部を有する樹脂部材と、前記樹脂部材の上面に設けられた前記配線パターンと、前記配線パターンのパッド部を除いた部分と前記突出部とを覆うように、前記樹脂部材上に設けられたソルダーレジストと、を有することを特徴とする半導体装置が提供される。

#### 【0024】

本発明によれば、内部接続端子の上端部の側面を覆った導電性端子によって、内部接続端子と配線パターンとが固定されることができる。

#### 【0025】

また、配線パターンが形成される樹脂部材本体の上面に突出部を設けることにより、配線パターンをパターニングするためのレジスト膜を露光処理する際、アライメントマークとして突出部を用いることが可能となる。これにより、従来よりもレジスト膜の形成位置の精度が向上するため、内部接続端子に対する配線パターンの形成位置の精度を向上させ

10

20

30

40

50

ることができる。

【0026】

さらに、レジスト膜を形成する際、CCDカメラを備えた安価な露光装置を用いてアライメントマークである突出部の位置を検出することができるため、半導体装置の製造コストを低減することができる。

【発明の効果】

【0027】

本発明によれば、半導体装置の製造コストの低減を図ることができると共に、内部接続端子に対する配線パターンの形成位置の精度を向上させることができる。

【発明を実施するための最良の形態】

【0028】

次に、図面に基づいて本発明の実施の形態について説明する。

【0029】

(第1の実施の形態)

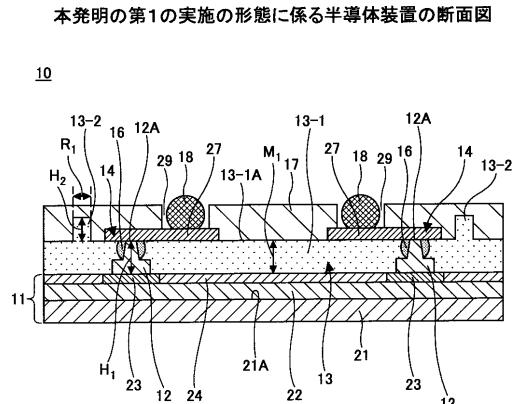

図11は、本発明の第1の実施の形態に係る半導体装置の断面図である。

【0030】

図11を参照するに、第1の実施の形態の半導体装置10は、半導体チップ11と、内部接続端子12と、樹脂部材13と、配線パターン14と、導電性端子16と、ソルダーレジスト17と、外部接続端子18とを有する。

【0031】

半導体チップ11は、半導体基板21と、半導体集積回路22と、電極パッド23と、保護膜24とを有する。半導体基板21は、半導体集積回路22を形成するための基板であり、薄板化されている。半導体基板21としては、例えば、シリコンからなる基板を用いることができる。半導体基板21の厚さは、例えば、 $100\mu\text{m} \sim 300\mu\text{m}$ とすることができる。

【0032】

半導体集積回路22は、半導体基板21の表面21A側に設けられている。半導体集積回路22は、半導体基板21に形成された拡散層(図示せず)、半導体基板21上に積層された絶縁層(図示せず)、及び積層された絶縁層に設けられ、拡散層(図示せず)と電気的に接続された配線パターン(図示せず)等から構成されている。

【0033】

電極パッド23は、半導体集積回路22上に複数設けられている。電極パッド23は、半導体集積回路22に設けられた配線パターン(図示せず)と電気的に接続されている。電極パッド23の材料としては、例えば、AlやAl合金(例えば、Al-Si-Cu合金)等を用いることができる。

【0034】

保護膜24は、半導体集積回路22上に設けられている。保護膜24は、半導体集積回路22を保護するための膜である。保護膜24としては、例えば、SiN膜やPSG膜等を用いることができる。

【0035】

内部接続端子12は、電極パッド23上に設けられている。内部接続端子12は、半導体集積回路22と配線パターン14とを電気的に接続するための端子である。内部接続端子12の上端部の上面12Aは、略平坦な面とされている。内部接続端子12の上端部の上面12Aは、配線パターン14の下面と接触している。これにより、電極パッド23は、配線パターン14と電気的に接続されている。また、内部接続端子12の上端部の上面12Aは、後述する樹脂部材本体13-1(樹脂部材13の構成要素の1つ)の上面13-1Aと略面一とされている。内部接続端子12の高さH<sub>1</sub>は、例えば、 $30\mu\text{m} \sim 50\mu\text{m}$ とすることができる。

【0036】

内部接続端子12としては、例えば、Auバンプ、Auめっき膜、無電解めっき法によ

10

20

30

40

50

り形成されたNi膜とそれを覆うAu膜から構成される金属膜等を用いることができる。内部接続端子12としてAuバンプを用いる場合、内部接続端子12は、例えば、ボンディング法やめっき法により形成することができる。

【0037】

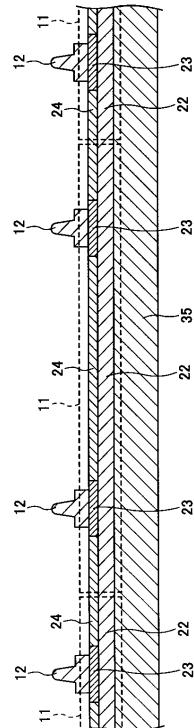

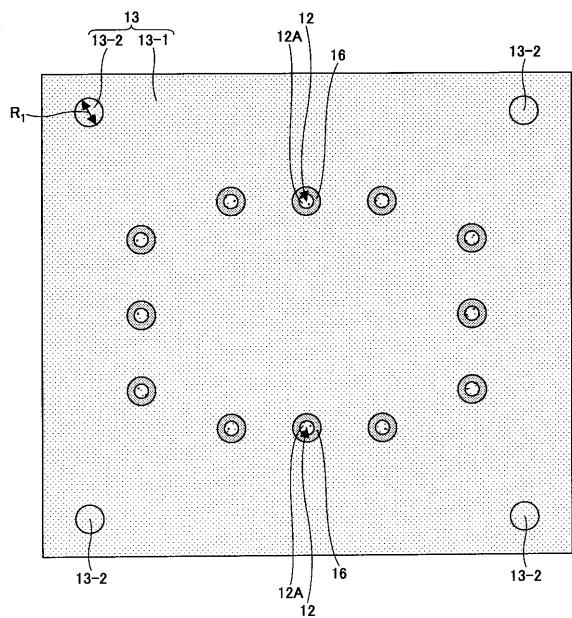

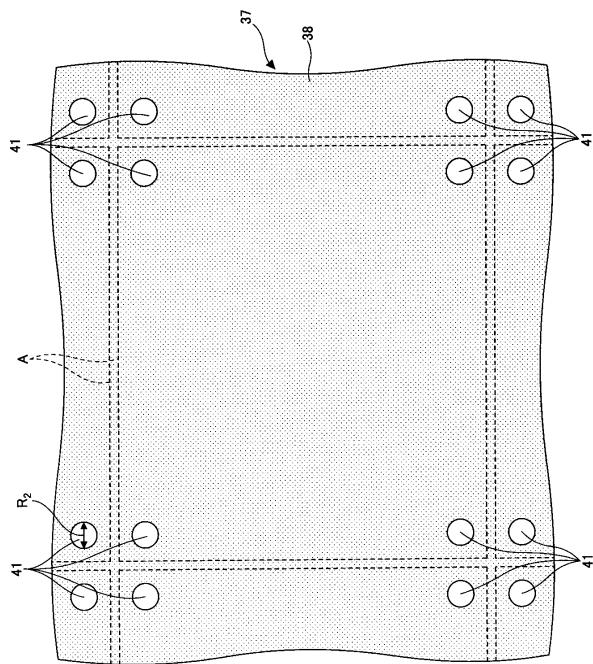

図12は、図11に示す半導体装置に設けられた樹脂部材を説明するための平面図である。図12において、図11に示す半導体装置10と同一構成部分には同一符号を付す。

【0038】

図11及び図12を参照するに、樹脂部材13は、樹脂部材本体13-1と、突出部13-2とを有する。樹脂部材本体13-1は、内部接続端子12の側面、内部接続端子12が設けられていない部分の電極パッド23の上面、及び保護膜24の上面を覆うように設けられている。樹脂部材本体13-1は、平面視四角形とされている。樹脂部材本体13-1の上面13-1Aは、略平坦な面とされている。樹脂部材本体13-1の上面13-1Aは、内部接続端子12の上端部の上面12Aと略面一とされている。樹脂部材本体13-1の上面13-1Aには、配線パターン14が形成されている。ソルダーレジスト17と保護膜24との間に配置された部分の樹脂部材本体13-1の厚さM<sub>1</sub>は、例えば、30μm～50μmとすることができます。

10

【0039】

突出部13-2は、円筒形状とされており、樹脂部材本体13-1の上面13-1Aに設けられている。突出部13-2は、樹脂部材本体13-1の4つの角部の近傍にそれぞれ1つずつ配置されている。突出部13-2は、配線パターン14をパターニングするための後述するレジスト膜を露光処理する際のアライメントマークとして用いる部材である。突出部13-2の直径R<sub>1</sub>は、例えば、100μmとすることができます。また、突出部13-2の高さH<sub>2</sub>は、例えば、50μmとすることができます。上記構成とされた樹脂部材13としては、例えば、アンダーフィル樹脂やモールド樹脂（例えば、エポキシ樹脂）等を用いることができる。

20

【0040】

このように、配線パターン14が形成される樹脂部材本体13-1の上面13-1Aに突出部13-2を設けることにより、配線パターン14の母材となる金属層（樹脂部材本体13-1の上面13-1Aに形成される金属層）をパターニングするためのレジスト膜を露光処理する際のアライメントマークとして突出部13-2を用いることが可能となる。これにより、従来よりもレジスト膜の形成位置の精度が向上するため、内部接続端子12に対する配線パターン14の形成位置の精度を向上させることができます。

30

【0041】

配線パターン14は、内部接続端子12の上端部の上面12Aと接触するように、樹脂部材本体13-1の上面13-1Aに設けられている。配線パターン14は、内部接続端子12を介して、半導体集積回路22と電気的に接続されている。配線パターン14は、パッド部27を有する。パッド部27は、外部接続端子18を配設するためのパッドであり、内部接続端子12から離間した位置に配置されている。配線パターン14としては、例えば、Cu膜を用いることができる。配線パターン14としてCu膜を用いた場合、配線パターン14の厚さは、例えば、12μmとすることができます。

40

【0042】

導電性端子16は、内部接続端子12と対向する部分の配線パターン14の下面に設けられている。導電性端子16は、内部接続端子12の上端部の側面を覆うように配置されている。導電性端子16は、内部接続端子12と配線パターン14とを固定するためのものである。導電性端子16としては、例えば、導電性ペースト（具体的には、例えば、AgペーストやCuペースト等）やバンプ（具体的には、例えば、Auバンプ、Cuバンプ等）等を用いることができる。

【0043】

ソルダーレジスト17は、パッド部27を除いた部分の配線パターン14と突出部13-2とを覆うように、樹脂部材13上に設けられている。ソルダーレジスト17は、パッ

50

ド部 27 を露出する開口部 29 を有する。

【 0 0 4 4 】

外部接続端子 18 は、パッド部 27 上に設けられている。外部接続端子 18 は、マザーボード等の実装基板（図示せず）に設けられた外部接続用パッド（図示せず）と接続される端子である。外部接続端子 18 としては、例えば、はんだバンプを用いることができる。

【 0 0 4 5 】

本実施の形態の半導体装置によれば、配線パターン 14 が形成される樹脂部材本体 13 - 1 の上面 13 - 1 A に突出部 13 - 2 を設けることにより、配線パターン 14 の母材となる金属層（樹脂部材本体 13 - 1 の上面 13 - 1 A に形成される金属層）をパターニングするためのレジスト膜を露光処理する際、アライメントマークとして突出部 13 - 2 を用いることが可能となる。これにより、従来よりもレジスト膜の形成位置の精度が向上するため、内部接続端子 12 に対する配線パターン 14 の形成位置の精度を向上させることができる。

【 0 0 4 6 】

また、配線パターン 14 の母材となる金属層（樹脂部材本体 13 - 1 の上面 13 - 1 A に形成される金属層）をパターニングするためのレジスト膜（図示せず）を形成する際、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）を用いてアライメントマークである突出部 13 - 2 を検出することが可能となるため、半導体装置 10 の製造コストを低減することができる。

10

20

【 0 0 4 7 】

なお、本実施の形態では、4 つの突出部 13 - 2 を平面視四角形とされた樹脂部材本体 13 - 1 の角部に設けた場合を例に挙げて説明したが、4 つの突出部 13 - 2 は、配線パターン 14 が形成される配線パターン形成領域以外の領域に対応する部分の樹脂部材本体 13 - 1 上に設けてよい。この場合、本実施の形態の半導体装置 10 と同様な効果を得ることができる。

【 0 0 4 8 】

また、本実施の形態では、4 つの突出部 13 - 2 を設けた場合を例に挙げて説明したが、突出部 13 - 2 は少なくとも 2 つ以上設けられておればよく、この場合も本実施の形態の半導体装置 10 と同様な効果を得ることができる。

30

【 0 0 4 9 】

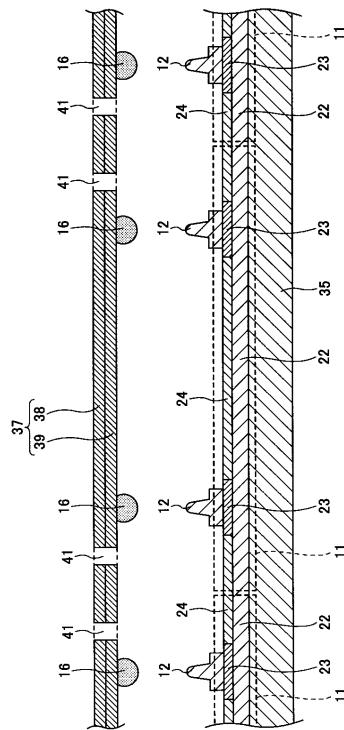

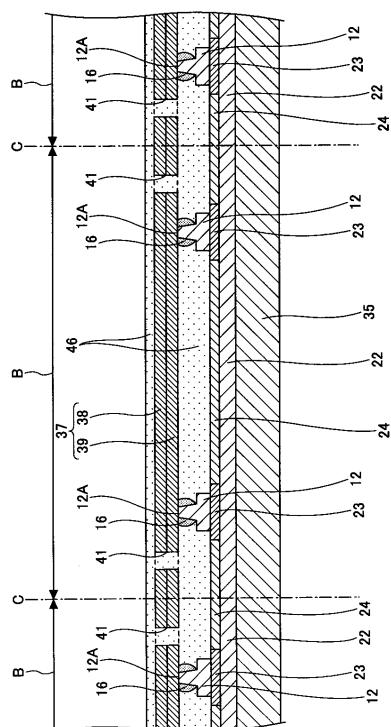

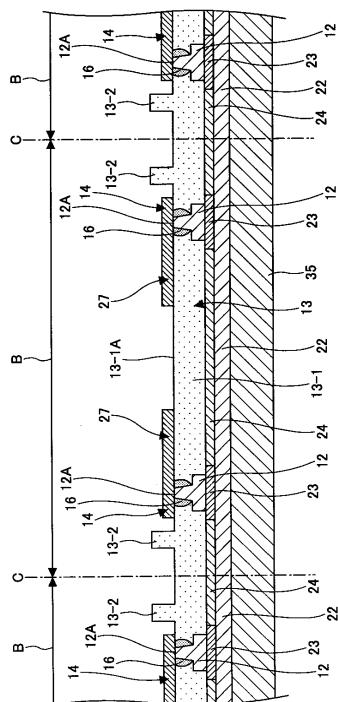

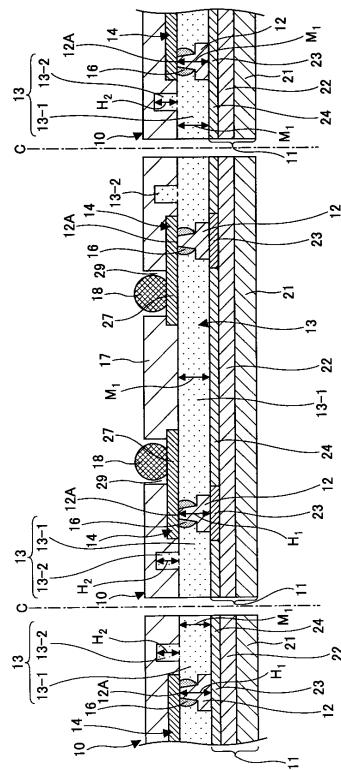

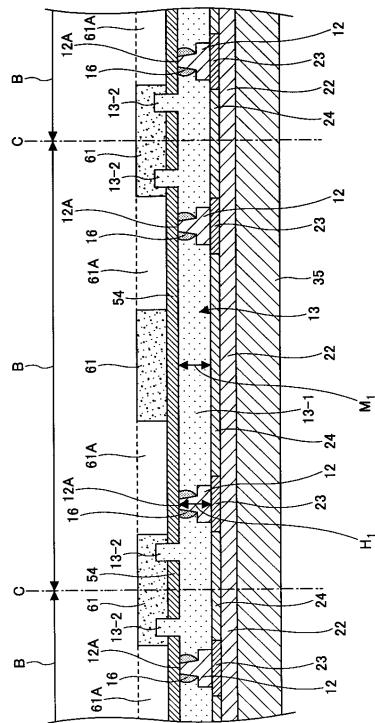

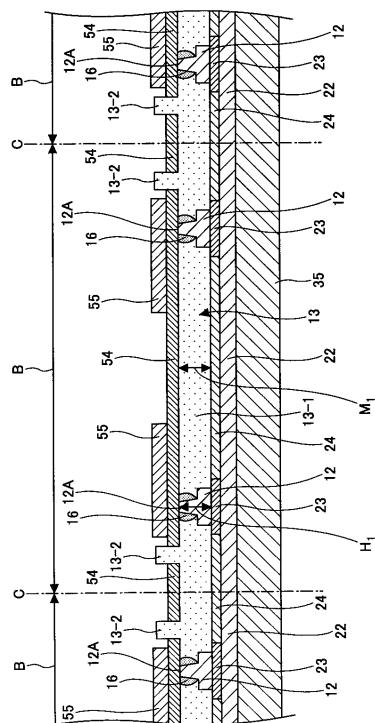

図 13 ~ 図 27 は、本発明の第 1 の実施の形態に係る半導体装置の製造工程を示す図である。図 28 は、金属層付き支持体に形成される貫通部を説明するための平面図である。図 13 ~ 図 28 において、第 1 の実施の形態の半導体装置 10 と同一構成部分には同一符号を付す。また、図 18 ~ 図 27 において、B は半導体装置 10 が形成される領域（以下、「半導体装置形成領域 B」とする）、C は複数の半導体装置 10 を個片化する際に半導体基板 35 を切断する位置（以下、「切断位置 C」とする）をそれぞれ示している。

【 0 0 5 0 】

図 13 ~ 図 28 を参照して、第 1 の実施の形態の半導体装置の製造方法について説明する。始めに、図 13 に示す工程では、複数の半導体チップ形成領域を有した半導体基板 35 に、半導体集積回路 22、電極パッド 23、及び保護膜 24 を有した複数の半導体チップ 11 を形成し、その後、電極パッド 23 上に内部接続端子 12 を形成する（内部接続端子形成工程）。半導体基板 35 は、後述する図 27 に示す工程において切断、個片化されることにより、図 11 で説明した半導体基板 21 となる基板である。半導体基板 35 としては、例えば、Si ウエハを用いることができる。半導体基板 35 の厚さは、例えば、500  $\mu\text{m}$  ~ 775  $\mu\text{m}$  とすることができる。電極パッド 23 の材料としては、Al や Al 合金（例えば、Al - Si - Cu 合金）を用いることができる。保護膜 24 としては、例えば、SiN 膜や PSG 膜等を用いることができる。

40

【 0 0 5 1 】

内部接続端子 12 としては、例えば、Al バンプ、Al めっき膜、無電解めっき法によ

50

り形成されたN<sub>i</sub>膜とそれを覆うAu膜から構成される金属膜等を用いることができる。内部接続端子12としてAuバンプを用いる場合、内部接続端子12は、例えば、ボンディング法やめつき法により形成する。なお、この段階では、複数の内部接続端子12には高さばらつきが存在する。また、この段階では、内部接続端子12の上端部の上面は、平坦な面とされていない。

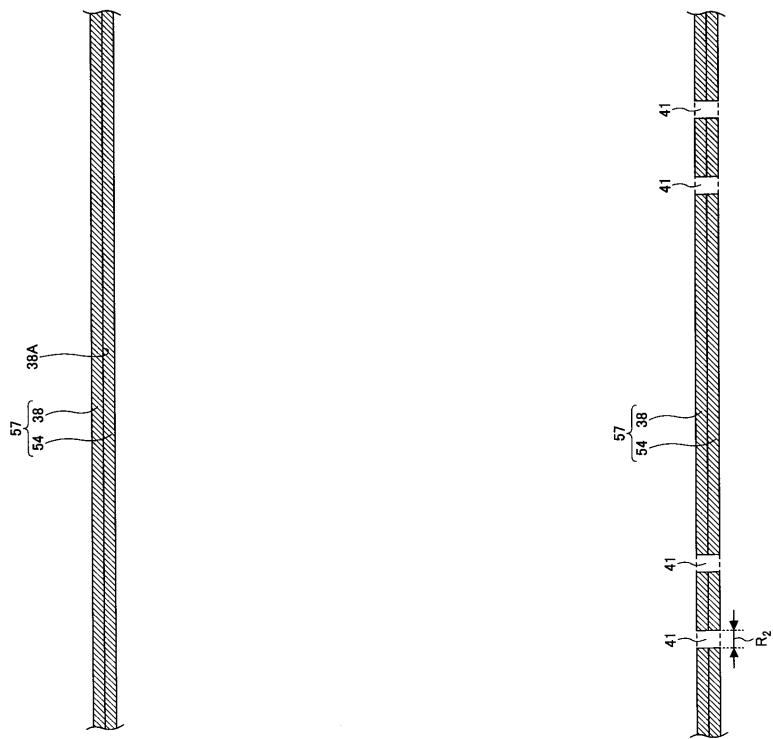

#### 【0052】

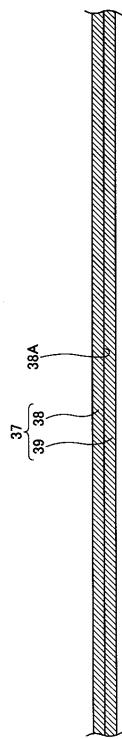

次いで、図14に示す工程では、支持板38の面38Aに配線パターン14の母材となる金属層39が貼り付けられた金属層付き支持板37を準備する（金属層付き支持板準備工程）。金属層39は、支持板38から剥がすことが可能な状態で、支持板38に貼り付けられている。支持板38は、金属層39を支持可能な板体で容易に剥離可能であればよい。具体的には、支持板38としては、例えば、金属板（例えば、Cu板）、金属箔（例えば、Cu箔）、樹脂板等を用いることができる。支持板38としてCu箔を用いた場合、支持板38の厚さは、例えば、35μmとすることができます。金属層39としては、例えば、Cu層を用いることができる。金属層39としてはCu層を用いた場合、金属層39の厚さは、例えば、12μmとすることができます。

10

#### 【0053】

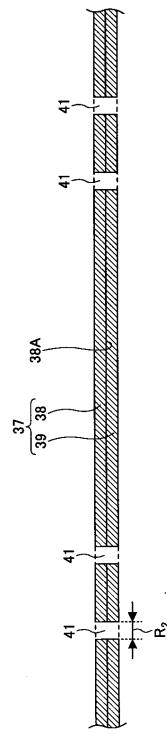

次いで、図15に示す工程では、図13に示す半導体チップ11と対向する部分の金属層付き支持板37に貫通部41を形成する（貫通部形成工程）。図28に示すように、貫通部41は、例えば、平面視四角形とされた半導体チップ11の外形位置Aの4つの角部と対向する部分の金属層付き支持板37にそれぞれ1つずつ形成する。貫通部41は、例えば、ルータ加工、ドリル加工、プレス加工等の方法により形成することができる。また、貫通部41の形状は、円筒、四角柱、スリット（溝）形状等を用いることができる（図15では、円筒形状とされた貫通部41を例に挙げて図示している）。貫通部41を円筒形状にした場合、貫通部41の直径R<sub>2</sub>は、例えば、100μmとすることができます。

20

#### 【0054】

次いで、図16に示す工程では、図13に示す構造体に設けられた内部接続端子12と対向する部分の金属層39に導電性端子16を形成する（導電性端子形成工程）。導電性端子16としては、例えば、導電性ペースト（具体的には、例えば、Agペースト、Cuペースト等）やバンプ（具体的には、例えば、Auバンプ、Cuバンプ等）等を用いることができる。

30

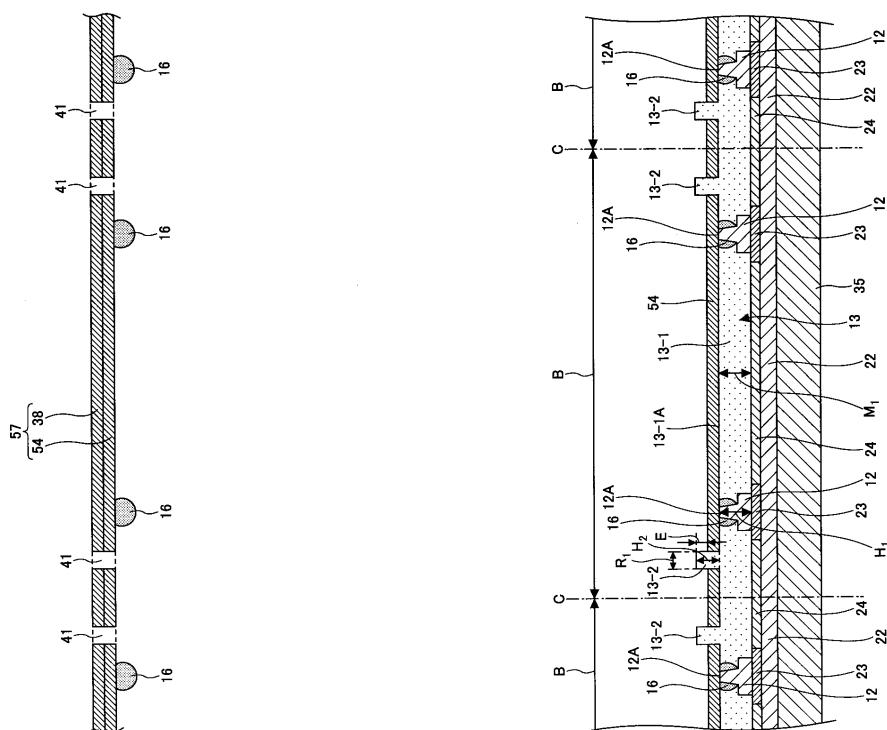

#### 【0055】

次いで、図17に示す工程では、金属層付き支持板37に形成された貫通部41をアライメントマークとして用いて、図13に示す構造体に設けられた内部接続端子12と、図16に示す構造体に設けられた導電性端子16とが対向するように、半導体基板35に形成された複数の半導体チップ11と金属層付き支持板37とを対向配置させる。

#### 【0056】

次いで、図18に示す工程では、内部接続端子12及び導電性端子16を加熱（導電性端子16としてAuバンプを用いた場合の加熱温度は、例えば、180℃）した状態で、内部接続端子12の上端部と金属層39とが接触するように金属層付き支持板37を押圧することで、内部接続端子12と金属層39とを圧着する（図17及び図18に示す工程が圧着工程）。このとき、複数の内部接続端子12の上端部と金属層39とが接触することで、複数の内部接続端子12の高さが揃えられると共に、複数の内部接続端子12の上端部の面12Aが略平坦な面になる。圧着工程後の内部接続端子12の高さH<sub>1</sub>は、例えば、30μm～50μmとすることができます。また、保護膜24と金属層39との隙間は、例えば、30μm～50μmとすることができます。

40

#### 【0057】

このように、半導体基板35に形成された複数の半導体チップ11と金属層付き支持板37とを対向配置する際のアライメントマークとして金属層付き支持板37に形成された貫通部41を用いることにより、内部接続端子12に対する導電性端子16の位置合わせを精度良く行うことが可能となるため、内部接続端子12と導電性端子16が設けられた

50

部分の金属層 39（配線パターン 14）との電気的な接続信頼性を向上させることができる。

【0058】

また、内部接続端子 12 及び導電性端子 16 を加熱した状態で、金属層付き支持体 37 を押圧して、内部接続端子 12 と金属層 39 とを圧着することにより、従来、別々に行われていた複数の内部接続端子 12 の高さを揃える工程と、内部接続端子 12 と配線パターン 14 とを接続する工程とを同時にを行うことが可能となるため、半導体装置 10 の製造コストを低減することができる。

【0059】

次いで、図 19 に示す工程では、半導体基板 35 に形成された複数の半導体チップ 11 10 と金属層付き支持基板 37 との間、及び貫通部 41 を樹脂で封止する（封止工程）。樹脂 46 は、先に説明した図 11 に示す樹脂部材 13 の母材である。樹脂 46 としては、例えば、アンダーフィル樹脂やモールド樹脂（例えば、エポキシ樹脂）等を用いることができる。

【0060】

樹脂 46 としてモールド樹脂を用いた場合、樹脂 46 は、トランスマルト法により形成することができる。この場合、図 19 に示すように、下部金型 43 と上部金型 44 との間に図 18 に示す構造体を収容し、その後、下部金型 43 と上部金型 44 との間に樹脂 46 を圧入することで、複数の半導体チップ 11 と金属層付き支持基板 37 との間、及び貫通部 41 を樹脂 46 で封止する。20

【0061】

また、トランスマルト法を用いて樹脂 46 を形成する場合、上部金型 44 と支持体 38 とが接触しないように、上部金型 44 と支持体 38 との間に隙間を形成するとい。このように、上部金型 44 と支持体 38 との間に隙間を形成することで、上部金型 44 により金属層付き支持体 37 が押圧されることがなくなるため、配線パターン 14 の母材となる金属層 39 が撓むことを防止できる。この場合、支持体 38 の上面を覆うように樹脂 46 が形成される。なお、図 19 に示す工程では、樹脂部材 13 の母材となる樹脂 46 をトランスマルト法により形成した場合を例に挙げて図示している。

【0062】

次いで、図 20 に示す工程では、樹脂 46 が形成された図 18 に示す構造体から図 19 30 に示す下部金型 43 及び上部金型 44 を除去する。

【0063】

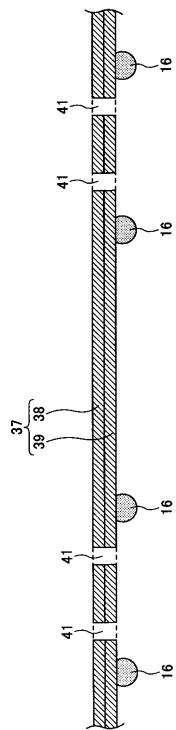

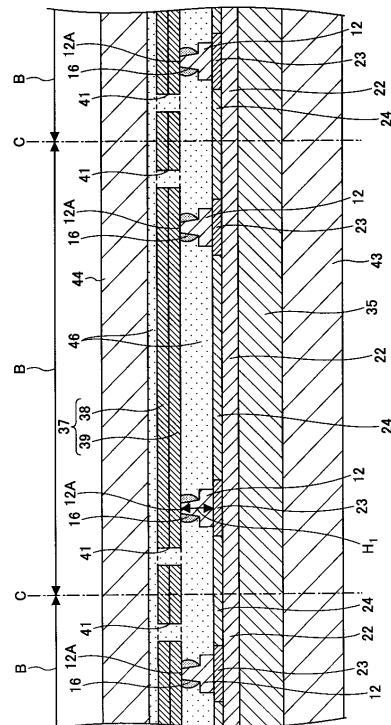

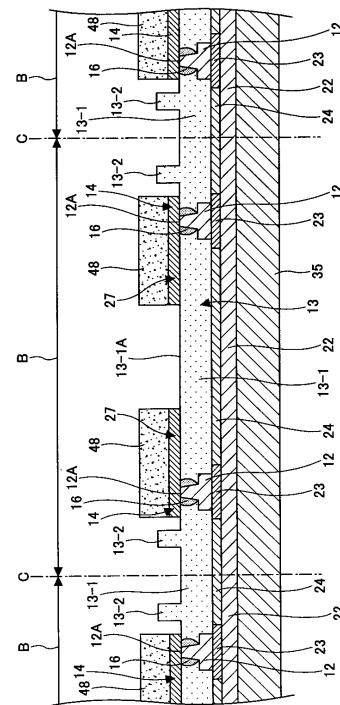

次いで、図 21 に示す工程では、図 20 に示す構造体に設けられた金属層 39 から支持体 38 を剥がして、支持体 38 と共に支持体 38 上に形成された樹脂 46 を除去することにより、突出部 13-2 を形成する（突出部形成工程）。これにより、樹脂部材本体 13-1 及び突出部 13-2 を備えた樹脂部材 13 が形成される。

【0064】

樹脂部材本体 13-1 の厚さ  $M_1$ （保護膜 24 と金属層 39 との間に配置された部分の樹脂部材本体 13-1 の厚さ）は、例えば、 $30 \mu m \sim 50 \mu m$  とすることができます。突出部 13-2 は、樹脂部材本体 13-1 の 4 つの角部の近傍にそれぞれ 1 つずつ形成されている。突出部 13-2 が円筒形状の場合、突出部 13-2 の直径  $R_1$  は、例えば、 $100 \mu m$  とすることができます。突出部 13-2 の高さ  $H_2$  は、例えば、 $50 \mu m$  とすることができます。また、金属層 39 の上面 39A を基準としたときの突出部 13-2 の突出量  $E$  40 は、例えば、 $38 \mu m$  とすることができます。

【0065】

次いで、図 22 に示す工程では、突出部 13-2 をアライメントマークとして用いて、配線パターン 14 の形成領域に対応する部分の金属層 39 上を覆うレジスト膜 48 を形成する（レジスト膜形成工程）。レジスト膜 48 は、金属層 39 をエッチングする際のマスクとなる膜である。具体的には、レジスト膜 48 がポジ型レジストの場合、金属層 39 上にレジストを塗布後、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）を 50

用いて、アライメントマークである突出部 13-2 の位置を検出し、配線パターン 14 の形成領域に対応する部分のレジストに光を照射して露光処理を行い、その後、露光後のレジストを現像処理することで、レジスト膜 48 を形成する。

【0066】

このように、配線パターン 14 の母材となる金属層 39 をパターニングするためのレジスト膜 48 を露光処理する際のアライメントマークとして突出部 13-2 を用いることにより、従来よりもレジスト膜 48 の形成位置の精度が向上するため、内部接続端子 12 に対する配線パターン 14 の形成位置の精度を向上させることができる。

【0067】

また、配線パターン 14 の母材となる金属層 39 をパターニングするためのマスクとなるレジスト膜（図示せず）を形成する際、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）を用いてアライメントマークである突出部 13-2 の位置を検出することが可能となるため、半導体装置 10 の製造コストを低減できる。

【0068】

次いで、図 23 に示す工程では、レジスト膜 48 をマスクとして、図 22 に示す金属層 39 をエッチング（具体的には、例えば、異方性エッチング）することで、内部接続端子 12 と接続された配線パターン 14 を形成する（配線パターン形成工程）。図 21～図 23 では、配線パターン 14 をサブトラクティブ法により形成する場合を例に挙げて図示している。

【0069】

配線パターン 14 は、外部接続端子 18 が配設されるパッド部 27 を有する。配線パターン 14 の厚さは、金属層 39 の厚さと略等しい。配線パターン 14 の厚さは、例えば、12  $\mu\text{m}$  とすることができます。次いで、図 24 に示す工程では、図 23 に示すレジスト膜 48 を除去する。

【0070】

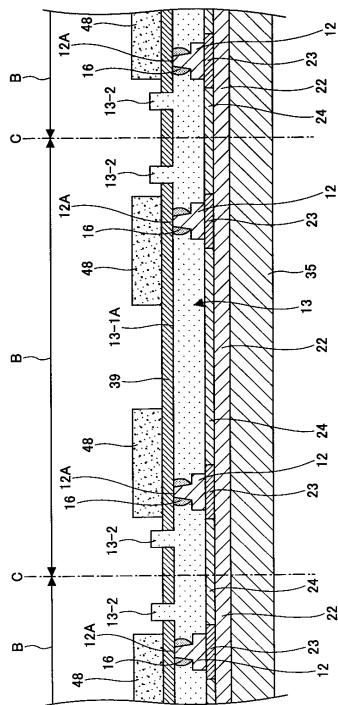

次いで、図 25 に示す工程では、周知の手法により、樹脂部材本体 13-1 の上面 13-1A にパッド部 27 を除いた部分の配線パターン 14 及び突出部 13-2 を覆うソルダーレジスト 17 を形成し、その後、パッド部 27 に外部接続端子 18 を形成する。ソルダーレジスト 17 は、パッド部 27 を露出する開口部 29 を有する。外部接続端子 18 としては、例えば、はんだバンプを用いることができる。

【0071】

次いで、図 26 に示す工程では、図 25 に示す半導体基板 35 の裏面 35B 側から半導体基板 35 を薄板化する。具体的には、半導体基板 35 の裏面 35B 側から半導体基板 35 を研磨又は研削して、半導体基板 35 を薄板化する。これにより、半導体基板 35 の半導体装置形成領域 B に半導体装置 10 に相当する構造体が形成される。半導体基板 35 の薄板化には、例えば、バックサイドグラインダーを用いることができる。薄板化後の半導体基板 35 の厚さは、例えば、100  $\mu\text{m}$  ~ 300  $\mu\text{m}$  とすることができます。

【0072】

次いで、図 27 に示す工程では、図 26 に示す構造体の切断位置 C に対応する部分を切断する。これにより、個片化されて、複数の半導体装置 10 が製造される。

【0073】

本実施の形態の半導体装置の製造方法によれば、内部接続端子 12 及び導電性端子 16 を加熱した状態で、金属層付き支持体 37 を押圧して、内部接続端子 12 と金属層 39 とを圧着することにより、従来、別々に行われていた複数の内部接続端子 12 の高さを揃える工程と、内部接続端子 12 と配線パターン 14 とを接続する工程とを同時に行うことが可能となるため、半導体装置 10 の製造コストを低減することができる。

【0074】

また、配線パターン 14 の母材となる金属層 39 をパターニングするためのマスクとなるレジスト膜 48 を露光処理する際、アライメントマークとして突出部 13-2 を用いることにより、従来よりもレジスト膜 48 の形成位置の精度が向上するため、内部接続端子

10

20

30

40

50

12に対する配線パターン14の形成位置の精度を向上させることができる。

【0075】

さらに、配線パターン14の母材となる金属層39をパターニングするためのマスクとなるレジスト膜48を形成する際、CCDカメラ(図示せず)を備えた安価な露光装置(図示せず)を用いてアライメントマークである突出部13-2の位置を検出することができるため、半導体装置10の製造コストを低減することができる。

【0076】

(第2の実施の形態)

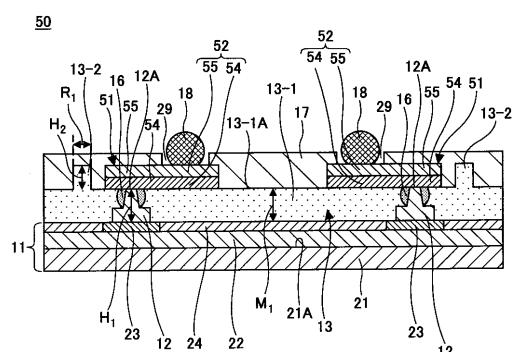

図29は、本発明の第2の実施の形態に係る半導体装置の断面図である。図29において、第1の実施の形態の半導体装置10と同一構成部分には同一符号を付す。

10

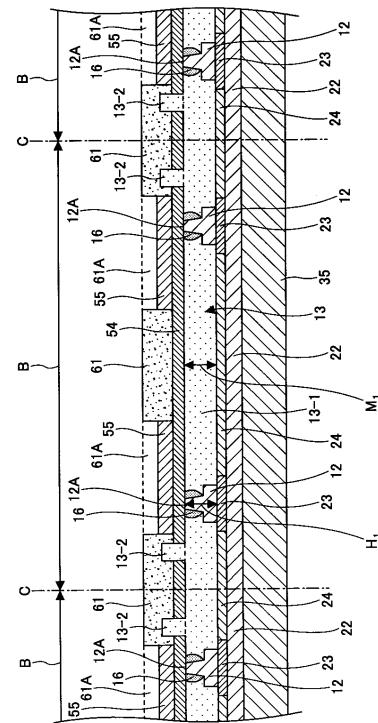

【0077】

図29を参照するに、第2の実施の形態の半導体装置50は、第1の実施の形態の半導体装置10に設けられた配線パターン14(サブトラクティブ法を用いて形成された配線パターン)の代わりに配線パターン51を設けた以外は半導体装置10と同様に構成される。

【0078】

配線パターン51は、金属層54と、めっき膜55とが積層された構成とされている。配線パターン51は、外部接続端子18が配設されるパッド部52を有する。金属層54は、内部接続端子12の上端部の上面12A及び樹脂部材本体13-1の上面13-1Aに設けられている。金属層54の下面是、内部接続端子12の上端部の上面12Aと接触している。金属層54の下面には、内部接続端子12を金属層54に接続するための導電性端子16が設けられている。金属層54は、めっき膜55を形成する際の給電層である。金属層54としては、例えば、Cu層を用いることができる。金属層54としてCu層を用いた場合、金属層54の厚さは、例えば、2μm~3μmとすることができます。

20

【0079】

めっき膜55は、金属層54上に積層されている。めっき膜55としては、例えば、Cuめっき膜を用いることができる。めっき膜55としてCuめっき膜を用いた場合、めっき膜55の厚さは、例えば、10μmとすることができる。めっき膜55は、例えば、電解めっき法により形成することができる。上記構成とされた配線パターン51は、例えば、セミアディティブ法により形成することができる。

30

【0080】

上記構成とされた第2の実施の形態の半導体装置50は、第1の実施の形態の半導体装置10と同様な効果を得ることができる。

【0081】

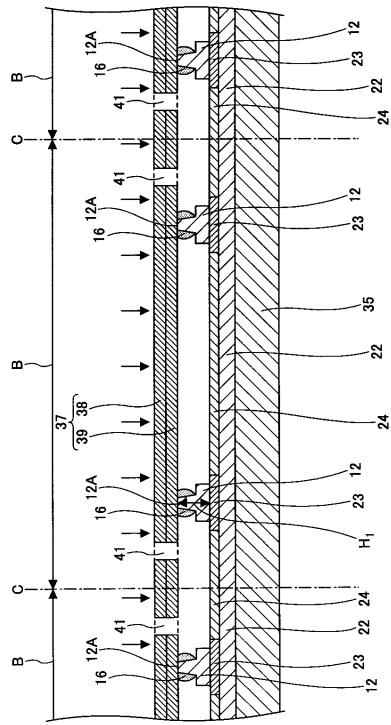

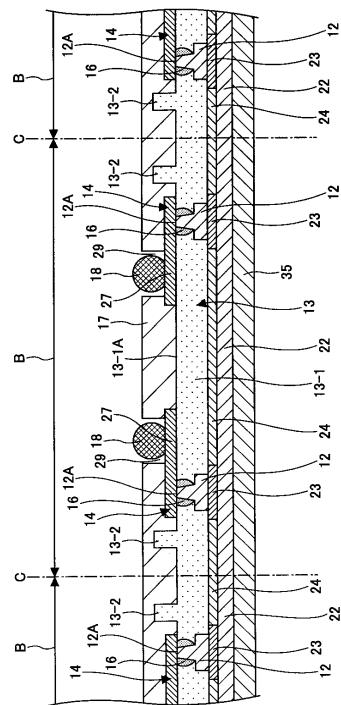

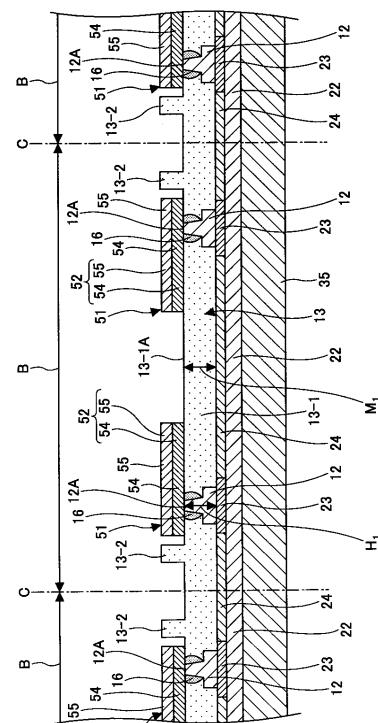

図30~図37は、本発明の第2の実施の形態に係る半導体装置の製造工程を示す図である。図30~図37において、第2の実施の形態の半導体装置50と同一構成部分には同一符号を付す。

【0082】

図30~図37を参照して、第2の実施の形態の半導体装置50の製造方法について説明する。始めに、第1の実施の形態で説明した図13に示す工程と同様な処理を行って、複数の半導体チップ形成領域を有した半導体基板35に、半導体集積回路22、電極パッド23、及び保護膜24を有した複数の半導体チップ11を形成し、その後、電極パッド23上に内部接続端子12を形成する(内部接続端子形成工程)。

40

【0083】

次いで、図30に示す工程では、支持板38の面38Aにめっき膜55(図29参照)を形成する際の給電層となる金属層54が貼り付けられた金属層付き支持板57を準備する(金属層付き支持板準備工程)。金属層54は、支持板38から剥がすことが可能な状態で、支持板38に貼り付けられている。支持板38は、金属層54を支持可能なものであればよい。具体的には、支持板38としては、例えば、金属板(例えば、Cu板)、金属箔(例えば、Cu箔)、樹脂板等を用いることができる。支持板38としてCu箔を用

50

いた場合、支持板 3 8 の厚さは、例えば、 $35 \mu m$  とすることができます。金属層 5 4 としては、例えば、Cu 層を用いることができる。金属層 5 4 としては Cu 層を用いた場合、金属層 5 4 の厚さは、例えば、 $2 \mu m \sim 3 \mu m$  とすることができます。

#### 【 0 0 8 4 】

次いで、図 3 1 に示す工程では、第 1 の実施の形態で説明した図 1 3 に示す半導体チップ 1 1 と対向する部分の金属層付き支持板 5 7 に貫通部 4 1 を形成する（貫通部形成工程）。貫通部 4 1 は、例えば、平面視四角形とされた半導体チップ 1 1 の外形位置 A の 4 つの角部と対向する部分の金属層付き支持板 3 7 にそれぞれ 1 つずつ形成する。貫通部 4 1 は、例えば、ルータ加工、ドリル加工、プレス加工等の方法を用いて形成することができる。また、貫通部 4 1 の形状は、円筒、四角柱、スリット（溝）形状等を用いることができる。貫通部 4 1 を円筒形状にした場合、貫通部 4 1 の直径  $R_2$  は、例えば、 $100 \mu m$  とすることができます。

#### 【 0 0 8 5 】

次いで、図 3 2 に示す工程では、第 1 の実施の形態で説明した図 1 3 に示す構造体に設けられた内部接続端子 1 2 と対向する部分の金属層 5 4 に導電性端子 1 6 を形成する（導電性端子形成工程）。導電性端子 1 6 としては、例えば、導電性ペースト（具体的には、例えば、Ag ペースト、Cu ペースト等）やバンプ（具体的には、例えば、Au バンプ、Cu バンプ等）等を用いることができる。

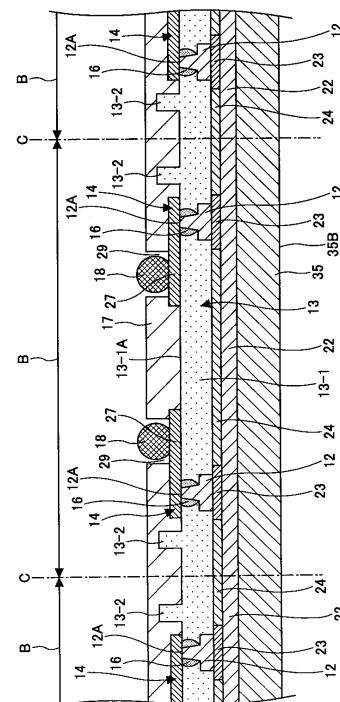

#### 【 0 0 8 6 】

次いで、図 3 3 に示す工程では、第 1 の実施の形態で説明した図 1 7 ~ 図 2 1 に示す工程（圧着工程、封止工程、突出部形成工程を含む）と同様な処理を行って、図 3 3 に示す構造体を形成する。圧着工程後の内部接続端子 1 2 の高さ  $H_1$  は、例えば、 $30 \mu m \sim 50 \mu m$  とすることができます。また、保護膜 2 4 と金属層 5 4 との隙間は、例えば、 $30 \mu m \sim 50 \mu m$  とすることができます。樹脂部材本体 1 3 - 1 の厚さ  $M_1$  は、例えば、 $30 \mu m \sim 50 \mu m$  とすることができます。突出部 1 3 - 2 は、樹脂部材本体 1 3 - 1 の 4 つの角部の近傍にそれぞれ 1 つずつ配置されている。突出部 1 3 - 2 が円筒形状の場合、突出部 1 3 - 2 の直径  $R_1$  は、例えば、 $100 \mu m$  とすることができます。突出部 1 3 - 2 の高さ  $H_2$  は、例えば、 $50 \mu m$  とすることができます。また、金属層 5 4 の上面を基準としたときの突出部 1 3 - 2 の突出量  $E$  は、例えば、 $48 \mu m$  とすることができます。

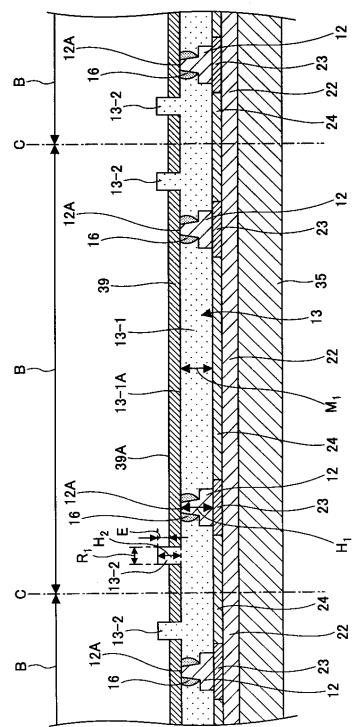

#### 【 0 0 8 7 】

次いで、図 3 4 に示す工程では、突出部 1 3 - 2 をアライメントマークとして用いて、配線パターン 5 1 の形成領域（具体的には、配線パターン 5 1 の構成要素の 1 つであるめっき膜 5 5 の形成領域）に対応する部分に開口部 6 1 A を有したレジスト膜 6 1 を樹脂部材 1 3 上及び金属層 5 4 上に形成する（レジスト膜形成工程）。具体的には、レジスト膜 6 1 がポジ型レジストの場合、レジスト膜 6 1 は、レジストを塗布後、露光装置（図示せず）により露光処理を行う際、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）により、アライメントマークである突出部 1 3 - 2 を用いて、配線パターン 5 1 の形成領域に対応する部分のレジストに光を照射して露光処理を行い、その後、露光後のレジストを現像処理することで、開口部 6 1 A を有したレジスト膜 6 1 を形成する。レジスト膜 6 1 は、配線パターン 5 1 の形成領域に対応する部分の金属層 5 4 上にのみめっき膜 5 5 を形成するためのマスクである。

#### 【 0 0 8 8 】

このように、配線パターン 5 1 の母材となる金属層 5 4 をパターニングするためのレジスト膜 6 1 を露光処理する際のアライメントマークとして突出部 1 3 - 2 を用いることにより、配線パターン 5 1 の形成領域（具体的には、配線パターン 5 1 の構成要素の 1 つであるめっき膜 5 5 の形成領域）に対応する部分に形成されるレジスト膜 6 1 の開口部 6 1 A の形成位置の精度が向上するため、内部接続端子 1 2 に対する配線パターン 5 1 の形成位置の精度を向上させることができる。

#### 【 0 0 8 9 】

また、配線パターン 5 1 の母材となる金属層 5 4 をパターニングするためのマスクとな

10

20

30

40

50

るレジスト膜 6 1 を形成する際、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）を用いてアライメントマークである突出部 13 - 2 の位置を検出することが可能となるため、半導体装置 5 0 の製造コストを低減できる。

【0090】

次いで、図 3 5 に示す工程では、金属層 5 4 を給電層とする電解めっき法により、開口部 6 1 A に露出された部分の金属層 5 4 上にめっき膜 5 5 を形成する（めっき膜形成工程）。めっき膜 5 5 としては、例えば、Cu めっき膜を用いることができる。めっき膜 5 5 として Cu めっき膜を用いた場合、めっき膜 5 5 の厚さは、例えば、10 μm とすることができます。

【0091】

次いで、図 3 6 に示す工程では、図 3 5 に示すレジスト膜 6 1 を除去する（レジスト膜除去工程）。次いで、図 3 7 に示す工程では、めっき膜 5 5 が形成されていない部分の金属層 5 4 を除去して、金属層 5 4 及びめっき膜 5 5 よりなる配線パターン 5 1 を形成する（配線パターン形成工程）。

【0092】

その後、第 1 の実施の形態で説明した図 2 5 ~ 図 2 7 に示す工程と同様な処理を行うことで、複数の半導体装置 5 0 が製造される。

【0093】

本実施の形態の半導体装置の製造方法によれば、配線パターン 5 1 の母材となる金属層 5 4 をパターニングするためのレジスト膜 6 1 を露光処理する際のアライメントマークとして突出部 13 - 2 を用いることにより、配線パターン 5 1 の形成領域（具体的には、配線パターン 5 1 の構成要素の 1 つであるめっき膜 5 5 の形成領域）に対応する部分に形成されるレジスト膜 6 1 の開口部 6 1 A の形成位置の精度が向上するため、内部接続端子 1 2 に対する配線パターン 5 1 の形成位置の精度を向上させることができる。

【0094】

また、配線パターン 5 1 の母材となる金属層 5 4 をパターニングするためのマスクとなるレジスト膜 6 1 を形成する際、CCD カメラ（図示せず）を備えた安価な露光装置（図示せず）を用いてアライメントマークである突出部 13 - 2 の位置を検出することが可能となるため、半導体装置 5 0 の製造コストを低減できる。

【0095】

以上、本発明の好ましい実施の形態について詳述したが、本発明はかかる特定の実施の形態に限定されるものではなく、特許請求の範囲内に記載された本発明の要旨の範囲内において、種々の変形・変更が可能である。

【産業上の利用可能性】

【0096】

本発明は、電極パッドを備えた半導体チップと、電極パッドに配設された内部接続端子と、内部接続端子と電気的に接続された配線パターンと、を備えた半導体装置とその製造方法に適用できる。

【図面の簡単な説明】

【0097】

【図 1】従来の半導体装置の断面図である。

【図 2】従来の半導体装置の製造工程を示す図（その 1）である。

【図 3】従来の半導体装置の製造工程を示す図（その 2）である。

【図 4】従来の半導体装置の製造工程を示す図（その 3）である。

【図 5】従来の半導体装置の製造工程を示す図（その 4）である。

【図 6】従来の半導体装置の製造工程を示す図（その 5）である。

【図 7】従来の半導体装置の製造工程を示す図（その 6）である。

【図 8】従来の半導体装置の製造工程を示す図（その 7）である。

【図 9】従来の半導体装置の製造工程を示す図（その 8）である。

【図 10】従来の半導体装置の製造工程を示す図（その 9）である。

10

20

30

40

50

【図11】本発明の第1の実施の形態に係る半導体装置の断面図である。

【図12】図11に示す半導体装置に設けられた樹脂部材を説明するための平面図である。

【図13】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その1)である。

【図14】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その2)である。

【図15】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その3)である。

【図16】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その4)である。 10

【図17】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その5)である。

【図18】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その6)である。

【図19】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その7)である。

【図20】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その8)である。

【図21】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その9)である。 20

【図22】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その10)である。

【図23】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その11)である。

【図24】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その12)である。

【図25】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その13)である。

【図26】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その14)である。 30

【図27】本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その15)である。

【図28】金属層付き支持体に形成される貫通部を説明するための平面図である。

【図29】本発明の第2の実施の形態に係る半導体装置の断面図である。

【図30】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その1)である。

【図31】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その2)である。

【図32】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その3)である。 40

【図33】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その4)である。

【図34】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その5)である。

【図35】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その6)である。

【図36】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その7)である。

【図37】本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その8)である。 50

ある。

【符号の説明】

【0098】

|                                 |           |    |

|---------------------------------|-----------|----|

| 10, 50                          | 半導体装置     |    |

| 11                              | 半導体チップ    |    |

| 12                              | 内部接続端子    |    |

| 13                              | 樹脂部材      |    |

| 13-1                            | 樹脂部材本体    |    |

| 13-1A                           | 上面        | 10 |

| 13-2                            | 突出部       |    |

| 14, 51                          | 配線パターン    |    |

| 16                              | 導電性端子     |    |

| 17                              | ソルダーレジスト  |    |

| 18                              | 外部接続端子    |    |

| 21, 35                          | 半導体基板     |    |

| 21A                             | 表面        |    |

| 22                              | 半導体集積回路   |    |

| 23                              | 電極パッド     |    |

| 24                              | 保護膜       |    |

| 27, 52                          | パッド部      | 20 |

| 29, 61A                         | 開口部       |    |

| 35B                             | 裏面        |    |

| 37                              | 金属層付き支持板  |    |

| 38                              | 支持板       |    |

| 38A                             | 面         |    |

| 39, 54                          | 金属層       |    |

| 39A                             | 上面        |    |

| 41                              | 貫通部       |    |

| 43                              | 下部金型      |    |

| 44                              | 上部金型      | 30 |

| 46                              | 樹脂        |    |

| 48, 61                          | レジスト膜     |    |

| 55                              | めっき膜      |    |

| A                               | 外形位置      |    |

| B                               | 半導体装置形成領域 |    |

| C                               | 切断位置      |    |

| E                               | 突出量       |    |

| H <sub>1</sub> , H <sub>2</sub> | 高さ        |    |

| M <sub>1</sub>                  | 厚さ        |    |

| R <sub>1</sub> , R <sub>2</sub> | 直径        | 40 |

【図1】

【図3】

従来の半導体装置の断面図

従来の半導体装置の製造工程を示す図(その2)

【図2】

【図4】

従来の半導体装置の製造工程を示す図(その1)

従来の半導体装置の製造工程を示す図(その3)

【図5】

【図7】

従来の半導体装置の製造工程を示す図(その4)

従来の半導体装置の製造工程を示す図(その6)

【図6】

【図8】

従来の半導体装置の製造工程を示す図(その5)

従来の半導体装置の製造工程を示す図(その7)

【図9】

【 1 0 】

### 従来の半導体装置の製造工程を示す図(その9)

【図 1 2】

【図11】

【図12】 【図13】

## 図11に示す半導体装置に設けられた樹脂部材を説明するための平面図

【図14】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その2) 本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その3)

【図15】

【図16】

【図17】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その4) 本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その5)

【図18】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その6) 本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その7)

【図20】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その8) 本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その9)

【 図 2 2 】

【 図 2 3 】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その10)

### 【図24】

【 図 25 】

## 本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その12)

## 【図26】

【図27】

本発明の第1の実施の形態に係る半導体装置の製造工程を示す図(その14)

【 図 2 8 】

### 【図29】

### 金属層付き支持体に形成される貫通部を説明するための平面図

【図30】

【図31】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その1) 本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その2)

【図3-2】

【 図 3 3 】

## 本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その3)

【図3-4】

【図35】

本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その5)

【図36】

【図37】

## 本発明の第2の実施の形態に係る半導体装置の製造工程を示す図(その7)

---

フロントページの続き

(56)参考文献 特許第3614828(JP,B2)

特開2001-250876(JP,A)

特開2006-13533(JP,A)

特開2002-118055(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12