(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-197258

(P2013-197258A)

(43) 公開日 平成25年9月30日(2013.9.30)

(51) Int.Cl.

|                   |                  |

|-------------------|------------------|

| <b>H01L 23/12</b> | <b>(2006.01)</b> |

| <b>H01L 25/07</b> | <b>(2006.01)</b> |

| <b>H01L 25/18</b> | <b>(2006.01)</b> |

| <b>H05K 3/46</b>  | <b>(2006.01)</b> |

F 1

|      |       |

|------|-------|

| H01L | 23/12 |

| H01L | 25/04 |

| H05K | 3/46  |

テーマコード(参考)

5E346

N

C

Q

審査請求 未請求 請求項の数 10 O L (全 17 頁)

(21) 出願番号

特願2012-61846 (P2012-61846)

(22) 出願日

平成24年3月19日 (2012.3.19)

(71) 出願人 000004547

日本特殊陶業株式会社

愛知県名古屋市瑞穂区高辻町14番18号

(74) 代理人 110000028

特許業務法人明成国際特許事務所

(72) 発明者 高山 泰史

名古屋市瑞穂区高辻町14番18号 日本

特殊陶業株式会社内F ターム(参考) 5E346 AA02 AA12 AA22 AA38 CC17

CC18 CC19 CC32 DD12 EE02

EE08 EE18 FF18 GG26 GG28

HH08

(54) 【発明の名称】回路基板、半導体モジュールの製造方法

## (57) 【要約】

【課題】半導体素子と配線基板との絶縁性の向上。

【解決手段】半導体素子150が第2接合層140の開口部145内に配置されると、接合層120において、開口部145の深さHと、開口部145の天面145aと半導体素子150の裏面155との間の距離hとの差分hに相当する余剰部が生じる。第2の配線基板110が半導体素子150の裏面側、すなわち、第2接合層140の第2の面142上に積層して配置され、配線基板110、110、半導体素子150および接合層120が拡散接合による加熱・加圧により一体化に接合されると、接合層120の余剰部は、接合時の加熱、圧縮による変形により、開口部145の側壁145bと半導体素子150の側面154との間の空隙を充填するよう変形する。この結果、半導体素子150の側面154の周囲は、第2接合層140により封止される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

回路基板であって、

ピアおよびパターン配線が形成された配線基板と、

前記配線基板の所定面上に積層して配置され、前記配線基板と半導体素子とを接合するとともに、無機系材料を主成分とする接合層と、を備え、

前記接合層は、

前記ピアに対応する位置に形成された少なくとも一つの貫通孔と、

前記貫通孔と連通し、前記配線基板が積層される面とは異なる面側に形成され、前記半導体素子を配置するための開口部と、

前記貫通孔内に配置され、前記開口部に配置される前記半導体素子の電極部と前記配線基板とを導通する導電接合部と、を有し、

前記半導体素子が前記開口部内に配置されたときに、前記開口部の深さが、前記開口部の天面と前記半導体素子の底面との間の距離より大きいことを特徴とする、回路基板。

**【請求項 2】**

請求項 1 記載の回路基板であって、

前記貫通孔は、前記導電接合部の体積と、前記半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成されており、

前記開口部の深さは、前記半導体素子の筐体の厚みより大きいことを特徴とする、

回路基板。

**【請求項 3】**

請求項 1 または請求項 2 記載の回路基板であって、

前記接合部は、前記開口部の深さと、前記開口部の天面と前記半導体素子の底面との間の距離と、の差分に対応する前記接合層の余剰部分の体積は、前記半導体素子と前記開口部との間に形成される空隙の容積以上となるように形成されている、

回路基板。

**【請求項 4】**

請求項 1 または請求項 2 記載の回路基板であって、

前記開口部は、テープ状に形成されている、

回路基板。

**【請求項 5】**

請求項 1 または請求項 2 記載の回路基板であって、

前記開口部の内壁は、前記積層の方向に沿った平面状に形成されている、

回路基板。

**【請求項 6】**

半導体モジュールの製造方法であって、

ピアとパターン配線が形成された第 1 の配線基板および第 2 の配線基板を製造する工程と、

無機系材料を主成分とする接合層を前記第 1 の配線基板の所定面上に積層して配置する工程と、

前記接合層に、

前記ピアに対応する位置に少なくとも一つの貫通孔を形成すること、および、

天面を有するとともに、前記貫通孔と連通し、半導体素子が配置されたときに、前記天面と前記半導体素子の底面との間の距離より大きな深さを有する開口部を前記第 1 の配線基板が配置されている第 1 の面とは異なる面側に形成すること、を含む工程と、

前記貫通孔内に、前記半導体素子の電極部と前記第 1 の配線基板とを導通するための導電接合部を形成する工程と、

前記導電接合部と、前記半導体素子の前記電極部とが導通可能となるように、前記開口部内に前記半導体素子を接合する工程と、

前記第 2 の配線基板を、前記接合層の前記第 1 の面とは反対側の第 2 の面上に配置する

10

20

30

40

50

工程と、

前記第1の配線基板、前記第2の配線基板、前記接合層および前記半導体素子を、加熱圧着し、前記第1の配線基板と前記接合層、および、前記接合層と前記第2の配線基板を拡散接合する工程と、を備える半導体モジュールの製造方法。

【請求項7】

請求項6記載の半導体モジュールの製造方法であって、

前記貫通孔は、前記導電接合部の体積と、前記半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成され、

前記開口部は、前記半導体素子の筐体の厚みより大きい深さを有するように形成される、

半導体モジュールの製造方法。

【請求項8】

請求項6または請求項7記載の半導体モジュールの製造方法であって、

前記開口部の深さと、前記開口部の天面と前記半導体素子の底面との間の距離と、の差分に対応する前記接合層の余剰部分の体積は、前記半導体素子と前記開口部との間に形成される空隙の容積以上となるように形成する、

半導体モジュールの製造方法。

【請求項9】

請求項6ないし請求項8記載の半導体モジュールの製造方法であって、

前記開口部は、テープ状に形成される、

半導体モジュールの製造方法。

【請求項10】

請求項6ないし請求項8記載の半導体モジュールの製造方法であって、

前記開口部の内壁は、前記積層の方向に沿った平面状に形成される、

半導体モジュールの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、多層基板により構成される回路基板、回路基板に半導体素子が搭載された半導体パワーモジュール、および、それらの製造方法に関する。

【背景技術】

【0002】

従来から、表裏両面に電極を備えた半導体素子と、半導体素子の各々の面に接合される配線基板と、配線基板と半導体素子の間を絶縁するための絶縁層とを備える多層構造の半導体モジュールが利用されている。半導体素子と配線基板との間を封止する方法として、例えば、半導体素子を収容可能に形成された開口部を有する絶縁性の封止層を用いる方法が利用されている。この方法では、半導体素子を封止層の開口部に嵌め込んで配線基板により挟み込み、配線基板、半導体素子および絶縁層を加熱圧着することにより、半導体素子と配線基板とが封止・接合される。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006-66582号公報

【特許文献2】特開2010-287869号公報

【特許文献3】特開2009-170930号公報

【特許文献4】特開2004-253579号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、従来の技術では、半導体素子を開口部内へ円滑に嵌め込むために、開口

10

20

30

40

50

部は半導体素子の外形よりも大きく形成されている必要がある。すなわち、積層方向の断面において、開口部の断面積は、半導体素子の断面積よりも大きい。そのため、半導体素子の実装後において、半導体素子の側面と開口部の側壁との間に空隙が生じ、半導体素子と配線基板との絶縁性能が低下するおそれがある。

【0005】

本発明は上述の課題に鑑みてなされたものであり、半導体素子と配線基板との絶縁性の向上を目的とする。

【課題を解決するための手段】

【0006】

本発明は、上述の課題の少なくとも一部を解決するためになされたものであり、以下の形態又は適用例として実現することが可能である。 10

【0007】

[適用例1]

回路基板であって、ビアおよびパターン配線が形成された配線基板と、前記配線基板の所定面上に積層して配置され、前記配線基板と半導体素子とを接合するとともに、無機系材料を主成分とする接合層と、を備え、前記接合層は、前記ビアに対応する位置に形成された少なくとも一つの貫通孔と、前記貫通孔と連通し、前記配線基板が積層される面とは異なる面側に形成され、前記半導体素子を配置するための開口部と、前記貫通孔内に配置され、前記開口部に配置される前記半導体素子の電極部と前記配線基板とを導通する導電接合部と、を有し、前記半導体素子が前記開口部内に配置されたときに、前記開口部の深さが、前記開口部の天面と前記半導体素子の底面との間の距離より大きいことを特徴とする、回路基板。 20

【0008】

適用例1の回路基板によれば、接合層の開口部は、開口部の深さが、開口部の天面と半導体素子の底面との間の距離よりも大きくなるように形成されている。従って、接合層において、開口部の深さと、開口部の天面と半導体素子の底面との間の距離との差分に相当する余剰部材を生じさせることができる。よって、配線基板と接合層の間や、接合層の開口部の側壁と半導体素子の側面との間に空隙が生じた場合、当該空隙を余剰部材で補填(充填)することができる。従って、半導体素子と配線基板との間の絶縁性の向上による半導体素子の沿面放電の防止や、空隙が存在することによる半導体素子の損傷の抑制を図ることができる。また、配線基板に製造上生じる反りに起因して配線基板と接合層との間に空隙が生じた場合にも、当該空隙を余剰部材で補填(充填)することができる。従って、配線基板と接合層との間の接合強度を向上できる。 30

【0009】

[適用例2]

適用例1記載の回路基板であって、前記貫通孔は、前記導電接合部の体積と、前記半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成されており、前記開口部の深さは、前記半導体素子の筐体の厚みより大きいことを特徴とする、回路基板。

【0010】

適用例2の回路基板によれば、貫通孔は、導電接合部の体積と、半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成され、開口部は、深さが半導体素子の厚みより大きくなるように形成されている。従って、開口部への半導体素子の実装時、電極部の全体が貫通孔内へ収容され、半導体素子の筐体の上面と開口部の天面とを確実に接触させることができる。よって、半導体素子の筐体の上面と接合層との間の絶縁性を確保でき、この結果、半導体素子の沿面放電の防止をすることができる。また、半導体素子の側面と開口部の側壁の間に形成される空隙を、接合層の余剰部材により充填することができる。 40

【0011】

[適用例3]

適用例1または適用例2の回路基板であって、前記接合部は、前記開口部の深さと、前

10

20

30

40

50

記開口部の天面と前記半導体素子の底面との間の距離と、の差分に対応する前記接合層の余剰部分の体積は、前記半導体素子と前記開口部との間に形成される空隙の容積以上である、回路基板。

【0012】

適用例3の回路基板によれば、接合層は、余剰部分の体積が、半導体素子と開口部との間に形成される空隙の容積以上となるように形成されている。従って、半導体素子と開口部との間に形成される空隙を、より確実に充填できる。

【0013】

[適用例4]

適用例1または適用例2記載の回路基板であって、前記開口部は、テープ状に形成されている、回路基板。

【0014】

適用例4の回路基板によれば、開口部がテープ形状となるように形成されている。従って、接合層と配線基板との接合時に積層方向に加圧され、空隙の充填効率を向上でき、気泡の発生を抑制できる。よって、配線基板と半導体素子との間の絶縁性を向上できる。

【0015】

[適用例5]

適用例1ないし適用例3記載の回路基板であって、前記開口部の内壁は、前記積層の方向に沿った平面状に形成されている、回路基板。

【0016】

適用例5の回路基板によれば、開口部の内壁は、積層方向に沿った平面状に形成されている。従って、開口部を、例えばパンチングなど、簡易な方法により製造できる。

【0017】

[適用例6]

半導体モジュールの製造方法であって、ピアとパターン配線が形成された第1の配線基板および第2の配線基板を製造する工程と、無機系材料を主成分とする接合層を前記第1の配線基板の所定面上に積層して配置する工程と、前記接合層に、前記ピアに対応する位置に少なくとも一つの貫通孔を形成すること、および、天面を有するとともに、前記貫通孔と連通し、前記半導体素子が配置されたときに、前記天面と前記半導体素子の底面との間の距離より大きな深さを有する開口部を前記第1の配線基板が配置されている第1の面とは異なる面側に形成すること、を含む工程と、前記貫通孔内に、前記半導体素子の電極部と前記第1の配線基板とを導通するための導電接合部を形成する工程と、前記導電接合部と、前記半導体素子の前記電極部とが導通可能となるように、前記開口部内に前記半導体素子を接合する工程と、前記第2の配線基板を、前記接合層の前記第1の面とは反対側の第2の面上に配置する工程と、前記第1の配線基板、前記第2の配線基板、前記接合層および前記半導体素子を、加熱圧着し、前記第1の配線基板と前記接合層、および、前記接合層と前記第2の配線基板を拡散接合する工程と、を備える半導体モジュールの製造方法。

【0018】

適用例6の半導体モジュールの製造方法によれば、開口部の深さが、開口部の天面と半導体素子の底面との間の距離よりも大きくなるように接合層が形成される。従って、接合層において、開口部の深さと、開口部の天面と半導体素子の底面との間の距離との差分に相当する余剰部材を生じさせることができる。よって、配線基板と接合層の間や、接合層の開口部の側壁と半導体素子の側面との間に空隙が生じた場合に、接合における加熱・圧着により、当該空隙を余剰部材で補填(充填)することができる。従って、半導体素子と配線基板との間の絶縁性の向上による半導体素子の沿面放電の防止や、空隙が存在することによる半導体素子の損傷の抑制を図ることができる。

【0019】

[適用例7]

適用例6記載の半導体モジュールの製造方法であって、前記貫通孔は、前記導電接合部

10

20

30

40

50

の体積と、前記半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成され、前記開口部は、前記半導体素子の筐体の厚みより大きい深さを有するように形成される、半導体モジュールの製造方法。

【0020】

適用例7の半導体モジュールの製造方法によれば、貫通孔は、導電接合部の体積と、半導体素子の前記電極部の体積との積算体積以上の容積を有するように形成され、開口部は、深さが半導体素子の厚みより大きくなるように形成されている。従って、開口部への半導体素子の実装時、電極部の全体が貫通孔内へ収容され、半導体素子の筐体の上面と開口部の天面とを確実に接触させることができる。よって、半導体素子の筐体の上面と接合層との間の絶縁性を確保でき、この結果、半導体素子の沿面放電の防止をすることができる。また、半導体素子の側面と開口部の側壁の間に形成される空隙を、接合層の余剰部材により充填することができる。

10

【0021】

【適用例8】

適用例6または適用例7記載の半導体モジュールの製造方法であって、前記開口部の深さと、前記開口部の天面と前記半導体素子の底面との間の距離と、の差分に対応する前記接合層の余剰部分の体積は、前記半導体素子と前記開口部との間に形成される空隙の容積以上となるように形成する、半導体モジュールの製造方法。

【0022】

適用例8の回路基板によれば、接合層は、余剰部分の体積が、半導体素子と開口部との間に形成される空隙の容積以上となるように形成される。従って、半導体素子と開口部との間に形成される空隙を、より確実に充填できる。

20

【0023】

【適用例9】

適用例6ないし適用例9いずれかに記載の半導体モジュールの製造方法であって、前記開口部は、テーパ状に形成される、半導体モジュールの製造方法。

【0024】

適用例9の半導体モジュールの製造方法によれば、開口部がテーパ形状となるように形成されている。従って、接合層と配線基板との接合時に積層方向に加圧されることにより、空隙の充填効率を向上でき、気泡の発生を抑制できる。

30

【0025】

【適用例10】

適用例6ないし適用例9いずれかに記載の半導体モジュールの製造方法であって、前記開口部の内壁は、前記積層の方向に沿った平面状に形成される、半導体モジュールの製造方法。

【0026】

適用例10の回路基板によれば、開口部の内壁は、積層方向に沿った平面状に形成される。従って、開口部の形成において、例えばパンチングなど、簡易な方法を利用できる。

【0027】

本発明において、上述した種々の態様は、適宜、組み合わせたり、一部を省略したりして適用することができる。

40

【図面の簡単な説明】

【0028】

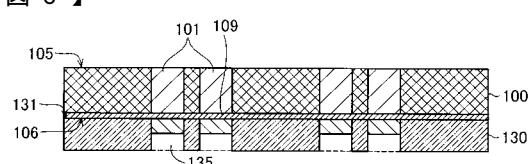

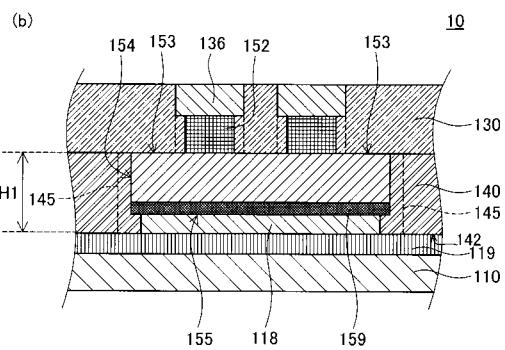

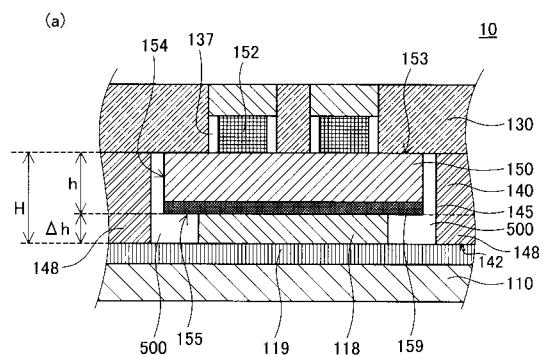

【図1】第1実施例における半導体パワーモジュール10の概略構成を示す断面図。

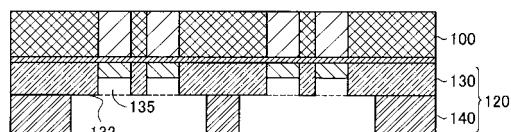

【図2】第1実施例における半導体パワーモジュール10について説明する分解断面図。

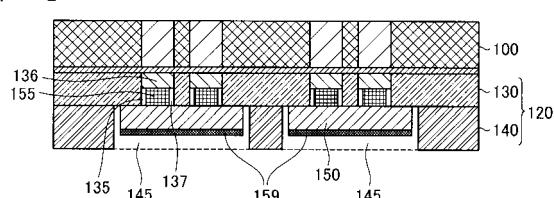

【図3】第1実施例における半導体パワーモジュール10の製造方法を説明する工程図。

【図4】第1接合層130の作製について説明する説明図。

【図5】第2接合層140の作製について説明する説明図。

【図6】第1実施例における第1の配線基板100と接合層120との仮接合について示す説明図。

50

【図7】第1実施例における第1の配線基板100と接合層120との仮接合について示す説明図。

【図8】第1実施例における半導体素子150の実装状態を示す説明図。

【図9】第1実施例における第2の配線基板110と接合層120との仮接合について示す説明図。

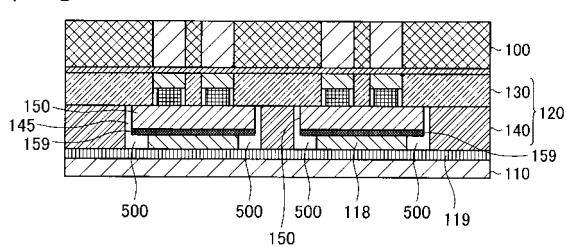

【図10】拡散接合時における、余剰部148による空隙500部分の充填について説明する。

【図11】第2実施例における接合層220と半導体素子150との間の空隙部分の充填について説明する説明図。

【発明を実施するための形態】

10

【0029】

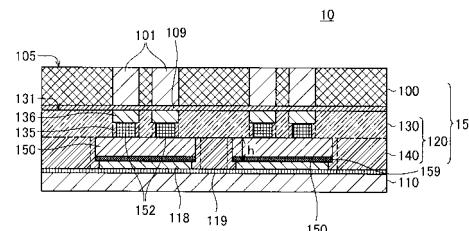

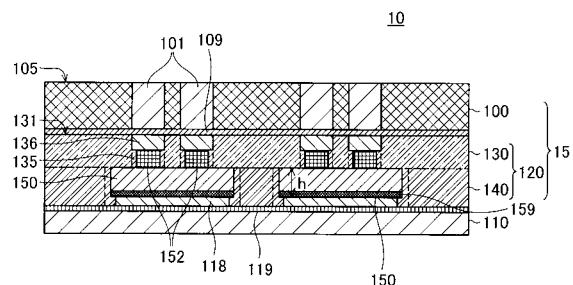

A. 第1実施例：

A1. 半導体モジュール概略構成：

図1は、第1実施例における半導体パワーモジュール10の概略構成を示す断面図である。図2は、第1実施例における接合前の半導体パワーモジュール10の分解断面図である。半導体パワーモジュール10は、第1の配線基板100、第2の配線基板110と、接合層120と、半導体素子150とを備える。第1の配線基板100と接合層120は、回路基板15を構成する。以降、明細書では、第1の配線基板100と第2の配線基板110を、単に、配線基板とも呼ぶ。

【0030】

20

配線基板100、110は、セラミックス材料、もしくはガラス成分を混合したガラスセラミックス材料により形成されている。セラミックス材料としては、例えば、酸化アルミナ( $Al_2O_3$ )、窒化アルミニウム(AlN)、窒化珪素( $Si_3N_4$ )などが用いられる。

【0031】

30

第1の配線基板100は、制御回路やコンデンサなどの電子部品が搭載される第1の面105と、第1の面105とは反対側に形成されている第2の面106と、第1の面105と第2の面106との間を電気的に接続するための内層ビアホール101と、パターン配線109を備える他、第1の面105上に配置される外部接続用の電極端子(図示せず)等を備える。パターン配線109は、第1の配線基板100の表面、内部の層の表面に形成されている。図1では、第1の配線基板100の内部の層に形成されたパターン配線は省略されている。

【0032】

30

第2の配線基板110は、半導体素子150が実装される第1の面115と、放熱板などの部品が搭載され得る第2の面116と、半導体素子150と電気的に導通するための金属製のバンプ118と、パターン配線119を備える。第2の配線基板110は、例えば、セラミックス板に回路パターン配線119が直接接合された基板、いわゆる、DBC(Direct Bonding Copper)基板とよばれる基板が用いられる。

【0033】

40

半導体素子150は、筐体151と、筐体151の表面153に形成されている電極部152と、筐体151の裏面155側に形成されている薄膜状の電極層159とを備える。電極部152は、電極パッドおよび電極パッド上に形成されている金属製の突状のバンプからなる。電極部152および電極層159は、例えば、金(Au)を主成分として形成されている。電極部152のバンプは、予め、バンプ形状に加工された金属柱を所望の位置に配置することにより形成してもよいし、アルミニウム、銅、錫、酸化銀等の金属種を主成分とするペーストを、電極パッド上に、フォトリソパターンにより転写する方法やスクリーン印刷により印刷する方法により形成してもよい。半導体素子150は、導電接合部136、パターン配線109および内層ビアホール101を介して、第1の配線基板100と電気的に接続される。また、半導体素子150は、第2の配線基板110のバンプ118、パターン配線119を介して第2の配線基板110と電気的に接続される。

50

## 【0034】

接合層120は、第1の配線基板100の第2の面106側に配置され、第1接合層130、第2接合層140とからなる絶縁性の薄いガラスシートである。接合層120は、半導体素子150と配線基板100、110とを絶縁する。接合層120は、絶縁性の無機系材料を主成分とし、半導体素子の実装時の加熱工程により軟化する粉末ガラスにより形成されている。粉末ガラスは、例えば、 $ZnO - B_2O_3 - SiO_2$ 、など、酸化ケイ素、酸化亜鉛、酸化ホウ素、酸化ビスマスなどの混相として形成される。接合層120の詳細な構成について図2を参照して説明する。

## 【0035】

第1接合層130は、第1の配線基板100と半導体素子150とを絶縁する。第1接合層130は、内層ピアホール101に対応する位置Pに形成された少なくとも一つの貫通孔135と、貫通孔135内に配置された導電接合部136とを有する。換言すれば、第1接合層130の貫通孔135は、後述する第2接合層140の開口部145の天面145aに形成されている。貫通孔135内に導電接合部136が配置されることにより、導電接合部136と貫通孔135の側壁135aとによって窪み部137が形成される。

10

## 【0036】

導電接合部136は、導電性の金属を主成分として形成されている。導電性の金属として、例えば、銅、銀、錫、アルミニウムなどを用いてもよい。導電接合部136は、半導体素子150が開口部145に配置されると、半導体素子150の電極部152と第1の配線基板100とを導通する。

20

## 【0037】

窪み部137は、後述する半導体素子150の電極部152の体積以上の容積を有し、図2に示すように、導電接合部136の厚みをd1、第1接合層130の厚みをd2、電極部152の高さをd3とし、第1の配線基板100の反りにより発生する、電極部152の高さバラつきの許容値をd4とすると、電極部152の高さd3は、窪み部137の高さd5 = (導電接合部136の厚みd2 - 第1接合層130の厚みd1)に対して、許容値d4を加えた大きさよりも大きくなるように、すなわち、電極部152の高さd3窪み部137の高さd5 + 許容値d4を満たすように設計される。このように設計することにより、導電接合部136と電極部152とを確実に接触させることができ、第1の配線基板100と半導体素子150との導通を確保できる。その理由は以下に説明する通りである。

30

## 【0038】

第1の配線基板100は製造時に微小な反り等が生じることがあるので、窪み部137の厚み方向の高さと、電極部152の厚み方向の高さd3とを等しくすると、第1の配線基板100の微小な反りの影響により、電極部152の窪み部137側の先端と対向する窪み部137との間に隙間が生じてしまうことがある。つまり、電極部152と導電接合部136との電気的接続が担保できなくなる。そのため、電極部152の厚み方向の高さd3は、第1の配線基板100の厚み方向の高さバラつきd4を考慮すること、つまり、電極部152の高さd3 > 窪み部137の高さd5を満たすことで窪み部137内への半導体素子150の配置時、電極部152と導電接合部136との電気的接続を確実に担保できる。第1の配線基板100に微小な反り等が生じても、「電極部152の高さd3 - 窪み部137の高さd5」以下の接合面の高さバラつきが許容される。

40

## 【0039】

なお、電極部152の高さd3 窪み部137の高さd5 + 許容値d4であるので、第1の配線基板100、接合層120および半導体素子150の接合前において、半導体素子150を開口部145内に配置したとき、半導体素子150の表面153と第2接合層140との間には若干の隙間が生じることがある。しかし、既述の通り、窪み部137の容積は、電極部152の体積より大きいので、接合時の加熱圧着により、電極部152が溶融して窪み部137内に全て収容され、電極部152の高さd3 = 窪み部137の高さd5となり、半導体素子150の表面153と第1接合層130の第2の面132とは密

50

着する。

【0040】

また、説明の便宜上、上記では、導電接合部136の厚みd1および第1接合層130の厚みd2を、単に厚みと表しているが、第1接合層130や導電接合部136は、厚みが完全に均一ではないことがあるため、測定位置によって厚みにばらつきが生じることがある。また、半導体素子150の電極部152は、第1実施例に示すような平面状に形成されるだけでなく、例えば、球状に形成されることもある。そのため、d1～d3を、以下のように定義してもよい。すなわち、導電接合部136の厚みd1は、導電接合部136における、第1の配線基板100の第1の面105から、導電接合部136の半導体素子150側の面までの距離の最大値を表し、第1接合層130の厚みd2は、第1の配線基板100の第1の面105側の面から、第1接合層130の、半導体素子150側の面までの距離の最大値を表し、電極部152の高さd3は、半導体素子150の表面153からの、電極部152の積層方向の高さの最大値を表す。

10

【0041】

第2接合層140は、貫通孔135と連通し、第1の配線基板100が積層される第1の面131とは異なる第2の面132側に形成され、半導体素子150を配置するための開口部145を有する。半導体素子150が開口部145に配置されると、半導体素子150の電極部152は貫通孔135内に収容され、電極部152と第1の配線基板100とが導通される。

20

【0042】

図2に示すように、開口部145は、半導体素子150の側面154と、開口部145の側壁145bとの間に、数nm～数mm程度の空隙が生じるように、半導体素子150の筐体151の外形より大きく形成されている。こうすることにより、開口部145への半導体素子150の嵌め込みを円滑に行うことができる。また、開口部145の天面145a(第1の面141)から第2接合層140の第2の面142までの距離に当たる、開口部145の積層方向の深さHは、半導体素子150が開口部145内に配置された状態における、開口部145の天面145aと、半導体素子150の裏面155との間の距離h(図1)より大きい。

【0043】

半導体素子150が第2接合層140の開口部145内に配置されると、接合層120において、開口部145の深さHと、開口部145の天面145aと半導体素子150の裏面155との間の距離hとの差分hに相当する余剰部148が生じる。第2の配線基板110が半導体素子150の裏面側、すなわち、第2接合層140の第2の面142上に積層して配置され、配線基板100、110、半導体素子150および接合層120が拡散接合による加熱・加圧により一体的に接合されるとき、余剰部148は、接合時の加熱、圧縮による変形により、開口部145の側壁145bと半導体素子150の側面154との間の空隙を充填するように変形する。この結果、半導体素子150の側面154の周囲は、第2接合層140により封止され、配線基板100、110と半導体素子150との間の絶縁性が向上される。また、配線基板100、110の製造時の反りに起因して第1の配線基板100、第2の配線基板110と接合層120との間に形成される空隙を余剰部148により補填(充填)され、第1の配線基板100、110と接合層120との接合強度が向上される。余剰部148による空隙の充填については、後述する製造方法において詳細に説明する。

30

【0044】

配線基板100、110、半導体素子150および接合層120が一体的に接合されると、第1の配線基板100と半導体素子150とは、導電接合部136、電極部152を介して電気的に接続され、半導体素子150と第2の配線基板110とは、半導体素子150の裏面155の配線層159、第2の配線基板110のバンプ118およびパターン配線119を介して電気的に接続される。

40

【0045】

50

また、電極部 152 と導電接合部 136 は接合時の加熱変形により、窪み部 137 内にて、その空間部を充填するように変形する。変形に伴い、半導体素子 150 は第 1 の配線基板 100 側へ移動し、第 1 接合層 130 の第 2 の面 132 (換言すれば、開口部 145 の天面 145a) と半導体素子 150 の表面 153 とが、隙間無く接合される。

【0046】

なお、電極部 152 および窪み部 137 は、電極部 152 の体積と窪み部 137 の容積とが等しくなるように形成されることが好ましいが、電気的接続が担保されていれば、「窪み部 137 の容積 > 電極部 152 の体積」であってもよい。

【0047】

A2. 製造方法 :

10

半導体パワーモジュール 10 の製造方法を、図 3 ~ 図 10 を用いて説明する。図 3 は、第 1 実施例における半導体パワーモジュール 10 の製造方法を説明する工程図である。

【0048】

ステップ S10 では、内層ビアホール 101 とパターン配線 109 を含む配線基板 100 とパターン配線 119 を含む 110 が作製される。

【0049】

ステップ S12 では、接合層 120 を構成する第 1 接合層 130、第 2 接合層 140 が作製される。図 4 は、第 1 接合層 130 の作製について説明する説明図である。図 5 は、第 2 接合層 140 の作製について説明する説明図である。

【0050】

第 1 接合層 130 を構成するガラスシート 330 (図 4 (a)) および第 2 接合層 140 を構成するガラスシート 340 (図 5 (a)) が作製される。具体的には、後述する拡散接合処理における加熱により軟化する粉末ガラスと、熱分解性の有機接着剤とを、有機溶媒や水などの溶媒を用いて形成されたスラリーが、ドクターブレード法によるシートキャスティング、もしくは、押し出し成型等の方法によりシート状に成形され、乾燥されることにより、ガラスシート 330、340 が作製される。粉末ガラスとして、酸化ケイ素、酸化亜鉛、酸化ホウ素、酸化鉛、酸化ビスマスなどを混層として形成される粉末ガラス、例えば、 $ZnO - B_2O_3 - SiO_2$  を利用できる。また、第 1 接合層 130、第 2 接合層 140 には、フィラーとしてアルミナ等のセラミックス粉末材料が配合されても良い。

20

【0051】

作製された第 1 接合層 130 を構成するガラスシート 330 において、図 4 (b) に示すように、第 1 の配線基板 100 の内層ビアホール 101 に対応する位置 P に対して、レーザもしくはマイコンパンチなどの機械加工が施され、貫通孔 135 が形成される。

30

【0052】

次に、図 4 (c) に示すように、貫通孔 135 内に、導電接合部 136 が形成される。具体的には、貫通孔 135 に、導電接合部 136 を構成するペーストがスクリーン印刷により一部充填される。ペーストは、金属を主成分としており、例えば、アルミニウムや酸化銀、銅、ナノ金属、ハンダ合金のような、後述する拡散接合により溶融する金属種と、熱分解性の有機接着剤とを、有機溶媒や水などの溶媒を用いて混練することにより形成される。なお、ペーストの充填には、スクリーン印刷に限られず、例えば、ディスペンサーによる吐出などの方法を用いられてもよい。貫通孔 135 内に導電接合部 136 が形成されることに伴い、窪み部 137 が形成される。このように、第 1 接合層 130 が形成される。

40

【0053】

また、第 2 接合層 140 を構成するガラスシート 430 において、図 5 (b) に示すように、半導体素子 150 が実装される位置に対して、レーザもしくはマイコンパンチなどの機械加工が施され、開口部 145 が形成される。この際、開口部 145 は、半導体素子 150 の側面 154 と、開口部 145 の側壁 145b との間に、数 nm ~ 数 mm 程度の空隙が生じるように、半導体素子 150 の筐体 151 の外形より大きく形成される。また、開口部 145 は、積層方向の深さ H が、半導体素子 150 が開口部 145 内に配置された

50

状態における、第2接合層140の第1の面141と、半導体素子150の裏面155との間の距離hより大きくなるように形成される。換言すれば、第2接合層140の厚みが、第2接合層140の第1の面141と、半導体素子150の裏面155との間の距離hより大きくなるように形成される。このように、第2接合層140が形成される。

【0054】

ステップS14では、第1の配線基板100と接合層120とが仮接着される。図6は、第1実施例における第1の配線基板100と第1接合層130との仮接着について示す説明図である。図7に示すように、第1接合層130の導電接合部136と第1の配線基板100の内層ピアホール101とが導通可能となるように、導電接合部136と内層ピアホール101とを対向させ、第1接合層130の第1の面131上に第1の配線基板100を積層し(換言すれば、第1の配線基板100の第2の面106上に第1接合層130を積層し)、第1接合層130に含まれる有機接着剤の接着力により仮接着する。当該有機接着剤は熱処理時に分解、除去される。

10

【0055】

続いて、図7に示すように、第1接合層130の第2の面132上に、第2接合層140が位置合わせされて積層され、第1接合層130および第2接合層140に含まれる有機接着剤の接着力により、第1接合層130と第2接合層140とが仮接着され、接合層120が形成される。第1接合層130と第2接合層140との位置合わせとは、貫通孔135と開口部145とが、半導体素子150の実装に適合するように、換言すれば、貫通孔135と開口部145とが連通され、開口部145内への半導体素子150配置時に20において、電極部152が窪み部137内に収容されるように、位置合わせすることを含む。

20

【0056】

ステップS16では、半導体素子150が、接合層120の開口部145内に実装される。図8は、第1実施例における半導体素子150の実装状態を示す説明図である。図8に示すように、半導体素子150が開口部145内に配置されることにより、半導体素子150の電極部152は、接合層120の貫通孔135内に収容され、導電接合部136と電気的に導通される。電極部152は、窪み部137の容積以下の体積となるようによめ形成されている。具体的には、アルミニウムや酸化銀、銅、錫、ナノ金属、ハンダ合金のような、後述するステップS20の加熱工程において溶融する金属種で形成された金属製のバンプを、電極部152上に配置する。バンプは、所望の位置にボール状に形成された金属を配置し、加熱処理により柱状形状とするボール搭載法により形成しても良いし、半導体素子150の予め対応する位置に、バンプとなる金属を転写する方法や、既述の金属種を主成分とするペーストを、スクリーン印刷により印刷する方法、フォトリソバーナンによりマスキングを施しメッキ法により所望の位置に金属バンプを形成してもよい。

30

【0057】

ステップS18では、開口部145内に半導体素子150が配置された状態で、接合層120と第2の配線基板110とが仮接着される。図9は、第1実施例における第2の配線基板110と接合層120との仮接着について示す説明図である。図9に示すように、第2の配線基板110のバンプ118と、半導体素子150の裏面155の配線層159とが対向するように接合層120と第2の配線基板110とを位置合わせし、接合層120に含まれる有機接着剤の接着力により仮接合する。当該有機接着剤は熱処理時に分解、除去される。

40

【0058】

配線基板100、110、接合層120および半導体素子150を拡散接合により接合し、半導体パワーモジュールを製造する(ステップS20)。具体的には、配線基板100、110、接合層120および半導体素子150を、積層方向に加圧するとともに、接合層120、導電接合部136、電極部152、バンプ118が熱融着する温度に加熱する。加圧および加熱により、第1の配線基板100と接合層120との接合面、接合層120と第2の配線基板110との接合面で原子の拡散が生じ、配線基板100、110と

50

接合層 120 とは接合される。また、半導体素子 150 の電極部 152 と導電接合部 136、および、半導体素子 150 の裏面 155 の配線層 159 とバンプ 118 についても、加熱により両材料が溶融し、接合される。

#### 【0059】

図 10 を参照して、拡散接合時における、余剰部 148 による空隙 500 部分の充填について説明する。図 10 (a) は、加熱・圧着される前における半導体素子 150 の実装箇所を拡大して示しており、図 10 (b) は、加熱・圧着された後における半導体素子 150 の実装箇所を拡大して示している。

#### 【0060】

図 10 (a) に示すように、半導体素子 150 が開口部 145 に収容された状態では、半導体素子 150 は、第 2 の配線基板 110 に当接する裏面 155 が、開口部 145 の端部、すなわち、第 2 接合層 140 の第 2 の面 142 から  $h$  (深さ  $H$  - 距離  $h$ ) だけ開口部 145 内に入り込んだ位置となるように実装されている。従って、第 2 接合層 140 のうち、開口部 145 を除く他の部分には、厚み  $h$  分の余剰部 148 が存在することとなる。厚み  $h$  は、余剰部 148 の体積が空隙 500 の容積以上となるように規定される。

#### 【0061】

図 10 (b) に示すように、配線基板 100、110、接合層 120 および半導体素子 150 が拡散接合において、加熱され、積層方向に押圧されると第 2 の配線基板 110 が半導体素子 150 および第 2 接合層 140 に押しつけられる。このとき、第 2 接合層 140 の基材であるガラス組成物の軟化温度よりも高温となっているため、第 2 接合層 140 は流動性に富み、開口部 145 の側壁 145b と、半導体素子 150 の間の空隙 500 は、第 2 接合層 140 により充填される。こうすることにより、半導体素子 150 の筐体 151 の外表面 (表面 153、側面 154) が絶縁性の第 2 接合層 140 により被覆されるので、半導体素子 150 の電極部 152 と第 2 の配線基板 110 のパターン配線 119 との間の絶縁性が向上され、半導体素子 150 の沿面放電が防止される。

#### 【0062】

空隙 500 の充填に伴い、第 2 接合層 140 の厚みは、接合前の厚み  $H$  より若干薄い  $H$  1 となる。第 2 接合層 140 の薄層化に伴い、溶融している第 2 の配線基板 110 のバンプ 118 は、水平方向 (押圧方向と略直交する方向) に広がり、厚みが若干薄くなる。バンプ 118 がこのように流動することにより、第 2 の配線基板 110 と第 2 接合層 140 、半導体素子 150 との接合強度を確保できる。

#### 【0063】

接合層 120、導電接合部 136、電極部 152 およびバンプ 118 が熱融着する温度とは、例えば、導電接合部 136、電極部 152 およびバンプ 118 を構成する金属の融点および接合層 120 の材料のガラス組成物の軟化点のうち、いずれか高い温度としてもよい。第 1 実施例では、導電接合部 136、電極部 152 およびバンプ 118 の材料として、融点 660 のアルミニウムを用い、接合層 120 の材料として軟化点 640 の  $ZnO - B_2O_3 - SiO_2$  ガラスを用い、両材料が熱融着する温度 670 で 5 分間加熱する。また、第 1 実施例では、配線基板 100、110、接合層 120 および半導体素子 150 を、100 kPa 程度の圧力で加圧する。以上説明した通り、図 1 に示す第 1 実施例の半導体パワーモジュール 10 が作製される。

#### 【0064】

以上説明した第 1 実施例の回路基板 15、半導体パワーモジュール 10、半導体パワーモジュール 10 の製造方法によれば、接合層 120 の開口部 145 は、開口部 145 の深さが、開口部 145 の天面 145a と半導体素子 150 の裏面 155 との間の距離  $h$  よりも大きくなるように形成されている。従って、接合層 120 において、開口部 145 の深さ  $H$  と、開口部 145 の天面 145a と半導体素子 150 の裏面 155 との間の距離  $h$  との差分  $h$  に相当する余剰部 148 を生じさせることができる。よって、配線基板 100、200 と接合層 120 の間や、接合層 120 の開口部 145 の側壁 145b と半導体素子 150 の側面 154 との間に空隙 500 が生じた場合、当該空隙 500 を余剰部 148

10

20

30

40

50

で補填（充填）することができる。従って、半導体素子 150 と配線基板 100, 110 との間の絶縁性の向上、より具体的には、半導体素子 150 の電極部 152 と第 2 の配線基板 110 のパターン配線 119 との間の絶縁性が向上されるので、半導体素子 150 の沿面放電の防止を図ることができる。また、半導体素子周囲に空隙が存在することによる半導体素子 150 の損傷の抑制を図ることができる。また、配線基板 100, 110 に製造上生じる反りに起因して配線基板 100, 110 と接合層 120 との間に空隙が生じた場合にも、当該空隙を余剰部 148 で補填（充填）することができる。従って、配線基板 100, 110 と接合層 120 との間の接合強度を向上できる。

【0065】

また、第 1 実施例の回路基板 15、半導体パワーモジュール 10、半導体パワーモジュール 10 の製造方法によれば、貫通孔 135 は、導電接合部 136 の体積と、半導体素子 150 の電極部 152 の体積との積算体積以上の容積を有するように形成され、開口部 145 は、深さ H が半導体素子 150 の厚みより大きくなるように形成されている。従って、開口部 145 への半導体素子 150 の実装時、電極部 152 の全体が貫通孔 135 内へ収容され、半導体素子 150 の表面 153 と開口部 145 の天面 145a とを確実に接触させることができる。よって、半導体素子 150 の表面 153 と接合層 120 との間の絶縁性を確保して半導体素子 150 の沿面放電を抑制しつつ、半導体素子 150 の側面 154 と開口部 145 の側壁 145b の間に形成される空隙を、接合層 120 により充填することができる。

【0066】

また、第 1 実施例の回路基板 15、半導体パワーモジュール 10、半導体パワーモジュール 10 の製造方法によれば、開口部の内壁は、積層方向に沿った平面状に形成されている。従って、開口部を、例えばパンチングなど、簡易な方法により製造できる。

【0067】

B. 第 2 実施例：

第 2 実施例では、半導体素子 150 を実装するための接合層の開口部の形状を、第 1 の配線基板 100 から第 2 の配線基板 110 に向けて拡径するテーパ形状とする。なお、第 2 実施例において、接合層の開口部の形状以外は、第 1 実施例と同様の構成、機能、作用を有しているので、第 1 実施例の符号を用いて説明する。また、第 2 実施例の半導体パワーモジュール 20 は、第 1 実施例の半導体パワーモジュール 10 と同様の製造工程により製造される。

【0068】

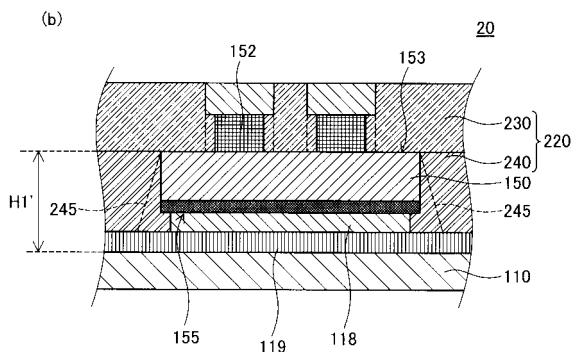

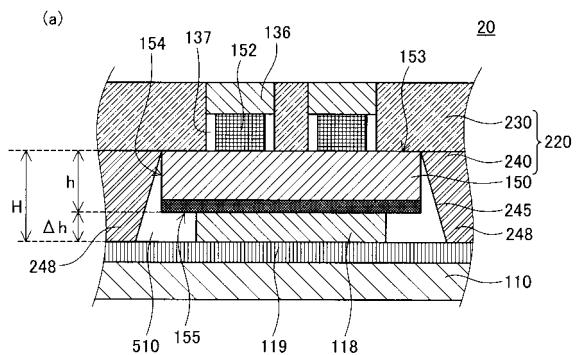

図 11 は、第 2 実施例における接合層 220 と半導体素子 150 との間の空隙部分の充填について説明する説明図である。図 11 (a) は、加熱・圧着される前ににおける半導体素子 150 の実装箇所を拡大して示しており、図 11 (b) は、加熱・圧着された後における半導体素子 150 の実装箇所を拡大して示している。接合層 220 は、第 1 の接合層 230 と第 2 接合層 240 とから構成される。図 11 に示すように、第 2 実施例では、接合層 220 の第 2 接合層 240 の開口部 245 は、第 1 の配線基板 100 から第 2 の配線基板 110 に向けて拡径するテーパ形状に形成されている。開口部 245 の深さ H は、第 1 実施例の開口部 145 の深さ H と同一である。

【0069】

図 11 (a) に示すように、半導体素子 150 が開口部 245 に収容された状態では、半導体素子 150 は、第 2 の配線基板 110 に当接する裏面 155 が、開口部 245 の端部、すなわち、第 2 接合層 240 の第 2 の面 242 から  $h$  (深さ H - 距離  $h$ ) だけ開口部 245 内に入り込んだ位置となるように実装されている。従って、第 2 接合層 240 のうち、開口部 245 を除く他の部分には、厚み  $h$  分の余剰部 248 が存在することとなる。

【0070】

図 11 (b) に示すように、配線基板 100、110、接合層 220 および半導体素子 150 が拡散接合において、加熱され、積層方向に押圧されると第 2 の配線基板 110 が

10

20

30

40

50

半導体素子 150 および第 2 接合層 240 に押しつけられる。このとき、第 2 接合層 240 の基材であるガラス組成物の軟化温度よりも高温となっているため、第 2 接合層 240 は流動性に富み、開口部 245 の側壁 245b と、半導体素子 150 の間の空隙 510 は、第 2 接合層 140 により充填される。なお、図 11 (b) において、充填される前の開口部 245 を破線で示す。こうすることにより、半導体素子 150 の筐体 151 の表面が絶縁性の第 2 接合層 240 により被覆されるので、半導体素子 150 の電極部 152 と第 2 の配線基板 110 のパターン配線 119 との間の絶縁性が向上され、半導体素子 150 の沿面放電が防止される。

#### 【0071】

空隙 510 の充填に伴い、第 2 接合層 240 の厚みは、接合前の厚み H より若干薄い H' となる。第 2 接合層 240 の薄層化に伴い、溶融している第 2 の配線基板 110 のバンプ 118 は、水平方向（押圧方向と略直交する方向）に広がり、厚みが若干薄くなる。バンプ 118 がこのように流動することにより、第 2 の配線基板 110 と第 2 接合層 240、半導体素子 150 との接合強度を確保できる。

#### 【0072】

以上説明した第 2 実施例の半導体パワーモジュール 20 によれば、開口部がテーパ形状となるように形成されている。従って、接合層と配線基板との接合時に積層方向に加圧されることにより、空隙の充填効率を向上でき、気泡の発生を抑制できる。

#### 【0073】

##### C. 変形例 :

(1) 第 1 実施例では、接合層 120 は、複数のガラスシートが積層して構成される多層構造を有しているが、単層構造であってもよい。この場合、例えば、1枚のガラスシートに対して、レーザ照射やパンチングなどの加工を施すことで、貫通孔 135、開口部 145 を形成する方法を利用できる。

#### 【0074】

(2) 第 1 実施例、第 2 実施例において、第 2 接合層 140 のガラスシートは、複数枚のガラスシートが積層されて形成されても良い。こうすることにより、開口部 145 の形状（例えば、第 2 実施例におけるテーパ形状等）のサイズ変更をより柔軟に行うことができ、第 2 接合層 140 の作製手法として、特に有効である。例えば、第 1 実施例では、第 1 接合層 130 に窪み部 137 が形成されるように、貫通孔 135 内の一部に導電接合部 136 を充填しているが、導電接合部 136 の積層方向の厚みに相当する厚みを有する層を第 1 接合層とともに、窪み部 137 の厚みに相当する厚みを有する層と、第 1 実施例における第 2 接合層 140 の 2 層からなる層を第 2 接合層としてもよい。第 1 実施例の第 1 接合層 130 の貫通孔 135 内に導電接合部 136 を充填して窪み部 137 が形成される場合、導電接合部 136 を構成する導電性のペーストの充填時に、当該ペーストが貫通孔 135 の壁面に付着したり、漏洩したりし、絶縁性が低下する可能性がある。一方、本変形例のように、第

2 接合層を複数層にすることにより、導電性のペーストの付着や漏洩を抑制でき、絶縁性の低下を抑制できる。

#### 【0075】

(3) 第 1 実施例では、第 1 接合層 130、第 2 接合層 140 を作製（貫通孔 135 内に導電接合部 136 が充填されている状態）した後に、第 1 の配線基板 100 に仮接着しているが、例えば、第 1 接合層 130、第 2 接合層 140 を構成するガラスシート 330, 340 を作製し、第 1 の配線基板 100 にガラスシート 330 を仮接着し、ガラスシート 330 にガラスシート 340 を仮接着した後に、レーザなどにより開口部 145、貫通孔 135 を形成し、導電接合部 136 を貫通孔 135 内に充填してもよい。すなわち、接合層 120 の形成と、接合層 120 と第 1 の配線基板 100 との仮接着との順番は、どのような順番であってもよい。

#### 【0076】

以上、本発明の種々の実施例について説明したが、本発明はこれらの実施例に限定され

10

20

30

40

50

ず、その趣旨を逸脱しない範囲で種々の構成をとることができる。

【符号の説明】

【0 0 7 7】

|                      |    |

|----------------------|----|

| 1 0 ... 半導体パワー モジュール |    |

| 1 5 ... 回路基板         |    |

| 2 0 ... 半導体パワー モジュール |    |

| 1 0 0 ... 配線基板       |    |

| 1 0 1 ... 内層ピアホール    |    |

| 1 0 5 ... 第1の面       | 10 |

| 1 0 6 ... 第2の面       |    |

| 1 0 9 ... 配線パターン     |    |

| 1 1 0 ... 接合層        |    |

| 1 1 5 ... 第1の面       |    |

| 1 1 6 ... 第2の面       |    |

| 1 1 8 ... バンプ        |    |

| 1 1 9 ... パターン配線     |    |

| 1 2 0 ... 接合層        |    |

| 1 2 1 ... 第1の面       |    |

| 1 3 0 ... 第1接合層      |    |

| 1 3 1 ... 第1の面       | 20 |

| 1 3 2 ... 第2の面       |    |

| 1 3 5 ... 貫通孔        |    |

| 1 3 5 a ... 側壁       |    |

| 1 3 6 ... 導電接合部      |    |

| 1 3 7 ... 窪み部        |    |

| 1 4 0 ... 第2接合層      |    |

| 1 4 1 ... 第1の面       |    |

| 1 4 2 ... 第2の面       |    |

| 1 4 5 ... 開口部        |    |

| 1 4 5 a ... 天面       | 30 |

| 1 4 5 b ... 側壁       |    |

| 1 4 8 ... 余剰部        |    |

| 1 4 9 ... 第2接合層      |    |

| 1 5 0 ... 半導体素子      |    |

| 1 5 1 ... 筐体         |    |

| 1 5 2 ... 電極部        |    |

| 1 5 3 ... 上面         |    |

| 1 5 4 ... 側面         |    |

| 1 5 5 ... 裏面         |    |

| 1 5 9 ... 電極層        |    |

| 2 2 0 ... 接合層        | 40 |

| 2 4 0 ... 第2接合層      |    |

| 2 4 5 ... 開口部        |    |

| 2 4 5 b ... 側壁       |    |

| 2 4 2 ... 第2の面       |    |

| 2 4 8 ... 余剰部        |    |

| 3 3 0 ... ガラスシート     |    |

| 4 3 0 ... ガラスシート     |    |

| 5 0 0 ... 空隙         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】