(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-228460

(P2007-228460A)

(43) 公開日 平成19年9月6日(2007.9.6)

(51) Int.C1.

HO4N 5/335 (2006.01)

HO1L 27/146 (2006.01)

F 1

HO4N 5/335

HO1L 27/14

テーマコード(参考)

4M118

5C024

審査請求 未請求 請求項の数 32 O L (全 68 頁)

(21) 出願番号

(22) 出願日特願2006-49605 (P2006-49605)

平成18年2月27日 (2006.2.27)(71) 出願人 597139147

小柳 光正

宮城県名取市ゆりが丘1-22-5

(74) 代理人 100095706

弁理士 泉 克文

(72) 発明者 小柳 光正

宮城県名取市ゆりが丘1-22-5

Fターム(参考) 4M118 AA01 AB01 BA14 CA02 CA03

DD04 DD12 FA06 FA28 FA33

5C024 CX41 CX54 GX03 GY31

(54) 【発明の名称】集積センサを搭載した積層型半導体装置

## (57) 【要約】

## 【課題】

全画素についての信号電荷の実質的同時蓄積が可能であると共に、高い画素開口率を実現できるセンサ回路及びアドレス指定型イメージセンサを提供する。

## 【解決手段】

マトリックス状に配置された複数の画素11をn個毎に共通ノード13に並列接続して、複数の画素ブロック12を構成する。各画素ブロック12は、共通ノード13に並列接続されたn個の光電変換素子PD<sub>1</sub>～PD<sub>n</sub>と、光電変換素子PD<sub>1</sub>～PD<sub>n</sub>の各々と共通ノード13とを結ぶ経路をそれぞれ開閉するn個のトランスマルチゲートTG<sub>1</sub>～TG<sub>n</sub>を含む。各画素ブロック12に対しては、その外部に、全画素11をリセットする共通のリセットトランジスタTr<sub>RST</sub>と、n個の画素11から読み出される信号を増幅する共通の増幅トランジスタTr<sub>AMP</sub>とが設けられる。

## 【選択図】 図4

**【特許請求の範囲】****【請求項 1】**

マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択するアドレス指定型イメージセンサに使用されるセンサ回路であって、

複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素をリセットするためのリセットトランジスタと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子とを含んでいることを特徴とするセンサ回路。

**【請求項 2】**

前記増幅トランジスタが、单一の出力端を有している請求項1に記載のセンサ回路。

**【請求項 3】**

前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えている請求項1に記載のセンサ回路。

**【請求項 4】**

前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続されている請求項1に記載のセンサ回路。

**【請求項 5】**

前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えている請求項4に記載のセンサ回路。

**【請求項 6】**

前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる請求項1～5のいずれか1項に記載のセンサ回路。

**【請求項 7】**

マトリックス状に配置された複数の画素を有していると共に、アドレス指定によって前記画素の各々を選択するアドレス指定型イメージセンサに使用されるセンサ回路であって、

複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子と、当該光電変換素子と前記第1ゲート素子との接続点に接続された、当該画素をリセットするためのリセットトランジスタとを含んでいることを特徴とするセンサ回路。

**【請求項 8】**

前記増幅トランジスタが、单一の出力端を有している請求項7に記載のセンサ回路。

**【請求項 9】**

前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶さ

10

20

30

40

50

れた信号の出力を制御する出力トランジスタとを、さらに備えている請求項 7 に記載のセンサ回路。

**【請求項 10】**

前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第 2 ゲート素子が接続されている請求項 7 に記載のセンサ回路。

**【請求項 11】**

前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えている請求項 10 に記載のセンサ回路。

10

**【請求項 12】**

前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる請求項 7 ~ 11 のいずれか 1 項に記載のセンサ回路。

**【請求項 13】**

マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択する、三次元積層構造を持つアドレス指定型イメージセンサであって、

複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

20

前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素をリセットするためのリセットトランジスタと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第 1 ゲート素子とを含んでおり、

少なくとも前記光電変換素子は、前記三次元積層構造を構成する第 1 半導体回路層の中に形成され、前記第 1 ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第 2 あるいは第 3 以降の半導体回路層の中に形成されていることを特徴とするアドレス指定型イメージセンサ。

30

**【請求項 14】**

複数の前記光電変換素子に加えて、複数の前記第 1 ゲート素子が前記第 1 半導体回路層の中に形成され、複数の前記増幅トランジスタと複数の前記リセットトランジスタが前記第 2 あるいは第 3 以降の半導体回路層の中に形成されている請求項 13 に記載のアドレス指定型イメージセンサ。

**【請求項 15】**

複数の前記光電変換素子に加えて、複数の前記第 1 ゲート素子及び複数の前記リセットトランジスタが前記第 1 半導体回路層の中に形成され、複数の前記増幅トランジスタが前記第 2 あるいは第 3 以降の半導体回路層の中に形成されている請求項 13 に記載のアドレス指定型イメージセンサ。

40

**【請求項 16】**

前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第 2 ゲート素子（選択トランジスタ）が接続されており、

複数の前記光電変換素子に加えて、複数の前記第 1 ゲート素子、複数の前記リセットトランジスタ及び複数の前記増幅トランジスタが前記第 1 半導体回路層の中に形成され、複数の前記第 2 ゲート素子（選択トランジスタ）が前記第 2 あるいは第 3 以降の半導体回路層の中に形成されている請求項 13 に記載のアドレス指定型イメージセンサ。

50

## 【請求項 17】

複数の前記光電変換素子のみが前記第1半導体回路層の中に形成され、複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成されている請求項13に記載のアドレス指定型イメージセンサ。

## 【請求項 18】

前記増幅トランジスタの各々が、単一の出力端を有している請求項13に記載のアドレス指定型イメージセンサ。

## 【請求項 19】

前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えている請求項18に記載のアドレス指定型イメージセンサ。

10

## 【請求項 20】

前記増幅トランジスタの各々が、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続されている請求項18に記載のアドレス指定型イメージセンサ。

20

## 【請求項 21】

前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えている請求項20に記載のアドレス指定型イメージセンサ。

20

## 【請求項 22】

前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる請求項13～21のいずれか1項に記載のアドレス指定型イメージセンサ。

30

## 【請求項 23】

マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択する、三次元積層構造を持つアドレス指定型イメージセンサであって、

30

複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子と、当該光電変換素子と前記第1ゲート素子との接続点に接続された、当該画素をリセットするためのリセットトランジスタとを含んでおり、

40

少なくとも前記光電変換素子は、前記三次元積層構造を構成する第1半導体回路層の中に形成され、前記第1ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第2あるいはそれ以降の半導体回路層の中に形成されていることを特徴とするアドレス指定型イメージセンサ。

## 【請求項 24】

複数の前記光電変換素子に加えて、複数の前記第1ゲート素子が前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタと複数の前記リセットトランジスタが前記第2あるいは第3以降の半導体回路層の中に形成されている請求項23に記載のアドレス指定型イメージセンサ。

## 【請求項 25】

複数の前記光電変換素子に加えて、複数の前記第1ゲート素子及び複数の前記リセット

50

トランジスタが前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成されている請求項23に記載のアドレス指定型イメージセンサ。

【請求項26】

前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子(選択トランジスタ)が接続されており、

複数の前記光電変換素子に加えて、複数の前記第1ゲート素子、複数の前記リセットトランジスタ及び複数の前記増幅トランジスタが前記第1半導体回路層の中に形成され、複数の前記第2ゲート素子(選択トランジスタ)が前記第2あるいは第3以降の半導体回路層の中に形成されている請求項23に記載のアドレス指定型イメージセンサ。

10

【請求項27】

複数の前記光電変換素子のみが前記第1半導体回路層の中に形成され、複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成されている請求項23に記載のアドレス指定型イメージセンサ。

【請求項28】

前記増幅トランジスタの各々が、単一の出力端を有している請求項23に記載のアドレス指定型イメージセンサ。

【請求項29】

前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えている請求項28に記載のアドレス指定型イメージセンサ。

20

【請求項30】

前記増幅トランジスタの各々が、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続されている請求項23に記載のアドレス指定型イメージセンサ。

【請求項31】

前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えている請求項30に記載のアドレス指定型イメージセンサ。

30

【請求項32】

前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる請求項23～31のいずれか1項に記載のアドレス指定型イメージセンサ。

40

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、集積センサを搭載した積層型半導体装置に関し、さらに言えば、光電変換素子、トランスファ(転送)ゲート、リセットトランジスタ及び増幅トランジスタを含むセンサ回路と、そのセンサ回路を使用して簡単な構成で全ピクセルについて同時シャッタ(グローバル・シャッタ、同時露光)を可能としたアドレス指定型イメージセンサに関する。

【背景技術】

【0002】

固体撮像装置としては、従来より、マトリックス状に配置された全画素の信号電荷をC

50

CCD (Charge-Coupled Device, 電荷結合素子) を用いて転送する構成の CCD イメージセンサ (電荷転送型イメージセンサ) が多く利用されてきた。しかし、近年は、水平方向及び垂直方向に走査することにより、マトリックス状に配置された全画素の各々を選択する CMOS イメージセンサ (X-Y アドレス指定型イメージセンサ) の利用が増えてきており、高級一眼レフのデジタル・スチル・カメラや携帯電話機にまで使用されるようになっている。これは、CCD イメージセンサと比較して、電源が一つで済む、低消費電力である、標準の CMOS (Complementary Metal-Oxide-Semiconductor, 相補型金属-酸化物-半導体) プロセスで製造できる、システム・オン・チップの実現が容易である、といった CMOS イメージセンサの利点が重視されるようになったためと考えられる。

## 【0003】

10

しかし、従来の一般的な CMOS (アドレス指定型) イメージセンサには、以下に述べるような二つの問題がある。

## 【0004】

第一の問題は、全画素についての信号電荷の同時蓄積 (換言すれば、同時ないしグローバルシャッタ化) ができない、という点である。

## 【0005】

20

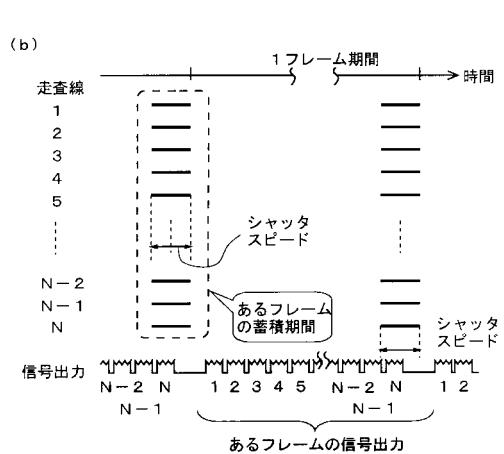

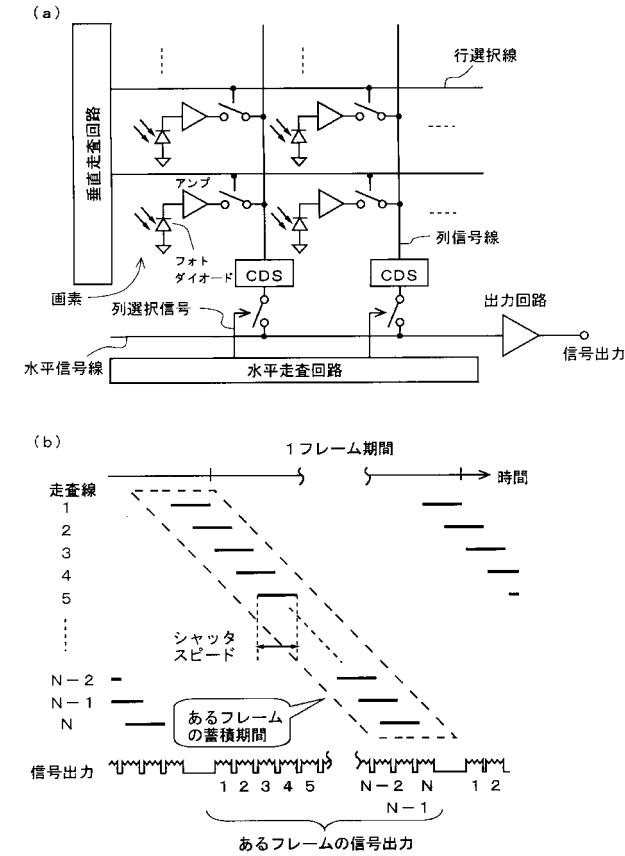

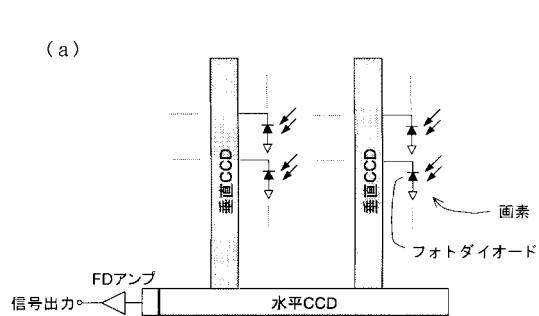

すなわち、CCD イメージセンサでは、全画素について同一時刻に信号電荷の蓄積が開始され、蓄積された信号電荷は各画素から一斉に読み出されて転送されるため、信号電荷の蓄積期間 (これは露光期間に等しい) は全画素について同一である。これに対し、従来の CMOS イメージセンサでは、画素マトリックスの各行毎にあるいは各画素毎に信号電荷の蓄積が開始され、各画素に蓄積された信号電荷はアドレス指定によって各画素から順に時系列的に読み出されるため、各画素の信号電荷の蓄積期間に時間的なズレ (タイミングのズレ) がある。したがって、CCD イメージセンサのような信号電荷の同時蓄積ができない。その理由を図 33 と図 30 を用いて説明する。

## 【0006】

30

図 33 (a) は、CCD イメージセンサの一般的な回路構成を示す概念図であり、図 33 (b) は同 CCD イメージセンサの信号電荷の蓄積期間を示す概念図である。図 30 (a) は、従来の CMOS イメージセンサの一般的な回路構成を示す概念図であり、図 30 (b) は同 CMOS イメージセンサの信号電荷の蓄積期間を示す概念図である。(米本和也著「CCD / CMOS イメージ・センサの基礎と応用」(CQ 出版社、2003 年発行) 175 頁及び 179 頁を参照)。

## 【0007】

40

CCD イメージセンサは、図 33 (a) に示すように、マトリックス状に配置された複数の画素の各々が光電変換素子としてのフォトダイオードを含んでおり、それらフォトダイオードの各々は照射された光の強さに応じた量の信号電荷を蓄積する。各画素に蓄積された信号電荷は、各画素用に設けられたトランスマネージャー (図示せず) を介して、画素マトリックスの列の各々に沿って配置された垂直 CCD に一斉に読み出される。この垂直 CCD への読み出しが、通常、垂直プランギング期間の最後に一斉に行われる。各垂直 CCD に読み出された信号電荷は、当該垂直 CCD の垂直転送作用によって、画素マトリックスの行に沿って配置された共通の水平 CCD まで順に転送される。こうして水平 CCD に転送された信号電荷は、さらに、水平 CCD によってその出力端に向かって順に水平転送され、当該出力端に設けられた FD (Floating Diffusion、浮遊拡散) アンプで増幅されて信号出力となる。

## 【0008】

CCD イメージセンサの信号電荷の蓄積期間は、図 33 (b) から容易に理解されるように、1 フレームを構成する N 本の走査線 (1 ~ N) の各々に対応する画素についての蓄積期間が同じになる、換言すれば、蓄積期間が同一のタイミングで設定される。各画素に蓄積された信号電荷が垂直 CCD に一斉に読み出されるという動作を考えれば、このようになることは明らかであろう。

## 【0009】

50

これに対して、従来の C M O S イメージセンサでは、図 3 0 ( a ) に示すように、マトリックス状に配置された複数の画素の各々が、光電変換素子としてのフォトダイオードと、そのフォトダイオードによって蓄積された信号電荷を増幅するアンプとを含んでいる。画素マトリックス中の各画素の選択は、垂直走査回路で行選択線を順に選択すると共に、水平走査回路で列信号線を順に選択する（つまり X - Y アドレスを順に指定する）ことによって行われる。（図 3 0 ( a ) では、その様子を各画素中に設けられたスイッチと各列信号線に設けられたスイッチとで示してある。）列信号線の各々に設けられた C D S ( Correlated Double Sampling、相関二重サンプリング）回路は、各列信号線を流れる信号電荷からノイズを除去するための回路である。こうして各画素から選択出力される信号電荷は、共通の水平信号線に順に送られ、当該水平信号線の一端に接続された出力回路を経て信号出力となる。

#### 【 0 0 1 0 】

従来の C M O S イメージセンサの信号電荷の蓄積期間については、図 3 0 ( b ) に示すように、1 フレームを構成する N 本の走査線 ( 1 ~ N ) の各々に対応する画素についての蓄積期間が、各走査線の走査タイミングに応じて順に時間的にずれてしまうことが分かる。これは、C M O S イメージセンサでは、C C D イメージセンサのような垂直レジスタ（垂直 C C D ）が存在しないため、各画素の信号電荷をリセットするタイミングを変えることによって、信号電荷を対応する列信号線に送るタイミングをずらしているからである。

#### 【 0 0 1 1 】

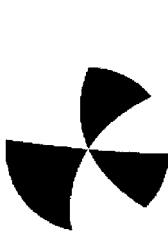

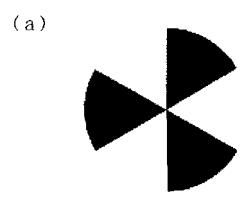

このように、従来の C M O S イメージセンサでは、信号電荷の蓄積期間が走査線毎にずれてしまい、信号電荷の同時蓄積（換言すれば同時シャッタ化）ができないという難点があることから、高速移動する被写体を撮像すると、得られた画像に歪みが生じる、という難点がある。例えば、高速回転する羽根を撮像すると、図 3 4 ( b ) のように歪んだ画像となってしまう、という問題が生じるのである。これに対し、信号電荷の同時蓄積（同時シャッタ化）が可能な C C D イメージセンサで撮像した場合は、画像は図 3 4 ( a ) に示すようになり、得られた画像に歪みは生じない（図 3 4 は、上記「 C C D / C M O S イメージ・センサの基礎と応用」180 頁に基づく）。

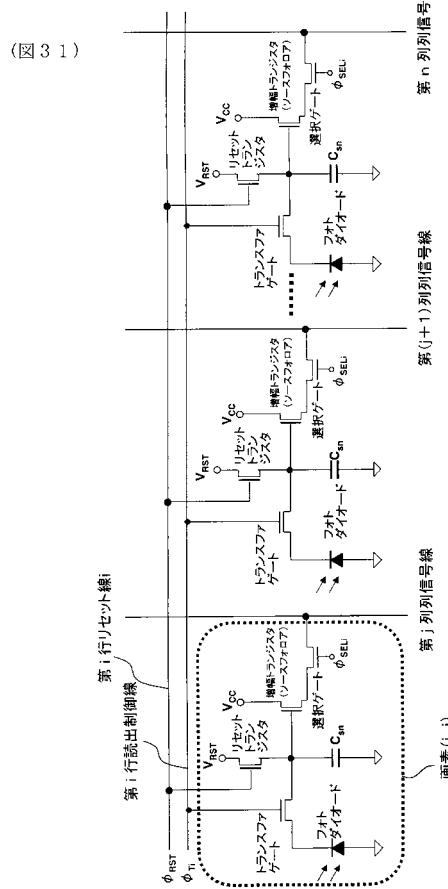

#### 【 0 0 1 2 】

従来の C M O S イメージセンサの持つ第二の問題は、画素面積に比べて実効的な受光領域が狭い、換言すれば、画素の開口率 ( fill factor ) が低い、という点である。その理由を図 3 1 及び図 3 2 を参照して説明する。図 3 1 は、従来の C M O S イメージセンサの概略回路構成を示す回路図であり、図 3 2 はその概略装置構造を示す要部断面図である。

#### 【 0 0 1 3 】

図 3 1 に示された回路構成は、4 トランジスタ型の画素を持つ C M O S イメージセンサのものであり、1 画素中に、フォトダイオードの他に四つのトランジスタ（トランジスタゲート、リセットトランジスタ、増幅トランジスタ、選択ゲート用の四つの M O S トランジスタ）を含んでいる。これらのトランジスタは、図 3 2 の装置構造に示すように、p 型シリコン ( S i ) 基板上に形成・配置されている。なお、 V <sub>CC</sub> は電源電圧、 V <sub>RST</sub> はリセット電圧である。

#### 【 0 0 1 4 】

図 3 1 の第 i 行第 j 列の画素 ( i , j ) ( ただし、 i , j は正の整数 ) について説明すると、トランジスタゲートは、第 i 行の読出制御線を介して電圧パルス <sub>T</sub> <sub>i</sub> を印加することにより導通状態となり、フォトダイオードに蓄積された信号電荷を、所定タイミングで、トランジスタゲートとリセットトランジスタと増幅トランジスタが相互接続されたノードに送る作用をする。リセットトランジスタは、第 i 行のリセット線を介して電圧パルス <sub>RST</sub> を印加することにより導通状態となり、導通状態となったトランジスタゲートを介して、フォトダイオードに蓄積された信号電荷を所定タイミングでリセットする（フォトダイオードに所定のリセット電圧 V <sub>RST</sub> を印加する）作用をする。前記ノードに接続された増幅トランジスタは、ソースフォロア構成とされており、前記ノードに送出された信号電荷を増幅する作用をする。選択ゲートは、第 i 行の行選択線（図示せず）を介し

10

20

30

40

50

て電圧パルス  $S_{E1i}$  を印加することにより導通状態となり、増幅された信号電荷を所定タイミングで対応する第  $j$  列の列信号線に送出する。なお、前記ノードに接続された  $C_{sn}$  は、当該ノードに生じる寄生容量を示す。

【0015】

CMOSイメージセンサの画素の回路構成には、3トランジスタ型もある。3トランジスタ型では、1画素中に、フォトダイオードの他に三つのトランジスタ（リセットトランジスタ、増幅トランジスタ、選択ゲート用のMOSトランジスタ）が含まれる。つまり、4トランジスタ型の構成からトランスファゲートが省略された構成となる。

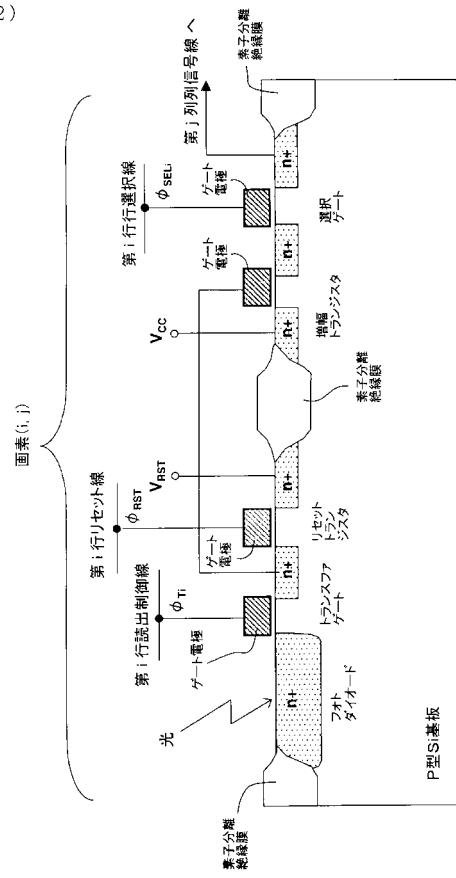

【0016】

図31の回路構成は、図32に示す構造として具体的に実現される。すなわち、P型シリコン（Si）基板の表面領域に素子分離絶縁膜によって画定された複数の素子領域内に、フォトダイオードと、トランスファゲート、リセットトランジスタ、増幅トランジスタ、選択ゲートをそれぞれ構成する四つのMOSトランジスタが形成されている。

【0017】

従来のCMOSイメージセンサの装置構造では、図32の要部断面図から明らかなように、4トランジスタ型と3トランジスタ型のいずれであっても、四つまたは三つのMOSトランジスタが画素面積の多くの部分を占有するため、画素面積の中でフォトダイオード（の開口部）が占める面積の割合、すなわち「開口率」がかなり小さくなっている。従来のCMOSイメージセンサの開口率は、一般に30%程度と低いのが通常である。このため、感度が低下してしまうという問題があり、この感度低下を解消しようとすると、画素面積（画素のサイズ）を拡大することが必要であるが、それは微細化の要請に反し、好ましくない。

【0018】

第一の問題として挙げた全画素同時シャッタ化を実現したCMOSイメージセンサの一例が、特許文献1（特開2004-266597号公報）に開示されている。このCMOSイメージセンサは、画素内に、受光素子と、当該受光素子で発生した信号電荷を次段へ転送する第1転送手段と、当該第1転送手段の出力を一時記憶する記憶部と、前記受光素子および前記記憶部の電荷の初期化を行う初期化手段と、前記記憶部に接続された第2転送手段と、当該第2転送手段からの電荷を電圧として外部に読み出す電荷検出部とを備え、全画素一斉に前記第1転送手段を動作させることにより蓄積電荷の読み出しを行い、かつ、全画素一斉に前記初期化手段を動作させることにより信号電荷の初期化を行うことを特徴とするものである（請求項1を参照）。発明の効果としては、「CMOSイメージセンサにおいて全画素同時に初期化する電子シャッタ動作を可能にし、かつ、画素回路も簡単で製造工程が単純化される。さらに、画素内で増幅することにより低雑音化が図れる」とされている（段落0036を参照）。

【0019】

他方、近年、複数の半導体チップを積層して三次元構造とした半導体装置が提案されている。例えば、栗野らは1999年に発行された「1999アイ・イー・ディー・エムテクニカル・ダイジェスト」において、「三次元構造を持つインテリジェント・イメージセンサ・チップ」を提案している（非特許文献1参照）。

【0020】

このイメージセンサ・チップは、4層構造を持っており、第1半導体回路層にプロセッサ・アレイと出力回路を配置し、第2半導体回路層にデータラッチとマスキング回路を配置し、第3半導体回路層に増幅器とアナログ・デジタル変換器を配置し、第4半導体回路層にイメージセンサ・アレイを配置している。イメージセンサ・アレイの最上面は、マイクロレンズ・アレイを含む石英ガラス層で覆われてあり、マイクロレンズ・アレイはその石英ガラス層の表面に形成されている。イメージセンサ・アレイ中の各イメージセンサには、半導体受光素子としてフォトダイオードが形成されている。4層構造を構成する各半導体回路層の間は、接着剤を用いて機械的に接続されていると共に、導電性プラグを用いた埋込配線とそれら埋込配線に接触せしめられたマイクロバンプ電極とを用いて電気的に

10

20

30

40

50

接続されている。

【0021】

また、李らは、2000年4月に発行された「日本応用物理学会誌」において、「高度並列画像処理チップ用の三次元集積技術の開発」とのタイトルで、栗野らの提案した上記固体イメージセンサと同様のイメージセンサを含む画像処理チップを提案している（非特許文献2参照）。

【0022】

李らの画像処理チップは、栗野らが上記論文で提案した固体イメージセンサとほぼ同じ構造を持っている。

【0023】

非特許文献1及び2に開示された従来のイメージセンサ・チップと画像処理チップは、いずれも、所望の半導体回路を内蔵した複数の半導体ウェハー（以下、単にウェハーともいう）を積層して互いに固着させた後、得られたウェハー積層体を切断（ダイシング）して複数のチップ群に分割することにより製造される。すなわち、内部に半導体回路を形成した半導体ウェハーをウェハーレベルで積層・一体化することにより三次元積層構造を形成し、それを分割してイメージセンサ・チップまたは画像処理チップを得ているのである。

【0024】

なお、これら従来のイメージセンサ・チップと画像処理チップでは、当該チップの内部の積層された複数の半導体回路のそれぞれが「半導体回路層」を構成する。

【非特許文献1】栗野ら、「三次元構造を持つインテリジェント・イメージセンサ・チップ」、1999年アイ・イー・ディー・エム テクニカル・ダイジェスト p. 36.4.1 ~ 36.4.4 (H. Kurino et al., "Intelligent Image Sensor Chip with Three Dimensional Structure", 1999 IEDM Technical Digest, pp. 36.4.1 - 36.4.4, 1999)

【非特許文献2】李ら、「高度並列画像処理チップ用の三次元集積技術の開発」、「日本応用物理学会誌」第39巻、p. 2473 ~ 2477、第1部4B、2000年4月、(K. Lee et al., "Development of Three-Dimensional Integration Technology for Highly Parallel Image-Processing Chip", Jpn. J. Appl. Phys. Vol. 39, pp. 2474 - 2477, April 2000)

【特許文献1】特開2004-266597号公報

（図1 - 図2、図8、図12、図15）

【発明の開示】

【発明が解決しようとする課題】

【0025】

上述したように、従来の一般的なCMOS（アドレス指定型）イメージセンサでは、全画素についての信号電荷の同時蓄積（換言すれば同時シャッタ化）ができない、画素の開口率が低い、という二つの問題がある。

【0026】

特許文献1に開示された従来のCMOSイメージセンサでは、全画素についての同時シャッタ化は可能である。しかし、各画素内に、受光素子の他に、当該受光素子で発生した信号電荷を次段へ転送する第1転送手段と、当該第1転送手段の出力を一時記憶する記憶部と、前記受光素子および前記記憶部の電荷の初期化を行う初期化手段と、前記記憶部に接続された第2転送手段とを設けることが必要であるから、3トランジスタ型のCMOSイメージセンサに記憶部を追加した構成である。したがって、このCMOSイメージセンサでは、画素の開口率が低い、という問題は残っている。

【0027】

非特許文献1及び2にそれぞれ開示されたイメージセンサ・チップと画像処理チップでは、半導体ウェーハあるいは半導体チップを積層・固着することにより三次元積層構造が実現できることについて開示されているだけであり、従来のCMOS（アドレス指定型）イメージセンサの持つ上記二つの問題については言及されていない。

## 【0028】

本発明は、これらの点を考慮してなされたものであって、その目的とするところは、全画素についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現できる、センサ回路及びアドレス指定型イメージセンサを提供することにある。

## 【0029】

本発明の他の目的は、従来のアドレス指定型イメージセンサにおいて見られる画像の歪みを生じることなく、高速で移動する被写体を撮像することができるセンサ回路及びアドレス指定型イメージセンサを提供することにある。

## 【0030】

本発明のさらに他の目的は、撮像領域の総面積に対する受光領域の総面積の割合が高いアドレス指定型イメージセンサを提供することにある。

## 【0031】

ここに明記しない本発明の他の目的は、以下の説明及び添付図面から明らかになるであろう。

## 【課題を解決するための手段】

## 【0032】

(1) 本発明の第1の観点によるセンサ回路は、マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択するアドレス指定型イメージセンサに使用されるセンサ回路であって、

複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素をリセットするためのリセットトランジスタと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子とを含んでいることを特徴とするものである。

## 【0033】

(2) 本発明の第1の観点によるセンサ回路は、複数の画素を所定数（例えばn個、nは2以上の整数）毎に共通ノードに並列接続して構成された複数の画素ブロックを有している。それら画素ブロックの各々では、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子とを含んでいる。そして、前記画素ブロックの各々の共通ノードに、リセットトランジスタと増幅トランジスタとが接続されているため、前記画素ブロックの各々で前記リセットトランジスタと前記増幅トランジスタとを共用することができる。これは、前記画素の内部には、リセットトランジスタと増幅トランジスタが設けられていないことを意味するものである。

## 【0034】

このセンサ回路では、次のようにして信号電荷の生成・蓄積から信号の出力までの動作を行う。

## 【0035】

まず、前記画素ブロックの各々に対して設けられた前記リセットトランジスタを用いて、前記画素のすべてについて一括してリセット（初期化）を行い（グローバルリセット）、前記画素ブロックのすべてについて前記共通ノードを所定のリセット電圧に設定する。この時、前記光電変換素子に対して設けられた前記第1ゲート素子はすべて導通状態とされる。

## 【0036】

次に、前記第1ゲート素子を遮断状態としてから、前記画素（光電変換素子）のすべて

10

20

30

40

50

に光を照射させ、それら画素に一括して信号電荷を生成・蓄積させる。

【0037】

その後、前記画素ブロックの各々において、前記第1ゲート素子を時系列的に順に導通状態にすることにより、当該画素ブロック中の前記画素に蓄積された信号電荷に対応する信号を、対応する前記共通ノードまで時系列的に順に読み出す。この動作は、複数の前記ブロックにおいて並行して行われる。この時、当該画素ブロック中の前記画素の一つより信号を読み出してから前記画素の他の一つより信号を読み出すまでの間に、前記リセットトランジスタを用いて前記共通ノードをリセットする必要がある。これは、前記共通ノードをリセットしないと、先に読み出された信号の影響が残って後の信号が変動する恐れがあるからである。

10

【0038】

前記画素ブロックの各々でこうして読み出された信号は、対応する前記増幅トランジスタによって順にあるいは並行して増幅され、その出力端から出力される。すなわち、当該増幅トランジスタの出力端が一つの場合は、当該画素ブロック中の複数の前記画素から順に送出された信号は、当該増幅トランジスタで増幅された後、その出力端子から時系列的に順に出力される。他方、当該増幅トランジスタの出力端子の総数が当該画素ブロック中の前記画素の総数に等しい場合は、当該増幅トランジスタの複数の出力端子から並列的に出力される。

【0039】

現在の現実的な最高シャッタースピード（つまり最短の信号電荷蓄積期間）は（1/8000）秒（=125μsec）であるから、前記リセットトランジスタによる前記共通ノードのリセット動作を必要回数（例えば（n-1）回）実行するのに要する時間（総リセット時間）と、前記画素ブロックの各々で前記画素の信号電荷を対応する前記増幅トランジスタで増幅するのに要する時間（総増幅時間）との和が、最短の信号電荷蓄積期間（=125μsec）よりも十分小さくなるようにn値を設定すれば、前記画素のすべてについての信号電荷の蓄積（露光）が実質的に同時に行われることになる。換言すれば、このセンサ回路を使用することにより、前記画素のすべてについての信号電荷の実質的に同時に蓄積（実質的に同時にシャッタ化）が可能となる。

20

【0040】

また、このようにして同時にシャッタ化が可能となることにより、従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

30

【0041】

さらに、本発明の第1の観点によるセンサ回路では、前記画素ブロックの各々に対して、当該ブロックの外側に前記リセットトランジスタと前記増幅トランジスタが設けられているため、前記画素は一つの光電変換素子と一つの第1ゲート素子（通常はMOSトランジスタ）を含むだけで済む。したがって、このセンサ回路を使用すれば、画素中に光電変換素子に加えて三つないし四つのMOSトランジスタを含む従来のアドレス指定型イメージセンサに比べて、高い画素開口率を実現することができる。

40

【0042】

（3） 本発明の第1の観点によるセンサ回路の好ましい例では、前記増幅トランジスタが、単一の出力端を有する。この場合、前記増幅トランジスタの出力端に接続される次段の配線が簡単になるという利点がある。

【0043】

この例では、前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えるのが好ましい。この場合、前記出力トランジスタを使用することによって、前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

【0044】

50

本発明の第1の観点によるセンサ回路の他の好ましい例では、前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続される。この場合、前記第2ゲート素子の各々を対応する前記第1ゲート素子と同期して開閉することにより、前記画素ブロック中の複数の前記画素からの信号を複数の前記出力端より並列的に出力することができる。その結果、次段の信号処理が迅速に行えるという利点がある。

#### 【0045】

この例では、前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えるのが好ましい。この場合、複数の前記出力トランジスタを使用することによって、複数の前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

#### 【0046】

本発明の第1の観点によるセンサ回路のさらに他の好ましい例では、前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる。この場合、実質的な同時シャッタ化が容易に実現できるという利点がある。

#### 【0047】

(4) 本発明の第2の観点によるセンサ回路は、マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択するアドレス指定型イメージセンサに使用されるセンサ回路であって、複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子と、当該光電変換素子と前記第1ゲート素子との接続点に接続された、当該画素をリセットするためのリセットトランジスタとを含んでいることを特徴とするものである。

#### 【0048】

(5) 本発明の第2の観点によるセンサ回路は、複数の画素を所定数(例えばn個、nは2以上の整数)毎に共通ノードに並列接続して構成された複数の画素ブロックを有している。それら画素ブロックの各々では、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子とに加えて、当該光電変換素子と前記第1ゲート素子との接続点に接続された、当該画素をリセットするためのリセットトランジスタとを含んでいる。そして、前記画素ブロックの各々の共通ノードに増幅トランジスタが接続されている。このため、前記画素ブロックの各々で前記増幅トランジスタとを共用することができる。これは、前記画素の内部には、増幅トランジスタが設けられていないことを意味するものである。

#### 【0049】

このように、本発明の第2の観点によるセンサ回路では、リセットトランジスタに関する構成が本発明の第1の観点によるセンサ回路とは異なっている。すなわち、本発明の第1の観点によるセンサ回路では、前記リセットトランジスタが、前記画素ブロックの各々に対して設けられている(つまり、前記リセットトランジスタが各画素ブロックの外部に設けられている)のに対し、本発明の第2の観点によるセンサ回路では、前記リセットトランジスタが、前記画素ブロックの各々に属する複数の前記画素の一つ一つに対して設け

10

20

30

40

50

られている（つまり、前記リセットトランジスタが前記画素の各々に対して設けられている）。このため、次のようにして信号電荷の生成・蓄積から信号の出力までの動作を行う。

【0050】

まず、前記画素の各々に対して設けられた前記リセットトランジスタを用いて、前記画素のすべてについて一括してリセット（初期化）を行い（グローバルリセット）、前記画素ブロックのすべてについて前記共通ノードを所定のリセット電圧に設定する。この時、前記光電変換素子に対して設けられた前記第1ゲート素子はすべて導通状態とされる。

【0051】

次に、前記第1ゲート素子を遮断状態としたままで、前記第1ゲート素子を遮断状態としてから、前記画素（光電変換素子）のすべてに光を照射させ、それら画素に一括して信号電荷を生成・蓄積させる。

【0052】

その後、前記画素ブロックの各々において、前記第1ゲート素子を時系列的に順に導通状態にすることにより、当該画素ブロック中の前記画素に蓄積された信号電荷に対応する信号を、対応する前記共通ノードまで時系列的に順に読み出す。この動作は、複数の前記ブロックにおいて並行して行われる。この時、当該画素ブロック中の前記画素の一つより信号を読み出してから前記画素の他の一つより信号を読み出すまでの間に、前記第1ゲート素子を一時的に導通状態にし、前記リセットトランジスタを用いて前記共通ノードをリセットする必要がある。これは、前記共通ノードをリセットしないと、先に読み出された信号の影響が残って後の信号が変動する恐れがあるからである。

【0053】

前記画素ブロックの各々でこうして読み出された信号は、対応する前記増幅トランジスタによって順にあるいは並行して増幅され、その出力端から出力される。すなわち、当該増幅トランジスタの出力端が一つの場合は、当該画素ブロック中の複数の前記画素から順に送出された信号は、当該増幅トランジスタで増幅された後、その出力端子から時系列的に順に出力される。他方、当該増幅トランジスタの出力端子の総数が当該画素ブロック中の前記画素の総数に等しい場合は、当該増幅トランジスタの複数の出力端子から並列的に出力される。この点は、本発明の第1の観点によるセンサ回路と同じである。

【0054】

現在の現実的な最高シャッタースピード（つまり最短の信号電荷蓄積期間）は（1/8000）秒（=125μsec）であるから、前記リセットトランジスタによる前記共通ノードのリセット動作を必要回数（例えば（n-1）回）実行するのに要する時間（総リセット時間）と、前記画素ブロックの各々で前記画素の信号電荷を対応する前記増幅トランジスタで増幅するのに要する時間（総増幅時間）との和が、最短の信号電荷蓄積期間（=125μsec）よりも十分小さくなるようにn値を設定すれば、前記画素のすべてについての信号電荷の蓄積（露光）が実質的に同時に行われることになる。換言すれば、このセンサ回路を使用することにより、前記画素のすべてについての信号電荷の実質的に同時蓄積（実質的に同時シャッタ化）が可能となる。

【0055】

また、このようにして同時シャッタ化が可能となることにより、従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

【0056】

さらに、本発明の第2の観点によるセンサ回路では、前記画素ブロックの各々に対して、当該ブロックの外側に前記増幅トランジスタが設けられているため、前記画素は一つの光電変換素子と一つの第1ゲート素子（通常はMOSトランジスタ）と一つのリセットトランジスタ（通常はMOSトランジスタ）を含むだけで済む。したがって、このセンサ回路を使用すれば、画素中に光電変換素子に加えて三つないし四つのMOSトランジスタを含む従来のアドレス指定型イメージセンサに比べて、高い画素開口率を実現することがで

10

20

30

40

50

きる。

【0057】

(6) 本発明の第2の観点によるセンサ回路の好ましい例では、前記増幅トランジスタが、単一の出力端を有する。この場合、前記増幅トランジスタの出力端に接続される次段の配線が簡単になるという利点がある。

【0058】

この例では、前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えるのが好ましい。この場合、前記出力トランジスタを使用することによって、前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

【0059】

本発明の第2の観点によるセンサ回路の他の好ましい例では、前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続される。この場合、前記第2ゲート素子の各々を対応する前記第1ゲート素子と同期して開閉することにより、前記画素ブロック中の複数の前記画素からの信号を複数の前記出力端より並列的に出力することができる。その結果、次段の信号処理が迅速に行えるという利点がある。

【0060】

この例では、前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えるのが好ましい。この場合、複数の前記出力トランジスタを使用することによって、複数の前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

【0061】

本発明の第2の観点によるセンサ回路のさらに他の好ましい例では、前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる。この場合、実質的な同時シャッタ化が容易に実現できるという利点がある。

【0062】

(7) 本発明の第3の観点によるアドレス指定型イメージセンサは、マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択する、三次元積層構造を持つアドレス指定型イメージセンサであって、複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素をリセットするためのリセットトランジスタと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子とを含んでおり、

少なくとも前記光電変換素子は、前記三次元積層構造を構成する第1半導体回路層の中に形成され、前記第1ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第2あるいは第3以降の半導体回路層の中に形成されていることを特徴とするものである。

【0063】

(8) 本発明の第3の観点によるアドレス指定型イメージセンサは、上述した本発明

10

20

30

40

50

の第1の観点によるセンサ回路を用い、少なくとも複数の前記光電変換素子を前記三次元積層構造を構成する前記第1半導体回路層の中に形成し、前記第1ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第2あるいはそれ以降の半導体回路層の中に形成したものに相当する。

【0064】

したがって、本発明の第1の観点によるセンサ回路について説明したのと同じ理由により、全画素についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現することができる。また、従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

10

【0065】

さらに、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現できることから、撮像領域の総面積に対する受光領域の総面積の割合を高くすることが可能となる。

【0066】

(9) 本発明の第3の観点によるアドレス指定型イメージセンサの好ましい例では、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子が前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタと複数の前記リセットトランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子が存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成する一つのトランジスタを含むだけであるから、各画素が光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。

20

【0067】

本発明の第3の観点によるアドレス指定型イメージセンサの他の好ましい例では、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子及び複数の前記リセットトランジスタが前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子と複数の前記リセットトランジスタが存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成する一つのトランジスタを含むだけであり、また、前記リセットトランジスタの総数は画素総数の(1/n)で済む。従って、各画素が、光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。

30

【0068】

本発明の第3の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記増幅トランジスタが、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子（選択トランジスタ）が接続される。そして、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子、複数の前記リセットトランジスタ及び複数の前記増幅トランジスタが前記第1半導体回路層の中に形成され、複数の前記第2ゲート素子（選択トランジスタ）が前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記増幅トランジスタが存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成する一つのトランジスタを含むだけであり、また、前記リセットトランジスタと前記増幅トランジスタの総数は、いずれも画素総数の(1/n)で済む。従って、各画素が、光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。

40

【0069】

本発明の第3の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では

50

、複数の前記光電変換素子のみが前記第1半導体回路層の中に形成され、複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子だけが形成されるから、各画素はまったくトランジスタを含まないことになる。よって、各画素が、光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。特に、画素開口率の向上が最大となる。

【0070】

本発明の第3の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記増幅トランジスタの各々が、単一の出力端を有する。この場合、前記増幅トランジスタの出力端に接続される次段の配線が簡単になるという利点がある。

【0071】

この例では、前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えるのが好ましい。この場合、前記出力トランジスタを使用することによって、前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

【0072】

本発明の第3の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記増幅トランジスタの各々が、当該増幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続される。この場合、前記第2ゲート素子の各々を対応する前記第1ゲート素子と同期して開閉することにより、前記画素ブロック中の複数の前記画素からの信号を複数の前記出力端より並列的に出力することができる。その結果、次段の信号処理が迅速に行えるという利点がある。

【0073】

この例では、前記第2あるいは第3以降の半導体回路層の中に、前記増幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えるのが好ましい。この場合、複数の前記出力トランジスタを使用することによって、複数の前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

【0074】

本発明の第3の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジスタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる。この場合、実質的な同時シャッタ化が容易に実現できるという利点がある。

【0075】

(10) 本発明の第4の観点によるアドレス指定型イメージセンサは、マトリックス状に配置された複数の画素を有すると共に、アドレス指定によって前記画素の各々を選択する、三次元積層構造を持つアドレス指定型イメージセンサであって、複数の前記画素を所定数毎に共通ノードに並列接続して構成された複数の画素ブロックと、

複数の前記画素ブロックの各々の前記共通ノードに接続された、当該画素ブロック内の複数の前記画素から送出される信号を増幅する増幅トランジスタとを備え、

前記画素ブロックの各々において、前記画素の各々は、照射された光に応じて信号電荷を生成する光電変換素子と、その光電変換素子と当該画素ブロックの前記共通ノードとの間の経路に設けられた第1ゲート素子と、当該光電変換素子と前記第1ゲート素子との接

10

20

30

40

50

続点に接続された、当該画素をリセットするためのリセットトランジスタとを含んでおり、

少なくとも前記光電変換素子は、前記三次元積層構造を構成する第1半導体回路層の中に形成され、前記第1ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第2あるいはそれ以降の半導体回路層の中に形成されていることを特徴とするものである。

【0076】

(11) 本発明の第4の観点によるアドレス指定型イメージセンサは、上述した本発明の第2の観点によるセンサ回路を用い、少なくとも複数の前記光電変換素子を前記三次元積層構造を構成する前記第1半導体回路層の中に形成し、前記第1ゲート素子と前記リセットトランジスタと前記増幅トランジスタは、前記三次元積層構造を構成する第2あるいはそれ以降の半導体回路層の中に形成したものに相当する。10

【0077】

したがって、本発明の第2の観点によるセンサ回路について説明したのと同じ理由により、全画素についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現することができる。また、従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

【0078】

さらに、従来のアドレス指定型イメージセンサよりも高い高い画素開口率を実現できることから、撮像領域の総面積に対する受光領域の総面積の割合を高くすることが可能となる。20

【0079】

(12) 本発明の第4の観点によるアドレス指定型イメージセンサの好ましい例は、上述した本発明の第3の観点によるアドレス指定型イメージセンサのそれと同様である。これは、本発明の第3の観点によるアドレス指定型イメージセンサでは、リセットトランジスタが前記ブロックの各々に対して設けられている（つまり、リセットトランジスタが各ブロックの外部に設けられている）のに対し、本発明の第4の観点によるアドレス指定型イメージセンサでは、リセットトランジスタが前記ブロックの各々に属する複数の前記光電変換素子の各々に対して設けられている点で、両者は異なるだけだからである。30

【0080】

すなわち、本発明の第4の観点によるアドレス指定型イメージセンサの好ましい例では、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子が前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタと複数の前記リセットトランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子が存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成する一つのトランジスタを含むだけであるから、各画素が光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。

【0081】

本発明の第4の観点によるアドレス指定型イメージセンサの他の好ましい例では、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子及び複数の前記リセットトランジスタが前記第1半導体回路層の中に形成され、複数の前記増幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子と複数の前記リセットトランジスタが存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成するトランジスタと前記リセットトランジスタの二つを含むだけであるから、各画素が光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。40

【0082】

10

20

30

40

50

本発明の第4の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記增幅トランジスタが、当該增幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子（選択トランジスタ）が接続される。そして、複数の前記光電変換素子に加えて、複数の前記第1ゲート素子、複数の前記リセットトランジスタ及び複数の前記增幅トランジスタが前記第1半導体回路層の中に形成され、複数の前記第2ゲート素子（選択トランジスタ）が前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子の他に複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記增幅トランジスタが存在するが、各画素は前記光電変換素子に加えて前記第1ゲート素子を構成するトランジスタと前記リセットトランジスタの二つだけであり、また、前記增幅トランジスタの総数は画素総数の（1/n）で済む。従って、各画素が、光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。10

#### 【0083】

本発明の第4の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、複数の前記光電変換素子のみが前記第1半導体回路層の中に形成され、複数の前記第1ゲート素子と複数の前記リセットトランジスタと複数の前記增幅トランジスタが前記第2あるいは第3以降の半導体回路層の中に形成される。この場合、前記第1半導体回路層の中には、複数の前記光電変換素子だけが形成されるから、各画素はまったくトランジスタを含まないことになる。よって、各画素が、光電変換素子に加えて4トランジスタまたは3トランジスタを含む従来のアドレス指定型イメージセンサに比べて、画素開口率が向上する。特に、画素開口率の向上が最大となる。20

#### 【0084】

本発明の第4の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記增幅トランジスタの各々が、単一の出力端を有する。この場合、前記增幅トランジスタの出力端に接続される次段の配線が簡単になるという利点がある。

#### 【0085】

この例では、前記第2あるいは第3以降の半導体回路層の中に、前記增幅トランジスタの出力端に接続された記憶用容量素子と、当該容量素子に記憶された信号の出力を制御する出力トランジスタとを、さらに備えるのが好ましい。この場合、前記出力トランジスタを使用することによって、前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。30

#### 【0086】

本発明の第4の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記增幅トランジスタの各々が、当該增幅トランジスタに対応する前記画素ブロック中の前記画素の総数に等しい数の出力端を有していると共に、それら出力端の各々に第2ゲート素子が接続される。この場合、前記第2ゲート素子の各々を対応する前記第1ゲート素子と同期して開閉することにより、前記画素ブロック中の複数の前記画素からの信号を複数の前記出力端より並列的に出力することができる。その結果、次段の信号処理が迅速に行えるという利点がある。40

#### 【0087】

この例では、前記第2あるいは第3以降の半導体回路層の中に、前記增幅トランジスタの複数の前記出力端にそれぞれ接続された複数の記憶用容量素子と、これら容量素子に記憶された信号の出力を制御する複数の出力トランジスタとを、さらに備えるのが好ましい。この場合、複数の前記出力トランジスタを使用することによって、複数の前記容量素子に記憶された信号を前記第1ゲート素子の開閉とは異なるタイミングで出力することができるという利点がある。

#### 【0088】

本発明の第4の観点によるアドレス指定型イメージセンサのさらに他の好ましい例では、前記画素のすべてに一括して信号電荷を生成・蓄積させる前に、前記リセットトランジ50

スタのすべてを用いて前記画素のすべてについて一括してリセットが行われ、前記画素ブロックの各々において、前記画素に蓄積された信号電荷に対応する信号が、対応する前記共通ノードを介して時系列的に読み出されてから対応する前記増幅トランジスタに送られる。この場合、実質的な同時シャッタ化が容易に実現できるという利点がある。

## 【0089】

(13) 本発明の第1及び第2の観点によるセンサ回路と、本発明の第3及び第4の観点によるアドレス指定型イメージセンサにおいて、「光電変換素子」とは、照射された光に応じて電荷を生成する素子を意味する。「光電変換素子」としては、半導体素子であるフォトダイオードが好適に使用できるが、照射された光に応じて電荷を生成する機能を持つ素子であれば、本発明はこれに限定されず、任意のものを使用可能である。

10

## 【0090】

「第1ゲート素子」とは、複数の前記光電変換素子の各々とそれに対応する前記共通ノードとを結ぶ経路を開閉するゲート機能を有する素子を意味する。MOSトランジスタが好適に使用できるが、本発明はこれに限定されるものではない。

## 【0091】

「リセットトランジスタ」は、前記グループに属する複数の前記画素（前記光電変換素子）で生成される信号電荷をリセットする機能を持つトランジスタであれば、任意のトランジスタを使用可能である。「リセットトランジスタ」としては、MOSトランジスタが好適に使用できるが、本発明はこれに限定されるものではない。

## 【0092】

「増幅トランジスタ」は、前記画素ブロックに属する複数の前記画素（前記光電変換素子）で生成される信号電荷に対応する信号を時系列的に増幅して出力信号を生成する機能を持つトランジスタであれば、任意のトランジスタを使用可能である。「増幅トランジスタ」としては、MOSトランジスタが好適に使用できるが、本発明はこれに限定されるものではない。

20

## 【0093】

「第1半導体回路層」及び「第2あるいは第3以降の半導体回路層」とは、それぞれ、半導体回路の層、換言すれば、層状に形成された半導体回路を意味する。通常は、「半導体基板」と、その半導体基板の内部または表面に形成された「素子」及び「配線」を含むが、これに限定されるわけではない。「半導体基板」の材質は任意であり、所望の半導体素子や回路を形成できるものであれば、シリコンでもよいし、化合物半導体でもよいし、その他の半導体でもよい。「半導体基板」の構造も任意であり、半導体製の单なる板でもよいし、いわゆるSOI(Silicon On Insulator)基板でもよい。

30

## 【0094】

「第1半導体回路層」及び「第2あるいは第3以降の半導体回路層」は、必要に応じて（例えば、第1半導体回路層と第2あるいは第3以降の半導体回路層だけでは所望の剛性が得られない場合）、それらを支持するに足る剛性を持つ任意の「支持基板」に対して固定される。「支持基板」の材質は任意である。すなわち、半導体であってもよいし、ガラスであってもよいし、その他の材質であってもよい。内部に回路が形成された半導体基板、すなわち、いわゆるLSIウェハーやLSIチップでもよい。

40

## 【0095】

「埋込配線」とは、「第1半導体回路層」または「第2あるいは第3以降の半導体回路層」の内部に埋設される積層方向の電気的接続用の配線ないし導体を言う。「埋込配線」は、通常、半導体基板に形成された「トレンチ」または「透孔」の内壁面全体を覆う「絶縁膜」と、その絶縁膜の内側の空間に充填された（埋め込まれた）「導電性材料」とから構成される。しかし、この構成に限定されるわけではない。

## 【0096】

ここで、「トレンチ」または「透孔」とは、所望の深さを持ち、埋込配線となる導電性材料を収容するものであればよく、構成は任意である。「トレンチ」または「透孔」の深さ、開口形状、開口寸法、断面形状等は、必要に応じて任意に設定できる。「トレンチ」

50

または「透孔」の形成方法は、半導体基板をその表面側から選択的に除去して形成できるものであれば、任意の方法が使用できる。例えば、マスクを用いた異方性エッチング法が好適に使用できる。

#### 【0097】

「トレンチ」または「透孔」の内壁面を覆う「絶縁膜」は、半導体基板と「トレンチ」または「透孔」の内部に充填される「導電性材料」とを電気的に絶縁できるものであれば、任意の絶縁膜が使用できる。例えば、二酸化シリコン(SiO<sub>2</sub>)、窒化シリコン(SiN<sub>x</sub>)等が好適に使用できる。「絶縁膜」の形成方法は、任意である。

#### 【0098】

「トレンチ」または「透孔」の内部に充填される「導電性材料」は、埋込配線(例えは導電性プラグ)として使用できるものであればよく、任意の材料が使用できる。例えば、ポリシリコン等の半導体、タンゲステン(W)、銅(Cu)、アルミニウム(Al)等の金属が好適に使用できる。「導電性材料」の充填方法は、半導体基板の片面から「導電性材料」を「トレンチ」または「透孔」の内部に充填できるものであれば、任意の方法が使用できる。

#### 【発明の効果】

#### 【0099】

本発明のセンサ回路によれば、(a)全画素についての信号電荷の実質的同時蓄積(実質的同時シャッタ化)が可能であると共に、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現できる、(b)従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる、という効果が得られる。

#### 【0100】

本発明のアドレス指定型イメージセンサによれば、(a)全画素についての信号電荷の実質的同時蓄積(実質的同時シャッタ化)が可能であると共に、従来のアドレス指定型イメージセンサよりも高い画素開口率を実現できる、(b)従来のアドレス指定型イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる、(c)撮像領域の総面積に対する受光領域の総面積の割合が高い、という効果が得られる。

#### 【発明を実施するための最良の形態】

#### 【0101】

以下、本発明の好適な実施の形態について、添付図面を参照して詳細に説明する。

#### 【0102】

##### (第1実施形態)

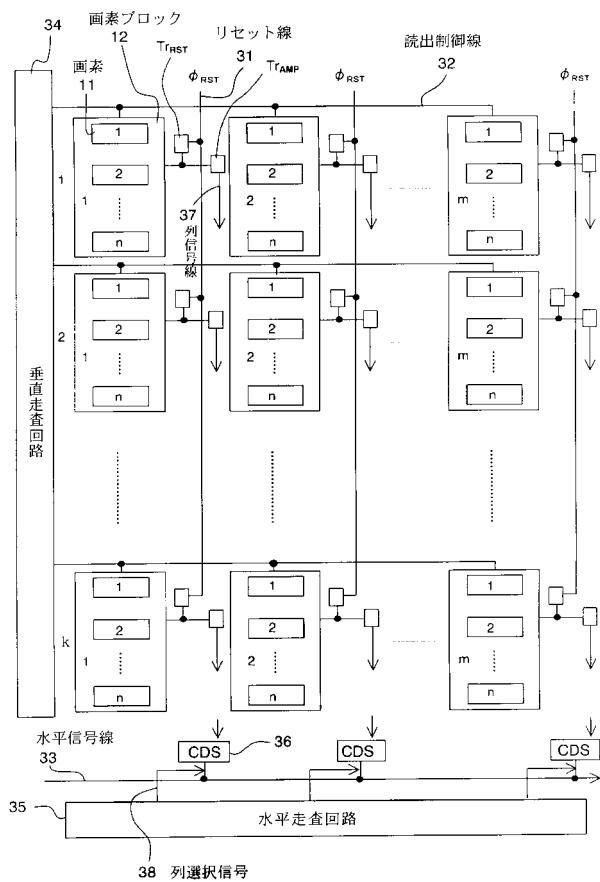

図2は、本発明の第1実施形態に係るセンサ回路1の要部回路構成を示す図である。図1は、このセンサ回路1が使用されるアドレス指定型イメージセンサ(以下、CMOSイメージセンサともいう)の全体構成を示す機能ブロック図である。このセンサ回路1は、本発明の第1の観点によるセンサ回路に対応する。

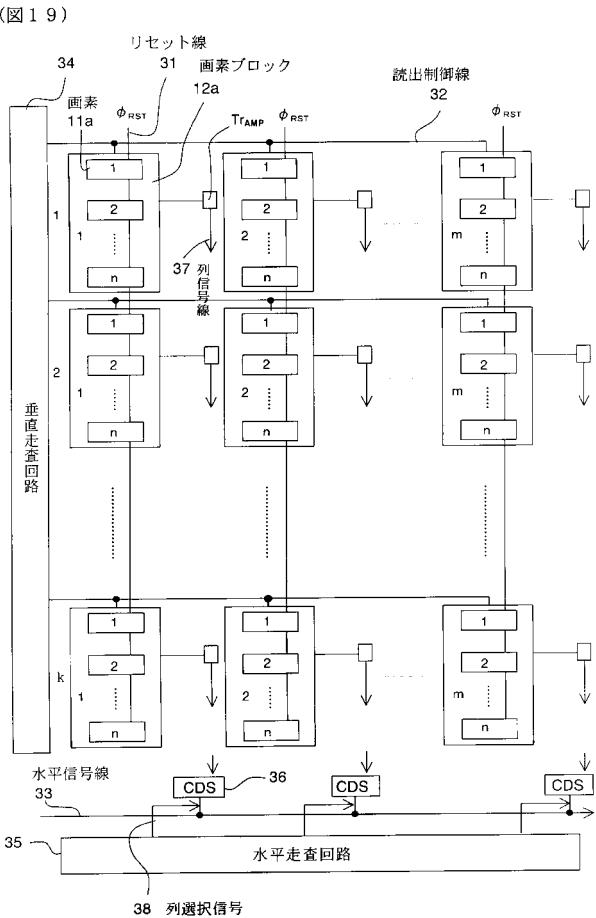

#### 【0103】

図1のイメージセンサの全体構成は、図30(a)に示す従来のCMOS(アドレス指定型)イメージセンサとほぼ同様であって、(k×n)行m列(k、n、mはいずれも2以上の整数)のマトリックス状に配置された(k×n)×m個の画素11(以下、これら画素11により形成されるマトリックスを「画素マトリックス」ともいう)を備えている。ただし、これらの画素11は、(k×m)個の画素ブロック12に区分(ブロック化)されている点と、各画素11中にリセットトランジスタ及び増幅トランジスタが含まれていない点で、従来のCMOSイメージセンサとは異なる。すなわち、各画素ブロック12では、同じ列に属する画素11がn個毎にまとめられて共通ノード(図1には図示せず。図2では共通ノード13に対応する)に並列接続されて、画素ブロック12を構成している(図2を参照)。画素ブロック12もマトリックス状に配置されている。

#### 【0104】

10

20

30

40

50

リセットトランジスタ  $T_{RST}$  及び増幅トランジスタ  $T_{AMP}$  は、画素ブロック 12 の外部において画素ブロック 12 毎に一つずつ設けられている。換言すれば、リセットトランジスタ  $T_{RST}$  及び増幅トランジスタ  $T_{AMP}$  は、それぞれ、各画素ブロック 12 中の  $n$  個の画素 11 に対して共用される。したがって、リセットトランジスタ  $T_{RST}$  の総数は  $(k \times m)$  個であり、増幅トランジスタ  $T_{AMP}$  の総数も  $(k \times m)$  個である。

#### 【0105】

各画素ブロック 12 の近傍には、それぞれが画素マトリックスの対応する列に沿って延在する  $m$  本のリセット線 31 が形成されている。各画素ブロック 12 毎に一つのリセットトランジスタ  $T_{RST}$  が設けられているので、各リセット線 31 には  $k$  個のリセットトランジスタ  $T_{RST}$  が接続されていることになる。それらリセットトランジスタ  $T_{RST}$  の各々の出力端には、一つの増幅トランジスタ  $T_{AMP}$  が接続されている。各リセット線 31 は、対応する列に属する  $k$  個の画素ブロック 12 中の画素 11 に蓄積された信号電荷をリセットするために使用される。それらの画素 11 へのリセット用電圧の印加は、対応するリセットトランジスタ  $T_{RST}$  を用いて制御される。（画素 11 の信号電荷をリセットする際に、増幅トランジスタ  $T_{AMP}$  のゲート電極もリセットされる。）各増幅トランジスタ  $T_{AMP}$  は、対応する画素ブロック 12 の中の各画素 11 から読み出された信号を増幅するために使用される。各増幅トランジスタ  $T_{AMP}$  で増幅された信号は、当該増幅トランジスタ  $T_{AMP}$  の出力端を介して、対応する列信号線 37 に順に送出される。

10

20

#### 【0106】

各画素ブロック 12 の近傍には、さらに、それぞれが画素マトリックスの対応する行に沿って延在する  $(k \times n)$  本の読出制御線 32 が形成されている。これら読出制御線 32 は、同じ行に属する  $m$  個の画素ブロック 12 に対して  $n$  本ずつ設けられており、各画素ブロック 12 中の  $n$  個の画素 11 の各々から信号を読み出すために使用される。図 1 では、同じ行に属する  $m$  個の画素ブロック 12 に対して設けられた  $n$  本の読出制御線 32 を、まとめて一本の線で示している。

30

#### 【0107】

画素マトリックスの左端の近傍には、画素マトリックスの列に沿って延在する一つの垂直走査回路 34 が設けられている。この垂直走査回路 34 は、 $(k \times n)$  本の読出制御線 32 を順に走査してそれらを時系列的に選択する。その際に、各読出制御線 32 には、対応する行に属する  $m$  個の画素ブロック 12 の各々に含まれている  $n$  個の画素 11 を、時系列的に選択する信号（図 2 のトランスファゲート制御信号  $T_1 \sim T_n$  に対応する）が送出される。

40

#### 【0108】

画素マトリックスの下端の近傍には、画素マトリックスの行に沿って延在する一つの水平信号線 33 及び一つの水平走査回路 35 と、ノイズ除去用の  $m$  個の CDS 回路 36 とが設けられている。水平走査回路 35 は、 $m$  個の列選択信号 38 によってこれら CDS 回路 36 を時系列的に選択する。

#### 【0109】

$m$  個の CDS 回路 36 の各々には、当該列に属する  $k$  個の増幅トランジスタ  $T_{AMP}$  の出力端にそれぞれ接続された  $k$  本の列信号線 37 が並列に接続されている。したがって、同じ行に属する  $k$  個の増幅トランジスタ  $T_{AMP}$  の  $k$  個の出力信号が、対応する CDS 回路 36 に並列に入力される。 $m$  個の CDS 回路 36 の出力端子は、水平信号線 33 にそれぞれ接続されているので、各 CDS 回路 36 の出力信号は、水平信号線 33 を介して順次、当該イメージセンサの外部に出力される。

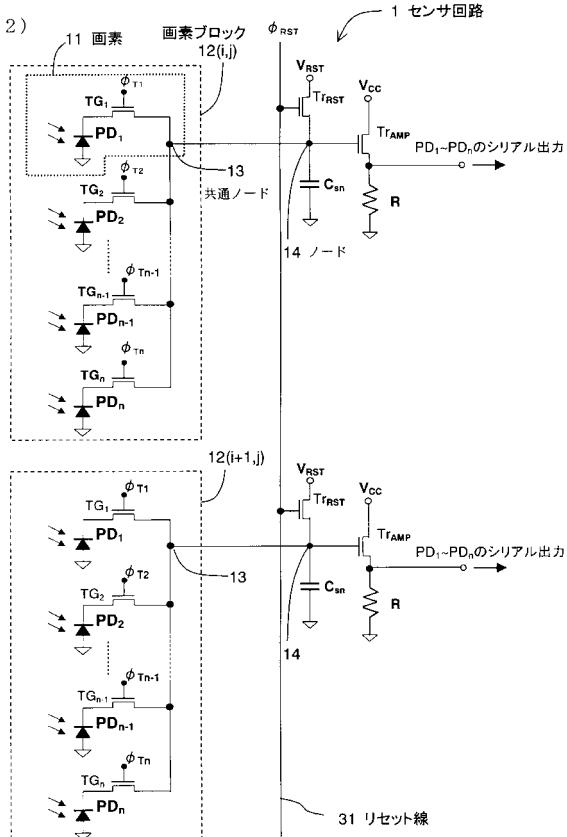

#### 【0110】

次に、図 2 を参照しながら、上記構成を持つアドレス指定型イメージセンサに使用される第 1 実施形態に係るセンサ回路 1 について説明する。

#### 【0111】

50

図2は、画素マトリックスの第j列（ただし、 $1 \leq j \leq m$ ）に属する二つの画素ブロック12の回路構成を示している。上の画素ブロック12は上からi番目（ただし、 $1 \leq i \leq k$ ）に位置し、下の画素ブロック12は上から第( $i+1$ )番目に位置している。したがって、必要に応じて、上の画素ブロック12を12( $i, j$ )と表示し、下の画素ブロック12を12( $i+1, j$ )と表示する。

#### 【0112】

上の画素ブロック12( $i, j$ )は、第j列の第[ $n \times (i-1) + 1$ ]行～第( $n \times i$ )行に属する画素11を含む。下の画素ブロック12( $i+1, j$ )は、第j列の第[ $n \times i + 1$ ]行～第[ $n \times (i+1)$ ]行に属する画素11を含む。これら二つの画素ブロック12( $i, j$ )と12( $i+1, j$ )は同一の構成を有するので、以下の説明では10、主として上の画素ブロック12( $i, j$ )について説明することにする。

#### 【0113】

画素ブロック12( $i, j$ )の中には、n個の画素11が含まれており、各画素11は一つのフォトダイオードと一つのトランスマジックゲートを含む。したがって、各画素11は、n個のフォトダイオードPD<sub>1</sub>～PD<sub>n</sub>と、n個のトランスマジックゲートTG<sub>1</sub>～TG<sub>n</sub>を含んでいる。トランスマジックゲートTG<sub>1</sub>～TG<sub>n</sub>の各々は、MOSトランジスタから構成されている。フォトダイオードPD<sub>1</sub>～PD<sub>n</sub>の各々のアノードは、トランスマジックゲートTG<sub>1</sub>～TG<sub>n</sub>の対応するものの一方のソース・ドレイン領域に接続され、カソードは所定電位（通常は接地電位）の端子または領域に共通接続されている。トランスマジックゲートTG<sub>1</sub>～TG<sub>n</sub>の各々の他方のソース・ドレイン領域は、画素ブロック12( $i, j$ )の中の共通ノード13に共通接続されている。すなわち、画素ブロック12( $i, j$ )の中のn個の画素11は、共通ノード13に並列に接続されている。

#### 【0114】

画素ブロック12( $i, j$ )の共通ノード13は、当該画素ブロック12( $i, j$ )に対応して設けられた共通のリセットトランジスタTR<sub>ST</sub>の一方のソース・ドレイン領域と、当該画素ブロック12( $i, j$ )に対応して設けられた共通の増幅トランジスタTA<sub>MP</sub>のゲート電極に、ノード14で接続されている。これらのリセットトランジスタTR<sub>ST</sub>と増幅トランジスタTA<sub>MP</sub>は、いずれも画素ブロック12( $i, j$ )の外側に設けられている。リセットトランジスタTR<sub>ST</sub>の他方のソース・ドレイン領域は、リセット用電圧源（リセット電圧=V<sub>\_RST</sub>）に接続されている。増幅トランジスタTA<sub>MP</sub>の一方のソース・ドレイン領域は、直流電源（電源電圧=V<sub>CC</sub>）に接続されており、他方のソース・ドレイン領域（出力側）は、当該画素ブロック12( $i, j$ )の出力端子（すなわち、対応する列信号線37）に接続されている。増幅トランジスタTA<sub>MP</sub>の出力端（出力側のソース・ドレイン領域）は、抵抗器Rを介して所定電位（通常は接地電位）の端子または領域に接続されており、ソースフォロア形式の増幅器を構成している。ノード14に接続された容量C<sub>s,n</sub>は、当該ノード14に生じる寄生容量である。ノード14は、寄生容量C<sub>s,n</sub>を介して所定電位（通常は接地電位）の端子または領域に接続されている。

#### 【0115】

増幅トランジスタTA<sub>MP</sub>の出力端子（出力側のソース・ドレイン領域）は、図1に示すように、対応する列信号線37に接続されているから、増幅トランジスタTA<sub>MP</sub>の出力信号、すなわちn個のフォトダイオードPD<sub>1</sub>～PD<sub>n</sub>のシリアル（時系列的な）出力信号は、対応する列信号線37を介して対応するCDS回路36に送られる。そして、CDS回路36から水平信号線33に送られる際に、水平走査回路35の走査によってm個の列選択信号38を介して当該列信号線37が選択され、それによって当該シリアル出力信号は水平信号線33に送られる。その後、水平信号線33の一端（図1では右端）に設けられた当該イメージセンサの出力端子（図示せず）まで送られる。

#### 【0116】

画素ブロック12( $i, j$ )の以外のすべての画素ブロック12は、画素ブロック12( $i, j$ )と同じ構成を有しているので、上述したのと同様にして、n個のフォトダイオ

10

20

30

40

50

ード  $P D_1 \sim P D_n$  のシリアル出力信号が当該イメージセンサの出力端子まで送られる。こうして被写体の撮像が可能となる。

#### 【0117】

次に、以上の構成を持つセンサ回路1を備えたアドレス指定型イメージセンサの動作(信号電荷の生成・蓄積から出力信号の出力まで)について説明する。

#### 【0118】

##### 1. 全画素(全フォトダイオード)のグローバルリセット

まず、全画素11のフォトダイオード  $P D_1 \sim P D_n$  の各々に対して設けられたトランスマジックゲート  $T G_1 \sim T G_n$  (第1ゲート素子)を構成するMOSトランジスタのゲート電極にそれぞれ印加されるパルス信号(トランスマジックゲート制御信号)  $T_1 \sim T_n$  の論理状態を  $H i g h (H)$  とし、もって全トランスマジックゲート  $T G_1 \sim T G_n$  を導通状態とする。

#### 【0119】

次に、全画素11のトランスマジックゲート  $T G_1 \sim T G_n$  を開いたままで、全画素ブロック12の各々に対して設けられたリセットトランジスタ  $T r_{R S T}$  のゲート電極に印加されるパルス信号(リセット制御信号)  $R S T$  の論理状態を  $H$  とし、もって全リセットトランジスタ  $T r_{R S T}$  を一括して導通状態にする。その結果、所定のリセット電圧  $V_{R S T}$  が、ノード14と共にノード13とトランスマジックゲート  $T G_1 \sim T G_n$  を介して、全画素11のフォトダイオード  $P D_1 \sim P D_n$  に同時に印加される。その結果、全画素11のフォトダイオード  $P D_1 \sim P D_n$  に印加される電圧がリセット電圧  $V_{R S T}$  にほぼ等しくされる、換言すれば、全画素11のフォトダイオード  $P D_1 \sim P D_n$  がリセットされる。こうして、全画素11の一括同時リセット、すなわち「グローバルリセット」が行われる。

#### 【0120】

##### 2. 露光(電荷蓄積)

次に、全画素11のトランスマジックゲート  $T G_1 \sim T G_n$  に印加されるトランスマジックゲート制御信号  $T_1 \sim T_n$  の論理状態を  $L o w (L)$  とし、すべてのトランスマジックゲート  $T G_1 \sim T G_n$  を遮断状態とする。また、それと同時に、リセット制御信号  $R S T$  の論理状態を  $L$  とし、全リセットトランジスタ  $T r_{R S T}$  も一括して遮断状態とする。

#### 【0121】

その後、その状態で、全画素11のフォトダイオード  $P D_1 \sim P D_n$  に光を照射させ、全フォトダイオード  $P D_1 \sim P D_n$  に一括して信号電荷を生成・蓄積させる。照射時間は通常、数百  $\mu s e c$  ないし数  $m s e c$  で、非常に長い。

#### 【0122】

信号電荷の生成・蓄積が完了すると同時に、リセット制御信号  $R S T$  の論理状態を再び  $H$  として全リセットトランジスタ  $T r_{R S T}$  を一括して導通状態にし、所定時間(例えば、1  $\mu s e c$ )経過後、リセット制御信号  $R S T$  の論理状態を再び  $L$  として全リセットトランジスタ  $T r_{R S T}$  を一括して遮断状態にする。こうして、全ノード14(すなわち全増幅トランジスタ  $T r_{A M P}$  のゲート電極)にリセット電圧  $V_{R S T}$  を一時的に印加し、全増幅トランジスタ  $T r_{A M P}$  のゲート電圧を所定の基準電圧に設定する。

#### 【0123】

##### 3. 信号の読み出しとその増幅

上記のようにして全フォトダイオード  $P D_1 \sim P D_n$  に生成・蓄積せしめられた電荷量に比例する信号は、電圧の形式で次のようにして各画素11から読み出され、増幅される。

#### 【0124】

すなわち、まず、垂直走査回路34と水平走査回路35によって一つの画素ブロック12が選択されると、その画素ブロック12中のn個のトランスマジックゲート制御信号  $T_1 \sim T_n$  の論理状態を順に  $L$  から  $H$  に変えてトランスマジックゲート  $T G_1 \sim T G_n$  を順に導通状態にしていく。そして、それらの導通状態を所定時間(例えば、0.1  $\mu s e c$ )保

10

20

30

40

50

持した後、順にそれらの論理状態を  $L$  に戻していく。こうして、当該画素ブロック 12 中の全フォトダイオード  $PD_1 \sim PD_n$  から信号がノード 14 に時系列的に読み出される。その間、全リセットトランジスタ  $Tr_{RST}$  は遮断状態に保持される。

【0125】

ノード 14 にソースフォロア形式で接続された増幅トランジスタ  $Tr_{AMP}$  は、そのゲート電極がノード 14 に接続されているので、ノード 14 に読み出された電圧信号は直ちに当該増幅トランジスタ  $Tr_{AMP}$  で増幅される。そして、増幅された信号は、当該増幅トランジスタ  $Tr_{AMP}$  の出力端子側のソース・ドレイン領域から列信号線 37 に向けて出力される。

【0126】

当該画素ブロック 12 中の  $n$  個の画素 11、すなわちフォトダイオード  $PD_1 \sim PD_n$  から信号を読み出して増幅する際に、一つの画素 11（例えば、フォトダイオード  $PD_1$ ）からの信号の読み出しと増幅が完了してから、次の画素 11（例えば、フォトダイオード  $PD_2$ ）の信号の読み出しが開始するまでの間に、当該画素ブロック 12 用のリセットトランジスタ  $Tr_{RST}$  を導通状態にすることによってリセット電圧  $V_{RST}$  をノード 14 に一時的に印加し、もって当該ノード 14（増幅トランジスタ  $Tr_{AMP}$  のゲート電極）を基準電位に設定する（リセットする）必要がある。これは、そうしないと、先の画素 11（例えば、フォトダイオード  $PD_1$ ）からの信号の影響が残って次の画素 11（例えば、フォトダイオード  $PD_2$ ）からの信号に誤差が生じる恐れがあるからである。

【0127】

当該画素ブロック 12 中には  $n$  個のフォトダイオード  $PD_1 \sim PD_n$  があるから、トランസファゲート制御信号  $T_1 \sim T_n$  による読み出し動作の総回数は  $n$  回、増幅トランジスタ  $Tr_{AMP}$  による増幅動作の総回数は  $n$  回、増幅トランジスタ  $Tr_{AMP}$  のリセット動作の総回数は ( $n - 1$ ) 回となる。

【0128】

具体的に説明すると、例えば、最初に、当該画素ブロック 12 の 1 番目のトランസファゲート  $TG_1$  を一時的に導通状態にして、1 番目のフォトダイオード  $PD_1$  に蓄積された信号電荷に比例する電圧信号をノード 14 に読み出す。その電圧信号は直ちに増幅トランジスタ  $Tr_{AMP}$  で増幅され、得られた増幅信号は列信号線 37 に向けて送られる。続いて、リセットトランジスタ  $Tr_{RST}$  を一時的に導通状態にして、増幅トランジスタ  $Tr_{AMP}$  のゲート電極（ノード 14）を基準電位にリセットする。その後、2 番目のフォトダイオード  $PD_2$  に蓄積された信号電荷に比例する電圧信号をノード 14 に読み出す。その電圧信号は直ちに増幅トランジスタ  $Tr_{AMP}$  で増幅され、得られた増幅信号は列信号線 37 に向けて送られる。続いて、リセットトランジスタ  $Tr_{RST}$  を一時的に導通状態にして、増幅トランジスタ  $Tr_{AMP}$  のゲート電極（ノード 14）を基準電位にリセットする。さらに、3 番目のフォトダイオード  $PD_3$ 、4 番目のフォトダイオード  $PD_4$  というように、上記と同じ動作が順に繰り返される。最後に、 $n$  番目のフォトダイオード  $PD_n$  についての読み出し動作と増幅動作を実行すると、当該画素ブロック 12 についての処理が終了する。

【0129】

図 1 のイメージセンサでは、当該画素ブロック 12 に対応する増幅トランジスタ  $Tr_{AMP}$  の出力端子が一つであるから、当該画素ブロック 12 中の全フォトダイオード  $PD_1 \sim PD_n$  から得られる  $n$  個の信号が、当該増幅トランジスタ  $Tr_{AMP}$  の出力端子側のソース・ドレイン領域から列信号線 37 に向けて時系列的に順に出力される。つまり、当該画素ブロック 12 から出力される信号は、フォトダイオード  $PD_1 \sim PD_n$  の信号電荷の量（照射された光の量）を反映する  $n$  個のパルス波形が所定間隔をあけて連結された一つのシリアル信号となる。

【0130】

上記イメージセンサは、合計で ( $k \times m$ ) 個の画素ブロック 12 を有するから、全画素 11 が走査される間に、上述した動作が ( $k \times m$ ) 回繰り返されることになる。

10

20

30

40

50

## 【0131】

当該画素ブロック12から出力される信号、すなわち、n個の信号パルスが所定間隔をあけて連結された一つのシリアル信号は、公知のサンプル・アンド・ホールド(Sample & Hold)回路やアナログ・デジタル(A/D)変換回路に送られ、所定の信号処理が行われる。

## 【0132】

現在の現実的な最高シャッタースピード(つまり最短の信号電荷蓄積期間)は(1/800)秒( $=125\mu\text{sec}$ )である。したがって、( $k \times m$ )個の画素ブロック12の各々について、リセットトランジスタ $T_{r_{RST}}$ によるノード14(増幅トランジスタ $T_{r_{AMP}}$ のゲート電極)のリセット動作を必要回数(つまり( $n-1$ )回)実行するのに要する時間(総リセット時間)と、当該画素ブロック12中の全画素11(全フォトダイオード $PD_1 \sim PD_n$ )からの信号を対応する増幅トランジスタ $T_{r_{AMP}}$ で増幅するのに要する時間(総増幅時間)の和を求め、その和の( $k \times m$ )倍の時間が、最短の信号電荷蓄積期間( $=125\mu\text{sec}$ )よりも十分小さくなるようにn値(各画素ブロック12中の画素11の総数)を設定すれば、全画素ブロック12に属する画素11(フォトダイオード $PD_1 \sim PD_n$ )についての信号電荷の蓄積(露光)が実質的に同時に行われることになる。換言すれば、全画素11についての信号電荷の実質的同时蓄積(実質的同时シャッタ化)が可能となる。

10

20

30

30

40

50

## 【0133】

また、全画素ブロック12の各々から独立して( $k \times m$ )個の出力シリアル信号が出力されるので、これら出力シリアル信号に対してアナログ・デジタル(A/D)変換等の処理を並列して行うことができる。よって、従来のCMOSイメージセンサにおけるものよりも高速でデータ処理が可能となる。これも、実質的同时シャッタ化の実現に貢献するものである。

## 【0134】

上述した動作から明らかなように、1フレーム内で見ると、各画素ブロック12から出力されるシリアル出力信号は、走査期間の終わりに近いものほど、当該走査期間の始めに生成・出力されたものよりも、わずかではあるが電荷蓄積期間が長くなる。このため、いっそう忠実度の高い画像データを得たい場合や、n値を大きくしたい場合は、電荷蓄積期間の変化に応じた信号補正を行う公知の回路を後段に設けてもよい。そうすれば、電荷蓄積期間の変動の影響を抑制あるいは回避することができるからである。

## 【0135】

このようにして実質的に同時シャッタ化が可能となることにより、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

## 【0136】

さらに、各画素ブロック12に対して、当該画素ブロック12の外側に共通のリセットトランジスタ $T_{r_{RST}}$ と共に増幅トランジスタ $T_{r_{AMP}}$ が設けられているため、当該画素ブロック12中の各画素11は一つのフォトダイオードと一つのゲート素子(MOSトランジスタ)を含むだけで済む。したがって、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率(例えば、60%程度)を実現することができる。

## 【0137】

なお、従来のCMOSイメージセンサでは、走査線の数に応じて信号処理がシリアルに行われるため、高速のA/D変換回路が必要であるが、この第1実施形態のセンサ回路1を用いたイメージセンサでは、n値を走査線数よりも小さく設定して並列度を上げることにより、増幅トランジスタ $T_{r_{AMP}}$ の各々のシリアル出力信号の処理速度を遅くすることが可能となる。このため、より簡単な構成のA/D変換回路を使用できるという効果もある。

## 【0138】

また、 $n$  個のフォトダイオード  $P D_1 \sim P D_n$  からの  $n$  個の出力信号が、シリアルに連結された形態で増幅トランジスタ  $T r_{AMP}$  の各々から出力されるため、増幅トランジスタ  $T r_{AMP}$  の各々の出力端子に接続される次段の配線が簡単になるという効果もある。

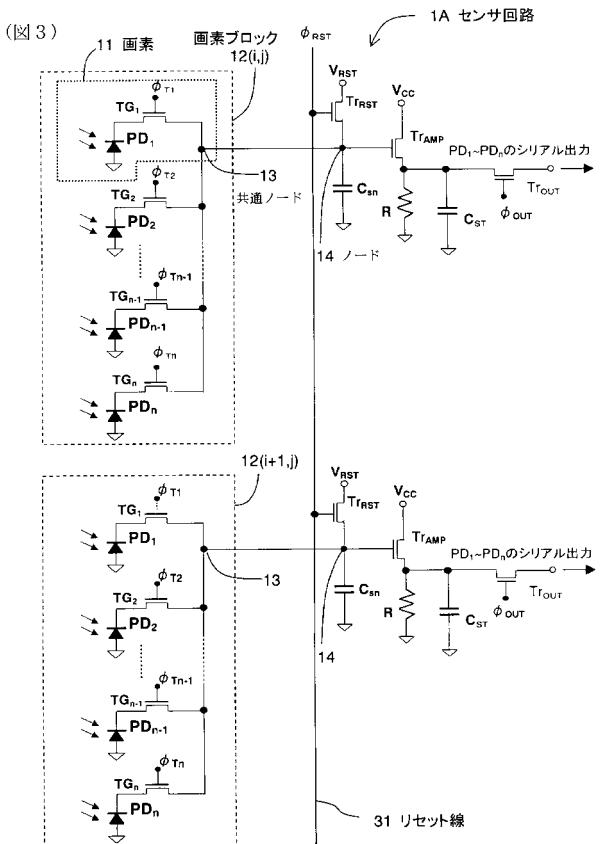

【0139】

(第2実施形態)

図3は、本発明の第2実施形態に係るセンサ回路1Aの構成を示す回路図である。このセンサ回路1Aが使用されるアドレス指定型イメージセンサの全体構成は、図1に示したものと同じであるから、その説明は省略する。このセンサ回路1Aは本発明の第1の観点によるセンサ回路に対応する。

【0140】

図3に示すセンサ回路1Aの回路構成は、第1実施形態に係るセンサ回路1(図2を参照)の回路構成とほぼ同じであり、各画素ブロック12に対して設けられた増幅トランジスタ  $T r_{AMP}$  の出力側に、記憶用容量素子  $C_{ST}$  と出力トランジスタ  $T r_{OUT}$  が追加されている点で異なるのみである。したがって、図2のセンサ回路1と同一の要素には同一の符号を付してその説明を省略する。

【0141】

記憶用容量素子  $C_{ST}$  は、対応する増幅トランジスタ  $T r_{AMP}$  で増幅された信号を一時的に記憶するためのもので、その一方の端子は当該増幅トランジスタ  $T r_{AMP}$  の出力側のソース・ドレイン領域に接続され、他方の端子は所定電位(通常は接地電位)の端子または領域に接続されている。

【0142】

出力トランジスタ  $T r_{OUT}$  は、当該記憶用容量素子  $C_{ST}$  に一時的に記憶せしめられた信号を対応する列信号線37に送出するためのもので、その出力側のソース・ドレイン領域は当該画素ブロック12の出力端子(列信号線37)に接続されている。出力トランジスタ  $T r_{OUT}$  は、そのゲート電極に印加される出力制御信号  $o_{UT}$  の論理状態をHにすることによって導通状態となり、Lにすることによって遮断状態となる。したがって、記憶用容量素子  $C_{ST}$  に一時的に記憶せしめられた信号を列信号線37に出力する際に、出力トランジスタ  $T r_{OUT}$  は、画素ブロック12中のトランスファゲート  $T G_1 \sim T G_n$  の開閉とは異なるタイミングで開閉されることが可能である。

【0143】

上述した第1実施形態のセンサ回路1を用いたイメージセンサでは、対応する画素ブロック12中の $n$ 個のフォトダイオード  $P D_1 \sim P D_n$  からのシリアル出力信号は、増幅トランジスタ  $T r_{AMP}$  で増幅された後に直ちに列信号線37に向けて出力される。これに対し、第2実施形態のセンサ回路2を用いたイメージセンサでは、画素ブロック12中の $n$ 個のフォトダイオード  $P D_1 \sim P D_n$  からのシリアル出力信号は、増幅トランジスタ  $T r_{AMP}$  で増幅された後に記憶用容量素子  $C_{ST}$  に一時的に記憶されるため、出力制御信号  $o_{UT}$  によって、当該フォトダイオード  $P D_1 \sim P D_n$  からの信号の読み出しのためのトランスファゲート  $T G_1 \sim T G_n$  の開閉とはタイミングをずらして、列信号線37に向けて出力させることができる。

【0144】

以上の構成を持つ第2実施形態に係るセンサ回路1Aを備えたイメージセンサでは、第1実施形態の場合と同様の理由により、全画素11についての信号電荷の実質的同時蓄積(実質的同時シャッタ化)が可能となる。また、このようにして実質的同時シャッタ化が可能となることにより、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

【0145】

また、各画素ブロック12に対して、当該画素ブロック12の外側に共通のリセットトランジスタ  $T r_{RST}$  と共に増幅トランジスタ  $T r_{AMP}$  が設けられているため、当該画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子(MOSトランジスタ)を含むだけで済む。したがって、一つの画素中にフォトダイオードに加えて

10

20

30

40

50

三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率を実現することができる。

【0146】

さらに、出力制御信号  $o_{UT}$  により、画素ブロック12中のトランジスタゲート  $TG_1 \sim TG_n$  の開閉とはタイミングをずらして列信号線37に信号を出力することができるため、第1実施形態のセンサ回路1を用いた場合よりも高速の撮像が可能であるという効果もある。

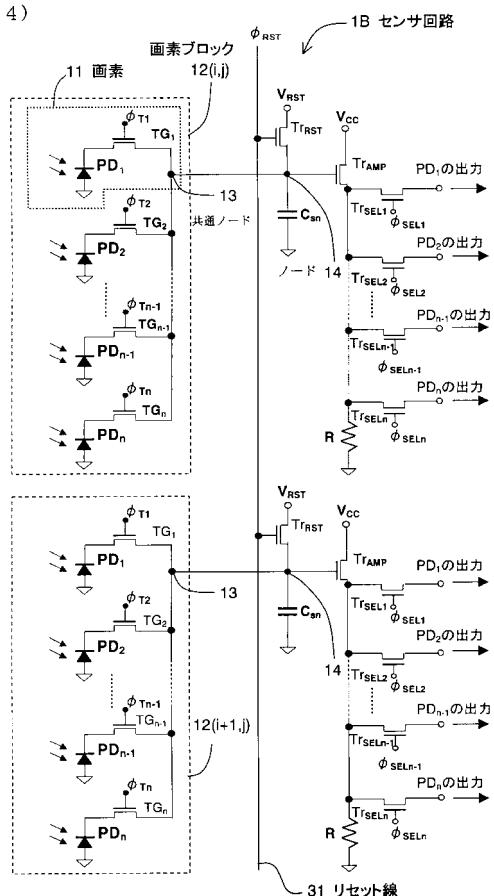

【0147】

(第3実施形態)

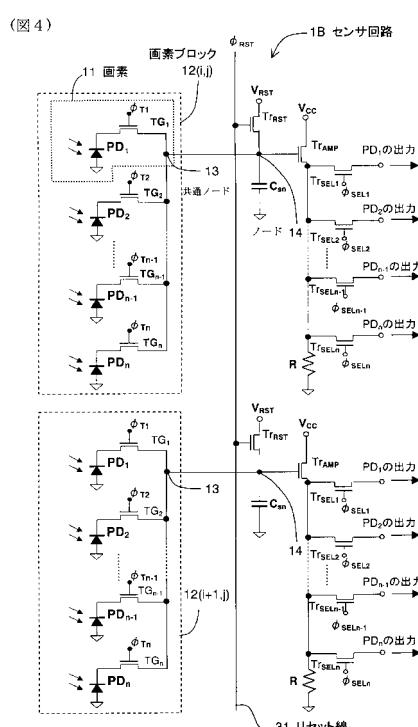

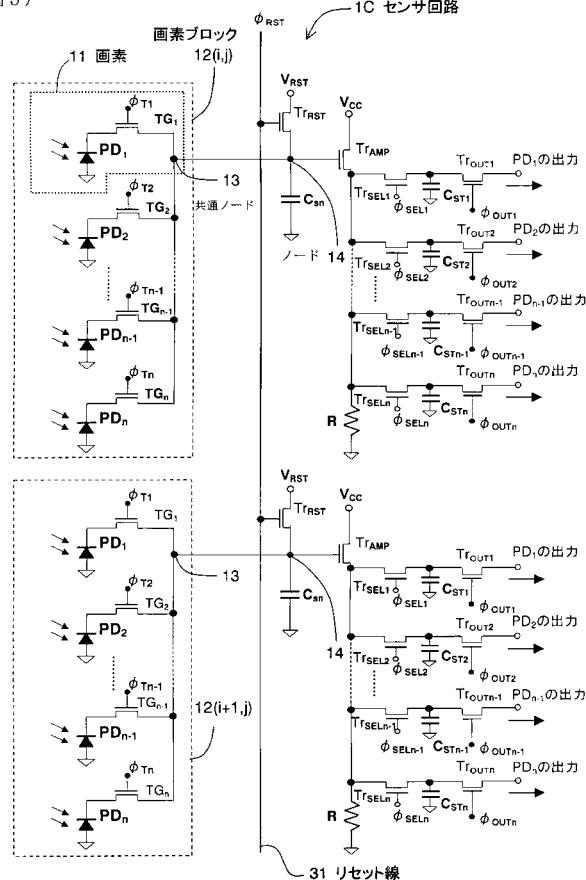

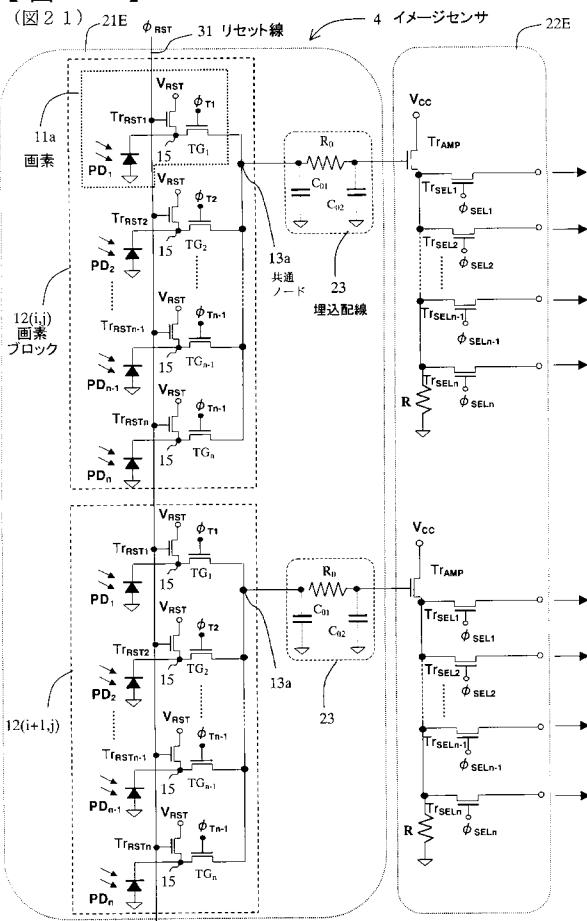

図4は、本発明の第3実施形態に係るセンサ回路1Bの構成を示す回路図である。このセンサ回路1Bが使用されるアドレス指定型イメージセンサの全体構成は、図1に示したものと同じであるから、その説明は省略する。このセンサ回路1Bは本発明の第1の観点によるセンサ回路に対応する。

【0148】

図4に示すセンサ回路1Bの回路構成は、第1実施形態に係るセンサ回路1(図2を参照)の回路構成とほぼ同じであり、各画素ブロック12に対して設けられた増幅トランジスタ  $Tr_{AMP}$  の出力側のソース・ドレン領域に、 $n$ 個の選択トランジスタ  $Tr_{SEL_1} \sim Tr_{SEL_n}$  (第2ゲート素子)が並列に接続されていて、増幅された  $n$ 個のフォトダイオード  $PD_1 \sim PD_n$  からの  $n$ 個の出力信号が、選択トランジスタ  $Tr_{SEL_1} \sim Tr_{SEL_n}$  を介して並列的に列信号線37に出力される点で異なるのみである。選択トランジスタ  $Tr_{SEL_1} \sim Tr_{SEL_n}$  は、それぞれ、ゲート電極に印加される出力選択信号  $SEL_1 \sim SEL_n$  の論理状態をHにすることによって導通状態となり、Lにすることによって遮断状態となる。したがって、図2のセンサ回路1と同一の要素には同一の符号を付してその説明を省略する。

【0149】

$n$ 個のフォトダイオード  $PD_1 \sim PD_n$  に生成・蓄積された信号電荷に対応する信号を読み出して増幅する際に、 $n$ 個の選択トランジスタ  $Tr_{SEL_1} \sim Tr_{SEL_n}$  は、対応する画素ブロック12中のトランジスタゲート  $TG_1 \sim TG_n$  とほぼ同期して開閉される。すなわち、例えば、フォトダイオード  $PD_1$  からの信号を読み出して増幅する際には、トランジスタゲート  $TG_1$  が開かれる(導通状態とされる)が、それとほぼ同期して選択トランジスタ  $Tr_{SEL_1}$  が開かれる(導通状態とされる)ので、読み出されたその信号電荷は、増幅トランジスタ  $Tr_{AMP}$  で増幅された後に直ちに選択トランジスタ  $Tr_{SEL_1}$  を介して列信号線37に向けて出力される。

【0150】

以上の構成を持つ第3実施形態に係るセンサ回路1Bを備えたイメージセンサでは、第1実施形態の場合と同様の理由により、全画素11についての信号電荷の実質的同時蓄積(実質的同時シャッタ化)が可能となる。また、このようにして実質的同時シャッタ化が可能となることにより、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

【0151】

さらに、各画素ブロック12に対して、当該画素ブロック12の外側に共通のリセットトランジスタ  $Tr_{RST}$  と共に増幅トランジスタ  $Tr_{AMP}$  が設けられているため、当該画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子(MOSトランジスタ)を含むだけで済む。したがって、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率を実現することができる。

【0152】

なお、増幅された  $n$ 個のフォトダイオード  $PD_1 \sim PD_n$  からの  $n$ 個の出力信号が、対応する  $n$ 個の選択トランジスタ  $Tr_{SEL_1} \sim Tr_{SEL_n}$  を介して並列的に列信号線37に向けて出力されるので、次段の信号処理が迅速に行えるという効果もある。

10

20

30

40

50

## 【0153】

## (第4実施形態)

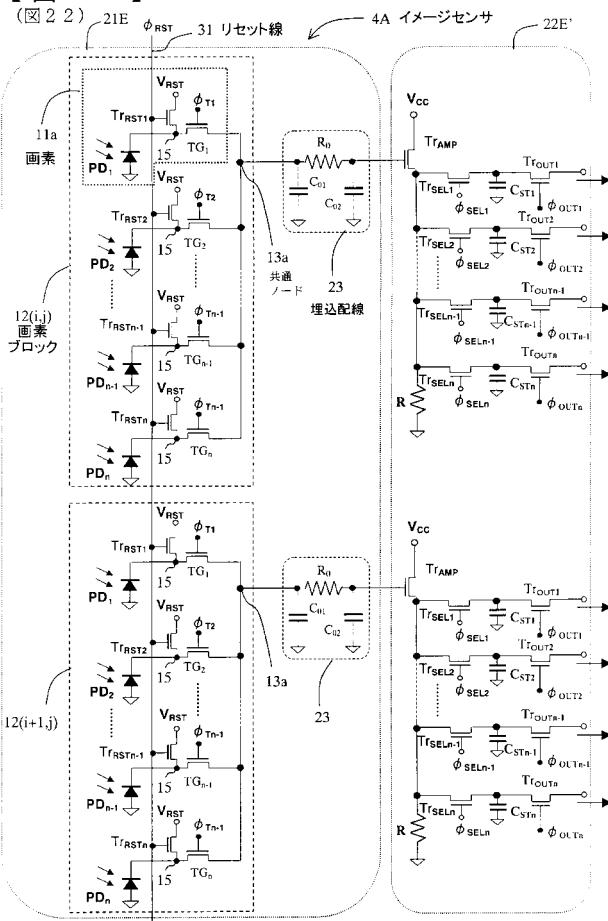

図5は、本発明の第4実施形態に係るセンサ回路1Cの構成を示す回路図である。このセンサ回路1Cが使用されるアドレス指定型イメージセンサの全体構成は、図1に示したものと同じであるから、その説明は省略する。このセンサ回路1Cは本発明の第1の観点によるセンサ回路に対応する。

## 【0154】

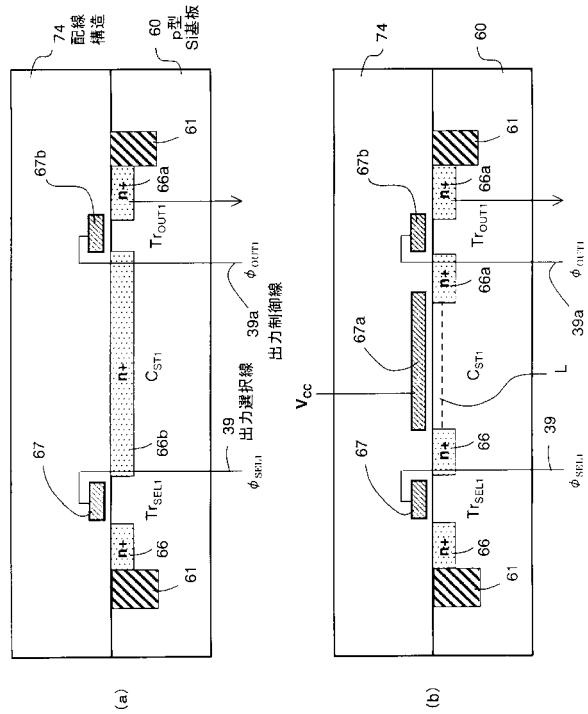

図5に示すセンサ回路1Cの回路構成は、第3実施形態に係るセンサ回路1B(図4を参照)の回路構成とほぼ同じであり、各画素ブロック12に対して設けられた増幅トランジスタTr<sub>AMP</sub>の出力側に、n個の選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>(第2ゲート素子)が並列に接続され、さらに、それら選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>の出力側に、n個の記憶用容量素子Cs<sub>T1</sub>～Cs<sub>Tn</sub>とn個の出力トランジスタTr<sub>OUT1</sub>～Tr<sub>OUTn</sub>が追加されている点で異なるのみである。したがって、図4のセンサ回路1Cと同一の要素には同一の符号を付してその説明を省略する。

10

## 【0155】

記憶用容量素子Cs<sub>T1</sub>～Cs<sub>Tn</sub>は、増幅トランジスタTr<sub>AMP</sub>で増幅されたn個のフォトダイオードPD<sub>1</sub>～PD<sub>n</sub>からの信号をそれぞれ一時的に記憶するためのもので、それらの一方の端子は対応する選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>の出力側のソース・ドレイン領域にそれぞれ接続され、他方の端子は所定電位(通常は接地電位)の端子または領域に接続されている。

20

## 【0156】

出力トランジスタTr<sub>OUT1</sub>～Tr<sub>OUTn</sub>は、当該記憶用容量素子Cs<sub>T1</sub>～Cs<sub>Tn</sub>に一時的に記憶せしめられた信号を対応する列信号線37に並列に送出するためのもので、それらの出力側のソース・ドレイン領域は当該画素ブロック12の出力端子(列信号線37)に接続されている。出力トランジスタTr<sub>OUT1</sub>～Tr<sub>OUTn</sub>は、それらのゲート電極に印加される出力制御信号o<sub>UT1</sub>～o<sub>UTn</sub>の論理状態をHにすることによって導通状態となり、Lにすることによって遮断状態となる。記憶用容量素子Cs<sub>T1</sub>～Cs<sub>Tn</sub>に一時的に記憶せしめられた増幅信号を列信号線37に並列出力する際に、出力トランジスタTr<sub>OUT1</sub>～Tr<sub>OUTn</sub>は、画素ブロック12中のトランスマニアゲートTG<sub>1</sub>～TG<sub>n</sub>の開閉とは異なるタイミングで開閉されることが可能である。

30

## 【0157】

上述した第3実施形態のセンサ回路1Bを用いたイメージセンサでは、対応する画素ブロック12中のn個のフォトダイオードPD<sub>1</sub>～PD<sub>n</sub>からのn個の出力信号は、増幅トランジスタTr<sub>AMP</sub>で増幅された後に直ちに列信号線37に向けて並列出力される。これに対し、第4実施形態のセンサ回路1Cを用いたイメージセンサでは、画素ブロック12中のn個のフォトダイオードPD<sub>1</sub>～PD<sub>n</sub>からの出力信号は、増幅トランジスタTr<sub>AMP</sub>で増幅された後に記憶用容量素子Cs<sub>T1</sub>～Cs<sub>Tn</sub>にそれぞれ一時的に記憶されるため、出力制御信号o<sub>UT1</sub>～o<sub>UTn</sub>によって、当該フォトダイオードPD<sub>1</sub>～PD<sub>n</sub>からの信号の読み出しのためのトランスマニアゲートTG<sub>1</sub>～TG<sub>n</sub>の開閉とはタイミングをずらして、列信号線37に向けて並列出力させることができる。

40

## 【0158】

以上の構成を持つ第4実施形態に係るセンサ回路1Cを備えたイメージセンサでは、第1実施形態の場合と同様の理由により、全画素11についての信号電荷の実質的同時蓄積(実質的同時シャッタ化)が可能となる。また、このようにして同時シャッタ化が可能となることにより、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができるようになる。

## 【0159】

また、各画素ブロック12に対して、当該画素ブロック12の外側に共通のリセットトランジスタTr<sub>\_RST</sub>と共に増幅トランジスタTr<sub>AMP</sub>が設けられているため、当該画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子(MOSト

50

ランジスタ)を含むだけで済む。したがって、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率を実現することができる。

#### 【0160】

さらに、出力制御信号  $o_{UT1} \sim o_{UTn}$  により、画素ブロック12中のトランスマッゲート  $TG_1 \sim TG_n$  の開閉とはタイミングをずらして列信号線37に信号を出力することができるため、第3実施形態のセンサ回路1Bを用いた場合よりも高速の撮像が可能であるという効果もある。

#### 【0161】

(第5実施形態)

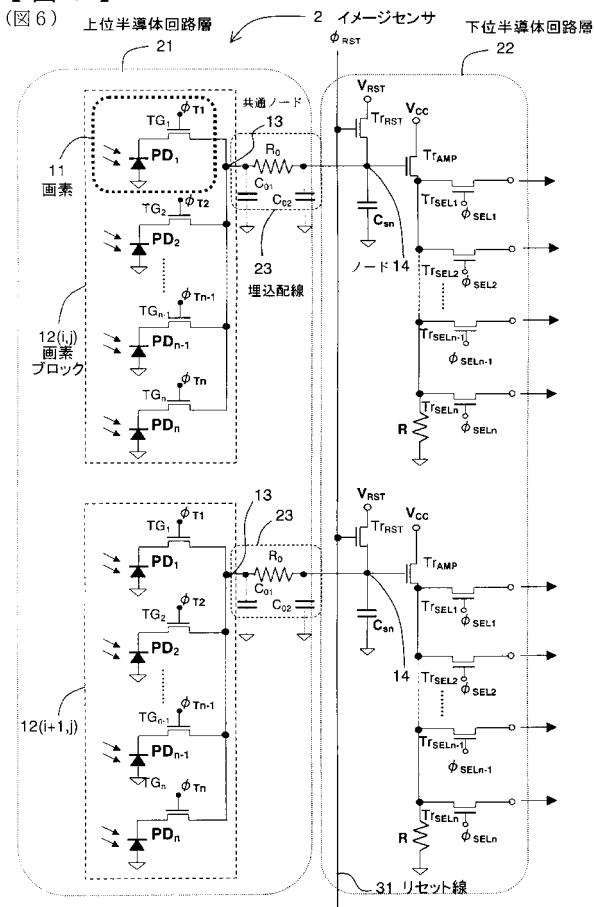

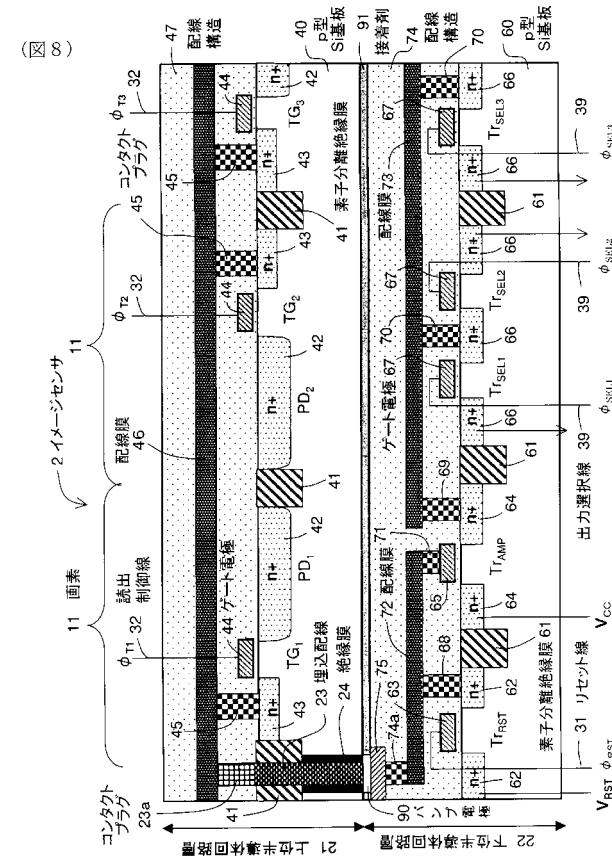

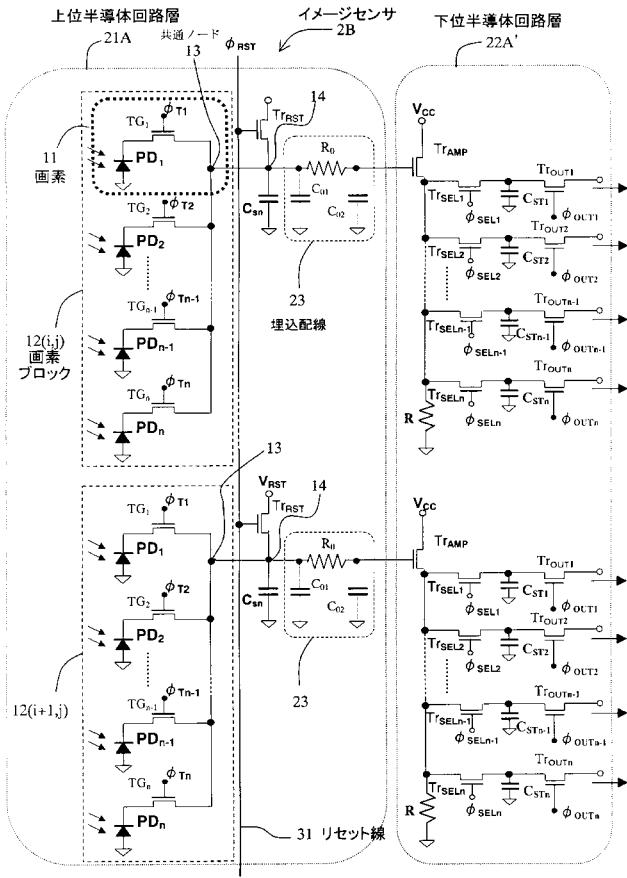

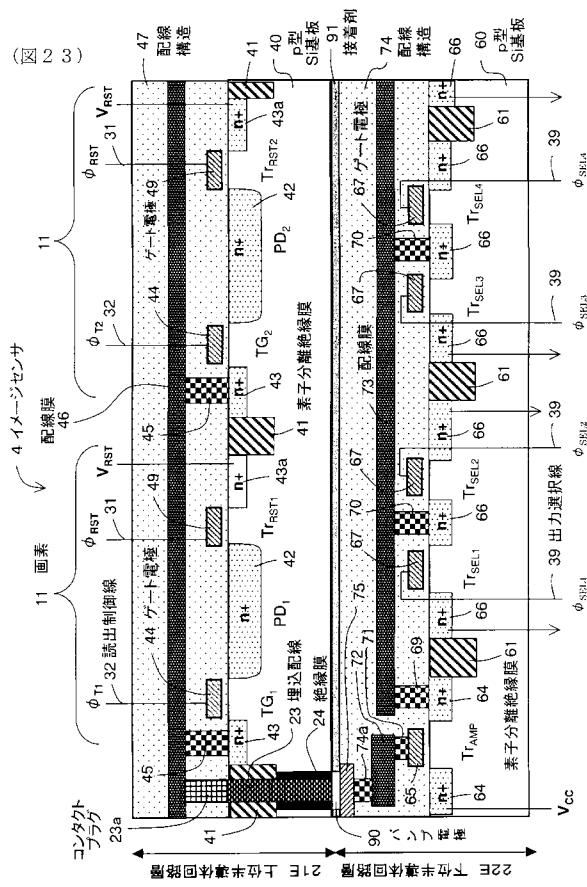

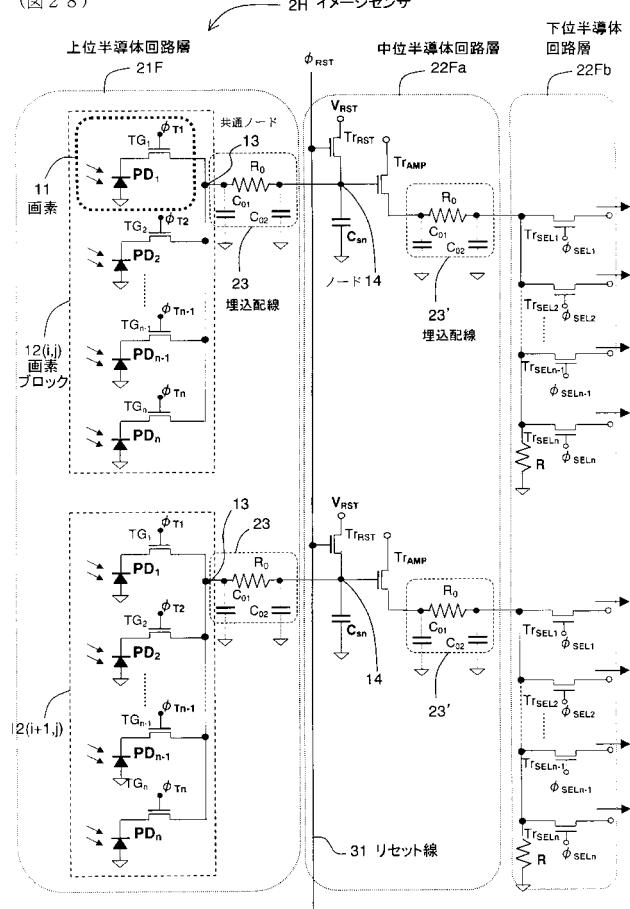

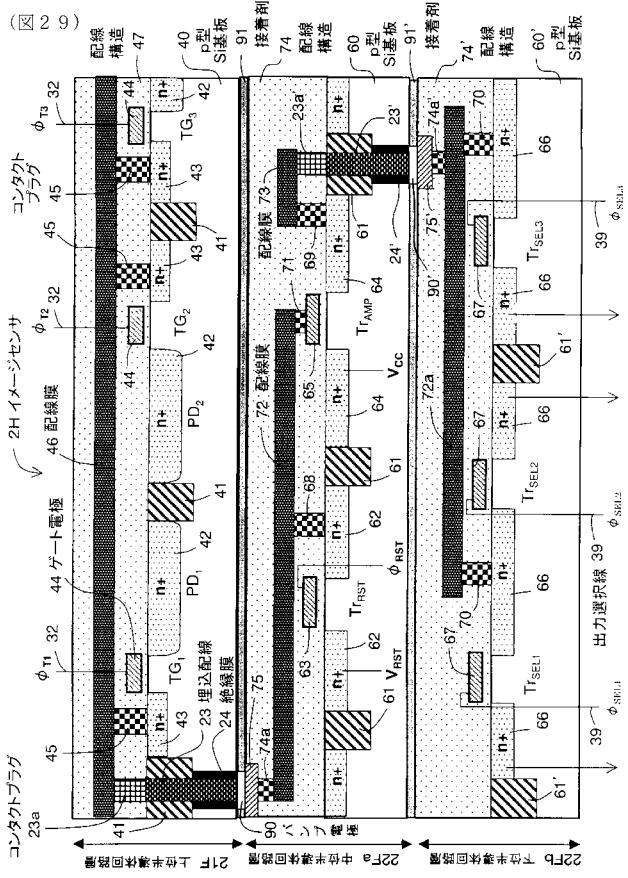

図6は、本発明の第5実施形態に係るアドレス指定型イメージセンサ2の要部の回路構成を示す回路図であり、図8はそのイメージセンサ2の実際構造を示す要部断面図である。このイメージセンサ2は、上述した第3実施形態のセンサ回路1B(図4参照)を使用したものであり、上位半導体回路層21と下位半導体回路層22を積層して二段の三次元積層構造とされている。このイメージセンサ2は、本発明の第3の観点によるイメージセンサに対応する。

#### 【0162】

イメージセンサ2の全体構成及び動作は、図1に示したものと同じであるから、それに関する説明は省略する。また、図6の回路構成は、図4に示した第3実施形態のセンサ回路1B(各増幅トランジスタ  $Tr_{AMP}$  の出力端に  $n$  個の選択トランジスタ  $Tr_{SEL1} \sim Tr_{SELn}$  が接続されており、記憶用容量素子と出力トランジスタは有しないもの)と同じであるから、同一の要素に同一の符号を付してその説明は省略する。ただし、イメージセンサ2では、後述するように、上位半導体回路層21中に形成された各画素ブロック12の共通ノード13と、下位半導体回路層22中に形成されたリセットトランジスタ  $Tr_{RST}$  及び増幅トランジスタ  $Tr_{AMP}$  の接続点であるノード14とを電気的に接続するために、公知の埋込配線23を使用していることから、埋込配線23と、当該埋込配線23によって生じる寄生抵抗  $R_0$  と寄生容量  $C_{01}$  及び  $C_{02}$  が図6に追加されている。埋込配線23は、各画素ブロック12(つまり、 $n$  個の画素11)に対して一つ設けられている。

#### 【0163】

次に、図8を参照しながら、イメージセンサ2の実際構造について説明する。

#### 【0164】

イメージセンサ2は、図8から明らかなように、上位半導体回路層21と下位半導体回路層22とを、埋込配線23と微細なバンプ電極(例えば、インジウム( $In$ )と金( $Ag$ )の積層体、あるいはタンゲステン( $W$ )等からなる)90と、電気的絶縁性の接着剤(例えばポリイミド)91とを用いて、機械的且つ電気的に接続して構成されている。

#### 【0165】

なお、埋込配線23及びバンプ電極90を形成する方法と、上位半導体回路層21と下位半導体回路層22を接着剤91を用いて機械的接続する方法としては、当業界に公知のものを用いることができるから、それに関する説明は省略する。

#### 【0166】

上位半導体回路層21には、( $k \times m$ )個の画素ブロック12、つまり( $k \times n$ ) $\times m$ 個の画素11が形成されている。したがって、上位半導体回路層21は、( $k \times n$ ) $\times m$ 個のフォトダイオード(すなわち、( $k \times m$ )組のフォトダイオード群  $PD_1 \sim PD_n$ )と、( $k \times n$ ) $\times m$ 個のトランスマッゲート(すなわち、( $k \times m$ )組のトランスマッゲート群  $TG_1 \sim TG_n$ )を含んでいる。上位半導体回路層21には、さらに、( $k \times m$ )個の埋込配線23が形成されている。

#### 【0167】

下位半導体回路層22には、( $k \times m$ )個のリセットトランジスタ  $Tr_{RST}$  と、( $k \times m$ )個の増幅トランジスタ  $Tr_{AMP}$  と、( $k \times n$ ) $\times m$ 個の選択トランジスタ(すな

10

20

30

40

50

わち、 $(k \times m)$ 組の選択トランジスタ群 $T_{r_{SEL1}} \sim T_{r_{SELn}}$ が形成されている。

### 【0168】

上位半導体回路層21では、p型の単結晶シリコン(Si)基板40の表面領域に、所定パターンで素子分離絶縁膜41が形成されており、それによって図1のレイアウトとなるように、 $(k \times n) \times m$ 個の画素11用の素子領域がマトリックス状に並んで形成されている。それら素子領域の各々が一つの画素11に対応する。画素ブロック12の構成はすべて同一であるから、ここでは一つの画素ブロック12(i,j)について説明する。

### 【0169】

画素ブロック12(i,j)に対応する素子領域の内部には、n個のフォトダイオード $PD_1 \sim PD_n$ とn個のトランスマルチゲート $TG_1 \sim TG_n$ が形成されている。例えば、フォトダイオード $PD_1$ は、図8に示すように、p型基板40に形成された $n^+$ 形領域42から構成される(つまり、フォトダイオード $PD_1$ はp-n接合フォトダイオードである)。トランスマルチゲート $TG_1$ は、ゲート電極44と、このゲート電極44を挟んで $n^+$ 形領域42に対向している $n^+$ 形領域43とを含むMOSトランジスタによって形成されている。トランスマルチゲート $TG_1$ は、フォトダイオード $PD_1$ の $n^+$ 形領域42を共用しているため、トランスマルチゲート $TG_1$ の一方のソース・ドレイン領域が、フォトダイオード $PD_1$ のアノードと電気的に接続されることになる。ゲート電極44と基板40の表面の間に存在するゲート絶縁膜は、図8では省略している。(ゲート電極44と基板40の表面の間のゲート絶縁膜の存在は自明であるから、以下の説明においても、ゲート絶縁膜に関する説明は省略する。)ゲート電極44は、基板40の表面に形成された配線構造47中の配線を介して、対応する読出制御線32に電気的に接続されている。ここで、配線構造47には、基板40の表面に形成された配線用導電体とそれを包含する絶縁体とを含み、基板40の表面に存在するゲート絶縁膜とゲート電極を含まない。(これは、以下の実施形態でも同様である。)他のフォトダイオード $PD_2 \sim PD_n$ とトランスマルチゲート $TG_2 \sim TG_n$ は、それぞれ、フォトダイオード $PD_1$ とトランスマルチゲート $TG_1$ と同様の構成を持つ。

### 【0170】

配線構造47の内部には、所定パターンで形成された配線膜46と、その配線膜46に対してトランスマルチゲート $TG_1 \sim TG_n$ のn個の $n^+$ 形領域43を電気的に接続するn個の導電性コンタクトプラグ45とが形成されている。画素ブロック12(i,j)中のn個のトランスマルチゲート $TG_1 \sim TG_n$ は、それらコンタクトプラグ45によって、配線膜46にそれぞれ電気的に接続されているから、トランスマルチゲート $TG_1 \sim TG_n$ は共通ノード13に並列に接続されることになる。

### 【0171】

基板40には、トランスマルチゲート $TG_1 \sim TG_n$ の $n^+$ 形領域(ソース・ドレイン領域)43に隣接する素子分離絶縁膜41と重なる位置に、素子分離絶縁膜41と基板40を上下方向に(基板40の主面に直交する方向に)貫通する $(k \times m)$ 個の透孔が形成されている。この透孔の基板40のSi部分に接する部分の内壁の全面は、絶縁膜24で覆われている。この透孔の内部(絶縁膜24の内側と素子分離絶縁膜41の内部)には、ポリシリコン等の導電性材料が充填されており、その導電性材料が埋込配線23を形成する。この埋込配線23の上端は、基板40(素子分離絶縁膜41)の表面から露出しており、配線構造47の内部に形成された導電性コンタクトプラグ23aの下端に接続されている。この導電性コンタクトプラグ23aの上端は、配線構造47の内部に形成された配線膜46に接続されている。したがって、埋込配線23は、導電性コンタクトプラグ23aを介して対応する配線膜46に電気的に接続されている。その結果、画素ブロック12(i,j)のn個のトランスマルチゲート $TG_1 \sim TG_n$ の $n^+$ 形領域(ソース・ドレイン領域)43は、図6に示した回路構成のように、対応する埋込配線23に電気的に共通接続されていることになる。各埋込配線23の下端は、基板40の裏面から露出していて、その下端において対応するバンプ電極90に機械的・電気的に接続されている。

10

20

30

40

50

## 【0172】

下位半導体回路層22では、p型の単結晶Si基板60の表面領域に、所定パターンで素子分離絶縁膜61が形成されており、それによって所定数のリセットトランジスタTr<sub>RST</sub>用の素子領域と、所定数の増幅トランジスタTr<sub>AMP</sub>用の素子領域と、所定数の選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>用の素子領域が形成されている。ここでは一つの画素ブロック12(i,j)に対応する構成について説明する。

## 【0173】

図8に示すように、リセットトランジスタTr<sub>RST</sub>は、ゲート電極63と、このゲート電極63を挟んで両側に形成された一対のn<sup>+</sup>形領域(ソース・ドレイン領域)62とを含むMOSトランジスタから構成されている。ゲート電極63は、基板60の表面に形成された配線構造74中の配線を介して、対応するリセット線31に電気的に接続されている。ここで、配線構造74は、基板60の表面に形成された配線用導電体とそれを包含する絶縁体とを含み、基板60の表面に存在するゲート絶縁膜とゲート電極を含まない(これは、以下の実施形態でも同様である)。一方のn<sup>+</sup>形領域62(ソース・ドレイン領域)は、配線構造74の内部に形成された導電性コンタクトプラグ68と配線膜72と導電性コンタクトプラグ74aと配線膜75を介して、対応するバンプ電極90に電気的に接続されている。その結果、リセットトランジスタTr<sub>RST</sub>の一方のソース・ドレイン領域は、対応する埋込配線23を介して、上位半導体回路層21の対応する共通ノード13(画素ブロック12(i,j))に電気的に接続されることになる(図6参照)。他方のn<sup>+</sup>形領域62(ソース・ドレイン領域)には、図示しない配線を介してリセット電圧V<sub>RST</sub>が印加される。

## 【0174】

増幅トランジスタTr<sub>AMP</sub>は、ゲート電極65と、このゲート電極65を挟んで両側に形成された一対のn<sup>+</sup>形領域(ソース・ドレイン領域)64とを含むMOSトランジスタから構成されている。ゲート電極65は、配線構造74の内部に形成された導電性コンタクトプラグ71と配線膜72と導電性コンタクトプラグ74aと配線膜75を介して、対応するバンプ電極90に電気的に接続されている。その結果、増幅トランジスタTr<sub>AMP</sub>のゲート電極は、対応する埋込配線23を介して、上位半導体回路層21の対応する共通ノード13(画素ブロック12(i,j))に電気的に接続されることになる(図6参照)。また、一方のn<sup>+</sup>形領域64(ソース・ドレイン領域)は、配線構造74の内部に形成された導電性コンタクトプラグ69を介して、配線構造74の内部に形成された配線膜73に電気的に接続されている。他方のn<sup>+</sup>形領域64(ソース・ドレイン領域)には、図示しない配線を介して電源電圧V<sub>CC</sub>が印加される。

## 【0175】

n個の選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>の各々は、ゲート電極67と、このゲート電極67を挟んで両側に形成された一対のn<sup>+</sup>形領域(ソース・ドレイン領域)66とを含むMOSトランジスタから構成されている。一方のn<sup>+</sup>形領域(ソース・ドレイン領域)66は、配線構造74の内部に形成された導電性コンタクトプラグ70と配線膜73と導電性コンタクトプラグ69を介して、対応する増幅トランジスタTr<sub>AMP</sub>の一方のn<sup>+</sup>形領域(ソース・ドレイン領域)64に電気的に接続されている。他方のn<sup>+</sup>形領域(ソース・ドレイン領域)66は、当該イメージセンサ2の対応する出力端子に接続されている。ゲート電極67は、配線構造74の内部に形成された配線を介して、出力選択線39に電気的に接続されている。選択トランジスタTr<sub>SEL1</sub>～Tr<sub>SELn</sub>のゲート電極67には、対応する出力選択線39を介して所定の出力選択信号SEL1～SELnがそれぞれ印加される。

## 【0176】

第5実施形態に係るイメージセンサ2では、図8に示すように、隣接する二つの選択トランジスタ、例えばTr<sub>SEL1</sub>とTr<sub>SEL2</sub>は、同じ素子領域中に形成されている。これは占有面積をできるだけ小さくするためである。当該素子領域の中には三つのn<sup>+</sup>形領域(ソース・ドレイン領域)66が所定距離をあけて並列して形成されており、中央の

$n^+$  形領域 66 を二つの選択トランジスタ  $T_{r_{SEL1}}$  と  $T_{r_{SEL2}}$  とで共用している。そして、共用されている  $n^+$  形領域 66 を、対応する増幅トランジスタ  $T_{r_{AMP}}$  の一方の  $n^+$  形領域 64 に電気的に接続している。共用されていない  $n^+$  形領域 66 は、対応する出力端子にそれぞれ接続されている。

## 【0177】

上位半導体回路層 21 内の  $n^+$  形領域 43 と下位半導体回路層 22 内の  $n^+$  形領域 62 (これらは埋込配線 23 を介して電気的に相互接続されている) は、FD (浮遊拡散) 領域の機能、すなわち光電変換によりフォトダイオード  $PD_1 \sim PD_n$  に蓄積された信号電荷量を電圧信号に変換する機能を有している。

## 【0178】

なお、上位半導体回路層 21 と下位半導体回路層 22 の内部構造を形成する方法は、当業界によく知られているから、それらに関する説明は省略する。

## 【0179】

以上述べたように、図 6 及び図 8 に示した第 5 実施形態に係るイメージセンサ 2 は、図 4 に示した第 3 実施形態のセンサ回路 1B を適用したものであって、(k × m) 個の画素ブロック 12 (それぞれのブロック 12 が n 個の画素 11 を含む) と (k × m) 個の埋込配線 23 を上位半導体回路層 21 中に形成すると共に、(k × m) 個のリセットトランジスタ  $T_{r_{RST}}$  と (k × m) 個の増幅トランジスタ  $T_{r_{AMP}}$  と (k × m) 組の選択トランジスタ群  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  を下位半導体回路層 22 中に形成し、さらに、埋込配線 23 及びバンプ電極 90 を介して、上位半導体回路層 21 中の画素ブロック 12 と、下位半導体回路層 22 中の対応するリセットトランジスタ  $T_{r_{RST}}$  及び増幅トランジスタ  $T_{r_{AMP}}$  とを電気的に相互接続している。

## 【0180】

また、下位半導体回路層 22 の上方の正面 (配線構造 74 の表面) は、バンプ電極 90 と接着剤 91 によって、上位半導体回路層 21 の下方の正面 (基板 40 の裏面) に電気的・機械的に接続されているので、両回路層 21 と 22 は二段の半導体積層構造 (三次元構造) を構成する。

## 【0181】

したがって、上述した第 3 実施形態のセンサ回路 1B について説明したのと同じ理由により、全画素 11 についての信号電荷の実質的同時蓄積 (実質的同時シャッタ化) が可能であると共に、従来の CMOS イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

## 【0182】

また、画素ブロック 12 の各画素 11 は一つのフォトダイオードと一つのゲート素子 (MOS トランジスタ) を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つの MOS トランジスタを含む従来の CMOS イメージセンサに比べて、高い画素開口率 (例えば、60% 程度) を実現することができ、しかも画素 11 自体の大きさを縮小することができる。

## 【0183】

さらに、従来の CMOS イメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層 21 の表面にある撮像領域の総面積に対する受光領域 (各フォトダイオードの開口部分) の総面積の割合を高くすることが可能となる。

## 【0184】

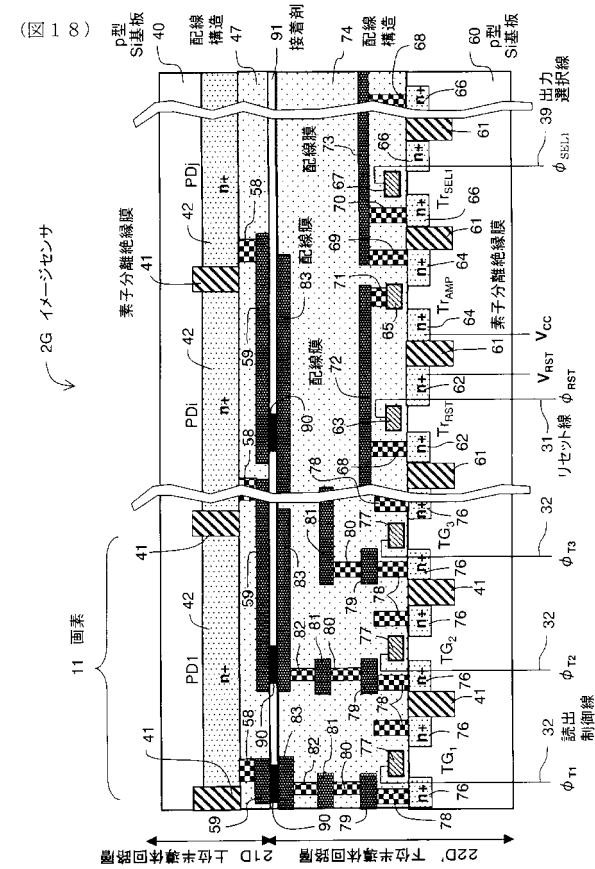

## (第 6 実施形態)

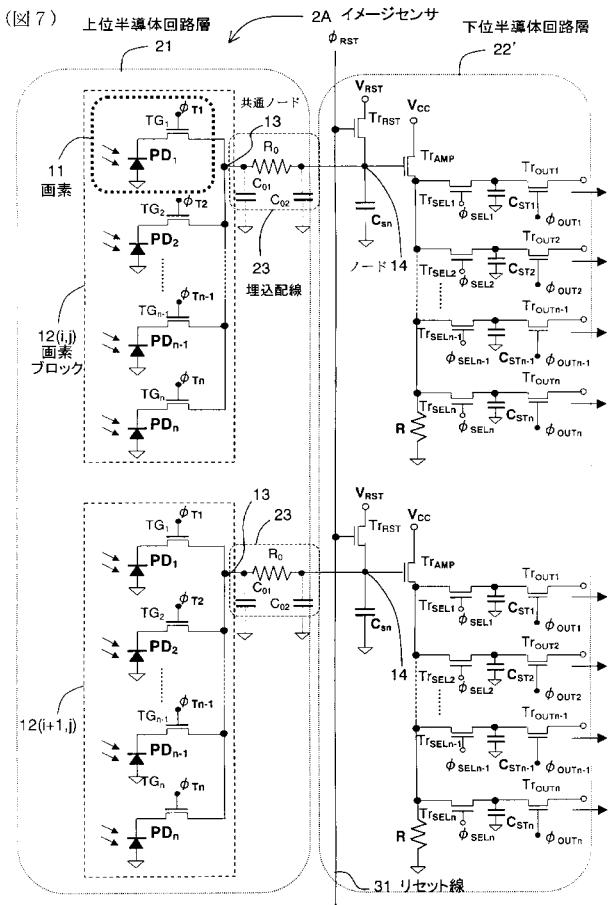

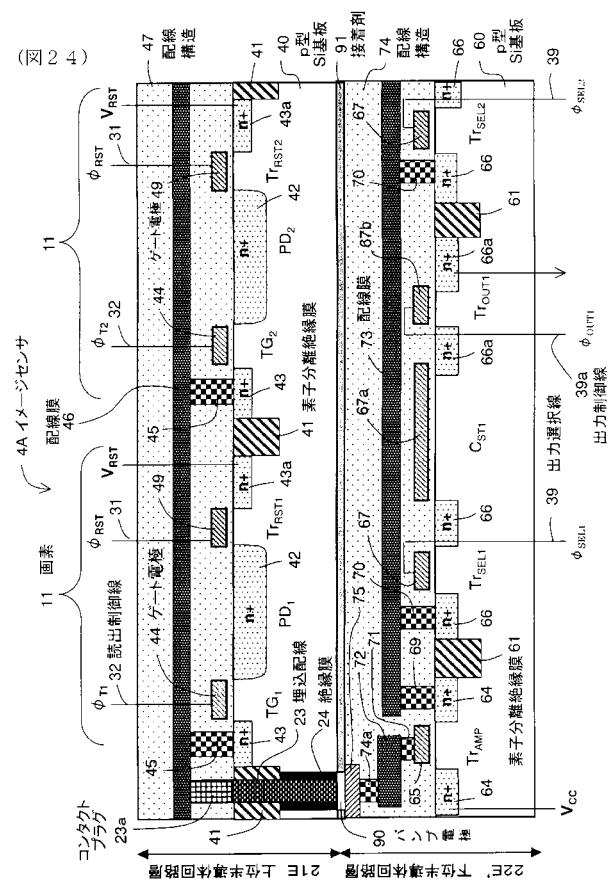

図 7 は、本発明の第 6 実施形態に係るアドレス指定型イメージセンサ 2A の要部の回路構成を示す回路図であり、図 9 は、同イメージセンサ 2A の実際構造を示す要部断面図である。このイメージセンサ 2A は、上述した第 4 実施形態のセンサ回路 1C (図 5 参照) を使用したものであり、上位半導体回路層 21 と下位半導体回路層 22' を積層して二段の三次元積層構造とされている。このイメージセンサ 2A は、本発明の第 3 の観点によるイメージセンサに対応する。

10

20

30

40

50

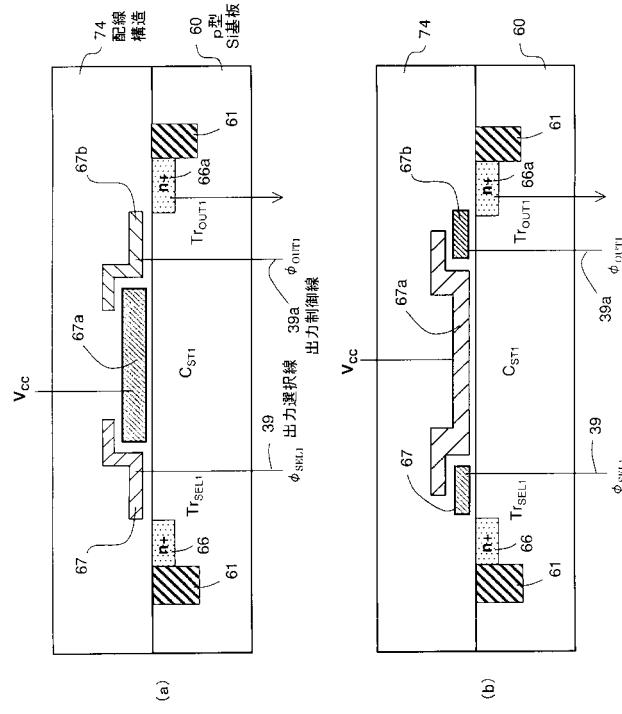

## 【0185】

このイメージセンサ2Aの全体構成及び動作は、図1に示したものと同じである。よって、それらに関する説明は省略する。また、図7に示された回路構成は、図5の第4実施形態のセンサ回路1C（各増幅トランジスタTr<sub>AMP</sub>の出力端にn個の選択トランジスタTr<sub>SEL</sub><sub>1</sub>～Tr<sub>SEL</sub><sub>n</sub>が接続されており、それら選択トランジスタTr<sub>SEL</sub><sub>1</sub>～Tr<sub>SEL</sub><sub>n</sub>の出力側にそれぞれ記憶用容量素子C<sub>ST</sub><sub>1</sub>～C<sub>ST</sub><sub>n</sub>と出力トランジスタTr<sub>OUT</sub><sub>1</sub>～Tr<sub>OUT</sub><sub>n</sub>とが接続されたもの）と同じであるから、同一の要素に同一の符号を付してその説明は省略する。ただし、イメージセンサ2Aでは、後述するように、上位半導体回路層21中に形成された各画素ブロック12の共通ノード13と、下位半導体回路層22'中に形成されたリセットトランジスタTr<sub>RST</sub>及び増幅トランジスタTr<sub>AMP</sub>の接続点であるノード14とを電気的に接続するために、公知の埋込配線23を使用していることから、埋込配線23と、当該埋込配線23によって生じる寄生抵抗R<sub>0</sub>と寄生容量C<sub>0</sub><sub>1</sub>及びC<sub>0</sub><sub>2</sub>が図7に追加されている。埋込配線23は、各画素ブロック12（つまり、n個の画素11）に対して一つ設けられている。

10

## 【0186】

次に、図9を参照しながら、イメージセンサ2Aの実際構造について説明する。

## 【0187】

イメージセンサ2Aは、図9から明らかなように、上位半導体回路層21と下位半導体回路層22'を、埋込配線23と微細なバンプ電極90と、電気的絶縁性の接着剤（例えばポリイミド）91とを用いて、機械的且つ電気的に接続して構成されている。

20

## 【0188】

上位半導体回路層21は、上述した第5実施形態のイメージセンサ2（図8参照）のそれと同じ構成であり、（k×m）個の画素ブロック12つまり（k×n）×m個の画素11と、（k×m）個の埋込配線23が形成されている。上位半導体回路層21の内部構成は、上述した第5実施形態のイメージセンサ2のそれと同じであるから、第5実施形態の場合と同じ符号を付してその詳細な説明は省略する。

## 【0189】

下位半導体回路層22'は、上述した第5実施形態のイメージセンサ2（図8参照）の下位半導体回路層22とほぼ同じ構成であるが、記憶用容量素子C<sub>ST</sub><sub>1</sub>～C<sub>ST</sub><sub>n</sub>と出力トランジスタTr<sub>OUT</sub><sub>1</sub>～Tr<sub>OUT</sub><sub>n</sub>が追加形成されている点が異なっている。すなわち、下位半導体回路層22'には、（k×m）個のリセットトランジスタTr<sub>RST</sub>と、（k×m）個の増幅トランジスタTr<sub>AMP</sub>と、（k×m）組の選択トランジスタ群Tr<sub>SEL</sub><sub>1</sub>～Tr<sub>SEL</sub><sub>n</sub>に加えて、（k×m）組の記憶用容量素子群C<sub>ST</sub><sub>1</sub>～C<sub>ST</sub><sub>n</sub>と、（k×m）組の出力トランジスタ群Tr<sub>OUT</sub><sub>1</sub>～Tr<sub>OUT</sub><sub>n</sub>が追加形成されている。

30

## 【0190】

図9に示すように、下位半導体回路層22'では、p型の単結晶Si基板60の表面領域に、所定パターンで素子分離絶縁膜61が形成されており、それによって所定数のリセットトランジスタTr<sub>RST</sub>用の素子領域と、所定数の増幅トランジスタTr<sub>AMP</sub>用の素子領域と、所定数の選択トランジスタTr<sub>SEL</sub><sub>1</sub>～Tr<sub>SEL</sub><sub>n</sub>、記憶用容量素子C<sub>ST</sub><sub>1</sub>～C<sub>ST</sub><sub>n</sub>及び出力トランジスタTr<sub>OUT</sub><sub>1</sub>～Tr<sub>OUT</sub><sub>n</sub>用の素子領域が形成されている。ここでは一つの画素ブロック12（i,j）に対応する構成について説明する。

40

## 【0191】

リセットトランジスタTr<sub>RST</sub>の構成は、上述した第5実施形態のイメージセンサ2（図8参照）の場合と同様であり、ゲート電極63と、このゲート電極63を挟んで両側に形成された一対のn<sup>+</sup>形領域（ソース・ドレイン領域）62とを含むMOSトランジスタから構成されている。リセットトランジスタTr<sub>RST</sub>の電気的接続も、第5実施形態のイメージセンサ2（図8参照）の場合と同様である。

## 【0192】

50

増幅トランジスタ  $T_{r_{AMP}}$  の構成は、上述した第5実施形態のイメージセンサ2（図8参照）の場合と同様であり、ゲート電極65と、このゲート電極65を挟んで両側に形成された一対の $n^+$ 形領域（ソース・ドレイン領域）64とを含むMOSトランジスタから構成されている。増幅トランジスタ  $T_{r_{AMP}}$  の電気的接続も、第5実施形態のイメージセンサ2（図8参照）の場合と同様である。

【0193】

$n$ 個の選択トランジスタ  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  の各々の構成は、上述した第5実施形態のイメージセンサ2（図8参照）の場合と同様であり、ゲート電極67と、このゲート電極67を挟んで両側に形成された一対の $n^+$ 形領域（ソース・ドレイン領域）66とを含むMOSトランジスタから構成されている。そして、そのMOSトランジスタに対して、記憶用容量素子と出力トランジスタとが、図7に示すような回路構成となるように接続されている。10

【0194】

例えば、選択トランジスタ  $T_{r_{SEL1}}$  について言えば、一方の $n^+$ 形領域（ソース・ドレイン領域）66は、配線構造74の内部に形成された導電性コンタクトプラグ70及び69と配線膜73を介して、対応する増幅トランジスタ  $T_{r_{AMP}}$  の一方の $n^+$ 形領域（ソース・ドレイン領域）64に電気的に接続されている。ゲート電極67は、配線構造74の内部に形成された配線を介して出力選択線39に電気的に接続されており、出力選択信号  $S_{EL1}$  が印加される。選択トランジスタ  $T_{r_{SEL1}}$  の他方の $n^+$ 形領域（ソース・ドレイン領域）66は、ゲート電極67aに関してそれとは反対側に形成された $n^+$ 形領域66aと共に、記憶用容量素子  $C_{ST1}$  として機能するMOSキャパシタを構成している。この $n^+$ 形領域66aは、ゲート電極67bと、そのゲート電極67bに関して当該 $n^+$ 形領域66aとは反対側に形成された $n^+$ 形領域66aと共に、出力トランジスタ  $T_{r_{OUT1}}$  として機能するMOSトランジスタを構成している。ゲート電極67aは、所定電位（通常は電源電圧  $V_{CC}$ ）の端子または領域に接続される。ゲート電極67bは、図示しない配線を介して出力制御線39aに電気的に接続されており、出力制御信号  $OUT1$  が印加される。20

【0195】

このように、一つの素子領域内に、選択トランジスタ  $T_{r_{SEL1}}$  と記憶用容量素子  $C_{ST1}$  と出力トランジスタ  $T_{r_{OUT1}}$  が形成されている。これは、他の選択トランジスタ  $T_{r_{SEL2}} \sim T_{r_{SELn}}$  についても同様である。30

【0196】

以上述べたように、図7及び図9に示した第6実施形態に係るイメージセンサ2は、図5に示したセンサ回路1Cを適用したものであって、 $(k \times m)$ 個の画素ブロック12（それが $n$ 個の画素11を含む）と $(k \times m)$ 組のトランスマニアゲート群  $TG_1 \sim TG_n$  ）と $(k \times m)$ 個の埋込配線23を上位半導体回路層21中に形成すると共に、 $(k \times m)$ 個のリセットトランジスタ  $T_{r_{RST}}$  と $(k \times m)$ 個の増幅トランジスタ  $T_{r_{AMP}}$  と $(k \times m)$ 組の選択トランジスタ群  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  と $(k \times m)$ 組の記憶用容量素子群  $C_{ST1} \sim C_{STn}$  と $(k \times m)$ 組の出力トランジスタ群  $T_{r_{OUT1}} \sim T_{r_{OUTn}}$  を下位半導体回路層22中に形成し、さらに、埋込配線23及びバンプ電極90を介して、上位半導体回路層21中の画素ブロック12と、下位半導体回路層22中のリセットトランジスタ  $T_{r_{RST}}$  及び増幅トランジスタ  $T_{r_{AMP}}$  とを電気的に相互接続している。40

【0197】

また、下位半導体回路層22の上方の主面（配線構造74の表面）は、バンプ電極90と接着剤91によって、上位半導体回路層21の下方の主面（基板40の裏面）に電気的・機械的に接続されているので、両回路層21と22は二段の半導体積層構造（三次元構造）を構成する。

【0198】

したがって、第4実施形態のセンサ回路1C（図5を参照）について説明したのと同じ50

理由により、全画素 11 についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来の CMOS イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

#### 【0199】

また、画素ブロック 12 の各画素 11 は一つのフォトダイオードと一つのゲート素子（MOS トランジスタ）を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つの MOS トランジスタを含む従来の CMOS イメージセンサに比べて、高い画素開口率（例えば、60% 程度）を実現することができ、しかも画素 11 自体の大きさを縮小することが可能となる。

#### 【0200】

さらに、従来の CMOS イメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層 21 の表面にある撮像領域の総面積に対する受光領域（各フォトダイオードの開口部分）の総面積の割合を高くすることが可能となる。

#### 【0201】

さらに、出力制御信号  $o_{U T 1} \sim o_{U T n}$  で出力トランジスタ  $T r_{o U T 1} \sim T r_{o U T n}$  を制御することにより、画素ブロック 12 中のトランスマルチプレクタ  $T G_1 \sim T G_n$  と選択トランジスタ群  $T r_{S E L 1} \sim T r_{S E L n}$  の開閉とはタイミングをずらして列信号線 37 に信号を出力することができるため、第 5 実施形態のイメージセンサ 2 よりも高速の撮像が可能であるという効果もある。

#### 【0202】

##### （第 7 実施形態）

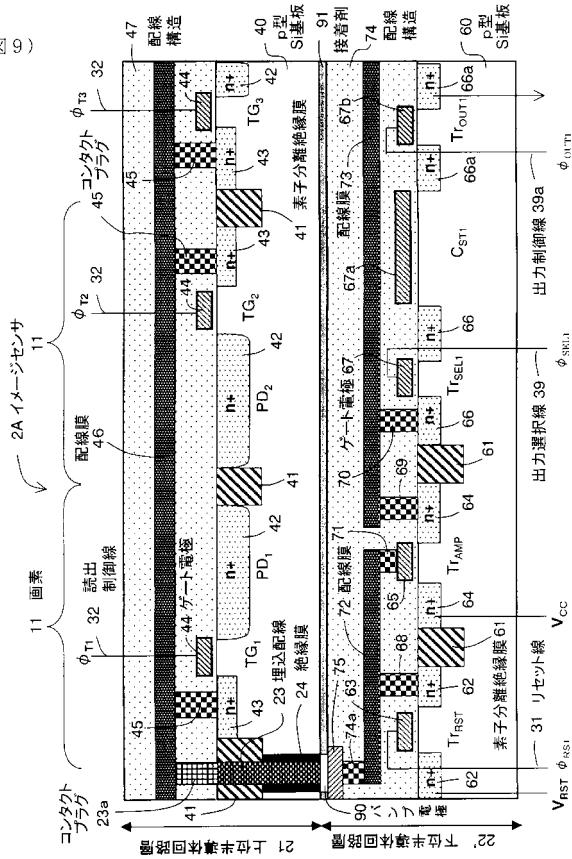

図 10 は、本発明の第 7 実施形態に係るアドレス指定型イメージセンサ 2B の要部の回路構成を示す回路図であり、図 11 は、イメージセンサ 2B の実際構造を示す要部断面図である。このイメージセンサ 2B は、上記第 4 実施形態のセンサ回路 1C（図 5 参照）を使用したものであり、上位半導体回路層 21A と下位半導体回路層 22A' を積層して二段の三次元積層構造とされている。イメージセンサ 2B は、本発明の第 3 の観点によるイメージセンサに対応する。

#### 【0203】

イメージセンサ 2B の全体構成及び動作は、図 1 に示したものと同じである。よって、それらに関する説明は省略する。また、図 10 に示された回路構成は、埋込配線 23 が追加されている点を除いて、図 5 の第 4 実施形態のセンサ回路 1C と同じであるから、同一の要素に同一の符号を付してその説明は省略する。

#### 【0204】

イメージセンサ 2B は、図 10 及び図 11 より明らかのように、上位半導体回路層 21A と下位半導体回路層 22A' とを、埋込配線 23 と微細なバンプ電極 90 と電気的絶縁性の接着剤 91 を用いて機械的且つ電気的に接続して構成されている。その構成は、第 6 実施形態のイメージセンサ 2A（図 7 及び図 9 参照）で下位半導体回路層 22' 中に形成されていた  $(k \times m)$  個のリセットトランジスタ  $T r_{R S T}$  を上位半導体回路層 21 中に移したものに相当する。すなわち、上位半導体回路層 21A には、 $(k \times n) \times m$  個のフォトダイオード（すなわち、 $(k \times m)$  組のフォトダイオード群  $P D_1 \sim P D_n$ ）と、 $(k \times n) \times m$  個のトランスマルチプレクタ（すなわち、 $(k \times m)$  組のトランスマルチプレクタ群  $T G_1 \sim T G_n$ ）と、 $(k \times m)$  個のリセットトランジスタ  $T r_{R S T}$  と、 $(k \times m)$  個の埋込配線 23 が形成されている。フォトダイオード  $P D_1 \sim P D_n$  とトランスマルチプレクタ  $T G_1 \sim T G_n$  の構成は、第 6 実施形態のイメージセンサ 2A の場合と同じであるので、それらに関する説明は省略する。

#### 【0205】

リセットトランジスタ  $T r_{R S T}$  は、図 11 に示すように、ゲート電極 49 と、このゲート電極 49 を挟んで両側に形成された一対の  $n^+$  形領域（ソース・ドレイン領域）48 とを含む MOS トランジスタから構成されている。ゲート電極 49 は、基板 40 の表面に形成された配線構造 47 中の配線を介して、対応するリセット線 31 に電気的に接続され

10

20

30

40

50

ている。一方の  $n^+$  形領域 48 (ソース・ドレイン領域) は、配線構造 47 の内部に形成された導電性コンタクトプラグ 50 と配線膜 46 と導電性コンタクトプラグ 23a と埋込配線 23 を介して、対応するバンプ電極 90 に電気的に接続されている。その結果、リセットトランジスタ  $T_{RST}$  の当該ソース・ドレイン領域は、下位半導体回路層 22A' の対応する増幅トランジスタ  $T_{AMP}$  のゲート電極 65 に電気的に接続されることになる。リセットトランジスタ  $T_{RST}$  の他方の  $n^+$  形領域 48 (ソース・ドレイン領域) には、図示しない配線を介してリセット電圧  $V_{RST}$  が印加される。

#### 【0206】

下位半導体回路層 22A' には、 $(k \times m)$  個の増幅トランジスタ  $T_{AMP}$  と、 $(k \times m)$  組の選択トランジスタ群  $T_{SEL1} \sim T_{SELn}$  と、 $(k \times m)$  組の記憶用容量素子群  $C_{ST1} \sim C_{STn}$  と、 $(k \times m)$  組の出力トランジスタ群  $T_{ROUT1} \sim T_{ROUTn}$  が形成されている。この構成は、第 6 実施形態 (図 7 及び図 9 参照) の下位半導体回路層 22' から  $(k \times m)$  個のリセットトランジスタ  $T_{RST}$  を除去した構成に相当する。増幅トランジスタ  $T_{AMP}$  と選択トランジスタ  $T_{SEL1} \sim T_{SELn}$  の構成は、第 6 実施形態の場合と同一であるから、それらに関する説明は省略する。

#### 【0207】

以上述べたように、図 10 及び図 11 に示した第 7 実施形態に係るイメージセンサ 2B は、第 4 実施形態のセンサ回路 1C (図 5 参照) を適用したものであって、 $(k \times m)$  個の画素ブロック 12 (それぞれのブロック 12 が  $n$  個の画素 11 を含む) と  $(k \times m)$  組のトランスマルチплексор群  $TG_1 \sim TG_n$  と  $(k \times m)$  個のリセットトランジスタ  $T_{RST}$  と  $(k \times m)$  個の埋込配線 23 を上位半導体回路層 21A 中に形成すると共に、 $(k \times m)$  個の増幅トランジスタ  $T_{AMP}$  と  $(k \times m)$  組の選択トランジスタ群  $T_{SEL1} \sim T_{SELn}$  と  $(k \times m)$  組の記憶用容量素子群  $C_{ST1} \sim C_{STn}$  と  $(k \times m)$  組の出力トランジスタ群  $T_{ROUT1} \sim T_{ROUTn}$  を下位半導体回路層 22A' 中に形成し、さらに、埋込配線 23 及びバンプ電極 90 を介して、上位半導体回路層 21 中のリセットトランジスタ  $T_{RST}$  と、下位半導体回路層 22A' 中の増幅トランジスタ  $T_{AMP}$  を電気的に相互接続している。

#### 【0208】

また、下位半導体回路層 22A' の上方の正面 (配線構造 74 の表面) は、バンプ電極 90 と接着剤 91 によって、上位半導体回路層 21A の下方の正面 (基板 40 の裏面) に電気的・機械的に接続されているので、両回路層 21A と 22A' は二段の半導体積層構造 (三次元構造) を構成する。

#### 【0209】

したがって、第 4 実施形態のセンサ回路 1C について説明したのと同じ理由により、全画素 11 についての信号電荷の実質的同時蓄積 (実質的同時シャッタ化) が可能であると共に、従来の CMOS イメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

#### 【0210】

また、画素ブロック 12 の各画素 11 は一つのフォトダイオードと一つのゲート素子 (MOS トランジスタ) を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つの MOS トランジスタを含む従来の CMOS イメージセンサに比べて、高い画素開口率 (例えば、60% 程度) を実現することができ、しかも画素 11 自体の大きさを縮小することができる。

#### 【0211】

さらに、従来の CMOS イメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層 21A の表面にある撮像領域の総面積に対する受光領域 (各フォトダイオードの開口部分) の総面積の割合を高くすることが可能となる。

#### 【0212】

さらに、出力制御信号  $ROUT1 \sim ROUTn$  で出力トランジスタ  $T_{ROUT1} \sim T_{ROUTn}$  を制御することにより、画素ブロック 12 中のトランスマルチплексор  $TG_1 \sim TG_n$

10

20

30

40

50

$n$  と選択トランジスタ群  $T r_{S E L 1} \sim T r_{S E L n}$  の開閉とはタイミングをずらして列信号線 37 に信号を出力することができるため、記憶用容量素子  $C_{S T 1} \sim C_{S T n}$  と出力トランジスタ  $T r_{O U T 1} \sim T r_{O U T n}$  を有しない場合よりも高速の撮像が可能であるという効果もある。

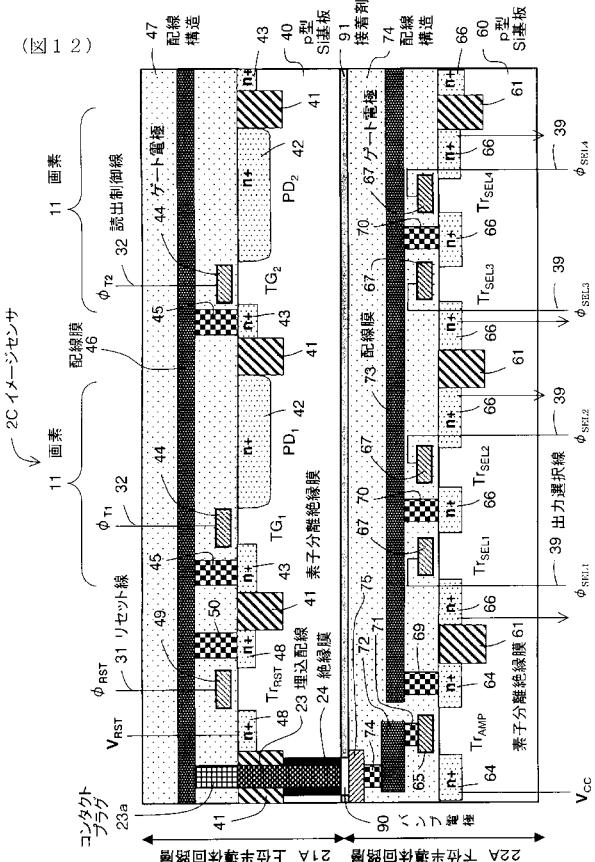

【0213】

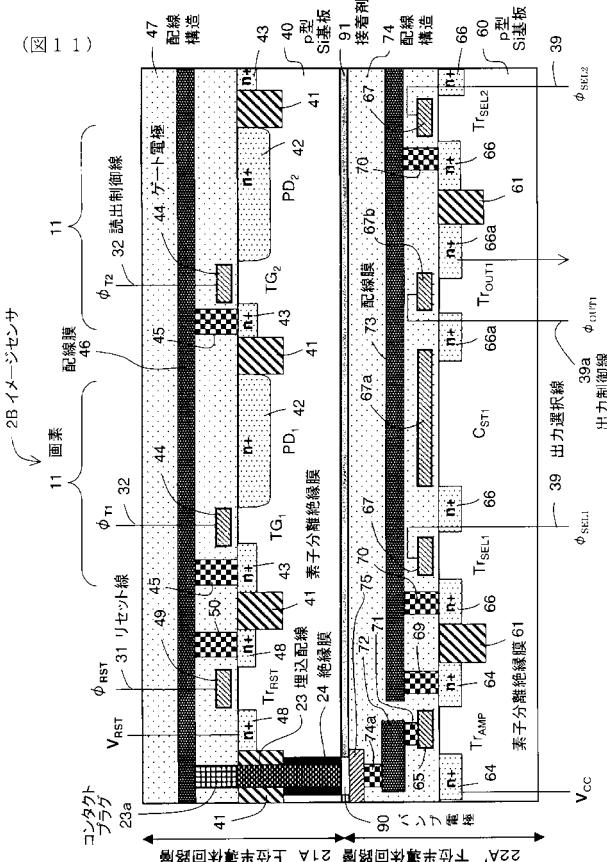

(第8実施形態)

図12は、本発明の第8実施形態に係るアドレス指定型イメージセンサ2Cの実際構造を示す要部断面図である。このイメージセンサ2Cは、上述した第7実施形態のイメージセンサ2B(図10及び図11参照)において、記憶用容量素子  $C_{S T 1} \sim C_{S T n}$  と出力トランジスタ  $T r_{O U T 1} \sim T r_{O U T n}$  を削除したものに相当する。このイメージセンサ2Cは、本発明の第3の観点によるアドレス指定型イメージセンサに対応する。

【0214】

第8実施形態のイメージセンサ2Cは、図12から明らかなように、上位半導体回路層21Aと下位半導体回路層22Aとを、埋込配線23と微細なバンプ電極90と電気的絶縁性の接着剤91を用いて機械的且つ電気的に接続して構成されている。上位半導体回路層21Aの構成は、第7実施形態のイメージセンサ2Bのそれと同じである。下位半導体回路層22Aの構成は、第7実施形態のイメージセンサ2Bの下位半導体回路層22A'から記憶用容量素子  $C_{S T 1} \sim C_{S T n}$  と出力トランジスタ  $T r_{O U T 1} \sim T r_{O U T n}$  を削除した構成に等しい。

【0215】

以上述べたように、第8実施形態に係るイメージセンサ2Cでは、第7実施形態のイメージセンサ2Bで述べたのと同様の理由により、全画素11についての信号電荷の実質的同時蓄積(実質的同时シャッタ化)が可能であると共に、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

【0216】

また、画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子(MOSトランジスタ)を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率(例えば、60%程度)を実現することができ、しかも画素11自体の大きさを縮小することが可能となる。

【0217】

さらに、従来のCMOSイメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層21Aの表面にある撮像領域の総面積に対する受光領域(各フォトダイオードの開口部分)の総面積の割合を高くすることが可能となる。

【0218】

(第9実施形態)

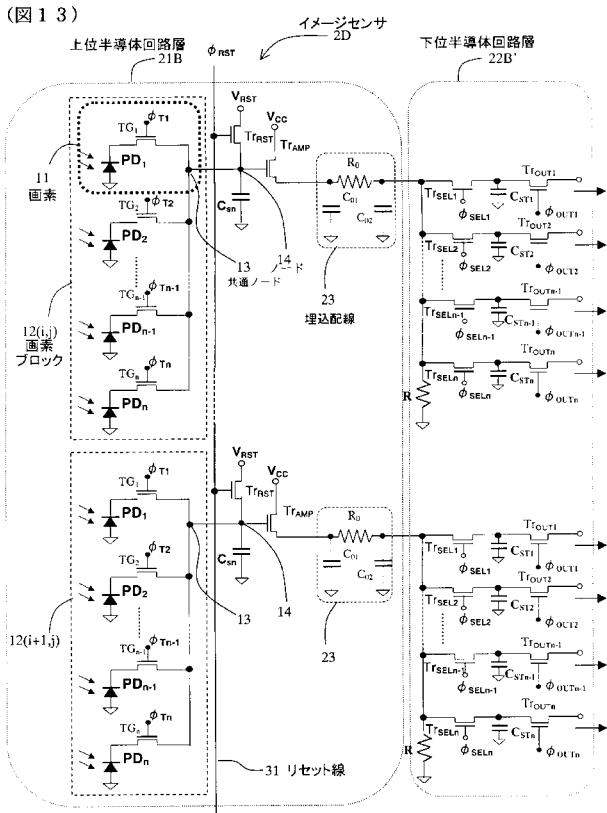

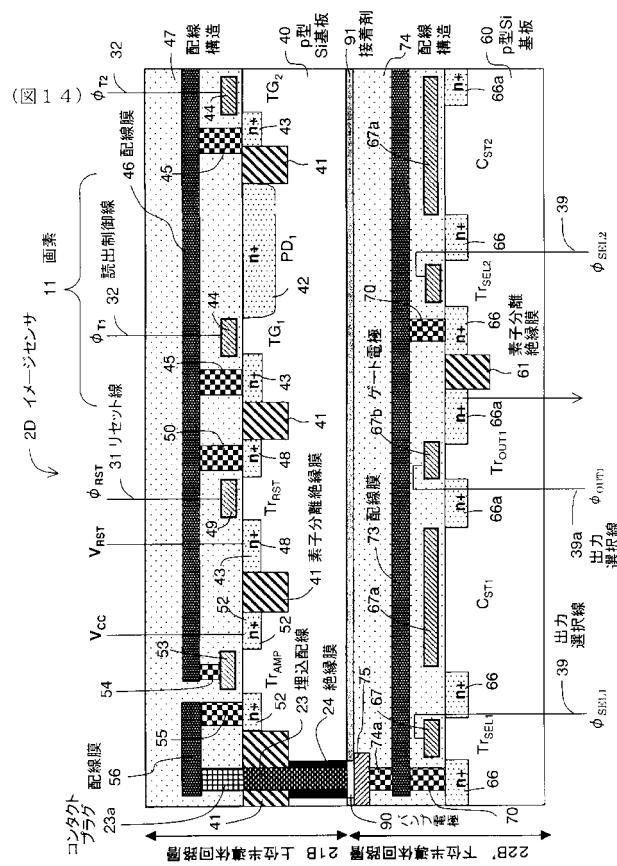

図13は、本発明の第9実施形態に係るアドレス指定型イメージセンサ2Dの要部の回路構成を示す回路図であり、図14は、イメージセンサ2Dの実際構造を示す要部断面図である。このイメージセンサ2Dは、上記第4実施形態のセンサ回路1C(図5参照)を使用したものであり、上位半導体回路層21Bと下位半導体回路層22B'を積層して二段の三次元積層構造とされている。イメージセンサ2Bは、本発明の第3の観点によるイメージセンサに対応する。

【0219】

イメージセンサ2Dの全体構成及び動作は、図1に示したものと同じであり、また、図13に示された回路構成は、埋込配線23が追加されている点を除いて、図5の第4実施形態のセンサ回路1Cと同じである。

【0220】

イメージセンサ2Dは、図13及び図14より明らかなように、上位半導体回路層21Bと下位半導体回路層22B'とを、埋込配線23と微細なバンプ電極90と電気的絶縁性の接着剤91を用いて機械的且つ電気的に接続して構成されている。その構成は、第7

10

20

30

40

50

実施形態のイメージセンサ 2 B (図 10 及び図 11 参照) で下位半導体回路層 22 A' 中に形成されていた ( $k \times m$ ) 個の増幅トランジスタ  $T_{r_{AMP}}$  を、その上位半導体回路層 21 A 中に移したものに相当する。

#### 【0221】

すなわち、上位半導体回路層 21 B には、( $k \times n$ )  $\times m$  個のフォトダイオード (すなわち、( $k \times m$ ) 組のフォトダイオード群  $PD_1 \sim PD_n$ ) と、( $k \times n$ )  $\times m$  個のトランスマニアゲート (すなわち、( $k \times m$ ) 組のトランスマニアゲート群  $TG_1 \sim TG_n$ ) と、( $k \times m$ ) 個のリセットトランジスタ  $T_{r_{RST}}$  と、( $k \times m$ ) 個の増幅トランジスタ  $T_{r_{AMP}}$  と、( $k \times m$ ) 個の埋込配線 23 が形成されている。フォトダイオード  $PD_1 \sim PD_n$  とトランスマニアゲート  $TG_1 \sim TG_n$  とリセットトランジスタ  $T_{r_{RST}}$  と構成は 10 第 7 実施形態のイメージセンサ 2 B の場合と同じであるので、それらに関する説明は省略する。

#### 【0222】

増幅トランジスタ  $T_{r_{AMP}}$  は、図 14 に示すように、ゲート電極 53 と、このゲート電極 53 を挟んで両側に形成された一対の  $n^+$  形領域 (ソース・ドレイン領域) 52 とを含む MOS トランジスタから構成されている。ゲート電極 53 は、配線構造 47 の内部に形成された導電性コンタクトプラグ 54 と配線膜 46 を介して、リセットトランジスタ  $T_{r_{RST}}$  とトランスマニアゲート  $TG_1 \sim TG_n$  に電気的に接続されている。一方の  $n^+$  形領域 52 (ソース・ドレイン領域) は、配線構造 47 の内部に形成された導電性コンタクトプラグ 55 と配線膜 56 と導電性コンタクトプラグ 23a と埋込配線 23 を介して、対応するバンプ電極 90 に電気的に接続されている。その結果、増幅トランジスタ  $T_{r_{AMP}}$  の当該ソース・ドレイン領域は、下位半導体回路層 22 B' の対応する選択トランジスタ  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  の一方の  $n^+$  形領域 66 (ソース・ドレイン領域) に電気的に接続されることになる。増幅トランジスタ  $T_{r_{AMP}}$  の他方の  $n^+$  形領域 52 (ソース・ドレイン領域) には、図示しない配線を介して電源電圧  $V_{cc}$  が印加される。 20

#### 【0223】

下位半導体回路層 22 B' には、( $k \times m$ ) 組の選択トランジスタ群  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  と、( $k \times m$ ) 組の記憶用容量素子群  $C_{ST1} \sim C_{STn}$  と、( $k \times m$ ) 組の出力トランジスタ群  $T_{ROUT1} \sim T_{ROUTn}$  が形成されている。この構成は、第 7 実施形態 (図 10 及び図 11 参照) の下位半導体回路層 22 A' から ( $k \times m$ ) 個の増幅トランジスタ  $T_{r_{AMP}}$  を除去した構成に相当する。選択トランジスタ  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  と記憶用容量素子  $C_{ST1} \sim C_{STn}$  と出力トランジスタ  $T_{ROUT1} \sim T_{ROUTn}$  の構成は、第 7 実施形態の場合と同一であるから、それらに関する説明は省略する。 30

#### 【0224】

以上述べたように、図 13 及び図 14 に示した第 9 実施形態に係るイメージセンサ 2 D は、第 4 実施形態のセンサ回路 1 C (図 5 参照) を適用したものであって、( $k \times m$ ) 個の画素ブロック 12 (それぞれのブロック 12 が  $n$  個の画素 11 を含む) と ( $k \times m$ ) 組のトランスマニアゲート群  $TG_1 \sim TG_n$  と ( $k \times m$ ) 個のリセットトランジスタ  $T_{r_{RST}}$  と ( $k \times m$ ) 個の増幅トランジスタ  $T_{r_{AMP}}$  と ( $k \times m$ ) 個の埋込配線 23 を上位半導体回路層 21 B 中に形成すると共に、( $k \times m$ ) 組の選択トランジスタ群  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  と ( $k \times m$ ) 組の記憶用容量素子群  $C_{ST1} \sim C_{STn}$  と ( $k \times m$ ) 組の出力トランジスタ群  $T_{ROUT1} \sim T_{ROUTn}$  を下位半導体回路層 22 B' 中に形成し、さらに、埋込配線 23 及びバンプ電極 90 を介して、上位半導体回路層 21 B 中の増幅トランジスタ  $T_{r_{AMP}}$  と、下位半導体回路層 22 B' 中の選択トランジスタ  $T_{r_{SEL1}} \sim T_{r_{SELn}}$  とを電気的に相互接続している。 40

#### 【0225】

また、下位半導体回路層 22 B' の上方の正面 (配線構造 74 の表面) は、バンプ電極 90 と接着剤 91 によって、上位半導体回路層 21 B の下方の正面 (基板 40 の裏面) に電気的・機械的に接続されているので、両回路層 21 B と 22 B' は二段の半導体積層構 50

造（三次元構造）を構成する。

【0226】

したがって、第4実施形態のセンサ回路1Cについて説明したのと同じ理由により、全画素11についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

【0227】

また、画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子（MOSトランジスタ）を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率（例えば、60%程度）を実現することができ、しかも画素11自体の大きさを縮小することが可能となる。

【0228】

さらに、従来のCMOSイメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層21Bの表面にある撮像領域の総面積に対する受光領域（各フォトダイオードの開口部分）の総面積の割合を高くすることが可能となる。

【0229】

さらに、出力制御信号 $o_{UT1} \sim o_{UTn}$ で出力トランジスタ $T_{ROUT1} \sim T_{ROUTn}$ を制御することにより、画素ブロック12中のトランスファゲート $TG_1 \sim TG_n$ と選択トランジスタ群 $T_{SEL1} \sim T_{SELn}$ の開閉とはタイミングをずらして列信号線37に信号を出力することができるため、記憶用容量素子 $C_{ST1} \sim C_{STn}$ と出力トランジスタ $T_{ROUT1} \sim T_{ROUTn}$ を有しない場合よりも高速の撮像が可能であるという効果もある。

【0230】

（第10実施形態）

図15は、本発明の第10実施形態に係るアドレス指定型イメージセンサ2Eの実際構造を示す要部断面図である。このイメージセンサ2Eは、上述した第9実施形態のイメージセンサ2C（図13及び図14参照）において、記憶用容量素子 $C_{ST1} \sim C_{STn}$ と出力トランジスタ $T_{ROUT1} \sim T_{ROUTn}$ を削除したものに相当する。このイメージセンサ2Eは、本発明の第3の観点によるアドレス指定型イメージセンサに対応する。

【0231】

第10実施形態のイメージセンサ2Eは、図15から明らかなように、上位半導体回路層21Bと下位半導体回路層22Bとを、埋込配線23と微細なバンプ電極90と電気的絶縁性の接着剤91を用いて機械的且つ電気的に接続して構成されている。上位半導体回路層21Bの構成は、第9実施形態のイメージセンサ2Dのそれと同じである。下位半導体回路層22Bの構成は、第9実施形態のイメージセンサ2Dの下位半導体回路層22B'から記憶用容量素子 $C_{ST1} \sim C_{STn}$ と出力トランジスタ $T_{ROUT1} \sim T_{ROUTn}$ を削除した構成に等しい。

【0232】

以上述べたように、第10実施形態に係るイメージセンサ2Eでは、第9実施形態のイメージセンサ2Dで述べたのと同様の理由により、全画素11についての信号電荷の実質的同時蓄積（実質的同時シャッタ化）が可能であると共に、従来のCMOSイメージセンサにおける画像の歪みを生じることなく、高速で移動する被写体を撮像することができる。

【0233】

また、画素ブロック12の各画素11は一つのフォトダイオードと一つのゲート素子（MOSトランジスタ）を含むだけで済むため、一つの画素中にフォトダイオードに加えて三つないし四つのMOSトランジスタを含む従来のCMOSイメージセンサに比べて、高い画素開口率（例えば、60%程度）を実現することができ、しかも画素11自体の大きさを縮小することが可能となる。

10

20

30

40

50

## 【0234】

さらに、従来のCMOSイメージセンサよりも高い画素開口率を実現できることから、上位半導体回路層21Bの表面にある撮像領域の総面積に対する受光領域（各フォトダイオードの開口部分）の総面積の割合を高くすることが可能となる。

## 【0235】

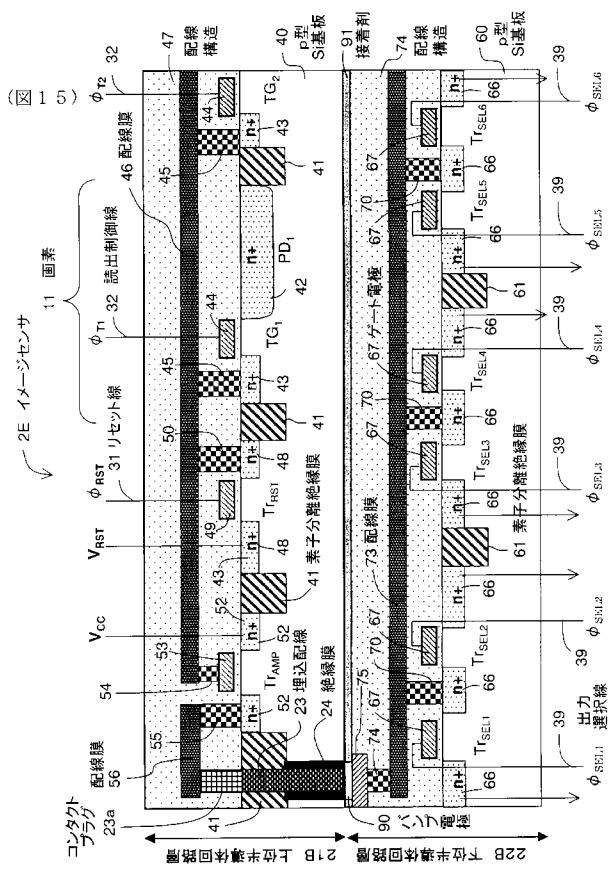

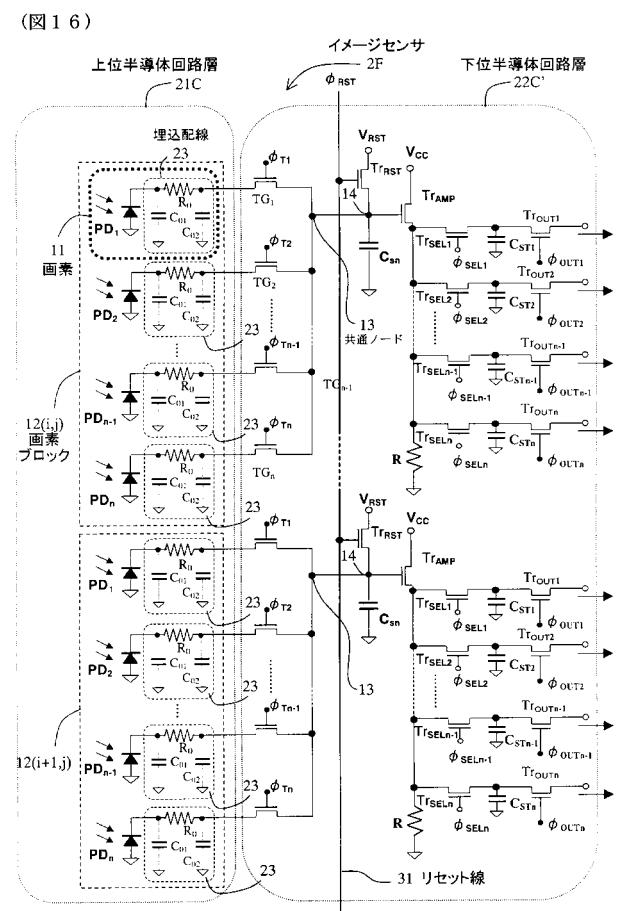

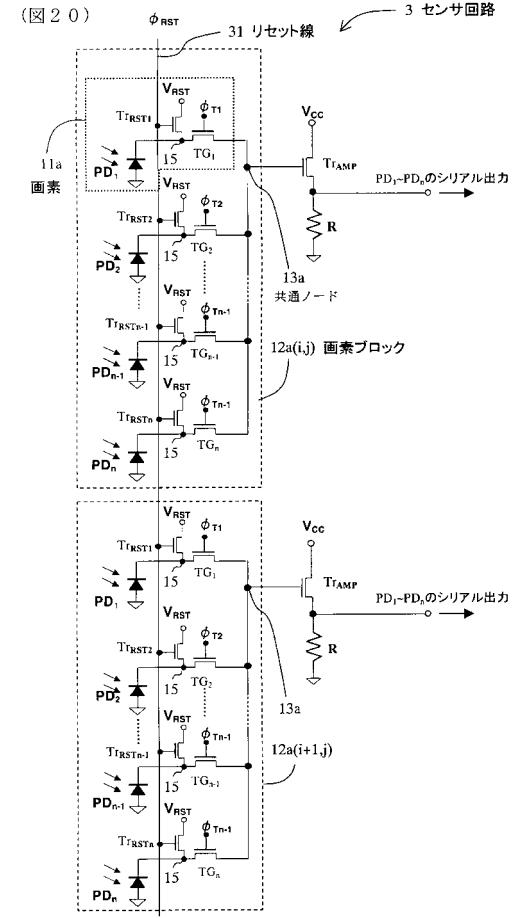

## (第11実施形態)

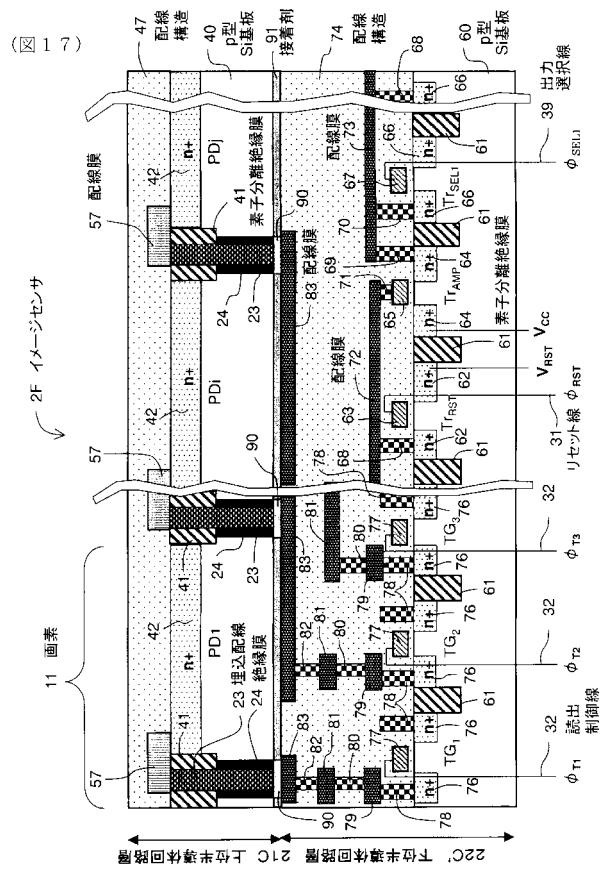

図16は、本発明の第11実施形態に係るアドレス指定型イメージセンサ2Fの要部の回路構成を示す回路図であり、図17は、イメージセンサ2Fの実際構造を示す要部断面図である。このイメージセンサ2Fは、上記第4実施形態のセンサ回路1C（図5参照）を使用したものであり、上位半導体回路層21Cと下位半導体回路層22C'を積層して二段の三次元積層構造とされている。イメージセンサ2Fは、本発明の第3の観点によるイメージセンサに対応する。

## 【0236】

イメージセンサ2Fの全体構成及び動作は、図1に示したものと同じであり、図16に示された回路構成は、埋込配線23が追加されている点を除いて、図5の第4実施形態のセンサ回路1Cと同じである。

## 【0237】

イメージセンサ2Fは、図16及び図17より明らかのように、上位半導体回路層21Cと下位半導体回路層22C'を、埋込配線23と微細なバンプ電極90と電気的絶縁性の接着剤91を用いて機械的且つ電気的に接続して構成されている。その構成は、第6実施形態に係るイメージセンサ2Aの（図7及び図9参照）で上位半導体回路層21中に形成されていた（k×m）組のトランスマジックゲート群TG<sub>1</sub>～TG<sub>n</sub>を、その下位半導体回路層22'中に移したものに相当する。したがって、上位半導体回路層21Cには、（k×n）×m個のフォトダイオード（すなわち、（k×m）組のフォトダイオード群PD<sub>1</sub>～PD<sub>n</sub>）と、（k×m）個の埋込配線23のみが形成されている。

## 【0238】

フォトダイオードPD<sub>1</sub>～PD<sub>n</sub>の構成は、第6実施形態のイメージセンサ2A（図7及び図9参照）の場合とほぼ同様であるが、基板40の各素子領域中に一つのフォトダイオードが形成されている点が異なる。例えば、フォトダイオードPD<sub>1</sub>について言えば、図17に示すように、素子分離絶縁膜41によってp型基板40の表面領域に形成された複数の素子領域の一つに、その全面にわたってn<sup>+</sup>領域42が形成されており、当該n<sup>+</sup>領域42がフォトダイオードPD<sub>1</sub>を形成する。基板40には、素子分離絶縁膜41と重なる適当な位置に、素子分離絶縁膜41と基板40を上下方向に（基板40の正面に直交する方向に）貫通する透孔が形成されており、この透孔の基板40に接する部分の内壁の全面は、絶縁膜24で覆われている。この透孔の内部（絶縁膜24の内側と素子分離絶縁膜41の内部）には、導電性材料が充填されており、その導電性材料が埋込配線23を形成する。この埋込配線23の上端は、基板40（素子分離絶縁膜41）の表面から露出しており、配線構造47の内部に形成された配線膜57の下面に接続されている。配線膜57の下面は、対応するn<sup>+</sup>領域42の表面にも接続されているから、n<sup>+</sup>領域42は埋込配線23に電気的に接続されていることになる。埋込配線23の下端は、基板40（素子分離絶縁膜41）の裏面から露出しており、対応するバンプ電極90に機械的・電気的に接続されている。

## 【0239】

下位半導体回路層22C'には、（k×m）組のトランスマジックゲート群TG<sub>1</sub>～TG<sub>n</sub>と、（k×m）個のリセットトランジスタTr<sub>RST</sub>と、（k×m）個の増幅トランジスタTr<sub>AMP</sub>と、（k×m）組の記憶用容量素子群C<sub>ST1</sub>～C<sub>STn</sub>と、（k×m）組の出力トランジスタ群Tr<sub>OUT1</sub>～Tr<sub>OUTn</sub>が形成されている。リセットトランジスタTr<sub>RST</sub>と増幅トランジスタTr<sub>AMP</sub>と記憶用容量素子C<sub>ST1</sub>～C<sub>STn</sub>と出力トランジスタTr<sub>OUT1</sub>～Tr<sub>OUTn</sub>は、第6実施形態に係るイメージセンサ2Aの場合（図7及び図9参照）と同じ構成を持つので、同一要素には同一符号を付してその

10

20

30

40

50

説明を省略する。なお、図17では、記憶用容量素子 $C_{S\ T_1} \sim C_{S\ T_n}$ と出力トランジスタ $T_{R\ O\ U\ T_1} \sim T_{R\ O\ U\ T_n}$ は省略されている。

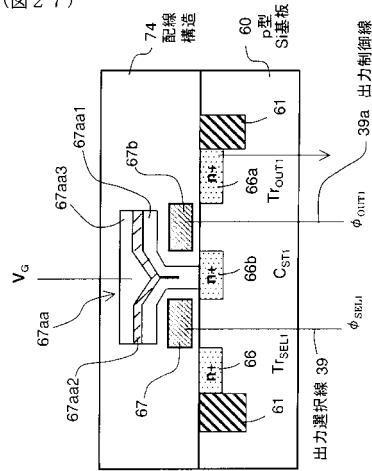

【0240】

トランスマルチゲート $TG_1 \sim TG_n$ は、次のような構成を持つ。例えば、トランスマルチゲート $TG_1$ について言えば、図17に示すように、ゲート電極77と、このゲート電極77を挟んで両側に形成された一対の $n^+$ 形領域（ソース・ドレイン領域）76とを含むMOSトランジスタから構成されている。ゲート電極77には、図示しない配線を介してトランスマルチゲート制御信号 $T_{T_1}$ が印加される。一方の $n^+$ 形領域76（ソース・ドレイン領域）は、配線構造74の内部に形成された導電性コンタクトプラグ78、80及び82と配線膜79、81及び83とを介して、対応するバンプ電極90に電気的に接続されている。その結果、トランスマルチゲート $TG_1$ の当該ソース・ドレイン領域は、埋込配線23を介して、上位半導体回路層21Cの対応するフォトダイオード $PD_1$ に電気的に接続されていることになる。当該MOSトランジスタの他方の $n^+$ 形領域76（ソース・ドレイン領域）は、配線構造74の内部に形成された導電性コンタクトプラグ78と図示しない配線膜を介して、対応するリセットトランジスタ $T_{R\ S\ T}$ と増幅トランジスタ $T_{r\ A\ M\ P}$ に電気的に接続されている。トランスマルチゲート $TG_2 \sim TG_n$ は、トランスマルチゲート $TG_1$ と同じ構造を持っている。このようにして、下位半導体回路層22C'内のトランスマルチゲート $TG_1 \sim TG_n$ は、埋込配線23を介して、上位半導体回路層21C内のフォトダイオード $PD_1 \sim PD_n$ にそれぞれ電気的に接続されている。

【0241】

以上述べたように、図16及び図17に示した第11実施形態に係るイメージセンサ2Fは、第4実施形態のセンサ回路1C（図5参照）を適用したものであって、 $(k \times m)$ 個の画素ブロック12（それぞれのブロック12が $n$ 個の画素11を含む）と $(k \times m)$ 個の埋込配線23を上位半導体回路層21C中に形成すると共に、 $(k \times m)$ 組のトランスマルチゲート群 $TG_1 \sim TG_n$ ）と $(k \times m)$ 個のリセットトランジスタ $T_{R\ S\ T}$ と $(k \times m)$ 個の増幅トランジスタ $T_{r\ A\ M\ P}$ と $(k \times m)$ 組の選択トランジスタ群 $T_{r\ S\ E\ L_1} \sim T_{r\ S\ E\ L_n}$ と $(k \times m)$ 組の記憶用容量素子群 $C_{S\ T_1} \sim C_{S\ T_n}$ と $(k \times m)$ 組の出力トランジスタ群 $T_{R\ O\ U\ T_1} \sim T_{R\ O\ U\ T_n}$ を下位半導体回路層22C'中に形成し、さらに、埋込配線23及びバンプ電極90を介して、上位半導体回路層21C中の画素ブロック12と、下位半導体回路層22C'中のトランスマルチゲート $TG_1 \sim TG_n$ とを電気的に相互接続している。

【0242】

また、下位半導体回路層22C'の上方の主面（配線構造74の表面）は、バンプ電極90と接着剤91によって、上位半導体回路層21Cの下方の主面（基板40の裏面）に電気的・機械的に接続されているので、両回路層21Cと22C'は二段の半導体積層構造（三次元構造）を構成する。

【0243】