**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>6</sup>

H03K 19/20

(45) 공고일자 2005년09월08일

(11) 등록번호 10-0484460

(24) 등록일자 2005년04월12일

(21) 출원번호

(22) 출원일자

10-1997-0033463

1997년07월18일

(65) 공개번호

(43) 공개일자

10-1998-0012921

1998년04월30일

(30) 우선권주장

08/687,800

1996년07월19일

미국(US)

(73) 특허권자

텍사스 인스트루먼츠 인코포레이티드

미국 텍사스주 75265 달拉斯 노스센트럴 익스프레스웨이 13500

(72) 발명자

보스하트 패트릭 더블유

미국 75025 텍사스주 플라노 타라 시티. 7508

(74) 대리인

장수길

주성민

**심사관 : 권호영**

**(54) 상이한 임계전압을 갖는 트랜지스터를 사용하는 동적 논리회로**

**요약**

바람직한 논리 회로 실시예(10)에는 프리차지 페이즈 동안 프리차지 전압( $V_{DD}$ )으로 프리차지 되도록 결합되고 평가 페이즈 동안 방전되도록 동작하는 프리차지 노드(14)가 있다. 회로는 프리차지 노드에 접속되고 프리차지 전압과는 다른 전압에 프리차지 노드를 결합하도록 동작하는 조건부 직렬 방전 경로(22, 24 및 16)도 포함한다. 조건부 직렬 방전 경로는 제1 임계 전압을 갖는 로우 임계 전압 트랜지스터(22 또는 24) 및 제1 임계 전압 보다 크기가 더 높은 제2 임계 전압을 갖는 하이 임계 전압 트랜지스터(16)를 구비하고, 하이 임계 전압 트랜지스터의 게이트에 접속된 전압은 프리차지 페이즈동안 디스에이블 된다.

**대표도**

도 1

**명세서**

**도면의 간단한 설명**

도 1은 GATED CLOCK 신호에 응답하여 상보 형태로 동작하도록 접속된 트랜지스터를 갖고 또한 이를 상보 동작 트랜지스터 사이에 접속된 논리 회로도 가지며, 상기 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 2는 도 1에서와 같은 게이트된 클럭에 접속된 상보 동작 트랜지스터가 없고, 게이트된 입력 신호를 갖는 논리 회로에 적어도 하나의 트랜지스터가 있는 논리 회로를 가지며, 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 3은 도 1의 구성 요소를 갖고, 논리 회로 내에 제2 방전 경로를 포함하며, 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 4는 GATED CLOCK 신호에 응답하여 상보 형태로 동작하도록 접속된 트랜지스터를 갖고 또한 이들 상보 동작 트랜지스터 사이에 접속된 논리 회로도 가지며, 프리차지 전압이 방전 전압 보다 낮고, 상기 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 5는 도 2의 구성 요소를 갖고, 논리 회로 내에 제2 방전 경로를 포함하며, 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 6은 도 1의 구성 요소를 갖고, 방전이 발생할 수 있는 모두 4개의 상이한 경로를 제공하는 추가 접속부를 포함하며, 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 논리 회로의 개략도.

도 7은 회로가 상이한 임계 전압을 갖는 트랜지스터를 포함하는 동적 지퍼 논리 회로의 개략도.

도 8a는 그의 방전 경로에 인버터 회로를 갖는 동적 논리 회로의 개략도.

도 8b는 인버터 회로 내의 트랜지스터에 대하여 더욱 상세히 도시한 도 8a의 개략도.

도 9는 2개의 프리차지 노드를 갖고, 이들 2개의 프리차지 노드 중의 하나 만이 주어진 평가 페이즈에서 방전되어 상보 출력이 제공되는 동적 논리 회로의 개략도.

도 10은 다음 p채널 도미노단에 전위 방전 경로를 제공하는 n채널 도미노단의 출력을 갖는 동적 논리 회로의 개략도.

도 11a는 그의 게이트가 접지에 접속되고 전체 전원 전압과 동일한 드레인-소스 전압을 갖는 로우 임계 전압 트랜지스터의 개략도.

도 11b는 각 트랜지스터의 게이트가 접지에 접속된 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터의 개략도.

도 12는 그들 트랜지스터의 각각이 동작의 프리차지 페이즈 동안 디스에이블 되고, 그의 방전 경로에서 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터를 갖는 동적 논리 회로의 개략도.

도 13은 로우 임계 전압 트랜지스터의 각각이 동작의 프리차지 페이즈 동안 디스에이블 되고, 하이 임계 전압 트랜지스터와 직렬 접속된 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터를 갖는 동적 논리 회로의 개략도.

도 14는 로우 임계 전압 트랜지스터의 각각이 동작의 프리차지 페이즈 동안 디스에이블 되고, 하이 전압 임계 트랜지스터가 두개의 로우 임계 전압 트랜지스터 사이에 접속되어 있고, 그의 방전 경로에 하이 전압 임계 트랜지스터와 직렬 접속된 2개의 로우 임계 전압 트랜지스터를 갖는 동적 논리 회로의 개략도.

도 15a는 트랜지스터의 각각이 동작의 프리차지 페이즈에서 디스에이블 되는 그의 방전 경로에 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터를 구비하는 제1 방전 경로 및 동작의 프리차지 페이즈에서 디스에이블 되는 하이 임계 전압 트랜지스터를 구비하는 제2 방전 경로를 갖는 동적 논리 회로의 개략도.

도 15b는 2개의 방전 경로를 갖지만, 2개의 방전 경로의 양자에 의해 공유되는 또 하나의 트랜지스터가 포함되어 있는 도 15a의 동적 논리 회로의 변경 개략도.

도 16은 트랜지스터의 각각이 동작의 프리차지 페이즈에서 디스에이블 되고 그의 방전 경로에 한 쌍의 캐스코드 접속된 로우 임계 전압 p채널 트랜지스터를 갖는 동적 논리 회로의 개략도.

도 17은 도 12의 구성 요소를 갖고 또한 방전이 발생할 수 있는 모두 4개의 상이한 경로를 제공하는 또 하나의 접속부를 더 포함하며, 각 방전 경로가 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터를 구비하고, 이들 트랜지스터의 각각이 동작의 프리차지 페이즈에서 디스에이블 되는 동적 논리 회로의 개략도.

도 18은 트랜지스터의 각각이 동작의 프리차지 페이즈 동안 디스에이블 되고 그의 방전 경로에 한 쌍의 캐스코드 접속된 로우 임계 전압 트랜지스터를 갖는 방전 경로를 각 회로단이 구비하는 동적 지폐 논리 회로의 개략도.

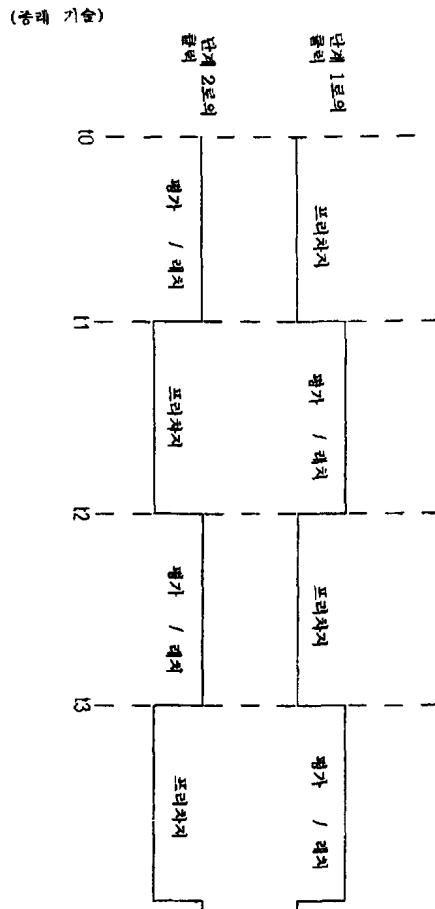

도 19a는 공통 클럭이 사용되어 프리차지 페이즈의 제1 동적 논리 회로 및 평가 페이즈의 제2 동적 논리 회로를 동시에 클럭하고 상보 형태로 동작하도록 그 회로들을 전환함으로써 제2 동적 논리 회로가 프리차지 페이즈인 동안 제1 동적 논리 회로가 평가 페이즈로 되는 종래 다상 회로의 블럭도.

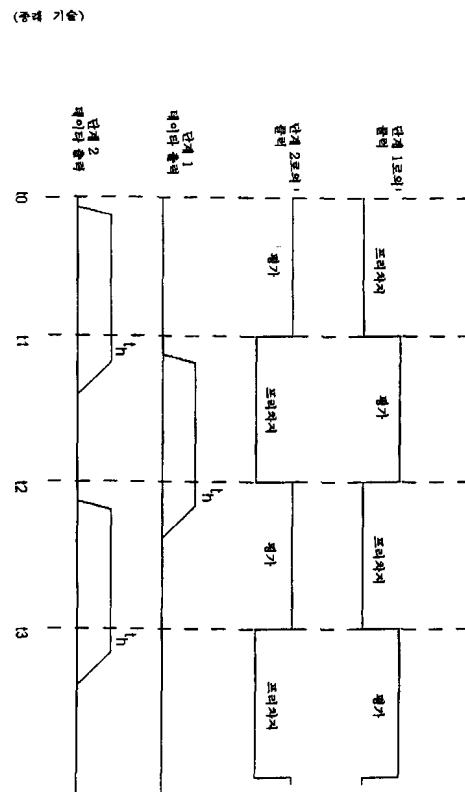

도 19b는 페이즈 회로 내에 포함된 트랜지스터단을 특히 강조하여 도 19a의 종래 블럭도를 도시한 개략도.

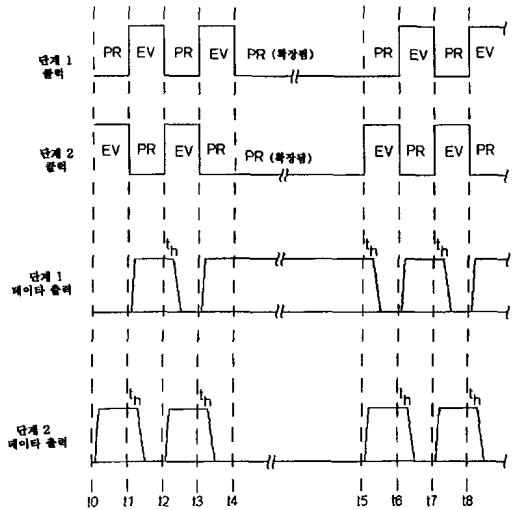

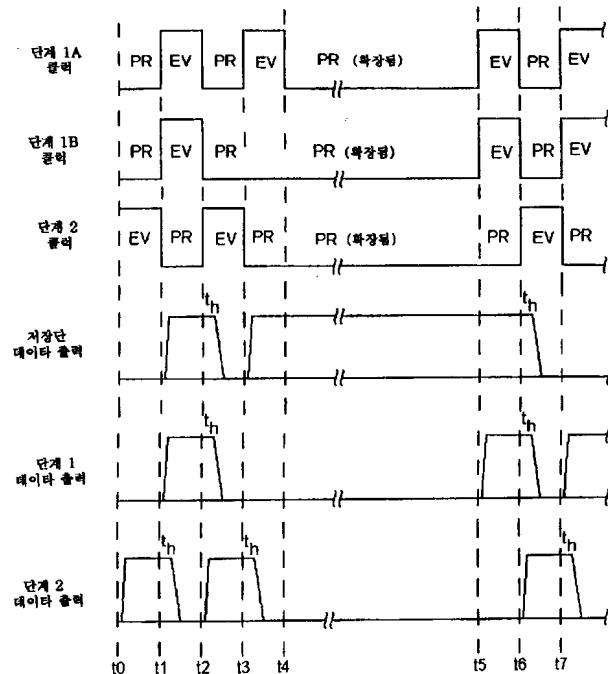

도 19c는 도 19a 및 도 19의 종래 회로의 동작을 설명하는 타이밍도.

도 20a는 페이즈 회로 사이에 복잡한 래칭 구조가 없고 평가 페이즈 이상의 홀드 시간 동안 출력 데이터를 제공하는 종래 홀드 시간 래치 회로의 개략도.

도 20b는 도 20a의 종래 회로의 동작을 설명하는 타이밍도.

도 21a는 페이즈 회로 사이에 복잡한 래칭 구조가 없고 확장된 프리차지 기간동안 하나의 페이즈 회로의 최종단이 데이터를 저장하는 다상 실시예의 개략도.

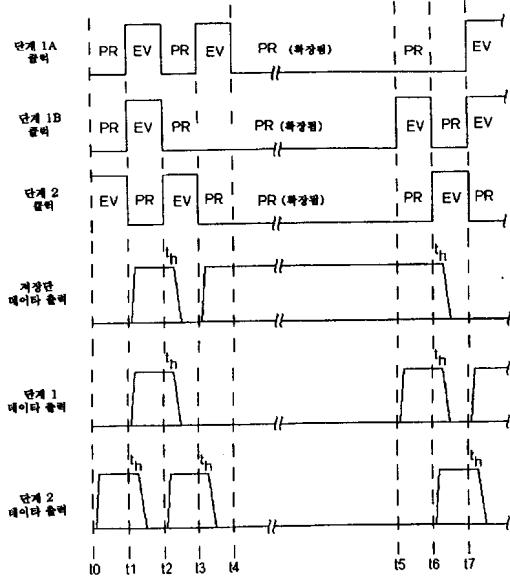

도 21b는 도 21a의 회로의 동작을 설명하는 타이밍도.

도 22a는 페이즈 회로 사이에 복잡한 래칭 구조가 없고 확장된 프리차지 기간동안 하나의 페이즈 회로의 최종단 이외의 단이 데이터를 저장하는 다상 실시예의 개략도.

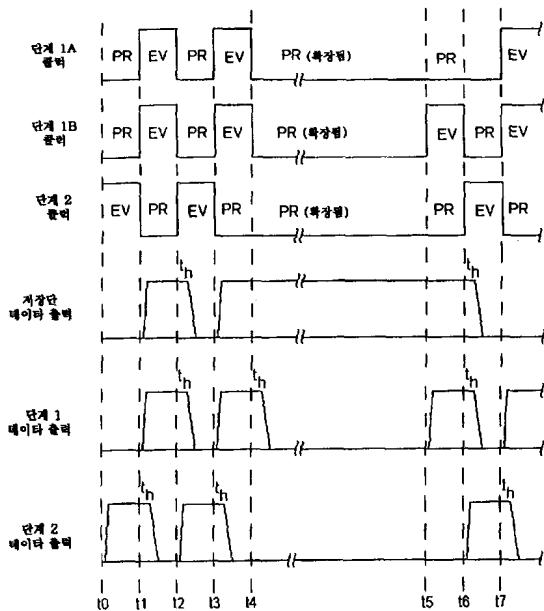

도 22b는 도 22a의 회로의 동작을 설명하는 타이밍도.

도 22c는 도 22a의 회로의 다른 동작을 설명하는 타이밍도.

도 22d는 도 22a의 회로의 변경예의 다른 동작을 설명하는 타이밍도.

도 23은 분리 페이즈 회로를 독립적으로 클럭 하는 분리 클럭을 갖는 회로를 도시한 도면.

도 24는 프리차지 주기의 기간에 대하여 평가 주기의 기간을 단축하는 회로를 도시한 도면.

<도면의 주요 부분에 대한 부호의 설명>

10 : 동적 논리 회로

14 : 프리차지 노드

16 : 하이 임계 전압 트랜지스터

22, 24 : 로우 임계 전압 트랜지스터

**발명의 상세한 설명**

**발명의 목적**

**발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 트랜지스터 회로 구성에 관한 것으로, 특히 상이한 임계 전압(threshold voltage)을 갖는 트랜지스터를 사용하는 동적 논리 회로(dynamic logic circuit)에 관한 것이다.

수많은 현재의 회로 어플리케이션에 있어서, 회로 어플리케이션의 동작 속도를 증가시키는 것이 요망되고 있다. 예를 들면, 마이크로프로세서 설계에서, 마이크로프로세서의 속도를 제한하는 부분을 이루거나 또는 속도에 영향을 주는 회로는 전체 마이크로프로세서 속도가 증가되도록 끊임없이 조사되어 재설계된다. 속도 증가는 성능을 향상시키므로, 더 짧은 시간에 더 상세하고 정교한 처리 기능이 허용된다.

마이크로프로세서 뿐만 아니라 속도가 중요한 또 다른 회로의 속도를 증가시키기 위해, 동적 논리 트랜지스터가 현재 사용되고 있는 데, 이것은 그들이 정적 논리 트랜지스터 회로와 비교하여 증가된 속도를 제공하기 때문이다. 동적 논리 회로는 두 페이즈의 동작에 의해 특징지어진다. 먼저, 프리차지 노드는 프리차지 페이즈 동안 제1 전위로 설정된다. 두 번째로, 평가 페이즈 동안, 회로에 의해 표현된 논리 조건이 만족되면, 프리차지 노드는 방전되고, 이것에 의해 회로의 논리 출력이 변경된다. 즉, 프리차지 페이즈의 결과, 프리차지 노드는 제1 논리 상태가 동적 논리 회로에 의해 출력되게 하고, 프리차지 노드가 평가 페이즈에서 방전되면, 동적 논리 게이트의 출력은 제1 논리 상태와는 다른 제2 논리 상태를 나타낸다. 예를 들면, 프리차지에서 방전으로 천이를 게이트하기 위해 하나 이상의 n채널 트랜지스터를 사용하여 수행될 때, 상태를 변경하는 방전의 동작은, 한 순간에 n채널 트랜지스터의 네트워크에 의해 천이를 실행하고 다른 순간에 p채널 트랜지스터의 네트워크에 의해 반대 천이를 실행하는 종래 정적 논리 회로의 동작 이상의 속도 증가를 나타낸다.

제조 중 현재 사용되고 있는 또 다른 동작 기술은 임의의 회로 기대값이 주어진 트랜지스터의 임계 전압을 목적으로 하고 있다. 특히, 대표적으로 제조자는 주어진 임계 전압의 트랜지스터를 포함하여, 트랜지스터를 만들거나 이용 가능한 트랜지스터 제조 공정을 사용한다. 이러한 공정이 제공될 때, 제조자는 통상 속도 개선 대 전력 소비의 트레이드 오프를 고려한다. 동작 속도를 증가시키기 위해, 회로내의 모든 트랜지스터의 임계 전압을 줄이는 것이 알려져 있다. 임계 전압을 낮추는 것에 의해, 이들 트랜지스터의 구동 전류는 증가된다. 그러나, 이들 동일한 트랜지스터의 누설 전류도 증가된다. 또한, 전원 전압이 감소되고 트랜지스터의 임계 전압이 전원 전압의 더 큰 부분을 점유할 때 이러한 접근 방법은 더욱 더 제한적이 된다는 것을 유의하라. 따라서, 하나의 접근 방법은 트랜지스터의 임계 전압을 낮추는 것이지만, 이것은 누설 전류를 증가시키므로, 전체 대기 전력 소비를 증가시킨다. 따라서, 보통은 제조자가 수용 가능한 한계인 누설의 레벨을 예측하고, 그 한계를 고려하여 회로의 트랜지스터 각각이 그 한계를 제공하게 될 지정된 임계 전압을 공유하도록 공지의 파라미터를 조정한다.

상기 접근 방법이 회로 동작 속도를 향상시키는 기술을 대표하는데, 그들은 여러 한계 및 문제점을 제공한다. 예를 들면, 동적 논리 속도는 논리에 사용된 트랜지스터의 임계 전압에 의해 여전히 제한된다. 다른 예로서, 상술한 바와 같이, 임계 전압을 낮추는 것에 의한 속도 향상은 누설 전류로 인한 대기 전력 소비를 반드시 증가시킨다. 본 발명의 발명자는 상기 문제점을 인식하고, 이하는 종래 전류 상태와 비교하여 누설 전류를 저감하면서 회로 속도를 증가시키는 실시예를 설명한다.

### **발명이 이루고자 하는 기술적 과제**

여러 실시예는 논리 회로, 시스템 및 방법에 관한 것이다. 바람직한 동적 논리 회로 실시예에는 프리차지 페이즈 동안 프리차지 전압으로 프리차지 되도록 결합되고 평가 페이즈 동안 방전 되도록 동작하는 프리차지 노드가 있다. 상기 회로는 프리차지 노드에 접속되고 프리차지 노드를 프리차지 전압과는 다른 전압에 결합하도록 선택적으로 동작하는 조건부 직렬 방전 경로를 포함한다. 조건부 직렬 방전 경로는 제1 임계 전압을 갖는 로우 임계 전압 트랜지스터 및 제1 임계 전압보다 크기가 더 높은 제2 임계 전압을 갖는 하이 임계 전압 트랜지스터를 포함하고, 하이 임계 전압 트랜지스터의 게이트에 접속된 전압은 프리차지 페이즈 동안 디스에이블 된다. 다른 회로, 시스템 및 방법도 기술되고 특허청구된다.

### **발명의 구성 및 작용**

이하, 본 발명을 첨부 도면을 참조하면서 본 발명의 여러 실시예를 설명한다. 독자를 돋지만, 이들 실시예의 신규한 범위 및 그러한 실시예의 수많은 특징을 제한하지 않고, 다음의 목차는 다음의 설명에서 특정 제목을 식별하기 위한 4개의 부표 제를 설명한다.

### **목 차**

#### **절 부제 제목**

## 1 상이한 임계 전압을 갖는 트랜지스터를 사용하는 동적 논리 회로, 시스템 및 방법1

## 2 로우 임계 전압을 갖는 캐스코드 트랜지스터를 사용하는 동적 논리 회로, 시스템 및 방법

## 3 동적 논리 게이트의 전력 감소 회로, 시스템 및 방법

## 4 결론

### 1. 상이한 임계 전압을 갖는 트랜지스터를 사용하는 동적 논리 회로, 시스템 및 방법

다음에 설명되는 도면에 제시된 여러 실시예에 앞서서, 임계 전압을 낮추는 것에 의한 회로 속도의 향상이 누설 전류를 바람직하지 못하게 증가시키고, 그 반대로, 임계 전압을 상승시키는 것에 의한 전류 누설의 개선이 회로 속도를 바람직스럽지 못하게 감소시킨다는 점에서 현재의 기술 수준이 트레이드 오프를 요구한다는 것을 상기하라. 그러나, 그와 반대로, 다음의 실시예는 상술한 종래 기술의 구성과 비교해 보면 전류 누설을 상응하여 증가시키지 않으면서도 회로 속도를 증가시킨다.

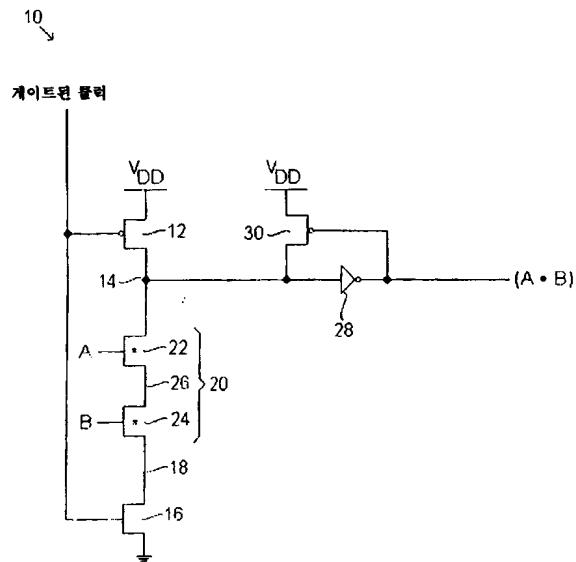

도 1은 도미노 게이트 구성(domino gate configuration)이라고 하는 것으로 구성되고, 참조부호(10)로 나타낸 제1 동적 논리 회로 실시예의 개략도이다. 회로 10은 p채널 프리차지 트랜지스터(12)의 게이트에 접속된 GATED CLOCK 신호를 포함하고, 상기 트랜지스터는 시스템 전압 레벨(예를 들면,  $V_{DD}$ )의 전압원에 접속된 소스 및 프리차지 노드(14)에 접속된 드레인을 갖는다. GATED CLOCK 신호는 n채널 방전 트랜지스터(16)의 게이트에 접속되고, 상기 n채널 트랜지스터는 그의 소스가 로우 기준 전압(예를 들면, 접지)에 접속되고, 그의 드레인이 노드 18에 접속되어 있다.

프리차지 노드(14)와 노드 18사이에는 논리 회로(20)가 접속되어 있다. 회로 10에서, 논리 회로(20)의 특정 논리는 A AND B의 논리식을 구현하고, 구체적으로, 이 논리 함수는 다음의 추가 구성요소에 의해 발생된다. 논리 회로(20)는 2개의 n채널 트랜지스터 22 및 24를 포함한다. n채널 트랜지스터(22)의 게이트는 입력 신호 A를 수신하도록 접속되고, n채널 트랜지스터(24)의 게이트는 입력 신호 B를 수신하도록 접속된다. n채널 트랜지스터(22)의 드레인은 프리차지 노드(14)에 접속되고, n채널 트랜지스터(22)의 소스는 노드 26에 접속된다. n채널 트랜지스터(24)의 드레인은 노드 26에 접속되고, n채널 트랜지스터(24)의 소스는 노드 18에 접속된다.

프리차지 노드(14)를 다시 보면, 이것은 인버터(28)의 입력에도 접속된다. 인버터(28)의 출력은 회로 10의 출력 신호(즉, A AND B)를 제공하고, p채널 트랜지스터(30)의 게이트에 접속된다. p채널 트랜지스터(30)의 소스는  $V_{DD}$ 에 접속되고, p채널 트랜지스터(30)의 드레인은 프리차지 노드(14)에 접속된다. p채널 트랜지스터(30)가 도 1에 도시한 다른 트랜지스터보다 더 작은 것이 바람직하다는 것에 유의하라.

다음에 설명하는 이유로 인해, 회로 10에 의해 실현되는 논리식은 도 1의 방법으로 접속된 회로를 포함하는 종래 구성과 동일하지만, 회로의 속도 뿐만 아니라 그의 누설 전류 특성은 상당히 다르다. 그러나, 설명이 간단하게 되도록, 일반적 논리 동작을 먼저 설명하고 나서, 종래 기술 이상의 성능 개선 및 회로 변경을 설명한다. 회로 10의 동작을 다시 보면, 그러한 동작이 2개의 페이즈, 즉 프리차지 페이즈라고 하는 첫 번째 페이즈 및 평가 페이즈라고 하는 두 번째 페이즈에 걸쳐 발생하는 것에 유의하라. 이들 페이즈의 선택 및 기간은 다음의 설명에서 명확하게 되는 바와 같이 GATED CLOCK 신호에 의해 회로 10에서 제어된다.

회로 10은 GATED CLOCK 신호가 프리차지 트랜지스터(12)에 대하여 인에이블될 때 프리차지 페이즈에 있다. 용어 "인에이블"은 당분야 공지이고, 게이트 전위가 접속된 트랜지스터의 도전 경로(즉, 소스/드레인)를 따라 도통을 일으키기에 충분한 것을 나타내는 것에 유의한다. 따라서, 회로 10은 프리차지 트랜지스터(12)가 도통되는 레벨로 GATED CLOCK 신호가 설정될 때 프리차지 페이즈에 있다. 따라서, 이 예에서, 이것은 GATED CLOCK 신호가 로우일 때 발생한다. 이 예에서, p채널 프리차지 트랜지스터(12)는 n채널 방전 트랜지스터(16)가 도통하지 않는 동안 도통한다. 그 결과, 프리차지 노드(14)는 p채널 프리차지 트랜지스터(12)를 거쳐 접속되고, 회로 10의 하나의 논리 상태를 나타내는 프리차지 전압(예를 들면,  $V_{DD}$ )으로 프리차지된다. 회로 10의 예에서,  $V_{DD}$  또는 그에 가까운 프리차지 전압은 인버터(22)에 의해 반전되고 논리 0을 나타내도록 출력된다. 이 논리 0도 p채널 트랜지스터(30)를 도통시켜 프리차지 노드(14)가  $V_{DD}$ 로 유지되는 것에 유의한다.

회로 10은 GATED CLOCK 신호가 방전 트랜지스터(16)에 대하여 인에이블될 때 평가 페이즈에 있으므로, 이 예에서, 이것은 GATED CLOCK 신호가 하이일 때 발생한다. 따라서, 평가 페이즈의 초기에, 논리 회로(20)는 프리차지단에 의해 발생된 논리 신호(즉, 이 예에서는 논리 0)를 계속 출력한다. 그러나, 논리 회로(20) 및 GATED CLOCK 신호에 응답하는 동작으로 인해, 그 논리 출력 신호는 프리차지 페이즈 후와 동일한 레벨로 유지되거나 또는 그 대신 다음에 기술하는 바와 같이 반대 논리 상태로 천이한다. 특히, 로우에서 하이로의 GATED CLOCK의 천이에 응답하여, n채널 프리차지 트랜지스터(16)는 p채널 프리차지 트랜지스터(12)가 도통하지 않는 동안 도통한다. 그 결과, 프리차지 노드(14)는 논리 회로(20)를 거쳐 접속되고 n채널 방전 트랜지스터(16)를 거쳐 접지에도 접속될 수 있다. 따라서, 이 페이즈 동안, 접지로의 접속은 논리 회로(20)에 의해 달성되는 논리가 그 직렬 경로내의 각 트랜지스터가 도통이도록 이루어지면 발생한다. 이 예에서, 논리 동작은 A AND B 이므로, A 및 B 입력 신호 모두가 하이이면, 논리 회로(20)를 통한 경로의 각 트랜지스터는 도통하고, 프리차지 노드(14)는 접지에 접속된다. 그 결과, 프리차지 노드(14)의 프리차지 전압(즉, 도 1의 예에서는  $V_{DD}$ )은 접지를 향해 방전되는 것이 허용된다. 이러한 방법으로 프리차지 노드(14)를 방전하는 것에 의해, 프리차지 노드(14)의 전압이 접지에 또는 그것에 가까이 도달하고 또한 인버터(28)에 의해 반전되는 것에 유의한다. 또한, 출력이 이러한 방법으로 상승한 후, 트랜지스터(30)가 오프하는 것에 유의한다. 또한, 이 방법으로의 방전은 회로 10의 논리값의 천이를 나타내고, 회로 10의 이 예에서의 방전 출력은 1의 논리값을 나타낸다.

상기로부터, 본 발명 분야의 숙련자는 회로 10이 프리차지 페이즈 동안 제1 논리 상태로 프리차지되고 나서 평가 페이즈 동안 그 상태를 유지하거나 또는 논리 회로(20)에 의해 실행된 논리 동작이 만족되면 평가 페이즈 동안 반대 논리 상태로 논리 천이를 달성하도록 방전될 수 있다는 것을 이해할 것이다. 상기 예에서 설명한 바와 같이, 트랜지스터의 접속 뿐만 아니라 논리 회로(20)의 종류도 (예를 들면, 기타의 또는 또 하나의 기능으로 변경하는 것에 의해 및/또는 더 많은 입력 신호를 추가하거나 또는 제거하는 것에 의해) 특정 논리 동작이 변경되도록 변환될 수 있다는 것에 유의한다. 그러나, 결국 본 실시예의 목적을 위해, 조건부 직렬 방전 경로가 프리차지 노드(14)에서 상이한 전위까지 발생되어, 그 상태에서 그 직렬 경로를 따라 있는 모든 트랜지스터의 도전 경로(즉, 소스/드레인 경로)가 도통하고, 프리차지 노드(14)의 전위가 제1 레벨에서 제2 레벨로 변경되는 것에 의해, 회로 10의 출력에 대한 논리 천이가 표현되는 것에 유의한다. 따라서, 본 명세서의 나머지 부분에 대하여, 이러한 종류의 그러한 경로를 따른 조건부 직렬 접속을 "방전 경로"라고 하고, 이것은 그 경로를 따라 있는 모든 트랜지스터가 도통이라는 조건이 맞을 때 방전이 발생되는 것으로 이해된다. 또한, 프리차지 및 방전은 당분야 공지의 용어이고, 하나의 논리 상태에서 다른 논리 상태로의 천이라고 고려되지만, 방전 전압 보다 높은 전압의 프리차지로 제한되지 않는다. 즉, 다른 구성에서, 다음의 도 4에 도시한 것은 제1 전압으로의 프리차지 및 제1 전압 보다 높은 제2 전압으로의 방전을 사용한다. 따라서, 이들 용어는 상대적 전압 레벨을 나타내지 않지만, 회로의 논리 레벨 출력에서의 변경을 나타내는 전압 변경은 나타낸다. 또한, 본 명세서의 목적은 이들 용어가 이러한 방법으로 사용되는 것을 의도한다.

도 1을 참조하고, 도 1과 종래 기술 사이의 중요한 차이에 초점을 맞출 때, 도면 중 별표가 n채널 트랜지스터 22 및 24에는 도시되어 있지만 n채널 트랜지스터(16)에는 없는 것에 유의한다. 바람직한 실시예에서, n채널 트랜지스터 22 및 24의 임계 전압("V<sub>T</sub>")은 n채널 트랜지스터(16)의 임계 전압 보다 낮다. 이러한 방법으로 별표를 사용하는 것, 즉 로우 임계 전압 트랜지스터를 나타내는 것이 나머지 도면에서도 마찬가지인 것에 유의한다. 하이 임계 전압 트랜지스터에 대하여 로우 임계 전압 트랜지스터의 사용을 강조하는 것을 설명하기 전에, 이들 용어가 다른 트랜지스터의 임계 전압에 대한 하나의 트랜지스터의 임계 전압의 상대적 값을 나타내도록 사용되며, 이들 용어가 어떤 절대적 값으로 반드시 제한되지 않는 것에 유의한다. 특히, 본 발명 분야에서는 트랜지스터가 소량의 전류를 통과시키는 게이트 소스간 전압을 결정하기 위해 그의 전류-전압 특성을 측정함으로써 트랜지스터의 임계 전압을 결정할 수 있는 것이 알려져 있다. 임계 전압의 상대적 속성을 설명하기 위해 다음을 고려한다. 제1 임계 전압을 갖는 제1 트랜지스터에 대하여, 주어진 드레인 소스간 전압에서 제1 양의 구동 전류를 공급한다(그의 게이트가 그의 드레인에 접속되어 있음). 제1 임계 전압 보다 낮은 제2 임계 전압을 갖는 제2 트랜지스터에 대하여, 제2 트랜지스터는 주어진 드레인 소스간 전압에서 제2 양의 구동 전류를 공급하고(그의 게이트가 그의 드레인에 접속되어 있음), 이 구동 전류는 동일한 드레인 소스간 전압에서 제1 트랜지스터에 의해 제공된 제1 양의 구동 전류보다 크다. 본 명세서의 나머지 부분에 대하여, 제1 종류의 트랜지스터는 HVT 트랜지스터(비교적 높은 V<sub>T</sub>를 갖는 트랜지스터)라고 하고, 제2 종류의 트랜지스터는 LVT 트랜지스터(비교적 낮은 V<sub>T</sub>를 갖는 트랜지스터)라고 한다. 또한, 모든 트랜지스터가 동일한 V<sub>T</sub>를 공유하고, 그 V<sub>T</sub>가 수용할 수 없는 큰 누설 전류를 충분히 피할 수 있도록 높게 결정되었을 때 HVT 트랜지스터가 전체 회로에 사용되는 트랜지스터의 V<sub>T</sub>와 거의 비슷한 V<sub>T</sub>를 갖는 것에 유의한다. 또한, LVT 트랜지스터가 HVT 트랜지스터와 반대로 더 높은 구동 전류의 이점을 제공하더라도, 그에 반하여 HVT 트랜지스터 보다 큰 누설 전류를 제공하는 문제점을 일으키는 것에 유의한다. 또한, 일반적으로 LVT 트랜지스터에 의한 누설은 HVT 트랜지스터의 누설 보다 크기가 두 자리수 또는 세 자리수 이상 클 수 있다.

도 1을 다시 보면, 별표로부터 n채널 트랜지스터 22 및 24는 LVT 트랜지스터이고 n채널 트랜지스터(16)는 HVT 트랜지스터인 것을 상기한다. 이러한 특징은 종래 기술과는 완전히 딴판인데, 종래 기술에서는 도 1과 같은 구성의 트랜지스터 각각이(즉, 더 낮은  $V_T$ 가 사용되었다면 생기게 되는 수용불가능한 큰 누설 전류를 회피하기 위해) 동일한 하이  $V_T$ 를 갖도록 구성되었고, 또한 규범적으로 반드시 동일한 하이  $V_T$ 를 가져야만 했다.

본 실시예에가 HVT 및 LVT 트랜지스터 양자를 사용하는 상술한 특징의 이점을 설명하기에 앞서, 본 명세서에서 설명되는 실시예가 다양한 방법으로 구성되어 상이한 임계 전압을 갖는 상이한 트랜지스터를 달성하는 것에 유의한다. 첫 번째 예로서, 이러한 목적을 달성하는 한 가지 방법은 상이한 임계 전압을 갖는 트랜지스터를 사용한 동적 논리 회로의 생성을 특별히 허용하는 제조 공정을 활용하는 것일 것이다. 예를 들면, 현재의 기술에서는 통상 단일 반도체 영역(예를 들면, 웨이퍼)을 마스크하고 노출된 영역을 임플란트(implant)에 노출시켜, 제1 도전형의 노출된 트랜지스터 채널에 대한 임계 전압을 확립한다. 예를 들면, 모든 n채널 트랜지스터의  $V_T$ 를 이러한 공정을 활용하는 것에 의해 설정하고 나서, 모든 p채널 트랜지스터에 대하여 상이한 마스크 세트로 그것을 반복할 수 있다. 따라서, 2개의 주입 공정을 활용하여, n채널 및 p채널 트랜지스터 양자에 대하여  $V_T$ 를 설정한다. 또한, 양 도전형에 대하여, 이 방법으로 사용된 임플란트의 깊이 및/또는 놓도는 노출에 기인하는 임계 전압의 레벨에 영향을 준다. 현재의 규격 하에서, 일반적 트랜지스터는 500 밀리볼트 정도의  $V_T$ 를 갖는다. 그러나, 양 세트가 동일한 도전형을 갖지만 한 세트는 HVT 트랜지스터를 포함하고 나머지 세트는 LVT 트랜지스터를 포함하는 적어도 2개의 상이한 세트의 트랜지스터가 제공되도록 방법을 확장할 수도 있다. 이러한 확장된 방법을 사용하였을 때, 하나의 도전형에 대하여, 제1 세트의 마스크는 적절한 위치에 HVT 트랜지스터의 세트를 만들도록 사용되고, 제2 세트의 마스크는 상이한 위치에 LVT 트랜지스터의 세트를 만들도록 사용될 수 있다. 따라서, 주어진 트랜지스터 도전형에 대하여, 하나의 임플란트가 HVT 트랜지스터를 만들도록 제1 세트의 마스크를 사용하여 발생된다. 그후, 다른 임플란트가 LVT 트랜지스터를 만들도록 제2 세트의 마스크를 사용하여 발생된다. 또한, 제2 트랜지스터 도전형에 대하여, 2개 이상의 세트의 마스크 및 임플란트를 마찬가지 방법으로 사용할 수 있다. 또한, HVT 트랜지스터의 500 밀리볼트  $V_T$ 와 반대로, 현재의 트랜지스터 기술은 LVT 트랜지스터에 대하여 200 밀리볼트 정도의  $V_T$ 를 기대할 수 있다. 또한, 이들 값은 당분야 공지의 다양한 고려 사항에 따라 가변할 수 있다. 상기에 부가하여, LVT 트랜지스터에 대한 HVT 트랜지스터의 형성 및/또는 구성이 다른 기술에 의해 물론 달성될 수 있다는 것에 유의한다. 다른 예로서, 일부의 트랜지스터는 실리콘-온 절연체(silicon-on-insulator : SOI) 기술로서 알려진 것을 사용하여 형성된다. 이 기술에서, 각 SOI 트랜지스터는 분리 본체 접속을 포함한다. 일반적으로, 이 본체는 임의의 노드에 접속되거나 또는 플로팅으로 된다. 본 발명의 발명자는 이러한 분리하여 이용가능한 접속이 본 명세서에서 설정된 상대적  $V_T$  규격을 달성하기 위해 사용할 수 있고,  $V_{DD}$ 의 레벨이 그러한 트랜지스터에 대한 다이오드 순방향 바이어스 전압 레벨 아래로 일단 떨어지면 이것에 대한 추가적인 고려 사항이 장래 발생할 수 있다는 것을 인식하였다. 약 0.8 볼트의 통상의 기대 순방향 바이어스 전압 보다 아직은 상당히 높은 현재의  $V_{DD}$  레벨이 주어질 때 또한 LVT 구성을 만들고자 할 때, 트랜지스터 본체를 비접속하여 그것을 플로팅으로 하는 것은 수용가능하다. 그 반대로, 동일한  $V_{DD}$ 가 주어질 때 또한 HVT 구성을 만들고자 할 때, n채널 트랜지스터에 대하여 접지에 (또는 p채널 트랜지스터에 대하여  $V_{DD}$ 에) 트랜지스터 본체를 접속하는 것은 수용가능하다. 상기에 부가하여, 장래의 어떤 시점에서  $V_{DD}$  레벨이 0.5 볼트 이하로 하강하고 따라서 0.8 볼트의 대표적인 기대 순방향 바이어스 전압 보다 상당히 아래로 하강해야 한다는 것에 유의하라. 이 예에서 그리고 LVT 구성을 만들고자 할 때, 전과 같이 트랜지스터 본체를 비접속하여 플로팅으로 하는 것은 수용가능하다. 그 결과, 프리차지 페이즈 동안 그 트랜지스터의 임계 전압은 비교적 낮다. 그와 반대로, HVT 구성을 만들고자 할 때, 트랜지스터 본체는 하이 임계 전압이 바람직한 페이즈(즉, 프리차지 페이즈) 동안 오프되는 것으로 알려진 트랜지스터의 게이트에 접속될 수 있다. 예를 들면, 이러한 방법으로 접속된 n채널 SOI 트랜지스터에 대하여, 프리차지 동안 로우 게이트 전압도 그 트랜지스터의 본체에 접속된다. 그 결과, 프리차지 동안 그 트랜지스터의 임계 전압은 비교적 높다. 또한, 비교적 높은  $V_T$ 도 트랜지스터 본체를 트랜지스터를 인에이블하지 않는 전위에 접속하거나(예를 들면, n채널 트랜지스터에 대하여 접지에 본체를 접속함) 또는 그 트랜지스터의 소스 또는 프리차지 동안 접지로 되는 상이한 신호에 접속하는 것에 의해 달성될 수 있다. 또 다른 기술이 당업자에 의해 상기될 수 있으며 선택된 특정 기술은 본 명세서에 설명될 필요가 없다. 예를 들면, 임의의 트랜지스터를 LVT 트랜지스터로 하고 다른 트랜지스터를 HVT 트랜지스터로 하는 정적 회로에 사용되는 현재의 제조 기술이 있다. 그러나, 이러한 종래 기술에 있어서, 처리는 동적 논리 회로라기보다는 정적 회로에 대하여 사용된다. 또한, 이 기술은 전체 회로 다이 상의 회로 세트 등의 전체 영역이 LVT 트랜지스터를 사용하여 구성되어 그 회로 세트의 속도를 증가시키도록 사용되지만, 이러한 방법으로 구성된 영역이 HVT 트랜지스터를 사용하여 구성되는 회로 다이 상의 나머지 영역과 비교하여 증가된 양의 전류 누설을 갖는 것을 알아야 한다. 따라서, 본 발명의 목적을 위해, 이러한 기술을 수정하거나 또는 당업자에게 입수가능한 다른 기술을 사용하는 것에 의해, 본 명세서에 기술된 실시예에 의해 안내되는 회로 구성 내의 LVT 또는 HVT를 선택하여, 상이한 트랜지스터에 대하여 상이한 임계 전압을 고의로 지정하는 것에 의해 주어진 회로를 구성할 필요가 있다.

혼합된 HVT 및 LVT 트랜지스터 회로의 개념을 도입하였지만, 본 발명의 발명자가 상술한 원리를 인식하여 동적 논리 회로의 어떤 속성 및 VHT 및 LVT 트랜지스터의 이점에서 유익한 다양한 유일 실시예를 창출한 것이 이해될 것이다. 이들이 점의 제1 예는 회로 10의 상이한 임계 전압 트랜지스터의 상세한 동작을 제공하는 것에 의해 실현될 수 있고, 다음의 설명은 먼저 동작의 프리차지 페이즈를 설명하고 두 번째로 동작의 평가 페이즈를 설명한다.

동작의 프리차지 페이즈 동안, GATED CLOCK 신호는 로우이므로, n채널 방전 트랜지스터(16)는 p채널 프리차지 트랜지스터(12)가 노드 14를 프리차지 전압  $V_{DD}$  까지 충전시키는 동안 오프로 된다. A 및 B의 데이터값에 따라, n채널 트랜지스터 22 및 24는 온 또는 오프로 될 수 있다. 그러나, 이들 마지막 2개 레지스터에 관계없이, n채널 방전 트랜지스터(16)가 오프이므로 방전은 프리차지 노드(14)에서 접지로 발생할 수 없다는 것에 유의한다. 또한, n채널 방전 트랜지스터(16)가 HVT 트랜지스터이고, 그 결과, HVT 트랜지스터가 오프일 때 (LVT 트랜지스터에 반하여) 더 낮은 누설 전류를 가지므로, HVT n채널 방전 트랜지스터(16)는 n채널 트랜지스터 22 및 24를 거쳐 접지로 얼마나 많은 전류가 프리차지 노드(14)에서 누설할 수 있는 가의 제한을 제공한다. 따라서, 방전 경로가 몇 개의 LVT 트랜지스터(즉, n채널 트랜지스터 22 및 24)를 포함한다 할지라도, 가능한 누설 전류의 양은 동작의 프리차지 페이즈 동안 HVT n채널 방전 트랜지스터(16)에 의해 제한된다.

동작의 평가 페이즈 동안, GATED CLOCK 신호는 하이이고 논리 회로(20)에 의해 달성되는 논리 함수가 실현될 수 있다. 즉, 프리차지 페이즈의 끝에서 회로 10의 출력이 도 1의 예에서는 논리 0인 프리차지 논리 상태를 나타내는 것을 상기 한다. 그러나, 논리 회로(20)에서의 논리식이 그 회로의 각 트랜지스터가 도통(즉, A AND B가 하이임)이도록 되면, 프리차지 노드(14)에서의 전하는 n채널 방전 트랜지스터(16) 뿐만 아니라 논리 회로(20)를 포함하는 방전 경로를 거쳐 접지로 방전되는 것이 허용된다. 이 순간동안, 방전 경로를 구성하는 3개의 트랜지스터(즉, 트랜지스터 22, 24 및 26)는 저항기로서 간주된다. 따라서, 트랜지스터 22 및 24가 LVT 트랜지스터이므로, 이들 트랜지스터의 저항은 HVT 트랜지스터의 저항 보다 현저히 작다는 것에 유의한다. 이들 3개의 저항이 직렬이므로, 방전 경로의 전체 저항은 모두 HVT 트랜지스터를 포함하는 경로에 비하여 줄어든다. 또한, 이러한 이점은 LVT 트랜지스터인 2개의 트랜지스터 22 또는 24 중의 하나만을 갖지만, 그들 양자를 LVT 트랜지스터로 하는 것에 의해 달성되고, 하나만 LVT 트랜지스터이고 나머지는 HVT 트랜지스터이면 전체 직렬 저항이 더 낮은 것에 유의한다. 어떠한 경우에도, 전체 직렬 저항이 줄어들므로, 회로를 방전(즉, 논리 상태를 변경)하기 위해 필요한 시간도 물론 단축된다.

상기 구성이 주어질 때, 당업자는 상이한 임계 전압을 갖는 트랜지스터를 혼합하는 것이 여러 가지 이점을 제공한다는 것을 용이하게 이해할 것이다. 동작의 프리차지 페이즈 동안, 누설 전류가 LVT 트랜지스터만 갖는 회로 이상으로 줄어드는 방전 경로의 HVT 트랜지스터의 이점이 실현된다. 또한, 이 누설은 HVT 트랜지스터만 포함하는 회로의 누설과 비슷하거나 또는 동일하다. 반대 형태에 있어서, 동작의 평가 페이즈 동안, 회로의 논리 상태가 천이할 수 있는 속도가 증가되는 방전 경로의 하나 이상의 LVT 트랜지스터의 이점이 실현된다. 이들 이점에 유의하면, 도 2 내지 도 10의 다음의 설명은 혼합된 임계 전압을 갖는 트랜지스터를 갖는 회로를 고려하여 다른 구성 및 고려 사항을 설명한다.

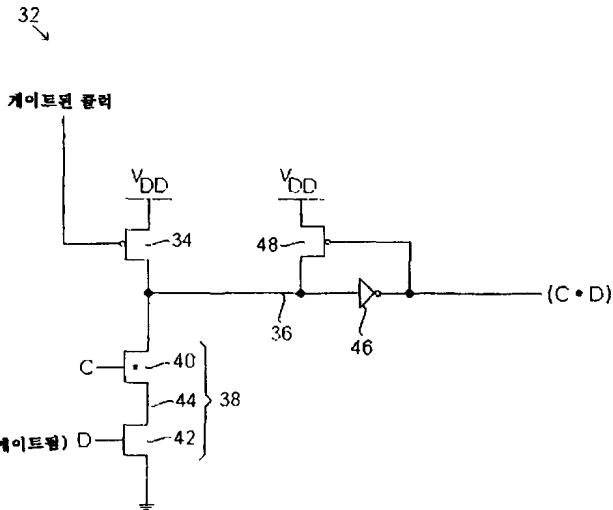

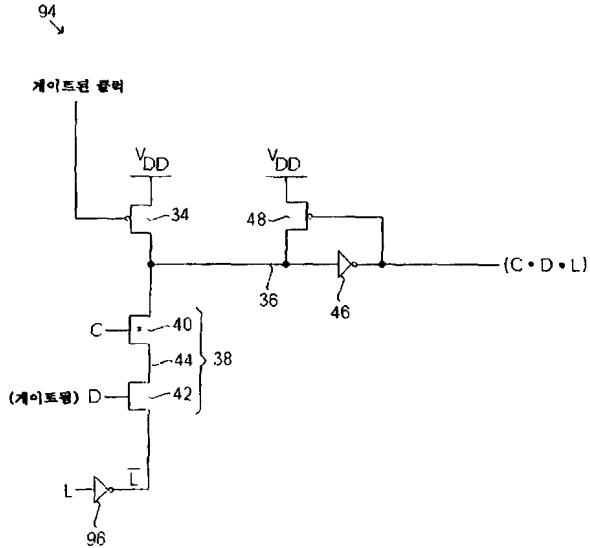

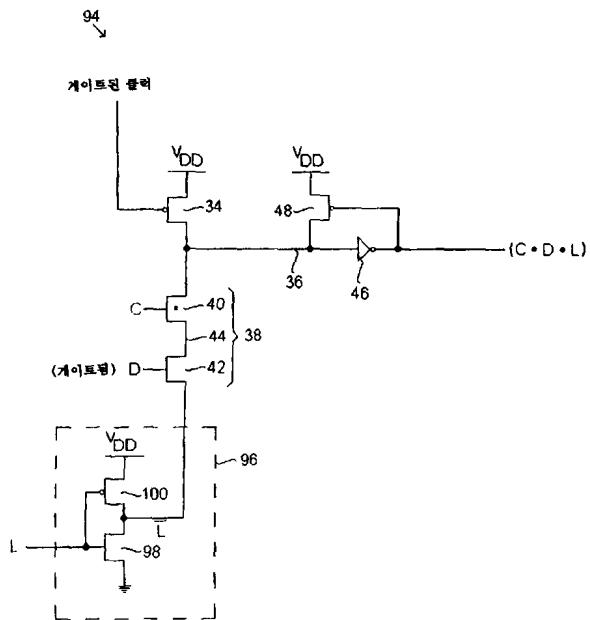

도 2는 클럭된 방전 트랜지스터가 없는 도미노 게이트 구성이라고도 하는 32로 나타낸 제2 동적 논리 회로 실시예의 개략도이다. 회로 32는 p채널 프리차지 트랜지스터(34)의 게이트에 접속된 GATED CLOCK 신호를 포함하고, 상기 p채널 프리차지 트랜지스터는  $V_{DD}$ 에 접속된 소스 및 프리차지 노드(36)에 접속된 드레인을 갖는다. 도 1의 회로 10과 반대로, 도 2의 GATED CLOCK 신호가 n채널 트랜지스터의 게이트에 접속되지 않아 방전 트랜지스터(16)에 대하여 상기 실시예에서 설명한 것과 같은 상보 동작을 일으키는 것에 유의한다.

(38)로 나타낸 논리 회로는 프리차지 노드(36)와 접지 사이에 접속된다. 도 1과 같이, 논리 회로는 여기서 40 및 42로 나타낸 2개의 직렬 접속된 n채널 트랜지스터를 포함한다. 논리 회로(38)의 특정 논리는 C AND D의 논리식을 구현하고, 구체적으로, n채널 트랜지스터(40)의 게이트는 입력 신호 C를 수신하도록 접속되고, n채널 트랜지스터(42)의 게이트는 입력 신호 D를 수신하도록 접속된다. 중요하게는, 입력 신호 D가 게이트된 신호이고 이것은 회로가 그의 평가 페이즈일 때 (즉, GATED CLOCK 신호가 하이일 때) 접속되는 트랜지스터 게이트에 대하여 인에이블될 수 있는 것을 의미하는 것에 유의한다. 따라서, 반대 형태로서, 게이트된 입력 신호 D는 회로가 그의 프리차지 페이즈일 때(즉, GATED CLOCK 신호가 로우일 때) 동일한 트랜지스터에 대하여 논-인에이블되어야 한다. 용어 "논-인에이블(non-enabling)" 또는 "디스에이블(disabling)"은 당분야 공지이고, 게이트 전위가 접속되는 트랜지스터의 도전 경로(즉, 소스/드레인)를 따라 도통을 일으키기에 충분하지 않은 것을 나타낸다. 예를 들면, 회로가 그의 프리차지 페이즈에 있고 트랜지스터 42가 n채널 트랜지스터일 때 게이트된 입력 신호 D가 트랜지스터 42에 대하여 논-인에이블되어야 하므로, GATED CLOCK 신호가 로우일 때 게이트된 입력 신호 D가 로우(n채널 트랜지스터에 대하여 논-인에이블됨, 즉 트랜지스터가 도통하지 않는 레벨)로 되는 것이 알려져 있다. 예를 들면, 게이트된 입력 신호는 도 1의 것과 같은 다른 동적 논리 도미노 게이트 구성의 프리차지 노드 및/

또는 출력에 의해 제공되는 것일 수 있다. 다른 예로서, 게이트된 입력은 정적 논리 회로의 출력에 의해 제공되지만 동작의 프리차지 페이즈 동안 디스에이블되도록 (예를 들면, 다른 신호로 논리 AND에 의해) 제어되는 것일 수 있다. 모든 경우에 있어서, 본 실시예에 대하여 게이트된 입력 신호의 특징의 중요한 점은 다음에 설명된다. 도 2를 계속 설명하면, n채널 트랜지스터(40)의 드레인은 프리차지 노드(36)에 접속되고, n채널 트랜지스터(40)의 소스는 노드 44에 접속된다. n채널 트랜지스터(42)의 드레인은 노드 44에 접속되고, n채널 트랜지스터(42)의 소스는 접지(또는 다음에 설명하는 바와 같이 방전이 허용되도록 전원 전압  $V_{DD}$ 와는 다른 전위)에 접속된다.

프리차지 노드(36)를 다시 보면, 이것은 인버터(46)의 입력에도 접속된다. 인버터(46)의 출력은 회로 32의 출력(즉, C AND D)을 제공하고, p채널 트랜지스터(48)의 게이트에 접속된다. p채널 트랜지스터(48)의 소스는  $V_{DD}$ 에 접속되고 p채널 트랜지스터(48)의 드레인은 프리차지 노드(36)에 접속된다.

도 1의 회로 10과 같이, 도 2의 회로 32에 의해 실현되는 논리식은 도 2의 방법으로 접속된 회로를 포함하는 종래 구성에서와 같지만, 회로의 속도 뿐만 아니라 그의 누설 전류 특징은 상이한 임계 전압을 갖는 상이한 트랜지스터의 포함으로 인해 상당히 상이하다. 설명이 간단하게 되도록, 다음의 설명은 먼저 일반적 논리 동작을 설명하고 다음에 상이한 임계 전압을 갖는 트랜지스터로 인한 회로 변경 및 성능 개선을 상세히 설명한다. 회로 32의 동작을 다시 보면, 이 회로는 동적 논리 회로이고, 따라서, 먼저 프리차지 페이즈에서 동작하고 두 번째로 평가 페이즈에서 동작하며, 이들 페이즈의 선택 및 기간은 GATED CLOCK 신호에 의해 제어된다. 이들 페이즈의 각각은 다음에 설명한다.

회로 32는 GATED CLOCK 신호가 로우일 때 그의 프리차지 페이즈에 있다. 이때, p채널 프리차지 트랜지스터(34)는 도통이고, 그 결과, 프리차지 노드(36)는 회로 32에 대한 하나의 논리 상태를 나타내는  $V_{DD}$ 로 프리차지된다. 회로 32의 예에서,  $V_{DD}$  또는 그것에 가까운 프리차지 전압은 인버터(46)에 의해 반전되고 출력되어 논리 0을 나타낸다(이것은 p채널 트랜지스터(48)를 거쳐 그 레벨로 계속 유지된다). 설명에 앞서서, 입력 신호 D는 게이트된 신호이고, 즉 프리차지 페이즈(즉, GATED CLOCK 신호가 로우임) 동안 인에이블되지 않는 것을 상기한다. 따라서, 프리차지 페이즈 동안 게이트된 입력 신호 D가 로우인 것을 알 수 있다. 그 결과, n채널 트랜지스터(42)는 프리차지 페이즈 동안 도통하지 않는다. 따라서, n채널 트랜지스터(40)가 프리차지 페이즈 동안 도통하더라도, 프리차지 노드(36)의 프리차지 전압은 n채널 트랜지스터(42)의 비도통 상태때문에 방전될 수 없다.

회로 32는 GATED CLOCK 신호가 하이일 때 그의 평가 페이즈에 있다. 따라서, 평가 페이즈의 처음에서, 논리 회로 32는 프리차지 페이즈에 의해 발생된 논리 신호(즉, 이 예에서는 논리 0)를 계속 출력한다. 평가 페이즈 동안 그리고 논리 회로(38) 및 GATED CLOCK 신호에 응답하는 동작으로 인해, 논리 출력 신호는 프리차지 페이즈후 그대로 동일한 상태로 유지되거나 또는 그 대신 반대 논리 상태로 천이할 수 있다. 특히, 로우에서 하이로의 GATED CLOCK 신호의 천이 중 또는 그후에, 논리 회로(38)에 의해 달성되는 논리가 그 회로내 각 트랜지스터를 도통하는 것이면 프리차지 노드(36)의 접지로의 접속이 발생한다. 이 예에서, 논리 동작은 C AND D 이므로, C 입력 신호가 하이이고, 로우에서 하이로 GATED CLOCK 신호의 천이중 또는 그후에 게이트된 입력 신호 D가 로우에서 하이로 상승하면, 논리 회로(38)의 트랜지스터는 도통하여, 프리차지 노드(36)는 접지에 접속된다. 즉, 주어진 이 예에서, 트랜지스터 40 및 42가 도통하는 것에 의해, 프리차지 노드(36)가 접지에 결합되고, 이러한 방법으로 프리차지 전압으로 방전되는 것에 의해 인버터(46)에 의해 제공될 때의 출력 신호는 그의 프리차지 상태(즉, 논리 0)에서 방전 상태로 천이하여 논리 1을 나타내는 출력이 마련된다.

상기 설명은 회로 32가 프리차지 페이즈 동안 제1 논리 상태로 프리차지 되고 나서, 평가 페이즈 동안 그 상태를 유지하거나 또는 논리 회로(38)에 의해 실행되는 논리 동작이 만족되면 평가 페이즈 동안 반대 논리 상태로 논리 천이를 실행하도록 방전될 수 있는 것을 기술한다. 도 1의 회로 10과 같이, 도 2의 회로 32는 상이한 논리 동작을 실행하거나 또는 다른 입력 신호를 추가하거나 또는 제거하도록 논리 회로(38)에 사용되는 트랜지스터 접속 및 종류를 통하여 또 수정될 수 있다. 모든 경우에 있어서, 프리차지 노드(36)에서 상이한 전위로의 경로를 따라 있는 모든 트랜지스터가 도통이면, 프리차지 노드(36)의 전위가 제1 레벨에서 제2 레벨로 변하여 회로 32의 출력에 대한 논리 천이를 나타내도록, 방전 경로를 만드는 것에 유의한다.

이상은 회로 32의 일반적 동작을 설명하였고, 이하는 상이한 임계 전압을 갖는 트랜지스터를 회로가 포함하는 것에 의한 효과에 주의를 기울인다. 특히, 별표가 n채널 트랜지스터(40)에는 도시되어 있지만 n채널 트랜지스터(42)에는 도시되어 있지 않은 것에 유의한다. 따라서, 위에서 도입한 규칙으로부터, n채널 트랜지스터(40)는 LVT 트랜지스터이고, p채널 트랜지스터(42)는 HVT 트랜지스터이다. 또한, 도 2에서와 같은 구성의 트랜지스터의 각각이 동일한  $V_T$ 를 갖도록 구성되었

다는 점에서, 이러한 특징은 순전히 종래 기술과 판판이다. 이러한 특징의 이점을 이해하기 위해, 위에서 상세히 설명된 모든 주된 동작을 다시 언급하지 않고, 회로 동작의 2가지 상이한 페이즈에서 회로 32 내의 상이한 임계 전압 트랜지스터의 상세한 동작을 설명한다.

동작의 프리차지 페이즈 동안, GATED CLOCK 신호는 로우이고, 따라서, n채널 트랜지스터(42)는 p채널 프리차지 트랜지스터(34)가 프리차지 노드(36)를 V<sub>DD</sub>를 향하여 충전시키는 동안 오프이다(그의 입력이 게이트되기 때문에). 입력 신호 C의 데이터값에 따라, n채널 트랜지스터(40)는 온 또는 오프로 된다. 그러나, 최종 트랜지스터에 관계없이, n채널 트랜지스터(42)가 오프이므로 프리차지 노드(36)에서 접지로의 방전은 발생할 수 없다는 것에 유의한다. 또한, n채널 트랜지스터(42)가 HVT 트랜지스터인 것에 유의한다. 또한, HVT 트랜지스터가 오프일 때 (LVT 트랜지스터에 반하여) 더 낮은 누설 전류를 가지므로, HVT n채널 트랜지스터(42)는 프리차지 노드(36)에서 n채널 트랜지스터(40)를 거쳐 접지로 누설되는 전류의 양을 제한한다. 따라서, 방전 경로가 LVT 트랜지스터(즉, n채널 트랜지스터(40))를 포함한다 할지라도, 가능한 누설 전류의 양은 동작의 프리차지 페이즈 동안 HVT n채널 트랜지스터(42)에 의해 제한된다.

동작의 평가 페이즈 동안, GATED CLOCK 신호는 하이이고 n채널 트랜지스터(42)로의 게이트된 입력 신호 D는 로우에서 하이로 천이할 수 있다. 이 천이가 발생하면, 또한 n채널 트랜지스터(40)로의 입력 신호 C도 평가 페이즈 동안 하이이면, 프리차지 노드(36)에서의 전하는 방전 경로(즉, 트랜지스터 40 및 42)를 거쳐 접지로 방전된다. 여기서, 트랜지스터 40이 LVT 트랜지스터이므로, 그의 저항은 HVT 트랜지스터(42)의 저항보다 충분히 작다. 이들 2개의 저항이 직렬이므로, 병진 경로의 전체 저항은 모두 HVT 트랜지스터로 구성된 경로에 비하여 줄어든다. 또한, 전체 직렬 저항이 줄어들므로, 회로가 방전할 수 있는 속도가 증가된다. 마지막으로, 입력 C가 게이트된 입력 신호이고 트랜지스터 40이 HVT 트랜지스터이며 트랜지스터 42가 LVT 트랜지스터이면, 동일하게 저감된 전류 누설 및 직렬 저항이 발생할 수 있다는 것에 유의한다.

따라서, 도 2는 도 1의 다른 예이지만, 양자는 상이한 임계 전압을 갖고 다양한 최종 이점을 갖는 트랜지스터의 혼합을 명료하게 설명한다. 프리차지 페이즈 동안 방전 경로의 하나 이상의 논-인에이블된 HVT 트랜지스터는 누설 전류를 제한하지만, 평가 페이즈 동안 방전 경로의 하나 이상의 LVT 트랜지스터는 동작 속도를 증가시킨다. 도 1 및 도 2 실시예가 상술한 바와 같이 다르지만, 여기서 그들이 공통으로 갖는 것에 유의한다. 먼저, 이들 구성은 방전 경로에 HVT 및 LVT 트랜지스터 모두를 공유한다. 두 번째로, 방전 경로의 적어도 하나의 트랜지스터는 동작의 프리차지 페이즈 동안 인에이블되지 않고, 논-인에이블된 트랜지스터는 HVT 트랜지스터이다. 도 1에서, 이것은 HVT n채널 방전 트랜지스터(16)의 게이트가 프리차지 페이즈 동안 로우로 된다고 알려진 GATED CLOCK 신호에 접속되기 때문에 알 수 있다. 도 2에서, 이것은 HVT n채널 트랜지스터(42)의 게이트가 게이트된 입력 신호에 접속되기 때문에 알 수 있다. 따라서, 방전 경로의 나머지 하나 이상의 트랜지스터는 LVT 트랜지스터를 포함하고, LVT 트랜지스터의 수가 커질수록 속도 성능이 증가할 가능성도 커진다. 지금은 상기 구성을 설명하고 있지만, 도 3 내지 도 10은 위에서 설명된 다양한 원리에 따라 종래 기술 이상의 이점을 갖는 추가 구성을 설명한다.

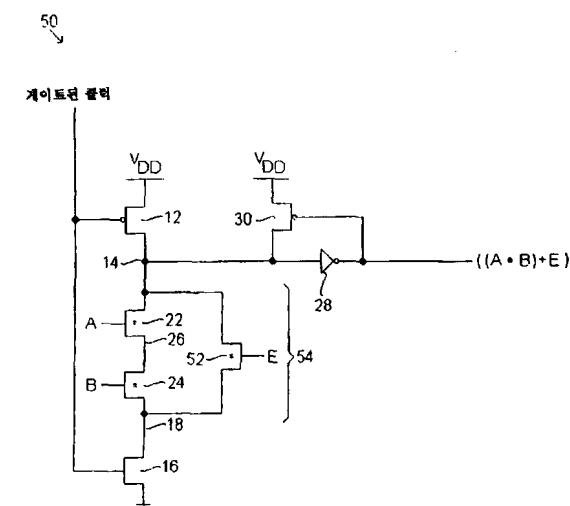

도 3은 도 1의 회로 10과 많은 점에 있어서 동일한 50으로 나타낸 동적 논리 회로 실시예의 개략도이다. 도 1 및 도 3과 공통인 부분에는 동일한 참조 부호가 사용되어 있다. 회로 10과 50의 차이는 회로 50이 프리차지 노드(14)와 노드 18에 접속된 또 하나의 n채널 트랜지스터(52)를 포함하는 것이다. 다음에 설명하는 바와 같이, 이 또 하나의 n채널 트랜지스터는 회로 50에 의해 실행되는 논리식 및 회로 10에 의한 것과 다르게 하므로, 회로 50의 전체 논리 회로도 논리 회로(54)를 나타내도록 번호가 다시 붙여져 있다. 다음에 설명하는 바와 같이, 논리 회로(54)는 회로 50의 출력이 ((A AND B) OR E)와 같도록 논리식을 실행하게 한다. 또한, n채널 트랜지스터(52)가 별표 표시를 가지므로, 본 명세서의 규정에 의해 LVT 트랜지스터인 것에 유의한다. 마지막으로, 회로 50이 2개의 방전 경로, 즉 도 1의 회로 10과 동일하고 n채널 트랜지스터 22, 24 및 16을 포함하는 제1 방전 경로 및 프리차지 노드(14)에서 n채널 트랜지스터 52 및 16을 거치는 제2 방전 경로를 포함하는 것에 유의한다.

회로 50의 동작은 다음과 같다. 먼저, 동작은 n채널 트랜지스터 22, 24 및 16을 통한 제1 방전 경로에 대하여 회로 10과 동일하다. 따라서, 양자는 상기 설명을 참조하기 바란다. 그러나, 두 번째로, n채널 트랜지스터 52 및 16을 통한 제2 방전 경로에 의해 영향을 받는 동작은 다음과 같다.

동작의 프리차지 페이즈 동안, 프리차지 노드(14)는 HVT n채널 방전 트랜지스터(16)가 오프인 동안 프리차지 전압 V<sub>DD</sub>를 향해 프리차지된다. 상술한 바와 같이, HVT n채널 방전 트랜지스터(16)가 오프이므로, 프리차지 노드(14)에서 프리차지된 전압은 제1 방전 경로를 거쳐 방전될 수 없고, 트랜지스터가 HVT 트랜지스터이므로 누설이 제한된다. 여기서, 제2 방전 경로도 HVT n채널 방전 트랜지스터(16)를 반드시 포함하는 것에 유의한다. 따라서, 제1 방전 경로와 같이, 프리차지 노드(14)에서 프리차지된 전압은 제2 방전 경로를 통해 방전될 수 없고, 프리차지 경로에 HVT n채널 방전 트랜지스터(16)가 있음으로 해서 누설은 또 제한된다.

동작의 평가 페이즈 동안, 도 1과 관련하여, 제1 방전 경로가 A AND B의 논리식을 발생시키는 것을 위에서 설명하였다. 그러나, 여기서 n채널 트랜지스터(52)가 도통이면 프리차지 노드(14)에서의 전압이 택일적으로 방전될 수 있는 것에 유의한다. 따라서, 회로 50에 의한 논리 신호 출력은 (A AND B)가 하이이면 또는 E가 하이이면 천이하므로, 전체 논리식은 ((A AND B) OR E)로 된다. 상기로부터 제1 방전 경로에 LVT 트랜지스터(즉, n채널 트랜지스터 22 및 24)가 있는 것이 천이가 발생할 수 있는 속도를 증가시키는 것을 상기한다. 따라서, 마찬가지 이유에 의해, 본 발명 분야의 숙련자는 회로 50의 제2 방전 경로의 LVT 트랜지스터(52)가 그렇지 않으면 논리 천이가 발생할 수 있는 속도를 증가시키는 것을 이해할 것이다.

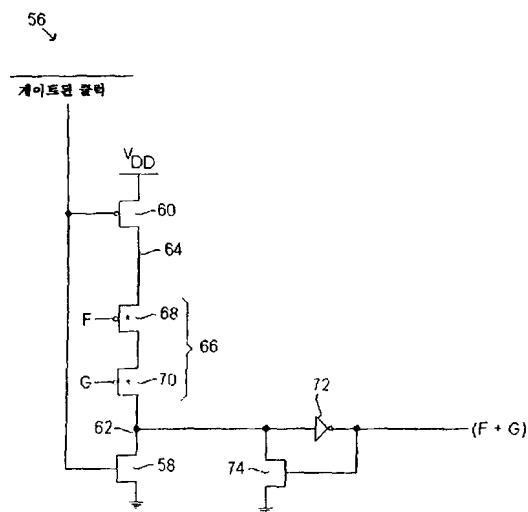

상기 실시예는 프리차지가 방전에 기인하는 전위 보다 높은 전위로 되는 예를 포함하여, 다양한 원리를 설명한다. 그러나, 상술한 바와 같이, 프리차지 전압이 방전 전압보다 적은 다른 구성도 구성할 수 있다. 도 4는 이러한 다른 프리차지 및 방전 동작의 예를 도시하고 p채널 도미노 게이트라고 하는 56으로 나타낸 회로의 개략도이다. 그러나, 또한, 도 4 실시예는 프리차지 노드에서 상이한 전위의 노드로의 방전 경로를 포함하여, 그 경로를 따라 있는 모든 트랜지스터가 도통이면, 프리차지 노드에서의 전위가 제1 레벨에서 제2 레벨로 변함으로써, 회로의 출력에 대한 논리 천이가 표현된다.

회로 56의 상세를 다시 보면, 이 회로는 소스가 프리차지 전압(즉, 접지)에 접속되고 드레인이 프리차지 노드(62)에 접속되어 있는 n채널 프리차지 트랜지스터(58)의 게이트에서 GATED CLOCK 신호의 상보 신호(도 4에서는 GATED CLOCK으로 나타냄)를 수신한다. GATED CLOCK신호도 p채널 방전 트랜지스터(60)의 게이트에 접속되고, 이 트랜지스터는 그의 소스가  $V_{DD}$ 에 접속되고 그의 드레인이 노드 64에 접속되어 있다. p채널 트랜지스터(60)는 별표가 표시되어 있지 않으므로 HVT인 것에 유의한다. 프리차지 노드(62)와 노드 64 사이에는 논리식 ( $F \text{ OR } G$ ) 또는 등가적으로, NOT( $\overline{F}$  AND  $\overline{G}$ )를 구현하는 66으로 나타낸 논리 회로에 접속된다. 논리 회로(66)는 2개의 직렬 접속된 p채널 트랜지스터 68 및 70을 포함하고, p채널 트랜지스터(68)의 게이트는 입력 신호 F를 수신하도록 접속되고, p채널 트랜지스터(70)의 게이트는 입력 신호 G를 수신하도록 접속된다. 양 트랜지스터 68 및 70이 LVT 트랜지스터인 것에 유의한다. 또한, 트랜지스터 60, 68 및 70의 각각이 p채널 트랜지스터이고, 따라서, 본 발명 분야에서 알려진 바와 같이, 부의 게이트 소스간 전압은 n채널 트랜지스터의 경우에서와 같이 정의 게이트 소스간 전압에 반하여 그러한 트랜지스터 종류를 도통으로 하는 것에 유의한다. 따라서, 상대적 임계 전압 레벨에 대하여 말할 때, 이것은 실제로 이슈가 되는 임계 전압의 크기이다. 즉, p채널 HVT 트랜지스터는 -0.5 볼트 정도의  $V_T$ 를 갖고, p채널 LVT 트랜지스터는 -0.2 볼트 정도의  $V_T$ 를 가지며, 따라서, p채널 HVT의  $V_T$ 의 크기는 p채널 LVT 트랜지스터의  $V_T$ 의 크기보다 크다.

프리차지 노드(62)를 다시 보면, 이것은 인버터(72)의 입력에도 접속된다. 인버터(72)의 출력은 회로 56의 출력 신호(즉,  $F \text{ OR } G$ )를 제공하고, n채널 트랜지스터(74)의 게이트에도 접속된다. n채널 트랜지스터(74)의 소스는 접지에 접속되고, n채널 트랜지스터(74)의 드레인은 프리차지 노드(62)에 접속된다.

회로 56의 동작은 프리차지 페이즈 및 평가 페이즈에 걸쳐 발생한다. 프리차지 페이즈 동안, GATED CLOCK 신호는 로우이고, 따라서, 그의 상보 신호는 하이이다. 이때, n채널 프리차지 트랜지스터(58)는 도통이고 p채널 방전 트랜지스터(60)는 도통하지 않는다. 그 결과, 프리차지 노드(62)는 n채널 트랜지스터(58)를 거쳐 접지의 프리차지 전압으로 프리차지되고, 그 프리차지 전압은 인버터(62)에 의해 반전되고 회로 56의 하나의 논리 상태(즉, n채널 트랜지스터(74)로의 피드백 접속에 의해 유지되는 논리 1)를 나타낸다. 평가 페이즈 동안, GATED CLOCK 신호는 하이이고, 따라서, 그의 상보 신호는 로우이다. 따라서, 평가 페이즈의 초기에, 논리 회로(66)는 프리차지 페이즈에 의해 발생된 논리 신호(즉, 이 예에서는 논리 1)를 계속 출력한다. 그러나, 논리 회로(66) 및 GATED CLOCK 신호의 상보 신호에 응답하는 동작으로 인해, 그 논리 출력 신호는 프리차지 페이즈 후의 것과 동일한 상태로 유지되거나 또는 그 대신 반대 논리 상태로 천이할 수 있다. 특히, 하이에서 로우로의 GATED CLOCK 신호의 상보 신호의 천이에 응답하여, p채널 방전 트랜지스터(60)는 도통하지만 n채널 프리차지 트랜지스터(58)는 도통하지 않는다. 그 결과, 프리차지 노드(62)는 논리 회로(66) 및 p채널 방전 트랜지스터(60)를 거쳐  $V_{DD}$ 에 접속될 수 있다. 따라서, 이 페이즈 동안, 논리 회로(66) 내의 각 트랜지스터가 도통이면  $V_{DD}$ 로의 접속이 발생한다. 즉, F 및 G 입력 신호 모두가 로우이면, 트랜지스터 68 및 70은 각각 도통하여  $V_{DD}$ 로의 상기의 접속이 허용된다. 그 결과, 프리차지 노드(62)에서의 프리차지 전압(즉, 도 4의 예에서는 접지)은  $V_{DD}$ 를 향해 방전되는 것이 허용된다. 이 방법으로 프리차지 노드(62)를 방전하는 것에 의해, 프리차지 노드(62)의 전압이  $V_{DD}$  또는 그의 가까이에 도달하고 나서 인버터(72)에 의해 반전되는 것에 유의한다. 따라서, 회로 56의 예에서, 이 방법으로의 방전은 논리 1에서 논리 0으로의 회로 56의 논리값의 천이를 나타낸다.

방금 설명한 동작에 부가하여, 회로 56이 프리차지 노드(62)와  $V_{DD}$  사이의 방전 경로에 LVT 및 HVT 트랜지스터 모두를 포함하는 것에서 이점을 갖는 것에 유의한다. 이러한 동작의 상세는 독자가 참조하는 상기 도면의 설명에서 용이하게 이해되고 다음에 간단히 언급된다. 동작의 프리차지 페이즈 동안, p채널 방전 트랜지스터(60)는 오프이고, HVT 트랜지스터로서, 방전 경로를 통해 누설할 수 있는 전류의 양을 제한한다. 그러나, 평가 페이즈 동안, p채널 트랜지스터 68 및 70은 (그들 각각의 입력이 로우이면) 도통하고, LVT 트랜지스터로서, 그들은 모두 HVT 트랜지스터를 포함하는 경로에 비하여 방전 경로의 속도를 증가시킨다. 따라서, 도 4 실시예는 종래 기술 보다 현저한 개선점을 제공한다.

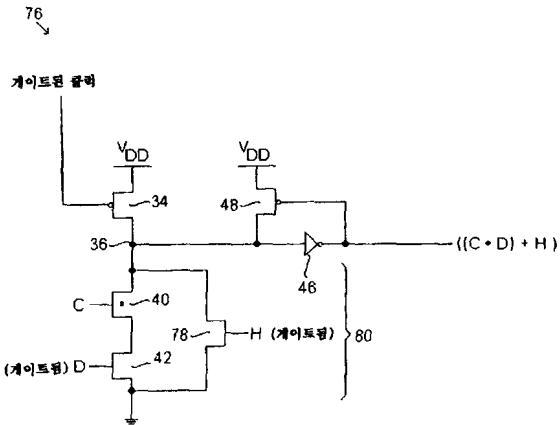

도 5는 하나이상의 방전 경로를 포함하고 76으로 나타낸 동적 논리 회로 실시예의 개략도이다. 특히, 회로 76은 도 2의 회로 32와 많은 점에 있어서 동일하다. 따라서, 도 2 및 도 5에서 공통으로 사용되는 부분에는 동일한 참조 부호가 사용되어 있다. 회로 32의 특징에 부가하여, 회로 76은 또 하나의 n채널 트랜지스터(78)을 포함하고, 이 트랜지스터의 게이트는 게이트된 입력 신호 H를 수신하도록 접속되고, 드레인 및 소스는 각각 프리차지 노드(36) 및 접지에 접속되어 있다. 따라서, 상이한 논리 회로(80)이 직렬 접속된 트랜지스터 40 및 42와 병렬로 트랜지스터(78)에 의해 형성되고, 본 발명 분야의 숙련자는 이 논리가 회로 76이 ((C AND D) OR H)의 논리 출력식을 실현하게 하는 것을 이해할 것이다.

상기의 회로 76의 접속이 주어질 때, 프리차지 노드(36)에서 상이한 전위(즉, 이 예에서는 접지)로 2개의 분리된 방전 경로가 제공되는 것에 유의한다. 제1 방전 경로는 도 2의 회로 32에서와 동일, 즉 프리차지 노드(36)에서 직렬 접속된 트랜지스터 40 및 42를 거친다. 새로 추가된 제2 프리차지 경로는 프리차지 노드(36)에서 트랜지스터(78)를 거쳐 접지로의 경로이다. 또한, n채널 트랜지스터(78)에는 별표가 없으므로 HVT 트랜지스터인 것에 유의한다. 또한, 상기 설명이 주어질 때, 제2 방전 경로가 하나의 트랜지스터만을 포함하고 따라서 그 트랜지스터가 프리차지 페이즈 동안 인에이블되지 않는 HVT 트랜지스터인 것이 바람직하며 동작의 프리차지 페이즈 동안 전류 누설을 제한하는 것에 유의한다. 또한, 회로 76의 제2 방전 경로에는 LVT 트랜지스터가 없지만, 제1 경로에는 LVT 트랜지스터(즉, 트랜지스터 40)가 있는 것에 유의한다. 그 결과, 제1 경로의 방전 속도는 HVT 트랜지스터만을 갖는 경로 이상으로 향상된다. 또한, 제2 방전 경로가 제1 방전 경로와 병렬이고, 따라서 그것이 도통일 때 제1 방전 경로의 저항이 저감되는 것에 의해 그것이 또한 도통일 때 제2 방전 경로의 속도를 향상시킬 수 있는 것에 유의한다. 따라서, 모든 경우에 있어서, 도 5의 회로는 종래 기술 이상의 개선을 제공한다.

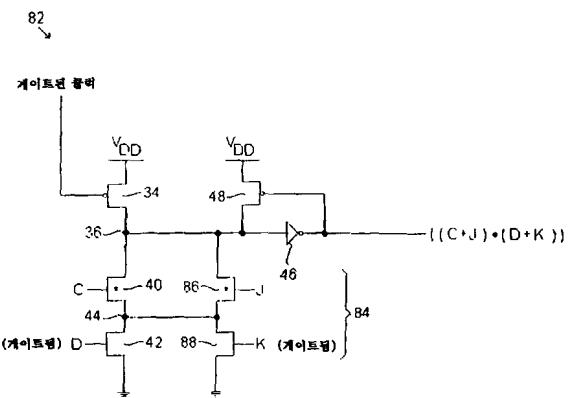

도 6은 논리 회로(84)를 포함하고 82로 나타낸 동적 논리 회로 실시예의 개략도이다. 회로 82는 도 2의 회로 32와 공통 부분을 공유하므로, 이 예에서도 동일한 참조 부호를 사용한다. 회로 84는 프리차지 노드(36)에서 접지로의 직렬 접속된 트랜지스터 40 및 42의 접속을 포함한다. 그러나, 논리 회로(84)는 프리차지 노드(36)에서 접지로 직렬 접속된 제2 세트의 n채널 트랜지스터 86 및 88을 포함하고, 트랜지스터(86)는 그의 게이트에서 입력 신호 J를 수신하고, 트랜지스터(88)는 그의 게이트에서 게이트된 입력 신호 K를 수신한다. 마지막으로, 트랜지스터 40 및 42를 접속하는 노드 44가 트랜지스터 86과 88 사이에도 접속되는 것에 유의한다.

회로 82는 방전 경로의 또 다른 예를 설명하는 것으로, 여기서, 방전은 프리차지 노드(36)에서 접지로 4가지 방법, 즉 (1) 트랜지스터 40 및 42를 거쳐, (2) 트랜지스터 86 및 88을 거쳐, (3) 트랜지스터 40 및 88을 거쳐, 그리고 (4) 트랜지스터 86 및 42를 거치는 방법 중의 하나로 실제로 발생할 수 있다. 따라서, 본 발명 분야의 숙련자는 회로 82가 ((C OR J) AND (D OR K))의 논리 출력식을 실현하는 것을 이해할 것이다. 각 방전 경로의 HVT 및 LVT 트랜지스터를 조합하는 것에 관한 상기 원리에 따라, n채널 트랜지스터(40)가 LVT 트랜지스터이고, 따라서 그 LVT 트랜지스터를 포함하는 각 방전 경로에 대하여, 프리차지 페이즈 동안 오프되는 HVT 트랜지스터가 있는 것이 바람직하다는 것을 상기한다. 그 결과, n채널 트랜지스터(42)는 HVT 트랜지스터이고, n채널 트랜지스터(88)도 마찬가지이다. 따라서, 누설이 n채널 트랜지스터(42) 또는 n채널 트랜지스터(88)를 통해 발생하는 거의 여부에 관계없이, 그 누설은 HVT 트랜지스터의 존재에 의해 제한된다. LVT n채널 트랜지스터(40)에 대한 것과 마찬가지 이유로 인해, n채널 트랜지스터(86)를 포함하는 각 방전 경로도 n채널 트랜지스터(42) 또는 n채널 트랜지스터(88)를 포함하고, 따라서 n채널 트랜지스터(86)도 LVT 트랜지스터일 수 있는 것에 유의한다. 또한, 트랜지스터 40 및 86의 각각이 게이트된 입력 신호를 수신하도록 모두 접속되면, 트랜지스터 42 및 88은 LVT 트랜지스터이고, 트랜지스터 40 및 86은 HVT 트랜지스터이며, 또한 종래 기술 이상으로 성능이 개선되는 것에 유의한다. 마지막으로, 4개 트랜지스터 40, 42, 86 및 88 모두가 게이트된 입력을 수신하도록 접속되면, 트랜지스터 40과 86 또는 트랜지스터 42와 88 중의 하나는 HVT 트랜지스터이고 대향하는 트랜지스터 쌍은 LVT 트랜지스터이다.

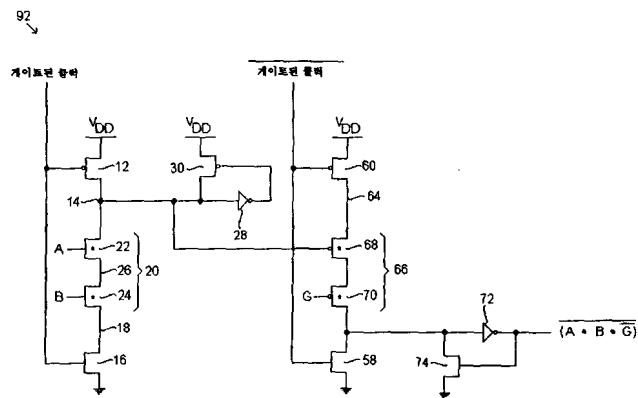

도 7은 92로 나타낸 소위 지퍼 논리 회로(zipper logic circuit)의 개략도이다. 회로 92 등의 지퍼 논리는 하나의 단이 다른 단을 구동하도록 접속된 연속하는 동적 논리 회로단에 특징이 있고, 여기서 제1 동적 논리 회로는 제1 도전형의 방전 경로 트랜지스터를 갖고, 제2 도전형의 방전 경로 트랜지스터를 갖는 제2 동적 논리 회로를 구동한다. 회로 92의 예에서, 제1 동적 논리 회로는 그의 방전 경로에 n채널 트랜지스터를 포함하고, 제2 동적 논리 회로는 그의 방전 경로에 p채널 트랜-

지스터를 포함한다. 또한, 위에서 상세히 설명하고 많은 예가 주어진 현재의 예가 단순하게 되도록, 회로 92는 일반적으로 각각 도 1 및 도 4의 회로 10 및 56을 결합하고, 따라서 이들 도면에서의 참조 부호가 도 7에도 사용되는 것에 유의한다. 그러나, 도 7의 전체 회로는 회로 10의 프리차지 노드(14)가 회로 56의 트랜지스터(68)에 게이트된 입력을 제공하도록 구성되는 것에 유의한다. 즉, 지폐 회로의 경우, 다음 단(들)으로의 입력의 적절한 천이가 확립되도록 회로내의 다음 단으로의 입력으로서 접속되기 전에 프리차지 노드 신호의 반전이 없다는 것에 유의한다.

상기 회로가 주어질 때, 본 발명 분야의 숙련자는 회로 92가 ( $\overline{A AND B}$ ) OR G)의 논리 출력식 또는 그와 등가로 NOT(A AND B AND  $\overline{G}$ )의 식을 실현하는 것을 이해할 것이다. 또한, 회로 92의 각 단은 상기의 방법에 있어서 이점이 있다. 특히, GATED CLOCK이 하이일 때, 양단은 동작의 프리차지 페이즈에 있고, HVT n채널 방전 트랜지스터(16)는 첫 번째 단의 누설 전류를 제한하고, HVT p채널 방전 트랜지스터(60)는 두 번째 단의 누설 전류를 제한한다. 또한, GATED CLOCK이 하이일 때, 양단은 동작의 평가 페이즈에 있고, LVT n채널 트랜지스터 22 및 24는 첫 번째 단의 동작 속도를 개선하고, p채널 트랜지스터 68 및 70은 두 번째 단의 동작 속도를 물론 개선할 것이다.

도시하고 상술한 바와 같이, 도 7 실시예의 하나의 단은 하나의 도전형의 방전 트랜지스터를 갖고, 다른 단은 다른 도전형의 방전 트랜지스터를 갖는다. 이것에 대하여, 주어진 트랜지스터가 동일한 도전형의 다른 트랜지스터에 대하여 LVT 또는 HVT로 되는 것에 유의한다. 예를 들면, n채널 트랜지스터 22 및 24는 HVT 트랜지스터(16)에 대하여 LVT이고, 트랜지스터(16)도 동일한 도전형(즉, n채널)이다. 마찬가지로, p채널 트랜지스터 66 및 68은 HVT 트랜지스터(60)에 대하여 LVT이고, 트랜지스터(60)도 동일한 도전형(즉, p채널)이다. LVT p채널 트랜지스터의  $V_T$ 의 크기가 LVT n채널 트랜지스터의  $V_T$ 의 크기와 다를 수 있고, 마찬가지로, HVT p채널 트랜지스터의  $V_T$ 의 크기가 HVT n채널 트랜지스터의  $V_T$ 의 크기와 다를 수 있으므로, 트랜지스터들이 이 방법으로(즉, 공통 도전형에 의해) 특징지워지는 것에 유의한다.

진행에 앞서, 회로 92가 다른 예를 형성하도록 수정될 수 있는 것에 유의한다. 구체적으로, 트랜지스터(68)로의 입력이 도시한 방법으로 동적 논리 회로 92에서 오므로, 입력값이 게이트된 신호를 나타내는 것, 즉 프리차지 페이즈 동안 논-인에이블인 것을 알 수 있다. 즉, 도시한 예에 대하여, 프리차지 페이즈 동안, 트랜지스터(68)로의 입력은 하이이고, 하이 신호는 p채널 트랜지스터에 대하여 논-인에이블된다. 따라서, p채널 트랜지스터가 프리차지 페이즈 동안 오프로 되는 것을 알 수 있다. 그 결과, 다른 예는 그의 목적이 프리차지 페이즈 동안 방전을 방지하는 것뿐이므로, 또한 p채널 트랜지스터(68)가 프리차지 동안 오프로 되고 따라서 같은 목적을 위해 기능하기 때문에 방전 트랜지스터(60) 및  $V_{DD}$ 로의 직접 노드 64를 제거한다. 또한, 상기의 원리에 부합하도록, 이 변경예가 이루어지면, p채널 트랜지스터(68)는 도시한 LVT 트랜지스터에 반대인 HVT 트랜지스터여야 한다. 이러한 방법으로 트랜지스터의  $V_T$ 를 변경하는 것에 의해, 방전 경로가 동작의 프리차지 페이즈 동안 오프인 것으로 알고 있는 HVT 트랜지스터를 포함하는 것이 재차 보장된다.

도 8a는 도 2의 회로 32와 일부의 부분(동일한 참조 숫자로 나타냄)을 공유하고 94로 나타낸 다른 실시예의 개략도이다. 구체적으로, 회로 94에서, 인버터(96)의 출력은 n채널 트랜지스터(42)의 소스에 접속되지만, 도 2의 나머지 접속은 회로 94에 대하여 이루어진다. 설명을 목적으로, 인버터(96)는 그의 입력에서 입력 신호 L을 수신하고, 따라서, L의 상보 신호는 n채널 트랜지스터(42)의 소스에 접속된다. 다음의 도 8b에 도시한 바와 같이, 인버터(96)는 공지의 기술에 따라 구성되면 이전 도면에서 설명된 원리의 응용을 발생시키는 방전 경로를 제공할 수 있다. 따라서, 인버터(96)가 도 8a의 회로 94의 나머지 부분에 매우 근접하지 않은 물리적 위치에 구성될 수 없더라도, 그 회로는 다음에 설명하는 바와 같이 상이한 임계 전압을 갖는 상이한 트랜지스터의 조합으로부터 이익을 얻는다.

도 8b는 도 8a를 반복하지만, 인버터의 공지 개념에 따라 인버터(96)의 구성 요소를 상세히 도시하고 있다. 특히, 인버터(96)의 입력은 n채널 트랜지스터(98)의 게이트에 접속된다. n채널 트랜지스터(98)의 소스는 접지에 접속되고, 그의 드레인은 인버터(96)의 출력에 접속된다. 또한, 인버터(96)는 p채널 트랜지스터(100)를 포함하고, 이 트랜지스터의 소스는  $V_{DD}$ 에 접속되고, 그의 드레인은 인버터(96)의 출력에 접속되며, 그의 게이트는 인버터(96)의 입력에 접속되어 있다.

인버터(96)의 구조를 알고 있다고 이미 언급하였지만, 도 8a 및 도 8b의 나머지 회로와 조합하여 트랜지스터 임계 전압을 특별히 선택하는 또 다른 신규한 실시예를 제공한다. 특히, n채널 트랜지스터(98)가 프리차지 노드(36)에서 n채널 트랜지스터 40 및 42, 최종적으로 n채널 트랜지스터(98)를 거치는 방전 경로를 완성하는 것에 유의한다. 인버터(96)에 의해 만들어진 방전 경로가 주어질 때, 위에서 설명한 다양한 원리는 회로 94에 적용될 수 있다. 예를 들면, 인버터(96)로의 입력 신호 L이 게이트된 신호이면, n채널 트랜지스터(98)가 회로 94의 동작의 프리차지 페이즈 동안 오프로 되는 것을 알 수 있다. 그 때, 하나의 실시예는 HVT 트랜지스터로서 n채널 트랜지스터(98)를 포함하고, n채널 트랜지스터 40 및 42의 각각은 LVT 트랜지스터이다. 다른 예로서, 인버터(96)로의 입력 신호 L이 게이트된 신호가 아니면, n채널 트랜지스터(98)는 동작의 프리차지 페이즈 동안에 있게 되므로, 방전 경로에서 게이트된 입력 신호를 갖는 상이한 트랜지스터(즉, 이 예에서는 n

채널 트랜지스터(42)가 HVT 트랜지스터이고, n채널 트랜지스터(98)이외의 나머지 트랜지스터는 LVT 트랜지스터로 될 수 있다. 후자의 경우, 게이트된 입력 HVT 트랜지스터(예를 들면 n채널 트랜지스터(42))에 의해 마련되는 전류 제한에도 불구하고, 인버터(96)의 n채널 트랜지스터(98)는 L의 값이 로우일 때 인버터(96) 내의 전류 누설을 제한하도록 여전히 HVT 트랜지스터인 것이 바람직하다. 따라서, 모든 경우에 있어서, 도 8a 및 도 8b는 이 실시예가 동작의 프리차지 페이즈 동안 HVT 트랜지스터에 의한 전류 누설 제한 및 동작의 평가 페이즈 동안 하나이상의 LVT 트랜지스터에 기인하는 속도 향상을 제공하는 또 다른 예를 도시하고 있다.

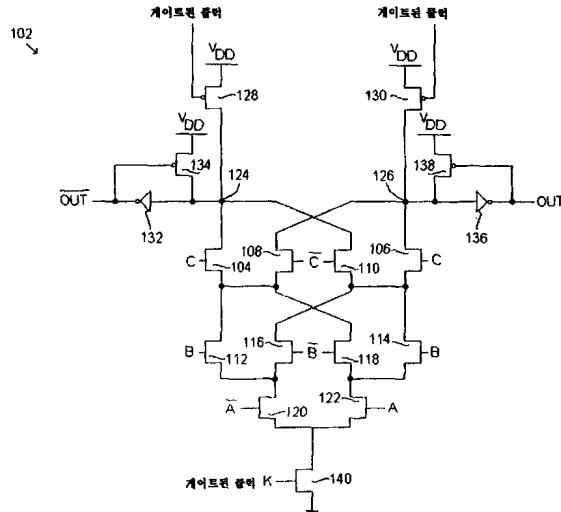

도 9는 듀얼 레일 도미노 게이트 구성(dual-rail domino gate configuration)으로 알려진 것으로 구성되고 102로 나타낸 다른 실시예의 개략도이다. 회로 102는 다음에 기술하는 바와 같이 평가 페이즈 동안 그의 2개의 출력 중 하나만 천이하도록 동작한다. 회로 102의 구성 요소 및 접속을 다시 보면, A 및  $\bar{A}$ , B 및  $\bar{B}$ , C 및  $\bar{C}$ 로 나타낸 상보 신호 입력을 수신하는 것에 유의한다. 신호 C는 n채널 트랜지스터 104 및 106의 게이트에 접속되고, 신호  $\bar{C}$ 는 n채널 트랜지스터 108 및 110의 게이트에 접속된다. 신호 B는 n채널 트랜지스터 112 및 114의 게이트에 접속되고, 신호  $\bar{B}$ 는 n채널 트랜지스터 116 및 118의 게이트에 접속된다. 마지막으로, 신호  $\bar{A}$ 는 n채널 트랜지스터(120)의 게이트에 접속되고, 신호 A는 n채널 트랜지스터(122)의 게이트에 접속된다.

트랜지스터에 접속된 입력 신호에 부가하여, 회로 102는 다음을 포함하는 여러 가지 다른 트랜지스터 및 접속을 포함한다. 회로 102는 제1 프리차지 노드(124) 및 제2 프리차지 노드(126)를 포함한다. 제1 프리차지 노드(124)는 p채널 트랜지스터(128)의 드레인에 접속되고, 이 트랜지스터의 소스는  $V_{DD}$ 에 접속되고, 그의 게이트는 GATED CLOCK 신호에 접속되어 있다. 마찬가지로, 제2 프리차지 노드(126)는 p채널 트랜지스터(130)의 드레인에 접속되고, 이 트랜지스터의 소스는  $V_{DD}$ 에 접속되고, 그의 게이트는 GATED CLOCK 신호에 접속되어 있다. 제1 프리차지 노드(124)는 p채널 트랜지스터(134)의 드레인 뿐만 아니라 인버터(132)의 입력에도 접속된다. p채널 트랜지스터(134)의 소스는  $V_{DD}$ 에 접속되고, 그의 게이트는 인버터(132)의 출력에 접속된다. 인버터(132)의 출력은 회로의 상보 출력(도 9에서는  $OUT$ 로 도시함)을 제공한다. 제2 프리차지 노드(126)는 p채널 트랜지스터(138)의 드레인 뿐만 아니라 인버터(136)의 입력에도 접속된다. p채널 트랜지스터(138)의 소스는  $V_{DD}$ 에 접속되고, 그의 게이트는 인버터(136)의 출력에 접속된다. 인버터(136)의 출력은 회로의 정 논리 출력(도 9에서는 OUT로 도시함)을 제공한다.

회로 102의 나머지 접속은 다양한 방전 경로를 제공한다. 이를 경로를 지정하기 전에, 회로 102가 프리차지 노드에서 접지로의 각 방전 경로에 공통인 n채널 방전 트랜지스터(140)를 포함하는 것에 유의한다. 특히, 회로 102의 각 프리차지 노드는 4개의 방전 경로에 의해 접지에 결합된다. 제1 프리차지 노드(124)에서 접지로의 4개의 방전 경로는 제1 프리차지 노드(124)에서, 다음의 4가지 중의 하나, 즉 (1) n채널 트랜지스터(104), n채널 트랜지스터(112), n채널 트랜지스터(120), n채널 트랜지스터(140), (2) n채널 트랜지스터(110), n채널 트랜지스터(116), n채널 트랜지스터(120), n채널 트랜지스터(140), (3) n채널 트랜지스터(104), n채널 트랜지스터(118), n채널 트랜지스터(122), n채널 트랜지스터(140), (4) n채널 트랜지스터(110), n채널 트랜지스터(114), n채널 트랜지스터(122), n채널 트랜지스터(140)의 경로를 거친다. 어떠한 경우에도, 제1 프리차지 노드(124)가 방전하면, 회로 102의 반전된 출력(즉,  $OUT$ )은 천이하지만, 회로 102의 비반전된 출력(즉, OUT)은 프리차지된 레벨을 유지한다. 반대 형태에 있어서, 제2 프리차지 노드(126)에서 접지로의 4개의 방전 경로는 제2 프리차지 노드(126)에서, 다음의 4가지 중의 하나, 즉 (1) n채널 트랜지스터(106), n채널 트랜지스터(114), n채널 트랜지스터(122), n채널 트랜지스터(140), (2) n채널 트랜지스터(108), n채널 트랜지스터(118), n채널 트랜지스터(122), n채널 트랜지스터(140), (3) n채널 트랜지스터(106), n채널 트랜지스터(116), n채널 트랜지스터(120), n채널 트랜지스터(140), (4) n채널 트랜지스터(108), n채널 트랜지스터(112), n채널 트랜지스터(120), n채널 트랜지스터(140)의 경로를 거친다. 마지막으로, 제2 프리차지 노드(126)가 방전하면, 회로 102의 비반전된 출력(즉, OUT)은 천이하지만, 회로 102의 반전된 출력(즉,  $OUT$ )은 프리차지된 레벨을 유지한다.

여기서는 해석을 상세히 설명하고 있지는 않지만, 본 발명 분야의 숙련자는 회로 102가 입력 신호 A, B, 및 C에 대하여 배타적 OR 게이트를 제공하는 기술이 결정되는 것을 인식할 것이다. 그의 다양한 방전 경로가 주어질 때, 상기의 원리는 회로 102에 적용되어, 입력 신호(비반전된 또는 상보 신호)를 수신하도록 결합되는 회로의 트랜지스터의 임계 전압에 대하여 다양한 대안이 제공될 수 있다. 따라서, 수많은 다른 변경때문에 도 9에서는 별표가 도시되어 있지 않다. 예를 들면, 트랜지스터 140이 HVT 트랜지스터이면, 입력 신호를 수신하도록 결합된 회로 102의 나머지 트랜지스터는 LVT 트랜지스터인 것이 바람직하다. 그러나, 트랜지스터 140은 신호 및 그의 상보 신호가 게이트되는 것을 알고 있으면(즉, 프리차지 페이즈 동안 논-인에이블됨) 회로 102에서 제거될 수 있다. 이 때, 회로 102는 입력 신호(비반전 것과 반전된 것) 중의 어느 것이 게이트되는 가에 따라 상이한 방법으로 수정될 수 있다. 예를 들면, 입력 신호 C 및  $\bar{C}$ 가 게이트된 입력 신호이면,

트랜지스터 104, 106, 108 및 110은 HVT 트랜지스터인 것이 바람직하고, 입력 신호를 수신하도록 결합된 회로 102의 나머지 트랜지스터는 LVT 트랜지스터이다. 다른 예로서, 입력 신호 B 및  $\bar{B}$ 가 게이트된 입력 신호이면, 트랜지스터 112, 114, 116 및 118은 HVT 트랜지스터인 것이 바람직하고, 입력 신호를 수신하도록 결합된 회로 102의 나머지 트랜지스터는 LVT 트랜지스터이다. 또 다른 예로서, 입력 신호 A 및  $\bar{A}$ 가 게이트된 입력 신호이면, 트랜지스터 120 및 122는 HVT 트랜지스터인 것이 바람직하고, 입력 신호를 수신하도록 결합된 회로 102의 나머지 트랜지스터는 LVT 트랜지스터이다.

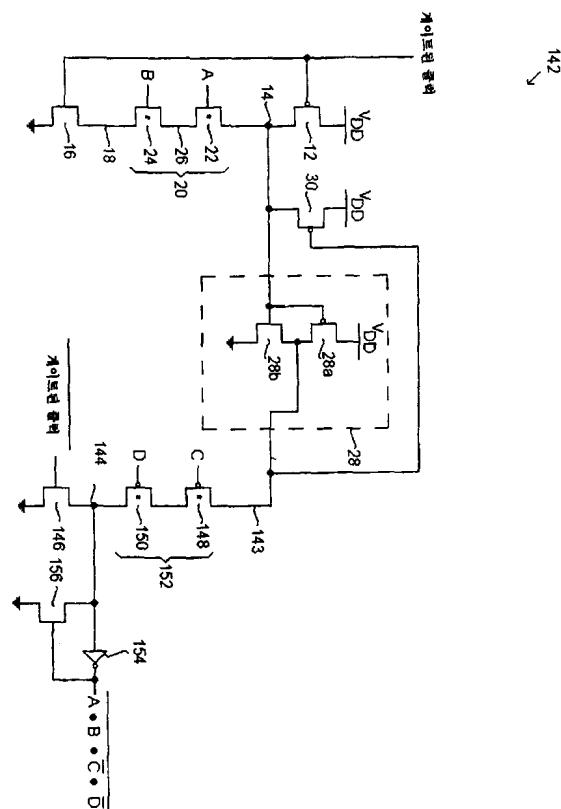

도 10은 종래에는 어떠한 형태로든 존재한다고 알려져 있지 않은 142로 나타낸 동적 논리 회로의 개략도이다. 도 10이 전위 방전 경로를 다음 p채널 도미노단에 제공하는 n채널 도미노단의 출력을 갖는 것에 유의한다. 특히, 도 10의 n채널 도미노단은 도 1의 회로 10과 동일하므로, 도 1 내지 도 10에서와 동일한 부분에는 동일한 부호를 사용한다. 그러나, 도 1의 인버터(28)가 p채널 트랜지스터(28a) 및 n채널 트랜지스터(28b)를 포함하도록 더욱 상세히 도시되어 있는 것에 유의한다. p채널 트랜지스터(28a)에 대하여, 그의 소스는  $V_{DD}$ 에 접속되고, 그의 드레인은 제1 단의 출력(143)에 접속되며, 그의 게이트는 프리차지 노드(14)에 접속된다. n채널 트랜지스터(28b)에 대하여, 그의 소스는 접지에 접속되고, 그의 드레인은 제1 단의 출력(143)에 접속되며, 그의 게이트는 프리차지 노드(14)에 접속된다. 인버터(28)를 상세히 도시한 이유는 회로 142의 동작과 관련하여 이하를 더욱 잘 이해하기 위함이다.

회로 142의 제2 단은 n채널 프리차지 트랜지스터(146)를 거쳐 접지에 접속된 프리차지 노드(144)를 포함한다. 제1 단의 출력(143)과 프리차지 노드(144) 사이에는 입력 신호 C 및 D를 각각 갖는 2개의 p채널 트랜지스터 148 및 150이 접속된다. 따라서, 트랜지스터 148 및 150은 제2 단의 논리 회로를 형성하고 152로 나타낸다. 프리차지 노드(144)는 회로 142의 전체 출력을 제공하는 인버터(154)의 입력에 접속된다. 마지막으로, 회로 142의 출력은 n채널 트랜지스터(156)의 게이트에 접속되고, 그 트랜지스터의 소스는 접지에 접속되고, 그의 드레인은 프리차지 노드(144)에 접속되어 있다.

회로 142의 동작은 다음과 같다. 도 1의 설명을 상기할 때, 논리식 ( $A \text{ AND } B$ )가 실현되는 것을 알 수 있다. 그러나, 그 회로가 방전될 때, 인버터(28)가 출력(143)을 p채널 트랜지스터(28a)를 통해  $V_{DD}$ 로 하는 것에 유의한다. 이것이 발생하면 또한 회로 142의 제2 단의 양 트랜지스터 148 및 150이 도통이면, 프리차지 노드(144)는  $V_{DD}$ 를 향해 접지로부터 방전된다. 따라서, 인버터(28)는 프리차지 노드(144)에서  $V_{DD}$ 로의 방전 경로의 일부를 제공할 수 있다. 또한, 동작의 프리차지 페이즈 동안, 프리차지 노드(114)는 하이이고, 따라서 p채널 트랜지스터(28a)는 인에이블되지 않는다. 이들 관찰 결과 및 위에서 설명된 여러 원리를 주어질 때, p채널 트랜지스터(28a)가 동적 논리 회로의 방전 경로에 위치한 HVT 트랜지스터이고 동작의 프리차지 페이즈 동안 논-인에이블되는 것에 유의한다. 따라서, 그 방전 경로의 나머지 트랜지스터(즉, 트랜지스터 148 및 150)는 LVT 트랜지스터인 것에 의해, 상기의 방법에서와 같이 성능이 개선될 수 있다. 마지막으로, 본 발명 분야의 숙련자는 회로 142가 논리식 ( $\text{NOT}(A \text{ AND } B \text{ AND } \bar{C} \text{ AND } \bar{D})$ )를 실현하는 것을 이해할 것이다.

상기로부터, 본 발명 분야의 숙련자는 적어도 하나의 HVT 트랜지스터가 동작의 프리차지 페이즈 동안 인에이블되지 않는 것을 알고 있을 때, 이 절의 실시예가 동적 논리 회로의 방전 경로에 적어도 하나의 HVT 트랜지스터 및 하나의 LVT 트랜지스터를 포함하는 것에 의해 이점을 얻는 다양한 회로를 설명하는 것을 이해할 것이다. 또한, HVT 트랜지스터에 대하여, 이것이 프리차지 페이즈 동안 전류 누설 제한과 관련하여, 즉 프리차지 페이즈 동안 인에이블되지 않는 소자를 통한 전류를 제한하도록 포함되는 것을 이해할 것이다. 또한, 또 다른 고려 사항으로서, 다른 트랜지스터도 프리차지 페이즈 동안 도통하는 것을 알 수 있다는 것에 유의한다. 이들 다른 트랜지스터에 대하여, 정의에 의해, 이들 다른 트랜지스터가 그러한 시간 동안 도통하므로 누설은 상관없다. 그 결과, 그러한 다른 트랜지스터(예를 들면, 도 1의 프리차지 트랜지스터(12), 여러 도면에 도시된 인버터(28)의 n채널 트랜지스터)도 LVT 트랜지스터로 구성되어 누설에 관계없이 그러한 트랜지스터의 동작 속도를 증가시킬 수 있다. 또한, 이상은 다양한 실시예를 설명하고 있지만, 다른 예들도 본 발명 분야의 숙련자에 의해 예상될 수 있다.

## 2. 로우 임계 저압을 갖는 캐스코드 트랜지스터를 사용하는

### 동적 논리 회로, 시스템 및 방법

도 11a, 도 11b 및 그들의 대응하는 설명은 도 12 내지 도 18과 관련하여 설명되고 도시되는 또 다른 실시예의 이해를 용이하게 하는 여러 트랜지스터 원리를 기술한다. 상기 실시예와 같이, 이들 또 다른 실시예도 누설 전류 및 회로 천이 시간을 줄이는 것에 의해 성능을 향상시킨다.

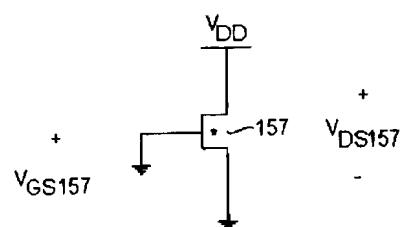

도 11a를 다시 보면, 이것은 드레인이 시스템 전압 레벨(예를 들면,  $V_{DD}$ )에 접속되고 게이트 및 소스가 로우 기준 전압(예를 들면, 접지)에 접속된 하나의 LVT n채널 트랜지스터(157)를 도시하고 있다. 다음의 설명이 간단하게 되도록, 도 11a는 트랜지스터(157)의 드레인-소스 전압( $V_{DS157}$ ) 및 게이트-소스 전압( $V_{GS157}$ )을 도시하고 있다. 트랜지스터(157)의 바이어스가 주어질 때, 그것이 명확하게 오프되지만, 본 발명 분야에서 알려진 바와 같이, 오프 상태의 트랜지스터는 그 트랜지스터를 통하는 약간의 양의 전류 누설을 여전히 갖는다. 또한, 트랜지스터(157)가 LVT 트랜지스터이므로, 그것을 통한 누설 전류의 양은 그것이 HVT 트랜지스터일 때 보다 크기가 몇 자리수 더 크다. 마지막으로 다음에 설명된 비교 목적을 위해, 트랜지스터(157)에 대하여,  $V_{DS157} = V_{DD}$ , 즉 전체 공급 전압  $V_{DD}$ 가 트랜지스터(157) 양단간의 전압인 것에 유의한다.

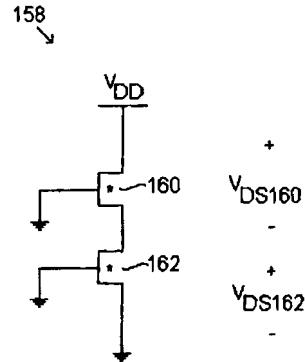

도 11b는 소위 캐스코드 방법으로 접속된 2개의 트랜지스터 160 및 162를 포함하는 158로 나타낸 회로를 도시하고 있다. 즉, 트랜지스터 160 및 162는 직렬로 그리고 서로 직접 접속되어 있다. 특히, 트랜지스터 160의 소스는 트랜지스터 162의 드레인에 접속되고, 트랜지스터 160의 드레인은  $V_{DD}$ 에 접속되고, 트랜지스터 162의 소스는 접지에 접속된다. 다음에 여러 가지 신규한 실시예를 도입하기 위해, 회로 158의 또 다른 특징에 유의한다. 먼저, 트랜지스터 160 및 162는 LVT 트랜지스터이다. 두 번째로, 트랜지스터 160 및 162 각각은 그들이 n채널 트랜지스터이고 그들의 대응하는 게이트가 접지와 동일한 논-인에이블 전압에 접속되어 있으므로(즉, 각 트랜지스터의 게이트-소스 전압이 그의 임계 전압 보다 낮음) 오프(즉, 인에이블되지 않음)이다. 세 번째로, 트랜지스터 160 및 162의 각각은 같은 도전형이고, 이 예에서는 n채널 트랜지스터인 것에 유의한다. 마지막으로, 다음의 설명이 간단하게 되도록, 도 11b는 트랜지스터 160 및 162 각각에 대한 드레인-소스 전압(각각,  $V_{DS160}$  및  $V_{DS162}$ )을 도시하고 있다.

도 11a의 트랜지스터(157)와 같이, 오프 트랜지스터 160 및 162를 통하여 약간의 누설 전류가 통과하지만, 다음에 설명하는 이유때문에, 오프 트랜지스터 160 및 162를 통과하는 누설 전류의 양은 트랜지스터(157)를 통한 누설 전류 보다 상당히 적다. 특히, 도 11a에서  $V_{DS162}$ 는  $V_{DD}$ 보다 매우 작고,  $V_{DS157}$ 은  $V_{DD}$ 와 같은 것에 주의한다. 예를 들면, 1.8 볼트 정도의  $V_{DD}$ 에 대하여,  $V_{DS162}$ 는 수백 밀리볼트로 될 수 있다. 또한, 트랜지스터의  $V_T$ 는 그의  $V_{DS}$ 에 좌우되는 일이 많다. 구체적으로, 비교적 높은  $V_{DS}$ 에 대하여, 트랜지스터의  $V_T$ 는 감소한다. 반대로, 비교적 낮은  $V_{DS}$ 에 대하여, 트랜지스터의  $V_T$ 는 증가하고, 따라서, 그 트랜지스터를 통한 누설 전류는 감소한다. 예를 들면, 누설 전류는 50배 정도 감소할 수 있다. 트랜지스터의  $V_{DS}$ 와 누설 전류 사이에 이러한 관계가 주어질 때, 도 11b의  $V_{DS162}$ 가 도 11a의  $V_{DS157}$ 보다 매우 작으므로, 트랜지스터 162를 통한 전류 누설은 트랜지스터(157)를 통한 전류 누설 보다 적다. 또한, 트랜지스터 160의 게이트-소스 전압이 부 전압(즉,  $-V_{DS162}$ )이고 동일하게 줄어든 양의 누설 전류가 그것을 통과하는 것에 유의한다. 마지막으로, 도 11b의 2개의 캐스코드된 트랜지스터가 누설 전류의 양을 제한하더라도, 그 직렬 경로에 접속된 하나 이상의 추가 오프 트랜지스터가 누설 전류의 양을 더욱 감소시킬 수 있지만, 그러한 감소는 모든 그러한 추가 트랜지스터(들)에 대하여 중요하지 않다는 것에 유의한다.

도 11b의 캐스코드 접속이 전류 누설 저감에 이익이 있다는 것을 이해한 후, 본 발명의 발명자는 다음에 도시하는 바와 같은 예의 동적 논리 회로에 이를 특징을 적용하였다. 편의상, 다음의 도면은 이전 도면중의 어떤 도면과 여러 특징을 공유한다. 따라서, 설명이 간단하게 되도록, 동일한 참조 부호가 여러 예에서 사용되고, 초대된 독자는 이를 특징의 더욱 상세한 설명에 대하여 이미 논의된 것을 참조한다. 그러나 다음의 실시예에 대하여, 처음에, 상기 1절에서와 같이 회로 구성의 방전 경로에 HVT 트랜지스터를 포함할 필요가 없고, 그 대신 도 11b에서 설명된 것과 같은 접속 또는 다른 대안을 사용하여 다음이 더욱 잘 이해되는 것에 유의한다.

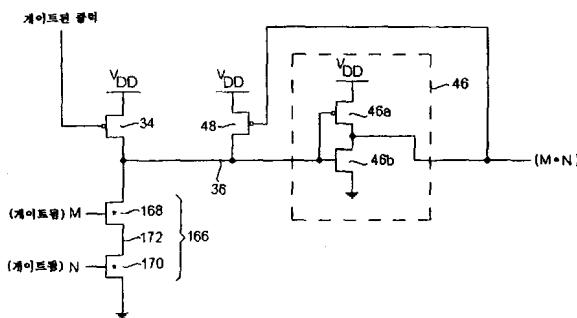

도 12는 도 2의 회로 32와 일부 접속을 공유하고 164로 나타낸 동적 논리 회로 실시예의 개략도이다. 간략하게, 이들 공통 특징은 GATED CLOCK 신호가 로우일 때 프리차지 노드(36)를 프리차지하는 p채널 트랜지스터(34)의 게이트를 구동하는 GATED CLOCK 신호를 포함한다. 도 12와 도 2 사이의 다른 공통적 특징은 다음에 기술하는 바와 같이 프리차지 노드(36)가 방전되지 않는 한 GATED CLOCK 신호가 천이한 후 프리차지 노드(36)를 하이로 유지하는 p채널 트랜지스터(48) 및 인버터(46)를 포함한다. 다음에 더욱 명확하게 되는 이유 때문에, 인버터(46)의 상세는 도 2에서는 없는 부분이 도 12에는 도시되어 있다. 그들의 설명을 다시 보면, 인버터(46)는 소스가  $V_{DD}$ 에 접속되고, 드레인이 인버터(46)의 출력에 접속되고, 게이트가 인버터(46)의 입력에 접속된 p채널 트랜지스터(46a)를 포함한다. 또한, 인버터(46)는 소스가 접지에 접속되고 드레인이 인버터(46)의 출력에 접속되며 게이트가 인버터(46)의 입력에 접속된 n채널 트랜지스터(46b)를 포함한다.

166으로 나타낸 논리 회로는 프리차지 노드(36)와 접지 사이에 접속된다. 논리 회로(166)는 2개의 직렬 접속된 n채널 트랜지스터 168 및 170을 포함한다. 논리 회로(166)의 특정 논리는 논리식 M AND N을 구현하고, 구체적으로, n채널 트랜지스터(168)의 게이트는 게이트된 입력 신호 M을 수신하도록 접속되고, n채널 트랜지스터(170)의 게이트는 게이트된 입력 신호 N을 수신하도록 접속된다. 또한, 입력 신호 M 및 N이 게이트된 신호이므로, 그들의 값은 GATED CLOCK 신호가 하이일 때 단지 어서트되고, 이들 게이트된 입력 신호는 GATED CLOCK 신호가 로우일 때 로우로 되는 것을 알 수 있다. 논리 회로(166)의 접속을 상세히 설명하면, n채널 트랜지스터(168)의 드레인은 프리차지 노드(36)에 접속되고, n채널 트랜지스터(168)의 소스는 노드 172에 접속된다. n채널 트랜지스터(170)의 드레인은 노드 172에 접속되고, n채널 트랜지스터(170)의 소스는 접지(또는 방전 경로 내의 모든 트랜지스터가 도통일 때 방전이 허용되도록 공급 전압과 다른 전위)에 접속된다. 마지막으로, 중요하게, 트랜지스터 168 및 170이 LVT 트랜지스터인 것에 유의한다.

도 12의 회로 164에 의해 실현되는 논리식은 그 도면의 방법으로 접속된 회로를 포함하는 종래 구성에서와 동일하지만, 회로의 속도 뿐만 아니라 그의 누설 전류 특징은 동작의 프리차지 페이즈 동안 도통하지 않는 직렬 접속된 LVT 트랜지스터를 포함하고 있기 때문에 상당히 다르다. 이러한 종래 기술 이상의 개선은 동적 논리 회로로서, 평가 페이즈로 이어지는 프리차지 페이즈에 걸쳐 발생하는 회로 164의 다음의 동작 설명에서 잘 이해된다.

회로 164는 GATED CLOCK 신호가 로우일 때 그의 프리차지 페이즈에 있고, 프리차지 노드(36)는 도 2와 관련하여 이미 설명된 것과 마찬가지 방법으로 프리차지된다. 그러나, 양 입력 신호 M 및 N이 게이트되므로, GATED CLOCK 신호가 로우일 때 이들 신호가 어서트되지 않는 것에 주의한다. 그 결과, n채널 트랜지스터 168 및 170은 프리차지 페이즈 동안 도통하지 않는다. 더욱 중요하게는, 이 순간 동안, n채널 트랜지스터 168 및 170이 도 11b의 트랜지스터 160 및 162와 마찬가지 방법으로 도통하고, 즉 그들이 직렬 접속되고 각각의 게이트가 접지에 접속되는 것에 유의한다. 도 11b에서 제한된 전류 누설의 상기 설명이 주어질 때, 따라서, 동작의 프리차지 페이즈 동안, 논리 회로(166)가 2개의 직렬 접속된 LVT 트랜지스터를 갖는 유사한 회로와 비교하여 소량의 전류를 누설하지만, 이들 트랜지스터 중 하나의 입력이 접지되지 않는 것에 유의한다.

회로 164는 GATED CLOCK 신호가 하이일 때 그의 평가 페이즈에 있다. 따라서, 평가 페이즈의 초기에, 회로 164는 프리차지 페이즈에 의해 발생된 0 논리 신호를 계속 출력한다(그리고, 이 출력은 p채널 트랜지스터(48)에 의해 유지된다). 평가 페이즈 동안, 그리고 논리 회로(166) 및 GATED CLOCK 신호에 응답하는 동작으로 인해, 논리 출력 신호는 프리차지 페이즈 후와 동일한 상태로 유지되거나 또는 그 대신 반대 논리 상태로 천이할 수 있다. 구체적으로, 로우에서 하이로 GATED CLOCK 신호의 천이 중 또는 그후에, 논리 회로(166)에 의해 달성되는 논리가 그 회로내의 각 트랜지스터를 도통하는 것이면, 접지에 프리차지 노드(36)가 접속되는 것이 발생한다. 이 예에서, 논리 동작은 M AND N이고, 따라서, 게이트된 입력 M 및 N이 GATED CLOCK 신호가 로우에서 하이로 천이하는 동안 또는 그 후에 로우에서 하이로 상승하면, 논리 회로(166)의 트랜지스터는 도통하고 프리차지 노드(36)는 접지에 접속된다. 따라서, 프리차지 전압은 방전되고, 인버터(46)에 의해 제공될 때의 출력 신호는 그의 프리차지 페이즈(즉, 논리 0)에서 방전 상태로 천이하여 논리 1을 나타내는 출력을 제공한다. 그러나, 그러한 방전이 발생할 때, 이것이 LVT 트랜지스터(즉, 트랜지스터 168 및 170)를 사용하여 발생하는 것에 유의한다. 이들 트랜지스터를 통하는 전류가 LVT 트랜지스터 대신에 HVT 트랜지스터를 갖는 회로 이상으로 증가하므로, 회로의 방전 속도는 향상되고 전체 성능도 향상된다.

회로 164의 적용 및 개선된 동작이 주어질 때, 이것은 트랜지스터가 프리차지 페이즈 동안 오프인 것으로 알고 있는 그의 방전 경로에 적어도 2개의 LVT 트랜지스터를 갖는 것에서 이익이 있다는 것에 유의한다. 그러나, 회로 164의 방전 경로가 2개의 트랜지스터만을 포함하는 것에 유의한다. 따라서, 상기 요구를 만족하기 위해, 방전 경로의 이들 트랜지스터의 각각은 동일한  $V_T$ (로우  $V_T$ )를 갖는다. 각 방전 경로 트랜지스터의  $V_T$ 가 동일하므로, 이들 트랜지스터의  $V_T$ 를 비교하기 위한 기준점이 있어야 한다. 즉, 도 1 내지 도 10b에서, 동일한 방전 경로의 트랜지스터를 가변하는 임계 전압을 대비하는 것이 용이하고, 여기서, 주어진 방전 경로 내의 트랜지스터의 일부는 동일한 방전 경로 내의 다른 트랜지스터 보다 낮은  $V_T$ 를 갖는다. 그러나, 그와 반대로, 도 12(이하는 다른 도면도 마찬가지임)에서, 모든 방전 경로 트랜지스터는 동일한  $V_T$ 를 갖는다. 따라서, 도 12에 대해서 뿐만 아니라 다음의 다양한 실시예와 관련하여, LVT 트랜지스터는 그 트랜지스터의  $V_T$ 가 회로의 신호 경로의 어느 곳에서 다른 트랜지스터의  $V_T$ 보다 더 낮은 것을 나타내는 것을 알아야 한다. 예를 들면, 도 12에서, 신호 경로는 M 및 N 입력을 포함하고 회로의 출력을 계속 통과시킨다. 그 신호 경로가 주어질 때, 이것은 명백하게 인버터(46)를 포함한다. 또한, 트랜지스터 168 및 170의  $V_T$ 는 인버터(46)를 구성하도록 포함된 n채널 트랜지스터(46b)의  $V_T$ 보다 낮다. 따라서, 도 12의 예에서, 다른 트랜지스터에 대하여 방전 경로 트랜지스터의  $V_T$ 를 비교하기 위한 기준은 프리차지 노드(36)에 대하여 중간에서 또한 접속부의 균방(즉, 인버터(46))에서 찾을 수 있다. 그러나, 다른 실시예에서, HVT 트랜지스터 또는 트랜지스터들은 주어진 단의 출력 및/또는 방전 노드에 결합된 다음 단 또는 주어진 단에 입력을 제

공하는 이전 단과 같은 이전 또는 다음 단에서와 같은 회로 신호 경로 이외의 곳에 결합된 것이 발견될 것이다. 또한, 신호 경로는 더 빠른 단 또는 단을 발생하는 후단을 통과할 수 있고, 여기서 그 단에서의 신호 변경은 LVT 트랜지스터를 갖는 단에서의 신호 변경에 영향을 주거나 또는 그것에 의해 영향을 받을 수 있다. 모든 경우에 있어서, 1절에서 설명한 실시예와 같이, 다음의 실시예는 1절에서 이미 설명한 바와 같이 상이한 마스크를 사용하는 것 등에 의해, LVT 또는 HVT 트랜지스터 사이의 임의의 트랜지스터에 대하여 상이한 임계 전압을 설계자가 선택하게 하는 제조 공정을 활용하여 구성된다.

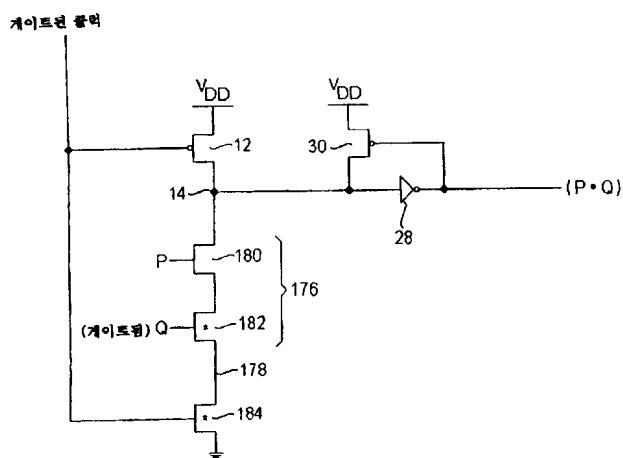

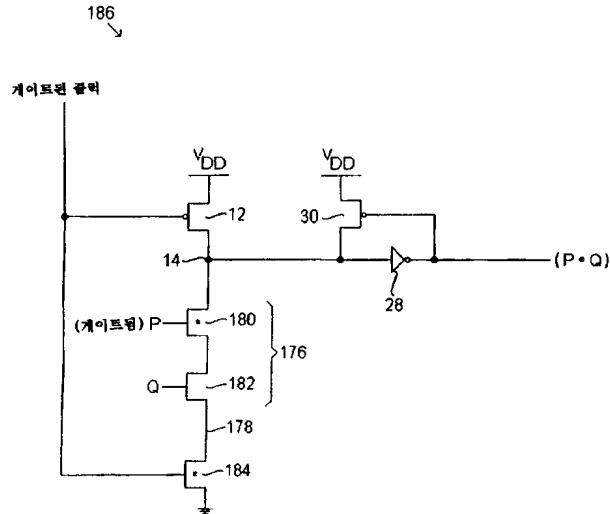

도 13은 도 1의 회로 10과 일부의 접속을 공유하고 174로 나타낸 동적 논리 회로 실시예의 개략도이다. 간략하게, 이들 공통 특징은 (1) GATED CLOCK 신호가 로우일 때 프리차지 노드(14)를 프리차지하는 p채널 트랜지스터(12)의 게이트를 구동하는 GATED CLOCK 신호, (2) 인버터(28), (3) 다음에 기술하는 바와 같이 프리차지 노드(14)가 그렇지 않으면 방전되지 않는 한 GATED CLOCK 신호 천이후 프리차지 노드(14)를 하이로 유지하는 p채널 트랜지스터(30)를 포함한다.

176으로 나타낸 논리 회로는 프리차지 노드(14)와 노드 178 사이에 접속된다. 논리 회로(176)는 2개의 직렬 접속된 n채널 트랜지스터 180 및 182를 포함한다. 논리 회로(176)의 특정 논리는 n채널 트랜지스터 180 및 182의 게이트가 이들 입력 신호에 각각 접속될 때 논리식 P AND Q를 실현한다. 입력 신호 Q는 게이트된 신호이고 입력 신호 P는 그렇지 않은 것에 주의한다. 논리 회로(176)의 접속을 상세히 설명하면, n채널 트랜지스터(180)의 드레인은 프리차지 노드(14)에 접속되고, n채널 트랜지스터(182)의 소스는 노드 178에 접속되고, n채널 트랜지스터(180)의 소스는 n채널 트랜지스터(182)의 드레인에 접속된다. 마지막으로, n채널 트랜지스터(182)는 LVT 트랜지스터인 것에 유의한다.

논리 회로(176)에 부가하여, 회로 174도 LVT n채널 트랜지스터(184)를 포함하고, 이 트랜지스터의 게이트는 GATED CLOCK 신호를 수신하도록 접속되고, 그의 드레인은 노드 178에 접속되며, 그의 소스는 접지에 접속되어 있다. 다음에 설명하는 바와 같이, n채널 트랜지스터(184)는 회로 174에서 실제로 제거될 수 있지만, 그러한 동작은 여기에 기술된 적어도 하나의 실시예 특징에 대하여 편리하도록 트랜지스터(182)의  $V_T$ 를 변경할 것을 요구한다. 이러한 가능성은 도 13의 다음의 동작 설명후 기술된다.

회로 174는 GATED CLOCK 신호가 로우일 때 그의 프리차지 페이즈에 있고, 프리차지 노드(14)는 도 1과 관련하여 이미 설명된 것과 마찬가지 방법으로 프리차지된다. 그러나, 로우 GATED CLOCK 신호도 n채널 트랜지스터(184)를 오프하므로, 논리 회로(176)의 동작에 관계에서 프리차지 노드(14)가 방전되는 것을 방지하는 것에 유의한다. 또한, 입력 신호 Q도 게이트되므로, n채널 트랜지스터(182)도 프리차지 페이즈 동안 도통하지 않는다. 이상을 감안할 때, 프리차지 페이즈 동안 n채널 트랜지스터 182 및 184는 도 11b의 n채널 트랜지스터 160 및 162와 마찬가지 방법으로 접속된다. 즉, 이들은 직렬 접속되고 각 트랜지스터의 게이트는 접지에 접속된다. 따라서, 프리차지 페이즈 동안, 논리 회로(176)는 2개의 직렬 접속된 LVT 트랜지스터를 갖는 유사 회로와 비교하여 소량의 전류를 누설하지만 이들 트랜지스터 중 하나의 트랜지스터의 입력은 접지되지 않는다.

상술한 바와 같이, n채널 트랜지스터(184)는 회로 174에서 제거될 수 있지만, 이 실시예가 주어질 때, 본 발명 분야의 숙련자는 n채널 트랜지스터 180 및 182의  $V_T$ 를 다시 고려해야 한다. n채널 트랜지스터(184)를 제거하는 것에 대하여, 이것은 그 페이즈 동안 n채널 트랜지스터(184)가 오프(즉, 인에이블되지 않음)를 보장하므로 프리차지 페이즈 동안 프리차지 노드(14)가 방전될 수 없다는 것을 상기한다. 그러나, n채널 트랜지스터(182)가 게이트된 입력을 가지므로, 프리차지 노드(14)가 프리차지 페이즈 동안 방전될 수 없는 것도 보장된다. 따라서, 방전 방지가 유일한 고려 사항이라면, n채널 트랜지스터(184)는 회로 174에서 제거될 수 있고 최종회로는 프리차지 페이즈 동안 여전히 방전을 방지한다. 그러나, 이러한 유일한 수정이 이루어지면, 방전 경로가 게이트된 LVT 트랜지스터(182)와 직렬로 HVT 트랜지스터(180)를 포함하는 것에 유의한다. 그 결과, 이 때, 입력 P가 프리차지 동안 하이이면, 방전 경로는 도 11a에 도시한 접속을 닮고 따라서 전류 누설이 더 높아진다. 이러한 발생을 방지하기 위해(또한, 상기 수정이 n채널 트랜지스터(184)를 회로 174에서 제거하려는 것이라고 가정할 때), n채널 트랜지스터(180)는 LVT 트랜지스터로, n채널 트랜지스터(182)는 HVT 트랜지스터로 구성되는 것이 바람직하므로, 상기 도 2에 도시한 구성이 달성된다. 마지막으로, 비록 n채널 트랜지스터(184)가 회로 174에서 제거되지 않더라도, n채널 트랜지스터(180)도 물론 LVT일 수 있으므로, 회로의 방전 경로에는 3개의 LVT 트랜지스터가 접속되게 된다.

도 14는 2가지 예외가 도 13에 도시한 것과 같은 회로 174와 같은 186으로 나타낸 동적 논리 회로 실시예의 개략도이다. 도 13과 도 14의 첫 번째 차이점은 n채널 트랜지스터(180)가 도 14에서는 LVT 트랜지스터이지만 도 13에서는 HVT 트랜지스터라는 것이다. 도 13과 도 14의 두 번째 차이점은 n채널 트랜지스터(182)가 도 14에서는 HVT 트랜지스터이지만 도 13에서는 LVT 트랜지스터라는 것이다. 이상을 상세히 다시 설명하지 않고도, 본 발명 분야의 숙련자는 회로 186가 회로 174와 동일한 논리 출력(즉, P AND Q)을 수행하는 것을 이해할 것이다. 그러나, 도 14의 현저한 특징은 2개의 방전 경로

LVT 직렬 접속된 트랜지스터(즉, 트랜지스터 180 및 184)가 비록 직렬로 접속되었다 할지라도, 서로 직접 접속되지 않는 것이다. 그 대신, HVT 트랜지스터(182)는 2개의 LVT 트랜지스터 180과 184사이에 접속된다. 그러나, 다음에 설명하는 바와 같이, 회로 186은 프리차지 페이즈 동안 오프되는 직렬 접속된 LVT 트랜지스터가 없는 회로에 비하여 이익이 있다.

프리차지 페이즈를 다시 보면, 양 LVT 트랜지스터 180 및 184는 오프인 것을 알 수 있다(전자가 게이트된 입력을 갖고, 후자가 GATED CLOCK 신호에 게이트 접속되기 때문임). 트랜지스터(182)가 온인지 오프인지는 알 수 없다. 그러나, 어떠한 경우에도, 다음은 회로 186이 트랜지스터(182)가 온 또는 오프인 지에 관계없이 성능을 개선하는 것을 설명한다. 첫 번째로 트랜지스터가 프리차지 페이즈 동안 온인 경우를 고려한다. 이러한 가정이 주어질 때, 트랜지스터 180 및 184는 대략 서로 직접 접속되고, 따라서 최종회로는 프리차지 페이즈 동안 도 12의 회로 110과 유사하다. 두 번째로 트랜지스터가 프리차지 페이즈 동안 오프인 경우를 고려한다. 이러한 가정이 주어질 때, 방전 경로에는 HVT 트랜지스터가 있고 이것은 오프이므로, HVT 트랜지스터는 상기 1절에서 설명한 바와 같이 가능한 누설 전류의 양을 또 제한한다.

도 14의 상기 설명이 주어질 때, 본 발명 분야의 숙련자는 이 절의 실시예에 따른 방전 경로가 2개의 직렬 접속된 LVT 트랜지스터를 포함하지만, 그들 트랜지스터가 서로 직렬 접속되지도 않고 동일한 방전 경로에도 접속되지 않는 것을 이해할 것이다. 예를 들면, 도 14의 실시예는 그 예에서, HVT이고 직렬 접속된 LVT 트랜지스터에서 분리되어 있는 하나의 가능한 구조를 도시하고 있다. 그러나, 이것은 단지 하나의 예에 불과하다는 것에 유의한다. 그러나, 도 14의 실시예가 또 수정될 수 있는 것에 유의한다. 예를 들면, n채널 트랜지스터(182)는 LVT 트랜지스터로 이루어질 수 있고, 최종회로는 그의 방전 경로에 3개의 직렬 접속된 LVT 트랜지스터를 갖는다. 이러한 수정이 주어질 때, 종래 기술 이상의 개선이 또 실현된다. 구체적으로, 입력 신호 Q가 프리차지 동안 인에이블되면, LVT 트랜지스터 180 및 184는 도 11b의 LVT 트랜지스터 160 및 162와 마찬가지 방법으로 대략 접속되어 결과적으로 이점이 있다. 그와 반대로, 입력 신호 Q가 프리차지 동안 디스에이블되면, 3개의 직렬 접속된 LVT 트랜지스터(즉, 180, 182 및 184)는 그 기간동안 누설 전류의 양을 더욱 제한할 것이다.

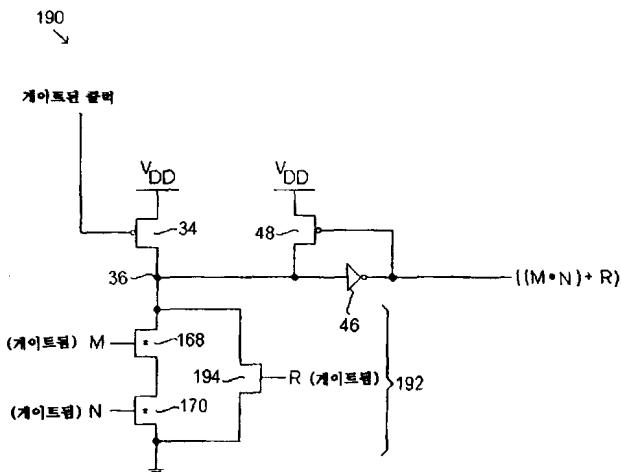

도 15a는 도 5의 회로 76과 일부의 접속을 공유하고 190으로 나타낸 동적 논리 회로 실시예의 개략도이다. 회로 190은 회로 76과 같이, 하나 이상의 방전 경로를 포함한다. 일반적으로, 결합된 방전 경로는 1절에서 도입된 개념과 도 11b 내지도 14에 대하여 도입된 개념을 결합하는 예를 설명한다. 예를 들면, 논리 회로 192로부터의 2개의 방전 경로는 프리차지 노드(36)와 접지 사이에 접속되어 있다. 제1 방전 경로는 도 12와 마찬가지이고, 따라서 2개의 직렬 접속된 LVT 트랜지스터 168 및 170을 포함하고, 이를 각각은 각각 게이트된 입력 신호 M 및 N을 갖는다. 제2 방전 경로는 하나의 n채널 트랜지스터(194)를 포함하고, 트랜지스터(194)가 게이트된 입력 신호(즉, R)를 갖는 HVT 트랜지스터인 것에 유의한다.

도 15a의 구성이 주어질 때, 본 발명 분야의 숙련자는 이것이 논리식((M AND N) OR B)을 실현하는 것을 이해할 것이다. 그 식의 첫 번째 부분(즉, ((M AND N))에 관심이 있는 한, 독자는 직렬 접속된 게이트된 입력 LVT 트랜지스터 168 및 170이 증가된 속도 성능 및 저감된 전류 누설을 제공하는 방법을 설명하는 도 12의 상기 설명을 참조하기 바란다. 이 논리식의 두 번째 부분(즉, OR R)에 대하여, R이 어서트되면 방전 노드(36)가 방전되어 트랜지스터(194)가 도통하는 것에 유의한다. 그러나, R이 게이트된 신호라는 것에 유의한다. 따라서, 이 절의 원리에 따르면, 프리차지 노드(36)에서 트랜지스터(194)를 통하는 방전 경로가 프리차지 동안 인에이블되지 않는 하나의 LVT 트랜지스터만을 포함하고 도 11a의 트랜지스터(157)의 누설 구성과 닮기 때문에, 프리차지 트랜지스터(194)는 LVT 트랜지스터로서 형성될 수 없다. 그 대신, 1절의 원리에 따르면, 트랜지스터 140은 방전 경로에서 HVT 트랜지스터이고, 프리차지 페이즈 동안 오프로(즉, 논-인에이블) 되는 것이 보장된다. 또한, 제2 방전 경로가 제1 방전 경로와 병렬이고, 따라서 그것이 도통중일 때 제1 방전 경로의 저감된 저항이 그것이 또한 도통중일 때 제2 방전 경로의 속도를 향상할 수 있다는 것에 유의한다.

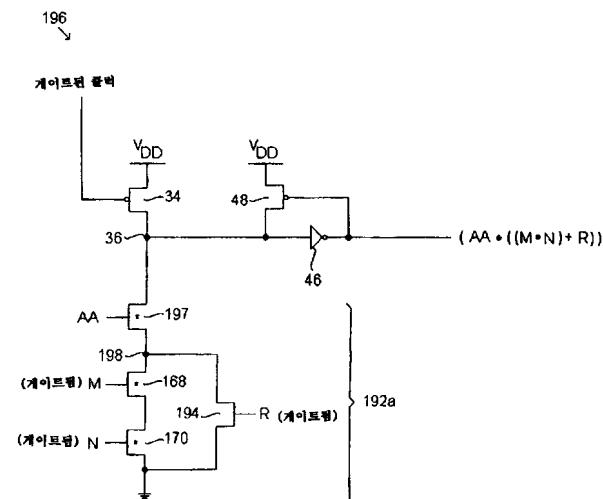

도 15b는 도 15a의 회로 190의 수정예를 도시한 것으로 196으로 나타낸 동적 논리 회로의 개략도이다. 도 15a의 회로 190이 프리차지 노드(36)에서 트랜지스터 168 및 170을 통하는 제1 방전 경로 및 프리차지 노드(36)에서 트랜지스터(194)를 통하는 제2 방전 경로의 2개의 방전 경로를 포함하는 것을 상기한다. 도 15b의 회로 196은 이들 경로를 포함하지만, 이들 경로는 모두 프리차지 노드(36)와 노드 198 사이에 접속된 또 하나의 n채널 LVT 트랜지스터(197)를 포함한다. 따라서, 양 방전 경로가 각각의 방전 경로의 일부로서 n채널 LVT 트랜지스터(197)를 공유하는 것에 유의한다. 또한, n채널 LVT 트랜지스터(197)가 AA로 나타낸 입력 신호를 수신하고, 그 신호 AA가 게이트된 입력 신호가 아니라는 것에 유의한다.

도 15a의 회로 190에 의해 실현되는 논리식이 주어질 때, 본 발명 분야의 숙련자는 도 15b의 회로 196이 논리식 (AA AND ((M AND N) OR R))을 실현하는 것을 이해할 것이다. 즉, 노드 198에서 접지로의 경로가 인에이블되어 트랜지스터(197)가 현재 도통하고 있으면, 프리차지 노드(36)의 프리차지된 전압이 방전된다. 프리차지 노드(36)에서 트랜지스터 197, 168 및 170을 통하는 방전 경로가 모두 LVT 트랜지스터를 포함하고 따라서 모두 HVT 트랜지스터를 포함하는 종래

방전 경로보다 방전이 더 신속한 것에 유의한다. 또한, 프리차지 노드(36)에서 트랜지스터 197 및 194를 통하는 방전 경로가 하나의 LVT 트랜지스터 및 하나의 HVT 트랜지스터를 포함하고, 따라서 2개의 HVT 트랜지스터를 포함하는 종래 방전 경로 보다 방전이 더 신속하다는 것에 유의한다.

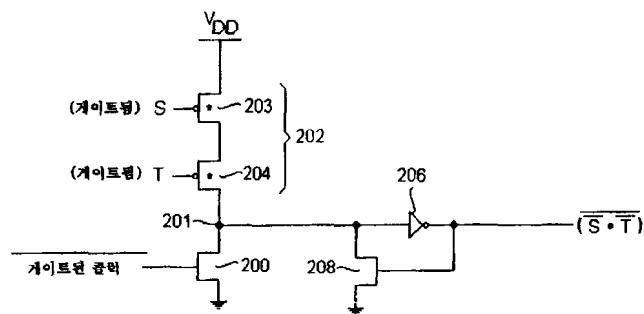

도 16은 프리차지가 로우 전압(예를 들면, 접지)이고 방전이 비교적 높은 전압(예를 들면,  $V_{DD}$ )을 향하는 다른 프리차지 및 방전 동작의 일 예를 도시한 것으로 상기 도 4와 같은 199로 나타낸 회로의 개략도이다. 그러나, 도 16은 전류 누설을 줄이고 회로 속도를 증가시키기 위해 직렬 접속된 LVT 트랜지스터를 사용하는 것을 설명한다. 회로 199의 설명을 다시 보면, 회로는 GATED CLOCK 신호의 상보 신호(즉, 도 16에서 GATED CLOCK)를 n채널 트랜지스터(200)의 게이트에서 수신하고, 이 트랜지스터의 소스는 접지에 접속되고, 드레인은 프리차지 노드(201)에 접속되어 있다. 프리차지 노드(201)와  $V_{DD}$  사이에는 논리식 S OR T(등가적으로, NOT( $\bar{S}$  AND  $\bar{T}$ ))를 구현하는 202로 나타낸 논리 회로가 접속되어 있다. 논리 회로(202)는 2개의 직렬 접속된 p채널 트랜지스터 203 및 204를 포함하고, 이들은 각각 게이트된 입력 신호 S 및 T를 수신하도록 접속되어 있다. 게이트된 입력 신호로서, S 및 T가 프리차지 페이즈 동안 논-인에이블되는 것을 알고 있다. 따라서, S 및 T가 p채널 트랜지스터의 게이트에 접속되므로, 이들은 프리차지 페이즈 동안 하이이다(즉, 하이 신호가 p채널 트랜지스터에 대하여 논-인에이블됨). 또한, p채널 트랜지스터 203 및 204의 각각이 LVT 트랜지스터인 것에 유의한다.

프리차지 노드(201)를 다시 보면, 이 노드는 인버터(206)의 입력에도 접속된다. 이 도면에서 도시되어 있지 않지만, 인버터(206)는 도 10b에 도시한 것과 마찬가지 방법으로 p채널 트랜지스터 및 n채널 트랜지스터를 모두 포함하고, p채널 트랜지스터는 p채널 트랜지스터 203 및 204의  $V_T$ 에 대하여 HVT 트랜지스터인 것이 바람직하다. 인버터(206)의 출력은 회로 199의 출력 신호(즉, (S OR T) 또는 등가적으로, NOT( $\bar{S}$  AND  $\bar{T}$ ))를 제공하고, n채널 트랜지스터(208)의 게이트에도 접속된다. n채널 트랜지스터(208)의 소스는 접지에 접속되고, n채널 트랜지스터(208)의 드레인은 프리차지 노드(201)에 접속된다.

회로 199의 동작은 도 12의 회로 164와 마찬가지이지만, p채널 트랜지스터가 n채널 트랜지스터 보다 방전을 위해 사용되는 반대 효과가 있다. 프리차지 페이즈 동안, GATED CLOCK 신호는 로우이고, 따라서, 그의 상보 신호는 하이이다. 이 때, n채널 트랜지스터(200)가 도통이므로, 프리차지 노드(201)는 접지로 방전되고 회로 199는 하이 신호(인버터(206)에 의해 반전되기 때문임)를 출력하게 된다. 또한, S 및 T가 게이트된 입력(즉, 프리차지 중 논-인에이블됨)이므로, 이들 신호에 의해 구동되는 p채널 트랜지스터는 프리차지 동안 오프되므로, 프리차지 노드(201)가 방전되는 것이 방지된다. 또한, 프리차지 동안, 이들 트랜지스터도 도 11b의 방법으로 비도통 직렬 접속된 LVT 트랜지스터를 나타내고, 따라서 누설 전류가 감소한다. 평가 페이즈 동안, GATED CLOCK 신호는 하이이고, 따라서, 그의 상보 신호는 로우이다. 따라서, 평가 페이즈의 초기에, 회로 199는 프리차지 페이즈에 의해 발생된 논리 1을 계속 출력한다. 그러나, 논리 회로(202) 및 GATED CLOCK 신호의 상보 신호에 응답하는 동작으로 인해, 그 논리 출력 신호는 프리차지 페이즈 후의(그리고, n채널 트랜지스터(208)에 의해 유지된) 것과 동일한 상태로 유지되거나 또는 그 대신 반대 논리 상태로 천이할 수 있다. 구체적으로, 평가 페이즈 동안, 프리차지 노드(201)는 S 및 T 입력 신호가 로우이면  $V_{DD}$ 에 접속된다. 그 결과, 프리차지 노드(201)의 프리차지 전압(즉, 도 16의 예에서는 접지)은  $V_{DD}$ 를 향해 방전되게 된다. 이 방법으로 프리차지 노드(201)가 방전되는 것에 의해, 프리차지 노드(201)에서의 전압이  $V_{DD}$  또는 그에 가까이 도달하고 또한 인버터(206)에 의해 반전되는 것에 유의한다. 따라서, 회로 199의 예에서, 이 방법으로의 방전은 논리 1에서 논리 0으로의 회로 199의 논리값의 천이를 나타낸다. 또한, 트랜지스터 203 및 204가 LVT 트랜지스터이므로, 이 방전의 속도는 HVT 이상으로 증가하는 것에 유의한다. 마지막으로, 트랜지스터 203 및 204의  $V_T$ 는 회로내의 또는 그것에 접속된 신호 경로를 따른 어느 것에 접속된 적어도 하나의 다른 p채널 트랜지스터와 비교할 때, 예를 들면 인버터(206)(구체적으로 도시하지는 않았지만, 도 12의 인버터(46)에 도시한 것과 마찬가지 방법으로 포함되어 있는 것으로 이해됨) 내의 p채널 트랜지스터와 비교할 때 낮다고 고려된다.

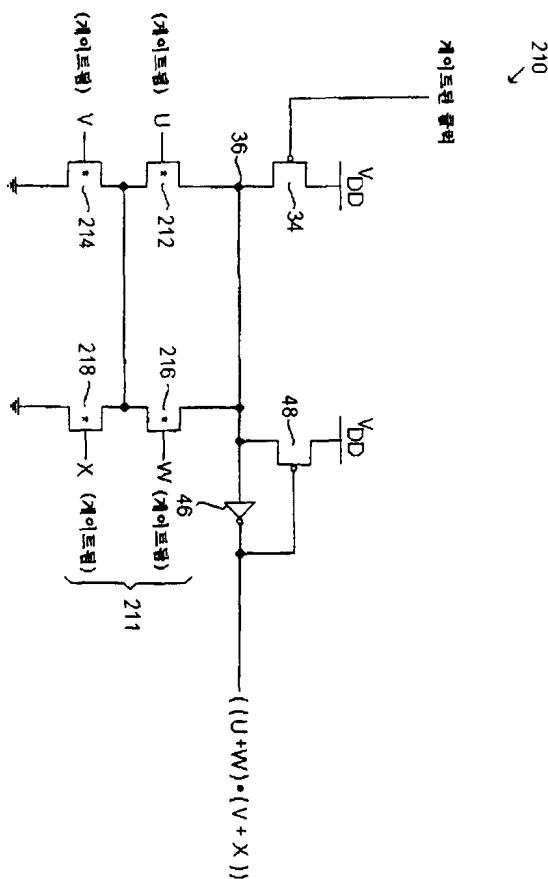

도 17은 도 6의 회로 82와 많은 동일한 접속을 공유하고 210으로 나타낸 동적 논리 회로 실시예의 개략도이다. 그러나, 도 17에서, 입력 신호는 회로의 방전 경로 내의 임의의 트랜지스터의 임계 전압에 대하여 변경되고, 따라서, 이전 도면과의 혼동을 피하기 위해 그 경로에 대하여 상이한 참조 숫자가 사용되어 있다. 회로 210의 상이한 특징을 다시 보면, 이 회로는 논리 회로(211)를 포함하고, 이 논리 회로는 프리차지 노드(36)에서 접지로 다음의 4가지 경로, 즉 (1) 트랜지스터 212 및 214, (2) 트랜지스터 216 및 218, (3) 트랜지스터 212 및 218, (4) 트랜지스터 216 및 214를 통하는 경로를 포함한다. 따라서, 본 발명 분야의 숙련자는 회로 211가 논리 출력식 ((U OR W) AND (V OR X))를 실현하는 것을 이해할 것이다. 그러나, 각 방전 경로에서 직렬 접속된 LVT 트랜지스터에 대한 상기 원리에 따르면, 4개의 전위 방전 경로의 각각이 2개의 트랜지스터만을 포함하는 것에 유의한다. 따라서, 도 12의 예와 같이, 각 방전 경로에서 프리차지 동안 인에이블되지 않는 2개의 트랜지스터는 LVT 트랜지스터이고, 이것에 의해 논리 회로(211)의 각 트랜지스터는 LVT 트랜지스터로 된다. 또한,

이들 트랜지스터의 각각이 동작의 프리차지 페이즈 동안 논-인에이블되는 입력을 갖는 것에 유의한다. 마지막으로, 트랜지스터 212 내지 218의  $V_T$ 는 회로내의 또는 그것에 접속된 신호 경로를 따라 어느 곳에 접속된 적어도 하나의 다른 n채널 트랜지스터와 비교할 때 예를 들면, 인버터(46) 내에 포함된 n채널 트랜지스터(46b)(도 17에는 도시되어 있지 않고, 도 12를 참조하기 바란다)와 비교할 때 낮다고 고려된다.

이상을 고려할 때, 프리차지 페이즈 동안, 각각의 가능한 방전 경로가 2개의 직렬 접속된 LVT 트랜지스터를 포함하고, 그의 논-인에이블링(예를 들면, 게이트된 입력) 입력 신호로 인해 이들의 각각이 프리차지 페이즈 동안 오프로 되는 것에 유의한다. 따라서, 도 11b에서와 같은 저감된 누설 이점은 프리차지 페이즈 동안 달성된다. 또한, 평가 페이즈 동안, 각 방전 경로는 2개의 LVT 트랜지스터를 반드시 포함하므로, 방전 경로에 모두 HVT 트랜지스터를 사용하는 회로 이상으로 친이 속도가 증가한다.

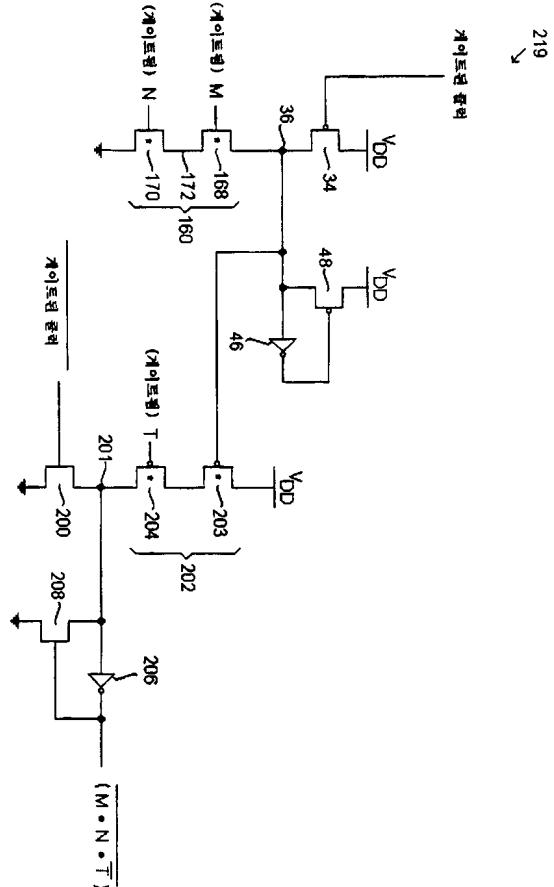

도 18은 도 12의 회로 164와 도 16의 회로 199를 결합시킨 것으로 219로 나타낸 동적 지퍼 논리 회로 실시예의 개략도이다. 지퍼 논리 및 주어진 이러한 결합에 대하여, 회로 219가 제2 도전형의 방전 경로 트랜지스터를 갖는 제2 동적 논리 단을 구동하는 제1 도전형의 방전 경로 트랜지스터를 갖는 제1 동적 논리 회로단을 포함하는 것에 유의한다. 도 18이 도 12와 도 16을 결합한다 할지라도, 도 12의 전체 회로는 회로 164의 프리차지 노드(36)가 회로 199의 트랜지스터(203)에 게이트된 입력을 제공하도록 접속되고, 즉 지퍼 회로의 경우, 회로내의 다음 단으로의 입력으로 접속되기 전에 프리차지 노드의 방전이 있어서 다음 단(들)으로의 입력의 적절한 천이가 보장되는 것에 유의한다. 또한, HVT인 신호 경로내의 동일 도전형의 임의의 다른 트랜지스터에 대하여 트랜지스터 168 및 170이 LVT인 것에 유의한다. 예를 들면, 인버터(46)는 프리차지 노드(36)에 접속되고, 따라서, 회로의 신호 경로 내인 것으로 고려된다(예를 들면, 프리차지 노드(36)의 값에 의해 영향을 받을 수 있기 때문임). 따라서, n채널 트랜지스터 168 및 170은 인버터(46) 내의 n채널 트랜지스터(46b)(도 18에는 도시하지 않음. 도 12를 참조)에 대하여 LVT로 고려할 수 있다. 또한, 인버터(206)가 연속하는 단에 있고 트랜지스터 168 및 170을 갖는 단에서 입력을 수신하는 회로의 신호 경로에 있는 것에 유의한다. 따라서, n채널 트랜지스터 168 및 170은 인버터(206) 내의 n채널 트랜지스터에 대하여 LVT로 고려할 수 있다(도시하지는 않지만, 인버터(206)는 인버터(46)와 마찬가지 방법으로 구성되는 것이 바람직하고, 이것에 의해, n채널 및 p채널 트랜지스터를 모두 포함하게 된다). 마찬가지로, p채널 트랜지스터 203 및 204가 HVT인 신호 경로 내의 동일 도전형의 임의의 다른 트랜지스터에 대하여 LVT로 고려할 수 있는 것에 유의한다. 예를 들면, 인버터 46 및 인버터 206은 도 18의 신호 경로에 접속되고, 동일한 도전형(즉, p채널)의 HVT 트랜지스터를 포함한다. 따라서, p채널 트랜지스터 203 및 204는 인버터 206 또는 인버터 46 내의 p채널 트랜지스터에 대하여 LVT로 고려할 수 있다. 마지막으로, 이전 절에서 설명한 바와 같이, LVT p채널 트랜지스터의  $V_T$ 의 크기가 LVT n채널 트랜지스터의  $V_T$ 의 크기와 다를 수 있으므로, LVT 대 HVT의 비교가 동일한 도전형의 트랜지스터에 대하여 이루어진다고 언급한 것에 유의한다. 마찬가지로, HVT p채널 트랜지스터의  $V_T$ 의 크기는 HVT n채널 트랜지스터의  $V_T$ 의 크기와 다를 수 있다.

이상을 고려할 때, 본 발명 분야의 숙련자는 회로 219가 논리 출력식 ((NOT M) OR (NOT N) OR T) 또는 등가적으로 NOT(M AND N AND  $\overline{T}$ )를 실현하는 것을 이해할 것이다. 또한, 회로 219의 각 단은 상기의 방법에서 이점이 있다. 구체적으로, GATED CLOCK 신호가 로우일 때, 양단은 동작의 프리차지 페이즈에 있고, 논-인에이블된 직렬 접속된 LVT 트랜지스터는 각 단의 방전 경로의 누설 전류를 제한한다. 또한, GATED CLOCK 신호가 하이일 때, 양단은 동작의 평가 페이즈에 있고, LVT 트랜지스터는 연속하는 단의 동작 속도를 물론 개선한다.

이상으로부터, 본 발명 분야의 숙련자는 이 절의 실시예가 동적 논리 회로의 방전 경로에 직렬 접속된 캐스코드 트랜지스터를 포함하는 것에 의해 이익이 있고, 이들 트랜지스터 중 적어도 2개의 트랜지스터가 동작의 프리차지 페이즈 동안 인에이블되지 않는 것을 이해할 것이다. 이점은 여러 실시예를 설명하였지만, 또 다른 실시예도 만들 수 있다. 예를 들면, 상술한 바와 같이, 프리차지 페이즈 동안 도통하는 것으로 알고 있는 또 하나의 트랜지스터를 LVT 트랜지스터로서 구성할 수 있다. 다른 예로서, 도 9에 도시한 듀얼 레일 회로의 트랜지스터의 임계 전압도 고려하여 여기에 설명된 원리에서 이익이 생기도록 조정될 수 있다. 또 다른 예로 본 발명 분야의 숙련자에 의해 기대될 수 있다.

### 3. 동적 논리 게이트의 전력 감소 회로, 시스템 및 방법

이전 절에서, LVT 트랜지스터를 포함하는 것이 동작의 프리차지 페이즈 동안 낮은 전류 누설을 유지하면서 회로 속도를 현저하게 증가시킬 수 있는 것은 명확하다. 그러나, 비교 가능한 HVT 트랜지스터보다 높은 누설을 나타낸다고 알고 있는 이들 LVT 트랜지스터가 동작의 평가 페이즈 동안 전류 누설을 제공 할 수 있다는 것에 유의한다. 예를 들면, 도 1에서, n채널 트랜지스터(16)가 동작의 프리차지 페이즈 동안 오프이고, 그 결과 그 시간 동안 누설 전류를 제한하는 것을 상기한다.

그러나, 그와 반대로, n채널 트랜지스터(16)는 동작의 평가 페이즈 동안은 온이다. 따라서, 도 1의 논리 회로(20)에 의해 실현된 논리가 거짓이면, LVT 트랜지스터 22 및 24는 그 시간 동안 누설할 것이다. 이 예는 비도통 LVT 트랜지스터가 동작의 평가 페이즈 동안 누설하는 상기 도시한 수많은 나머지 실시예에 그렇지 않으면 적용될 수 있다.

이것을 감안하여, 본 발명자는 동작의 평가 페이즈 동안 발생할 수 있는 누설 전류의 가능성을 줄이는 또 하나의 실시예들을 발명하였다. 하나의 기술에 있어서, 논리 회로 전체를 아이들 상태로 하는 것에 의해(즉, 그의 방전 경로 각각이 하나 이상의 클럭 기간에 걸쳐 디스에이블됨), 누설할 수 있는 회로 부분이 없거나 또는 거의 없게 한다. 즉, 이 때, 그의 평가 페이즈에 있는 회로 부분이 없고, 따라서, 위에서 방금 지적한 평가 페이즈 누설은 발생하지 않는다. 또한, 다상 회로의 하나 이상의 페이즈가 프리차지 페이즈로 유지되는 기간을 갖는 것을 심각하게 고려하는 것에 유의한다. 예를 들면, 마이크로프로세서에서 플로팅 포인트 데이타 파이프라인은 실행되는 플로팅 포인트 명령이 없는 클럭 사이클 동안 빈다고 기대될 수 있다. 다른 예로서, 주어진 포인트에서만 동작하는 논리 게이트 및/또는 상태 머신의 집합이 있을 수 있고, 이것은 결국 다른 포인트에서 필요하게 될 때까지 유지 또는 저장된다. 다른 기술에 있어서, 각 회로가 동작의 확장된 프리차지 페이즈에 있어서 동시에 존재할 수 있도록 상이한 페이즈 회로를 제어하기 위해 분리 클럭이 사용된다. 또 다른 기술에서는 프리차지 페이즈의 기간에 대하여 평가 페이즈의 기간을 단축하기 위해 정규 동작중 피드백 회로를 사용한다. 따라서, 모든 경우에 있어서, 이들 기술 및 고려 사항은 다음에 기술하는 실시예에 대한 것이다.

다상 회로의 하나 이상의 페이즈를 동시에 프리차지로 할 때, 여러 가지를 고려해야 한다. 예를 들면, 다상 회로의 하나 이상의 페이즈가 프리차지에 있으면, 평가 페이즈를 방금 처리한 단에 의해 발생되는 데이타는 보존되어야 한다. 정상 동작 동안 데이타를 저장하는 하나의 기술은 도 19a 내지 도 19c의 종래 기술에 있어서 도시되어 있고, 즉 페이즈들 사이에 확장 래칭 회로를 포함하는 것에 의한다. 그러나, 이 기술은 홀로 또 다른 이유에 항상 적합하거나 또는 바람직스럽지 않고, 다음의 설명은 종래 기술을 설명한다.

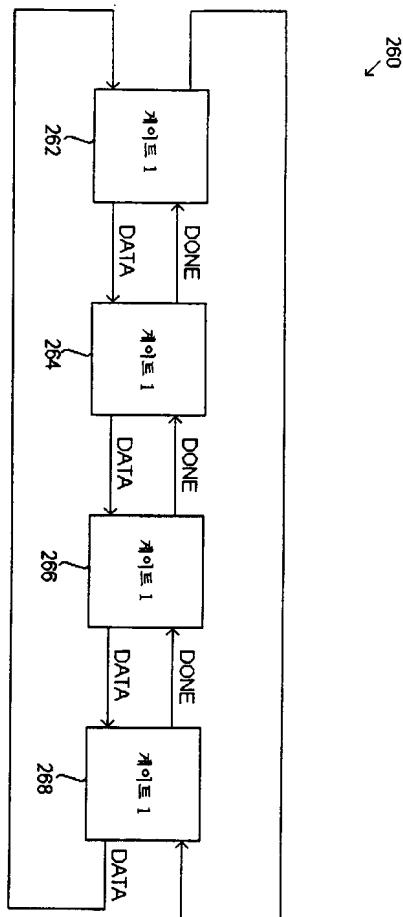

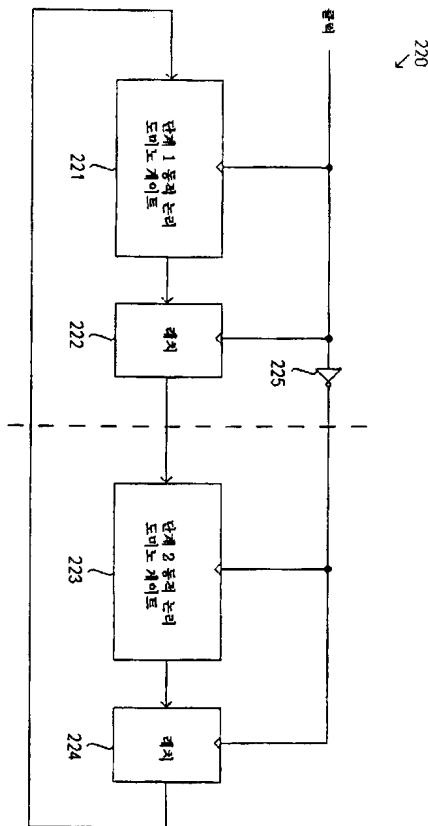

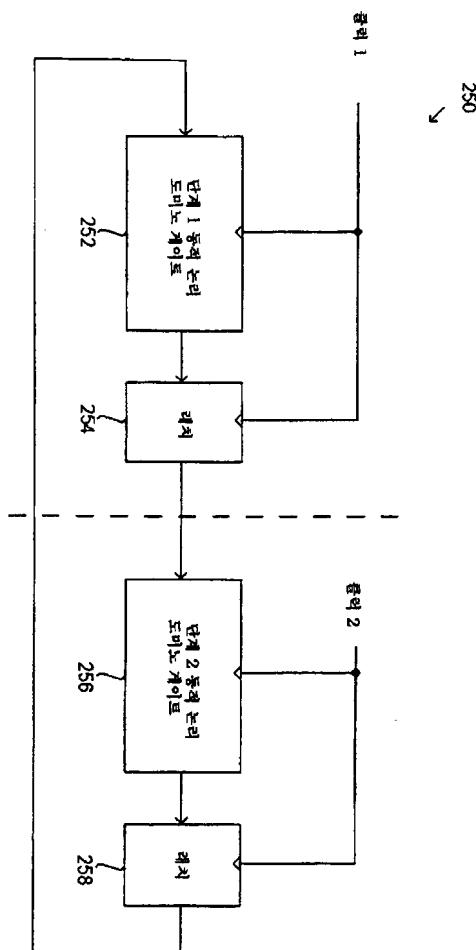

도 19a는 220으로 나타낸 종래 논리 시스템의 블럭도이다. 시스템 220은 이하의 도 20a 내지 도 22d에 도시된 또 다른 실시예가 잘 이해되도록 도시되고 기술된다. 도 19a를 다시 보면, 시스템 220이 2개의 페이즈에서 동작하는 회로를 포함한다. 즉 종방향 점선은 도면의 대략 중간에 도시되어, 일반적으로 점선의 한쪽에 있는 회로가 하나의 페이즈에 속하고, 점선의 반대쪽에 있는 회로가 다른 페이즈에 속하게 된다. 구체적으로, 시스템 220은 점선의 좌측에 한 세트의 페이즈 1 동적 논리 도미노 게이트(221)를 포함하고, 이 게이트는 래치(222)로 데이타를 출력한다. 래치(222)는 통상 투명한 래치 구조를 갖고, 도시하지는 않지만, 제2 인버터의 입력으로 패스게이트를 거쳐 접속된 출력을 갖는 제1 인버터를 포함한다. 도 19a의 종방향 점선의 우측에 대하여, 시스템 220도 마찬가지로 한 세트의 페이즈 2 동적 논리 도미노 게이트(223)를 포함하고, 이 게이트는 래치(222)와 동일한 방법으로 구성된 래치(224)에 데이타를 출력한다. 마지막으로, CLOCK 신호가 도 19b의 종방향 점선의 양쪽에 모두 사용되는 것에 유의한다. 특히, 페이즈 1 게이트(221) 및 래치(222)는 CLOCK 신호에 의해 클럭되지만, CLOCK 신호는 인버터(225)에 의해 반전되고, 따라서, 페이즈 2 게이트(223) 및 래치(224)는 다음의 도 19c와 관련하여 설명되는 이유때문에 CLOCK 신호의 상보 신호에 의해 클럭된다.

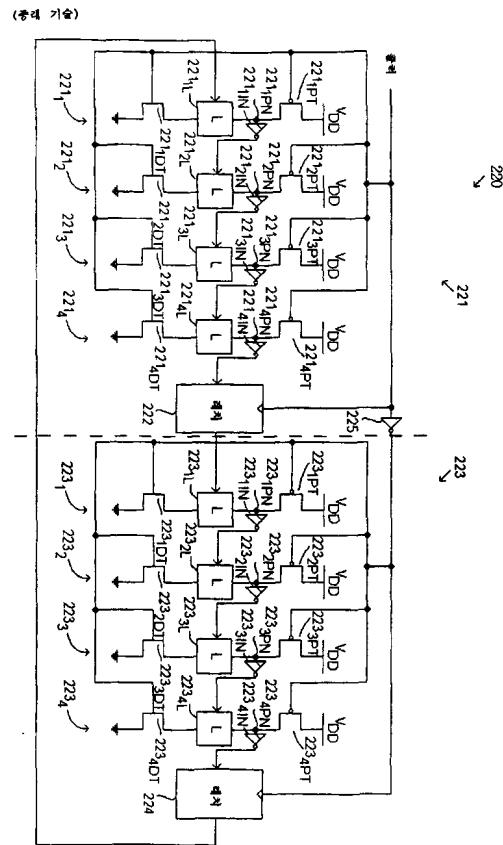

도 19b는 페이즈 1 및 2 게이트 221 및 223의 일부를 더욱 강조하여 도 19a가 시스템 220을 도시하고 있다. 그들의 설명을 다시 보면, 예시를 목적으로, 게이트 221 및 223의 각각은 4개의 단을 포함하고, 이들 4개의 단의 각 세트 사이에는 연속하는 신호 경로가 있다. 게이트(221)에서, 첫 번째 단, 마지막 단 및 첫 번째 단과 마지막 단 사이에 여러 단들이 있도록, 단들은 연속해서 221<sub>1</sub> 내지 221<sub>4</sub>로 번호가 매겨진다. 마찬가지로, 게이트(223)에서, 첫 번째 단, 마지막 단 및 첫 번째 단과 마지막 단 사이에 여러 단들이 있도록, 단들은 연속해서 223<sub>1</sub> 내지 223<sub>4</sub>로 번호가 매겨진다. 게이트 221 및 223이 모든 수의 게이트를 포함할 수 있고 한 세트의 게이트들이 다른 것과 상이한 수의 단들을 가질 수 있는 것에 유의한다. 그러나, 예시에 의해 이 예에서는 4개의 단이 각 페이즈에 대하여 도시되어 있다.

게이트 221 및 223의 각 단은 프리차지 노드, 출력 인버터, 프리차지 트랜지스터, 논리 회로 및 방전 트랜지스터를 포함하여 임의의 구성요소를 포함한다. 참조 숫자가 단순하게 되도록, 이들 항목의 각각은 대응하는 항목의 첨자인 하나 이상의 문자와 함께 대응하는 단을 식별하는 밀수가 붙어 있다. 예를 들면, 단 221<sub>1</sub>에 대하여, 그의 프리차지 노드는 221<sub>1PN</sub>이고, 그의 출력 인버터는 221<sub>1IN</sub>이고, 그의 프리차지 트랜지스터는 221<sub>1PT</sub>이고, 그의 논리 회로는 221<sub>1L</sub>이고, 그의 방전 트랜지스터는 221<sub>1DT</sub>이다. 이들 항목의 접속 및 관계를 고려할 때, 일반적으로 각 단이 적어도 하나의 입력을 수신하는, 그 입력 신호(들)에 응답하여, 하나 이상의 회로에 신호를 출력하는 분리 동적 논리 회로인 것에 유의한다. 각 회로의 최종단 이외의 각 단에 대하여, 그 단의 출력은 상이한 동적 논리 회로의 입력에 접속된다. 회로의 최종단인 각 단에 대하여, 그 단의 출력은 래치의 입력에 접속된다. 따라서, 예를 들면 단 221<sub>1</sub>를 자세히 살펴보면, 이것은 CLOCK 신호를 수신하고, 이 신호는 앞서의 도면의 GATED CLOCK 신호와 같이, 프리차지 트랜지스터(221<sub>1PT</sub>)인 p채널 트랜지스터의 게이트에 접속

한다. 프리차지 트랜지스터( $221_{1PT}$ )는 시스템 전압 레벨(예를 들면,  $V_{DD}$ )의 전원에 접속된 소스 및 프리차지 노드( $221_{1PN}$ )에 접속된 드레인을 갖는다. CLOCK 신호도 방전 트랜지스터( $221_{1DT}$ )인 n채널 트랜지스터의 게이트에 접속되고, 이 트랜지스터는 그의 소스가 로우 기준 전압(예를 들면, 접지)에 접속되고, 그의 드레인이 논리 회로( $221_{1L}$ )에 접속되어 있다. 앞서의 도면에서와 같이, 논리 회로( $221_{1L}$ ) 및 방전 트랜지스터( $221_{1DT}$ )는 프리차지 노드( $221_{1PN}$ )에서 접지(또는 동작의 프리차지 페이즈 동안 프리차지 노드에 저장된 전위와는 다른 전위)로의 방전 경로를 형성한다. 앞서의 절에서 설명한 바와 같이, 논리 회로는 대응하는 방전 트랜지스터(방전 경로에 하나가 포함되면)도 도통하고 있으면, 프리차지 노드가 방전될 수 있는 하나 이상의 직렬 경로를 포함할 수 있다. 또한, 논리 회로( $221_{1L}$ )로의 입력이 래치(224)에서 수신되고, 도 19b에서 용이하게 알 수 있는 바와 같이, 이 래치는 페이즈 2 게이트(223)의 단 223<sub>4</sub>에 의한 데이터 출력을 저장하는 것에 유의한다. 또한, 인버터( $221_{1IN}$ )에 의해 나타낸 바와 같이, 단 221<sub>1</sub>의 출력이 다음 연속하는 단의 논리 회로(즉, 논리 회로( $221_{2L}$ ))의 입력에 접속되는 것에 유의한다. 또한, 도 19b의 각 인버터가 인버터 기호의 상반부에 짧은 대각선을 갖는 것으로 도시된 것에 유의한다. 본 명세서의 목적을 위해, 이 기호는 규칙으로서 p채널 트랜지스터(명백히 도시하지 않음)가 인버터의 출력에서 그의 입력으로 피드백 방법으로 접속되는 것을 설명하도록 포함된 것이다. 구체적으로, 피드백 p채널 트랜지스터의 게이트는 대응하는 인버터의 출력에 접속되고, 피드백 p채널 트랜지스터의 소스는  $V_{DD}$ 에 접속되며, 피드백 p채널 트랜지스터의 드레인은 대응하는 인버터의 입력에 접속된다. 따라서, 본 발명 분야의 숙련자는 일단 (예를 들면 평가 페이즈 동안) 프리차지 전압이 주어진 프리차지 노드에 더 이상 접속되지 않으면, 피드백 p채널 트랜지스터는 프리차지 노드가 그의 대응하는 논리 회로에 의해 방전되지 않은 한, 인버터의 입력에 하이 신호를 유지한다.

도 19a 및 도 19b의 시스템 220의 동작은 페이즈 1 및 페이즈 2 게이트 221 및 223에 각각 인가되는 CLOCK 신호 뿐만 아니라 그 CLOCK 신호에 응답하여 그들 회로의 페이즈 동작을 도시하는 도 19c의 타이밍도에 의해 이해된다. 시간 t0에 의해 시스템 220이 대기 상태로 실행한다고 가정한다. t0와 t1사이에서, CLOCK 신호는 로우이다. 따라서, 도 19b로부터, 본 발명 분야의 숙련자는 t0와 t1사이에서 게이트(221)의 각 단이 프리차지 페이즈에 있는 것을 이해할 것이다. 따라서, 각 프리차지 노드 221<sub>1PN</sub> 내지 221<sub>4PN</sub>은 대응하는 프리차지 트랜지스터 221<sub>1PT</sub> 내지 221<sub>4PT</sub>에 의해  $V_{DD}$ 로 프리차지된다. 또한, CLOCK 신호의 상보 신호가 페이즈 2 게이트(223)에 접속되는 것을 상기한다. 따라서, t0와 t1사이에서, 게이트(223)의 각 단은 평가 페이즈에 있다(즉, 각 단의 프리차지 트랜지스터는 오프이고 각 단의 방전 트랜지스터는 인에이블 됨). 일단 평가 페이즈에서 주어진 논리 회로 223<sub>1L</sub> 내지 223<sub>4L</sub> 내의 직렬 경로를 따라 있는 각 트랜지스터(도시하지 않음)가 도통하면, 그 주어진 단의 프리차지 노드는 방전되고 그 단에 의한 논리 상태 출력은 반대 논리 레벨로 상태를 변경한다. t1에서, CLOCK 신호는 로우에서 하이로 천이한다. 그 결과, 위상 1 게이트(221)는 그들의 평가 페이즈를 시작한다. 그와 동시에, 래치(224)의 클럭 입력에 하강 천이가 인가되고, 그에 응답하여, 래치(224)가 t0과 t1사이의 평가 페이즈 동안 게이트(223)에 의해 실현되었던 값을 래치하는 것에 유의한다. 따라서, 도 19c에서, 페이즈 2 게이트(223)는 t1에서 평가 및 래치하도록 도시되어 있다. t1에서 t2까지, 상술한 바와 같은 동작은 역으로 된다. 따라서, 페이즈 1 게이트(221)는 단 221에 의한 데이터 출력이 t2에서 래치(222)에 저장되도록 평가 및 래치 페이즈를 경험한다. 그 동안, 페이즈 2 게이트(223)는 프리차지되므로, 각 프리차지 노드 223<sub>1PN</sub> 내지 223<sub>4PN</sub>은  $V_{DD}$ 로 프리차지된다. t2후 도면의 나머지 부분으로부터, 본 발명 분야의 숙련자는 게이트 세트 각각의 연속하는 상보 동작을 이해할 것이다. 또한, 데이터 경로 때문에, 각 게이트 세트 사이에서 데이터가 연속 형태로 통과하고 나서, 래치(224)에 저장된 후 경로의 끝에서 경로의 처음으로 순환하는 것에 유의한다. 마지막으로, 각 게이트 세트가 상술한 바와 같은 페이즈 동안 동작하므로, 이 포인트의 앞쪽으로부터, 그와 같은 게이트 세트를 페이즈 회로라고 하여, 도 19b는 게이트(221)를 포함하는 제1 페이즈 회로 및 게이트(223)를 포함하는 제2 페이즈 회로를 포함하도록 한다.

진행에 앞서, 도 19b 내의 회로가 주어진 경로를 따라 2개의 회로만을 도시하는 것에 유의한다. 그러나, 실제로는, 하나의 경로가 2개 이상의 회로를 포함할 가능성이 매우 높다. 또한, 각 회로가 다수의 입력 및 다수의 출력을 갖는 회로의 전체 네트워크의 일부로 되는 것은 일반적이다. 그러한 네트워크에서, 제1 경로는 그것이 여러 회로를 포함할 때 주어진 기간동안 네트워크를 거쳐 형성되지만, 다른 경로는 그것이 다른 회로를 포함할 때 주어진 기간동안 네트워크를 거쳐 형성될 수 있으며, 상기 다른 경로는 네트워크를 거쳐 제1 경로와 동일한 회로를 포함하거나 포함하지 않을 수 있다. 마지막으로, 이 방법으로 회로의 네트워크를 구성하는 것이 본 발명 분야에서 공지인 것에 유의한다.

도 19a 내지 도 19c의 접근 방법이 어떤 점에 있어서는 만족스럽다고 할지라도, 본 발명자는 그의 여러 가지 문제점을 이해하였다. 하나의 예로서, 하나의 페이즈는 직접 클럭하고 다른 페이즈를 구동하기 위해서는 상보로 되는 하나의 클럭을 사용하는 것에 의해, 클럭 사이클의 1/2 기간동안 각 페이즈가 평가 동작으로 되는 것이 반드시 요구된다. 그러나, 상술한 바와 같이, 상이한 클럭 페이즈 동안 인에이블되는 적어도 2개의 상이한 페이즈 회로의 단이 적어도 하나의 클럭 기간에 걸쳐 동시에 동작의 프리차지 페이즈로 되도록 다상 회로의 하나 이상의 페이즈를 아이들 상태로 하는 것이 어떤 때에는

바람직스럽지만, 이것은 도 19a 및 도 19b에 도시한 하나의 클럭 접근 방법을 사용해서는 발생할 수 없다. 또한, 이하에는 페이즈 회로 사이에 래치를 만들기 위해 복잡도가 더해지는 것을 피하는 것이 설명된다. 또한, 페이즈 회로 내의 모든 단이 프리차지 또는 평가가 아닌 상태(즉, 그의 프리차지 트랜지스터 또는 그의 방전 경로가 도통함)로 될 수 있고 그 상태에 의해 정상 동작이 개재될 때까지 그 단이 데이터를 저장하는 것이 설명된다. 따라서, 다음의 실시예는 다음의 설명에서 상세하고 더욱 용이하게 이해되는 바와 같이, 이들 원리를 설명하고, 이들 제한을 극복하며, 또 다른 효과를 제공한다.

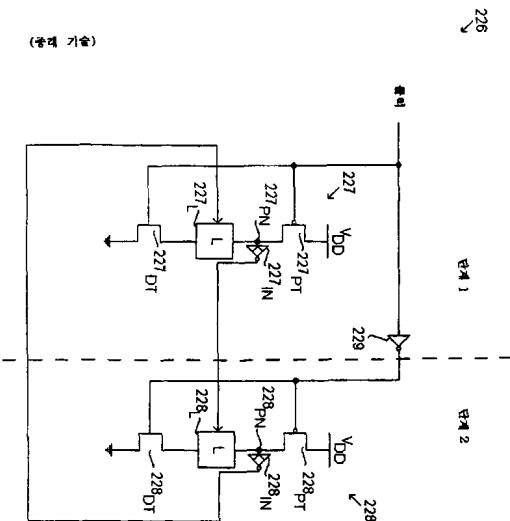

도 20a는 본 발명 분야에서 때때로 홀드 시간 래치라고 하는 226으로 나타낸 종래 논리 회로 실시예 시스템의 개략도이다. 도 19a 및 도 19b의 시스템 220과 같이, 시스템 226은 상이한 페이즈에서 동작하는 페이즈 회로를 포함하고, 따라서, 일반적으로 종방향 접선은 이들 페이즈 회로를 분리한다. 접선의 좌측을 다시 보면, 제1 페이즈 회로(227)는 동적 논리 회로 단을 포함하고, 이 단은 프리차지 트랜지스터( $227_{PT}$ ), 프리차지 노드( $227_{PN}$ ), 출력 인버터( $227_{IN}$ )와 논리 회로( $227_L$ ) 및 방전 트랜지스터( $227_{DT}$ )를 갖는 방전 경로를 포함한다. 도 20a의 접선 우측은 동적 논리 단을 포함하는 제2 페이즈 회로(228)이고, 이것은 마찬가지로, 프리차지 트랜지스터( $228_{PT}$ ), 프리차지 노드( $228_{PN}$ ), 출력 인버터( $228_{IN}$ )와 논리 회로( $228_L$ ) 및 방전 트랜지스터( $228_{DT}$ )를 갖는 방전 경로를 포함하도록 접속된다. 또한, 시스템 226은 CLOCK 신호를 포함하고, 이 신호는 프리차지 트랜지스터( $227_{PT}$ ) 및 방전 트랜지스터( $227_{DT}$ )의 게이트에 직접 접속되고, 인버터(229)에 의해 반전되어 그의 상보 신호가 프리차지 트랜지스터( $228_{PT}$ ) 및 방전 트랜지스터( $228_{DT}$ )에 접속된다. 마지막으로, 도 19a 및 도 19b의 시스템 220과 같이, 시스템 226도 더 큰 순환 논리 네트워크의 작은 부분의 일 예가 설명되도록 순환 형태로 접속된다.

시스템 226의 동작은 도 20b의 타이밍도를 참조하여 이해된다. 그러나, 도면을 연구하기 전에, 시스템 226는 도 19a 및 도 19b의 시스템 220과 반대로 각 단의 출력에 분리된 복잡한 래치 구조를 포함하지 않는 것에 유의한다. 이러한 또 다른 구조가 없음에도 불구하고 시스템 226이 동작하는 기능을 도 20b와 관련하여 설명한다. 도 20b를 참조하면, 그의 첫 번째 두 줄은 각각 시스템 226의 페이즈 1 회로(227) 및 페이즈 2 회로(228)에 인가되는 CLOCK 신호의 상태를 나타낸다. 도 20b의 두 번째 2줄은 각각 페이즈 1 회로(227) 및 페이즈 2 회로(228)에 의한 데이터값 출력을 나타낸다.

시간  $t_0$ 에 의해, 시스템 226은 대기 상태로 실행되는 것으로 가정한다.  $t_0$ 와  $t_1$  사이에서, CLOCK 신호는 로우이다. 그 결과, 페이즈 1 회로(227)는 동작의 프리차지 페이즈이지만 페이즈 2 회로(228)는 동작의 평가 페이즈에 있다.  $t_1$ 에서, 페이즈 회로 227 및 228로의 클럭 신호는 반대 레벨로 천이한다. 따라서,  $t_1$ 에서, 페이즈 2 회로(228)는 그의 동작의 평가 페이즈를 끝냈고, 따라서 인버터( $228_{IN}$ )의 출력에는 유효 데이터가 존재한다. 그러나,  $t_1$  직후,  $p$  채널 프리차지 트랜지스터( $228_{PT}$ )의 게이트에서의 신호는 하이에서 로우로 천이한다. 따라서,  $p$  채널 프리차지 트랜지스터( $228_{PT}$ )가 도통하기 시작하고 (이전 평가 페이즈에서 방전되었다고 가정할 때)프리차지 노드( $228_{PN}$ )에서의 전압이 상승하기 시작하는 것에 유의한다. 그러나,  $p$  채널 프리차지 트랜지스터( $228_{PT}$ )의 응답 시간 지연으로 인해, 프리차지 노드( $228_{PN}$ )가 로우에서 그의 완전한 하이 레벨로 프리차지하기 전 약간의 시간이 걸린다. 그 결과, 도 20b에서  $t_h$ 로 나타낸  $t_1$  후 대응하는 양의 시간이 페이즈 2 회로(228)의 출력(즉, 인버터( $228_{IN}$ )의 출력)이 하이에서 로우로 천이하기 전에 프리차지 효과로 인해 경과한다. 즉, 그 회로에 접속된 클럭 신호가 이제 전환되어 그의 단(들)이 동작의 평가 페이즈에서 동작의 프리차지 페이즈로 변하게 된다 하더라도,  $t_h$ 로 나타낸 짧은 기간 또는 "홀드 시간" 동안 페이즈 2 회로(228)에 의한 데이터 출력은 유지(즉, 유효 상태를 유지)된다.

상술한 바와 같이 회로 228에 의한 데이터의 홀드에 부가하여,  $t_h$  동안 페이즈 1 회로(227)가 그의 동작의 평가 페이즈에 있는 것에 유의한다. 따라서,  $t_h$  동안 페이즈 2 회로(228)에서 계속 출력된 데이터 따라 그의 평가가 이루어진다. 따라서, 다음 회로 227는 이전 회로 228에서의 데이터에 따라 평가를 하지만, 도 19a 내지 도 19c와 관련하여 설명된 종래 시스템에서 필요하였던 추가 배치의 요구는 없다. 또한, 본 발명 분야의 숙련자는 도 20b의 나머지 부분으로부터 이 개념이 도 20a의 2 페이즈 회로 사이에 순환 방법으로 데이터가 연속하도록 계속 적용되는 것을 이해할 것이다. 또한, 이러한 같은 특징은 시스템 226이 상이한 시간에 프리치지되도록 클럭되는 추가의 연속 회로를 포함하면, 또는 각 페이즈 회로가 그 페이즈 회로의 클럭에 접속된 하나 이상의 동적 논리 단을 포함하면 또 적용된다. 또한, 도 20a가 순환 방법으로 2개의 연속 회로만을 도시하도록 단순화되어 있지만, 실제로는, 적절히 기동하는 회로에 대하여, 회로의 적어도 하나의 입력은 디스에 이를 레벨(예를 들면, 논리 0)로 프리치지되지 않는 소스로부터 와야 하는 것에 유의한다. 그렇지 않으면, 도시한 바와 같이 단순화된 구조가 주어질 때, 모든 프리차지 노드의 방전이 있을 수 없고 따라서 논리 0이 회로를 순환하게 되므로, 회로 내 데이터는 항상 디스에 이를 레벨로 유지된다. 따라서, 단순화되지 않을 때, 도 20a 내의 하나 이상의 회로는 실제로 하나 이상의 페이즈 회로에 대하여 래치된 입력과 혼합될 수 있는 큰 회로의 일부이다.

상기에 부가하여, 도 20a의 각 인버터가 인버터 기호의 상반부 및 하반부에 짧은 대각선을 갖도록 도시된 것에 유의한다. 상부 대각선은 상기와 동일한 방법으로, 즉 대응하는 인버터 출력에서 그 인버터의 입력으로 다시 접속된 피드백 p채널 트랜지스터가 존재하는 것을 나타내도록 사용된다. 또한, 본 명세서의 목적상, 하부 대각선도 마찬가지 방법으로 사용되지만, 대응하는 인버터의 출력에서 입력으로 접속되는 피드백 n채널 트랜지스터를 나타낸다. 피드백 n채널 트랜지스터는 그의 게이트가 인버터의 출력에 접속되고, 그의 소스가 접지에 접속되며, 그의 드레인은 인버터의 입력에 접속되어 있다. 따라서, 도 20a의 각 인버터에 대하여, 인버터는 227<sub>IN</sub> 및 228<sub>IN</sub>의 각각에 접속된 p채널 및 n채널 피드백 트랜지스터를 모두 갖는다. 이들 인버터 각각이 대응하는 단이 그의 다음 프리차지 페이즈를 끝낸 후에 일시적으로 데이터를 출력하도록 사용된다고 할 때, 이들 2개의 트랜지스터를 사용함으로써 이 데이터가 t<sub>h</sub> 기간후 인버터의 출력에서 유지되는 것이 또 보장된다.

도 20b의 타이밍도와 관련하여 설명된 도 20a의 실시예는 연속하는 단의 동적 논리 회로가 접속될 때 복잡한 래치가 반드시 필요하지 않다는 것을 설명한다. 그러나, 상기로부터, 본 발명자가 연속하는 동적 논리 회로의 단을 동시에 프리차지 페이즈로 하여 그렇지 않으면 동작의 프리차지 페이즈 동안 발생하게 되는 누설을 최소화하는 것이 바람직하다는 여러 순간(예를 들면, 동적 논리 게이트의 방전 경로에 LVT 트랜지스터를 사용할 때)을 인식하였던 것을 상기한다. 도 20a의 실시예가 복잡한 래치 구조를 제거하더라도, 그들은 공통 클럭 신호를 공유하기 때문에 모두 프리차지 페이즈에 있을 수 없다. 그러나, (다음의 도 23의 실시예에 나타낸 것 등의) 분리 클럭을 사용한다 하더라도, 도 20a의 양단이 동시에 그리고 t<sub>h</sub> 보다 긴 시간 동안 프리차지 페이즈에 있으면, 그 회로에 의해 저장되는 데이터는 상실된다. 따라서, 본 발명자는 도 19a, 도 19b 및 도 20a에 도시한 종래 구성을 절대로 사용하지 않고 상기 기술된 목적을 만족하는 또 다른 실시예를 이하에 제공한다.

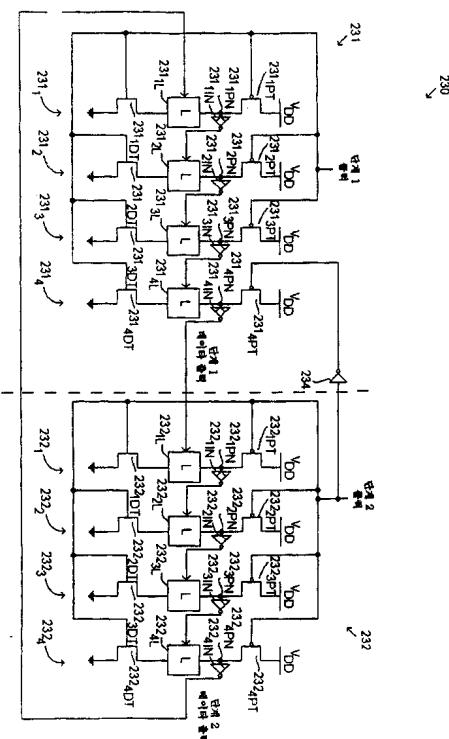

도 21a는 230으로 나타낸 논리 회로 시스템의 개략도이다. 위에서 도입된 방법에서와 같이, 시스템 230은 231 및 나타낸 페이즈 1 회로 및 232로 나타낸 페이즈 2 회로의 2개의 동작 페이즈로 동작하는 회로를 포함한다. 또한, 각 페이즈 회로는 하나 이상의 단을 포함한다. 이 예에서, 각 회로는 각 회로가 모두 4개의 단을 포함하도록 첫 번째 및 마지막 단과 첫 번째와 마지막 단 사이의 신호 경로를 따라 추가 단을 포함한다. 또한, 주어진 페이즈 회로 내의 각 단이 연속적으로 번호가 매겨지고 주어진 단 내의 각 항목이 그 단 뿐만 아니라 항목에 대응하는 번호 및 밑첨자로 나타내어지도록 도 19b에서 도입된 단 및 밑첨자 번호 매김 형태를 도 21a에도 실행한다. 예를 들면, 페이즈 1 회로(231) 내의 첫 번째 단은 231<sub>1</sub>이고, 프리차지 노드는 231<sub>1PN</sub>, 프리차지 트랜지스터는 231<sub>1PT</sub>, 출력 인버터는 231<sub>1IN</sub>, 방전 경로의 논리 회로는 231<sub>1L</sub>, 방전 트랜지스터는 231<sub>1DT</sub>이다. 다른 예로서, 페이즈 2 회로(232) 내의 첫 번째 단은 232<sub>1</sub>이고, 프리차지 노드는 232<sub>1PN</sub>, 프리차지 트랜지스터는 232<sub>1PT</sub>, 출력 인버터는 232<sub>1IN</sub>, 방전 경로의 논리 회로는 232<sub>1L</sub>, 방전 트랜지스터는 232<sub>1DT</sub>이다. 시스템 230이 분리 클럭 신호를 포함하는 것에 유의한다. 일반적으로, 페이즈 1 회로(231)는 PHASE 1 CLOCK에 의해 클럭되지만, 페이즈 2 회로(232)는 PHASE 2 CLOCK에 의해 클럭된다. 중요하게는, 도 21b를 설명할 때 다음에 설명되는 이유로 인해, PHASE 2 CLOCK도 인버터(234)의 입력에 접속되고, 인버터(234)의 출력은 페이즈 1 회로(231)의 최종 단의 p채널 프리차지 트랜지스터(231<sub>1PT</sub>)의 게이트에 접속된다.

도 21b는 도 21a의 시스템 230의 동작을 설명하는 타이밍도이다. 도 21b의 첫 번째 두 줄은 각각 PHASE 1 및 PHASE 2 CLOCK 신호의 레벨을 나타낸다. 도 21b의 마지막 두 줄은 각각 페이즈 1 회로(231) 및 페이즈 2 회로(232)에 의한 유효 데이터 출력(즉, 각 페이즈 회로의 최종단에 의한 출력) 기간을 나타낸다. 이들 파형을 살펴볼 때, 시간 t0직후, 시스템 230은 대기 상태로 실행된다고 가정한다. t0과 t1사이에서, PHASE 1 CLOCK 신호는 로우이지만 PHASE 2 CLOCK 신호는 하이이다. 따라서, 도 21a로부터, t0과 t1사이에서 회로 231의 각 단은 프리차지 페이즈(도 21b에서는 "PR"로 약어화함)에 있다. 그러나, 상기의 종래 기술과는 반대로, t0과 t1사이의 다음의 특징에 유의한다. 먼저, 2개의 분리 클럭 신호가 동작의 다수 페이즈를 제어하기 위해 사용되는 것이 바람직하다. 두 번째로, 이들 클럭이 일반적으로 상보적이라고 고려할 수 있다. 이것은 다음의 설명에서 항상 그렇지만은 않다. 분리 클럭이 주어질 때, 각각의 효과에 유의한다. 회로 231의 첫 번째 3개의 단은 로우인 PHASE 1 CLOCK 신호에 응답하여 프리차지 페이즈에 있다. 그러나, 회로 231의 최종 단(즉, 네 번째 단 231<sub>4</sub>)은 하이인 PHASE 2 CLOCK 신호에 응답하여 프리차지 페이즈에 있고, 이때, 하이 신호가 반전되고 나서 p채널 프리차지 트랜지스터(231<sub>PT</sub>)의 게이트에 접속된다. 이러한 후자의 동작 및 접속의 중요한 점은 양 CLOCK 신호가 로우가 되도록 시스템 230이 전환될 때 다음에 설명되는 t4에서 더욱 용이하게 나타난다. t0와 t1 사이의 시간에 이어져서, 페이즈 2 회로(232)는 동작의 평가 페이즈(도 21b에서는 "EV"로 약어화됨)에 있다. 따라서, t0 조금후의 포인트에서, 데이터는 페이즈 2 회로(232)의 각 단을 관통하여 도 21b의 네 번째 행에 도시한 바와 같이 유효 데이터가 페이즈 2

회로(232)의 최종 단에 의해 출력된다. 마지막으로 상기 도 20a 및 도 20b에서 도입된 경우에서와 같이, 페이즈 2 회로(232)가 t1에서 그의 평가 페이즈 끝낸 후라도  $t_h$ 로 나타낸 짧은 홀드 시간 동안 그의 출력에 유효 데이터를 계속 홀드하는 것에 유의한다.

t1에서, PHASE 1 CLOCK 신호는 로우에서 하이로 천이하지만, PHASE 2 CLOCK은 하이에서 로우로 천이한다. 따라서, 페이즈 1 회로(231)는 그의 동작의 평가 페이즈를 시작하고, t1에서 조금 지나서 도 21b의 세 번째 줄에 도시한 바와 같이 유효 데이터를 출력한다. 여기서, 페이즈 1 회로(231)의 첫 번째 3개의 단이 하이인 PHASE 1 CLOCK 신호에 응답하여 평가 페이즈에 있고 그 단의 각각에 대한 프리차지 트랜지스터 및 방전 트랜지스터에 접속되는 것에 유의한다. 그와 반대로, 페이즈 1 회로(231)의 단 231<sub>4</sub>는 로우인 PHASE 2 CLOCK 신호에 응답할 뿐만 아니라 하이인 PHASE 1 CLOCK 신호에 응답하여 평가 페이즈에 있고, 이때 로우 신호는 반전되고 나서 p채널 프리차지 트랜지스터(231<sub>4PT</sub>)의 게이트에 접속되고, 하이 신호는 n채널 방전 트랜지스터(231<sub>4DT</sub>)의 게이트에 접속된다. 또한, 페이즈 1 회로의 평가 페이즈가 t1 직후 홀드 시간  $t_h$  동안 페이즈 2 회로(232)의 출력에 유지된 데이터에 의해 트리거되는 것에 유의한다. 또한, t1에서 페이즈 2 회로(232)는 그의 동작의 프리차지 페이즈로 전환된다. 따라서, 홀드 시간  $t_h$  후, 페이즈 2 회로(232)의 출력은 일단 단 232<sub>4</sub>의 프리차지 노드(232<sub>4PN</sub>)가 인버터(232<sub>4IN</sub>)의 출력에 천이를 충분히 일으키는 하이로 프리차지되면 변할 수 있다.

상기 페이즈 회로 231 및 232의 상보 동작은 t4까지 계속된다. 그러나, t4에서, 페이즈 회로 231 및 232의 가능하다면 많은 단들이 적어도 하나의 클럭 기간(즉, 프리차지 페이즈와 평가 페이즈의 결합 기간) 동안 동작의 프리차지 페이즈에 있고 또한 그 상태 동안 프리차지 노드가 방전되지 않도록 시스템 228이 이미 아이들 상태라고 하였던 상태로 되는 것이 바람직하다. 그렇게 하는 것에 의해, 동작의 평가 페이즈 동안 발생할 수 있는 전류 누설이 회피된다. 따라서, t4에서 PHASE 2 CLOCK 신호가 로우를 유지하고 PHASE 1 CLOCK 신호가 하이에서 로우로 천이하는 것에 유의한다. 따라서, t4에서 t5까지, 페이즈 1 회로(231)의 하나의 단을 제외한 모두 및 페이즈 2 회로(232)의 모든 단은 다음에 설명하는 바와 같이 동작의 프리차지 페이즈에 있게 되고, 이 상태는 도 21b의 첫 번째 두 줄에 t4와 t5 사이에 확장된 프리차지 페이즈로서 도시되어 있다. 이때 프리차지 페이즈에 있지 않은 페이즈 1 회로(231)의 하나의 단에 대하여, 상기로부터, 필수적인 것이 아니면, 일단 그의 다수 페이즈 중 하나 이상의 단이 프리차지 페이즈로 유지되면 회로의 데이터 상태를 유지하는 것이 바람직하다고 하였던 것을 상기한다. 따라서, 이점에 있어서, 본 발명 분야의 숙련자는 단 231<sub>4</sub>로의 PHASE 2 CLOCK 신호의 반전된 클럭 결합이 이러한 목적을 달성하는 것을 이해할 것이다. 구체적으로, t4에서, PHASE 1 CLOCK 신호가 하이에서 로우로 천이하는 것을 상기한다. 이 신호가 (p채널 프리차지 트랜지스터 231<sub>1PT</sub>, 231<sub>2PT</sub> 및 231<sub>3PT</sub>의 게이트에 대한 것과 같이) p채널 프리차지 트랜지스터(231<sub>4PT</sub>)의 게이트에 접속되면, t4에서 또는 매우 짧은 시간 후에 인버터(231<sub>4IN</sub>)로부터의 데이터 출력은 프리차지 노드(231<sub>4PN</sub>)가 V<sub>DD</sub>를 향해 상승할 때 오버라이트된다. 그러나, 이러한 접속 대신, p채널 프리차지 트랜지스터(231<sub>4PT</sub>)의 게이트가 PHASE 2 CLOCK 신호의 상보 신호에 접속되는 것을 상기한다. 따라서, t4에서 PHASE 2 CLOCK 신호는 t3으로부터와 같이 로우이다. 따라서, 그의 상보 신호는 하이이고 p채널 프리차지 트랜지스터(231<sub>4PT</sub>)는 t3에서 오프되어 t4 후 오프 상태를 유지한다. 따라서, 단 231<sub>4</sub>의 t4까지, 프리차지 트랜지스터 및 방전 트랜지스터는 도통하지 않는다. 프리차지 트랜지스터(231<sub>4PT</sub>)가 도통하지 않으므로, 인버터(231<sub>4IN</sub>)에 의한 데이터 출력은 프리차지 동작에 의해 변할 수 없다. 또한, 방전 트랜지스터(231<sub>4DT</sub>)가 현재 도통하고 있지 않으므로, 인버터(231<sub>4IN</sub>)에 의한 데이터 출력은 평가 동작에 의해 변경(즉, 방전)될 수 없다. 따라서, 인버터(231<sub>4IN</sub>)로부터의 데이터 출력은 도 21b의 세 번째 줄에 도시한 바와 같이 t4 후 유지된다. 마지막으로, 단 231<sub>4</sub>가 이러한 형태로 데이터를 저장하므로, (마찬가지 방법으로 데이터를 저장하는 다른 단과 같이) 이하 이것을 데이터 저장단이라고 한다. 따라서, 데이터 저장단이 적어도 t4와 t5 사이의 시간동안 데이터를 유지하고, 이 확장된 시간이 모든 회로단의 프리차지 페이즈와 평가 페이즈의 결합 기간과 반드시 같거나 또는 그보다 큰 것을 유의한다.

이상은 전체 회로의 하나의 단을 제외한 모든 단이 동작의 프리차지 페이즈로 되는 때(즉, 아이들 상태)의 시스템 230의 동작을 설명하고 또한 그 단이 적어도 하나의 클럭 기간에 걸쳐 데이터를 저장하는 것을 설명하였고, 도 21b의 나머지 부분은 유효 데이터 출력을 유지하는 방법으로 그의 대표적 상보 프리차지/평가 동작으로 회로를 재기동하는 것을 설명한다. t5에서, PHASE 2 CLOCK 신호는 로우에서 하이로 천이한다. 그 결과, 페이즈 1 회로(231)의 단 231<sub>1</sub>, 231<sub>2</sub> 및 231<sub>3</sub>이 동작의 프리차지 페이즈를 유지하고 데이터 저장단 231<sub>4</sub>가 데이터를 저장하지만, 페이즈 2 회로(232)는 그의 평가 페이즈를 시작한다. 그 결과, 단 231<sub>1</sub>은 단 231<sub>4</sub>에 의해 프리차지 동안 유지된 데이터에 따라 평가될 수 있다. 또한, 데이터 저장단(즉, 단 231<sub>4</sub>의 바로 다음 단(예를 들면 단 232<sub>1</sub>)이 데이터 저장단에서의 데이터가 오버라이트되기 전 그의 평가 페이즈

로 전환되므로 이 동작이 보장되는 것에 유의한다. 도 21b를 계속 설명하면, t5후 짧은 시간에 있어서, 페이즈 2 회로(232) 내의 나머지 단은 평가하고, 유효 데이터 출력은 페이즈 2 회로(232)에서의 데이터로서 인버터( $232_{4IN}$ )에 의해 제공된다. t6에서, PHASE 1 CLOCK 신호 및 PHASE 2 CLOCK는 전환하고, 이 점에서 앞쪽으로 동작은 시스템 228이 동작의 확장된 프리차지 페이즈에 있기 전 상기의 방법에서와 같이 계속된다.

상기에 부가하여, 도 21a의 각 인버터가 p채널 피드백 트랜지스터에 접속되고 이들 인버터(즉, 인버터  $231_{1IN}$ ,  $231_{4IN}$  및  $232_{1IN}$ )의 일부가 n채널 피드백 트랜지스터에도 물론 접속되는 것에 유의한다. 각 트랜지스터에 대하여, 프리차지 전압  $V_{DD}$ 가 대응하는 프리차지 노드에 더이상 접속되지 않는 후이지만, (주어진 평가 기간동안 모두 방전되면) 프리차지 노드가 방전되기 전에 p채널 트랜지스터는 대응하는 인버터에서의 로우 출력을 유지한다. 인버터  $231_{1IN}$  및  $232_{1IN}$ 에 대하여, 각각은 n채널 피드백 트랜지스터에도 접속되는 데, 이것은 이들 인버터에 대응하는 단이 홀드 시간 래치로부터 입력을 수신하고, 따라서 짧은 기간동안만 유효 입력 데이터를 나타낼 수 있기 때문이다. 그러한 경우에 있어서, 이러한 짧은 기간 데이터가 그 단의 프리차지 노드에 대하여 방전하면, n채널 피드백 트랜지스터는 다음 프리차지 페이즈까지 인버터의 하이 출력을 유지한다. 인버터( $231_{4IN}$ )에 대하여, 그것이 데이터 저장단인 단에 대응하는 것을 상기한다. 또한, 아이들 상태 동안, 데이터 저장단은 프리차지되지도 방전되지도 않고, 따라서 프리차지 노드( $231_{4IN}$ )에서의 전압 반전은 플로팅할 수 없다. 그러나, 모든 잘못된 데이터를 피하기 위해, p채널 및 n채널 트랜지스터를 모두 포함하는 것에 의해 이러한 아이들 상태 동안 프리차지 노드에서의 전압이 유지된다.

상기가 주어질 때, 본 발명 분야의 숙련자는 시스템 230의 여러 가지 효과를 이해하고, 더 나아가서 본 발명의 요지를 이탈하지 않고 변경될 수 있다는 것을 이해할 것이다. 예를 들면, 데이터 저장단 이외의 전체 시스템은 동작의 프리차지 페이즈로 될 수 있다. 따라서, 시스템이 상기의 임의의 LVT 실시예의 경우에서와 같이 평가 기간이 줄어들 수 있는 또는 일시적으로 제한되는 것이면, 시스템 230은 회로의 데이터 상태를 저장하면서 이러한 효과를 달성한다. 즉, 이 기간 동안 시스템 230내에서 방전되는 단은 없고, 따라서, 각 방전 경로를 따른 전류 누설의 위험은 1절 및/또는 2절의 원리가 이들 단의 방전 경로 내에서 사용된다는 가정이 제거되면 줄어든다. 다른 예로서, 그렇지 않으면 또 다른 복잡한 래치 구조를 필요로 하는 리소스가 필요없다. 또 다른 예로서, 시스템은 순환하는 것으로 도시되고 각 페이즈 회로에 주어진 수의 단이 있지만, 최종 회로에서 최초 회로로의 데이터 순환없이 또한 각 회로 내에 같은 개수의 단이 없더라도, 시스템은 다른 연속 동적 논리 회로에 사용될 수 있다. 또 다른 예로서, 상기 1절 및 2절의 여러 예에 의해 설명된 것과 같은 다른 종류의 동적 논리 회로를 사용하여 여러 단을 구성할 수 있다. 또 다른 예로서, 상술한 바와 같이, 각 회로는 적어도 하나의 단 만을 포함하기만 하면 되고, 각 회로는 임의의 시간에 네트워크를 통한 상이한 경로를 갖는 회로의 더 큰 네트워크의 일부일 수 있다. 또 다른 예로서, 단  $231_4$ 가 데이터 저장단으로 되도록 시스템 230이 동작하는 것에 유의한다. 그러나, 대안으로서, PHASE 1 CLOCK 신호는 (그 게이트를 PHASE 2 CLOCK에 접속하기보다는) 인버터를 거쳐 단  $232_4$ 의 프리차지 트랜지스터 ( $232_{4PT}$ )의 게이트에 결합된다. 이때, 단  $232_4$ 도 PHASE 2 CLOCK 신호가 프리차지 레벨로 하강한 직후 확장된 프리차지 페이즈를 시작하는 것에 의해 저장단으로서 동작할 수 있다. 또한, 단  $232_4$ 에 대한 또 다른 접속이 단  $231_4$ 에 대한 접속이 도 21a에 도시한 바와 같이 유지되면서 이루질 수 있는 것에 의해, 확장된 프리차지 페이즈 동안 단  $232_4$ 와  $231_4$  중의 어느 것이 데이터를 저장하게 하는 가를 선택할 수 있고 이러한 선택이 확장된 프리차지 페이즈 직전 평가 페이즈를 마지막으로 통과한 어느 쪽 클럭 신호에 의해 지정되는 것에 유의한다. 또 다른 예로서, 1절 및 2절에서, 방전 트랜지스터를 동적 논리 회로에서 제거할 수 있고 그러한 회로는 그렇게 하지 않으면 동작의 프리차지 페이즈 동안 방전하지 않는다고 설명된 것을 상기하고, 따라서 이 원리는 트랜지스터  $231_{2DT}$  내지  $231_{4DT}$ 와 트랜지스터  $232_{2DT}$  내지  $232_{4DT}$ 를 제거하는 것에 의해 3절의 실시예에도 물론 적용될 수 있다. 마지막 예로서, 기타의 다음 실시예의 예에 의해 설명되는 바와 같이, 본 실시예도 주어진 페이즈 회로 내의 모든 단이 데이터 저장단이 되도록 하는 한편, 시스템의 나머지 단은 동작의 확장된 프리차지 페이즈로 한다. 이러한 특징은 때때로 수차례의 설계 반복후 하나의 페이즈 회로의 최종단에 접속된 래치 전에 위치하는 단에 데이터를 저장하는 것이 바람직한 회로 설계에 있어서 상당히 유용하다고 증명되지만, 지금까지 상당한 부가적인 노력 및/또는 하드웨어가 없으면 그렇게 하는 것이 불가능하였다. 마지막으로, 2개의 페이즈만을 도시하고 있지만, 본 명세서에 실시예들은 3개 이상의 페이즈를 수용하도록 변경될 수 있는 것은 물론이다.

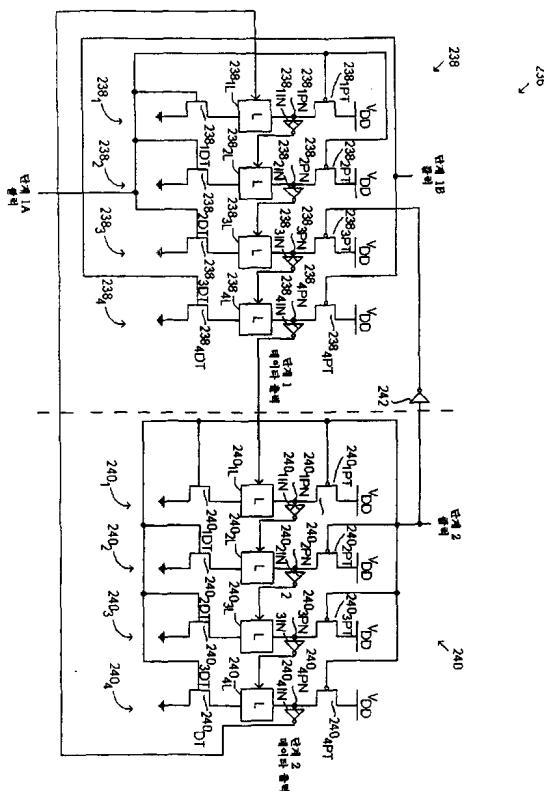

도 22a는 236으로 나타낸 논리 회로 시스템의 개략도이다. 시스템 236은 많은 점에 있어서 도 21a의 시스템 230과 유사 하지만, 다음에 상세히 설명하는 바와 같이, 시스템 236은 다상 회로의 나머지 단이 확장된 시간 동안 프리차지 페이즈에 있을 때 데이터 상태가 페이즈 회로의 최종단 이외의 단에 저장되는 다상 회로를 설명한다. 구체적으로, 도 22a의 예에서, 회로 238의 세 번째 단(예를 들면, 단  $238_3$ )은 다상 회로의 나머지 단이 확장된 시간 동안 프리차지 페이즈에 있을 때 데이터 저장단의 기능을 수행한다. 시스템 236의 상세를 다시 보면, 시스템은 페이즈 1 회로(238) 및 페이즈 2 회로(240)를 포함한다. 또한, 종래 번호 매김 형태가 사용되어 연속 번호 매김을 사용하여 주어진 페이즈 회로 내의 각 단을 식별하고 주

어진 단 내의 각 항목을 그 항목 뿐만 아니라 그 단에 따라 번호매김한다. 예를 들면, 페이즈 1 회로(238)의 첫 번째 단은 238<sub>1</sub>이고, 프리차지 노드는 238<sub>1PN</sub>이고, 프리차지 트랜지스터는 238<sub>1PT</sub>이고, 출력 인버터는 238<sub>1IN</sub>이며, 방전 경로를 구성하는 논리 회로는 238<sub>1IL</sub>이고, 방전 트랜지스터는 238<sub>1DT</sub>이다. 시스템 238은 3개의 분리 클럭 신호, 즉 (1) PHASE 1A CLOCK 신호, (2) PHASE 1B CLOCK 신호, (3) PHASE 2 CLOCK 신호를 포함한다. 다음에 설명하는 하나의 예외에 의하면, 페이즈 1 회로(238)는 PHASE 1A CLOCK 및 PHASE 1B CLOCK에 의해 클럭되지만, 페이즈 2 회로(240)는 PHASE 2 CLOCK에 의해 클럭된다. 이들 신호에 의한 클럭의 더욱 상세한 분석은 다음과 같다.