(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4987723号

(P4987723)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年5月11日(2012.5.11)

(51) Int.Cl.

H03H 7/38 (2006.01)

H04B 1/04 (2006.01)

F 1

H03H 7/38

H04B 1/04Z

B

請求項の数 3 (全 11 頁)

(21) 出願番号 特願2007-542410 (P2007-542410)

(86) (22) 出願日 平成17年11月16日 (2005.11.16)

(65) 公表番号 特表2008-521318 (P2008-521318A)

(43) 公表日 平成20年6月19日 (2008.6.19)

(86) 國際出願番号 PCT/IB2005/053775

(87) 國際公開番号 WO2006/054245

(87) 國際公開日 平成18年5月26日 (2006.5.26)

審査請求日 平成20年11月14日 (2008.11.14)

(31) 優先権主張番号 04105944.5

(32) 優先日 平成16年11月19日 (2004.11.19)

(33) 優先権主張国 歐州特許庁(EP)

前置審査

(73) 特許権者 300002160

エプコス アクチエンゲゼルシャフト

E P C O S A G

ドイツ連邦共和国 ミュンヘン ザンクト

マルティン-シュトラーセ 53

S t. -M a r t i n - S t r a s s e

53, D-81669 Muench e

n, G e r m a n y

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100103263

弁理士 川崎 康

最終頁に続く

(54) 【発明の名称】 増幅段出力に結合の負荷ラインを備えるデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

增幅段の出力に結合された信号ラインを備えると共に、前記信号ラインを前記増幅段に整合させるための被制御整合段を備え、

アンテナ段を整合させるための付加被制御整合段をさらに備え、この付加被制御整合段はスイッチング段を介して前記被制御整合段に結合され、

前記被制御整合段は、

前記信号ラインから信号を取り出すための取り出し手段と、

前記信号の信号パラメータを検出するための検出手段と、

前記整合のために前記検出に応答して調整可能インピーダンスネットワークを制御するための制御手段と、

を備え、

前記取り出し手段は第1素子と第2素子とを備え、前記検出手段は前記第1素子に結合された第1検出器システムと前記第2素子に結合された第2検出器システムとを備え、前記調整可能インピーダンスネットワークは前記第1検出器システムにより実行される第1検出に応答して制御される第1調整可能インピーダンスネットワークを備えると共に前記第2検出器システムにより実行される第2検出に応答して制御される第2調整可能インピーダンスネットワークを備え、

前記第1検出器システムと前記第2検出器システムは、第1ピーク検出器、第2ピーク検出器、第1ミキサ、第2ミキサ、位相シフタをそれぞれ備え、

10

20

前記第1検出器システムにおいて、

前記第1ピーク検出器は前記第1素子の入力電圧を受信し、

前記第2ピーク検出器は前記第1素子の入力と出力との間の電圧を受信し、

前記第1ピーク検出器の入力が前記第1ミキサの第1入力に結合され、

前記第2ピーク検出器の入力が前記位相シフタを介して前記第1ミキサの第2入力に結合され、

前記第1ピーク検出器の入力が前記第2ミキサの第1入力に結合され、

前記第2ピーク検出器の入力が前記第2ミキサの第2入力に結合されており、

前記第2検出器システムにおいて、

前記第1ピーク検出器は前記第2素子の入力電圧を受信し、

10

前記第2ピーク検出器は前記第2素子の入力と出力との間の電圧を受信し、

前記第1ピーク検出器の入力が前記第1ミキサの第1入力に結合され、

前記第2ピーク検出器の入力が前記位相シフタを介して前記第1ミキサの第2入力に結合され、

前記第1ピーク検出器の入力が前記第2ミキサの第1入力に結合され、

前記第2ピーク検出器の入力が前記第2ミキサの第2入力に結合されており、

前記第1素子と前記第2素子は抵抗であるデバイス。

### 【請求項2】

前記付加被制御整合段は、

20

前記信号ラインから信号を取り出すための取り出し手段と、

前記信号の信号パラメータを検出するための検出手段と、

前記整合のために前記検出に応答して調整可能インピーダンスネットワークを制御するための制御手段と、

を備える請求項1に記載のデバイス。

### 【請求項3】

少なくとも1つの検出器システムは、前記信号のうちの1つに関するピーク情報を検出する第1ピーク検出器と、前記信号のうちの他の1つに関するピーク情報を検出する第2ピーク検出器と、前記信号の位相情報を検出する位相検出器と、を備える請求項1又は2に記載のデバイス。

### 【発明の詳細な説明】

30

### 【技術分野】

### 【0001】

この発明は増幅段 [an amplifier stage] 出力に結合された負荷ライン [load line] に関し、さらに被制御整合段 [a controlled matching stage] に関し、付加被制御整合段 [a further controlled matching stage] に関し、その方法に関し、そのプロセッサプログラム製品に関する。

### 【0002】

このような装置の例は、移動電話、無線インターフェース、さらに送信機および/または受信機である。

### 【背景技術】

40

### 【0003】

先行技術デバイスは、国際特許公開02/063782A2より既知とされ、これは、その図2においてスイッチを介してアンテナに結合された電力増幅器（増幅段）を備えるセルラ電話（デバイス）を開示する。電力増幅器の出力とスイッチとの間の結合は、負荷ラインと呼ばれる。その図6～図8で、国際特許公開02/063782A2は、可変整合ネットワーク（被制御整合段）を開示する。これらの可変整合ネットワークは、アンテナをスイッチまたは電力増幅器に整合させる。

### 【0004】

既知のデバイスは、とりわけ、その可変整合ネットワークがアンテナの不整合を補償するだけであるという事実により、不利である。既知のデバイスは、アンテナ不整合とは別

50

の付加不整合 [ further mismatch ] を、相対的に低い帯域に対して補償する。

【発明の開示】

【発明が解決しようとする課題】

【0005】

この発明の目的は、とりわけ、アンテナ不整合とは別の付加不整合を、より高い帯域に対して補償するデバイスを提供することである。

【0006】

この発明のさらなる目的は、とりわけ、被制御整合段、付加被制御整合手段、アンテナ不整合とは別の付加不整合を、より高い帯域に対して補償する方法およびプロセッサプログラム製品を提供することである。

10

【課題を解決するための手段】

【0007】

この発明に係るデバイスは、増幅段の出力に結合された負荷ラインを備え、前記増幅段に対して前記負荷ラインを整合するための被制御整合段を備える。

【0008】

前記増幅段に対して前記負荷ラインを整合するための被制御整合段を導入することにより、この発明に係るデバイスは、負荷ラインと増幅段の出力との間の不整合の形態での付加不整合を、より高い帯域に対して補償する。

【0009】

この発明に係るデバイスは、被制御整合段が増幅段の線形性と効率を向上させるであろうし、サイズおよび／またはコストのさらなる低減に対して相殺（トレードオフ）できる信頼性の要求を和らげるであろうし、この装置のユーザが以前よりも興奮しない場合のユーザの親しみを向上させるという点でさらに有利である。

20

【0010】

アティア・ゾロミー (Attila Zolomy)、フェレンク・メンエイ (Ferenc Mernyei)、ヤノス・エーデリ (Janos Erdelyi)、マチス・パルドン (Matthijs Pardoen)、ゲボ・トス (Gabor Toth) らによる、統合ハンガリ株式会社 (Integration Hungary Ltd.)、ザホニー・ユー.7.1031、ブダペスト、ハンガリ (Zahony u.7.1031 Budapest, Hungary) および統合組合有限会社、110パイオニア・ウェイ、ユニット・エル、マウンテン・ビュー、カルフォルニア 94041、U.S.A.、0-7803-8333-8/04/\$20.00(C)2004 IEEE の文献「高Qアンテナを適用するRF送信機IC用自動アンテナ同調（"Automatic Antenna Tuning for RF Transmitter IC Applying High Q Antenna"）」は、その図3でアンテナ不整合を補償するためのアンテナ同調回路（被制御整合段）を開示する。この文献は、負荷ラインを増幅段に整合させるための被制御整合段を示していない。

30

【0011】

さらに、このデバイスのモードおよび／または出力電力のインピーダンスにおける増幅段の出力でのインピーダンスに適合する増幅段の出力での被制御インピーダンスネットワークを用いることが一般的な常識であることは注意されるべきである。より高い（より低い）出力電力は負荷ラインのより低い（より高い）インピーダンスを選び、より高い（より低い）電圧源は負荷ラインのより高い（より低い）インピーダンスを選ぶ。これは、負荷ラインの増幅段への最適な整合を自動制御することとは完全に異なっている。この発明によれば、負荷ラインの増幅段への整合の制御がモード依存であっても良いが、例えば出力電力または供給電圧に依存して、1つおよび同一のモード内で行なわれても良い。

40

【0012】

被制御整合段は、例えば、オープンループ（前方制御）またはクローズドループ（後方制御）のようなループを介して、（自動で）制御される整合段である。

【0013】

この発明によるデバイスの実施形態は、アンテナ段を整合するための付加被制御整合段

50

であって、被制御整合段に結合される付加被制御整合段をさらに備えることにより定義される。この付加被制御整合段は、アンテナ不整合を補償するであろう。アンテナ段は、例えば、アンテナおよび／またはアンテナ接続を備えている。

【0014】

この発明によるデバイスの実施形態は、スイッチング段を介して被制御整合段に結合された付加被制御整合段により定義される。このスイッチング段は例えば、被制御整合段を介して（增幅段の出力をスイッチング段に結合するために被制御整合段の一部を形成する負荷ラインを有する）増幅段の出力に結合された入力を備え、受信段に結合された出力を備え、さらに、付加被制御整合段を介してアンテナ段に結合された入／出力を備える。

【0015】

この発明によるデバイスの実施形態は、

前記負荷ラインから信号を取り出すための取り出し手段と、

前記信号の信号パラメータを検出するための検出手段と、

前記整合のために前記検出に応答して調整可能インピーダンスネットワークを制御するための制御手段と、

を備える前記被制御整合段により定義される。

【0016】

調整可能インピーダンスネットワークを制御することにより、負荷ラインは増幅段に整合される。

【0017】

この発明によるデバイスの実施形態は、第1素子と第2素子とを備える前記取り出し手段、前記第1素子に結合された第1検出器システムと前記第2素子に結合された第2検出器システムとを備える前記検出手段、前記第1検出器システムにより実行される第1検出に応答して制御される第1調整可能インピーダンスネットワークを備えると共に前記第2検出器システムにより実行される第2検出に応答して制御される第2調整可能インピーダンスネットワークを備える前記調整可能インピーダンスネットワークにより定義される。この被制御整合段は、2つまたはそれ以上のサブ段を備える。

【0018】

この発明によるデバイスの実施形態は、

前記負荷ラインから信号を取り出すための取り出し手段と、

前記信号の信号パラメータを検出するための検出手段と、

前記整合のために前記検出に応答して調整可能インピーダンスネットワークを制御するための制御手段と、

を備える前記付加被制御整合段により定義される。

【0019】

この発明によるデバイスの実施形態は、第1素子と第2素子とを備える前記取り出し手段、前記第1素子に結合された第1検出器システムと前記第2素子に結合された第2検出器システムとを備える前記検出手段、前記第1検出器システムにより実行される第1検出に応答して制御される第1調整可能インピーダンスネットワークを備えると共に前記第2検出器システムにより実行される第2検出に応答して制御される第2調整可能インピーダンスネットワークを備える前記調整可能インピーダンスネットワークにより定義される。この付加被制御整合段は、2つまたはそれ以上のサブ段を備える。

【0020】

この発明によるデバイスの実施形態は、前記信号のうちの1つに関するピーク情報を検出する第1ピーク検出器と、前記信号のうちの他の1つに関するピーク情報を検出する第2ピーク検出器と、前記信号の位相情報を検出する位相検出器と、を備える少なくとも1つの検出器システムにより定義される。第1検出器システムは、例えば前記複数の信号間の位相差を検出する。第2検出器システムは、例えば前記複数の信号の各信号のピーク値と、前記複数の信号間の位相差のサインおよびコサインと、を検出する。各位相検出器は線形位相検出器または非線形位相検出器であっても良い。

10

20

30

40

50

## 【0021】

この発明による被制御整合段の実施形態およびこの発明による付加被制御整合段の実施形態並びにこの発明による方法の実施形態およびこの発明によるプロセッサプログラム製品の実施形態は、この発明によるデバイスの実施形態に対応する。

## 【0022】

この発明は、とりわけ、アンテナ不整合とは異なる付加不整合がデバイス内で生じるかもしれないという洞察に基づいており、とりわけ、この付加不整合が補償されるべき必要があるという基本概念に基づいている。

## 【0023】

この発明は、とりわけ、アンテナ不整合とは異なる付加不整合を、より高い帯域に対し 10 補償するデバイスを提供する問題を解決して、とりわけ、被制御整合段が増幅段の線形性および効率を向上させるであろうし、サイズおよび／またはコストのさらなる低減に対して相殺（トレードオフ trade-off）できる信頼性の要求を和らげるであろうし、この装置のユーザが以前よりも興奮しない場合のユーザの親しみを向上させるという点で有利である。

## 【0024】

この発明のこれらおよび他のアスペクトは、以下に説明される実施形態にしたがって明白となり、かつ、明瞭となるであろう。

## 【発明を実施するための最良の形態】

## 【0025】

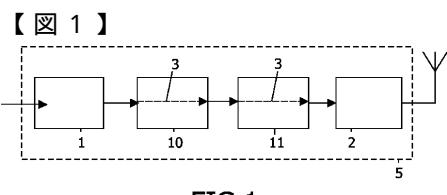

図1に示されたこの発明によるデバイス5は、増幅段1、この発明による被制御整合段 10、この発明による付加被制御整合段11、および、アンテナ段2を備える。増幅段1の出力は被制御整合段10の入力に結合されると共に、被制御整合段10の出力は付加被制御整合段11の入力に結合される。付加被制御整合段11の出力はアンテナ段2の入力に結合される。実際には、増幅段1の出力は、負荷ライン3を介してアンテナ段2の入力に結合され、両被制御整合段10、11はこの負荷ライン3を干渉している。増幅段1は例えば電力トランジスタを備えると共に、アンテナ段2は例えばアンテナおよび／またはアンテナ接続を備える。

## 【0026】

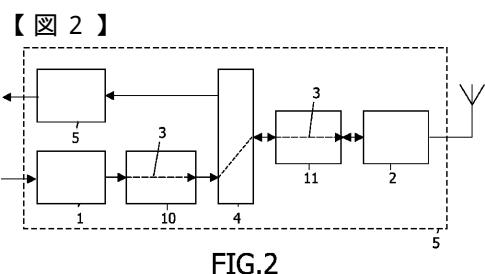

図2に示されたこの発明によるデバイス5は、増幅段1、この発明による被制御整合段 10、スイッチング段4、受信機段5、この発明による付加被制御整合段11、および、アンテナ段2を備える。増幅段1の出力は被制御整合段10の入力に結合されると共に、被制御整合段10の出力はスイッチング段4の入力に結合される。スイッチング段4の入／出力は、付加被制御整合段11を介してアンテナ段2の入／出力に結合される。実際には、増幅段1の出力は負荷ライン3を介してアンテナ段2の入／出力に結合され、両被制御整合段10、11およびスイッチング段4はこの負荷ライン3を干渉している。スイッチング段4の出力は、受信機段5の入力に結合される。

## 【0027】

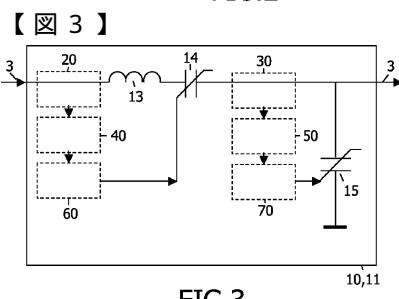

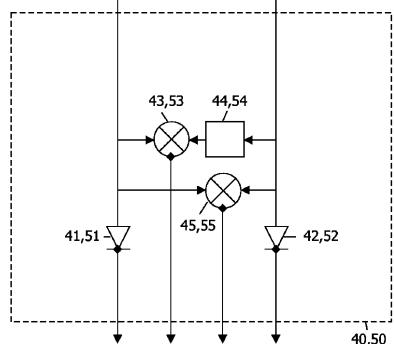

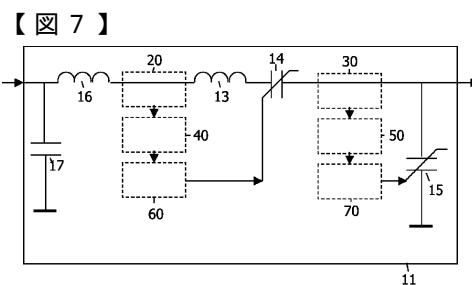

図3に示されたこの発明による（付加）被制御整合段10（11）は、負荷ライン3から複数信号を取り出す取り出し手段20、30、前記複数信号の信号パラメータを検出する検出手段40、50、および、前記整合のための前記検出に応答して調整可能インピーダンスネットワーク14、15を制御する制御手段60、70を備える。インダクタ13および調整可能インピーダンスネットワーク14（調整可能キャパシタバンク）の直列回路は取り出し手段20の第1部分の出力に結合されて負荷ライン3を遮断すると共に、取り出し手段30の第2部分の入力に結合され、その出力は調整可能インピーダンスネットワーク15（調整可能キャパシタバンク）を介して接地に結合される。

## 【0028】

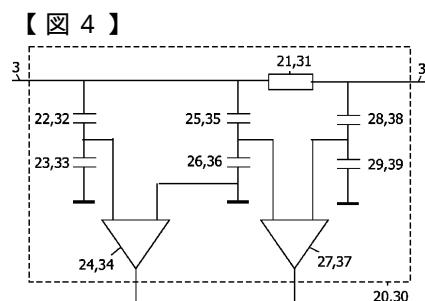

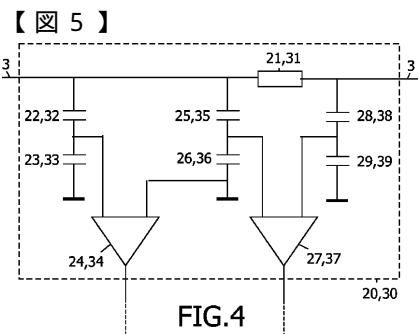

取り出し手段20（30）の第1（第2）部分は図4に示されると共に、例えば抵抗等の第1（第2）素子21（31）を備える。素子21（31）の入力側は、キャパシタ22（32）および23（33）の直列回路を介して接地に結合され、この直列回路の共通

10

20

30

40

50

接続点は増幅器 24 (34) の第1入力に結合され、その第2入力は接地に結合される。素子 21 (31) の入力側はさらに、キャパシタ 25 (35) および 26 (36) の直列回路を介して接地に結合され、この直列回路の共通接続点は増幅器 27 (37) の第1入力に結合される。素子 21 (31) の出力側はキャパシタ 28 (38) および 29 (39) の直列回路を介して接地に結合され、この直列回路の共通接続点は増幅器 27 (37) の第2入力に結合される。両増幅器 24, 27 (34, 37) は、負荷ライン 3 から取り出される複数信号を生成する。これらの複数信号は、検出手段 40 (50) の第1 (第2) 部分に供給される。受動素子 21 (31) の代わりに、インダクタや (部分的に) 偶数の非受動素子のような他の受動素子が用いられても良いし、それゆえに、これらは排除されない。

10

### 【0029】

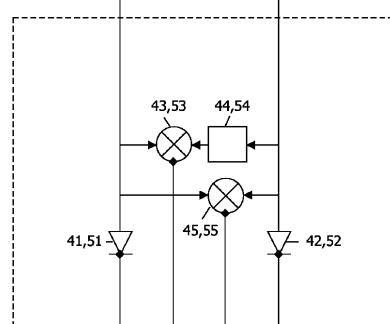

第1 (第2) 検出器システム 40 (50) が図5に示され、これは増幅器 24 (34) からの取り出し信号を受信するダイオードのような第1ピーク検出器 41 (51) を備えると共に、増幅器 27 (37) からの取り出し信号を受信するためのダイオードのような第2ピーク検出器 42 (52) を備える。第1ピーク検出器 41 (51) の入力は第1ミキサ 43 (53) の第1入力に結合されると共に、第2ピーク検出器 42 (52) の入力は位相シフタ 44 (54) を介して第1ミキサ 43 (53) の第2入力に結合される。第1ピーク検出器 41 (51) の入力は第2ミキサ 45 (55) の第1入力に結合されると共に、第2ピーク検出器 42 (52) の入力は第2ミキサ 45 (55) の第2入力に結合される。第1ピーク検出器 41 (51) は例えば検出手段 40 (50) の第1 (第2) 部分での負荷ライン 3 に現れる電圧の振幅値を生成し、第2ピーク検出器 42 (52) は例えば検出手段 40 (50) の第1 (第2) 部分電負荷ライン 3 を介して流れる電流の振幅値を生成し、第1ミキサ 43 (53) は例えば両振幅値の積および検出された位相値のサイン (sine 正弦) であって値 2 により割り算された値 (以下、サイン積と呼ばれる) を生成し、さらに、第2ミキサ 45 (55) は例えば両振幅値の積および検出された位相値のコサイン (cosine 余弦) であって値 2 により割り算された値 (以下、コサイン積と呼ばれる) を生成する。

20

### 【0030】

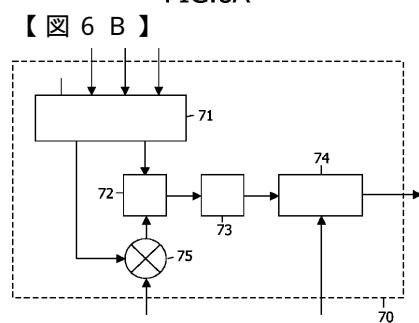

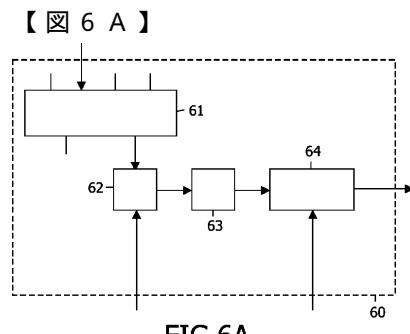

図6Aに示された制御手段 60 の第1部分は、第1ミキサ 43 からのサイン積を受信すると共にこのサイン積を加算器 62 の負入力に供給するための演算器 61 を備える。この加算器 62 は、例えば図示されないベースバンド制御から零度であるような基準位相信号を受信するための正入力と、リミッタ 63 を介してカウンタのような制御器 64 へ差分信号を供給する出力と、を備える。この制御器 64 は、図示されないベースバンド制御からのイネーブル信号を受信して、調整可能インピーダンスネットワーク 14 を制御する。このイネーブル信号は例えばカウンタへのアップ / ダウン値をロードするための立ち上がりエッジとアップ / ダウン・カウンティングを実行させるための立ち下がりエッジとを有するパルスを備える。

30

### 【0031】

図6Bに示された制御手段 70 の第2部分は、第1ミキサ 53 からのサイン積を受信すると共に第2ミキサ 55 からのコサイン積を受信し、さらに第2ピーク検出器 52 からの電流の振幅値を受信する演算器 71 を備える。この演算器 71 は、前記電流の振幅値の二乗により前記コサイン値を割り算してその結果の信号を加算器 72 の負入力に供給する。この加算器は、掛け算器 75 の出力に結合された正入力を備える。この掛け算器 75 は、前記演算器 71 からサイン積の符号を受け取ると共に、図示されないベースバンド制御から公称抵抗値を受け取る。加算器 72 は、リミッタ 73 を介してカウンタのような制御器 74 へ差分信号を供給する。この制御器 74 は、図示されないベースバンド制御からのイネーブル信号を受信すると共に、調整可能インピーダンスネットワーク 15 を制御する。このイネーブルシング信号は、例えば、前記カウンタへアップ / ダウン値をロードする立ち上がりエッジとアップ / ダウン・カウンティングを実行するための立ち下がりエッジとを有するパルスを備える。公称抵抗値は、取り出し手段 20 の第1部分の入力における前記

40

50

負荷ライン3で得られるべき抵抗値である。

【0032】

図7に示されたこの発明による付加被制御整合段11は、図3に示された付加被制御整合段とは、取り出し手段20の第1部分の入力での負荷ライン3においてインダクタ16がこの入力に対して直列に結合されている点のみが異なる。このインダクタ16の一方側はこの入力に結合され、他方側はキャパシタ17を介して接地に結合される。適切に機能させるために、掛け算器75は今や公称抵抗値の一部分、例えば公称抵抗値の半分を受け取るべきであり、この公称抵抗値の一部分は取り出し手段20の第1部分の入力における負荷ライン3で得られるべき抵抗値である。インダクタ16とキャパシタ17との共通接続点では、このため初めの抵抗値が同一の一部分をもつインピーダンス・アップ・コンバージョンにより得られるであろう。10

【0033】

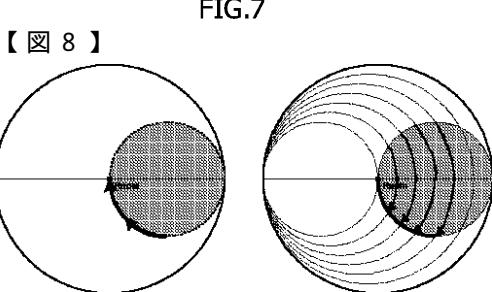

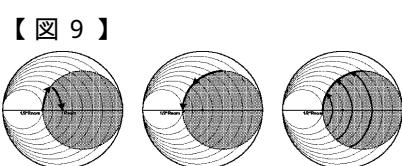

図8は、図3の(付加)被制御整合段10, 11に関するスミス・チャートを示す。適応性のあるインピーダンス・ダウント・コンバージョンは、(付加)被制御整合段10, 11により得られることができる。例えば、これは、不整合とされたアンテナの虚数部分を補償するため、および、より低い直列抵抗に対してアンテナ直列抵抗を変換するために用いられることができる。第2検出器システム50は、検知された電圧および電流を検出して、整合されたインピーダンス $|Z_{\text{matched}}|$ の大きさを決定する。さらに、この第2検出器システムは、電圧および電流間の位相差 $\phi_{\text{hi}}$ のサインおよびコサインを決定する。第2検出器システム出力信号の適切な結合は、整合された抵抗値 $R_{\text{matched}} = A_u / A_i \cos(\phi_{\text{hi}})$ をもたらす。この検出された抵抗値は、 $R_{\text{nom}}$ に設定された公称抵抗値と比較される。しかしながら、 $\cos(\phi_{\text{hi}})$ 項はゼロに対して対称であり、それゆえに、1つは容量性であり他は誘導性である: 2つの解を有する。唯一の解を得るため、ループが制御する抵抗値を表す公称抵抗値 $R_{\text{nom}}$ 掛け算の因数として、 $\sin(\phi_{\text{hi}})$ の符号が用いられる。容量性のシャント・ネットワークの属性[properties]が与えられたとすると、右手側のループは、この参照抵抗に向かって、一定の並列コンダクタンスの環状部分を超えて、図8のスミス・チャートの右手側に視覚化されているように、制御する。左手側の制御ループは、制御規準として $\sin(\phi_{\text{hi}}) = 0$ を用いる。その結果として、この規準は全体のリアクタンスがゼロになり、これにより所望のインダクタンスが $R_{\text{nom}}$ と等しくなるように帰着するようにキャパシタを変更する。スミス・チャートの解釈は以下の通りである。並列調整可能インピーダンスネットワーク15は、 $R_{\text{nom}}$ に等しい整合された直列抵抗 $R_{\text{matched}}$ を得るように変更される。このことは、位相がゼロに設定される参照位相信号 $\phi_{\text{hi\_ref}}$ に等しくなるように、直列のLCネットワーク(インダクタ13 + 調整可能インピーダンスネットワーク14)を変更することにより補償される容量性リアクタンスに帰着する。2030

【0034】

図9は、図7の付加被制御整合段用のスミス・チャートを示す。代替的な実施が、固定のアップ・コンバージョンに結合された適応性のあるLダウン・コンバージョンの結合を利用する。例えば、アンテナインピーダンスを $R_{\text{nom}}/2$ にまで下げる適応性のある変更は、2の因数の固定のアップ・コンバージョンにより結合されることができる。ネットワークの固定部分は、アンテナインピーダンスを電力トランジスタのコレクタに整合させるために通常は用いられる、(固定の)整合ネットワークの一部分となり得るであろう。その利点は、第1に、適応性のあるネットワークがインピーダンスを下方へと変換し、これにより、コレクタ整合のために必要とされる方向へと変換することである。したがって、ネットワークの固定部分は、正統的な出力整合ネットワークへと、より容易に同化されることができる。第2に、スイッチまたは制御の複雑さを除去するアップおよびダウン・コンバージョン間の再構築の必要がなくなる。第3に、図示されない適応性のあるTまたは適応性のあるP/I構成の場合の3つに比べて、僅か2つの検出器が必要とされるだけである。第4に、図示されない適応性のあるTまたは適応性のあるP/I構成に比べて、単純な制御アルゴリズムを用いることができる。その他の利点は、図3に示された実施形態に4050

比較して、より大きいインピーダンス適応レンジが得られ、これは、スミス・チャートのグレイの領域により視覚化される。

【0035】

図5に示される第1および第2検出器システム40, 50に関し、これらのシステムは線形位相検出器（ミキサ43, 53, 45, 55）を備える。ミキサ43, 53, 45, 55の入力にリミッタを導入することにより、非線形位相検出器が創出される。さらに、第1検出器システム40からの4つの出力信号の中の1つを用いるだけの制御手段60の第1部分を考慮して、また、第2検出器システム50からの4つの出力信号の中の1つを用いるだけの制御手段70の第2部分を考慮して、これらの検出器システムの特定部分が回避されることができる。

10

【0036】

図3, 図7に示された、インダクタ13と調整可能インピーダンスネットワーク14, 15よりなるもの以外の他のインピーダンスネットワーク構成は、例えば上述した適応性のあるTまたは適応性のあるPI構成のように、この発明の範囲から逸脱することなく、可能である。さらに、図3, 図7（一方側の20, 40, 60, 13, 14および他方側の30, 50, 70, 15）に示された2つのサブ段の代わりに、例えば直列LCネットワークまたは並列LCネットワークをもつただ1つのサブ段、または3つまたはそれ以上のサブ段は、この発明の範囲を逸脱することなく可能である。負荷ライン3を增幅段1へ整合させる被制御整合段10は、アンテナ段2を整合させる付加被制御整合段11と結合して用いられるべき必要性は必ずしもない。例えば、アンテナ段2が不整合から相対的に小さな損害を受ける場合、付加被制御整合段11は省略することができる。

20

【0037】

上述した実施形態はこの発明を限定するよりもむしろ表示すること、および、当業者が添付された請求項の範囲から逸脱することなく多くの代替的な実施形態を意図することが可能であろうことは、注目されるべきである。請求項において、括弧に挟まれて位置される何れの参照符号も請求項を限定するものとして解釈されるべきではない。「備える」という動詞の使用、および、その活用は、請求項の中で述べられた構成要素またはステップ以外のステップまたは構成要素の存在を排除するものではない。構成要素に先行する冠詞「a」または「a n」は複数のそのような構成要素の存在を排除するものではない。この発明は、いくつかの異なる構成要素を備えるハードウェアにより、および、最適にプログラムされたコンピュータにより、実施されても良い。いくつかの手段を列挙するデバイスの請求項においては、いくつかのこれらの手段は、1つおよび同一種類のハードウェアにより実施化されても良い。特定の対策が相互に異なる独立請求項に記載されているという単なる事実は、これらの対策の組み合わせが有利に用いられることができないということを示すものではない。

30

【図面の簡単な説明】

【0038】

【図1】増幅段、この発明による被制御整合段、この発明による付加被制御整合段、アンテナ段を備える、この発明によるデバイスを示す図。

40

【図2】増幅段、この発明による被制御整合段、スイッチング段、この発明による付加被制御整合段、アンテナ段を備える、この発明によるデバイスをより詳細に示す図。

【図3】この発明によるデバイス内で用いるために、この発明による（付加）被制御整合段を示す図。

【図4】図3の（付加）被制御整合段のための取り出し手段の第1（第2）部分をより詳細に示す図。

【図5】図3の（付加）被制御整合段のための検出手段の第1（第2）検出器システムをより詳細に示す図。

【図6A】図3の（付加）被制御整合段のための制御手段の第1部分（A）をより詳細に示す図。

【図6B】図3の（付加）被制御整合段のための制御手段の第2部分（B）をより詳細に示す図。

50

示す図。

【図7】この発明によるデバイス内で用いるために、この発明による付加被制御整合段を示す図。

【図8】図3の（付加）被制御整合段を示すスミス図である。

【図9】図7の付加被制御整合段を示すスミス図である。

FIG.1

FIG.2

FIG.3

FIG.4

FIG.5

FIG.5

FIG.8

FIG.9

---

フロントページの続き

(74)代理人 100107582

弁理士 関根 毅

(74)代理人 100118843

弁理士 赤岡 明

(74)代理人 100096921

弁理士 吉元 弘

(72)発明者 アドリアヌス、ファン、ベゾーイエン

オランダ国 5 6 5 6、アーアー、アンドーフェン、ケアオブ、プロフ. ホルストラーン、6

審査官 畑中 博幸

(56)参考文献 米国特許出願公開第 2 0 0 2 / 0 1 4 5 4 8 3 ( U S , A 1 )

特開 2 0 0 1 - 2 5 1 2 0 2 ( J P , A )

特開 2 0 0 1 - 0 1 6 0 4 4 ( J P , A )

特開 平 0 8 - 1 5 4 0 0 7 ( J P , A )

特開 平 1 1 - 2 5 1 9 5 6 ( J P , A )

特開 平 0 9 - 0 8 3 4 0 3 ( J P , A )

特開 2 0 0 3 - 2 0 4 2 3 7 ( J P , A )

特開 平 0 4 - 3 0 1 9 1 3 ( J P , A )

特開 昭 6 3 - 2 7 9 6 0 9 ( J P , A )

(58)調査した分野( Int.CI. , D B 名)

H03H 7/38

H04B 1/04