(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6324214号

(P6324214)

(45) 発行日 平成30年5月16日(2018.5.16)

(24) 登録日 平成30年4月20日(2018.4.20)

|                         |                                |

|-------------------------|--------------------------------|

| (51) Int.Cl.            | F 1                            |

| HO 1 L 29/786 (2006.01) | HO 1 L 29/78 6 1 7 N           |

| HO 1 L 21/336 (2006.01) | HO 1 L 29/78 6 1 2 Z           |

| HO 1 L 51/50 (2006.01)  | HO 1 L 29/78 6 1 8 B           |

| HO 5 B 33/08 (2006.01)  | HO 5 B 33/14 A<br>HO 5 B 33/08 |

請求項の数 5 (全 86 頁)

(21) 出願番号 特願2014-110113 (P2014-110113)

(22) 出願日 平成26年5月28日 (2014.5.28)

(65) 公開番号 特開2015-15459 (P2015-15459A)

(43) 公開日 平成27年1月22日 (2015.1.22)

審査請求日 平成29年5月18日 (2017.5.18)

(31) 優先権主張番号 特願2013-119149 (P2013-119149)

(32) 優先日 平成25年6月5日 (2013.6.5)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 井上 聖子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 松田 慎平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

発光素子と、

前記発光素子の駆動トランジスタとして機能する第1のトランジスタと、

前記第1のトランジスタと電気的に接続し、選択トランジスタとして機能する第2のトランジスタと、を含む画素を有し、

前記第1のトランジスタは、

絶縁表面上の第1のゲート電極と、

前記第1のゲート電極上の第1の絶縁膜と、

前記第1の絶縁膜を介して前記第1のゲート電極と重なる領域を有する第1の酸化物半導体膜と、

前記第1の酸化物半導体膜と電気的に接続され、前記第1の酸化物半導体膜上に端部を有する一対の電極と、

前記第1の酸化物半導体膜上の第2の絶縁膜と、

前記第2の絶縁膜を介して、第1の酸化物半導体膜上に設けられ、前記第1のゲート電極と重なる領域を有する第2のゲート電極と、を有し、

前記第1のゲート電極は、前記第2のゲート電極と接する領域を有し、

前記第2のゲート電極は、チャネル幅方向において前記第2の絶縁膜を介して前記酸化物半導体膜の側面と対向する領域を有し、

前記第2のトランジスタは、

10

20

前記絶縁表面上の第3のゲート電極と、

前記第3のゲート電極上の前記第1の絶縁膜と、

前記第1の絶縁膜を介して前記第3のゲート電極と重なる領域を有する第2の酸化物半導体膜と、

前記第2の酸化物半導体膜と電気的に接続され、前記第2の酸化物半導体膜上に端部を有する一対の電極と、

前記第2の酸化物半導体膜上の前記第2の絶縁膜と、を有し、

前記第2のトランジスタの前記一対の電極の間隔は、前記第1のトランジスタの前記一対の電極の間隔よりも大きいことを特徴とする表示装置。

## 【請求項2】

10

発光素子と、

前記発光素子の駆動トランジスタとして機能する第1のトランジスタと、

前記第1のトランジスタと電気的に接続し、選択トランジスタとして機能する第2のトランジスタと、を含む画素を有し、

前記第1のトランジスタは、

絶縁表面上の第1のゲート電極と、

前記第1のゲート電極上の第1の絶縁膜と、

前記第1の絶縁膜を介して前記第1のゲート電極と重なる領域を有する第1の酸化物半導体膜と、

前記第1の酸化物半導体膜と電気的に接続され、前記第1の酸化物半導体膜上に端部を有する一対の電極と、

20

前記第1の酸化物半導体膜上の第2の絶縁膜と、

前記第2の絶縁膜を介して、第1の酸化物半導体膜上に設けられ、前記第1のゲート電極と重なる領域を有する第2のゲート電極と、を有し、

前記第1のゲート電極は、前記第2のゲート電極と接する領域を有し、

前記第2のゲート電極は、チャネル幅方向において前記第2の絶縁膜を介して前記酸化物半導体膜の側面と対向する領域を有し、

前記第2のトランジスタは、

前記絶縁表面上の第3のゲート電極と、

前記第3のゲート電極上の前記第1の絶縁膜と、

前記第1の絶縁膜を介して前記第3のゲート電極と重なる領域を有する第2の酸化物半導体膜と、

30

前記第2の酸化物半導体膜と電気的に接続され、前記第2の酸化物半導体膜上に端部を有する一対の電極と、

前記第2の酸化物半導体膜上の前記第2の絶縁膜と、を有し、

前記第2のトランジスタの前記一対の電極の間隔は、前記第1のトランジスタの前記一対の電極の間隔よりも大きく、且つ、前記第2のトランジスタのカットオフ電流の値は前記第1のトランジスタのカットオフ電流の値より小さいことを特徴とする表示装置。

## 【請求項3】

40

請求項1又は2において、

前記第2のトランジスタは、

前記第2の絶縁膜を介して前記第2の酸化物半導体膜上に設けられ、前記第3のゲート電極と重なる第4のゲート電極を有し、

前記第3のゲート電極及び前記第4のゲート電極は、互いに接する領域を有することを特徴とする表示装置。

## 【請求項4】

請求項1乃至3のいずれか一において、

前記第1のゲート電極のチャネル長方向の幅は、前記第2のゲート電極のチャネル長方向の幅よりも大きいことを特徴とする表示装置。

## 【請求項5】

50

- 請求項 1 乃至 4 のいずれか一において、

前記第 1 のトランジスタの前記一対の電極の間隔は、前記第 2 のゲート電極のチャネル長方向の幅よりも大きいことを特徴とする表示装置。

- 【発明の詳細な説明】

- 【技術分野】

- 【0001】

- 本明細書等で開示する発明は、表示装置及びその作製方法に関する。特に、本発明の一態様は、酸化物半導体膜を有するトランジスタを備えた表示装置及びその作製方法に関する。

- 【背景技術】 10

- 【0002】

- 有機エレクトロルミネッセンス (Electroluminescence、以下 EL とも記す) 等の発光素子を用いた表示装置は視認性が高く、薄型化に最適であると共に、視野角にも制限が無いため、CRT (cathode ray tube) や液晶表示装置に替わる表示装置として注目されている。発光素子を用いたアクティブマトリクス型の表示装置は通常、少なくとも発光素子と、画素へのビデオ信号の入力を制御するトランジスタ (スイッチング (選択) 用トランジスタ) と、当該発光素子に供給する電流値を制御するトランジスタ (駆動用トランジスタ) とが、各画素に設けられている。

- 【0003】

- 表示装置に用いられているトランジスタは、ガラス基板上に形成された非晶質シリコン、単結晶シリコンまたは多結晶シリコンなどのシリコン半導体によって構成されている。 20

- 【0004】

- また、近年、シリコン半導体に代わって、半導体特性を有する金属酸化物 (酸化物半導体) をトランジスタに用いる技術が注目されている。例えば、酸化物半導体として、酸化亜鉛、または In - Ga - Zn 酸化物を用いたトランジスタを作製し、該トランジスタを表示装置の画素のスイッチング用トランジスタなどに用いる技術が開示されている (特許文献 1 参照)。

- 【先行技術文献】

- 【特許文献】

- 【0005】 30

- 【特許文献 1】特開 2007 - 123861 号公報

- 【発明の概要】

- 【発明が解決しようとする課題】

- 【0006】

- 発光素子を含む表示装置では、駆動用トランジスタのドレイン電流が発光素子に供給される。従って、駆動用トランジスタが劣化し、しきい値電圧が変動すると、発光素子の輝度も変動する。従って、駆動用トランジスタのしきい値電圧の変動を抑制することは、表示装置の画質向上を図る上で重要な課題である。

- 【0007】

- また、表示装置の高速駆動のためには、駆動用トランジスタとして、電界効果移動度の高いトランジスタを用いることが望まれる。 40

- 【0008】

- 一方、表示装置の低消費電力化のためには、選択用トランジスタとして、しきい値電圧がプラスとなる電気特性 (ノーマリーオフ特性ともいう。) のトランジスタを適用することが望まれる。または、選択用トランジスタとして、ドレイン電流 ( $I_d$ ) - ゲート電圧 ( $V_g$ ) 特性カーブにおいて、ゲート電圧が 0 V の時のドレイン電流 (カットオフ電流 ( $I_{cut}$ )) の値が低減されたトランジスタを適用することが望まれる。

- 【0009】

- 上述の問題に鑑み、本発明の一態様は、トランジスタのしきい値電圧の変動による影響が低減された表示装置を提供することを課題の一とする。または、本発明の一態様は、信 50

頼性の高い表示装置を提供することを課題の一とする。

【0010】

また、本発明の一態様は、良好な表示特性を有する表示装置を提供することを課題の一とする。

【0011】

また、本発明の一態様は、低消費電力化を達成した表示装置を提供することを課題の一とする。

【0012】

なお、これらの課題の記載は、他の課題の存在を妨げるものではない。本発明の一態様は、これらの課題の全てを解決する必要はないものとする。また、上記以外の課題は、明細書等の記載から自ずと明らかになるものであり、明細書等の記載から上記以外の課題を抽出することが可能である。10

【課題を解決するための手段】

【0013】

選択トランジスタ、駆動トランジスタ及び発光素子を含む画素において、駆動トランジスタとして、酸化物半導体膜にチャネルが形成され、そのチャネル長が $0.5\text{ }\mu\text{m}$ 以上 $4.5\text{ }\mu\text{m}$ 以下、好ましくは $1\text{ }\mu\text{m}$ より大きく $4\text{ }\mu\text{m}$ 以下、より好ましくは $1\text{ }\mu\text{m}$ より大きく $3.5\text{ }\mu\text{m}$ 以下、より好ましくは $1\text{ }\mu\text{m}$ より大きく $2.5\text{ }\mu\text{m}$ 以下であるトランジスタを適用する。また、該駆動トランジスタとして、酸化物半導体膜の上層及び下層にそれぞれ重なる第1のゲート電極及び第2のゲート電極を有し、各ゲート電極が互いに電気的に接続している構成とする。これによって、駆動トランジスタの電界効果移動度及びオン電流を向上させることができ、高駆動周波数においても良好な表示を行うことが可能な表示装置とすることができます。また、駆動トランジスタほどの電界効果移動度が要求されない画素の選択トランジスタのチャネル長を、少なくとも駆動トランジスタのチャネル長よりも大きくすることで、画素の開口率を高めながら低消費電力化を達成することが可能となる。20

【0014】

より具体的には、例えば以下の構成とすることができます。

【0015】

本発明の一態様は、発光素子と、発光素子の駆動トランジスタとして機能する第1のトランジスタと、第1のトランジスタと電気的に接続し、選択トランジスタとして機能する第2のトランジスタと、を含む画素を有し、第1のトランジスタは、絶縁表面上の第1のゲート電極と、第1のゲート電極上の第1の絶縁膜と、第1の絶縁膜を介して第1のゲート電極と重なる第1の酸化物半導体膜と、第1の酸化物半導体膜と電気的に接続し、第1の酸化物半導体膜上に端部を有する一対の電極と、第1の酸化物半導体膜上の第2の絶縁膜と、第2の絶縁膜を介して、第1の酸化物半導体膜上に設けられ、第1のゲート電極と重なる第2のゲート電極と、を有し、第2のゲート電極は、チャネル幅方向において第2の絶縁膜を介して第1の酸化物半導体膜の側面と対向する領域を有し、第2のトランジスタは、絶縁表面上の第3のゲート電極と、第3のゲート電極上の第1の絶縁膜と、第1の絶縁膜を介して第3のゲート電極と重なる第2の酸化物半導体膜と、第2の酸化物半導体膜と電気的に接続し、第2の酸化物半導体膜上に端部を有する一対の電極と、を有し、第1のトランジスタの一対の電極の間隔は、 $0.5\text{ }\mu\text{m}$ 以上 $4.5\text{ }\mu\text{m}$ 以下であり、第2のトランジスタの一対の電極の間隔は、第1のトランジスタの一対の電極の間隔よりも広いことを特徴とする表示装置である。30

【0016】

また、本発明の一態様は、発光素子と、発光素子の駆動トランジスタとして機能する第1のトランジスタと、第1のトランジスタと電気的に接続し、選択トランジスタとして機能する第2のトランジスタと、を含む画素を有し、第1のトランジスタは、絶縁表面上の第1のゲート電極と、第1のゲート電極上の第1の絶縁膜と、第1の絶縁膜を介して第1のゲート電極と重なる第1の酸化物半導体膜と、第1の酸化物半導体膜と電気的に接続し40

50

、第1の酸化物半導体膜上に端部を有する一対の電極と、第1の酸化物半導体膜上の第2の絶縁膜と、第2の絶縁膜を介して、第1の酸化物半導体膜上に設けられ、第1のゲート電極と重なる第2のゲート電極と、を有し、第2のゲート電極は、チャネル幅方向において第2の絶縁膜を介して第1の酸化物半導体膜の側面と対向する領域を有し、第2のトランジスタは、絶縁表面上の第3のゲート電極と、第3のゲート電極上の第1の絶縁膜と、第1の絶縁膜を介して第3のゲート電極と重なる第2の酸化物半導体膜と、第2の酸化物半導体膜と電気的に接続し、第2の酸化物半導体膜上に端部を有する一対の電極と、を有し、第1のトランジスタの一対の電極の間隔は、0.5 μm以上4.5 μm以下であり、第2のトランジスタの一対の電極の間隔は、第1のトランジスタの一対の電極の間隔よりも広く、且つ、第2のトランジスタのカットオフ電流の値は第1のトランジスタのカットオフ電流の値より小さいことを特徴とする表示装置である。10

#### 【0017】

また、上記の表示装置において、第2のトランジスタは、第2の絶縁膜を介して第2の酸化物半導体膜上に設けられ、第3のゲート電極と重なる第4のゲート電極を有し、第3のゲート電極及び第4のゲート電極は、互いに接する領域を有していてもよい。

#### 【0018】

また、上記の表示装置において、第1のゲート電極と第2のゲート電極は、互いに接する領域を有することが好ましい。

#### 【0019】

また、上記の表示装置において、第1の絶縁膜及び第2の絶縁膜の少なくとも一は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を有することが好ましい。20

#### 【発明の効果】

#### 【0020】

本発明の一態様によって、酸化物半導体膜を含むトランジスタのしきい値電圧の変動による影響が低減された表示装置を提供することができる。

#### 【0021】

また、本発明の一態様によって、信頼性の高い表示装置を提供することができる。

#### 【0022】

また、本発明の一態様によって、良好な表示特性を有する表示装置を提供することができる。30

#### 【0023】

また、本発明の一態様によって、低消費電力化を達成した表示装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0024】

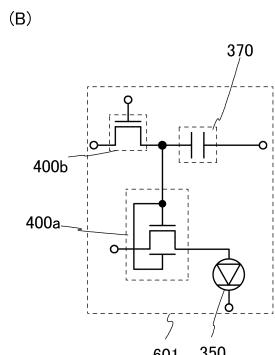

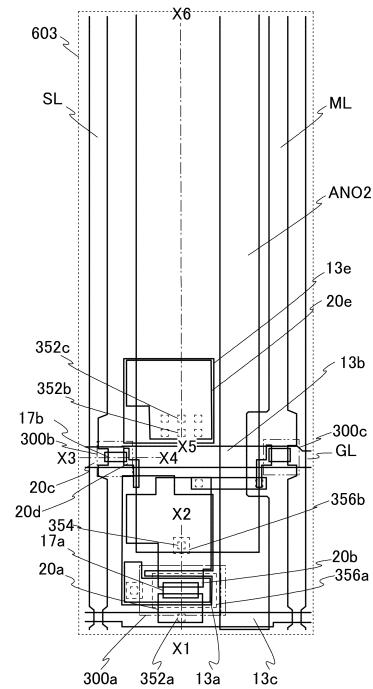

【図1】表示装置の一態様を示す概念図及び画素の一態様を示す回路図。

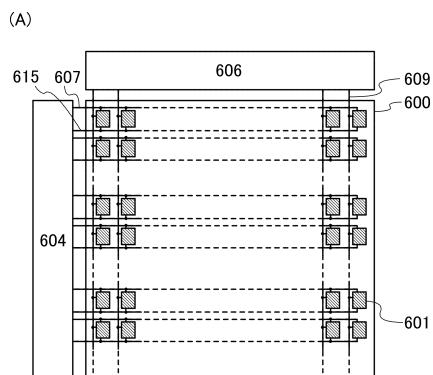

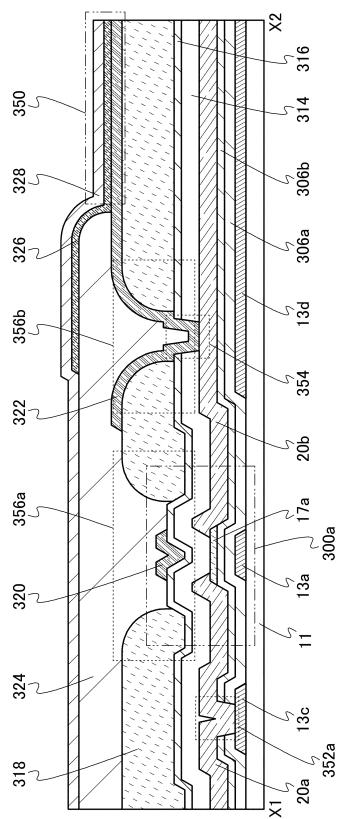

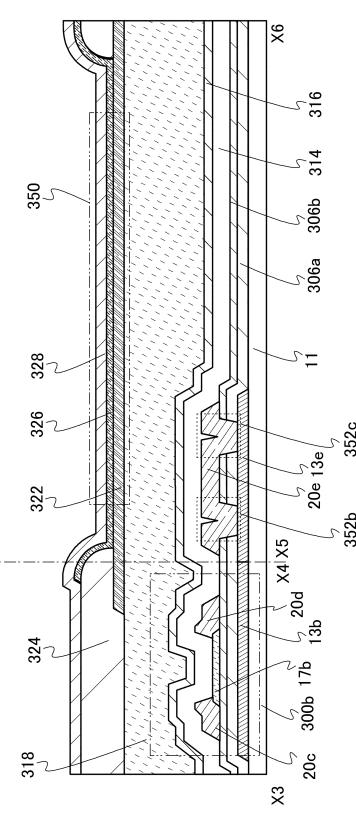

【図2】表示装置の一態様を示す平面図及び断面図。

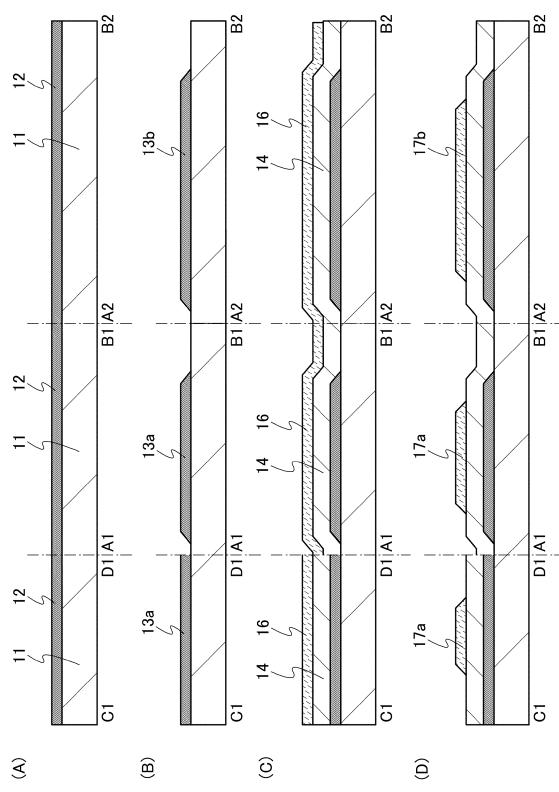

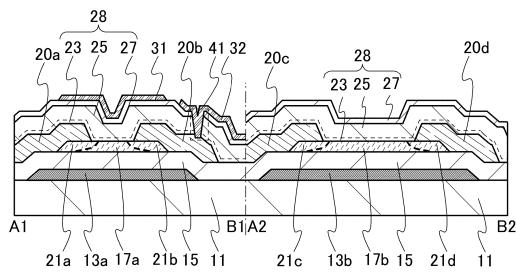

【図3】表示装置の作製方法の一態様を説明する断面図。

【図4】表示装置の作製方法の一態様を説明する断面図。

40

【図5】表示装置の作製方法の一態様を説明する断面図。

【図6】表示装置の作製方法の一態様を説明する断面図。

【図7】表示装置の一態様を示す平面図及び断面図。

【図8】表示装置の一態様を示す平面図及び断面図。

【図9】表示装置の一態様を示す平面図、断面図及び回路図。

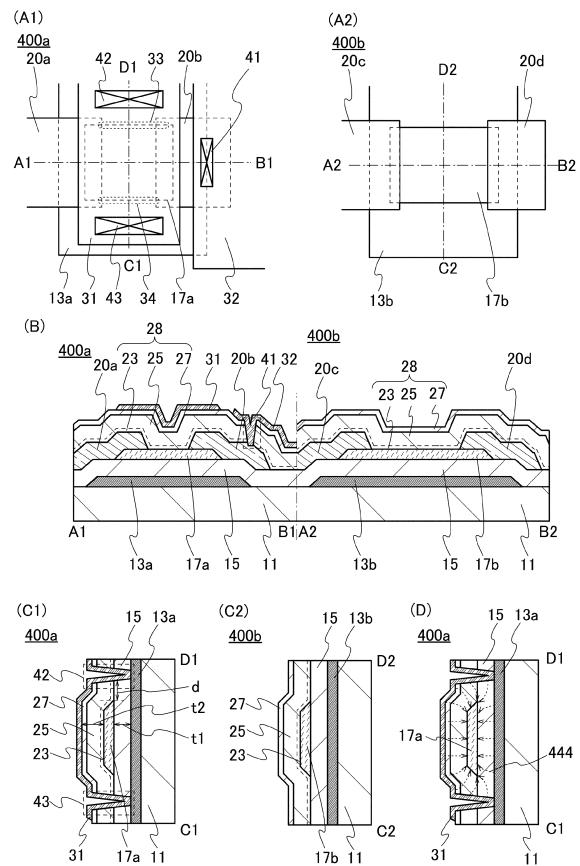

【図10】回路記号とトランジスタの構成を示す図。

【図11】表示装置の一態様を示す平面図及び断面図。

【図12】表示装置の一態様を示す平面図及び断面図。

【図13】表示装置の作製方法の一態様を説明する断面図。

【図14】表示装置の作製方法の一態様を説明する断面図。50

- 【図15】表示装置の作製方法の一態様を説明する断面図。

- 【図16】表示装置の画素構成の一態様を説明する平面図。

- 【図17】表示装置の画素構成の一態様を説明する断面図。

- 【図18】表示装置の画素構成の一態様を説明する断面図。

- 【図19】表示装置の一形態を説明する断面図。

- 【図20】表示装置の一形態を説明する平面図及び断面図。

- 【図21】表示装置の一形態を説明する断面図。

- 【図22】トランジスタのバンド構造を説明する図。

- 【図23】表示装置の画素構成の一態様を説明する回路図。

- 【図24】表示装置を説明する上面図および断面図。 10

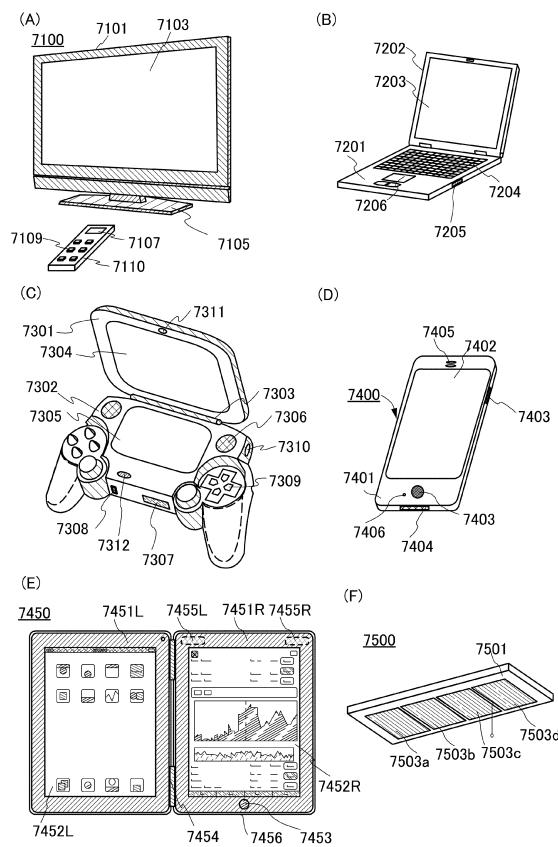

- 【図25】電子機器の一例を説明する図。

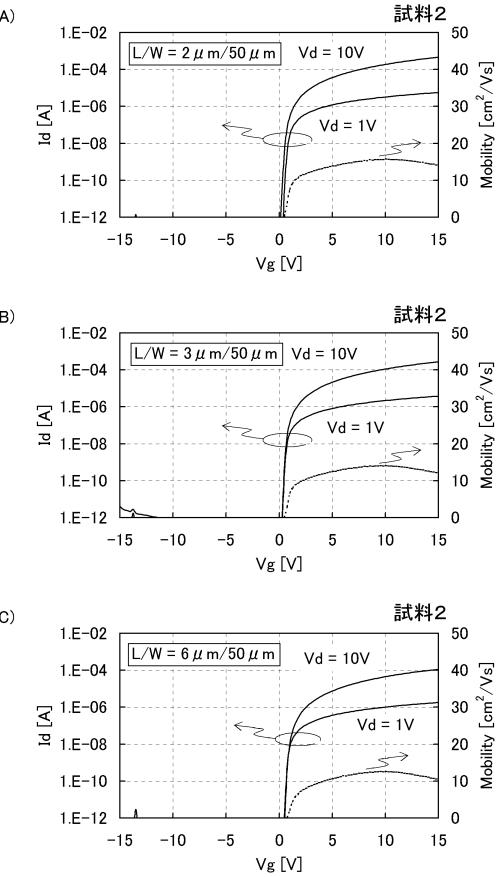

- 【図26】実施例に係る、トランジスタのV<sub>g</sub> - I<sub>d</sub>特性。

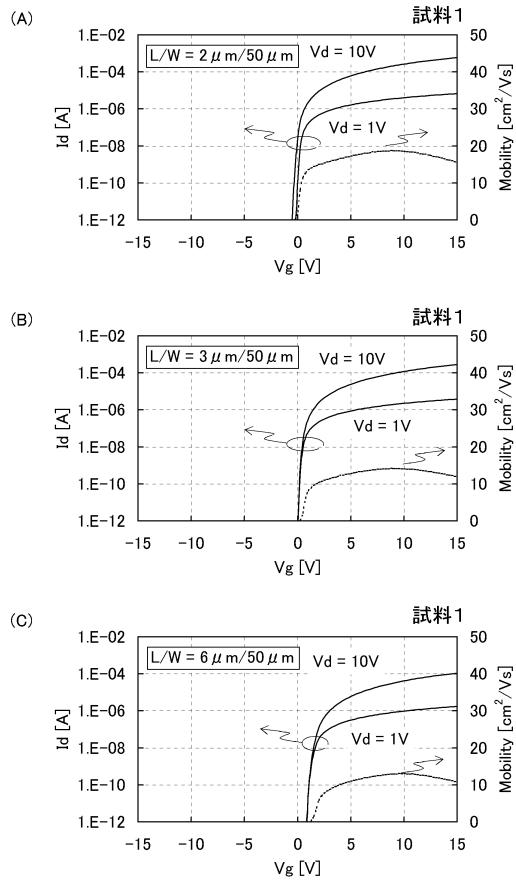

- 【図27】実施例に係る、トランジスタのV<sub>g</sub> - I<sub>d</sub>特性。

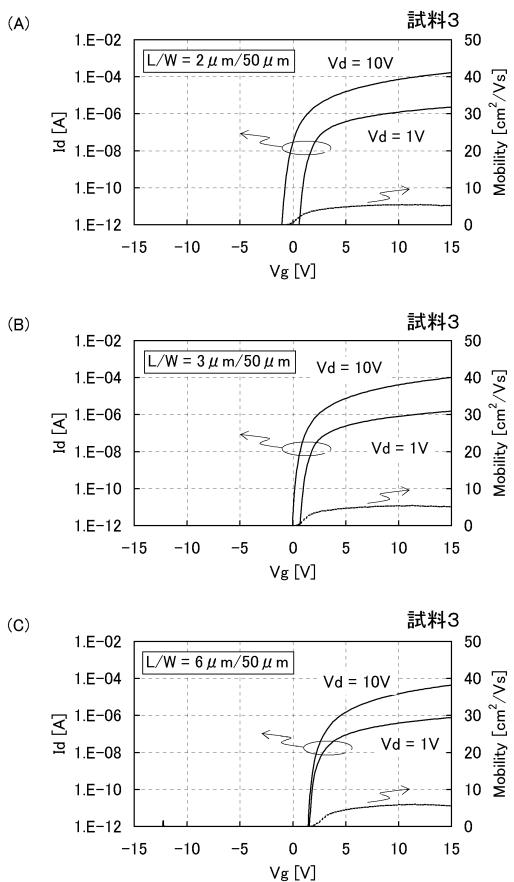

- 【図28】実施例に係る、トランジスタのV<sub>g</sub> - I<sub>d</sub>特性。

- 【図29】計算に用いたトランジスタの構造と、計算により得られた電界効果移動度及びオン電流を説明する図。

- 【図30】計算に用いたトランジスタのモデルを説明する図。

- 【図31】計算によって得られた飽和移動度のチャネル長依存性を説明する図。

- 【図32】計算によって得られたオン電流のチャネル長依存性を説明する図。

- 【図33】計算によって得られたトランジスタのV<sub>g</sub> - I<sub>d</sub>特性及び酸化物半導体膜中の電流分布を説明する図。 20

- 【図34】計算によって得られたトランジスタのV<sub>g</sub> - I<sub>d</sub>特性及びシリコン膜中の電流分布を説明する図。

- 【図35】計算に用いた電子トラップ及び計算によって得られた飽和移動度のチャネル長依存性を説明する図。

- 【図36】トランジスタのオフ状態及びオン状態におけるキャリアの流れを説明する図。

- 【発明を実施するための形態】

- 【0025】

- 以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明は、以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではない。また、以下に説明する実施の形態及び実施例において、同一部分又は同様の機能を有する部分には同一の符号又は同一のハッチパターンを異なる図面間で共通して用い、その繰り返しの説明は省略する。 30

- 【0026】

- なお、本明細書で説明する各図において、各構成の大きさ、膜の厚さ、又は領域は、明瞭化のために誇張されている場合がある。よって、必ずしもそのスケールに限定されない。

- 【0027】

- また、本明細書にて用いる第1、第2等の序数詞は、構成要素の混同を避けるために付したものであり、数的に限定するものではない。そのため、例えば、「第1の」を「第2の」又は「第3の」等と適宜置き換えて説明することができる。 40

- 【0028】

- また、「ソース」や「ドレイン」の機能は、回路動作において電流の方向が変化する場合には入れ替わることがある。このため、本明細書等においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

- 【0029】

- また、電圧とは、2点間ににおける電位差のことをいい、電位とはある一点における静電場の中にある単位電荷が持つ静電エネルギー（電気的な位置エネルギー）のことをいう。 50

ただし、一般的に、ある一点における電位と基準となる電位（例えば接地電位）との電位差のことを、単に電位もしくは電圧と呼び、電位と電圧が同義語として用いられることが多い。このため、本明細書では特に指定する場合を除き、電位を電圧と読み替えてよいし、電圧を電位と読み替えてよいこととする。

#### 【0030】

本明細書において、フォトリソグラフィ工程を行った後にエッチング工程を行う場合は、フォトリソグラフィ工程で形成したマスクは除去するものとする。

#### 【0031】

##### (実施の形態1)

本実施の形態では、本発明の一態様の表示装置及びその作製方法について、図面を参照して説明する。

10

#### 【0032】

##### <表示装置の構成例>

図1(A)に、表示装置の一例のブロック図を示す。図1(A)に示す表示装置は、画素部600と、走査線駆動回路604と、信号線駆動回路606と、各々が平行又は略平行に配置され、且つ走査線駆動回路604によって電位が制御されるm本の走査線607と、各々が平行又は略平行に配置され、且つ信号線駆動回路606によって電位が制御されるn本の信号線609と、を有する。さらに画素部600はマトリクス状に配置された複数の画素601を有する。また、走査線駆動回路604及び信号線駆動回路606をまとめて駆動回路部という場合がある。

20

#### 【0033】

各走査線607は、画素部600においてm行n列に配置された画素601のうち、いずれかの行に配置されたn個の画素601と電気的に接続される。また、各信号線609は、m行n列に配置された画素601のうち、いずれかの列に配置されたm個の画素601に電気的に接続される。m、nはともに1以上の整数である。また、各容量線615は、m行n列に配置された画素601のうち、いずれかの行に配置されたn個の画素601と電気的に接続される。なお、容量線615が、信号線609に沿って、各々が平行又は略平行に配置されている場合は、m行n列に配置された画素601のうち、いずれかの列に配置されたm個の画素601と電気的に接続される。

30

#### 【0034】

##### <画素の構成例>

図1(B)は、図1(A)に示す表示装置の画素601に用いることができる回路構成の一例を示している。

#### 【0035】

図1(B)に示す画素601は、選択トランジスタとして機能するトランジスタ400bと、駆動トランジスタとして機能するトランジスタ400aと、容量素子370と、発光素子350と、を有する。

#### 【0036】

トランジスタ400aのソース電極及びドレイン電極の一方は、発光素子350の一方の電極に電気的に接続され、トランジスタ400aのソース電極及びドレイン電極の他方は、高電源電位が与えられるアノード線(図示せず)と電気的に接続される。また、トランジスタ400aは、半導体膜を間に挟んで重なり合う一対のゲート電極を有しており、トランジスタ400aのゲート電極の一方は、トランジスタ400aのゲート電極の他方、トランジスタ400bのソース電極及びドレイン電極の一方、及び容量素子370の一方の電極に電気的に接続される。トランジスタ400bのゲート電極は、走査線607に電気的に接続され、トランジスタ400bのソース電極及びドレイン電極の他方は、信号線609に電気的に接続される。また、容量素子370の他方の電極は、容量線615に電気的に接続され、発光素子350の他方の電極は、低電源電位が与えられるカソード線(図示せず)に電気的に接続される。

40

#### 【0037】

50

トランジスタ400aは、オン状態又はオフ状態になることにより、発光素子350に流れる電流を制御する機能を有する。

#### 【0038】

駆動トランジスタとして機能するトランジスタ400aは、発光素子350に十分な輝度を得るために、オン電流の高いトランジスタを適用することが求められる。また、表示装置の駆動周波数を向上させてより滑らかな動画表示を実現するために、電界効果移動度が高いトランジスタを適用することが求められる。

#### 【0039】

そこで、本実施の形態の表示装置においては、トランジスタ400aとして、チャネル長が0.5μm以上4.5μm以下、好ましくは1μmより大きく4μm以下、より好ましくは1μmより大きく3.5μm以下、より好ましくは1μmより大きく2.5μm以下であるトランジスタを適用する。トランジスタのオン電流は、チャネル幅に対するチャネル長の比(L/W比)が小さいほど増加するため、トランジスタ400aのチャネル長を上述の範囲程度に縮小することで、オン電流を向上させることができる。または、チャネル長を上述の範囲程度に縮小し、且つチャネル幅も縮小することで、オン電流を一定に保ったままトランジスタサイズを小さくすることができ、画素の開口率を向上させることができる。

#### 【0040】

また、トランジスタ400aは、チャネルが形成される酸化物半導体膜と、酸化物半導体膜を間に挟んで重なり合う第1のゲート電極と第2のゲート電極を有する。また、トランジスタ400aに含まれる第1のゲート電極及び第2のゲート電極は電気的に接続している。このように、酸化物半導体膜を挟んで一対のゲート電極を設け、且つ該一対のゲート電極を電気的に接続することで、一対のゲート電極の片方にだけ一定の電位を与える場合とは異なり、一対のゲート電極に同じ電位が与えられるので、チャネル形成領域が増え、トランジスタ400aのドレイン電流の増加を実現することができる。よって、オン電流の低下を抑えつつトランジスタ400aのサイズを小さく抑えることができる。

#### 【0041】

さらに、第1のゲート電極と第2のゲート電極とを接続するために、酸化物半導体膜のチャネル幅方向の側面の少なくとも一方に重なるように第2のゲート電極が設けられる。これによって、酸化物半導体膜のチャネル幅方向の側面にも電界が印加されることとなり、電流の流れる領域を拡大することが可能となる。したがって、トランジスタ400aの電界効果移動度を向上させることができる。

#### 【0042】

また、電気的に接続された一対のゲート電極を設けることで、酸化物半導体膜に空乏層ができやすくなるため、トランジスタ400aのサブスレッショルド特性を改善することができる。

#### 【0043】

また、チャネル長を短縮することで、トランジスタのしきい値電圧がマイナス方向に変動する場合がある。しかしながら、トランジスタ400aでは、第1のゲート電極に加えて、バックチャネル領域側に第2のゲート電極(バックゲート電極)を設けることで、バックチャネル領域にマイナスの電荷が生じるのを防ぎ、トランジスタのしきい値電圧がマイナス方向へシフトするのを抑えることができる。

#### 【0044】

トランジスタ400bは、オン状態又はオフ状態となることにより、データ信号の書き込みを制御する機能を有する。

#### 【0045】

トランジスタ400bとしては、しきい値電圧がプラスとなる電気特性(ノーマリーオフ特性ともいう。)を有するトランジスタを適用することが好ましい。また、カットオフ電流の低減されたトランジスタを適用することが好ましい。

#### 【0046】

10

20

30

40

50

上述したように、トランジスタのチャネル長を小さくすることで、高いオン電流が得られる一方で、トランジスタのしきい値電圧がマイナス方向に変動（マイナスシフト）する場合がある。本実施の形態の表示装置では、高いオン電流、高い電界効果移動度が要求される駆動トランジスタとして機能するトランジスタ400aのチャネル長を0.5μm以上4.5μm以下とし、且つ電気的に接続された一対のゲート電極を設けることで、オン電流及び電界効果移動度を向上させつつ、しきい値電圧のマイナスシフトを抑制する。

#### 【0047】

一方、選択トランジスタとして機能するトランジスタ400bは、トランジスタ400aほど高い電界効果移動度を要しないため、そのチャネル長をトランジスタ400aのチャネル長よりも大きくすることで、トランジスタ400bのしきい値電圧のマイナスシフトを抑制する。これによって、表示装置の高速動作及び低消費電力化を図ることが可能となる。

10

#### 【0048】

例えば、トランジスタ400aのチャネル長を0.5μm以上4.5μm以下とした場合には、トランジスタ400bのチャネル長を6μmとすることができる。ただし、トランジスタ400bのチャネル長は、少なくともトランジスタ400aのチャネル長よりも大きければよく、表示装置に求められる特性によって適宜設定することができる。

#### 【0049】

また、トランジスタ400bのカットオフ電流の値は、トランジスタ400aのカットオフ電流の値よりも小さいことが好ましい。例えば、トランジスタ400bのチャネル幅に対するチャネル長の比（L/W比）をトランジスタ400aのL/W比よりも大きくすることにより、トランジスタ400bのカットオフ電流の値を、トランジスタ400aのカットオフ電流の値よりも小さくできる。また、トランジスタ400aとトランジスタ400bのチャネル幅が同等の場合には、トランジスタ400bのチャネル長をトランジスタ400aのチャネル長よりも大きくすることで、トランジスタ400bのカットオフ電流の値を低減することが可能となる。

20

#### 【0050】

なお、トランジスタ400bを、トランジスタ400aと同様に、電気的に接続された一対のゲート電極を有する構成としてもよい。ただし、トランジスタ400bを前述の構成とした場合、一対のゲート電極を接続するための領域が必要になり、結果として、トランジスタ400bの面積が大きくなり、画素の開口率が低下してしまう。そのため、トランジスタ400bはシングルゲート構造が好ましい。また、表示装置が大型化した場合、トランジスタ400bのゲート配線の寄生容量が表示装置の動作速度に影響を与えるようになる。そのため、トランジスタ400bは、ゲート配線の寄生容量が小さいシングルゲート構造が好ましい。

30

#### 【0051】

発光素子350としては、例えば、有機エレクトロルミネセンス素子（有機EL素子）、又は無機EL素子を用いることができる。

#### 【0052】

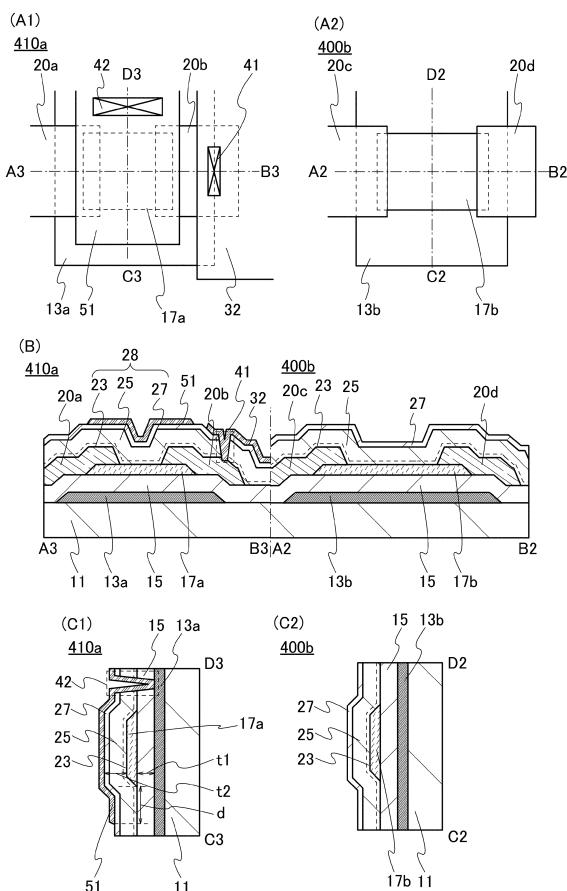

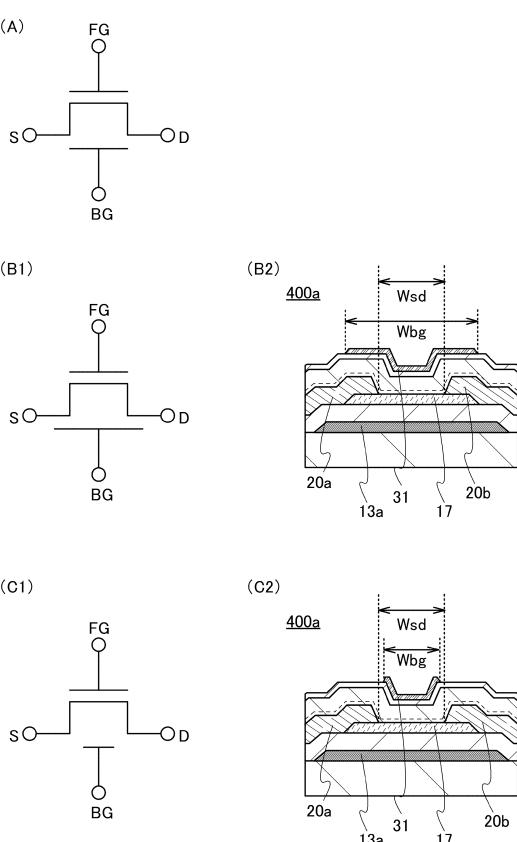

<トランジスタの回路記号>

40

ここで、本明細書で用いる、酸化物半導体膜を間に挟んで重なり合う一対のゲート電極を有するトランジスタの回路記号について、図10(A)に示す。図10(A)に示す回路記号では、一対のゲート電極をFG、BGで示し、ソース電極をS、ドレイン電極をDで示している。

#### 【0053】

図10(B2)は、図10(B1)の回路記号で表すことのできるトランジスタ400aの断面図の一例を示している。図10(B2)に示すトランジスタ400aは、ソース電極またはドレイン電極として機能する一対の電極20a、20bが、酸化物半導体膜17aにおいて、ゲート電極31と部分的に重なっている。図10(B1)に示す回路記号では、図10(A)に示す回路記号と同様に、一対のゲート電極をFG、BGで示し、

50

ソース電極をS、ドレイン電極をDで示している。

**【0054】**

図10(B2)に示すトランジスタ400aは、チャネル長方向において、一対の電極20a、20bの端部の距離Wsdが、ゲート電極31の端部間の距離Wbgに比べて短い。そして、チャネル長方向における断面図では、ゲート電極31の一対の端部が、一対の電極20a、20bと重なっている。

**【0055】**

図10(C2)は、図10(C1)の回路記号で表すことのできるトランジスタ400aの断面図の一例を示している。図10(C2)に示すトランジスタ400aは、ソース電極またはドレイン電極として機能する一対の電極20a、20bが、酸化物半導体膜17a上において、ゲート電極31と重なっていない。図10(C1)に示す回路記号では、図10(A)に示す回路記号と同様に、一対のゲート電極をFG、BGで示し、ソース電極をS、ドレイン電極をDで示している。

**【0056】**

図10(C2)に示すトランジスタ400aは、チャネル長方向において、一対の電極20a、20bの距離Wsdが、ゲート電極31の端部間の距離Wbgに比べて長い。そして、チャネル長方向における断面図では、ゲート電極31の一対の端部が、一対の電極20a、20bと重なっていない。

**【0057】**

本明細書に添付された図面では、図10(A)に示す回路記号が、図10(B1)の回路記号で表される構造のトランジスタ400aと、図10(C1)の回路記号で表される構造のトランジスタ400aとを、含むものとする。

**【0058】**

<画素に含まれるトランジスタの構成例>

次いで、表示装置の画素に含まれるトランジスタの具体的な構成について説明する。

**【0059】**

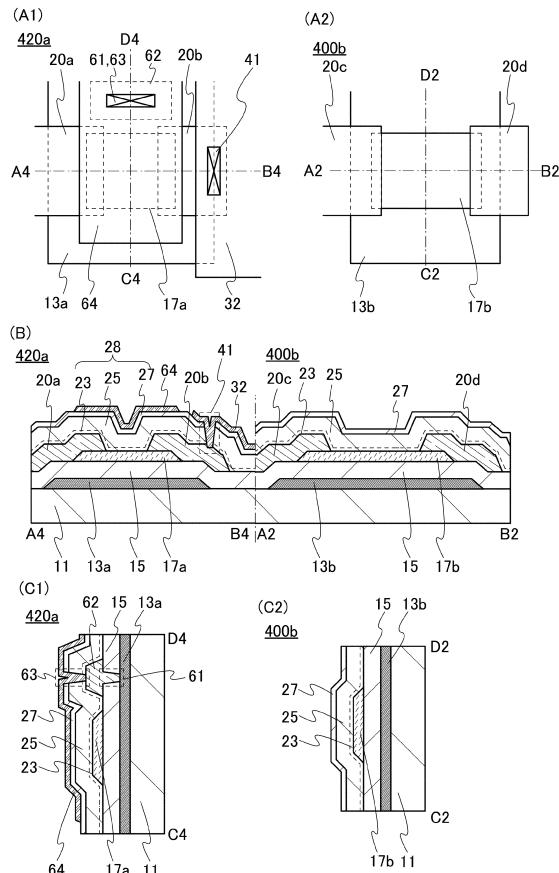

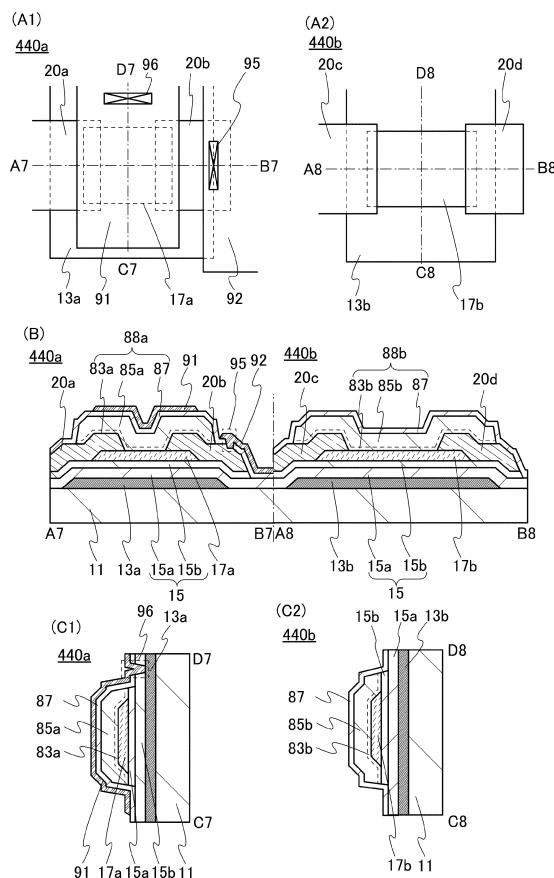

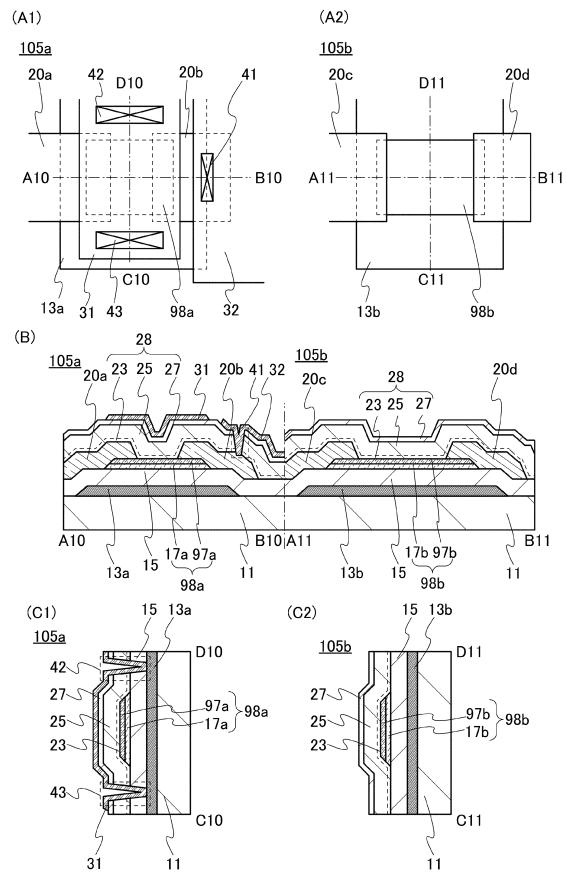

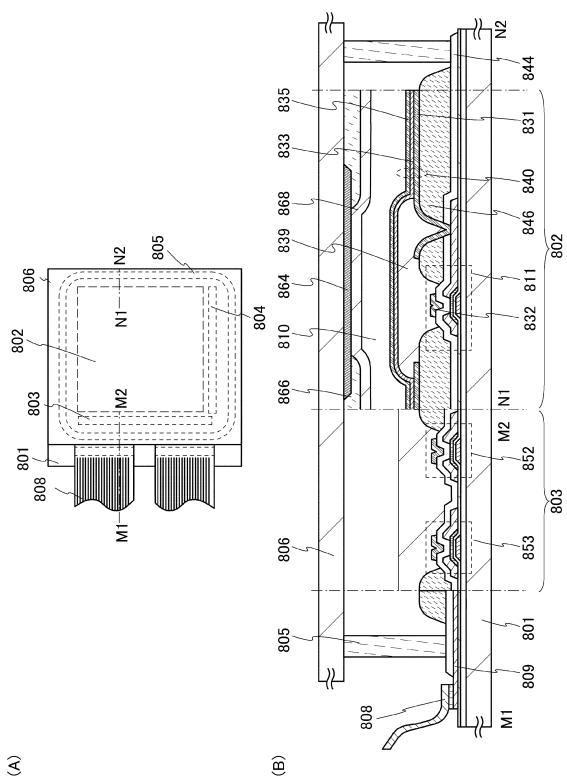

図2(A1)乃至図2(C2)に、表示装置の画素601に含まれるトランジスタ400a及びトランジスタ400bの上面図及び断面図を示す。図2(A1)は駆動トランジスタとしての機能を有するトランジスタ400aの上面図であり、図2(A2)は選択トランジスタとしての機能を有するトランジスタ400bの上面図であり、図2(B)は、図2(A1)の一点鎖線A1-B1間及び図2(A2)の一点鎖線A2-B2間の断面図であり、図2(C1)は、図2(A1)の一点鎖線C1-D1間の断面図であり、図2(C2)は、図2(A2)の一点鎖線C2-D2間の断面図である。なお、図2(A1)及び図2(A2)では、明瞭化のため、基板11及び絶縁膜15などを省略している。

**【0060】**

図2(A1)、図2(B)及び図2(C1)に示すトランジスタ400aは、チャネルエッチ型のトランジスタであり、基板11上に設けられるゲート電極13aと、基板11及びゲート電極13a上に形成される絶縁膜15と、絶縁膜15を介して、ゲート電極13aと重なる酸化物半導体膜17aと、酸化物半導体膜17aに接する一対の電極20a、20bとを有する。また、絶縁膜15、酸化物半導体膜17a、及び一対の電極20a、20b上に、酸化物絶縁膜23、酸化物絶縁膜25、及び窒化物絶縁膜27で構成される絶縁膜28と、絶縁膜28上に形成されるゲート電極31とを有する。ゲート電極31は、絶縁膜15及び絶縁膜28に設けられた開口部42、43においてゲート電極13aと接続する。また、一対の電極20a、20bの一方、ここでは電極20bに接続する電極32が、窒化物絶縁膜27上に形成される。なお、電極32は画素電極として機能する。

**【0061】**

図2(B)及び図2(C2)に示すトランジスタ400bは、チャネルエッチ型のトランジスタであり、基板11上に設けられるゲート電極13bと、基板11及びゲート電極13b上に形成される絶縁膜15と、絶縁膜15を介して、ゲート電極13bと重なる酸

10

20

30

40

50

化物半導体膜 17 b と、酸化物半導体膜 17 b に接する一対の電極 20 c、20 d を有する。また、絶縁膜 15、酸化物半導体膜 17 b、及び一対の電極 20 c、20 d 上に、酸化物絶縁膜 23、酸化物絶縁膜 25、及び窒化物絶縁膜 27 で構成される絶縁膜 28 と、を有する。

#### 【0062】

トランジスタ 400 a 及びトランジスタ 400 b において、絶縁膜 15 は、ゲート絶縁膜（トランジスタ 400 a においては第 1 のゲート絶縁膜）として機能する。また、絶縁膜 28 は、トランジスタ 400 a の第 2 のゲート絶縁膜として機能し、トランジスタ 400 b においては、保護絶縁膜として機能する。

#### 【0063】

本実施の形態に示すトランジスタ 400 a は、チャネル長が 0.5 μm 以上 4.5 μm 以下、好ましくは 1 μm より大きく 4 μm 以下、より好ましくは 1 μm より大きく 3.5 μm 以下、より好ましくは 1 μm より大きく 2.5 μm 以下である。また、トランジスタ 400 a は、チャネル幅方向において、ゲート電極 13 a 及びゲート電極 31 の間に、絶縁膜 15 及び絶縁膜 28 を介して酸化物半導体膜 17 a が設けられている。また、ゲート電極 31 は図 2 (A1) に示すように、上面から見て、絶縁膜 28 を介して酸化物半導体膜 17 a の端部と重なる。

#### 【0064】

トランジスタ 400 a に含まれる酸化物半導体膜 17 a は、チャネル長方向の側面が、一対の電極 20 a、20 b と重なり、チャネル幅方向の側面が、ゲート電極 31 と重なる構成を有する。酸化物半導体膜 17 a の端部は、酸化物半導体膜 17 a を島状に加工するためのエッチング処理でプラズマに曝される際に、エッチングガスから生じた塩素ラジカル、フッ素ラジカル等が、酸化物半導体を構成する金属元素と結合しやすい。よって、酸化物半導体膜 17 a の端部では、当該金属元素と結合していた酸素が脱離しやすい状態にあるため、酸素欠損が形成され、n 型化しやすい場合がある。特に、酸化物半導体膜 17 a の端部のうち、破線 33 及び破線 34 で囲まれた領域が n 型化すると、この領域を介して、一対の電極 20 a、20 b の間にリーク電流が流れやすい。しかしながら、トランジスタ 400 a では、上述の領域がゲート電極 31 と重なるため、ゲート電極 31 (ゲート電極 31 と同電位のゲート電極 13 a を含む) の電位を制御することにより、当該領域に印加される電界を制御することができる。よって、酸化物半導体膜 17 a の端部が n 型化されていたとしても、一対の電極 20 a、20 b 間に流れうるリーク電流を、一対のゲート電極に与える電位によって制御することができる。

#### 【0065】

具体的に、トランジスタ 400 a が非導通状態となるような電位を一対のゲート電極に与えたときには、破線 33 及び破線 34 で囲まれた酸化物半導体膜 17 a の端部を介して一対の電極 20 a、20 b 間に流れるオフ電流を小さく抑えることができる。そのため、トランジスタ 400 a では大きなオン電流を得るためにチャネル長を短くし、その結果、酸化物半導体膜 17 a の端部における一対の電極 20 a、20 b 間の長さが短くなってしまって、オフ電流を小さく抑えることが可能となる。すなわち、トランジスタ 400 a は、導通状態の場合には、大きなオン電流を得ることができ、非導通状態の場合には、オフ電流を小さく抑えることが可能なトランジスタである。

#### 【0066】

また、本実施の形態に示すトランジスタ 400 b のチャネル長は、トランジスタ 400 a のチャネル長よりも大きい。これにより、シングルゲート構造であるトランジスタ 400 b のしきい値電圧のマイナス方向への変動を抑制し、カットオフ電流の値を小さく抑えることができる。

#### 【0067】

絶縁膜 15 及び絶縁膜 28 には複数の開口部を有する。代表的には、図 2 (B) に示すように、一対の電極 20 a、20 b の一方を露出する開口部 41 を有する。また、図 2 (C1) に示すように、チャネル幅方向において、酸化物半導体膜 17 a を挟む開口部 42

10

20

30

40

50

、43を有する。即ち、酸化物半導体膜17aの側面の外側に開口部42、43を有する。開口部41において、一対の電極20a、20bの一方、ここでは電極20bと電極32が接続する。また、開口部42、43において、ゲート電極13a及びゲート電極31が接続する。即ち、チャネル幅方向において、ゲート電極13a及びゲート電極31は、絶縁膜15及び絶縁膜28を介して酸化物半導体膜17aを囲む。また、当該開口部42、43の側面において、ゲート電極31は酸化物半導体膜17aの側面と対向する。

#### 【0068】

なお、図2(C1)に示すように、チャネル幅方向において、酸化物半導体膜17aの側面と開口部42、43におけるゲート電極31との距離dは、絶縁膜15の膜厚t1と絶縁膜28の膜厚t2を足し合わせた膜厚の1倍以上7.5倍以下とする。酸化物半導体膜17aの側面と開口部42、43におけるゲート電極31との距離dが、絶縁膜15の膜厚t1と絶縁膜28の膜厚t2を足し合わせた膜厚の1倍以上の場合、図2(D)の電気力線444で示すように、ゲート電極31の電界が酸化物半導体膜17aの側面、または側面及びその近傍を含む端部に影響するため、酸化物半導体膜17aの側面または端部における寄生チャネルの発生を抑制することができる。一方、酸化物半導体膜17aの側面と開口部42、43におけるゲート電極31との距離dが、絶縁膜15の膜厚t1と絶縁膜28の膜厚t2を足し合わせた膜厚の7.5倍以下の場合、トランジスタの面積をより小さくすることができる。

#### 【0069】

トランジスタ400aに含まれる酸化物半導体膜17aと、トランジスタ400bに含まれる酸化物半導体膜17bは、同一の作製工程にて形成することが可能である。酸化物半導体膜17a及び酸化物半導体膜17bは、少なくともIn若しくはZnを含む金属酸化物で形成され、代表的には、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)等で形成される。

#### 【0070】

なお、酸化物半導体膜17a及び酸化物半導体膜17bがIn-M-Zn酸化物であるとき、ZnおよびOを除いてのInおよびMの原子数比率は、Inが25atomic%以上、Mが75atomic%未満、さらに好ましくはInが34atomic%以上、Mが66atomic%未満とする。

#### 【0071】

酸化物半導体膜17a及び酸化物半導体膜17bは、エネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。このように、エネルギーギャップの広い酸化物半導体を用いることで、トランジスタ400a及びトランジスタ400bのオフ電流を低減することができる。

#### 【0072】

酸化物半導体膜17a及び酸化物半導体膜17bの厚さは、3nm以上200nm以下、好ましくは3nm以上100nm以下、さらに好ましくは3nm以上50nm以下とする。

#### 【0073】

酸化物半導体膜17a及び酸化物半導体膜17bがIn-M-Zn酸化物(MはAl、Ga、Y、Zr、La、Ce、またはNd)の場合、In-M-Zn酸化物を成膜するために用いるスパッタリングターゲットの金属元素の原子数比は、In M、Zn Mを満たすことが好ましい。このようなスパッタリングターゲットの金属元素の原子数比として、In : M : Zn = 1 : 1 : 1、In : M : Zn = 1 : 1 : 1.2、In : M : Zn = 3 : 1 : 2が好ましい。なお、成膜される酸化物半導体膜17a及び酸化物半導体膜17bの原子数比はそれぞれ、誤差として上記のスパッタリングターゲットに含まれる金属元素の原子数比のプラスマイナス40%の変動を含む。

#### 【0074】

酸化物半導体膜17a及び酸化物半導体膜17bとしては、キャリア密度の低い酸化物半導体膜を用いる。例えば、酸化物半導体膜17a及び酸化物半導体膜17bは、キャリ

10

20

30

40

50

ア密度が $1 \times 10^{-7}$ 個/ $\text{cm}^3$ 以下、好ましくは $1 \times 10^{-5}$ 個/ $\text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{-3}$ 個/ $\text{cm}^3$ 以下、より好ましくは $1 \times 10^{-1}$ 個/ $\text{cm}^3$ 以下の酸化物半導体膜を用いる。

#### 【0075】

なお、これらに限らず、必要とするトランジスタの半導体特性及び電気特性（電界効果移動度、しきい値電圧等）に応じて各々の酸化物半導体膜に適切な組成のものを用いればよい。また、必要とするトランジスタの半導体特性を得るために、酸化物半導体膜17a及び酸化物半導体膜17bのキャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0076】

なお、酸化物半導体膜17a及び酸化物半導体膜17bとして、不純物濃度が低く、欠陥準位密度の低い酸化物半導体膜を用いることで、さらに優れた電気特性を有するトランジスタを作製することができ好ましい。なお、不純物としては、水素、窒素、アルカリ金属、またはアルカリ土類金属等が挙げられる。本明細書では、不純物濃度が低く、欠陥準位密度の低い（酸素欠損の少ない）ことを高純度真性または実質的に高純度真性とよぶ。高純度真性または実質的に高純度真性である酸化物半導体は、キャリア発生源が少ないため、キャリア密度を低くすることができる。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、しきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）になりやすい。また、高純度真性または実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。また、高純度真性または実質的に高純度真性である酸化物半導体膜を用いたトランジスタは、オフ電流が著しく小さく、ソース電極とドレイン電極間の電圧（ドレイン電圧）が1Vから10Vの範囲において、オフ電流が、半導体パラメータアナライザの測定限界以下、すなわち $1 \times 10^{-13}$ A以下という特性を得ることができる。従って、当該酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性の変動が小さく、信頼性が高い。なお、酸化物半導体膜のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体膜にチャネル領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

#### 【0077】

酸化物半導体膜に含まれる水素は金属原子と結合する酸素と反応して水になり、水素と反応した酸素は金属原子から脱離して、格子（または酸素が脱離した部分）に酸素欠損を形成する。当該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合することで、キャリアである電子を生成する場合がある。従って、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。

#### 【0078】

このため、酸化物半導体膜17a及び酸化物半導体膜17bは酸素欠損と共に、水素ができる限り低減されていることが好ましい。具体的には、酸化物半導体膜17a及び酸化物半導体膜17bにおいて、二次イオン質量分析法（SIMS：Secondary Ion Mass Spectrometry）により得られる水素濃度を、 $2 \times 10^{-2}$ atoms/ $\text{cm}^3$ 以下、好ましくは $5 \times 10^{-9}$ atoms/ $\text{cm}^3$ 以下、より好ましくは $1 \times 10^{-9}$ atoms/ $\text{cm}^3$ 以下、より好ましくは $5 \times 10^{-8}$ atoms/ $\text{cm}^3$ 以下、より好ましくは $1 \times 10^{-8}$ atoms/ $\text{cm}^3$ 以下、より好ましくは $5 \times 10^{-7}$ atoms/ $\text{cm}^3$ 以下、さらに好ましくは $1 \times 10^{-6}$ atoms/ $\text{cm}^3$ 以下とする。

#### 【0079】

酸化物半導体膜17a及び酸化物半導体膜17bにおいて、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体膜17a及び酸化物半導体膜17bにおいて酸素欠損が増加し、n型化してしまう。このため、酸化物半導体膜17a及び酸化物半導

10

20

30

40

50

体膜 17 b におけるシリコンや炭素の濃度（二次イオン質量分析法により得られる濃度）を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup> 以下とする。

#### 【 0080 】

また、酸化物半導体膜 17 a 及び酸化物半導体膜 17 b において、二次イオン質量分析法により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup> 以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup> 以下にする。アルカリ金属及びアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流が増大してしまうことがある。このため、酸化物半導体膜 17 a 及び酸化物半導体膜 17 b のアルカリ金属またはアルカリ土類金属の濃度を低減することが好ましい。10

#### 【 0081 】

また、酸化物半導体膜 17 a 及び酸化物半導体膜 17 b に窒素が含まれていると、キャリアである電子が生じ、キャリア密度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。従って、当該酸化物半導体膜において、窒素はできる限り低減されていることが好ましい、例えば、二次イオン質量分析法により得られる窒素濃度は、 $5 \times 10^{18}$  atoms / cm<sup>3</sup> 以下にすることが好ましい。

#### 【 0082 】

酸化物半導体膜 17 a 及び酸化物半導体膜 17 b に含まれる不純物濃度を上述の値まで低減することで、トランジスタ 400 a、400 b にしきい値電圧がプラスとなる電気特性（ノーマリーオフ特性ともいう。）を付与することが可能となる。20

#### 【 0083 】

また、酸化物半導体膜 17 a 及び酸化物半導体膜 17 b は、例えば非単結晶構造でもよい。非単結晶構造は、例えば、後述する CAAAC - OS (C Axis Aligned Crystalline Oxide Semiconductor)、多結晶構造、後述する微結晶構造、または非晶質構造を含む。非単結晶構造において、非晶質構造は最も欠陥準位密度が高く、CAAAC - OS は最も欠陥準位密度が低い。

#### 【 0084 】

なお、酸化物半導体膜 17 a を CAAAC - OS 膜で形成することで、チャネル長の小さい、代表的には $0.5\text{ }\mu\text{m}$ 以上 $4.5\text{ }\mu\text{m}$ 以下、好ましくは $1\text{ }\mu\text{m}$ より大きく $4\text{ }\mu\text{m}$ 以下、より好ましくは $1\text{ }\mu\text{m}$ より大きく $3.5\text{ }\mu\text{m}$ 以下、より好ましくは $1\text{ }\mu\text{m}$ より大きく $2.5\text{ }\mu\text{m}$ 以下とした場合であってもチャネルエッチ型のトランジスタを作製することができるため、好ましい。30

#### 【 0085 】

なお、酸化物半導体膜 17 a 及び酸化物半導体膜 17 b が、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAAC - OS の領域、単結晶構造の二種以上を有する混合膜であってもよい。混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAAC - OS の領域、単結晶構造の領域のいずれか二種以上の領域を有する場合がある。また、混合膜は、例えば、非晶質構造の領域、微結晶構造の領域、多結晶構造の領域、CAAAC - OS の領域、単結晶構造の領域のいずれか二種以上の領域の積層構造を有する場合がある。40

#### 【 0086 】

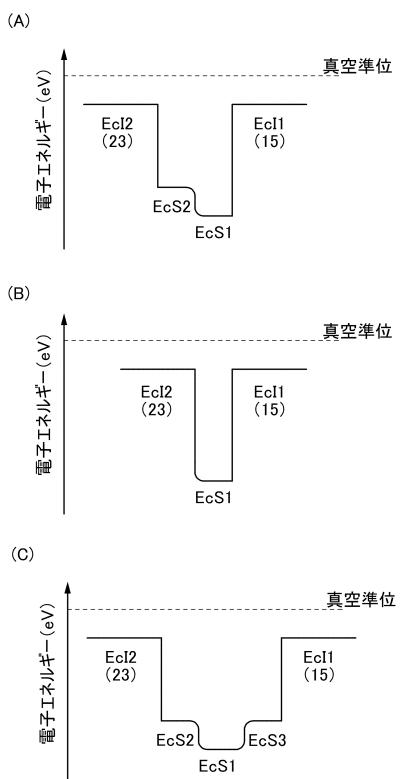

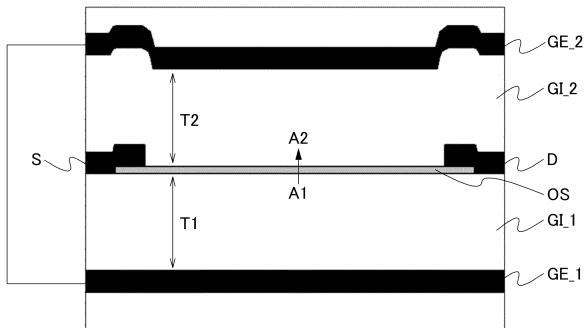

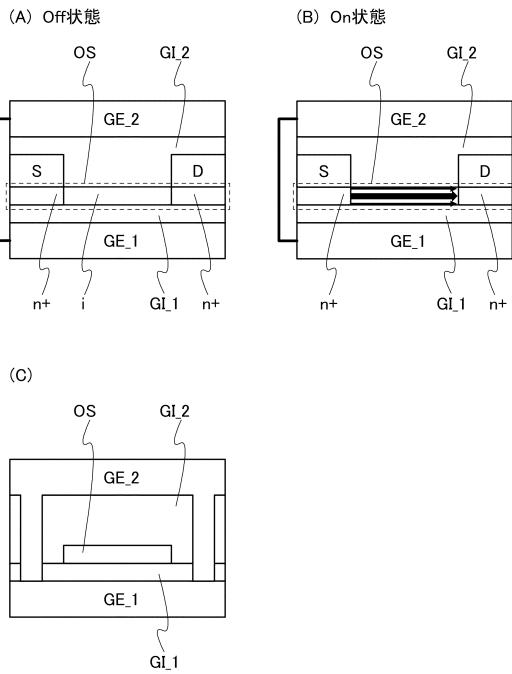

酸化物半導体膜を有するトランジスタは、蓄積型のトランジスタである。ここで、酸化物半導体膜を有するトランジスタのオフ状態及びオン状態におけるキャリアの流れについて、図 36 に示す模式図を用いて説明する。また、図 36 (A) 及び図 36 (B) は、チャネル長方向の断面図であり、図 36 (C) は、チャネル幅方向の断面図である。

#### 【 0087 】

図 36 において、酸化物半導体膜を有するトランジスタは、ゲート電極 GE\_1 と、ゲート電極 GE\_1 上のゲート絶縁膜 GI\_1 と、ゲート絶縁膜 GI\_1 上の酸化物半導体50

膜OSと、酸化物半導体膜OS上の電極S、Dと、酸化物半導体膜OS及び電極S、D上のゲート絶縁膜GI\_2と、ゲート絶縁膜GI\_2上のゲート電極GE\_2とを有する。酸化物半導体膜OSは、チャネル領域iと、電極S、Dに接する低抵抗領域n<sup>+</sup>とを有する。ゲート電極GE\_1及びゲート電極GE\_2は、図36(C)に示すように、接続されている。

#### 【0088】

トランジスタがオフ状態の場合、図36(A)に示すように、ゲート電極GE\_1、GE\_2に負の電圧が印加されると、酸化物半導体膜OSのチャネル領域iから電子が排斥され、チャネル領域iは完全に空乏化する。この結果、トランジスタのオフ電流が極めて小さくなる。

10

#### 【0089】

一方、オン状態の場合、図36(B)に示すように、電極Sと接する低抵抗領域n<sup>+</sup>から電極Dと接する低抵抗領域n<sup>+</sup>へかけて電子が蓄積され、矢印で示すように電流パスが形成される。図36(C)に示すように、ゲート電極GE\_1及びゲート電極GE\_2を同電位とし、且つ酸化物半導体膜OSの側面がゲート電極GE\_2と対向することで、さらには、チャネル幅方向において、ゲート電極GE\_1及びゲート電極GE\_2が、ゲート絶縁膜GI\_1及びゲート絶縁膜GI\_2を介して酸化物半導体膜OSを囲むことで、図36(B)に示すように、酸化物半導体膜OSにおいてキャリアが、ゲート絶縁膜GI\_1、GI\_2と酸化物半導体膜OSとの界面のみでなく、酸化物半導体膜OS中の広い範囲において流れることで、トランジスタにおけるキャリアの移動量が増加する。この結果、トランジスタのオン電流が大きくなると共に、電界効果移動度が高くなり、代表的には電界効果移動度が10cm<sup>2</sup>/V·s以上、さらには20cm<sup>2</sup>/V·s以上となる。なお、ここで電界効果移動度は、酸化物半導体膜の物性値としての移動度の近似値ではなく、トランジスタの飽和領域における電界効果移動度である。なお、トランジスタのチャネル長(L長ともいう。)を0.5μm以上6.5μm以下、好ましくは1μmより大きく6μm未満、より好ましくは1μmより大きく4μm以下、より好ましくは1μmより大きく3.5μm以下、より好ましくは1μmより大きく2.5μm以下とすることで、電界効果移動度の増加が顕著である。また、チャネル長が0.5μm以上6.5μm以下のように小さいことで、チャネル幅も小さくすることが可能である。このため、図36(C)に示すように、ゲート電極GE\_1及びゲート電極GE\_2の接続部となるための領域を設けても、トランジスタの面積を縮小することが可能である。

20

#### 【0090】

図2(A1)、図2(B)、図2(C1)、及び図2(D)に示すトランジスタ400aでは、ゲート電極13a及びゲート電極31を有することで、それぞれが外部からの電界を遮蔽する機能を有するため、基板11及びゲート電極13aの間、ゲート電極31上に存在する固定電荷が酸化物半導体膜17aに影響しない。この結果、ストレス試験(例えば、ゲート電極にマイナスの電位を印加する-GBT(Gate Bias-Temperature)ストレス試験)の劣化が抑制されると共に、異なるドレイン電圧におけるオン電流の立ち上がり電圧の変動を抑制することができる。

30

#### 【0091】

なお、BTストレス試験は加速試験の一種であり、長期間の使用によって起こるトランジスタの特性変化(即ち、経年変化)を、短時間で評価することができる。特に、BTストレス試験前後におけるトランジスタのしきい値電圧の変動量は、信頼性を調べるために重要な指標となる。BTストレス試験前後において、しきい値電圧の変動量が少ないほど、信頼性が高いトランジスタであるといえる。

40

#### 【0092】

トランジスタのチャネル長を微細化すると、しきい値電圧がマイナス方向にシフトする場合がある。しかしながら、本実施の形態の表示装置においては、画素の選択トランジスタとして機能するトランジスタ400bのチャネル長を駆動トランジスタとして機能するトランジスタ400aよりも長くすることで、表示装置の高速動作と低消費電力化を図る

50

ことができる。

**【0093】**

また、酸化物半導体膜17a及び酸化物半導体膜17b上に設けられる絶縁膜28において、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜が含まれることが好ましい。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、表面温度が100以上700以下、または100以上500以下の範囲で行われるTDS(Thermal Desorption Spectroscopy)分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18}$ atoms/cm<sup>3</sup>以上、好ましくは $3.0 \times 10^{20}$ atoms/cm<sup>3</sup>以上である酸化物絶縁膜である。

10

**【0094】**

絶縁膜28において、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜が含まれると、絶縁膜28に含まれる酸素の一部を酸化物半導体膜17a及び酸化物半導体膜17bに移動させ、該酸化物半導体膜に含まれうる酸素欠損を低減することが可能である。

**【0095】**

酸化物半導体膜中に酸素欠損が含まれている酸化物半導体膜を用いたトランジスタは、しきい値電圧がマイナス方向に変動しやすく、ノーマリーオン特性となりやすい。これは、酸化物半導体膜に含まれる酸素欠損に起因して電荷が生じ、酸化物半導体膜が低抵抗化するためである。トランジスタがノーマリーオン特性を有すると、動作時に動作不良が発生しやすくなる、または非動作時の消費電力が高くなるなどの、様々な問題が生じる。また、時間経過やストレス試験により、トランジスタの電気特性、代表的にはしきい値電圧の変動量が増大するという問題がある。

20

**【0096】**

しかしながら、本実施の形態に示すトランジスタ400a及びトランジスタ400bは、酸化物半導体膜17a、17b上に設けられる絶縁膜28に、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜が含まれることで、絶縁膜28に含まれる酸素を酸化物半導体膜17a、17bに移動させ、該酸化物半導体膜の酸素欠損を低減することが可能である。また、絶縁膜28は、エッティング雰囲気に曝されていないため、欠陥が少ない。これらの結果、ノーマリーオフ特性を有するトランジスタとなる。また、時間経過やストレス試験において、トランジスタの電気特性、代表的には動作時間に対するしきい値電圧の変動量を低減することができる。さらには、ストレス試験を繰り返しても、しきい値電圧の変動を低減することができる。

30

**【0097】**

また、トランジスタ400a及びトランジスタ400bがチャネルエッチ型のトランジスタであることも、電気特性の向上に有効である。ここで、チャネルエッチ型のトランジスタとチャネル保護型のトランジスタとを比較する。例えば、酸化物半導体膜を挟んで2つのゲート電極を有するチャネル保護型のトランジスタは、第1のゲート電極上に第1のゲート絶縁膜が形成され、第1のゲート絶縁膜上に酸化物半導体膜が形成される。酸化物半導体膜上にチャネル保護膜が形成され、該チャネル保護膜上に酸化物半導体膜と接する一対の電極が形成される。さらに、チャネル保護膜及び一対の電極上に第2のゲート絶縁膜が形成され、第2のゲート絶縁膜上に第2のゲート電極が形成される。

40

**【0098】**

チャネル保護膜は、一対の電極を形成する際のエッティング工程において、プラズマに曝され、ダメージを受ける。このため、チャネル保護膜には欠陥が形成されやすい。この結果、酸化物半導体膜を流れるキャリアがチャネル保護膜の欠陥に捕獲されてしまい、トランジスタの電気特性が動作時間と共に変動し、信頼性が低い。しかしながら、本実施の形態に示すトランジスタ400a及びトランジスタ400bは、チャネルエッチ型であり、絶縁膜28において、酸化物半導体膜17a又は酸化物半導体膜17bと重なる領域は、

50

エッティングの雰囲気に曝されない。このため、絶縁膜 28 の欠陥が少なく、信頼性の高いトランジスタである。

#### 【0099】

また、チャネル保護型のトランジスタにおいて、酸化物半導体膜において一対の電極と重なる領域では、一対の電極が第2のゲート電極の電界を遮蔽してしまい、第2のゲート電極の電界が酸化物半導体膜に均一に影響しない。この結果、第2のゲート電極の電界により誘起されて酸化物半導体膜を流れるキャリア量が減少してしまう。しかしながら、本実施の形態に示すトランジスタ 400a は、チャネルエッチ型のトランジスタであり、ゲート電極 31 の電界が、酸化物半導体膜 17a のバックチャネルに均一に影響する。さらには、酸化物半導体膜 17a の側面においてもゲート電極 31 の電界の影響を受ける。これらの結果、酸化物半導体膜 17a の広い範囲においてキャリアが流れるため、トランジスタの電界効果移動度が上昇すると共に、オン電流が増大する。10

#### 【0100】

また、チャネル保護型のトランジスタは、酸化物半導体膜と一対の電極それぞれとを接続させるため、一対の電極それぞれの一方の端部をチャネル保護膜上に位置させる。また、一対の電極それぞれの一方の端部は、酸化物半導体膜と一対の電極それぞれとの接続領域よりも内側に位置する。これらのため、フォトマスクの位置ずれを考慮すると、酸化物半導体膜と一対の電極それぞれの接続領域の間隔を広く設計する必要がある。一方、チャネルエッチ型のトランジスタは、酸化物半導体膜に一対の電極それぞれの一方の端部が直接接続するため、チャネルエッチ型のトランジスタは、チャネル保護型のトランジスタと比較して、一対の電極間の距離を小さくすることが容易である。特に本発明の一態様の表示装置で画素の駆動トランジスタとして機能するトランジスタ 400a はチャネル長の短いトランジスタであるため、チャネルエッチ型とすることで、表示装置を歩留りよく作製することが可能となる。20

#### 【0101】

さらには、トランジスタ 400a 及びトランジスタ 400b の双方がチャネルエッチ型であり、トランジスタ 400b とトランジスタ 400a の構成の相違点は、チャネル長の長さ及びトランジスタ 400a がバックゲート電極として機能するゲート電極 31 の有する点である。したがって、トランジスタ 400a 及びトランジスタ 400b を同一の工程で作製することが可能である。よって、表示装置の作製工程の簡略化を図ることが可能となる。30

#### 【0102】

<トランジスタの構成要素の詳細>

以下に、トランジスタ 400a、トランジスタ 400b の構成の詳細について説明する。。

#### 【0103】

基板 11 の材質などに大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有している必要がある。例えば、ガラス基板、セラミック基板、石英基板、サファイア基板等を、基板 11 として用いてもよい。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウム等の化合物半導体基板、SOI 基板等を適用することも可能であり、これらの基板上に半導体素子が設けられたものを、基板 11 として用いてもよい。なお、基板 11 として、ガラス基板を用いる場合、第 6 世代 (1500 mm × 1850 mm)、第 7 世代 (1870 mm × 2200 mm)、第 8 世代 (2200 mm × 2400 mm)、第 9 世代 (2400 mm × 2800 mm)、第 10 世代 (2950 mm × 3400 mm) 等の大面積基板を用いることで、大型の表示装置を作製することができる。40

#### 【0104】

また、基板 11 として、可撓性基板を用い、可撓性基板上に直接、トランジスタ 400a、トランジスタ 400b を形成してもよい。または、基板 11 とトランジスタ 400a、トランジスタ 400b の間に剥離層を設けてもよい。剥離層は、その上に半導体装置を50

一部あるいは全部完成させた後、基板 11 より分離し、他の基板に転載するのに用いることができる。その際、トランジスタ 400a、トランジスタ 400b は耐熱性の劣る基板や可撓性の基板にも転載できる。

#### 【0105】

ゲート電極 13a、13b は、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タンクスチルから選ばれた金属元素、または上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いて形成することができる。また、マンガン、ジルコニウムのいずれか一または複数から選択された金属元素を用いててもよい。また、ゲート電極 13a、13b は、単層構造でも、二層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、窒化チタン膜上にチタン膜を積層する二層構造、窒化チタン膜上にタンクスチル膜を積層する二層構造、窒化タンタル膜または窒化タンクスチル膜上にタンクスチル膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、チタン膜と、そのチタン膜上にアルミニウム膜を積層し、さらにその上にチタン膜を形成する三層構造等がある。また、アルミニウムに、チタン、タンタル、タンクスチル、モリブデン、クロム、ネオジム、スカンジウムから選ばれた元素の膜、または複数組み合わせた合金膜、もしくは窒化膜を用いててもよい。

#### 【0106】

また、ゲート電極 13a、13b は、インジウム錫酸化物 (ITO)、酸化タンクスチルを含むインジウム酸化物、酸化タンクスチルを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物等の透光性を有する導電性材料を適用することもできる。また、上記透光性を有する導電性材料と、上記金属元素の積層構造とすることもできる。

#### 【0107】

絶縁膜 15 は、例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化ハフニウム、酸化ガリウムまたは Ga-Zn 系金属酸化物、窒化シリコンなどを用いればよく、積層または単層で設ける。

#### 【0108】

また、絶縁膜 15 として、ハフニウムシリケート ( $HfSiO_x$ )、窒素が添加されたハフニウムシリケート ( $HfSi_{x-y}O_yN_z$ )、窒素が添加されたハフニウムアルミネート ( $HfAl_xO_yN_z$ )、酸化ハフニウム、酸化イットリウムなどの high-k 材料を用いることでトランジスタのゲートリーキを低減できる。

#### 【0109】

絶縁膜 15 の厚さは、5 nm 以上 400 nm 以下、より好ましくは 10 nm 以上 300 nm 以下、より好ましくは 50 nm 以上 250 nm 以下とするとよい。

#### 【0110】

一対の電極 20a、20b 及び一対の電極 20c、20d は、アルミニウム、チタン、クロム、ニッケル、銅、イットリウム、ジルコニウム、モリブデン、銀、タンタル、またはタンクスチルからなる単体金属、またはこれを主成分とする合金を単層構造または積層構造として用いる。例えば、シリコンを含むアルミニウム膜の単層構造、チタン膜上にアルミニウム膜を積層する二層構造、タンクスチル膜上にアルミニウム膜を積層する二層構造、銅 - マグネシウム - アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タンクスチル膜上に銅膜を積層する二層構造、チタン膜または窒化チタン膜と、そのチタン膜または窒化チタン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にチタン膜または窒化チタン膜を形成する三層構造、モリブデン膜または窒化モリブデン膜と、そのモリブデン膜または窒化モリブデン膜上に重ねてアルミニウム膜または銅膜を積層し、さらにその上にモリブデン膜または窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫または酸化亜鉛を含む透明導電材料を用いてもよい。

10

20

30

40

50

## 【0111】

絶縁膜28は、酸化物半導体膜17a、17bに接する酸化物絶縁膜23、酸化物絶縁膜23に接する酸化物絶縁膜25、酸化物絶縁膜25に接する窒化物絶縁膜27を有する。絶縁膜28は、少なくとも、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を有することが好ましい。ここでは、酸化物絶縁膜23として、酸素を透過する酸化物絶縁膜を形成し、酸化物絶縁膜25として、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を形成し、窒化物絶縁膜27として、水素及び酸素をプロックする窒化物絶縁膜を形成する。なお、ここでは、絶縁膜28を3層構造としたが、適宜1層、2層、または4層以上とすることができます。なお、これらの場合、少なくとも、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を有することが好ましい。

10

## 【0112】

酸化物絶縁膜23は、酸素を透過する酸化物絶縁膜である。このため、酸化物絶縁膜23上に設けられる、酸化物絶縁膜25から脱離する酸素を、酸化物絶縁膜23を介して酸化物半導体膜17a、17bに移動させることができる。また、酸化物絶縁膜23は、後に形成する酸化物絶縁膜25を形成する際の、酸化物半導体膜17a、17bへのダメージ緩和膜としても機能する。

## 【0113】

酸化物絶縁膜23としては、厚さが5nm以上150nm以下、好ましくは5nm以上50nm以下の酸化シリコン、酸化窒化シリコン等を用いることができる。なお、本明細書中において、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多い膜を指し、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多い膜を指す。

20

## 【0114】

また、酸化物絶縁膜23は、欠陥量が少ないことが好ましく、代表的には、E S R (Electron Spin Resonance)測定により、シリコンのダングリングボンドに由来する $g = 2.001$ に現れる信号のスピン密度が $3 \times 10^{17} \text{ spins/cm}^3$ 以下であることが好ましい。これは、酸化物絶縁膜23に含まれる欠陥密度が多いと、当該欠陥に酸素が結合してしまい、酸化物絶縁膜23における酸素の透過量が減少してしまうためである。

30

## 【0115】

また、酸化物絶縁膜23と酸化物半導体膜17a、17bとの界面における欠陥量が少ないことが好ましく、代表的には、E S R測定により、酸化物半導体膜17a、17bの欠陥に由来する $g = 1.93$ に現れる信号のスピン密度が $1 \times 10^{17} \text{ spins/cm}^3$ 以下、さらには検出下限以下であることが好ましい。

## 【0116】

なお、酸化物絶縁膜23においては、外部から酸化物絶縁膜23に入った酸素が全て酸化物絶縁膜23の外部に移動する場合がある。または、外部から酸化物絶縁膜23に入った酸素の一部が、酸化物絶縁膜23にとどまる場合もある。また、外部から酸化物絶縁膜23に酸素が入ると共に、酸化物絶縁膜23に含まれる酸素が酸化物絶縁膜23の外部へ移動することで、酸化物絶縁膜23において酸素の移動が生じる場合もある。

40

## 【0117】

酸化物絶縁膜23に接するように酸化物絶縁膜25が形成されている。酸化物絶縁膜25は、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を用いて形成する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、加熱により酸素の一部が脱離する。化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜は、表面温度が100以上700以下、または100以上500以下の範囲で行われるTDS分析にて、酸素原子に換算しての酸素の脱離量が $1.0 \times 10^{18} \text{ atoms/cm}^3$ 以上、好ましくは $3.0 \times 10^{20} \text{ atoms/cm}^3$ 以上である酸化物絶縁膜である。

50

## 【0118】

酸化物絶縁膜25としては、厚さが30nm以上500nm以下、好ましくは50nm以上400nm以下の、酸化シリコン、酸化窒化シリコン等を用いることができる。

## 【0119】

また、酸化物絶縁膜25は、欠陥量が少ないことが好ましく、代表的には、ESR測定により、シリコンのダンギリングボンドに由来する $g = 2.001$ に現れる信号のスピニ密度が $1.5 \times 10^{18}$ spins/cm<sup>3</sup>未満、更には $1 \times 10^{18}$ spins/cm<sup>3</sup>以下であることが好ましい。なお、酸化物絶縁膜25は、酸化物絶縁膜23と比較して酸化物半導体膜17a、17bから離れているため、酸化物絶縁膜23より、欠陥密度が多くともよい。

10

## 【0120】

窒化物絶縁膜27は、少なくとも、水素及び酸素のブロッキング効果を有する。さらに、好ましくは、酸素、水素、水、アルカリ金属、アルカリ土類金属等のブロッキング効果を有する。絶縁膜28に窒化物絶縁膜27を設けることで、酸化物半導体膜17a、17bからの酸素の外部への拡散と、外部から酸化物半導体膜17a、17bへの水素、水等の侵入を防ぐことができる。

## 【0121】

窒化物絶縁膜27としては、厚さが50nm以上300nm以下、好ましくは100nm以上200nm以下の、窒化シリコン、窒化酸化シリコン、窒化アルミニウム、窒化酸化アルミニウム等がある。

20

## 【0122】

なお、窒化物絶縁膜27の代わりに、酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜を設けてもよい。酸素、水素、水等のブロッキング効果を有する酸化物絶縁膜としては、酸化アルミニウム、酸化窒化アルミニウム、酸化ガリウム、酸化窒化ガリウム、酸化イットリウム、酸化窒化イットリウム、酸化ハフニウム、酸化窒化ハフニウム等がある。

## 【0123】

トランジスタ400aにおいて、ゲート電極31及び電極32は、透光性を有する導電膜を用いる。透光性を有する導電膜は、インジウム錫酸化物(以下、ITOともいう。)、インジウム亜鉛酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、酸化ケイ素を含むインジウム錫酸化物等がある。

30

## 【0124】

< Dual Gate 駆動による電流駆動力の向上について>

本実施の形態の表示装置では、高いオン電流及び高い電界効果移動度が望まれる画素の駆動トランジスタとして機能するトランジスタ400aとして、チャネルが形成される酸化物半導体膜17aの上層及び下層にそれぞれ重なるゲート電極13a及びゲート電極31を有し、各ゲート電極が互いに電気的に接続している、すなわちデュアルゲート駆動(Dual Gate 駆動)を行うトランジスタを用い、且つそのチャネル長を0.5μm以上4.5μm以下と微細化している。以下では、酸化物半導体膜を挟んで対向するゲート電極が接続し、両電極が同電位であるDual Gate 駆動のトランジスタにおいて、チャネル長Lを小さくすることにより、電流駆動力が向上することについて説明する。

40

## 【0125】

<<理想的なモデルにおける飽和移動度について>>

はじめに、界面準位や界面散乱などの効果を考慮しない、理想的なモデルについてシミュレーションで検討を行った。図30に、計算で用いたトランジスタのモデルを示す。なお、計算にはデバイスシミュレーションソフトAtlas(Silvaco社製)を用いた。

## 【0126】

図30に示すトランジスタは、ゲート電極GE\_1上にゲート絶縁膜GI\_1が形成さ

50

れ、ゲート絶縁膜 GI\_1 上に酸化物半導体膜 OS が形成される。ゲート絶縁膜 GI\_1 及び酸化物半導体膜 OS 上にソース電極 S 及びドレイン電極 D が形成される。酸化物半導体膜 OS、ソース電極 S 及びドレイン電極 D 上にゲート絶縁膜 GI\_2 が形成される。ゲート絶縁膜 GI\_2 上にゲート電極 GE\_2 が形成される。また、ゲート電極 GE\_1 及びゲート電極 GE\_2 は、ゲート絶縁膜 GI\_1 及びゲート絶縁膜 GI\_2 に形成される開口部(図示しない。)において、接続する。

## 【0127】

計算に用いた条件を表1に示す。

## 【0128】

## 【表1】

10

|                    |                                          |

|--------------------|------------------------------------------|

| チャネル長(条件振り)        | 2, 3, 6, 10 μm                           |

| チャネル幅              | 50 μm                                    |

| GI_1の厚さT1          | 450nm                                    |

| GI_2の厚さT2          | 450nm                                    |

| GI_1、GI_2の誘電率Er    | 3.9                                      |

| OSの厚さ              | 35nm                                     |

| OSの移動度             | 10cm <sup>2</sup> /V sec                 |

| GI_1、GI_2の誘電率Er    | 15                                       |

| SD直下におけるOSのドナー密度   | 1 × 10 <sup>19</sup> / cm <sup>3</sup>   |

| チャネル領域におけるOSのドナー密度 | 6.6 × 10 <sup>-9</sup> / cm <sup>3</sup> |

| ドレイン電圧             | 1V, 10V                                  |

20

## 【0129】

ゲート電極 GE\_1 及びゲート電極 GE\_2 は接続されているため、常に等電位である。また、当該モデルは二次元シミュレーションを用いているため、チャネル幅方向の効果については考慮されない。また、ドレイン電圧(Vd)が10VのときのVg - Id特性の値を式1に代入することによって飽和移動度μ<sub>FE</sub>を算出した。なお、ここでは、飽和領域の電界効果移動度を飽和移動度として説明する。なお、計算によって得られる飽和移動度の最大値は、飽和領域(ゲート電圧(Vg) < ドレイン電圧(Vd) + しきい値電圧(Vth))における電流駆動力の指標であって、酸化物半導体膜の物性値としての移動度の近似値とは異なる。

30

## 【0130】

## 【数1】

$$\mu_{FE} = \left( \frac{\partial \sqrt{I_d}}{\partial V_g} \right)^2 \frac{2L}{C_{Bottom} W} \quad (1)$$

40

## 【0131】

なお、式1において、Wはトランジスタのチャネル幅であり、C<sub>Bottom</sub>は、ゲート電極 GE\_1 及び酸化物半導体膜 OS の間の単位面積当たりの容量値である。

## 【0132】

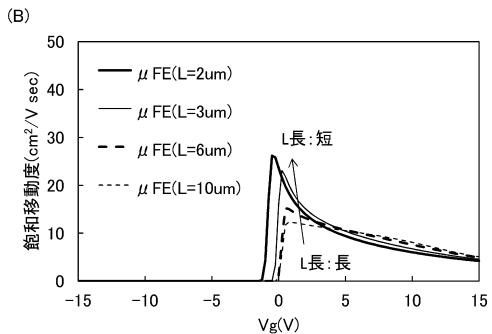

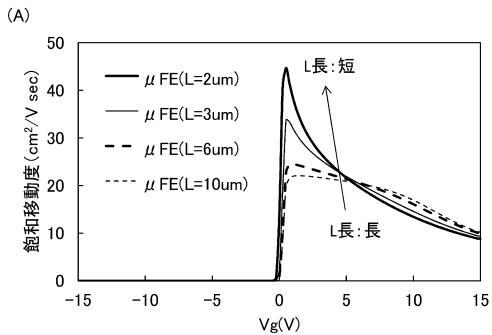

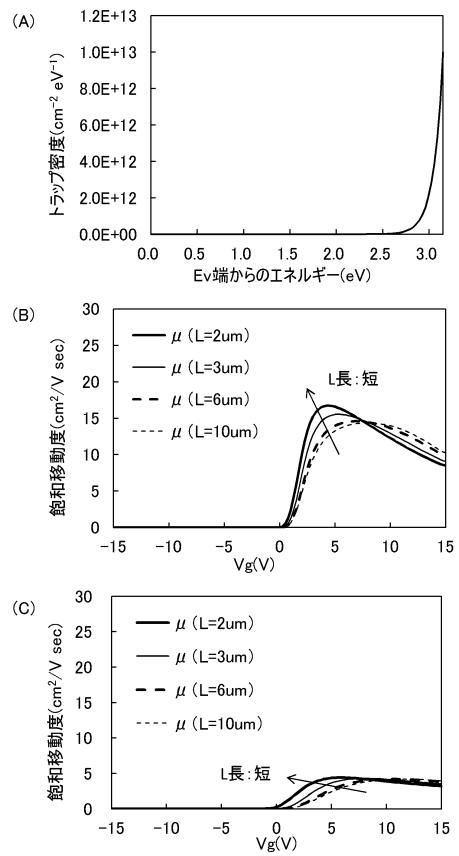

Dual Gate 駆動のトランジスタの計算結果を図31(A)に示し、ゲート電極 GE\_2 を有さないSingle Gate 駆動のトランジスタの計算結果を図31(B)に示す。

## 【0133】

50

図31より、Dual Gate駆動のトランジスタ、及びSingle Gate駆動のトランジスタそれぞれにおいて、鋭いピークを有する飽和移動度が得られた。また、L長が短いほど飽和移動度のピーク値が高くなっている。

#### 【0134】

ここで、チャネル長Lが短くなるにつれ飽和移動度が向上しているが、これがトランジスタの電流駆動力の向上に相当するかについて、以下に説明する。

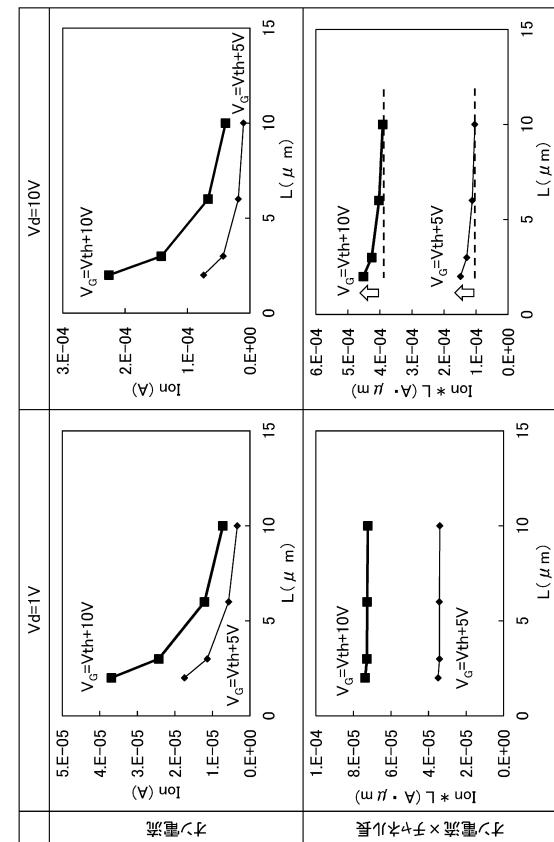

#### 【0135】

理想的なモデルのシミュレーションから得られた結果において、ゲート電圧が  $V_g = V_{th} + 5\text{V}$  のときと  $V_g = V_{th} + 10\text{V}$  のときにおける、オン電流をL長に対してプロットしたグラフを図32に示す。図32の上段は、オン電流を示し、図32の下段は、オン電流 × チャネル長を示す。なお、図32において、左欄はドレイン電圧( $V_d$ )が1Vのときの計算結果であり、右欄はドレイン電圧( $V_d$ )が10Vのときの計算結果である。

#### 【0136】

図32に示すオン電流は、チャネル長(L)に反比例している。これは、オン電流はチャネル長(L)に反比例するためである。

#### 【0137】

また、オン電流が完全にチャネル長に反比例するのであれば、オン電流 × チャネル長の値は、チャネル長に依存せず一定値となる。図32において、ドレイン電圧( $V_d$ )が1Vの場合は、オン電流 × チャネル長の値は、チャネル長(L)に対して略一定値となっている。一方、ドレイン電圧( $V_d$ )が10Vの場合は、チャネル長(L)が短くなるにつれ、オン電流 × チャネル長の値が増加している。これは、ドレイン電圧( $V_d$ )が10Vの場合は、実効チャネル長(後述において説明する)が、図30において定められるチャネル長(ソース電極Sとドレイン電極Dの間の距離)よりも短くなっていることを表している。

#### 【0138】

<<バルク電流の理論>>

以下、理想的なモデルのトランジスタの飽和移動度において、低いゲート電圧でピークが生じる原因について説明する。

#### 【0139】

図30に示すトランジスタにおいて、酸化物半導体膜OSに含まれる電子密度は、酸化物半導体膜OSの膜厚方向に一定の値  $n_0(y)$  で表されると仮定する。yは酸化物半導体膜OS内のチャネル長方向の任意の位置を表している。酸化物半導体膜OSの膜厚方向におけるポテンシャル  $\phi$  は数式2に示され、一定となる。ただし、ゲート電極GE\_1のゲート電圧  $V_{g1}$  及びゲート電極GE\_2のゲート電圧  $V_{g2}$  が同電位であり、ゲート電極GE\_1側及びゲート電極GE\_2側におけるフラットバンド電圧を共に、フラットバンド電圧  $V_{FB}$  と仮定する。

#### 【0140】

#### 【数2】

$$\phi - V(y) = V_g - V_{FB} - V(y) \quad (2)$$

#### 【0141】

このとき、蓄積型である酸化物半導体膜を有するトランジスタにおいて、ドレイン電流  $I_d$  は、数式3に示すようなバルク電流  $I_{bulk}$  のみで近似的に与えられる。

#### 【0142】

10

20

30

40

## 【数3】

$$I_d \cong I_{bulk} = \frac{Wt}{L_{eff}} \mu k_B T [n_0(0) - n_0(L_{eff})] \quad (3)$$

## 【0143】

なお、数式3において、 $t$ は酸化物半導体膜の膜厚、 $\mu$ は酸化物半導体膜の電子移動度、 $k_B$ はボルツマン定数、 $T$ は絶対温度、 $L_{eff}$ は実効チャネル長である。なお、ここでは、チャネル長はソース電極及びドレイン電極の間隔のことであり、実効チャネル長とは酸化物半導体膜において、ソース電極下から広がるn領域と、ドレイン電極下から広がるn領域の間の距離を表す。特に、チャネル長が短い場合あるいはドレイン電圧が高い場合、実効チャネル長はチャネル長よりも短くなる。

## 【0144】

なお、 $n_0(0)$ は、上述の実効チャネル長で定められる領域のソース電極側端部における電子密度であり、数式4で表される。また、 $n_0(L_{eff})$ は、上述の実効チャネル長で定められる領域のドレイン電極側端部における電子密度であり、数式5で表される。なお、数式4及び数式5において、 $N_D$ は酸化物半導体膜のチャネル領域のドナー密度であり、 $q$ は素電荷である。

## 【0145】

## 【数4】

10

20

$$n_0(0) = N_D e^{q\phi/k_B T} = N_D e^{q(V_g - V_{FB})/k_B T} \quad (4)$$

## 【0146】

## 【数5】

30

$$n_0(L_{eff}) = N_D e^{q(\phi - V_d)/k_B T} = N_D e^{q(V_g - V_{FB} - V_d)/k_B T} \quad (5)$$

## 【0147】

$V_d > V_g - V_{th}$ 、且つ $V_g > V_{th}$ の飽和領域の場合、ドレイン電圧 $V_d$ は $V_g - V_{th}$ に置き換えられるので、数式3は数式6となる。

## 【0148】

## 【数6】

$$I_d = \frac{Wt}{L_{eff}} \mu k_B T N_D e^{-qV_{FB}/k_B T} (e^{qV_g/k_B T} - e^{qV_{th}/k_B T}) \quad (6)$$

40

## 【0149】

数式6で得られるドレイン電流 $I_d$ に対して、飽和移動度 $\mu_{FE}^{sat}$ を計算すると数式7となる。

## 【0150】

## 【数7】

$$\mu_{FE}^{sat} \equiv \left( \frac{d\sqrt{I_d}}{dV_g} \right)^2 \frac{2L}{C_{GI}W} = \frac{L t \mu q^2 N_D e^{-qV_{FB}/k_B T}}{2 L_{eff} C_{GI} k_B T} \frac{e^{qV_g/k_B T}}{1 - e^{q(V_g - V_{th})/k_B T}} \quad (7)$$

50

## 【0151】

数式7において、 $V_g$ を $V_t h$ とすると、分母が0になり、飽和移動度 $\mu_{FE}^{sat}$ は無限大に発散する。この性質が、図31に示されるような飽和移動度における、低いゲート電圧 $V_g$ でのピークの原因である。すなわち、酸化物半導体膜OSの内部を流れるバルク電流がドレイン電流の主要因であればあるほど、図31のチャネル長が2μmのときの飽和移動度のように、よりはっきりとしたピークが表れる。

## 【0152】

また、飽和移動度が大きくなる他の要因の一つとして、実効チャネル長 $L_{eff}$ がチャネル長Lに比べて短くなることが考えられる。例えば、酸化物半導体膜OSにおいて、ソース電極S及びドレイン電極Dと接する領域近傍において、n領域が広がることにより、実効チャネル長 $L_{eff}$ がチャネル長Lより短くなる。この影響は、数式7に示す飽和移動度 $\mu_{FE}^{sat}$ の $L/L_{eff}$ に対する比例関係からも明らかである。10

## 【0153】

<<酸化物半導体膜中の電流密度>>

バルク電流が飽和移動度に影響することは、蓄積型のデバイスである酸化物半導体膜を有するトランジスタに特有の現象であり、半導体膜としてシリコン膜を有するトランジスタのような、反転型のデバイスではバルク電流の影響が少ない。

## 【0154】

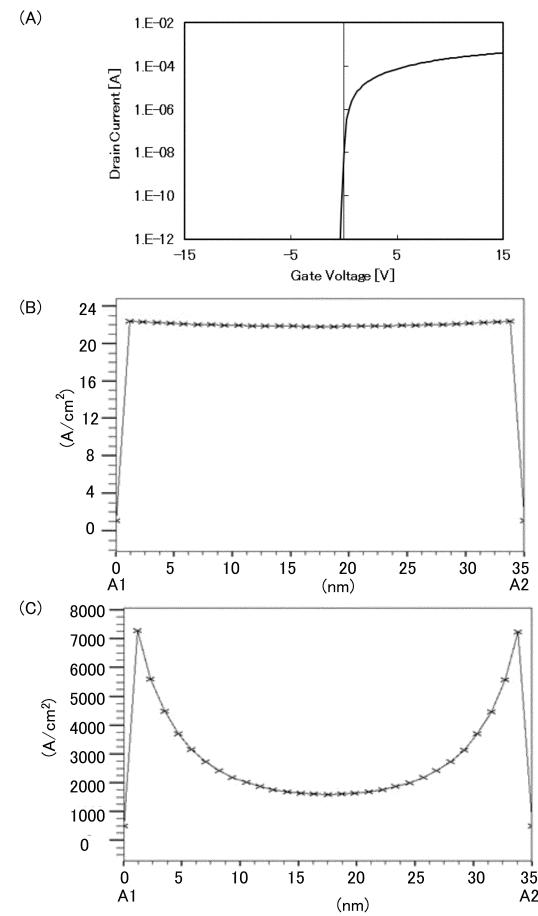

次に、デバイスシミュレーションによって得られた電流密度分布をプロットしたグラフを図33(B)及び図33(C)に示す。図33(A)は、ドレイン電圧を10Vとして計算で得られた $V_g - I_d$ 特性を示し、図33(B)及び図33(C)は、図30に示す酸化物半導体膜のA1-A2の断面方向の電流密度分布を示す。図33(B)は飽和領域( $V_g = 0.5V$ )、図33(C)は線形領域( $V_g = 15V$ )における電流密度分布を示す。なお、計算に用いたトランジスタのチャネル長L/チャネル幅Wは2μm/50μmであり、ドレイン電圧 $V_d$ を10Vとした。20

## 【0155】

図33(B)より、飽和領域(低いゲート電圧 $V_g$ )では、酸化物半導体膜OS中にほぼ一様に電流密度が分布している。一方で、図33(C)に示すように、線形領域(高いゲート電圧 $V_g$ )では、酸化物半導体膜OSの表面付近を流れる電流が支配的になっている。図33(B)に示すように飽和領域では、酸化物半導体膜OS中において電流密度がほぼ一様に分布していることから、飽和移動度にピークが生じている原因の一つは、バルク電流であることが分かる。30

## 【0156】

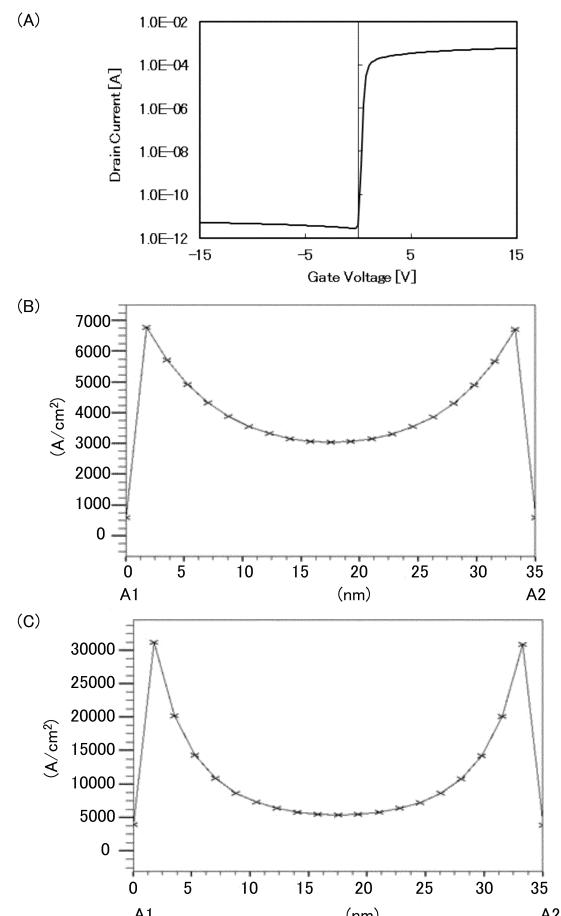

一方、デバイスシミュレーションによって得られた反転型デバイスの半導体膜の電流密度分布を図34(B)及び図34(C)に示す。図34は、図30に示すトランジスタの酸化物半導体膜OSを、n-p-n接合を含む半導体膜(シリコン)に置き換えた場合の計算結果である。半導体膜のチャネル領域には、 $1 \times 17 / \text{cm}^3$ の密度をもつアクセプター型不純物を仮定した。

## 【0157】

図34(A)は、ドレイン電圧を10Vとして計算で得られた $V_g - I_d$ 特性を示し、図34(B)及び図34(C)は、図30に示す半導体膜のA1-A2の断面方向の電流密度分布を示す。図34(B)は飽和領域( $V_g = 0.5V$ )、図34(C)は線形領域( $V_g = 15V$ )における電流密度分布である。なお、計算に用いたトランジスタのチャネル長L/チャネル幅Wは2μm/50μmであり、ドレイン電圧 $V_d$ を10Vとした。40

## 【0158】

蓄積型デバイスである酸化物半導体膜を有するトランジスタと異なり、反転型デバイスである半導体膜を有するトランジスタは、図34(B)に示すように、しきい値電圧近傍においても、半導体膜の表面を流れる電流が多くなっており、バルク電流の寄与は蓄積型デバイスと比べると小さい。

## 【0159】

10

30

40

50

以上のことから、蓄積型デバイスである酸化物半導体膜を有するトランジスタにおいて、理想的なモデルでは、バルク電流によって飽和移動度に鋭いピークが生じることが分かる。また、バルク電流によって、チャネル長 $L$ が短くなるほど飽和移動度が向上している。

#### 【0160】

なお、チャネル長 $L$ が短くなるほど、バルク電流によって生じた飽和移動度のピーク値が高くなる原因として、酸化物半導体膜OSにおいて、ソース電極S及びドレイン電極Dと接する領域近傍において、n領域が広がることにより、実効チャネル長 $L_{eff}$ がチャネル長 $L$ より短くなることが考えられる。また、チャネル長 $L$ が小さいと、ソース電極S及びドレイン電極Dの影響で酸化物半導体膜OSの伝導帯下端のエネルギー(Ec)が低くなり、伝導帯下端のエネルギーとフェルミエネルギーが近づく現象(CBL効果(Conduction band lowering effect))により、実効チャネル長 $L_{eff}$ がチャネル長 $L$ より短くなることが考えられる。飽和移動度は、式7に示したように、実効チャネル長 $L_{eff}$ が小さくなることで、 $L/L_{eff}$ に比例して大きくなる。この効果は、チャネル長 $L$ が小さいほど顕著に生じるので、チャネル長 $L$ が小さいほど飽和移動度が向上していると考えられる。10

#### 【0161】

<<浅い電子トラップ準位を仮定したモデル>>

次に、実際のトランジスタの飽和移動度に近似させるために、理想的なモデルのトランジスタにおいて、ゲート絶縁膜GI\_1及び酸化物半導体膜OSの界面に、電子をトラップすると負に帯電するアクセプター型の準位、即ち浅い電子トラップ準位を仮定して計算した結果を図35に示す。20

#### 【0162】

図35(A)に、ゲート絶縁膜GI\_1及び酸化物半導体膜OSの界面に仮定した電子トラップ準位のDOS(density of state)を示す。

#### 【0163】

次に、Dual Gate駆動のトランジスタ及びSingle Gate駆動のトランジスタそれぞれの飽和移動度を計算した。Dual Gate駆動のトランジスタの計算結果を図35(B)に示し、Single Gate駆動のトランジスタの計算結果を図35(C)に示す。30

#### 【0164】

図35(B)及び図35(C)より、Dual Gate駆動のトランジスタ及びSingle Gate駆動のトランジスタの飽和移動度において、理想的なモデルで得られたような鋭いピークが現れなかった。また、図35(C)より、Single Gate駆動のトランジスタでは、チャネル長 $L$ にあまり依存せず、飽和移動度のピーク値はおよそ $5\text{ cm}^2/\text{V}\cdot\text{sec}$ 前後であった。一方、Dual Gate駆動のトランジスタでは、チャネル長 $L$ が小さくなるほど、飽和移動度のピーク値が高くなり、その値は15乃至 $20\text{ cm}^2/\text{V}\cdot\text{sec}$ となった。この結果は、後述する実施例の結果と同じ傾向である。

#### 【0165】

このことから、Dual Gate駆動のトランジスタにおいて、チャネル長 $L$ を小さくする程、飽和移動度が上昇することが分かる。40

#### 【0166】

<Dual Gate駆動におけるチャネルエッチ型のトランジスタ及びチャネル保護型のトランジスタの比較>

以下に、チャネルエッチ型のトランジスタ及びチャネル保護型のトランジスタの電気特性について計算を行った結果を用いて、チャネルエッチ型のトランジスタ及びチャネル保護型のトランジスタ、それぞれの電界効果移動度及びオン電流について比較する。なお、ここでは、酸化物半導体膜を挟んで対向するゲート電極が接続し、同電位であるDual Gate駆動のトランジスタの電界効果移動度( $\mu_{FE}$ )及びオン電流( $I_{on}$ )につ50

いて比較するものとする。

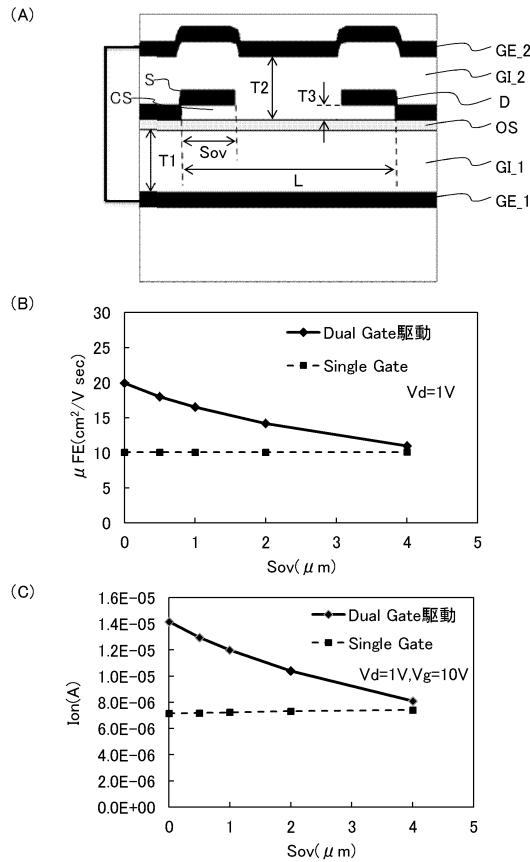

**【0167】**

図29(A)に、計算で用いたチャネル保護型のトランジスタの構造を示す。なお、計算にはデバイスシミュレーションソフト Atlas (Silvaco社製)を用いた。

**【0168】**

チャネル保護型のトランジスタは、ゲート電極GE\_1上にゲート絶縁膜GI\_1が形成され、ゲート絶縁膜GI\_1上に酸化物半導体膜OSが形成される。ゲート絶縁膜GI\_1及び酸化物半導体膜OS上にソース電極S及びドレイン電極Dが形成される。なお、ソース電極S及びドレイン電極Dの端部と酸化物半導体膜OSの間にはチャネル保護膜CSが形成される。酸化物半導体膜OS、ソース電極S及びドレイン電極D、並びにチャネル保護膜CS上にゲート絶縁膜GI\_2が形成される。ゲート絶縁膜GI\_2上にゲート電極GE\_2が形成される。また、ゲート電極GE\_1及びゲート電極GE\_2は、ゲート絶縁膜GI\_1及びゲート絶縁膜GI\_2に形成される開口部(図示しない。)において、接続する。

10

**【0169】**

チャネルエッチ型のトランジスタは、チャネル保護膜CSが設けられず、ソース電極S及びドレイン電極Dの端部が、酸化物半導体膜OSに接する構造である。

**【0170】**

計算に用いた条件を表2に示す。

**【0171】**

**【表2】**

20

|                    |                                          |

|--------------------|------------------------------------------|

| チャネル長L             | 10 μm                                    |

| チャネル幅W             | 50 μm                                    |

| GI_1の厚さT1          | 450nm                                    |

| GI_2の厚さT2          | 450nm                                    |

| チャネル保護膜CSの厚さT3     | 100nm                                    |

| GI_1、GI_2、CSの誘電率Er | 3.9                                      |

| OSの厚さ              | 35nm                                     |

| OSの移動度             | 10cm <sup>2</sup> /Vsec                  |

| OSの誘電率Er           | 15                                       |

| SD直下におけるOSのドナー密度   | 1 × 10 <sup>19</sup> / cm <sup>3</sup>   |

| チャネル領域におけるOSのドナー密度 | 6.6 × 10 <sup>-9</sup> / cm <sup>3</sup> |

30

**【0172】**

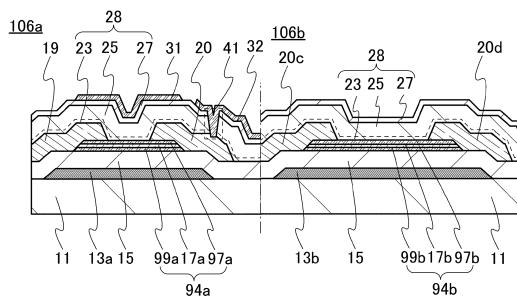

図29(A)は、Dual Gate駆動のトランジスタを示すが、比較例として、ゲート電極GE\_2を有さない、Single Gate駆動のトランジスタに関しても、Dual Gate駆動のトランジスタと同様の計算を行った。Single Gate駆動のトランジスタは、図2(A2)、図2(B)、及び図2(C2)の選択トランジスタとして機能するトランジスタ400bに相当する。

40

**【0173】**

チャネル保護型のトランジスタにおいて、チャネル保護膜CSを介して、酸化物半導体膜OSとソース電極Sまたはドレイン電極Dとが重畳する領域の長さを Sov とする。また、ソース電極S及びドレイン電極Dにおいて、チャネル保護膜CSを介して酸化物半導体膜OSと重畳する領域を Sov 領域とする。 Sov と電界効果移動度との関係を計算した結果を図29(B)に示し、 Sov とオン電流との関係を計算した結果を図29(C)

50

に示す。

**【0174】**

また、チャネルエッチ型のトランジスタにおいては、 $S_{ov}$ を $0 \mu m$ として、電界効果移動度及びオン電流を計算した。また、計算結果をそれぞれ図29(B)及び図29(C)に示す。

**【0175】**

なお、図29(B)は、ドレイン電圧 $V_d$ を $1V$ としたときの結果である。また、図29(C)は、ドレイン電圧 $V_d$ を $1V$ 、ゲート電圧 $V_g$ を $10V$ としたときの結果である。

**【0176】**

図29(B)に示すように、チャネルエッチ型のトランジスタ( $S_{ov}$ が $0 \mu m$ )では、Single Gate駆動のトランジスタと比較して、Dual Gate駆動のトランジスタの電界効果移動度は約2倍になっている。一方、チャネル保護型のトランジスタでは、Dual Gate駆動のトランジスタの電界効果移動度は、 $S_{ov}$ の長さが大きくなるに従って減少している。

**【0177】**

また、図29(C)に示すように、チャネルエッチ型のトランジスタ( $S_{ov}$ が $0 \mu m$ )では、Single Gate駆動のトランジスタと比較して、Dual Gate駆動のトランジスタのオン電流は約2倍になっている。一方、チャネル保護型のトランジスタでは、Dual Gate駆動のトランジスタのオン電流は、 $S_{ov}$ の長さが大きくなるに従って減少している。

**【0178】**

チャネル保護型のトランジスタでは、ソース電極S及びドレイン電極Dにおける $S_{ov}$ 領域がゲート電極GE\_2の電界を遮蔽する。このため、酸化物半導体膜OSにおいて、ゲート電極GE\_2の電圧によりキャリア密度を制御ができない領域が広がる。この結果、 $S_{ov}$ の長さが大きくなるにつれ、電界効果移動度が低減し、オン電流が小さくなると考えられる。以上のことから、チャネル保護型のトランジスタと比較して、チャネルエッチ型のトランジスタの方が、Dual Gate駆動における電界効果移動度の上昇効果及び電流增幅効果が高い。すなわち、本実施の形態の表示装置において発光素子の駆動トランジスタとして用いられるトランジスタ400aには、チャネルエッチ型のトランジスタを適用することが効果的である。

**【0179】**

また、チャネルエッチ型のトランジスタは、チャネル保護型のトランジスタと比較して、一対の電極の距離を小さくすることが容易である。このため、トランジスタ400aは、チャネル長を $0.5 \mu m$ 以上 $4.5 \mu m$ 以下、好ましくは $1 \mu m$ より大きく $4 \mu m$ 以下、より好ましくは $1 \mu m$ より大きく $3.5 \mu m$ 以下、より好ましくは $1 \mu m$ より大きく $2.5 \mu m$ 以下とすることができます。

**【0180】**

<表示装置の作製方法>

次に、図2に示すトランジスタ400a及びトランジスタ400bを含む表示装置の作製方法について、図3乃至図6を用いて説明する。なお、図3乃至図6において、A1-B1に示すチャネル長方向の断面図及びC1-D1に示すチャネル幅方向の断面図を用いて、トランジスタ400aの作製方法を説明し、A2-B2に示すチャネル長方向の断面図を用いてトランジスタ400bの作製方法を説明する。

**【0181】**

なお、トランジスタ400bのチャネル幅方向の断面図は、開口部42、43においてゲート電極13aと接するゲート電極31を有さない点以外はトランジスタ400aと同様である。

**【0182】**

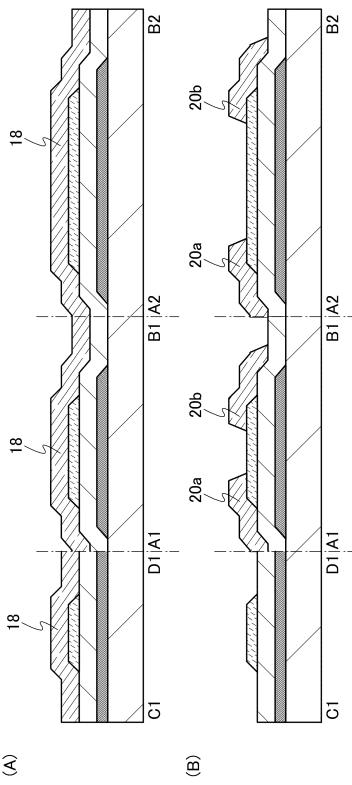

図3(A)に示すように、基板11上に、のちにゲート電極13a、13bとなる導電

10

20

30

40

50

膜 1 2 を形成する。

【 0 1 8 3 】

ここでは、基板 1 1 としてガラス基板を用いる。

【 0 1 8 4 】

導電膜 1 2 は、スパッタリング法、CVD 法、蒸着法等により形成する。

【 0 1 8 5 】

ここでは、導電膜 1 2 として、厚さ 100 nm のタンゲステン膜をスパッタリング法により形成する。

【 0 1 8 6 】

次に、導電膜 1 2 上に第 1 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜 1 2 の一部をエッチングして、ゲート電極 1 3 a、1 3 b を形成する。この後、マスクを除去する(図 3 (B) 参照。)。

【 0 1 8 7 】

導電膜 1 2 の一部をエッチングする方法としては、ウエットエッチング法、ドライエッティング法等があり、これらの一方または両方を用いることができる。

【 0 1 8 8 】

ここでは、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて導電膜 1 2 をドライエッティングして、ゲート電極 1 3 a、1 3 b を形成する。

【 0 1 8 9 】

なお、ゲート電極 1 3 a、1 3 b は、上記形成方法の代わりに、電解メッキ法、印刷法、インクジェット法等で形成してもよい。

【 0 1 9 0 】

次に、図 3 (C) に示すように、基板 1 1 及びゲート電極 1 3 a、1 3 b 上に、のちに絶縁膜 1 5 となる絶縁膜 1 4 を形成し、絶縁膜 1 4 上に、のちに酸化物半導体膜 1 7 a、1 7 b となる酸化物半導体膜 1 6 を形成する。

【 0 1 9 1 】

絶縁膜 1 4 は、スパッタリング法、CVD 法、蒸着法等で形成する。

【 0 1 9 2 】

絶縁膜 1 4 として酸化シリコン膜、酸化窒化シリコン膜、または窒化酸化シリコン膜を形成する場合、原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

【 0 1 9 3 】

絶縁膜 1 4 として酸化ガリウム膜を形成する場合、MOCVD (Metal Organic Chemical Vapor Deposition) 法を用いて形成することができる。

【 0 1 9 4 】

酸化物半導体膜 1 6 は、スパッタリング法、塗布法、パルスレーザー蒸着法、レーザーアブレーション法等を用いて形成することができる。

【 0 1 9 5 】

スパッタリング法で酸化物半導体膜 1 6 を形成する場合、プラズマを発生させるための電源装置は、RF 電源装置、AC 電源装置、DC 電源装置等を適宜用いることができる。

【 0 1 9 6 】

スパッタリングガスは、希ガス(代表的にはアルゴン) 霧囲気、酸化霧囲気、希ガス及び酸素の混合ガスを適宜用いる。なお、希ガス及び酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

【 0 1 9 7 】

また、ターゲットは、形成する酸化物半導体膜 1 6 の組成にあわせて、適宜選択すればよい。

10

20

30

40

50

## 【0198】

高純度真性または実質的に高純度真性である酸化物半導体膜16を得るために、チャンバー内を高真空排気するのみならずスパッタガスの高純度化も必要である。スパッタガスとして用いる酸素ガスやアルゴンガスは、露点が-40以下、好ましくは-80以下、より好ましくは-100以下、より好ましくは-120以下にまで高純度化したガスを用いることで酸化物半導体膜16に水分等が取り込まれることを可能な限り防ぐことができる。

## 【0199】

ここでは、In-Ga-Zn酸化物ターゲット( In : Ga : Zn = 1 : 1 : 1 )を用いたスパッタリング法により、酸化物半導体膜16として厚さ35nmのIn-Ga-Zn酸化物膜を形成する。

## 【0200】

次に、酸化物半導体膜16上に、第2のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて酸化物半導体膜16の一部をエッチングすることで、素子分離された酸化物半導体膜17a、17bをそれぞれ形成する。この後、マスクを除去する(図3(D)参照。)。

## 【0201】

酸化物半導体膜16の一部をエッチングする方法としては、ウエットエッチング法、ドライエッティング法等があり、これらの一方または両方を用いることができる。

## 【0202】

ここでは、フォトリソグラフィ工程によりマスクを形成し、当該マスクを用いて酸化物半導体膜16をウエットエッティングして、酸化物半導体膜17a、17bを形成する。

## 【0203】

なお、この後、150以上基板歪み点未満、好ましくは200以上450以下、更に好ましくは300以上450以下の加熱処理を行ってもよい。この結果、酸化物半導体膜17a、17bに含まれる水素、水等の含有量を低減することが可能であり、酸化物半導体膜17a、17bに含まれる不純物を低減することが可能である。

## 【0204】

次に、図4(A)に示すように、のちにトランジスタ400aの一対の電極20a、20b、及びトランジスタ400bの一対の電極20c、20dとなる導電膜18を形成する。

## 【0205】

導電膜18は、スパッタリング法、CVD法、蒸着法等で形成する。

## 【0206】

ここでは、厚さ50nmのタンゲステン膜及び厚さ300nmの銅膜を順にスパッタリング法により積層し、導電膜18を形成する。

## 【0207】

次に、導電膜18上に第3のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜18をエッティングして、一対の電極20a、20b及び一対の電極20c、20dを形成する。この後、マスクを除去する(図4(B)参照。)。

## 【0208】

ここでは、当該マスクを用いてタンゲステン膜及び銅膜をドライエッティングして、一対の電極20a、20b及び一対の電極20c、20dを形成する。なお、はじめに、ウエットエッティング法を用いて銅膜をエッティングし、次に、SF<sub>6</sub>を用いたドライエッティング法により、タンゲステン膜をエッティングすることで、該エッティングにおいて、銅膜の表面にフッ化物が形成される。該フッ化物により、銅膜からの銅元素の拡散が低減され、酸化物半導体膜17a、17bにおける銅濃度を低減することができる。

## 【0209】

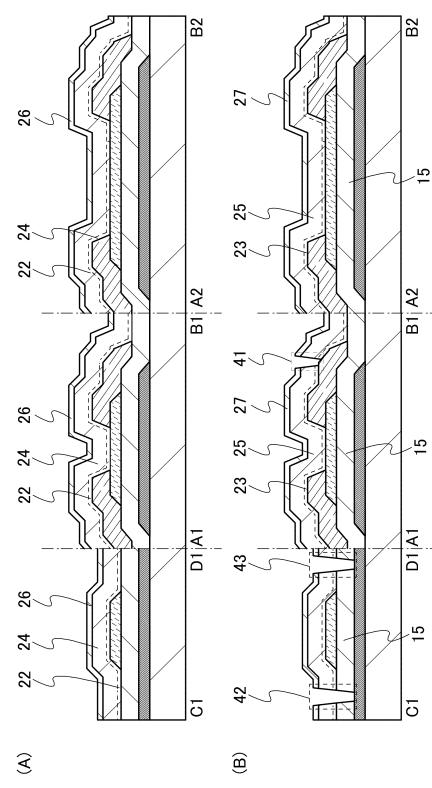

次に、図5(A)に示すように、酸化物半導体膜17a及び一対の電極20a、20b

10

20

30

40

50

上、並びに、酸化物半導体膜 17 b 及び一対の電極 20 c、20 d 上に、後に酸化物絶縁膜 23 となる酸化物絶縁膜 22、及び後に酸化物絶縁膜 25 となる酸化物絶縁膜 24 を形成する。

#### 【 0 2 1 0 】

なお、酸化物絶縁膜 22 を形成した後、大気に曝すことなく、連続的に酸化物絶縁膜 24 を形成することが好ましい。酸化物絶縁膜 22 を形成した後、大気開放せず、原料ガスの流量、圧力、高周波電力及び基板温度の一以上を調整して、酸化物絶縁膜 24 を連続的に形成することで、酸化物絶縁膜 22 及び酸化物絶縁膜 24 における界面の大気成分由來の不純物濃度を低減することができると共に、酸化物絶縁膜 24 に含まれる酸素を酸化物半導体膜 17 a、17 b に移動させることができると共に、酸化物半導体膜 17 a、17 b の酸素欠損量を低減することができる。

10

#### 【 0 2 1 1 】

酸化物絶縁膜 22 としては、プラズマ CVD 装置の真空排気された処理室内に載置された基板を 280 以上 400 以下に保持し、処理室に原料ガスを導入して処理室内における圧力を 20 Pa 以上 250 Pa 以下、さらに好ましくは 100 Pa 以上 250 Pa 以下とし、処理室内に設けられる電極に高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

#### 【 0 2 1 2 】

酸化物絶縁膜 22 の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

20

#### 【 0 2 1 3 】

上記条件を用いることで、酸化物絶縁膜 22 として酸素を透過する酸化物絶縁膜を形成することができる。また、酸化物絶縁膜 22 を設けることで、後に形成する酸化物絶縁膜 25 の形成工程において、酸化物半導体膜 17 a、17 b へのダメージ低減が可能である。

。

#### 【 0 2 1 4 】

当該成膜条件において、基板温度を上記温度とすることで、シリコン及び酸素の結合力が強くなる。この結果、酸化物絶縁膜 22 として、酸素が透過し、緻密であり、且つ硬い酸化物絶縁膜、代表的には、25 において 0.5 重量 % のフッ酸に対するエッチング速度が 10 nm / 分以下、好ましくは 8 nm / 分以下である酸化シリコン膜または酸化窒化シリコン膜を形成することができる。

30

#### 【 0 2 1 5 】

また、加熱をしながら酸化物絶縁膜 22 を形成するため、酸化物半導体膜 17 a、17 b に水素、水等が含まれる場合、当該工程において酸化物半導体膜 17 a、17 b に含まれる水素、水等を脱離させることができる。酸化物半導体膜 17 a、17 b に含まれる水素は、プラズマ中で発生した酸素ラジカルと結合し、水となる。酸化物絶縁膜 22 の成膜工程において基板が加熱されているため、酸素及び水素の結合により生成された水は、酸化物半導体膜 17 a、17 b から脱離する。即ち、プラズマ CVD 法によって酸化物絶縁膜 22 を形成することで、酸化物半導体膜 17 a、17 b に含まれる水及び水素の含有量を低減することができる。

40

#### 【 0 2 1 6 】

また、酸化物絶縁膜 22 を形成する工程において加熱するため、酸化物半導体膜 17 a、17 b が露出された状態での加熱時間が少なく、加熱処理による酸化物半導体膜からの酸素の脱離量を低減することができる。即ち、酸化物半導体膜 17 a、17 b 中に含まれる酸素欠損量を低減することができる。

#### 【 0 2 1 7 】

さらには、処理室の圧力を 100 Pa 以上 250 Pa 以下とすることで、酸化物絶縁膜 23 に含まれる水の含有量が少なくなるため、トランジスタ 400 a 及びトランジスタ 4

50

00bの電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。

#### 【0218】

また、処理室の圧力を100Pa以上250Pa以下とすることで、酸化物絶縁膜22を成膜する際に、酸化物半導体膜17a、17bへのダメージを低減することが可能であり、酸化物半導体膜17a、17bに含まれる酸素欠損量を低減することができる。特に、酸化物絶縁膜22または後に形成される酸化物絶縁膜24の成膜温度を高くする、代表的には220より高い温度とすることで、酸化物半導体膜17a、17bに含まれる酸素の一部が脱離し、酸素欠損が形成されやすい。また、トランジスタの信頼性を高めるため、後に形成する酸化物絶縁膜24の欠陥量を低減するための成膜条件を用いると、酸素脱離量が低減しやすい。10 これらの結果、酸化物半導体膜17a、17bの酸素欠損を低減することが困難な場合がある。しかしながら、処理室の圧力を100Pa以上250Pa以下とし、酸化物絶縁膜22の成膜時における酸化物半導体膜17a、17bへのダメージを低減することで、酸化物絶縁膜24からの少ない酸素脱離量でも酸化物半導体膜17a、17b中の酸素欠損を低減することが可能である。

#### 【0219】

なお、シリコンを含む堆積性気体に対する酸化性気体量を100倍以上とすることで、酸化物絶縁膜22に含まれる水素含有量を低減することが可能である。この結果、酸化物半導体膜17a、17bに混入する水素量を低減できるため、トランジスタのしきい値電圧のマイナスシフトを抑制することができる。20

#### 【0220】

ここでは、酸化物絶縁膜22として、流量30sccmのシラン及び流量4000sccmの一酸化二窒素を原料ガスとし、処理室の圧力を200Pa、基板温度を220とし、27.12MHzの高周波電源を用いて150Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ50nmの酸化窒化シリコン膜を形成する。当該条件により、酸素が透過する酸化窒化シリコン膜を形成することができる。

#### 【0221】

酸化物絶縁膜24としては、プラズマCVD装置の真空排気された処理室内に載置された基板を180以上280以下、さらに好ましくは200以上240以下に保持し、処理室内に原料ガスを導入して処理室内における圧力を100Pa以上250Pa以下、さらに好ましくは100Pa以上200Pa以下とし、処理室内に設けられる電極に0.17W/cm<sup>2</sup>以上0.5W/cm<sup>2</sup>以下、さらに好ましくは0.25W/cm<sup>2</sup>以上0.35W/cm<sup>2</sup>以下の高周波電力を供給する条件により、酸化シリコン膜または酸化窒化シリコン膜を形成する。30

#### 【0222】

酸化物絶縁膜24の原料ガスとしては、シリコンを含む堆積性気体及び酸化性気体を用いることが好ましい。シリコンを含む堆積性気体の代表例としては、シラン、ジシラン、トリシラン、フッ化シラン等がある。酸化性気体としては、酸素、オゾン、一酸化二窒素、二酸化窒素等がある。

#### 【0223】

酸化物絶縁膜24の成膜条件として、上記圧力の反応室において上記パワー密度の高周波電力を供給することで、プラズマ中で原料ガスの分解効率が高まり、酸素ラジカルが増加し、原料ガスの酸化が進むため、酸化物絶縁膜25中における酸素含有量が化学量論的組成よりも多くなる。一方、基板温度が、上記温度で形成された膜では、シリコンと酸素の結合力が弱いため、後の工程の加熱処理により膜中の酸素の一部が脱離する。この結果、化学量論的組成を満たす酸素よりも多くの酸素を含み、加熱により酸素の一部が脱離する酸化物絶縁膜を形成することができる。また、酸化物半導体膜17上に酸化物絶縁膜22が設けられている。このため、酸化物絶縁膜24の形成工程において、酸化物絶縁膜22が酸化物半導体膜17の保護膜となる。この結果、酸化物半導体膜17へのダメージを低減しつつ、パワー密度の高い高周波電力を用いて酸化物絶縁膜24を形成することができる。4050

きる。

**【0224】**

ここでは、酸化物絶縁膜24として、流量200sccmのシラン及び流量4000scdmの一酸化二窒素を原料ガスとし、反応室の圧力を200Pa、基板温度を220とし、27.12MHzの高周波電源を用いて1500Wの高周波電力を平行平板電極に供給したプラズマCVD法により、厚さ400nmの酸化窒化シリコン膜を形成する。なお、プラズマCVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると0.25W/cm<sup>2</sup>である。

**【0225】**

次に、加熱処理を行う。該加熱処理の温度は、代表的には、150以上400以下、好ましくは300以上400以下、好ましくは320以上370以下とする。

**【0226】**

該加熱処理は、電気炉、RTA装置等を用いることができる。RTA装置を用いることで、短時間に限り、基板の歪み点以上の温度で熱処理を行うことができる。そのため加熱処理時間を短縮することができる。

**【0227】**

加熱処理は、窒素、酸素、超乾燥空気（水の含有量が20ppm以下、好ましくは1ppm以下、好ましくは10ppb以下の空気）、または希ガス（アルゴン、ヘリウム等）の雰囲気下で行えばよい。なお、上記窒素、酸素、超乾燥空気、または希ガスに水素、水等が含まれないことが好ましい。

**【0228】**

当該加熱処理により、酸化物絶縁膜24に含まれる酸素の一部を酸化物半導体膜17a、17bに移動させ、酸化物半導体膜17a、17bに含まれる酸素欠損量をさらに低減することができる。

**【0229】**

また、酸化物絶縁膜22及び酸化物絶縁膜24に水、水素等が含まれる場合、水、水素等をブロッキングする機能を有する窒化物絶縁膜26を形成した後で加熱処理を行うと、酸化物絶縁膜22及び酸化物絶縁膜24に含まれる水、水素等が、酸化物半導体膜17a、17bに移動し、酸化物半導体膜17a、17bに欠陥が生じてしまう。しかしながら、当該加熱処理を窒化物絶縁膜26の形成前に行うことにより、酸化物絶縁膜22及び酸化物絶縁膜24に含まれる水、水素等を脱離させることができるのであり、トランジスタ400a、トランジスタ400bの電気特性のばらつきを低減すると共に、しきい値電圧の変動を抑制することができる。

**【0230】**

なお、加熱しながら酸化物絶縁膜24を、酸化物絶縁膜22上に形成することで、酸化物半導体膜17a、17bに酸素を移動させ、酸化物半導体膜17a、17bに含まれる酸素欠損を低減することができるため、当該加熱処理を行わなくともよい。

**【0231】**

ここでは、窒素及び酸化雰囲気で、350、1時間の加熱処理を行う。

**【0232】**

また、一対の電極20a、20b及び一対の電極20c、20dを形成する際、導電膜のエッチングによって、酸化物半導体膜17a、17bはダメージを受け、酸化物半導体膜17a、17bのバックチャネル（酸化物半導体膜17a、17bにおいて、ゲート電極13a、13bと対向する面と反対側の面）側に酸素欠損が生じる。しかし、酸化物絶縁膜24に化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を適用することで、加熱処理によって当該バックチャネル側に生じた酸素欠損を低減することができる。これによりトランジスタ400a、400bの信頼性を向上させることができる。

**【0233】**

次に、スパッタリング法、CVD法等により、のちに窒化物絶縁膜27となる窒化物絶

10

20

30

40

50

縁膜 2 6 を形成する。

**【 0 2 3 4 】**

なお、窒化物絶縁膜 2 6 をプラズマ C V D 法で形成する場合、プラズマ C V D 装置の真空排気された処理室内に載置された基板を 3 0 0 以上 4 0 0 以下、さらに好ましくは 3 2 0 以上 3 7 0 以下にとすることで、緻密な窒化物絶縁膜を形成できるため好ましい。

**【 0 2 3 5 】**

窒化物絶縁膜 2 6 としてプラズマ C V D 法により窒化シリコン膜を形成する場合、シリコンを含む堆積性気体、窒素、及びアンモニアを原料ガスとして用いることが好ましい。

原料ガスとして、窒素と比較して少量のアンモニアを用いることで、プラズマ中でアンモニアが解離し、活性種が発生する。当該活性種が、シリコンを含む堆積性気体に含まれるシリコン及び水素の結合、及び窒素の三重結合を切断する。この結果、シリコン及び窒素の結合が促進され、シリコン及び水素の結合が少なく、欠陥が少なく、緻密な窒化シリコン膜を形成することができる。一方、原料ガスにおいて、窒素に対するアンモニアの量が多いと、シリコンを含む堆積性気体及び窒素それぞれの分解が進まず、シリコン及び水素結合が残存してしまい、欠陥が増大した、且つ粗な窒化シリコン膜が形成されてしまう。これらのため、原料ガスにおいて、アンモニアに対する窒素の流量比を 5 以上 5 0 以下、好ましくは 1 0 以上 5 0 以下とすることが好ましい。

**【 0 2 3 6 】**

ここでは、プラズマ C V D 装置の反応室に、流量 5 0 s c c m のシラン、流量 5 0 0 0 s c c m の窒素、及び流量 1 0 0 s c c m のアンモニアを原料ガスとし、処理室の圧力を 1 0 0 P a 、基板温度を 3 5 0 とし、 2 7 . 1 2 M H z の高周波電源を用いて 1 0 0 0 W の高周波電力を平行平板電極に供給したプラズマ C V D 法により、窒化物絶縁膜 2 6 として、厚さ 5 0 n m の窒化シリコン膜を形成する。なお、プラズマ C V D 装置は電極面積が 6 0 0 0 c m <sup>2</sup> である平行平板型のプラズマ C V D 装置であり、供給した電力を単位面積あたりの電力（電力密度）に換算すると  $1 . 7 \times 1 0 ^ { - 1 } W / c m ^ { 2 }$  である。

**【 0 2 3 7 】**

以上の工程により、酸化物絶縁膜 2 2 、酸化物絶縁膜 2 4 、及び窒化物絶縁膜 2 6 を形成することができる。

**【 0 2 3 8 】**

次に、加熱処理を行ってもよい。該加熱処理の温度は、代表的には、 1 5 0 以上 4 0 0 以下、好ましくは 3 0 0 以上 4 0 0 以下、好ましくは 3 2 0 以上 3 7 0 以下とする。

**【 0 2 3 9 】**

次に、窒化物絶縁膜 2 6 上に第 4 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて、絶縁膜 1 4 、酸化物絶縁膜 2 2 、酸化物絶縁膜 2 4 、及び窒化物絶縁膜 2 6 のそれぞれ一部をエッチングして、絶縁膜 1 5 と、酸化物絶縁膜 2 3 、酸化物絶縁膜 2 5 、及び窒化物絶縁膜 2 7 で構成される絶縁膜 2 8 とを形成する。なお、絶縁膜 2 8 は、トランジスタ 4 0 0 a のチャネル長方向の断面図である図 5 ( B ) の A 1 - B 1 に示すように、開口部 4 1 を有する。また、絶縁膜 1 5 及び絶縁膜 2 8 には、トランジスタ 4 0 0 a のチャネル幅方向の断面図である図 5 ( B ) の C 1 - D 1 に示すように、開口部 4 2 、 4 3 を有する。

**【 0 2 4 0 】**

次に、図 6 ( A ) に示すように、後にゲート電極 3 1 及び電極 3 2 となる導電膜 3 0 を形成する。

**【 0 2 4 1 】**

導電膜 3 0 は、スパッタリング法、 C V D 法、蒸着法等により形成する。

**【 0 2 4 2 】**

ここでは、スパッタリング法により導電膜 3 0 として厚さ 1 0 0 n m の I T O 膜を形成する。

10

20

30

40

50

**【 0 2 4 3 】**

次に、導電膜 3 0 上に第 5 のフォトマスクを用いたフォトリソグラフィ工程によりマスクを形成する。次に、該マスクを用いて導電膜の一部をエッチングして、ゲート電極 3 1 及び電極 3 2 を形成する。この後、マスクを除去する。

**【 0 2 4 4 】**

なお、図 6 ( B ) に示すように、トランジスタ 4 0 0 a では、チャネル幅方向において、絶縁膜 1 5 及び絶縁膜 2 8 に設けられる開口部の側面において酸化物半導体膜 1 7 a の側面と対向するように、ゲート電極 3 1 を形成する。

**【 0 2 4 5 】**

以上の工程により、トランジスタ 4 0 0 a 及びトランジスタ 4 0 0 b を作製することができる。 10

**【 0 2 4 6 】**

本実施の形態に示すトランジスタは、チャネル領域として機能する酸化物半導体膜に重畠して、化学量論的組成を満たす酸素よりも多くの酸素を含む酸化物絶縁膜を形成することで、当該酸化物絶縁膜の酸素を酸化物半導体膜に移動させることができる。この結果、酸化物半導体膜に含まれる酸素欠損の含有量を低減することが可能であり、信頼性の高いトランジスタとなる。

**【 0 2 4 7 】**

また、発光素子の駆動トランジスタとして機能するトランジスタ 4 0 0 a では、チャネル幅方向において、ゲート電極 3 1 を、絶縁膜 1 5 及び絶縁膜 2 8 に設けられる開口部 4 2、4 3 の側面において、酸化物半導体膜 1 7 a の側面と対向させることで、酸化物半導体膜 1 7 a の側面においても、ゲート電極 3 1 の電界の影響を受け、酸化物半導体膜 1 7 a の広い範囲においてキャリアが流れるため、トランジスタの電界効果移動度が上昇すると共に、オン電流が増大する。 20

**【 0 2 4 8 】**

また、発光素子の駆動トランジスタとして機能するトランジスタ 4 0 0 a のチャネル長を、0.5 μm 以上 4.5 μm 以下、好ましくは 1 μm より大きく 4 μm 以下、より好ましくは 1 μm より大きく 3.5 μm 以下、より好ましくは 1 μm より大きく 2.5 μm 以下とすることで、トランジスタの電界効果移動度をさらに上昇させることができる。 30

**【 0 2 4 9 】**

また、画素の選択トランジスタとして機能するトランジスタ 4 0 0 b のチャネル長を、トランジスタ 4 0 0 a よりも大きくすることで、カットオフ電流を低減することが可能となる。これによって、表示装置の低消費電力化を実現することができる。

**【 0 2 5 0 】**

上記より、酸化物半導体膜を有するトランジスタを備えた表示装置であって電気特性の優れた表示装置を得ることができる。また、酸化物半導体膜を有するトランジスタを備えた表示装置において、信頼性の高い表示装置を得ることができる。

**【 0 2 5 1 】**

なお、本実施の形態に示す構成及び方法などは、他の実施の形態に示す構成及び方法などと適宜組み合わせて用いることができる。 40

**【 0 2 5 2 】**

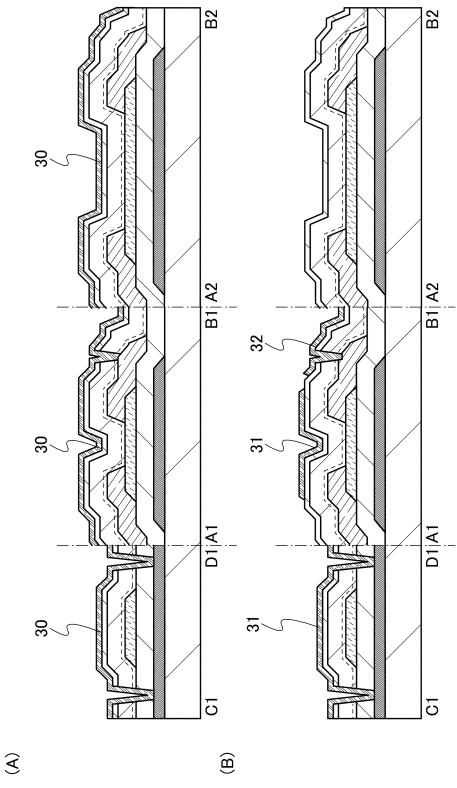

< 表示装置の変形例 1 >

図 2 と異なる構造の表示装置について、図 7 を用いて説明する。図 7 に示す表示装置は、駆動トランジスタとして機能するトランジスタ 4 1 0 a と、選択トランジスタとして機能するトランジスタ 4 0 0 b と、を含む画素を有する。図 7 ( A 1 ) は、駆動トランジスタとして機能するトランジスタ 4 1 0 a の上面図であり、図 7 ( A 2 ) は、選択トランジスタとして機能するトランジスタ 4 0 0 b の上面図であり、図 7 ( B ) は、図 7 ( A 1 ) の一点鎖線 A 3 - B 3 及び図 7 ( A 2 ) の一点鎖線 A 2 - B 2 の断面図であり、図 7 ( C 1 ) は、図 7 ( A 1 ) の一点鎖線 C 3 - D 3 間の断面図であり、図 7 ( C 2 ) は、図 7 ( 50

A 2 ) の一点鎖線 C 2 - D 2 間の断面図である。なお、図 7 ( A 1 ) 及び図 7 ( A 2 ) では、明瞭化のため、基板 1 1 及び絶縁膜などを省略している。

#### 【 0 2 5 3 】

図 7 ( A 2 ) 、図 7 ( B ) 及び図 7 ( C 2 ) において選択トランジスタとして機能するトランジスタ 4 0 0 b は、図 2 ( A 2 ) 、図 2 ( B ) 及び図 2 ( C 2 ) の構成と同様である。

#### 【 0 2 5 4 】

トランジスタ 4 1 0 a は、チャネル幅方向において、酸化物半導体膜 1 7 a の一方の側面の外側において、ゲート電極 1 3 a 及びゲート電極 5 1 が接続するが、酸化物半導体膜 1 7 a の他方の側面の外側において、絶縁膜 1 5 及び絶縁膜 2 8 を介して、ゲート電極 1 3 a 及びゲート電極 5 1 が対向する点が、先に示すトランジスタ 4 0 0 a と異なる。

10

#### 【 0 2 5 5 】

図 7 ( A 1 ) 、図 7 ( B ) 及び図 7 ( C 1 ) に示すトランジスタ 4 1 0 a は、チャネルエッヂ型のトランジスタであり、基板 1 1 上に設けられるゲート電極 1 3 a と、基板 1 1 及びゲート電極 1 3 a 上に形成される絶縁膜 1 5 と、絶縁膜 1 5 を介して、ゲート電極 1 3 a と重なる酸化物半導体膜 1 7 a と、酸化物半導体膜 1 7 a に接する一対の電極 2 0 a 、 2 0 b とを有する。また、絶縁膜 1 5 、酸化物半導体膜 1 7 a 、及び一対の電極 2 0 a 、 2 0 b 上に、酸化物絶縁膜 2 3 、酸化物絶縁膜 2 5 、及び窒化物絶縁膜 2 7 で構成される絶縁膜 2 8 と、絶縁膜 2 8 上に形成されるゲート電極 5 1 とを有する。ゲート電極 5 1 は、絶縁膜 1 5 及び絶縁膜 2 8 に設けられた開口部 4 2 においてゲート電極 1 3 a に接続する。また、一対の電極 2 0 a 、 2 0 b の一方、ここでは電極 2 0 b に接続する電極 3 2 が絶縁膜 2 8 上に形成される。なお、電極 3 2 は画素電極として機能する。

20

#### 【 0 2 5 6 】

トランジスタ 4 1 0 a は、チャネル長が 0 . 5  $\mu\text{m}$  以上 4 . 5  $\mu\text{m}$  以下、好ましくは 1  $\mu\text{m}$  より大きく 4  $\mu\text{m}$  以下、より好ましくは 1  $\mu\text{m}$  より大きく 3 . 5  $\mu\text{m}$  以下、より好ましくは 1  $\mu\text{m}$  より大きく 2 . 5  $\mu\text{m}$  以下である。トランジスタ 4 1 0 a は、ゲート電極 1 3 a 及びゲート電極 5 1 の間に酸化物半導体膜 1 7 a が設けられている。また、ゲート電極 5 1 は図 7 ( A 1 ) に示すように、上面から見て、絶縁膜 2 8 を介して酸化物半導体膜 1 7 a の端部と重なる。

#### 【 0 2 5 7 】

また、絶縁膜 1 5 及び絶縁膜 2 8 には複数の開口部を有する。代表的には、図 7 ( B ) に示すように、一対の電極 2 0 a 、 2 0 b の一方を露出する開口部 4 1 を有する。また、図 7 ( C 1 ) に示すように、酸化物半導体膜 1 7 a のチャネル幅方向の側面の一方の外側において、絶縁膜 1 5 及び絶縁膜 2 8 に開口部 4 2 が設けられ、該開口部 4 2 においてゲート電極 5 1 とゲート電極 1 3 a とが接続する。また、ゲート電極 5 1 は開口部 4 2 の側面において、酸化物半導体膜 1 7 a のチャネル幅方向の側面と対向する。また、酸化物半導体膜 1 7 a のチャネル幅方向の側面の他方の外側においては、ゲート電極 5 1 はゲート電極 1 3 a と接続しない。また、ゲート電極 5 1 端部は、酸化物半導体膜 1 7 a の側面の外側に位置する。

30

#### 【 0 2 5 8 】

なお、図 7 ( C 1 ) に示すように、チャネル幅方向において、絶縁膜 1 5 及び絶縁膜 2 8 の界面にゲート電極 5 1 を投影した際の端部と、酸化物半導体膜 1 7 a の側面との距離 d は、絶縁膜 1 5 の膜厚 t 1 と絶縁膜 2 8 の膜厚 t 2 を足し合わせた膜厚の 1 倍以上 7 . 5 倍以下とすることが好ましい。距離 d が、絶縁膜 1 5 の膜厚 t 1 と絶縁膜 2 8 の膜厚 t 2 を足し合わせた膜厚の 1 倍以上の場合、ゲート電極 5 1 の電界が酸化物半導体膜 1 7 a の側面、または側面及びその近傍を含む端部に影響するため、酸化物半導体膜 1 7 a の側面または端部における寄生チャネルの発生を抑制することができる。一方、距離 d が絶縁膜 1 5 の膜厚 t 1 と絶縁膜 2 8 の膜厚 t 2 を足し合わせた膜厚の 7 . 5 倍以下の場合、トランジスタの面積を小さくすることができる。

40

#### 【 0 2 5 9 】

次に、トランジスタ410aの作製工程について説明する。

**【0260】**

図3乃至図5(A)の工程を経て、基板11上にゲート電極13a、絶縁膜14、酸化物半導体膜17a、一対の電極20a、20b、酸化物絶縁膜22、酸化物絶縁膜24、及び窒化物絶縁膜26を形成する。なお、当該工程においては、第1のフォトマスク乃至第3のフォトマスクを用いたフォトリソグラフィ工程を行う。

**【0261】**

次に、第4のフォトマスクを用いたフォトリソグラフィ工程により窒化物絶縁膜26上にマスクを形成した後、絶縁膜14、酸化物絶縁膜22、酸化物絶縁膜24、及び窒化物絶縁膜26の一部をエッチングして、図7(A1)、図7(B)及び図7(C1)に示す開口部41、42を形成する。

10

**【0262】**

次に、図6(A)に示す工程と同様に、導電膜30を形成する。次に、第5のフォトマスクを用いたフォトリソグラフィ工程により導電膜30上にマスクを形成した後、導電膜30の一部をエッチングして図7(A1)、図7(B)及び図7(C1)に示すゲート電極51及び電極32を形成する。

**【0263】**

以上の工程により、トランジスタ410aを作製することができる。

**【0264】**

<表示装置の変形例2>

20

図2及び図7と異なる構造の表示装置について、図8を用いて説明する。図8に示す表示装置は、駆動トランジスタとして機能するトランジスタ420aと、選択トランジスタとして機能するトランジスタ400bと、を含む画素を有する。図8(A1)は、駆動トランジスタとして機能するトランジスタ420aの上面図であり、図8(A2)は、選択トランジスタとして機能するトランジスタ400bの上面図であり、図8(B)は、図8(A1)の一点鎖線A4-B4及び図8(A2)の一点鎖線A2-B2の断面図であり、図8(C1)は、図8(A1)の一点鎖線C4-D4間の断面図であり、図8(C2)は、図8(A2)の一点鎖線C2-D2間の断面図である。なお、図8(A1)及び図8(A2)では、明瞭化のため、基板11及び絶縁膜などを省略している。

**【0265】**

30

図8(A2)、図8(B)及び図8(C2)において選択トランジスタとして機能するトランジスタ400bは、図2(A2)、図2(B)及び図2(C2)の構成と同様である。また、図8(A1)、図8(B)及び図8(C1)において駆動トランジスタとして機能するトランジスタ420aは、ゲート電極13a及びゲート電極64が、導電膜62を介して接続している点が、先に示すトランジスタ410aと異なる。

**【0266】**

図8(A1)、(B)及び図8(C1)に示すトランジスタ420aは、チャネルエッチ型のトランジスタであり、基板11上に設けられるゲート電極13aと、基板11及びゲート電極13a上に形成される絶縁膜15と、絶縁膜15を介して、ゲート電極13aと重なる酸化物半導体膜17aと、酸化物半導体膜17aに接する一対の電極20a、20bとを有する。また、絶縁膜15、酸化物半導体膜17a、及び一対の電極20a、20b上に、酸化物絶縁膜23、酸化物絶縁膜25、及び窒化物絶縁膜27で構成される絶縁膜28と、絶縁膜28上に形成されるゲート電極64とを有する。ゲート電極64は、導電膜62を介して、ゲート電極13aに接続する。また、一対の電極20a、20bの一方、ここでは電極20bに接続する電極32が絶縁膜28上に形成される。なお、電極32は画素電極として機能する。

40

**【0267】**

トランジスタ420aは、チャネル長が0.5μm以上4.5μm以下、好ましくは1μmより大きく4μm以下、より好ましくは1μmより大きく3.5μm以下、より好ましくは1μmより大きく2.5μm以下である。また、トランジスタ420aは、ゲート

50

電極 13a 及びゲート電極 64 の間に酸化物半導体膜 17a が設けられている。また、ゲート電極 64 は図 8 (A1) に示すように、上面から見て、絶縁膜 28 を介して酸化物半導体膜 17a の端部と重なる。

#### 【0268】

また、絶縁膜 15 及び絶縁膜 28 は複数の開口部を有する。代表的には、図 8 (B) に示すように、トランジスタ 420a の一対の電極 20a、20b の一方を露出する開口部 41 を有する。また、図 8 (C1) に示すように、絶縁膜 15 に設けられた開口部 61 において、導電膜 62 がゲート電極 13a と接続する。なお、導電膜 62 は、一対の電極 20a、20b と同時に形成される。また、絶縁膜 28 に設けられた開口部 63 において、ゲート電極 64 は導電膜 62 と接続する。即ち、導電膜 62 を介してゲート電極 13a 及びゲート電極 64 は電気的に接続する。また、ゲート電極 13a 及びゲート電極 64 と同電位である導電膜 62 は酸化物半導体膜 17a の側面と対向する。

10

#### 【0269】

なお、図 8 (C1) に示すように、トランジスタ 420a は、酸化物半導体膜 17a のチャネル幅方向の側面の一方の外側のみにおいて、ゲート電極 13a 及びゲート電極 64 が導電膜 62 を介して接続するが、酸化物半導体膜 17a のチャネル幅方向の側面の双方の外側において、ゲート電極 13a 及びゲート電極 64 が導電膜 62 を介して接続してもよい。

#### 【0270】

次に、トランジスタ 420a の作製工程について説明する。

20

#### 【0271】

図 3 の工程を経て、基板 11 上に、ゲート電極 13a、絶縁膜 14、及び酸化物半導体膜 17a を形成する。当該工程においては、第 1 のフォトマスク及び第 2 のフォトマスクを用いたフォトリソグラフィ工程を行う。

#### 【0272】

次に、第 3 のフォトマスクを用いたフォトリソグラフィ工程により絶縁膜 14 上にマスクを形成した後、絶縁膜 14 の一部をエッチングして、図 8 (A1) 及び図 8 (C1) に示す開口部 61 を形成する。

#### 【0273】

次に、図 4 (A) 及び図 4 (B) に示す工程と同様に、第 4 のフォトマスクを用いたフォトリソグラフィ工程により導電膜 18 上にマスクを形成した後、導電膜 18 の一部をエッチングして、一対の電極 20a、20b、及び導電膜 62 を形成する。

30

#### 【0274】

次に、図 5 (A) に示す工程と同様に、酸化物絶縁膜 22、酸化物絶縁膜 24、及び窒化物絶縁膜 26 を形成する。次に、第 5 のフォトマスクを用いたフォトリソグラフィ工程により窒化物絶縁膜 26 上にマスクを形成した後、窒化物絶縁膜 26 の一部をエッチングして、図 8 (A1) 及び図 8 (C1) に示す開口部 63 を形成する。

#### 【0275】

次に、図 6 (A) に示す工程と同様に、導電膜 30 を形成する。次に、第 6 のフォトマスクを用いたフォトリソグラフィ工程により導電膜 30 上にマスクを形成した後、導電膜 30 の一部をエッチングして、図 8 (A1)、図 8 (B) 及び図 8 (C1) に示すゲート電極 64 及び電極 32 を形成する。

40

#### 【0276】

以上の工程により、トランジスタ 420a を作製することができる。

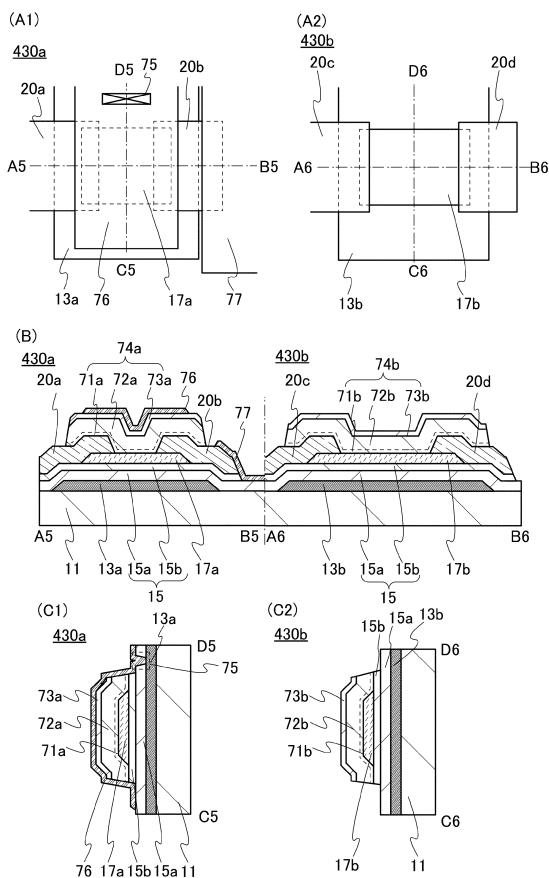

#### 【0277】

<表示装置の変形例 3 >

図 2、図 7 及び図 8 と異なる構造の表示装置について、図 11 を用いて説明する。図 11 に示す表示装置は、駆動トランジスタとして機能するトランジスタ 430a と、選択トランジスタとして機能するトランジスタ 430b と、を含む画素を有する。図 11 (A1) は、駆動トランジスタとして機能するトランジスタ 430a の上面図であり、図 11 (50

A 2 ) は、選択トランジスタとして機能するトランジスタ 4 3 0 b の上面図であり、図 1 1 ( B ) は、図 1 1 ( A 1 ) の一点鎖線 A 5 - B 5 及び図 1 1 ( A 2 ) の一点鎖線 A 6 - B 6 の断面図であり、図 1 1 ( C 1 ) は、図 1 1 ( A 1 ) の一点鎖線 C 5 - D 5 間の断面図であり、図 1 1 ( C 2 ) は、図 1 1 ( A 2 ) の一点鎖線 C 6 - D 6 間の断面図である。なお、図 1 1 ( A 1 ) 及び図 1 1 ( A 2 ) では、明瞭化のため、基板や絶縁膜などを省略している。

#### 【 0 2 7 8 】

図 1 1 ( A 1 ) 、図 1 1 ( B ) 及び図 1 1 ( C 1 ) に示すトランジスタ 4 3 0 a は、一对の電極 2 0 a 、 2 0 b の一方に接続する電極 7 7 が絶縁膜 1 5 上に形成される。また、酸化物半導体膜 1 7 a 及び一对の電極 2 0 a 、 2 0 b 上にトランジスタごとに分離された絶縁膜 7 4 a を有する点が、先に示す他の駆動用トランジスタと異なる。

#### 【 0 2 7 9 】

また、図 1 1 ( A 2 ) 、図 1 1 ( B ) 及び図 1 1 ( C 2 ) に示すトランジスタ 4 3 0 b は、酸化物半導体膜 1 7 b 及び一对の電極 2 0 c 、 2 0 d 上にトランジスタごとに分離された絶縁膜 7 4 b を有する点が、先に示したトランジスタ 4 0 0 b と異なる。

#### 【 0 2 8 0 】

図 1 1 ( A 1 ) 、図 1 1 ( B ) 及び図 1 1 ( C 1 ) に示すトランジスタ 4 3 0 a は、チャネルエッチ型のトランジスタであり、基板 1 1 上に設けられるゲート電極 1 3 a と、基板 1 1 及びゲート電極 1 3 a 上に形成される絶縁膜 1 5 と、絶縁膜 1 5 を介して、ゲート電極 1 3 a と重なる酸化物半導体膜 1 7 a と、酸化物半導体膜 1 7 a に接する一对の電極 2 0 a 、 2 0 b とを有する。また、絶縁膜 1 5 、酸化物半導体膜 1 7 a 、及び一对の電極 2 0 a 、 2 0 b 上に、酸化物絶縁膜 7 1 a 、酸化物絶縁膜 7 2 a 、及び窒化物絶縁膜 7 3 a で構成されるゲート絶縁膜として機能する絶縁膜 7 4 a と、絶縁膜 7 4 a 及び窒化物絶縁膜 1 5 a 上に形成されるゲート電極 7 6 とを有する。ゲート電極 7 6 は、窒化物絶縁膜 1 5 a に設けられた開口部 7 5 においてゲート電極 1 3 a と接続する。また、一对の電極 2 0 a 、 2 0 b の一方、ここでは電極 2 0 b に接続する電極 7 7 が絶縁膜 1 5 上に形成される。なお、電極 7 7 は画素電極として機能する。

#### 【 0 2 8 1 】

また図 1 1 ( A 2 ) 、図 1 1 ( B ) 及び図 1 1 ( C 2 ) に示すトランジスタ 4 3 0 b は、チャネルエッチ型のトランジスタであり、基板 1 1 上に設けられるゲート電極 1 3 b と、基板 1 1 及びゲート電極 1 3 b 上に形成される絶縁膜 1 5 と、絶縁膜 1 5 を介して、ゲート電極 1 3 b と重なる酸化物半導体膜 1 7 b と、酸化物半導体膜 1 7 b に接する一对の電極 2 0 c 、 2 0 d とを有する。また、絶縁膜 1 5 、酸化物半導体膜 1 7 b 、及び一对の電極 2 0 c 、 2 0 d 上に、酸化物絶縁膜 7 1 b 、酸化物絶縁膜 7 2 b 、及び窒化物絶縁膜 7 3 b で構成される絶縁膜 7 4 b と、を有する。

#### 【 0 2 8 2 】

トランジスタ 4 3 0 a 、 4 3 0 b に含まれる絶縁膜 1 5 は、窒化物絶縁膜 1 5 a 及び酸化物絶縁膜 1 5 b で形成される。酸化物絶縁膜 1 5 b は、酸化物半導体膜 1 7 a 、一对の電極 2 0 a 、 2 0 b 及び酸化物絶縁膜 7 1 a と重複する領域と、酸化物半導体膜 1 7 b 、一对の電極 2 0 c 、 2 0 d 及び酸化物絶縁膜 7 1 b と重複する領域と、に形成される。

#### 【 0 2 8 3 】

また、絶縁膜 7 4 a 、 7 4 b は、トランジスタごとに分離されており、且つ酸化物半導体膜 1 7 a 、 1 7 b とそれぞれ重畠する。具体的には、図 1 1 ( B ) に示すトランジスタ 4 3 0 a のチャネル長方向において、一对の電極 2 0 a 、 2 0 b 上に絶縁膜 7 4 a の端部が位置し、図 1 1 ( C 1 ) に示すトランジスタ 4 3 0 a のチャネル幅方向において、酸化物半導体膜 1 7 a の外側に絶縁膜 7 4 a の端部が位置する。また、図 1 1 ( B ) に示すトランジスタ 4 3 0 b のチャネル長方向において、一对の電極 2 0 c 、 2 0 d 上に絶縁膜 7 4 b の端部が位置し、図 1 1 ( C 2 ) に示すトランジスタ 4 3 0 b のチャネル幅方向において、酸化物半導体膜 1 7 b の外側に絶縁膜 7 4 b の端部が位置する。

#### 【 0 2 8 4 】

10

20

30

40

50

また、図11(C1)に示すチャネル幅方向において、ゲート電極76は、ゲート絶縁膜として機能する絶縁膜74aの側面において、酸化物半導体膜17aの側面と対向する。なお、絶縁膜74aの端部は、チャネル長方向において、一対の電極20a、20b上に設けられず、絶縁膜15上に設けられてもよい。この場合、電極77は、絶縁膜74a上に形成され、且つ絶縁膜74aの開口部において、一対の電極20a、20bの一方と接続する。

#### 【0285】

トランジスタ430aは、チャネル長が0.5μm以上4.5μm以下、好ましくは1μmより大きく4μm以下、より好ましくは1μmより大きく3.5μm以下、より好ましくは1μmより大きく2.5μm以下である。また、トランジスタ430aは、チャネル幅方向において、ゲート電極13a及びゲート電極76の間に、絶縁膜15及び絶縁膜74aを介して酸化物半導体膜17aが設けられている。また、ゲート電極76は、図11(A1)に示すように、上面から見て、絶縁膜74aを介して酸化物半導体膜17aの端部と重なる。

#### 【0286】

また、トランジスタ430bのチャネル長は、トランジスタ430aよりも大きい。これによって、画素の選択トランジスタとして機能するトランジスタ430bのカットオフ電流の値を低減することが可能となる。

#### 【0287】

なお、図11(C1)ではチャネル幅方向において、酸化物半導体膜17aのチャネル幅方向の側面の一方の外側のみにおいて、ゲート電極13a及びゲート電極76が接続する場合を例に示すが、酸化物半導体膜17aのチャネル幅方向の側面の双方の外側において、ゲート電極13a及びゲート電極76が接続してもよい。

#### 【0288】

次に、トランジスタ430a、430bの作製方法について説明する。

#### 【0289】

トランジスタ430a、430bは、図3乃至図5(A)に示す工程を経て、基板11上に、ゲート電極13a、13b、絶縁膜14、酸化物半導体膜17a、17b、一対の電極20a、20b、一対の電極20c、20d、酸化物絶縁膜22、酸化物絶縁膜24、及び窒化物絶縁膜26を形成する。当該工程においては、第1のフォトマスク乃至第3のフォトマスクを用いたフォトリソグラフィ工程を行う。

#### 【0290】

次に、図5(B)に示す工程において、第4のフォトマスクを用いたフォトリソグラフィ工程により、窒化物絶縁膜26上にマスクを形成した後、酸化物絶縁膜22、酸化物絶縁膜24、及び窒化物絶縁膜26の一部をエッチングして、トランジスタごとに分離された絶縁膜74a、74bを形成することができる。なお、絶縁膜14が窒化物絶縁膜及び酸化物絶縁膜で積層される場合、酸化物絶縁膜23のエッチングと共に、絶縁膜14の一部もエッチングされる。この結果、図11(B)に示すように、窒化物絶縁膜15a及び酸化物絶縁膜15bで形成される段差を有する絶縁膜15が形成される。

#### 【0291】

この後、図6に示す工程を経て、ゲート電極76及び電極77を形成する。

#### 【0292】

以上の工程により、トランジスタ430a、430bを作製することができる。

#### 【0293】

<表示装置の変形例4>

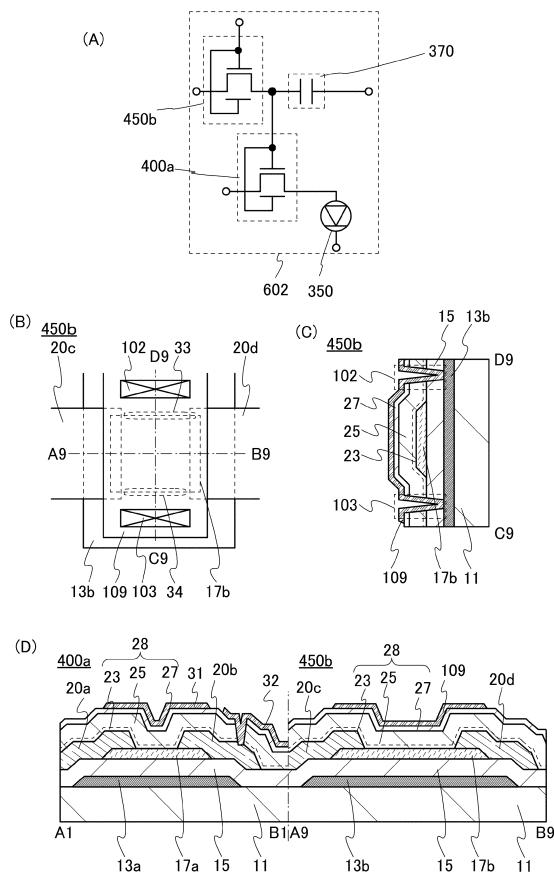

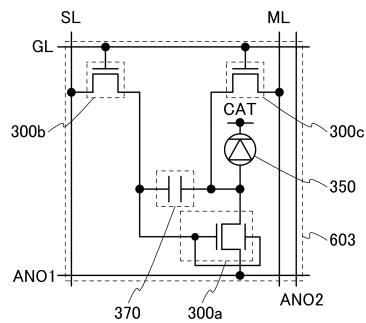

図2、図7、図8及び図11と異なる構造の表示装置について、図9を用いて説明する。図9(A)に、表示装置に含まれる画素602の等価回路図を示す。

#### 【0294】

図9(A)に示すように、本変形例の画素602は、発光素子350と、発光素子350の駆動トランジスタとして機能するトランジスタ400aと、選択トランジスタとして

10

20

30

40

50

機能するトランジスタ450bと、容量素子370と、を有し、トランジスタ400a及びトランジスタ450bは、ともに酸化物半導体膜の上下に配置されたゲート電極を含むいわゆるデュアルゲート型のトランジスタである。

**【0295】**

図素602に含まれるトランジスタ400aは、図2(A1)、図2(B)、図2(C1)及び図2(D)に示した構成と同様の構成とすることができます。

**【0296】**

また、図9(B)は、選択トランジスタとして機能するトランジスタ450bの上面図であり、図9(C)は、図9(B)の一点鎖線C9-D9の断面図であり、図9(D)は、図2(A1)で図示したトランジスタ400aの一点鎖線A1-B1及び図9(B)の一点鎖線A9-B9の断面図である。なお、図9(B)では、明瞭化のため、基板11及び絶縁膜などを省略している。

10

**【0297】**

図9に示すトランジスタ450bは、絶縁膜28上に、酸化物半導体膜17b及びゲート電極13bと重なるゲート電極109を有する点が、先に示す他の選択用トランジスタと異なる。

**【0298】**

図9に示すトランジスタ450bは、チャネルエッチ型のトランジスタであり、基板11上に設けられるゲート電極13bと、基板11及びゲート電極13b上に形成される絶縁膜15と、絶縁膜15を介して、ゲート電極13bと重なる酸化物半導体膜17bと、酸化物半導体膜17bに接する一対の電極20c、20dとを有する。また、絶縁膜15、酸化物半導体膜17b、及び一対の電極20c、20d上に、酸化物絶縁膜23、酸化物絶縁膜25、及び窒化物絶縁膜27で構成されるゲート絶縁膜として機能する絶縁膜28と、絶縁膜28及び絶縁膜15上に形成されるゲート電極109とを有する。ゲート電極109は、絶縁膜15及び絶縁膜28に設けられた開口部102、103においてゲート電極13bと接続する。

20

**【0299】**

トランジスタ450bに含まれるゲート電極109は、トランジスタ400aに含まれるゲート電極31と同じ層で形成される。

**【0300】**

また、トランジスタ450bは、少なくともトランジスタ400aよりも大きいチャネル長を有する。また、チャネル幅方向において、ゲート電極13b及びゲート電極109の間に、絶縁膜15及び絶縁膜28を介して酸化物半導体膜17bが設けられている。また、ゲート電極109は図9(B)に示すように、上面から見て、絶縁膜28を介して酸化物半導体膜17bの端部と重なる。

30

**【0301】**

トランジスタ400a、450bにおいて、エッティング等で島状に加工された酸化物半導体膜の端部においては、加工におけるダメージにより欠陥が形成されると共に、不純物付着などにより汚染される場合がある。このため、トランジスタにおいて酸化物半導体膜の上側又は下側に形成されるゲート電極のうち、一方のみが形成される場合、酸化物半導体膜が真性または実質的に真性であっても、電界などのストレスが与えられることによって酸化物半導体膜の端部は活性化され、n型(低抵抗領域)となりやすい。例えば、当該n型の端部が、図9(B)の破線33、34のように、一対の電極20c、20dの間に設けられると、n型の領域がキャリアのパスとなってしまい、寄生チャネルが形成される。この結果、しきい値電圧におけるドレイン電流の上昇が段階的であり、且つしきい値電圧がマイナスシフトしたトランジスタとなってしまう。

40

**【0302】**

しかしながら、図9に示すトランジスタ450bは、同電位であるゲート電極13b及びゲート電極109を有し、チャネル幅方向において、ゲート電極109が、絶縁膜28の側面において、酸化物半導体膜17bの側面と対向することで、ゲート電極109の電

50

界が酸化物半導体膜 17 b 側面からも影響する。この結果、酸化物半導体膜 17 b の側面、または側面及びその近傍を含む端部における寄生チャネルの発生が抑制される。この結果、トランジスタ 450 b は、しきい値電圧におけるドレイン電流の上昇が急峻である、電気特性の優れたトランジスタとすることができます。なお、上記の記載は、トランジスタ 400 a が有するゲート電極 13 a、ゲート電極 31 及び酸化物半導体膜 17 a についても適用することができる。

### 【0303】

なお、上記に示した本実施の形態の表示装置の構成及び変形例の表示装置の構成は、一部が異なる構成であるが、それぞれの構成を自由に組み合わせることが可能である。

### 【0304】

以上、本実施の形態で示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

### 【0305】

#### (実施の形態 2)

本実施の形態では、実施の形態 1 と異なる表示装置及びその作製方法について図面を参照して説明する。本実施の形態では、酸化物半導体膜に含まれる酸素欠損がより低減されたトランジスタを図 12 乃至図 15 を用いて説明する。

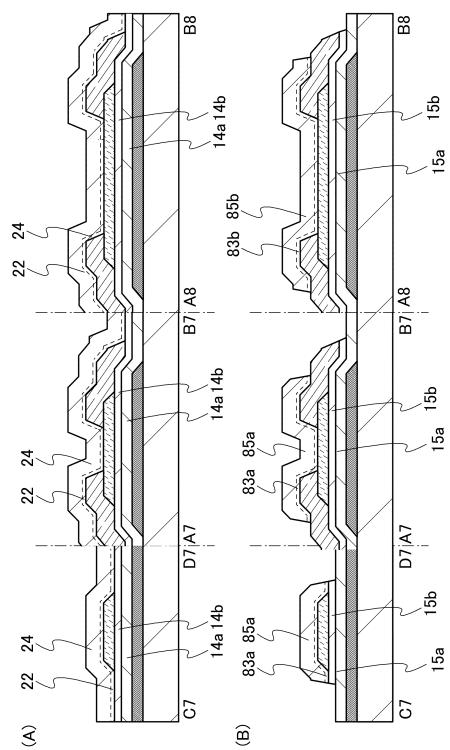

### 【0306】

図 12 に本実施の形態の表示装置の画素に含まれるトランジスタの上面図及び断面図を示す。

### 【0307】

本実施の形態の表示装置は、駆動トランジスタとして機能するトランジスタ 440 a と、選択トランジスタとして機能するトランジスタ 440 b と、を含む画素を有する。図 12 (A1) は、駆動トランジスタとして機能するトランジスタ 440 a の上面図であり、図 12 (A2) は、選択トランジスタとして機能するトランジスタ 440 b の上面図であり、図 12 (B) は、図 12 (A1) の一点鎖線 A7 - B7 間の断面図及び図 12 (A2) の一点鎖線 A8 - B8 間の断面図であり、図 12 (C1) は、図 12 (A1) の一点鎖線 C7 - D7 間の断面図であり、図 12 (C2) は、図 12 (A2) の一点鎖線 C8 - D8 間の断面図である。なお、図 12 (A1) 及び図 12 (A2) では、明瞭化のため、基板 11 及び絶縁膜などを省略している。

### 【0308】

図 12 (A1)、図 12 (B) 及び図 12 (C1) に示すトランジスタ 440 a は、チャネルエッチ型のトランジスタであり、基板 11 上に設けられるゲート電極 13 a と、基板 11 及びゲート電極 13 a 上に形成される絶縁膜 15 と、絶縁膜 15 を介して、ゲート電極 13 a と重なる酸化物半導体膜 17 a と、酸化物半導体膜 17 a に接する一対の電極 20 a、20 b とを有する。また、絶縁膜 15、酸化物半導体膜 17 a、及び一対の電極 20 a、20 b 上に、酸化物絶縁膜 83 a、酸化物絶縁膜 85 a、及び窒化物絶縁膜 87 で構成される絶縁膜 88 a と、絶縁膜 88 a 上に形成されるゲート電極 91 とを有する。ゲート電極 91 は、絶縁膜 15 及び窒化物絶縁膜 87 に設けられた開口部 96 においてゲート電極 13 a と接続する。また、一対の電極 20 a、20 b の一方、ここでは電極 20 b に接続する電極 92 が、窒化物絶縁膜 87 上に形成される。電極 92 は窒化物絶縁膜 87 に設けられた開口部 95 において、電極 20 b と接続する。なお、電極 92 は画素電極として機能する。

### 【0309】

また、図 12 (A2)、図 12 (B) 及び図 12 (C2) に示すトランジスタ 440 b は、チャネルエッチ型のトランジスタであり、基板 11 上に設けられるゲート電極 13 b と、基板 11 及びゲート電極 13 b 上に形成される絶縁膜 15 と、絶縁膜 15 を介して、ゲート電極 13 b と重なる酸化物半導体膜 17 b と、酸化物半導体膜 17 b に接する一対の電極 20 c、20 d とを有する。また、絶縁膜 15、酸化物半導体膜 17 b、及び一対の電極 20 c、20 d 上に、酸化物絶縁膜 83 b、酸化物絶縁膜 85 b、及び窒化物絶縁膜 87 で構成される絶縁膜 88 b と、絶縁膜 88 b 上に形成されるゲート電極 91 とを有する。ゲート電極 91 は、絶縁膜 15 及び窒化物絶縁膜 87 に設けられた開口部 96 においてゲート電極 13 b と接続する。また、一対の電極 20 c、20 d の一方、ここでは電極 20 d に接続する電極 92 が、窒化物絶縁膜 87 上に形成される。電極 92 は窒化物絶縁膜 87 に設けられた開口部 95 において、電極 20 d と接続する。

10

20

30

40

50

膜 8 7 で構成される絶縁膜 8 8 b を有する。

**【 0 3 1 0 】**

トランジスタ 4 4 0 a において、絶縁膜 1 5 及び絶縁膜 8 8 a はそれぞれゲート絶縁膜として機能する。また、トランジスタ 4 4 0 b において、絶縁膜 1 5 はゲート絶縁膜として機能する。絶縁膜 1 5 は、窒化物絶縁膜 1 5 a 及び酸化物絶縁膜 1 5 b で形成される。酸化物絶縁膜 1 5 b は、酸化物半導体膜 1 7 a、1 7 b、一対の電極 2 0 a、2 0 b、一対の電極 2 0 c、2 0 d、又は酸化物絶縁膜 8 3 a のいずれかと重なる領域に形成される。

**【 0 3 1 1 】**

なお、トランジスタ 4 4 0 b において、絶縁膜 8 8 b 上であって、ゲート電極 1 3 b 及び酸化物半導体膜 1 7 b と重なる領域に第 2 のゲート電極を設けてもよい。その場合、該第 2 のゲート電極は、絶縁膜 1 5 及び窒化物絶縁膜 8 7 に設けられた開口部においてゲート電極 1 3 b と接続することが好ましい。10

**【 0 3 1 2 】**

本実施の形態では、窒化物絶縁膜 1 5 a として、窒化シリコン膜を用いて形成する。また、酸化物絶縁膜 1 5 b は、実施の形態 1 に示す絶縁膜 1 5 において列挙した酸化物を適宜用いることができる。また、窒化物絶縁膜 1 5 a 及び酸化物絶縁膜 1 5 b はそれぞれ、絶縁膜 1 4 に列挙した作製方法を適宜用いることができる。また、酸化物絶縁膜 8 3 a、8 3 b は、実施の形態 1 に示す酸化物絶縁膜 2 3 と同様の材料及び作製方法を適宜用いて形成することができる。また、酸化物絶縁膜 8 5 a、8 5 b は、実施の形態 1 に示す酸化物絶縁膜 2 5 と同様の材料及び作製方法を適宜用いて形成することができる。窒化物絶縁膜 8 7 は、実施の形態 1 に示す窒化物絶縁膜 2 7 と同様の材料及び作製方法を適宜用いて形成することができる。また、ゲート電極 9 1 及び電極 9 2 は、実施の形態 1 に示すゲート電極 3 1 及び電極 3 2 と同様の材料及び作製方法を適宜用いて形成することができる。20

**【 0 3 1 3 】**

また、酸化物絶縁膜 8 3 a、8 3 b 及び酸化物絶縁膜 8 5 a、8 5 b は、トランジスタごとに分離されており、且つ酸化物半導体膜 1 7 a、1 7 b とそれぞれ重畳する。具体的には、図 1 2 ( B ) に示すトランジスタ 4 4 0 a のチャネル長方向の断面図において、一対の電極 2 0 a、2 0 b 上に酸化物絶縁膜 8 3 a 及び酸化物絶縁膜 8 5 a の端部が位置し、図 1 2 ( C 1 ) に示すトランジスタ 4 4 0 a のチャネル幅方向の断面図において、酸化物半導体膜 1 7 a の外側に酸化物絶縁膜 8 3 a 及び酸化物絶縁膜 8 5 a の端部が位置する。同様に、図 1 2 ( B ) に示すトランジスタ 4 4 0 b のチャネル長方向の断面図において、一対の電極 2 0 c、2 0 d 上に酸化物絶縁膜 8 3 b 及び酸化物絶縁膜 8 5 b の端部が位置し、図 1 2 ( C 2 ) に示すトランジスタ 4 4 0 b のチャネル幅方向の断面図において、酸化物半導体膜 1 7 b の外側に酸化物絶縁膜 8 3 b 及び酸化物絶縁膜 8 5 b の端部が位置する。30

**【 0 3 1 4 】**

また、窒化物絶縁膜 8 7 は、酸化物絶縁膜 8 3 a、8 3 b 及び酸化物絶縁膜 8 5 a、8 5 b の上面及び側面を覆うように形成され、窒化物絶縁膜 1 5 a と接する。

**【 0 3 1 5 】**

なお、トランジスタ 4 4 0 a において、酸化物絶縁膜 8 3 a 及び酸化物絶縁膜 8 5 a の端部は、チャネル長方向において、一対の電極 2 0 a、2 0 b 上に設けられず、窒化物絶縁膜 1 5 a 上に設けられてもよい。また、トランジスタ 4 4 0 b において、酸化物絶縁膜 8 3 b 及び酸化物絶縁膜 8 5 b の端部は、チャネル長方向において、一対の電極 2 0 c、2 0 d 上に設けられず、窒化物絶縁膜 1 5 a 上に設けられてもよい。40

**【 0 3 1 6 】**

また、図 1 2 ( C 1 ) に示すトランジスタ 4 4 0 a のチャネル幅方向の断面図において、ゲート電極 9 1 は、酸化物絶縁膜 8 3 a 及び酸化物絶縁膜 8 5 a の側面を介して、酸化物半導体膜 1 7 a の側面と対向する。

**【 0 3 1 7 】**

50

20

30

40

50

本実施の形態に示すトランジスタ440aは、チャネル長が0.5μm以上4.5μm以下、好ましくは1μmより大きく4μm以下、より好ましくは1μmより大きく3.5μm以下、より好ましくは1μmより大きく2.5μm以下である。また、トランジスタ440aは、チャネル幅方向において、ゲート電極13a及びゲート電極91の間に、絶縁膜15及び絶縁膜88aを介して酸化物半導体膜17aが設けられている。また、ゲート電極91は図12(A1)に示すように、上面から見て、絶縁膜88aを介して酸化物半導体膜17aの端部と重なる。

### 【0318】

また、トランジスタ440bのチャネル長は、トランジスタ440aよりも大きい。これによって、画素の選択トランジスタとして機能するトランジスタ440bのカットオフ電流の値を低減することが可能となる。10

### 【0319】

トランジスタ440aは、図12(C1)に示すように、酸化物半導体膜17aのチャネル幅方向の側面の一方の外側において、絶縁膜15及び窒化物絶縁膜87の開口部96が設けられている。そして該開口部96において、ゲート電極91はゲート電極13aと接続する。また、ゲート電極91は酸化物絶縁膜83a、85aの側面において、酸化物半導体膜17aのチャネル幅方向の側面と対向する。また、酸化物半導体膜17aのチャネル幅方向の側面の他方の外側においては、ゲート電極91はゲート電極13aと接続しない。また、ゲート電極91端部は、酸化物半導体膜17aの側面の外側に位置する。20

### 【0320】

なお、トランジスタ440aでは、図12(C1)に示すように、酸化物半導体膜17aのチャネル幅方向の側面の一方の外側のみにおいて、ゲート電極13a及びゲート電極91が接続するが、酸化物半導体膜17aのチャネル幅方向の側面の双方の外側において、ゲート電極13a及びゲート電極91が接続してもよい。

### 【0321】

本実施の形態に示すトランジスタ440a又はトランジスタ440bにおいて、酸化物半導体膜17a及び酸化物絶縁膜85a、又は酸化物半導体膜17b及び酸化物絶縁膜85bが、窒化物絶縁膜15a及び窒化物絶縁膜87で、周囲を囲まれている。窒化物絶縁膜15a及び窒化物絶縁膜87は、酸素の拡散係数が低く、酸素に対するバリア性を有するため、酸化物絶縁膜85a、85bに含まれる酸素の一部を効率よく酸化物半導体膜17a、17bに移動させることができ、酸化物半導体膜17a、17bの酸素欠損量を減らすことが可能である。また、窒化物絶縁膜15a及び窒化物絶縁膜87は、水、水素等の拡散係数が低く、水、水素等に対するバリア性を有するため、外部から酸化物半導体膜17a、17bへの水、水素等の拡散を防ぐことが可能である。これらの結果、トランジスタ440a及びトランジスタ440bは、信頼性の高いトランジスタとなる。30

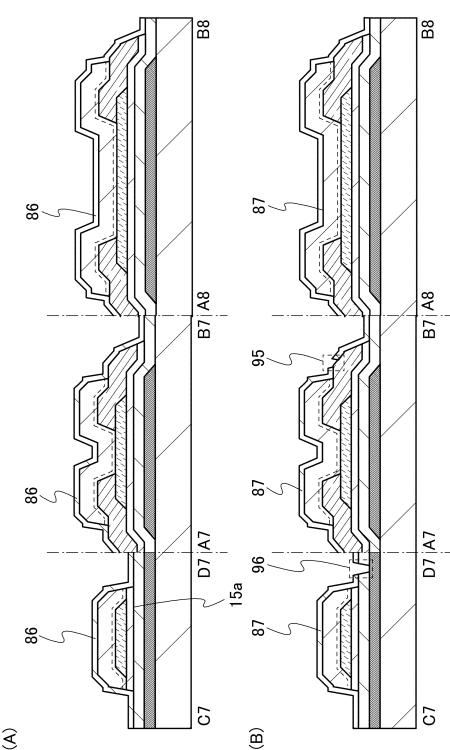

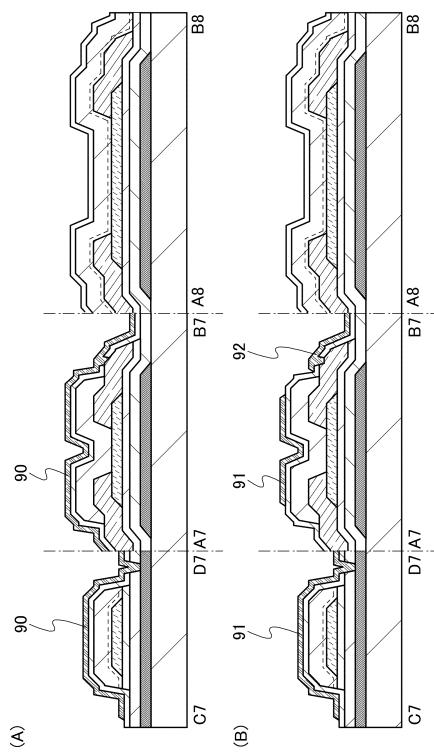

### 【0322】

次に、トランジスタ440a及びトランジスタ440bを含む本実施の形態の表示装置の作製工程について図13乃至図15を用いて説明する。

### 【0323】

なお、図13乃至図15において、A7-B7に示すチャネル長方向の断面図及びC7-D7に示すチャネル幅方向の断面図を用いて、トランジスタ440aの作製方法を説明し、A8-B8に示すチャネル長方向の断面図を用いてトランジスタ440bの作製方法を説明する。40

### 【0324】

なお、トランジスタ440bのチャネル幅方向の断面図は、開口部96においてゲート電極13aと接するゲート電極91を有さない点以外はトランジスタ440aと同様である。

### 【0325】

トランジスタ440a及びトランジスタ440bは、図3乃至図4(B)に示す工程と同様の工程を経て、基板11上に、ゲート電極13a、13b、窒化物絶縁膜15a、酸

10

20

30

40

50

化物絶縁膜 14 b、酸化物半導体膜 17 a、17 b、一対の電極 20 a、20 b 及び一対の電極 20 c、20 d を形成する。当該工程においては、第 1 のフォトマスク乃至第 3 のフォトマスクを用いたフォトリソグラフィ工程を行う。

#### 【0326】