(19) 日本国特許庁(JP)

## (12) 特許公報(B1)

(11) 特許番号

特許第4765127号

(P4765127)

(45) 発行日 平成23年9月7日(2011.9.7)

(24) 登録日 平成23年6月24日(2011.6.24)

(51) Int.Cl.

G O 1 R 31/26 (2006.01)

F 1

G O 1 R 31/26

G O 1 R 31/26Z

J

請求項の数 2 (全 21 頁)

(21) 出願番号 特願2010-292784 (P2010-292784)

(22) 出願日 平成22年12月28日 (2010.12.28)

審査請求日 平成23年1月5日 (2011.1.5)

(31) 優先権主張番号 特願2010-171857 (P2010-171857)

(32) 優先日 平成22年7月30日 (2010.7.30)

(33) 優先権主張国 日本国 (JP)

早期審査対象出願

(73) 特許権者 510208767

合同会社 P L E S O N

大分県大分市大字森町425番地の4

(74) 代理人 100101971

弁理士 大畠 敏朗

(72) 発明者 宮川 末晴

大分県大分市大字森町425番地の4

審査官 吉岡 一也

最終頁に続く

(54) 【発明の名称】 トレイユニットおよび半導体デバイスの検査装置

## (57) 【特許請求の範囲】

## 【請求項 1】

検査対象としての半導体デバイスを複数個にわたって搭載可能とされたトレイユニットであって、底部を形成する底板部材と、該底板部材の上に載置され、且つ水平方向に複数に分割され、それぞれが複数個の前記半導体デバイスを搭載保持する半導体デバイス搭載トレーとを有し、前記半導体デバイスが備える端子を上面側に向かた状態で各半導体デバイスの電気的特性を試験する半導体デバイスの検査装置に着脱自在に載置され、

前記各半導体デバイス搭載トレーは、別途設けられる位置決め手段による位置決めが行われるまでは、前記底板部材に対して水平方向の移動を所定範囲で許容した状態で保持され、

前記底板部材の上面には、半導体デバイスの直交する2辺の位置を規制する突起部、或いは半導体デバイスの移動を規制する角穴を持ち、前記半導体デバイストレーを所定の方向に押圧すると同時に半導体デバイスも同方向に移動され、前記底板部材に設けられる直交する2辺の突起に押し付けられることで前記半導体デバイスと前記半導体デバイス搭載トレーとの隙間を無くす手段を備え、

前記位置決め手段は、

前記半導体デバイス搭載トレーに設けられ前記所定の方向に沿った長円形状を有する位置合わせ用の孔と、

前記半導体デバイス搭載トレーと対向して設けられるコンタクト基板側に設けられ、前記長円形状を有する位置合わせ用の孔と相似の断面形状を有し、前記位置合わせ用の孔に

挿通される位置合わせ用のピンと、

前記位置合わせ用のピンを前記位置合わせ用の孔から抜いた際に、弾発力によって前記半導体デバイス搭載トレーを前記所定の方向と反対方向の元の位置に復帰させる押圧手段とを備える、

ことを特徴とするトレーユニット。

**【請求項 2】**請求項 1 に記載のトレーユニットを載置する載置部と、

前記トレーユニットに搭載された半導体デバイスの電極端子と電気的導通を行って前記半導体デバイスの電気的特性を試験するデバイス検査手段に接続されたテストボードと、前記テストボードと前記半導体デバイス搭載トレーとの間に設けられ、前記トレーユニットが備える半導体デバイス搭載トレーに搭載された各半導体デバイスの電極端子と前記テストボードが備える電極端子とを電気的に接続させる導電手段が設けられたコンタクト基板と、前記コンタクト基板を介して前記半導体デバイスと前記テストポートに接続された前記デバイス検査手段とを電気的に接続させる接続機構とを備え、

前記接続機構は、前記載置部の両側に設けられる昇降手段と、該昇降手段により前記載置部が所定位置まで相対移動された際に、前記半導体デバイスが備える端子と前記コンタクト基板、当該コンタクト基板と前記テストボードとがそれぞれ密着するように負圧吸引する減圧手段とから構成され、

前記減圧手段は、前記コンタクト基板を囲むコンタクト基板枠上の周囲に設けられる、或いは前記載置部の端部に設けられるシール部材と当該載置部が移動された際に前記コンタクト基板枠或いは前記載置部に当接されるシール部材と、前記コンタクト基板枠、前記コンタクト基板、前記載置部および前記シール部材とによって形成される減圧チャンバ内の雰囲気を吸引する真空ポンプと、から構成されることを特徴とする半導体デバイスの検査装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は半導体デバイスの各種特性試験を行うためのトレーユニットおよび半導体デバイスの検査装置に関するものである。

**【背景技術】****【0002】**

従来から、試験対象としての半導体デバイスに目的とする高温または低温の温度ストレスを与える半導体デバイスの検査装置が存在する。

**【0003】**

半導体デバイスの検査装置としては、例えば、半導体デバイスに対して高温または低温の温度ストレスを与える恒温槽と、この恒温槽で熱ストレスが与えられた状態にある半導体デバイスをテストヘッドに電気的に接触させて電気的特性を試験するテストチャンバと、テストチャンバで試験された半導体デバイスから、与えられた熱ストレスを除去する除熱槽を備えるものがある。

**【0004】**

このような半導体デバイスの検査装置では、複数個の半導体デバイスを同時に試験するために、半導体デバイスを搭載する複数個のソケットを取付けたソケットボードを用いている。

**【0005】**

このようなソケットボードを用いた半導体デバイスの検査装置に関する技術は種々提案されている。

**【0006】**

例えば、特開2000-304808号公報には、一度に検査を行なうことができる半導体装置の数を増加させると共に検査装置のコストを低減し、また、検査工程を安定して行なうことができるようとした半導体装置の検査装置が開示されている。

10

20

30

40

50

**【0007】**

この半導体装置の検査装置では、プリント基板の上には、ヒータ、多層配線基板及び異方導電性ゴムシートが順次設けられ、異方導電性ゴムシートの上には、半導体パッケージの多層配線基板に対する位置を規制する位置規制部材が配置され、位置規制部材の上方には押圧部材を有する押圧板が設けられ、該押圧板の周縁部には環状のシール部材が設けられ、押圧板、シール部材及び多層配線基板によって密封空間が形成され、密封空間を減圧すると、シール部材が変形して、半導体パッケージのバンプと多層配線基板の電極とが異方導電性ゴムシートを介して電気的に確実に接続するようになっている。

**【0008】**

また、特開2007-309787号公報には、ICトレーに搭載されている全ての半導体デバイスをテスト容易な専用トレーに一括に移し変える事が可能なテストトレー構造が開示されている。 10

**【先行技術文献】****【特許文献】****【0009】**

【特許文献1】特開2000-304808号公報

【特許文献2】特開2007-309787号公報

**【発明の概要】****【発明が解決しようとする課題】****【0010】**

ところで、近年の半導体デバイスはその高密度化及び回路の複雑化に伴って一つの半導体デバイスの試験に要する時間が長くなる傾向にあり、テストコストの低廉化のために半導体デバイス試験の一層の効率化が望まれている。 20

**【0011】**

また、半導体デバイスについて多品種の少量生産の傾向が強くなっているため、半導体デバイスの種類に応じて温度条件等の試験環境を頻繁に変更する必要性が高まっている。

**【0012】**

しかしながら、上記特開2000-304808号公報に係る従来技術では、配線基板(コンタクト基板)は固定されており、端子配列の異なる半導体デバイスに迅速に対応することができないという問題があった。 30

**【0013】**

また、半導体デバイスの構成毎に端子配列が異なるため、従来は、各半導体デバイスの構成毎に端子配列に適合させたソケットやソケットボードを用意する必要がありコストが嵩むという不都合があった。

**【0014】**

また、検査用ピンの数の増加に伴ってソケット自体が高価になり、検査装置のコストや検査コストが高騰化するという問題もある。特に、微細化、高集積化等によりテストに長時間を要するデバイスも増加しており、検査効率の低下および検査コストの上昇は大きな問題になる。

**【0015】**

また、近年の半導体デバイスのバーンインテストおよびファイナルテストは、ハンドラーと呼ばれる自動機によりトレーからバーンインボード上のソケットに移し替え、或いはテスターのキャリアボード上のキャリアソケットに移し替え、バーンイン槽或いはテストハンドラーのテストステージで検査を実施している。 40

**【0016】**

そのため、一度に検査を実可能な処理数量の限界および高価で多量に使用するソケットやボード等によるテストコストの増大が大きな課題になっている。

**【0017】**

また、ロジックの一部では組立工程ラインでテストを実施されているが、メモリを含めた多くのデバイスの検査は検査専用工程が設けられ、且つ専用のテストハンドラーと一緒に 50

のシステムが使用され、効率的な生産ラインが実現できていないという課題もある。

**【0018】**

一方、比較対象としての半導体デバイスを載せるトレー（ICトレー）では、半導体デバイスの搭載部を構成する樹脂部と、この樹脂部を載せる比較的熱伝導性の高い金属で形成されるベース板とから構成されていた。

**【0019】**

また、半導体デバイスとテストボードとの電気的接続を行うコンタクト基板とのアライメントは、例えばトレーの四隅に形成される位置決め用の孔を介して行われていた。

**【0020】**

しかしながら、樹脂と金属の線膨張率の違い、比較的薄い樹脂板で成形される場合に樹脂部に熱変形が生じ易いという問題があった。 10

**【0021】**

特に、基板及びトレーの長さが例えば300mm程度と比較的大きい場合、コンタクト基板の端子とトレー内の半導体デバイスの端子の位置合わせ（アライメント手段）が難しいという問題あり、且つトレーとトレー内の半導体デバイス間の隙間のばらつきの抑え手段が無く、高精度の位置合わせが難しいという問題もあった。

**【0022】**

そこで、本発明は、半導体デバイスをより効率的且つ低コストで試験することができ、トレーにおける位置合わせの精度を向上させることのできるトレイユニットおよび半導体デバイスの検査装置を提供することを目的とする。 20

**【課題を解決するための手段】**

**【0023】**

上記課題を解決するために、請求項1の発明に係るトレイユニットは、検査対象としての半導体デバイスを複数個にわたって搭載可能とされたトレイユニットであって、底部を形成する底板部材と、該底板部材の上に載置され、且つ水平方向に複数に分割され、それぞれが複数個の前記半導体デバイスを搭載保持する半導体デバイス搭載トレーとを有し、前記半導体デバイスが備える端子を上面側に向かた状態で各半導体デバイスの電気的特性を試験する半導体デバイスの検査装置に着脱自在に載置され、前記各半導体デバイス搭載トレーは、別途設けられる位置決め手段による位置決めが行われるまでは、前記底板部材に対して水平方向の移動を所定範囲で許容した状態で保持され、前記底板部材の上面には、半導体デバイスの直交する2辺の位置を規制する突起部、或いは半導体デバイスの移動を規制する角穴を持ち、前記半導体デバイストレーを所定の方向に押圧すると同時に半導体デバイスも同方向に移動され、前記底板部材に設けられる直交する2辺の突起に押し付けられることで前記半導体デバイスと前記半導体デバイス搭載トレーとの隙間を無くす手段を備え、前記位置決め手段は、前記半導体デバイス搭載トレーに設けられ前記所定の方向に沿った長円形状を有する位置合わせ用の孔と、前記半導体デバイス搭載トレーと対向して設けられるコンタクト基板側に設けられ、前記長円形状を有する位置合わせ用の孔と相似の断面形状を有し、前記位置合わせ用の孔に挿通される位置合わせ用のピンと、前記位置合わせ用のピンを前記位置合わせ用の孔から抜いた際に、弾发力によって前記半導体デバイス搭載トレーを前記所定の方向と反対方向の元の位置に復帰させる押圧手段とを備えることを特徴とする。 30

**【0026】**

請求項2の発明に係る半導体デバイスの検査装置は、請求項1に記載のトレイユニットを載置する載置部と、前記トレイユニットに搭載された半導体デバイスの電極端子と電気的導通を行って前記半導体デバイスの電気的特性を試験するデバイス検査手段に接続されたテストボードと、前記テストボードと前記半導体デバイス搭載トレーとの間に設けられ、前記トレイユニットが備える半導体デバイス搭載トレーに搭載された各半導体デバイスの電極端子と前記テストボードが備える電極端子とを電気的に接続させる導電手段が設けられたコンタクト基板と、前記コンタクト基板を介して前記半導体デバイスと前記テストポートに接続された前記デバイス検査手段とを電気的に接続させる接続機構とを備え、前 40

記接続機構は、前記載置部の両側に設けられる昇降手段と、該昇降手段により前記載置部が所定位置まで相対移動された際に、前記半導体デバイスが備える端子と前記コンタクト基板、当該コンタクト基板と前記テストボードとがそれぞれ密着するように負圧吸引する減圧手段とから構成され、前記減圧手段は、前記コンタクト基板を囲むコンタクト基板枠上の周囲に設けられる、或いは前記載置部の端部に設けられるシール部材と当該載置部が移動された際に前記コンタクト基板枠或いは前記載置部に当接されるシール部材と、前記コンタクト基板枠、前記コンタクト基板、前記載置部および前記シール部材とによって形成される減圧チャンバ内の雰囲気を吸引する真空ポンプと、から構成されることを特徴とする。

**【発明の効果】**

10

**【0041】**

本発明によれば以下の効果を奏することができる。

**【0042】**

すなわち、請求項1に記載の発明によれば、半導体デバイス搭載トレーを用いて搭載した各半導体デバイスの電気的特性を試験するので、試験効率を向上させることができ、試験コストを低廉化させるという優れた効果を奏することができる。

**【0043】**

また、トレイユニットは、底部を形成する底板部材と、該底板部材の上に載置され、且つ水平方向に複数に分割され、それぞれが半導体デバイスを複数個にわたって保持する半導体デバイス搭載トレーとから構成されるので、熱変形等を抑制して半導体デバイスとデバイス検査手段との電気的接続をより確実に行うことができる。

20

**【0044】**

また、請求項1に記載の発明によれば、各半導体デバイス搭載トレーは、位置決め手段による位置決めが行われるまでは、底板部材に対して水平方向の移動を所定範囲で許容した状態で保持される所謂フローティング構造となっているので、位置決め手段による位置決めの精度を向上させることができる。

**【0048】**

さらに、請求項1に記載の発明によれば、トレーと半導体デバイス間の隙間が無くなる状態で位置合わせが出来るため、より一層の位置合わせ精度を向上させて、電気的な接続をより確実に行うことができる。

30

**【0049】**

請求項1に記載の発明によれば、簡易な構成で半導体デバイスが備える端子とコンタクト基板と位置合わせ精度を向上させて、電気的な接続をより確実に行うことができる。

**【0050】**

請求項1に記載の発明によれば、簡易な構成で半導体デバイス搭載トレーを元の位置に復帰させることができる。

**【0054】**

請求項2に記載の発明によれば、端子配列が異なる半導体デバイスや構成の異なる半導体デバイスに対応することができ、試験効率を高めると共に試験コストを低廉化することができるという効果がある。

40

**【0056】**

また、請求項2に記載の発明によれば、半導体デバイスが備える端子とコンタクト基板との電気的な接続を確実に行うことができる。

**【図面の簡単な説明】****【0062】**

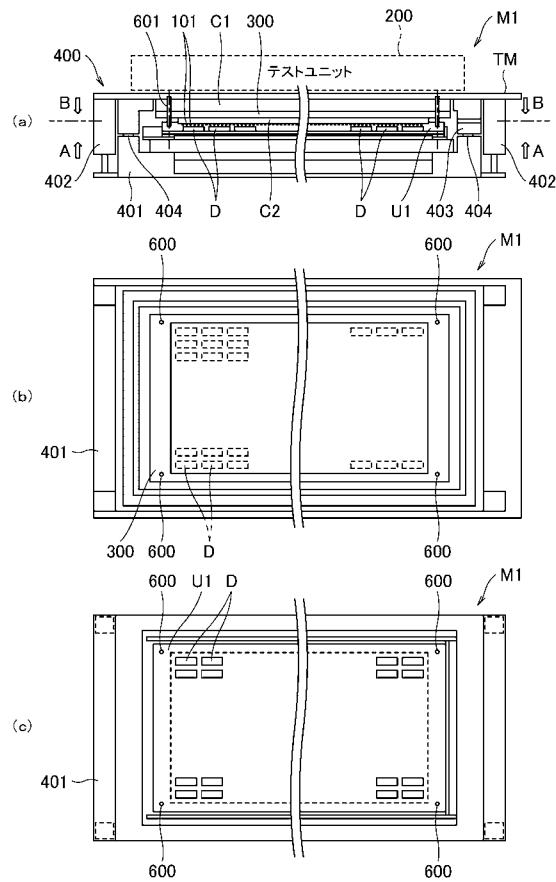

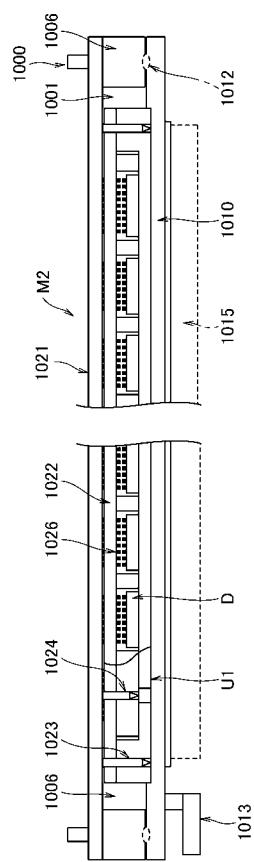

【図1】本発明の第1の実施の形態に係る半導体デバイスの検査装置の概略構成を示す側面図(a)、A-A線矢視(b)、B-B線矢視図(c)である。

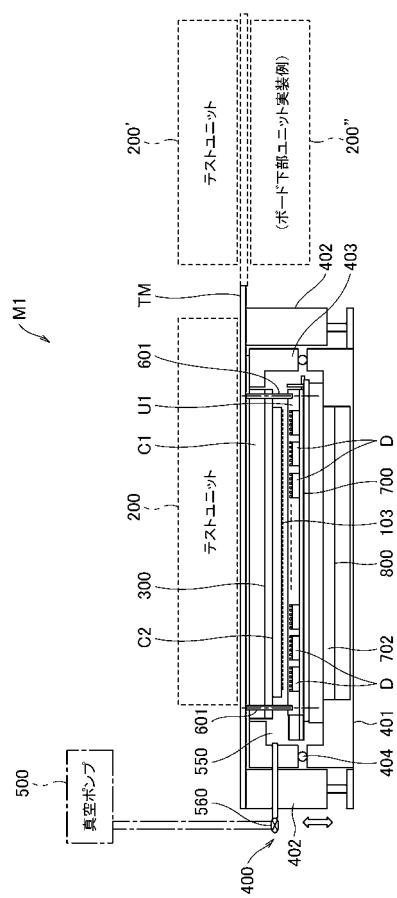

【図2】本発明の第1の実施の形態に係る半導体デバイスの検査装置の概略構成を示す説明図である。

【図3】本発明の第1の実施の形態に係る半導体デバイスの検査装置の一部拡大図である

50

。

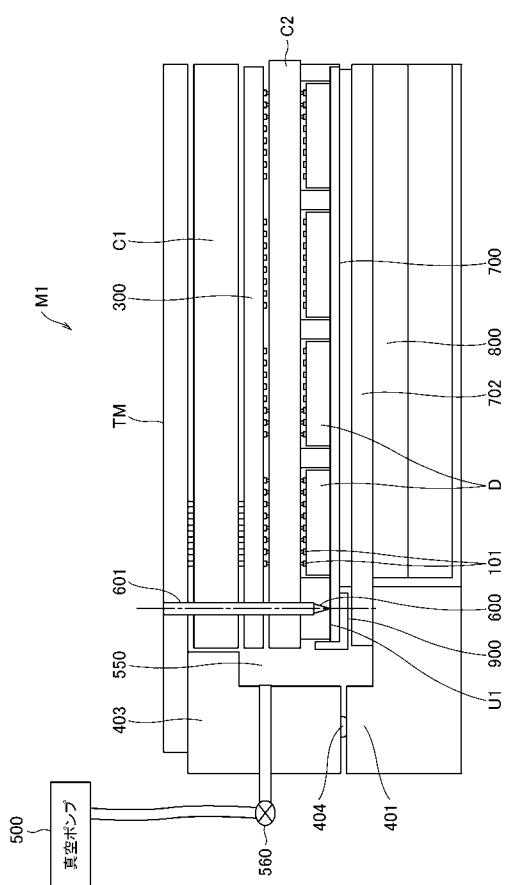

【図4】本発明の第2の実施の形態に係る半導体デバイスの検査装置の概略構成を示す分解斜視図である。

【図5】本発明の第2の実施の形態に係る半導体デバイスの検査装置における1層構成真空チャンバの構成例を示す概略構成図である。

【図6】本発明の第2の実施の形態に係る半導体デバイスの検査装置における2槽構成真空チャンバの構成例を示す概略構成図である。

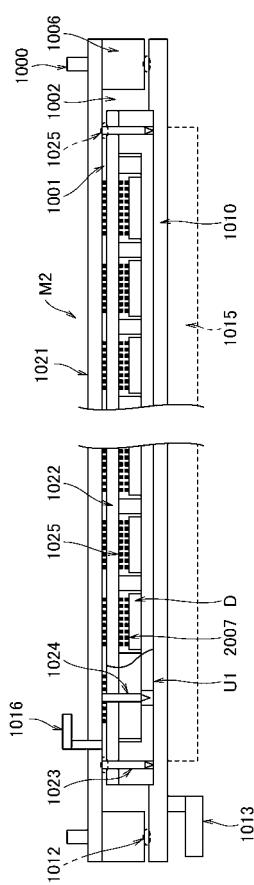

【図7】半導体デバイス搭載トレーのアライメント用ピンの構成図である。

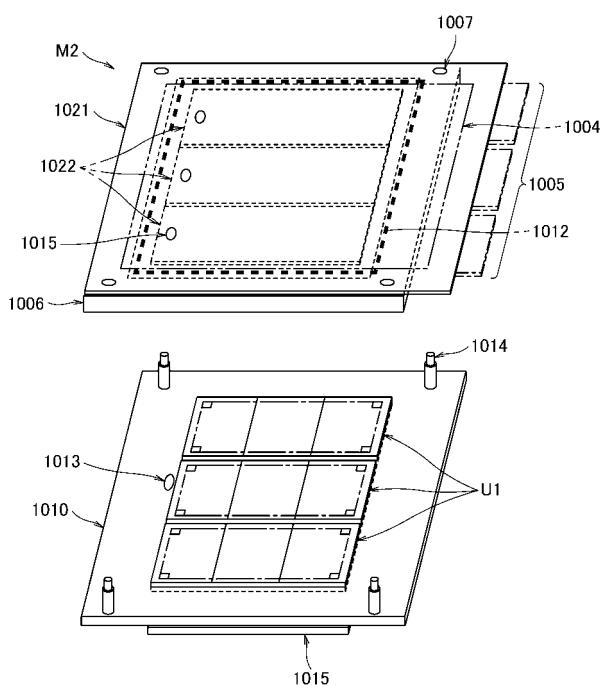

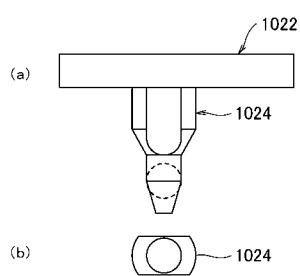

【図8】テストトレーの構成例を示す平面図(a)および側面図(b)である。

【図9】トレーのデバイス収納部の詳細を示す平面図(a)および側面図(b)である。 10

【図10】トレーとコンタクト基板がアライメントされた後の状態を示す説明図である。

【図11】デバイスがトレーに搭載された後(アライメント前)の状態を示す説明図である。

【図12】コンタクト基板とトレー全体のアライメント用穴の説明図(a)、コンタクト基板とトレー上部フレームのアライメント用穴の説明図(b)、トレー上部フレームのフローティング機構の説明図(c)である。

【図13】半導体デバイスの検査システムの構成例を示す説明図である。

【図14】半導体デバイスの検査システムの構成例を示す説明図である。

#### 【発明を実施するための形態】

##### 【0063】

以下、本発明を実施するための最良の形態を、図面を参照しつつさらに具体的に説明する。ここで、添付図面において同一の部材には同一の符号を付しており、また、重複した説明は省略されている。なお、ここでの説明は本発明が実施される最良の形態であることから、本発明は当該形態に限定されるものではない。

##### 【0064】

図1から図3等に示される第1の実施の形態に係る半導体デバイスの検査装置M1は、検査対象としての半導体デバイスDが搭載される図8、図9で示されるトレイユニット(半導体デバイス搭載トレーの一例)U1と、トレイユニットU1に搭載された半導体デバイスDの電極端子101と電気的導通を行って半導体デバイスDの電気的特性を試験するテスタユニット200(デバイス検査手段の一例)が搭載されたテスタマザー基板TM(テストボードの一例)と、テスタマザー基板TMに対向して設けられ、テスタマザー基板TMが備える端子の配列に対応したコンタクトピン102(導電手段の一例)が設けられた第1のコンタクト基板C1と、第1のコンタクト基板C1に対向して交換可能に設けられ、半導体デバイスDが備える端子101の配列とテスタマザー基板TMが備える端子の配列の相違に対応させて双方を電気的に接続させる電極および配線構造を有する端子配列の変換基板300と、変換基板300とトレイユニットU1との間に設けられ、半導体デバイスDが備える端子101の配列に対応したコンタクトピン103(導電手段の一例)が設けられ、当該コンタクトピン103が直接半導体デバイスDと導通する第2のコンタクト基板C2と、第1のコンタクト基板C1、変換基板300および第2のコンタクト基板C2を介して半導体デバイスDとテスタマザー基板TMに接続されたテスタユニット200とを電気的に接続させる接続機構400(接続手段の一例)とを備える。 30

##### 【0065】

半導体デバイス搭載トレー(フレーム2002)は、検査対象としての半導体デバイスDを複数個にわたって搭載し、トレイユニットU1に複数個のフレーム2002を搭載するようになっている。

##### 【0066】

なお、半導体デバイス搭載トレーU1は、テスタユニット200による検査結果に関する情報(例えば、トレイユニットU1を識別するIDデータ等を含む)を格納するメモリ、RFID(ICCタグ)或いはバーコードなど(図示せず)を備えるようにしてもよい。

##### 【0067】

10

20

30

40

50

これにより、例えばトレーのID(識別番号)に基づいて、不良品を良品に入れ替えたり、不良品を分類するなどの処理を行うことができ、利便性を向上させることができる。

**【0068】**

また、コントラクトピンに代えて、メンブレンシート、異方性導電シート等で前記導電手段を構成するようにしてもよい。

**【0069】**

テスタユニット200は、図2に示すようにテスタマザー基板TMの直上に設けてもよいし、テスタマザー基板TMの延長部の表面側200'または裏面側200''に設けるようにしてもよい。

**【0070】**

また、テスタユニット200は、同軸ケーブル等の接続で外部に設けるようにしてもよい。

10

**【0071】**

また、本実施の形態において、半導体デバイスDは、当該半導体デバイスDが備える端子101側が上面となるようにトレイユニットU1に保持されている。

**【0072】**

また、第1のコントラクト基板C1、変換基板300および第2のコントラクト基板C2を介して半導体デバイスDとテスタマザー基板TMに接続されたテスタユニット200とを電気的に接続させる接続機構400を備えている。

**【0073】**

本実施の形態において、接続機構400は、トレイユニットU1を載置する載置部401と、当該載置部401を第2のコントラクト基板C2に対して昇降させるアクチュエータ(例えば、エアシリンダ等で構成される昇降手段402)とを備える。

20

**【0074】**

さらに、本実施の形態において接続機構400は、載置部401の両側に設けられる昇降手段402と、この昇降手段402により載置部401が所定位置まで上昇された際に、半導体デバイスDが備える端子101とコントラクト基板C2とが密着するように負圧吸引する真空ポンプ500(減圧手段の一例)とから構成されている。

**【0075】**

また、減圧手段は、第2のコントラクト基板C2を囲むコントラクト基板枠403に設けられ、或いは載置部401の端部に設けられて当該載置部401が上昇された際にコントラクト基板枠403或いは載置部401に当接されるシール部材404と、コントラクト基板枠403、第1のコントラクト基板C1、載置部401およびシール部材404とによって減圧チャンバ550が形成され、この減圧チャンバ550内の雰囲気を真空ポンプ500で吸引するようになっている。

30

**【0076】**

なお、真空ポンプ500は、減圧量を調整する減圧弁560を備えている。

**【0077】**

即ち、コントラクト基板枠403を昇降手段402で加圧することにより、半導体デバイスDの表面およびトレイユニットU1の上面を押し下げ、シール部材404に予圧を加えた後、真空ポンプ500に接続された減圧弁560をオンすることにより、減圧チャンバ550が減圧され、半導体デバイスDとトレイユニットU1がさらに熱板701により押圧され、第2のコントラクト基板C2、変換基板300及び第2のコントラクト基板C2がテスタマザー基板TMに加圧され、トレイユニットU1に収納された半導体デバイスDとテスタマザー基板TM間の全コントラクトが所定の力で一括接続される。

40

**【0078】**

このように、本実施の形態に係る半導体デバイスの検査装置M1によれば、端子配列が異なる半導体デバイスDや構成の異なる半導体デバイスDに機動的に対応することができ、試験効率を高めると共に試験コストを低廉化することができる。

**【0079】**

50

なお、減圧手段は、上記構成に限定されるものではなく、第1のコンタクト基板C1、変換基板300および第2のコンタクト基板C2を介して半導体デバイスDとテスタマザーベース板TMとを密着させて電気的に接続させることのできる構造であれば採用できる。

#### 【0080】

また、トレーのベース板2001のコーナーには、位置決め用の孔600が複数箇所(図1から図3に示す例では4隅)に形成され、テスタマザーベース板TMから下方に延伸されるアライメントピン601が係合されて位置合わせを行うようになっている(図1(a)、図3、図4等参照)。

#### 【0081】

また、半導体デバイスの検査装置M1は、各トレイユニットU1に搭載された半導体デバイスDの周囲温度を所定の試験環境温度に調整する温度調整手段をさらに備えている。 10

#### 【0082】

本実施の形態において、温度調整手段は、例えば、トレーのベース板2001の下方に配設され、伝熱プレート700、熱板702を介してペルチェモジュールやヒータ等の熱源800等で構成されている。

#### 【0083】

なお、特には限定されないが、伝熱プレート700は厚さ数ミリメートル程度のアルミニウム、銅、ステンレス、黄銅板等で形成される。

#### 【0084】

また、熱源800は、チラーから供給される冷媒又は熱媒、或いはLN2などとしてもよいし、あるいはペルチェモジュール、ヒータ、冷媒(LN2含む)及び熱媒による冷却と加熱を組み合わせてもよい。 20

#### 【0085】

このような構成の温度調整手段により、従来のように恒温槽等にトレイユニットU1を収容することなく、簡便に試験環境温度を調整することができ、利便性が向上され試験の高速化が図られると共に、試験コストを低廉化することができる。

#### 【0086】

また、熱源800としてペルチェモジュールを実装することにより、高温テスト及び低温テスト、或いは高温と低温との間のサイクルテストを容易に実現することができる。 30

#### 【0087】

なお、符号900は、トレイユニットU1を下方から支持する受部である。

#### 【0088】

次に、本実施の形態に係る半導体デバイスの検査装置M1の動作について説明する。

#### 【0089】

まず、半導体デバイスの検査装置M1において、検査対象としての半導体デバイスDの特性(端子配列、構成等)に対応するように、第2のコンタクト基板C2および変換基板300を交換する。

#### 【0090】

次いで、検査対象としての半導体デバイスDを搭載したトレイユニットU1を載置部401にセットする。 40

#### 【0091】

続いて、昇降手段402が作動され、トレイユニットU1が載置部401ごと上昇される。

#### 【0092】

そして、所定の高さに達すると、真空ポンプ500が駆動され、上述の減圧チャンバ550内の雰囲気が吸引される。

#### 【0093】

これにより、半導体デバイスDが備える端子101と、第1コンタクト基板C1、第2のコンタクト基板C2、変換基板300、テスタマザーベース板TMとが密着され、電気的に接続される。 50

**【0094】**

次いで、温度調整手段により半導体デバイスDが所定の温度まで加熱または冷却された後、テスタマザー基板TMおよびテスタユニット200の動作によって各半導体デバイスDの検査処理が実行されることとなる。

**【0095】**

また、他の構成の半導体デバイスを検査する場合には、コンタクト基板C2および変換基板300を対応するものに交換した後、上述の手順で検査を行う。

**【0096】**

このように、本実施の形態に係る半導体デバイスの検査装置M1によれば、端子配列が異なる半導体デバイスDや構成の異なる半導体デバイスDに機動的に対応することができ、試験効率を高めると共に試験コストを低廉化することが可能となる。10

**【0097】**

なお、本実施の形態では、半導体デバイスDの端子を上向きにした場合を示したが、半導体デバイスDの端子を下向きにした場合にも本発明を適用することが可能である。

**【0098】**

次に、図8から図12を参照して、第3の実施の形態に係る半導体デバイスの検査装置M3について説明する。

**【0099】**

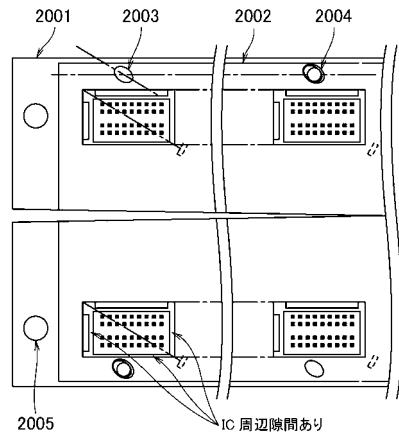

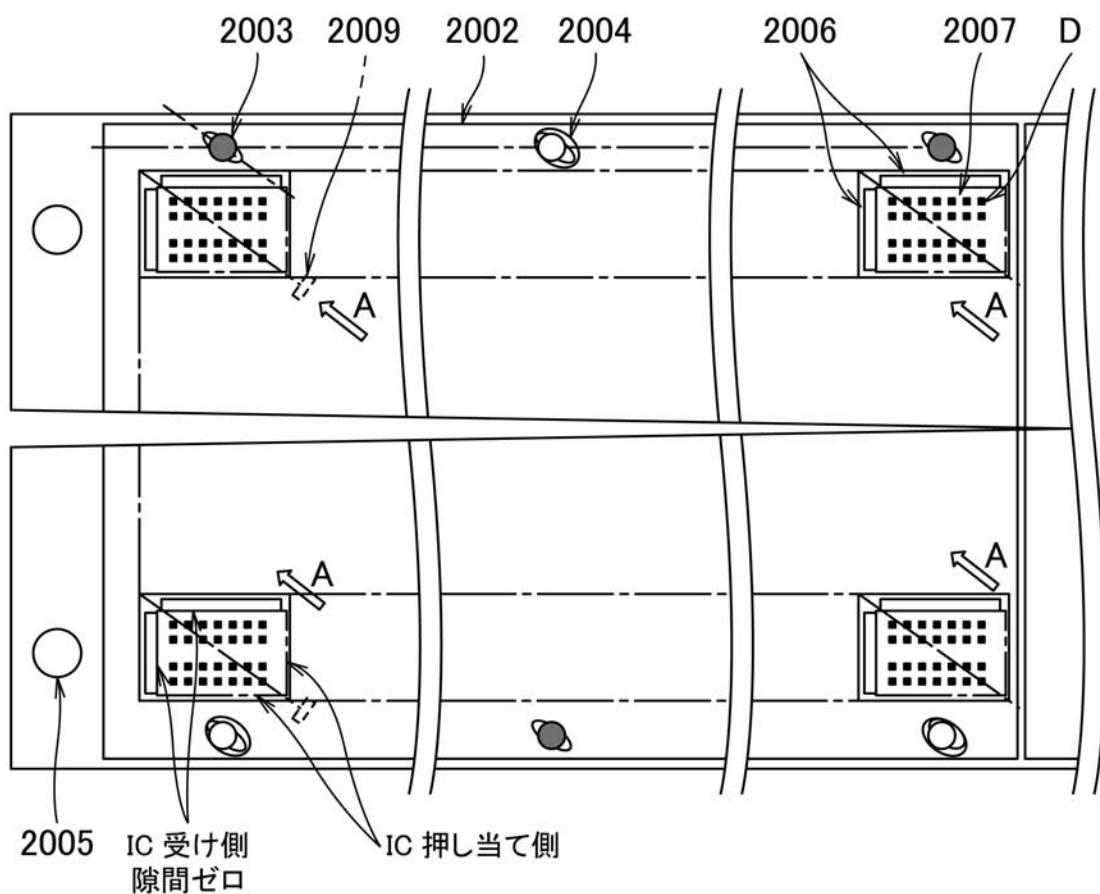

半導体デバイスの検査装置M3では、検査対象としての半導体デバイスDを複数個にわたって並列状態で搭載する1または2以上のトレーユニットU1を用い、各トレーユニットU1に、半導体デバイスDが備える端子を上面側に向けて搭載した状態で各半導体デバイスDの電気的特性を一括して試験するテストボード（デバイス検査手段の一例：図8には現れない）を備え、トレーユニットU1は、アルミニウム等の金属で形成される底板部材（ベース板）2001と、このベース板2001の上に載置され、且つ水平方向に複数に分割され、それぞれが半導体デバイスDを複数個にわたって保持する半導体デバイス搭載トレー（例えば樹脂あるいは金属で形成されるフレーム）2002a、2002b、2002cとから構成される。20

**【0100】**

また、各フレーム2002a、2002b、2002cは、別途設けられる位置決め装置（図5～図12参照）による位置決めが行われるまでは、ベース板2001に対して水平方向の移動（例えば、矢印A方向への移動）を所定範囲（例えば、図9の（c）で示すアライメント穴2003の隅部に接触するまでの範囲）で許容した状態で保持される所謂フローティング構造とされている。30

**【0101】**

また、ベース板2001の構成材料は、アルミニウムに限らないが、熱伝導率が100W/（m・K）以上の材料が好ましい。

**【0102】**

なお、本実施の形態では、フレームを3つに分割しているが、これに限定されず、2以上であれば幾つに分割してもよい。

**【0103】**

各フレーム2002a、2002b、2002cの縁部には、図示しないコンタクト基板との間で各フレーム2002a、2002b、2002cの位置合わせを行うためのアライメント孔2003が穿設されている。40

**【0104】**

また、ベース板2001の四隅には、トレーユニットU1全体の位置合わせを行うためのアライメント孔2005が穿設されている。

**【0105】**

アライメント孔2003およびアライメント孔2005には、装置内において対応するアライメント用のピン（図7参照）が係合して、それぞれの部材の位置合わせを行うようになっている。50

**【0106】**

これにより、アライメント用のピンにより位置補正を行うことができる。

**【0107】**

また、トレーユニットU1における熱変形の抑制を図ることもできる。

**【0108】**

また、本実施の形態では、図5～図9に示すように、一つのトレーユニットU1にフレーム2002が横に2個(2002a、2002b、2002c)設けられるようになっている。

**【0109】**

また、本実施の形態では、各フレーム2002に、複数個の半導体デバイスD(例えば10、DDR3、BGAパッケージ)が、端子2500を上側に向けた状態で搭載されるようになっている。

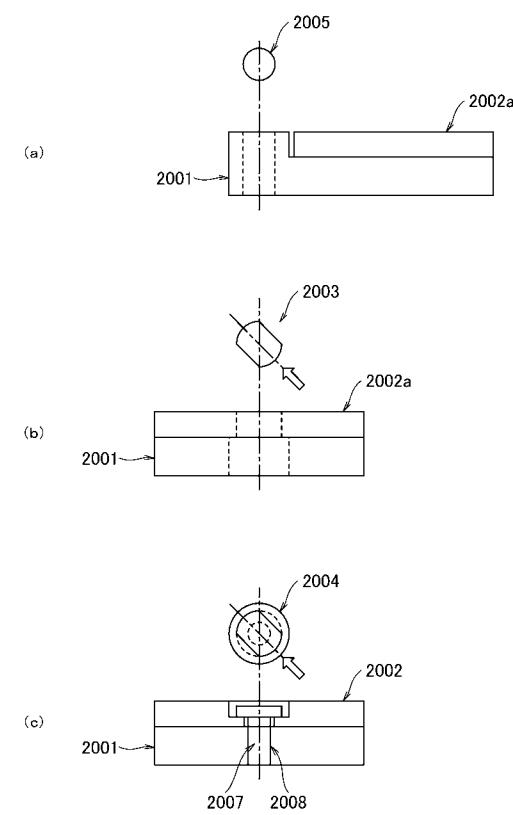

**【0110】**

各フレーム2002の上下周辺部には、3つのアライメント用の孔2003と、3つのフローティング用の孔2004が設けられている。

**【0111】**

アライメント用の孔2003およびフローティング用の孔2004は、図12の(a)、(b)に示すように矢印A方向に沿って形成される長円形状とされている。

**【0112】**

図5～図7に示すように、コンタクト基板1022には、アライメント用の孔2003に挿通されるアライメント用のピン1024が設けられている。20

**【0113】**

アライメント用のピン1024の形状は、特には限定されないが、例えば図7に示すように、アライメント用の孔2003の長円形状と相似の断面形状を有するようにされる。

**【0114】**

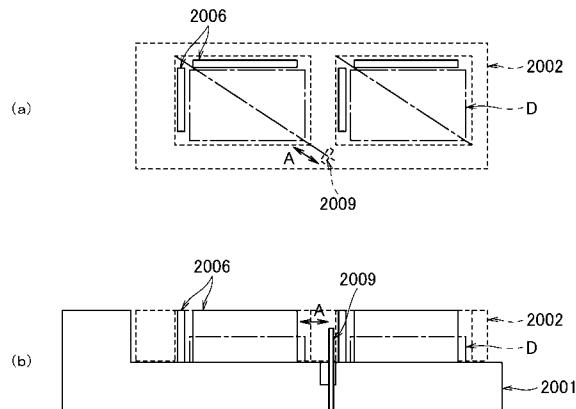

図9の(a)、(b)に示すようにベース板2001の上部のデバイスDが収納される所定の位置にはデバイスDをガイドするための直交する2辺の突起2006が設けられている。

**【0115】**

そして、アライメント用の孔2003にアライメント用のピン1024が挿通されると、アライメント用のピン1024とアライメント用の孔2003との係合により、各フレーム2002が、矢印A方向に移動(図8～図12参照)すると同時にフレーム2002に搭載されている半導体デバイスも同方向に移動され、ベース板2001に設けられた直交する2辺の突起2006に押しつけられることでデバイスDとフレーム2002間の隙間が無くなり(図10～図12参照)精度の高い位置合わせが行われる。30

**【0116】**

なお、本実施の形態においては、図8および図9に示すように、ベース板2001の所定の位置に、板バネ2009が設けられ、アライメント用のピン1024をアライメント用の孔2003から抜いた際に、板バネ2009の弾発力により各フレーム2002が矢印Aと逆方向に戻って、デバイスDも同時に元の位置に復帰させるようになっている。40

**【0117】**

一方、ベース板2001には固定孔2008が形成され、フローティングピン2007がフローティング用の孔2004から挿通され、先端部が固定孔2008に圧入されて固定されるようになっている(図12の(c)を参照)。

**【0118】**

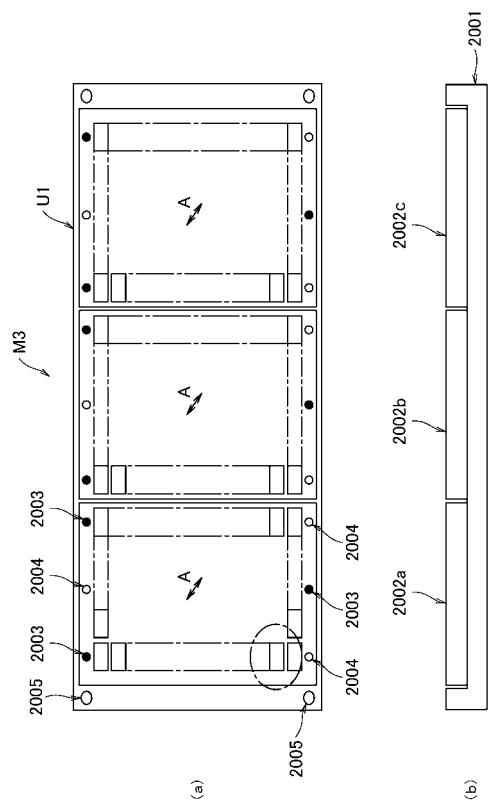

次に、図4～図12を参照して、第2の実施の形態に係る半導体デバイスの検査装置M2について説明する。

**【0119】**

半導体デバイスの検査装置M2は、トレーユニットU1と、トレーユニットU1に搭載された半導体デバイスDの電極端子2007(図10～図12参照)と電気的導通を行つ50

て半導体デバイスDの電気的特性を試験するテストユニット（デバイス検査手段の一例：図示せず）に接続されたテストボード1021と、テストボード1021と下部真空チャンバを構成するフレーム1010との間に設けられ、トレーユニットU1が備える半導体デバイス搭載トレー2002に搭載された各半導体デバイスDの電極端子2007とテストボード1021が備える電極端子とを電気的に接続させる配線構造（導電手段）が設けられたコンタクト基板1022と、コンタクト基板1022を介して半導体デバイスDとテストポート1021に接続されたテストユニットとを電気的に接続させる接続機構（図5～図7参照）とを備えている。

#### 【0120】

また、テストボード1021は、半導体デバイスDの種類または半導体デバイスDが備える電極端子2007の配列に応じて、交換可能とされている。 10

#### 【0121】

次に、本実施の形態に係る半導体デバイスの検査装置M2におけるアライメント動作の概要について説明する。

#### 【0122】

まず、トレーユニットU1を下部真空チャンバベース板1010に設置し、次いで、コンタクト基板1022のアライメントピン1023とトレーのベース板2001のアライメント孔2005によりアライメントを行う。これにより、トレーユニットU1の位置が決められる。

#### 【0123】

次に、分割されたフレーム2002上のアライメント孔2003とコンタクト基板1022に設けられたコンタクトピン1024によりアライメントを行う。 20

#### 【0124】

そして、最後にコンタクト基板1022の端子1026の先端と半導体デバイスDの端子2007との間のアライメントを行う。

#### 【0125】

これにより、フレーム2002の熱変形等を抑制して半導体デバイスDとテストボードとの電気的接続をより確実に行うことができる。

#### 【0126】

また、アライメント用のピン1024とアライメント用の孔2003との係合によりフレーム2002を移動させる機構に代えて、フレーム2002の外部にフレーム2002自体を矢印A方向に押圧する機構を設けるようにしてもよい。 30

#### 【0127】

次に、図4～図6を参照して、第2の実施の形態に係る半導体デバイスの検査装置M2について説明する。

#### 【0128】

図4～図6に示すように、上部構成は、テストボード1021の下側には分割された3つのコンタクト基板1022が配置されている。

#### 【0129】

テストボード1021の四隅には、後述するガイドピン1014が挿通されるガイド孔1023が設けられている。 40

#### 【0130】

符号1004は、各種回路部材や接続コネクタの実装領域を示す。

#### 【0131】

また、テストボード1021の一側方にはエッジコネクタを設けるようにしてもよい。

#### 【0132】

テストボード1021の下方には、コンタクト基板枠（上部真空チャンバ枠）1006が設けられている。

#### 【0133】

また、図4～図6に示すように、コンタクト基板枠1006の周囲には、Oリング等の 50

シール部材 1012 が設けられている。

**【0134】**

一方、下部構成は、金属製（例えばアルミ製）の載置部（下部真空チャンバ）1010 の上に、前出の図8で示したトレーユニットU1が載置されている。

**【0135】**

ベース板1010の四隅には、テストボード1021側のガイド孔1007に挿通されるガイドピン1014が立設されている。

**【0136】**

また、下部の載置部ベース板1010の一部には、真空バルブの取付口1013が形成されている。

10

**【0137】**

また、載置部ベース板の下方には、ヒートシンク或いは熱源等で構成される温調部1015が設けられている。

**【0138】**

なお、トレーユニットU1の詳細については、第3の実施の形態に係る半導体デバイスの検査装置M3で説明したので省略する。

**【0139】**

また、図5～図9に示すように、接続機構として、半導体デバイスDが備える端子2007とコンタクト基板1022と、コンタクト基板1022とテストボード1021とがそれぞれ密着するように負圧吸引する減圧機構（減圧手段）1000を備えている。

20

**【0140】**

本実施の形態において、減圧機構1000は、テストボード1021、コンタクト基板1022およびシール部材1025によって形成される第1の減圧チャンバ1001と、第1の減圧チャンバ1002内の雰囲気を吸引する真空バルブ1016に接続される第1の真空ポンプ（図示せず）と、コンタクト基板1022を囲むコンタクト基板枠1006と、載置部1010の端部に設けられて当該載置部1010が移動された際にコンタクト基板枠1006との間に介在されるシール部材1012とによって形成される第2の減圧チャンバ1002と、該第2の減圧チャンバ1002内の雰囲気を吸引する真空バルブ1013に接続される第2の真空ポンプ（図示せず）とから構成される。

**【0141】**

30

そして、特には限定されないが、例えば、まず最初に第1の真空ポンプにより第1の減圧チャンバ1001を減圧し、次いで第2の真空ポンプにより第2の減圧チャンバ1002を減圧することにより、半導体デバイスDとテストボード1021との確実な電気的接続を行うことができる。

**【0142】**

また、第1の真空ポンプ、第2の真空ポンプに代えて、一つの真空ポンプを設け、バルブの切り換えによって、第1の減圧チャンバ1001と第2の減圧チャンバ1002内の雰囲気を吸引するようにしてもよい。

**【0143】**

また、例えば、テストトレーユニットU1に底板を設け、この底板を熱伝導率が100W/(m·K)以上の材料で構成するようにしてもよい。

40

**【0144】**

より具体的には、底板を銅（熱伝導率385W/(m·K)、比重8.9g/cm<sup>3</sup>）またはアルミニウム（熱伝導率200W/(m·K)、比重2.7g/cm<sup>3</sup>）或いは黄銅（熱伝導率105W/(m·K)、比重8.7g/cm<sup>3</sup>）で構成するとよい。

**【0145】**

これにより、トレーユニットU1の底板の熱伝導率を高めて半導体デバイスの検査効率を向上させることができる。

**【0146】**

また、トレーのベース板2001の複数箇所に図8～図12で示すような板バネ200

50

9を設けて、フレーム2002を矢印A方向と反対方向に付勢して、位置を復帰させるようにしてよい。

**【0147】**

また、図9の(a)、(b)では1例として、半導体デバイスDを押し付けたい側の2辺に突起を設けているがベース板2001にデバイスの位置を規制する角穴(図示は省略)を設けるなど他の手段でも良い。

**【0148】**

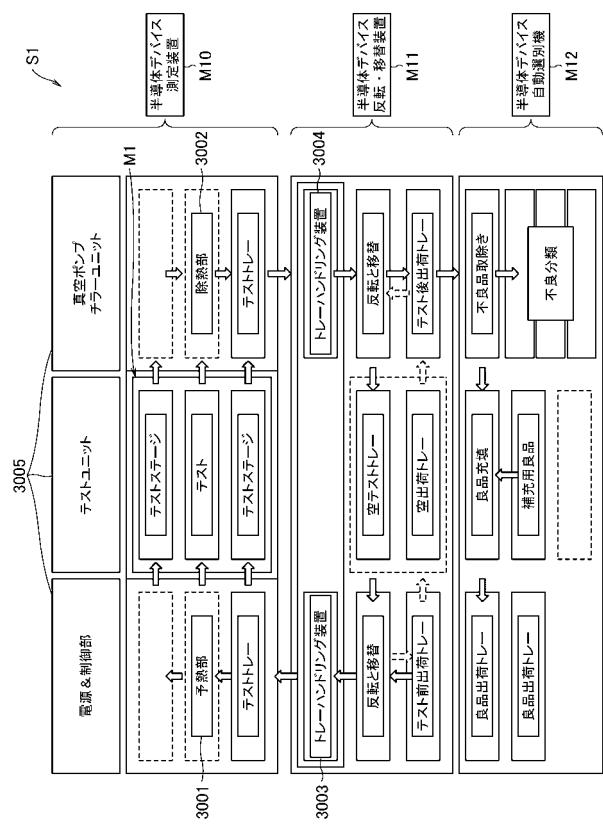

次に、図13、図14を参照して、半導体デバイスの検査システムS1について簡単に説明する。

**【0149】**

図13に示すように、半導体デバイスの検査システムS1は、本発明に係る半導体デバイスの検査装置M1を適用してトレーユニットU1ごと一括して半導体デバイスDの電気的特性等の測定を行う半導体デバイス測定装置M10と、半導体デバイスDの反転および移し替えを行う半導体デバイストレー移替装置M11と、半導体デバイスDの良否を選別する半導体デバイス自動選別機M12とから構成されている。

**【0150】**

半導体デバイス測定装置M10は、テストユニット200を備えている。

**【0151】**

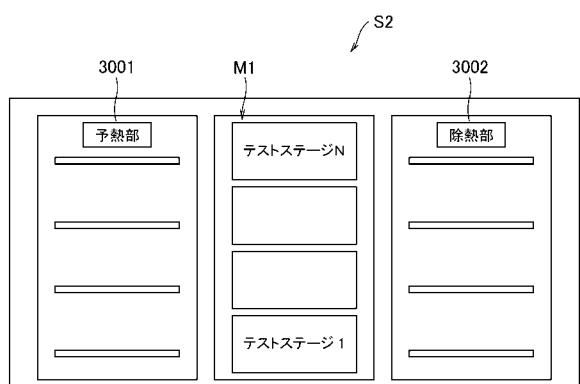

そして、半導体デバイス測定装置M10では、半導体デバイストレー移替装置M11から移送されたトレーユニットU1を予熱部3001で予熱した後、図1～図3等に示す構成の半導体デバイスの検査装置M1によってトレーユニットU1に搭載された半導体デバイスDについて一括して電気的特性の試験が行われる。

**【0152】**

次いで、トレーユニットU1は除熱部3002に移送され、除熱された後に、半導体デバイストレー移替装置M11へ移送される。

**【0153】**

半導体デバイストレー移替装置M11において、テスト前出荷トレー 半導体デバイスDのトレー移替 トレーハンドリング装置3003の過程で半導体デバイス測定装置M10にトレーユニットU1を移送し、導体デバイス測定装置M10にテストトレーU1から戻って来たトレーユニットU1について、トレーハンドリング装置3004

半導体デバイスDの反転と移替 テスト後出荷トレーの過程で半導体デバイス自動選別機M12に移送したり、あるいはトレーハンドリング装置3004 半導体デバイスDのトレー移替 空テストトレーの流れで移送する。

**【0154】**

また、半導体デバイス自動選別機M12では、テスト後出荷トレーを介して移送されて来た半導体デバイスDについて、検査結果に基づいて、不良品の取除き 良品充填 良品出荷トレーの流れで半導体デバイスDをテスト結果に基づき選別する。

**【0155】**

なお、取り除いた不良品については、トレーユニットU1に、識別情報等を格納するメモリ、RFID(I Cタグ)或いはバーコードを備えるようにした場合に、それらの情報に基づいて不良品を分類するようにしてよい。

**【0156】**

また、半導体デバイスの検査装置M1を適用したテストステージを1～N(Nは整数)段にわたって積み重ねた多段構造を有する半導体デバイスの検査システムS2として構成してもよい。

**【0157】**

以上本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本明細書で開示された実施の形態はすべての点で例示であつて開示された技術に限定されるものではないと考えるべきである。即ち、本発明の技術的な範囲は、上記の実施の形態における説明に基づいて制限的に解釈されるものではなく、あくまでも特許請求の範囲の記載に従

つて解釈すべきであり、特許請求の範囲の記載技術と均等な技術および特許請求の範囲内でのすべての変更が含まれる。

【産業上の利用可能性】

【0158】

本発明による半導体デバイスの検査装置および当該検査装置を用いた半導体デバイスの検査システムは、特性テストが必要な様々な半導体デバイスの検査装置に適用できるものであり、SDRAM、スタティックRAM、フラッシュメモリ、ロジックデバイス、ロジック・アナログ混載デバイスなど、様々な半導体デバイスをテスト対象として適用することができる。

【符号の説明】

10

【0159】

M1～M3 半導体デバイス検査装置

C1 第1のコンタクト基板

C2 第2のコンタクト基板

101 電極端子

102 コンタクトピン

103 コンタクトピン

200 テスタユニット

300 変換基板

301 予熱部

20

400 接続機構

401 載置部

402 昇降手段

403 コンタクト基板枠

404 シール部材

500 真空ポンプ

550 減圧チャンバ

560 減圧弁

600 位置決め用の孔

601 アライメントピン

30

700 伝熱プレート

701 热板

702 热板

800 热源

U1 トレーユニット

1000 減圧機構

1001 第1の減圧チャンバ

1002 第2の減圧チャンバ

1004 回路部品及び同軸コネクタ実装域

1005 エッジコネクタ

40

1006 コンタクト基板枠

1007 ガイド孔

1010 ベース板(下部真空チャンバ)

1012 シール部材

1013 取付口

1014 ガイドピン

1015 温調部

1016 取付口

1021 テストボード(テスタマザー基板)

1022 コンタクト基板

50

|                                                                                                                                                                                                                |                              |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----|

| 1 0 2 3                                                                                                                                                                                                        | アライメントピン（コンタクト基板とトレーユニット間）   |    |

| 1 0 2 4                                                                                                                                                                                                        | アライメントピン（コンタクト基板と半導体搭載トレー間）  |    |

| 1 0 2 5                                                                                                                                                                                                        | シール部材                        |    |

| 1 0 2 6                                                                                                                                                                                                        | コンタクト基板端子                    |    |

| 2 0 0 1                                                                                                                                                                                                        | トレーベース板                      |    |

| 2 0 0 2                                                                                                                                                                                                        | フレーム（分割された半導体デバイス搭載トレー）      |    |

| 2 0 0 3                                                                                                                                                                                                        | アライメント用の孔（コンタクト基板と半導体搭載トレー間） |    |

| 2 0 0 4                                                                                                                                                                                                        | フローティング用の孔                   |    |

| 2 0 0 5                                                                                                                                                                                                        | アライメント用の孔（コンタクト基板とトレーユニット間）  |    |

| 2 0 0 6                                                                                                                                                                                                        | 位置規制用突起                      | 10 |

| 2 0 0 7                                                                                                                                                                                                        | 半導体デバイスの端子                   |    |

| 2 0 0 8                                                                                                                                                                                                        | フローティングピン用孔                  |    |

| 2 0 0 9                                                                                                                                                                                                        | 板バネ                          |    |

| 3 0 0 1                                                                                                                                                                                                        | 予熱部                          |    |

| 3 0 0 2                                                                                                                                                                                                        | 除熱部                          |    |

| 3 0 0 3                                                                                                                                                                                                        | トレーハンドリング装置                  |    |

| 3 0 0 4                                                                                                                                                                                                        | トレーハンドリング装置                  |    |

| 3 0 0 5                                                                                                                                                                                                        | テスター用電源装置等                   |    |

| D                                                                                                                                                                                                              | 半導体デバイス                      |    |

| M 1 0                                                                                                                                                                                                          | 半導体デバイス測定装置                  | 20 |

| M 1 1                                                                                                                                                                                                          | 半導体デバイストレー移替装置               |    |

| M 1 2                                                                                                                                                                                                          | 半導体デバイス自動選別機                 |    |

| S 1 , S 2                                                                                                                                                                                                      | 検査システム                       |    |

| 5 0 0 2                                                                                                                                                                                                        | 第1の真空バルブ                     |    |

| 5 0 0 3                                                                                                                                                                                                        | 第2の真空バルブ                     |    |

| 【要約】                                                                                                                                                                                                           |                              |    |

| 【課題】位置合わせの精度を向上させることのできるトレーユニットを提供する。                                                                                                                                                                          |                              |    |

| 【解決手段】検査対象としての半導体デバイスを複数個にわたって搭載可能とされたトレーユニットであって、底部を形成する底板部材と、該底板部材の上に載置され、且つ水平方向に複数に分割され、それぞれが複数個の前記半導体デバイスを搭載保持する半導体デバイス搭載トレーとを有し、前記半導体デバイスが備える端子を上面側に向けた状態で各半導体デバイスの電気的特性を一括して試験する半導体デバイスの検査装置に着脱自在に載置される。 |                              | 30 |

| 【選択図】図 8                                                                                                                                                                                                       |                              |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 义 6 】

【図7】

【 図 8 】

【図 9】

【図 11】

【図 12】

【図 13】

【図14】

【図10】

---

フロントページの続き

(56)参考文献 特開2008-039666(JP,A)

国際公開第2008/050443(WO,A1)

特開平10-024986(JP,A)

特開平05-072269(JP,A)

特開平07-260879(JP,A)

国際公開第2010/021038(WO,A1)

特開2000-304808(JP,A)

特開2007-278901(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 01 R 31 / 26