(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7023637号**

**(P7023637)**

(45)発行日 令和4年2月22日(2022.2.22)

(24)登録日 令和4年2月14日(2022.2.14)

## (51)国際特許分類

|        |                  |     |        |        |       |

|--------|------------------|-----|--------|--------|-------|

| H 01 L | 21/8239(2006.01) | F I | H 01 L | 27/105 | 4 4 7 |

| H 01 L | 27/105(2006.01)  |     | H 01 L | 29/82  | Z     |

| H 01 L | 29/82 (2006.01)  |     | H 01 L | 43/08  | M     |

| H 01 L | 43/08 (2006.01)  |     | H 01 L | 43/08  | Z     |

| H 01 L | 43/10 (2006.01)  |     | H 01 L | 43/10  |       |

請求項の数 6 (全20頁) 最終頁に続く

|               |                             |

|---------------|-----------------------------|

| (21)出願番号      | 特願2017-153003(P2017-153003) |

| (22)出願日       | 平成29年8月8日(2017.8.8)         |

| (65)公開番号      | 特開2019-33167(P2019-33167A)  |

| (43)公開日       | 平成31年2月28日(2019.2.28)       |

| 審査請求日<br>前置審査 | 令和2年1月22日(2020.1.22)        |

|          |                                                |

|----------|------------------------------------------------|

| (73)特許権者 | 501387839<br>株式会社日立ハイテク<br>東京都港区虎ノ門一丁目17番1号    |

| (74)代理人  | 110000350<br>ボレール特許業務法人                        |

| (72)発明者  | 三浦 勝哉<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内       |

| (72)発明者  | 山田 将貴<br>東京都港区西新橋一丁目24番14号<br>株式会社日立ハイテクノロジーズ内 |

| (72)発明者  | 濱村 浩孝<br>東京都千代田区丸の内一丁目6番6号<br>株式会社日立製作所内       |

| 審査官      | 加藤 俊哉                                          |

最終頁に続く

(54)【発明の名称】 磁気トンネル接合素子の製造方法

## (57)【特許請求の範囲】

## 【請求項 1】

磁気トンネル接合素子の製造方法において、

第1の強磁性層と、前記第1の強磁性層の下方に配置された障壁層と、第1の磁化方向を有し前記障壁層の下方に配置された第2の強磁性層と、前記第2の強磁性層の下方に配置された第1の非磁性層と、前記第1の磁化方向と反平行である第2の磁化方向を有し前記第1の非磁性層の下方に配置された第3の強磁性層とを有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第3の強磁性層表面または前記第1の非磁性層の途中までプラズマエッチングし、

前記パターニングされた前記積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層\_前記側壁堆積層および前記金属層をマスクとして前記第3の強磁性層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第1の磁化方向は、前記積層膜の積層方向と平行であり、

前記第1の非磁性層の材料および膜厚は、前記第3の強磁性層の磁化方向が前記第2の強磁性層の磁化方向と反平行となる材料および膜厚とされ、

前記パターニングされた第2の強磁性層、第1の非磁性層および第3の強磁性層により前

記磁気トンネル接合素子の積層フェリ型参照層が構成され、前記第3の強磁性層の直径は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる直径とされていることを特徴とする磁気トンネル接合素子の製造方法。

### 【請求項2】

磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第1の非磁性層および第3の強磁性層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第2の強磁性層表面または途中までプラズマエッチングし、

前記パターニングされたハードマスク層よりも外側領域の磁化を消失させることにより磁化消失層を前記第2の強磁性層に形成し、

パターニングされた前記積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記磁化消失層、前記第1の非磁性層および前記第3の強磁性層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして

プラズマエッチングを行った後、前記金属層を除去し、

前記第2の強磁性層の材料および膜厚は、磁化方向が積層方向に対して平行となる材料および膜厚とされ、

前記第1の非磁性層の材料および膜厚は、前記第3の強磁性層の磁化方向が前記第2の強磁性層の磁化方向と反平行となる材料および膜厚とされ、

前記パターニングされた第2の強磁性層、第1の非磁性層および第3の強磁性層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記磁化消失層の幅は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる幅とされていることを特徴とする磁気トンネル接合素子の製造方法。

### 【請求項3】

磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第1の磁性多層膜層表面または前記第1の非磁性層の途中までプラズマエッチングし、

前記パターニングされた積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記第1の磁性多層膜層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして

プラズマエッチングを行った後、前記金属層を除去し、

前記第1の非磁性層の材料および膜厚は、前記第1の磁性多層膜層の磁化方向が前記第2の磁性多層膜層の磁化方向と反平行となる材料および膜厚とされ、

前記第2の非磁性層の材料および膜厚は、前記第2の強磁性層の磁化方向が前記第2の磁性多層膜層の磁化方向と平行となる材料および膜厚とされ、

前記パターニングされた第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記第1の磁性多層膜層の直径は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる直径とされていることを特徴とする磁気トンネル接合素子の製造方法。

10

20

30

40

50

**【請求項 4】**

磁気トンネル接合素子の製造方法において、

上層から順に第1の強磁性層、障壁層、第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層を有しハードマスク層が前記第1の強磁性層の上方に形成された積層膜を形成し、

前記ハードマスク層を円柱形状にパターニングし、

前記パターニングされたハードマスク層をマスクとして前記積層膜を前記第2の磁性多層膜層表面または途中までプラズマエッチングし、

前記パターニングされたハードマスク層よりも外側領域の磁化を消失させることにより磁化消失層を前記第2の磁性多層膜層に形成し、

前記パターニングされた積層膜に側壁堆積層を化学気相成長により積層し、

金属層を前記側壁堆積層に積層して前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとして前記磁化消失層、前記第1の非磁性層および前記第1の磁性多層膜層をプラズマエッチングし、

前記パターニングされたハードマスク層、前記側壁堆積層および前記金属層をマスクとしてプラズマエッチングを行った後、前記金属層を除去し、

前記第1の非磁性層の材料および膜厚は、前記第1の磁性多層膜層の磁化方向が前記第2の磁性多層膜層の磁化方向と反平行となる材料及び膜厚とされ、

前記第2の非磁性層の材料および膜厚は、前記第2の強磁性層の磁化方向が前記第2の磁性多層膜層の磁化方向と平行となる材料及び膜厚とされ、

前記パターニングされた第2の強磁性層、第2の非磁性層、第2の磁性多層膜層、第1の非磁性層および第1の磁性多層膜層により前記磁気トンネル接合素子の積層フェリ型参照層が構成され、

前記磁化消失層の幅は、前記積層フェリ型参照層から前記第1の強磁性層への漏れ磁場の絶対値が概ね0となる幅とされていることを特徴とする磁気トンネル接合素子の製造方法。

**【請求項 5】**

請求項1ないし請求項4のいずれか一項に記載の磁気トンネル接合素子の製造方法において、

前記側壁堆積層は、シリコン酸化物またはシリコン窒化物であることを特徴とする磁気トンネル接合素子の製造方法。

**【請求項 6】**

請求項2または請求項4に記載の磁気トンネル接合素子の製造方法において、

酸化またはイオン注入により前記磁化消失層を形成することを特徴とする磁気トンネル接合素子の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、磁気メモリ(MRAM: Magnetoresistive Random Access Memory)及びMRAMのメモリセルを構成する磁気トンネル接合(MTJ: Magnetic Tunnel Junction)素子に係る、高集積化と安定性を両立する構造及びその製造方法に関する。

**【背景技術】****【0002】**

MRAMは、MTJ素子がメモリセルを構成する抵抗変化型の不揮発メモリである。MTJ素子の基本構造は、第1の強磁性層、障壁層、第2の強磁性層を積層した3層構造である。通常、第1の強磁性層、第2の強磁性層のうちどちらか一方を磁化が可変である記録層とし、他方を磁化が反転しづらい参照層とする。MTJ素子の特徴は、2つの強磁性層の磁化の相対角に応じて素子抵抗が変化する点である。第1の強磁性層の磁化及び第2の強磁性層の磁化が互いに平行になるとき(平行状態)にMTJ素子抵抗は低い状態となり、反平行になるとき(反平行状態)にMTJ素子は高抵抗となる。MRAMでは、この2つの抵抗状態をピット情報に対応させる。このため、電源を遮断しても磁化方向を保ち続

けることが可能であるため不揮発性を有する。また、MTJ素子に電流を印加することで発生するスピントランスマートトルクによって、記録層の磁化反転を誘起し、情報を書き込む方式が主流である。

#### 【0003】

従来、MTJ素子の磁化方向は、膜面に対して水平方向となる磁性体を、第1の強磁性層、第2の強磁性層に適用することが一般的であった。しかし、MTJ素子の磁化方向は、膜面に対して垂直であるほうが微細化に向く。そのため、大きな抵抗変化を示し、且つ垂直磁化を実現する材料技術が開発されてきている。特許文献1などがその例である。

#### 【先行技術文献】

##### 【特許文献】

##### 【0004】

【文献】特開2011-258596号公報

特開2012-248688号公報

特開2014-179639号公報

10

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0005】

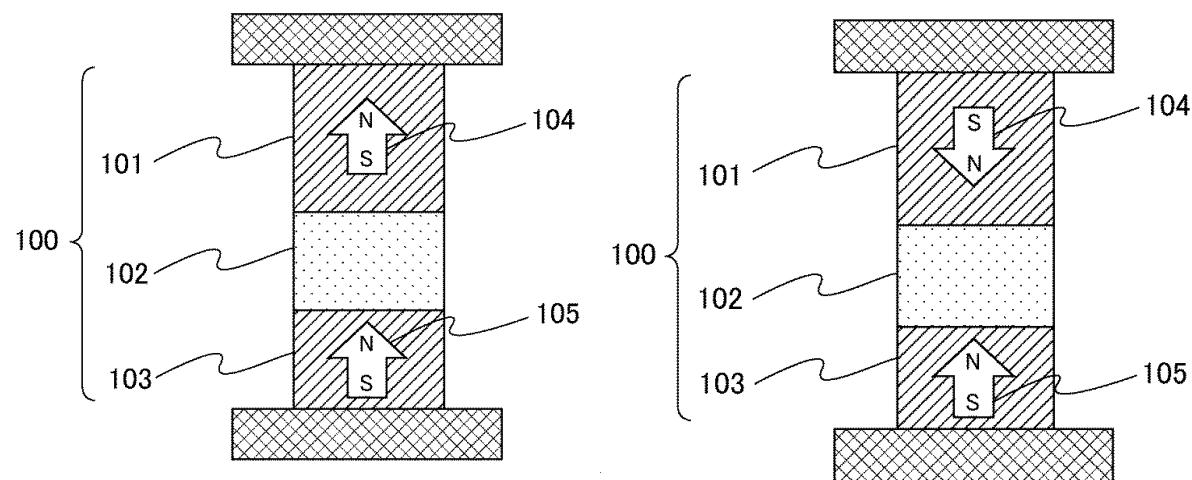

膜面に対して垂直方向の磁化を持つMTJ素子（垂直磁化MTJ素子）は、平行状態と反平行状態で記録層の磁化の安定性に差がある。この理由を、図1A、Bに示した3層構造を持つ基本的なMTJ素子100を例に説明する。MTJ素子100は、第1の強磁性層101、障壁層102、第2の強磁性層103が積層されて構成されている。図1Aは、第1の強磁性層101の磁化104と第2の強磁性層103の磁化105とが互いに平行である平行状態を示している。図1Bは、第1の強磁性層101の磁化104と第2の強磁性層103の磁化105とが互いに反平行である反平行状態を示している。

20

#### 【0006】

図1Aに示す平行状態では、障壁層102を介して異なる磁極（磁化104のS極と磁化105のN極）が接近しているため、磁化104と磁化105との間には引力がはたらく。一方、図1Bに示す反平行状態では、障壁層102を介して同じ磁極（磁化104のN極と磁化105のN極）が接近しているため、磁化104と磁化105との間には斥力がはたらく。従って、平行状態と比較して、反平行状態は磁極同士が反発するため不安定となり、磁化が反転して反平行状態を維持できなくなる確率が増加する。この結果、反平行状態では保証される記録保持時間が減少する。

30

#### 【0007】

この課題に対し、特許文献2では、参照層の面積を記録層の面積より大きくすることで、第1の強磁性層101（記録層）にかかる第2の強磁性層103（参照層）からの漏れ磁場を低減する。これによりMTJ素子は、障壁層102の上側界面または下側界面で段差を設ける構造となる。この構造では、記録層と比較して参照層の面積が増大する程、記録保持時間の減少を抑制できることから、大きな記録保持効果を得るためにには参照層の面積を巨大にしていかなければならない。このため、MTJ素子の微細化を阻害するおそれがある。

40

#### 【0008】

特許文献3は、特許文献2と同様に参照層の面積を記録層の面積より大きくし、さらに参照層を積層フェリ型構造としたMTJ素子を開示する。積層フェリ型構造は基本的に強磁性層／非磁性層／強磁性層の3層構造が適用されるため、参照層に積層フェリ型構造を採用する場合は、第2の強磁性層103（参照層）の代わりに、強磁性層／非磁性層／強磁性層の3層を備えた構造を採用する。このとき2層の強磁性層の磁化は互いに反平行に固定されるように非磁性層の材質と膜厚が選択される。互いに反平行な2層の強磁性層からの漏れ磁界が記録層において互いに相殺されるように、各強磁性層の飽和磁化、平面サイズ、厚さを設定する。しかしながら、この構造ではそれぞれの膜厚を原子層レベルで精密に制御する必要があり、記録層に印加される漏れ磁場を低減することは困難である。

50

**【課題を解決するための手段】**

**【0009】**

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。一実施の形態におけるMTJ素子は、参照層として積層フェリ型構造を備え、かつ積層フェリ構造を構成する2層の磁性層の面積が異なっている。

**【発明の効果】**

**【0010】**

反平行状態における記録保持時間の減少を抑制し、かつ微細化に適したMTJ素子を提供する。

**【図面の簡単な説明】**

10

**【0011】**

【図1A】垂直磁化MTJ素子の磁化配置（平行状態）を説明する図である。

【図1B】垂直磁化MTJ素子の磁化配置（反平行状態）を説明する図である。

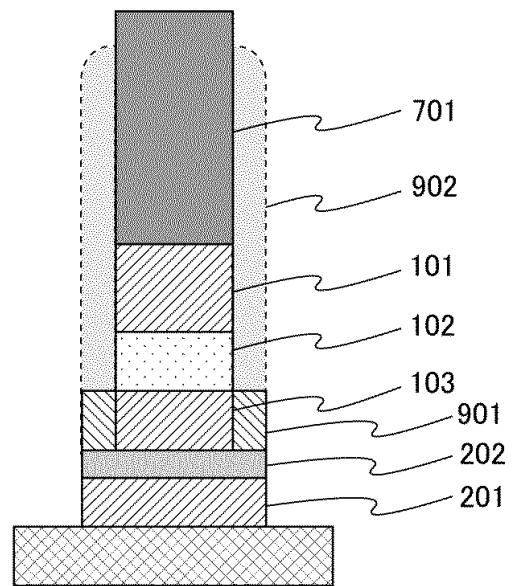

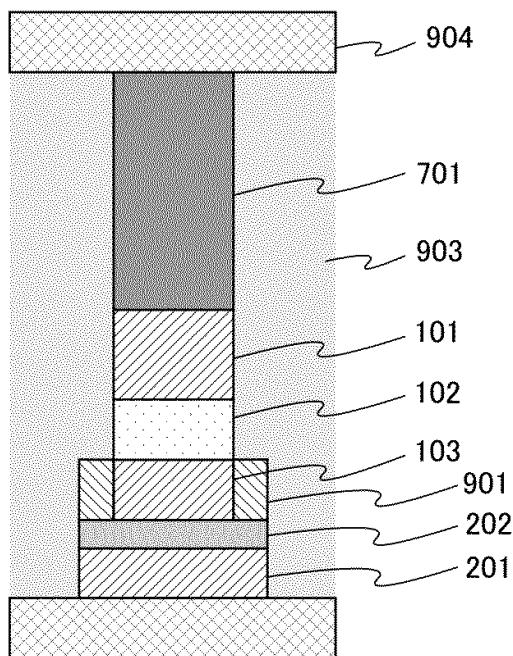

【図2】垂直磁化MTJ素子（第1の構造例）の断面図である。

【図3】参照層から記録層に印加される漏れ磁場の大きさを示すグラフである。

【図4】垂直磁化MTJ素子（第2の構造例）の断面図である。

【図5A】垂直磁化MTJ素子のプロセスフローである。

【図5B】垂直磁化MTJ素子のプロセスフローである。

【図5C】垂直磁化MTJ素子のプロセスフローである。

20

【図5D】垂直磁化MTJ素子のプロセスフローである。

【図5E】垂直磁化MTJ素子のプロセスフローである。

【図5F】垂直磁化MTJ素子のプロセスフローである。

【図6A】垂直磁化MTJ素子のプロセスフローである。

【図6B】垂直磁化MTJ素子のプロセスフローである。

【図6C】垂直磁化MTJ素子のプロセスフローである。

【図7A】垂直磁化MTJ素子のプロセスフローである。

【図7B】垂直磁化MTJ素子のプロセスフローである。

【図7C】垂直磁化MTJ素子のプロセスフローである。

【図7D】垂直磁化MTJ素子のプロセスフローである。

【図7E】垂直磁化MTJ素子のプロセスフローである。

30

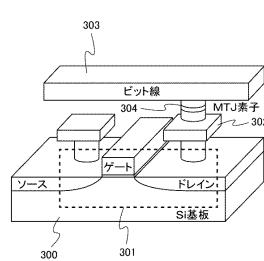

【図8】MRAMの1ビットの鳥瞰図である。

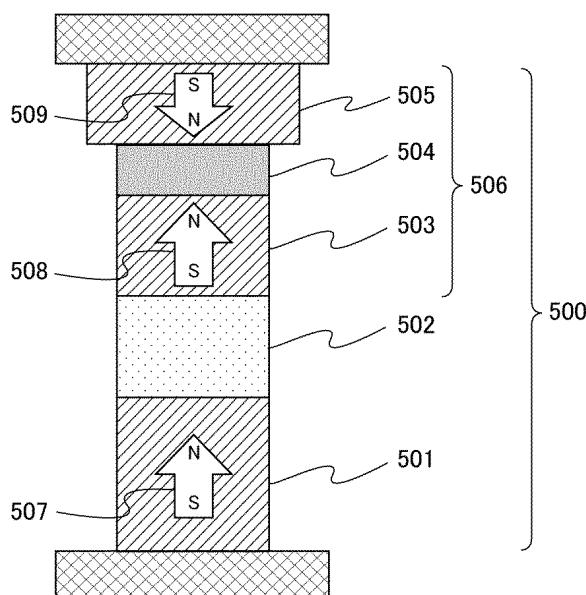

【図9】垂直磁化MTJ素子（第3の構造例）の断面図である。

【図10】垂直磁化MTJ素子（第4の構造例）の断面図である。

【図11】MRAMのメモリセルアレイである。

**【発明を実施するための形態】**

**【0012】**

以下の実施の形態においては便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明等の関係にある。

**【0013】**

40

また、要素の数等（個数、数値、量、範囲等を含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合等を除き、その特定の数に限定されるものではなく、特定の数以上でも以下でもよい。

**【0014】**

さらに、その構成要素（要素ステップ等も含む）は、特に明示した場合および原理的に明らかに必須であると考えられる場合等を除き、必ずしも必須のものではない。

**【0015】**

同様に、構成要素等の形状、位置関係等に言及するときは特に明示した場合および原理的に明らかにそうではないと考えられる場合等を除き、実質的にその形状等に近似または類似するもの等を含むものとする。このことは、数値についても同様である。

50

**【 0 0 1 6 】**

また、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。なお、図面をわかりやすくするために、平面図であってもハッチングを付す場合があり、また断面図であってもハッチングを省略する場合がある。

**【実施例 1】****【 0 0 1 7 】**

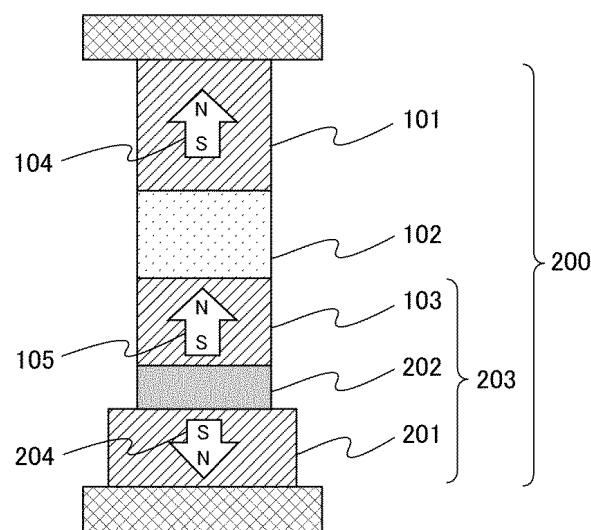

実施の形態に係るMTJ素子の構造（第1の構造例）を、図2を用いて説明する。図2は、実施の形態に係るMTJ素子の一例を示す断面図である。MTJ素子200は、第3の強磁性層201、第1の非磁性層202、第2の強磁性層103、障壁層102、第1の強磁性層101を下から順に積層した積層膜を加工して作製される。第3の強磁性層201、第1の非磁性層202、及び第2の強磁性層103は積層フェリ型参照層203を構成する。このため、第3の強磁性層201の磁化204及び第2の強磁性層103の磁化105が互いに反平行に結合するように、第1の非磁性層202の材料と膜厚が決定されている。第1の強磁性層101は記録層として動作する。

10

**【 0 0 1 8 】**

MTJ素子は円柱などの柱状に加工され、積層フェリ型参照層203を構成する第3の強磁性層201の面積と第2の強磁性層103の面積とが異なるように加工されている。図2の例では、第1の強磁性層101、障壁層102及び第2の強磁性層103が第1の円柱形状をなし、第3の強磁性層201は第1の円柱を積層方向に投影した領域よりも大きい断面を有する第2の円柱形状をなしている。これにより、第3の強磁性層201と第2の強磁性層103との間で段差がある構造となる。なお、積層フェリ型参照層203の断面をテーパー状に加工し、第3の強磁性層201の面積と第2の強磁性層103の面積とを不連続にすることでも効果は得られるが、面積の異なる柱状の第3の強磁性層201と柱状の第2の強磁性層103とを形成する（段差を設ける）方が性能を最適化しやすく、望ましい。

20

**【 0 0 1 9 】**

積層フェリ型参照層203は磁化204と磁化105とが反平行に結合することにより、参照層から発生する漏れ磁場を抑制する効果を有している。しかしながら、参照層203から記録層101に出る漏れ磁場は、参照層のエッジ付近になると急激に大きくなる。これは、エッジ付近の反磁場が小さいことが原因である。そこで、第3の強磁性層201の漏れ磁場が第1の強磁性層101（記録層）に影響を与えない程度に、第3の強磁性層201の面積を大きくする。漏れ磁場が大きくなる部分（エッジ付近）は、一般的にエッジからおよそ2nmから5nmの範囲と考えられる。

30

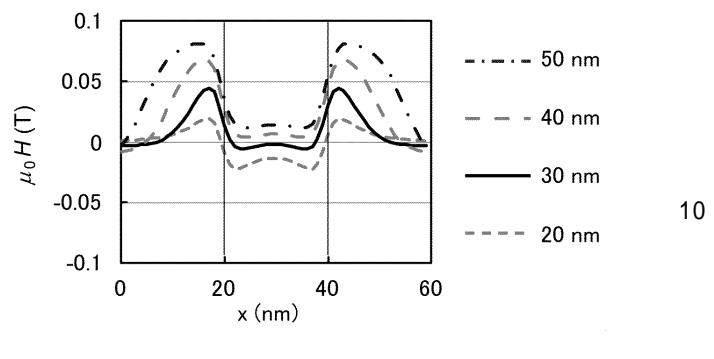

**【 0 0 2 0 】**

図3は、図2に示すMTJ素子における積層フェリ型参照層203から記録層（第1の強磁性層101）に印加される漏れ磁場の大きさを表している。記録層（第1の強磁性層101）の直径を20nmとし、積層フェリ型参照層203を構成する第3の強磁性層201の直径を20、30、40、50nmの4種類で漏れ磁場の大きさをシミュレーションしたものである。MTJ素子の記録層は、図3の横軸において、20nmから40nmの範囲に位置し、第3の強磁性層は、図3の横軸において、それぞれ20nmから40nm、15nmから45nm、10nmから50nm、5nmから55nmの範囲に位置する。縦軸はそれぞれの場合において、その位置において記録層にかかる漏れ磁場を示している。記録層が存在する横軸20nmから40nmの範囲の漏れ磁場の絶対値がゼロに近いほど、積層フェリ型参照層として優れた特性であるといえる。

40

**【 0 0 2 1 】**

図3から、第3の強磁性層201の直径を30nmとした場合（実線の波形）に、横軸20nmから40nmの範囲の漏れ磁場の絶対値がゼロに近くできることがわかる。第3の強磁性層201の直径を30nmとした場合と比較すると、第3の強磁性層201の直径を20nmとした場合には、記録層に対して漏れ磁場はマイナス方向に大きく印加されて

50

いる。また、第3の強磁性層201の直径を40nm、50nmと大きくした場合、記録層に対して印加される漏れ磁場はプラス方向に徐々に大きくなっている。以上より、第3の強磁性層201の直径を30nmとしたときに最も特性が優れているといえる。

#### 【0022】

このようにMTJ素子200は、先行技術文献に開示されるMTJ素子とは明らかな違いがある。特許文献2、特許文献3に開示されているMTJ素子は、断面構造において障壁層のところに段差があるため、障壁層より下の参照層が増大するほど、記録層に印加される漏れ磁場が小さくなる構造である。これに対して、MTJ素子200のように積層フェリ型参照層203を構成する2つの強磁性層間で段差を設けた場合には、第3の強磁性層201の面積には記録層の面積との関係で最適値があることが分かる。このため、メモリセルのフットプリントをそれほど大きくする必要がなく、微細化に適した構造であるといえる。

10

#### 【0023】

障壁層102は、MTJ素子の平行状態と反平行状態とにおける抵抗変化が大きくなる材料であれば良く、酸化物がよく用いられる。特に、MgOが大きな抵抗変化を示すことが知られているため、MgOを用いることが望ましい。また、障壁層102に接する第1の強磁性層101及び第2の強磁性層103には、3d遷移金属元素を少なくとも一つ含む磁性材料が用いられる。特に、MgOと組み合わせることで優れた特性を示すCoFeBを適用する場合が多い。本実施の形態におけるMTJ素子200の場合は、第3の強磁性層201も同様にCoFeBを適用するが、これに限らず3d遷移金属元素を少なくとも一つ含む磁性材料を用いることができる。第1の非磁性層202の材料には、第3の強磁性層201の磁化204及び第2の強磁性層103の磁化105の間の強い反平行結合を得るためにRuを用いることが望ましい。

20

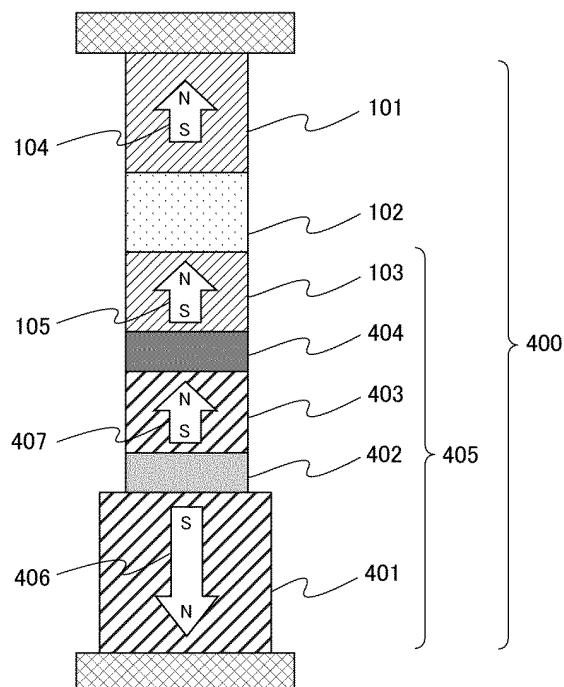

#### 【0024】

前述のようにMgOと接する面にはCoFeBを用いるのが望ましい。しかし、それ以外の磁性層はCoFeBでないほうが望ましい場合がある。特に、参照層の磁気異方性を大きくするために、Co/Pt多層膜などが用いられることがある。その場合のMTJ素子400の構造(第2の構造例)を図4に示す。第1の磁性多層膜層401、第1の非磁性層402、第2の磁性多層膜層403、第2の非磁性層404、第2の強磁性層103、障壁層102、及び第1の強磁性層101を下から順に積層した積層膜を加工して作製される。第1の磁性多層膜層401、第1の非磁性層402、第2の磁性多層膜層403、第2の非磁性層404、及び第2の強磁性層103は積層フェリ型参照層405を構成する。第1の磁性多層膜層401の磁化406及び第2の磁性多層膜層403の磁化407が互いに反平行に結合するように、第1の非磁性層402の材料と膜厚が決定される。さらに、第2の磁性多層膜層403の磁化407及び第2の強磁性層103の磁化105が互いに平行に結合するように、第2の非磁性層404の材料と膜厚が決定される。第1の強磁性層101は記録層として動作する。

30

#### 【0025】

図4の例では、第1の強磁性層101、障壁層102、第2の強磁性層103、第2の非磁性層404及び第2の磁性多層膜層403は第1の円柱形状をなし、第1の磁性多層膜層401は第1の円柱を積層方向に投影した領域よりも大きい断面を有する第2の円柱形状をなしている。これにより、第1の磁性多層膜層401と第2の磁性多層膜層403との間で段差がある構造となる。

40

#### 【0026】

第1の磁性多層膜層401にはCo/Pt、Co/Pd、CoFe/Ptなどが材料として利用可能である。また、磁性多層膜ではなくTbFeCoなどの合金も利用できる可能性がある。第1の非磁性層402の材料は、第1の磁性多層膜層401の磁化406と第2の磁性多層膜層403の磁化407が反平行結合するようRuが選択される場合が多い。膜厚は0.3nm程度である。また、第2の非磁性層404の材料は、第2の磁性多層膜層403の磁化407と第2の強磁性層103の磁化105が平行結合するようTaが

50

選択される場合が多い。膜厚は 0 . 5 nm 程度である。

#### 【 0 0 2 7 】

第 2 の構造例の利点は、参照層の磁化方向の安定性にある。CoFeB と比較して Co / Pt 多層膜に代表される垂直磁化の磁気多層膜のほうが、一般的に磁気異方性が大きく、磁化方向が安定化しやすいためである。これは結果として MRAM の誤動作抑制に寄与する。

#### 【 0 0 2 8 】

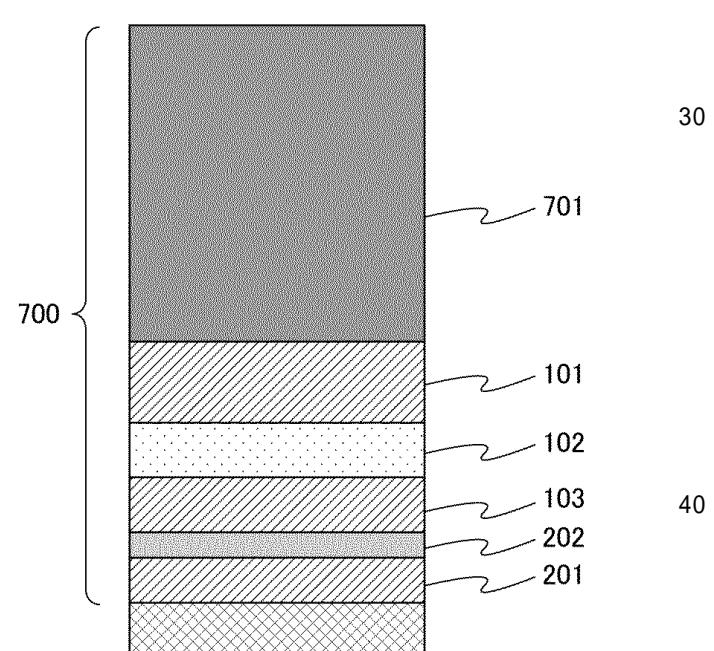

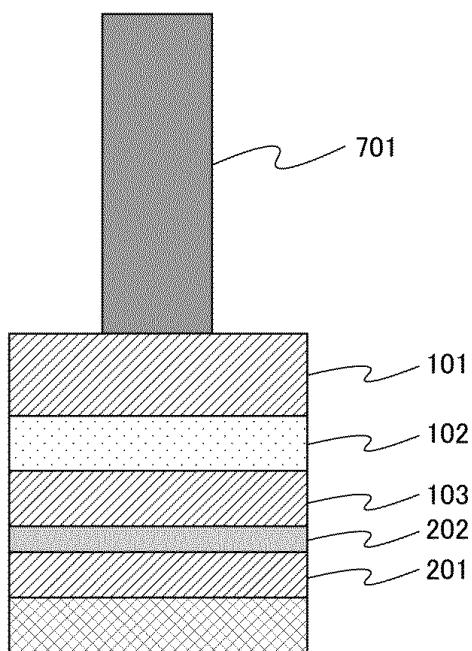

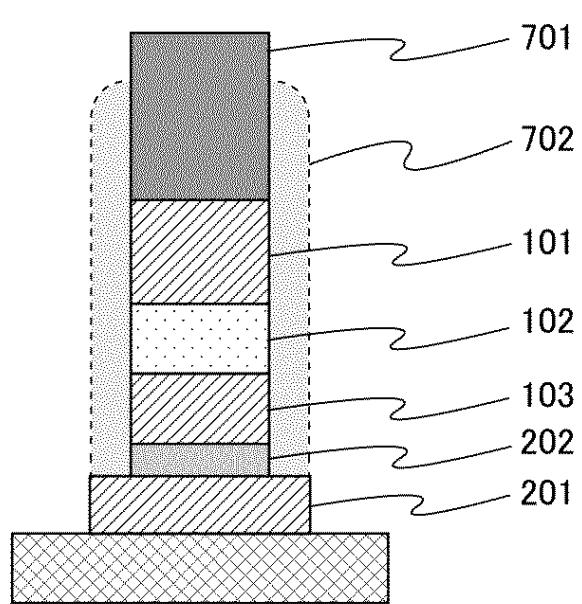

次に、図 2 に示した第 1 の構造例の MTJ 素子を作製するプロセスを説明する。図 5 A は、MTJ 素子を形成する下部電極上に、第 3 の強磁性層 201、第 1 の非磁性層 202、第 2 の強磁性層 103、障壁層 102、第 1 の強磁性層 101 を下から順に積層し、さらに加工のためのハードマスク層 701 を積層した積層膜 700 を示している。第 3 の強磁性層 201 の膜厚は 1 nm、第 1 の非磁性層 202 の膜厚は 0 . 5 nm、第 2 の強磁性層 103 の膜厚は 1 nm、障壁層 102 の膜厚は 1 nm、第 1 の強磁性層 101 の膜厚は 1 . 5 nm、ハードマスク層 701 の膜厚は 150 nm とする。ハードマスク層 701 としては 1 層の Ta を用いる例を示しているが、酸化物などの他の材料と組み合わせた複数層の構造でも良い。MTJ 素子のピラー形成位置に、リソグラフィーを用いてレジストマスクを形成し、ハードマスク層 701 にパターンを転写する。図 5 B は、レジストパターンをハードマスク層 701 に転写し、ハードマスク層 701 を直径 20 nm の円柱形状とした後の断面構造を示している。

10

#### 【 0 0 2 9 】

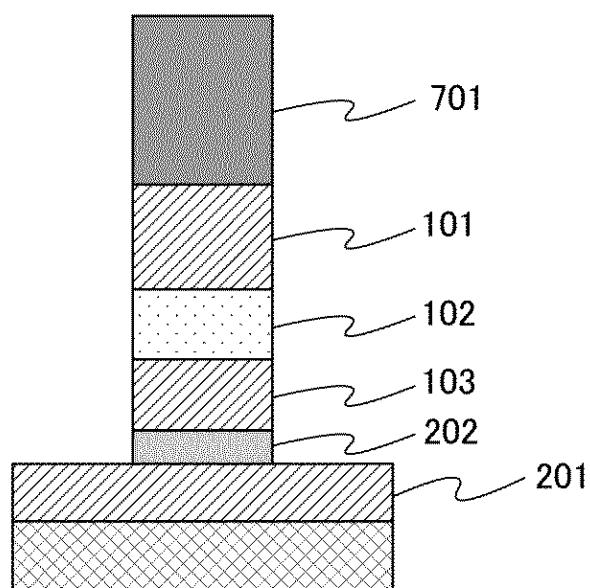

次にプラズマエッティングを用いて、ハードマスク層 701 をマスクとして、第 1 の強磁性層 101、障壁層 102、第 2 の強磁性層 103、第 1 の非磁性層 202 を加工する。図 5 C はプラズマエッティングによる加工を施した後の断面形状である。なお、図 5 C では、プラズマエッティングは第 3 の強磁性層 201 の表面で停止したように示しているが、実際は、第 1 の非磁性層 202 の途中（第 3 の強磁性層 201 の表面に達する前）で停止しても良い。第 3 の強磁性層 201 と第 1 の強磁性層 101 との間に段差が形成されればよいためである。なお、プラズマエッティングの作用により、ハードマスク層 701 の膜厚も当初の厚さから薄くなる（~ 50 nm）。

20

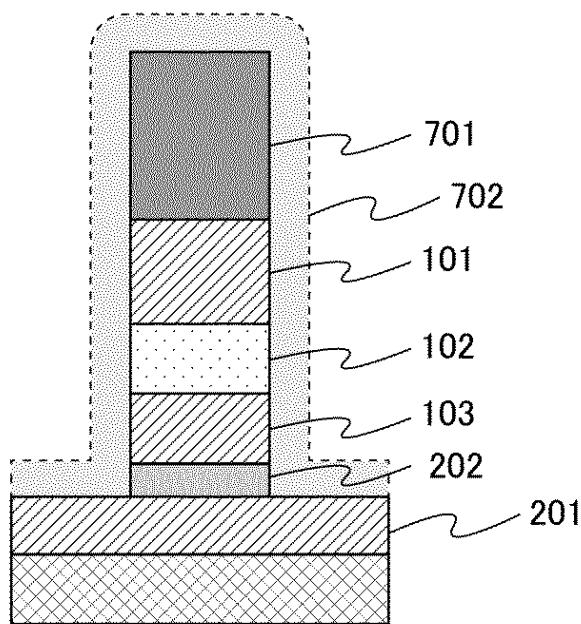

#### 【 0 0 3 0 】

次に、化学気相成長（CVD : Chemical Vapor Deposition）を用いて側壁堆積層 702 をコンフォーマルに成膜したときの断面図を図 5 D に示す。この工程直前の MTJ 素子の状態は、強磁性層及び障壁層が露出しているので、大気に曝すことなく真空中で CVD 成膜装置まで搬送することが望ましい。側壁堆積層 702 には SiN を用いるが、SiO などの絶縁性を有する他の材料でも適用することが可能である。この側壁堆積層 702 は、第 3 の強磁性層 201 をプラズマエッティングする際のマスクになる役割がある。作製する MTJ 素子について、第 1 の非磁性層 202、第 2 の強磁性層 103、障壁層 102、第 1 の強磁性層 101 は直径 20 nm の円柱形状とし、第 3 の強磁性層 201 は直径 30 nm の円柱形状とする。このため、第 1 の非磁性層 202、第 2 の強磁性層 103、障壁層 102 及び第 1 の強磁性層 101 の側壁に堆積する側壁堆積層 702 の膜厚は 5 nm であれば良い。5 nm の膜厚の側壁堆積層 702 と元々の 20 nm のハードマスク層 701 をマスクとしてプラズマエッティングすることで、 $5 \text{ nm} + 20 \text{ nm} + 5 \text{ nm} = 30 \text{ nm}$  直径の円柱形状である第 3 の強磁性層 201 が得られる。プラズマエッティングで第 3 の強磁性層 201 を加工した後の断面形状を図 5 E に示す。

30

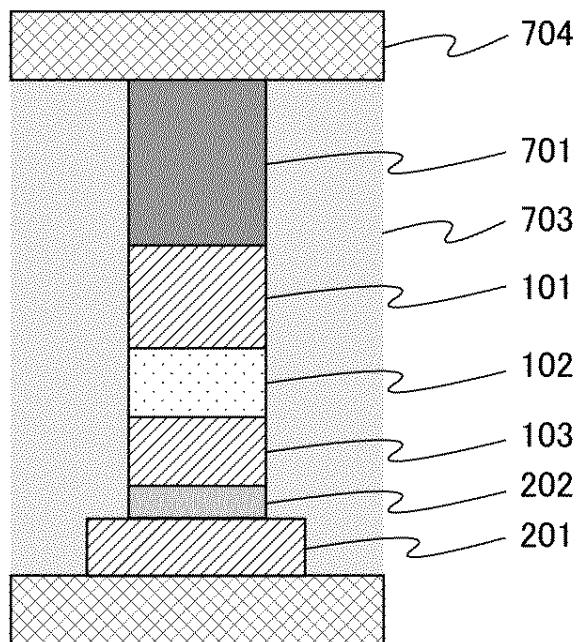

#### 【 0 0 3 1 】

その後、さらに層間絶縁膜 703 を CVD によって堆積し、化学機械研磨（CMP : Chemical Mechanical Polishing）やエッティングバック処理によってハードマスク層 701 の上部をコンタクト開口し、上部電極 704 を作製してプロセスが完了する。プロセス完了後の断面形状を図 5 F に示す。このプロセスの利点は、側壁に積層した層間絶縁膜をマスクとしたセルフアライメントのプロセスであるため、マスクを追加する必要がなくコストが抑えられる点である。また、各層の膜厚や面積の差などがセルフアライメントのプロ

40

50

セスが適用しやすいという点も有利である。

#### 【0032】

図5A～図5Fにて説明したプロセス（第1のプロセス）では、マスクとする側壁堆積層702として1層のSiN層を例示した。しかし、プラズマエッティングする際の、被エッティング材料である磁性体との選択比を考慮した場合、エッティングマスクとしてTaに代表される金属マスクを用いることが望ましい。そこでTaを側壁に積層してマスクとして利用するプロセス例（第2のプロセス）を以下に説明する。

#### 【0033】

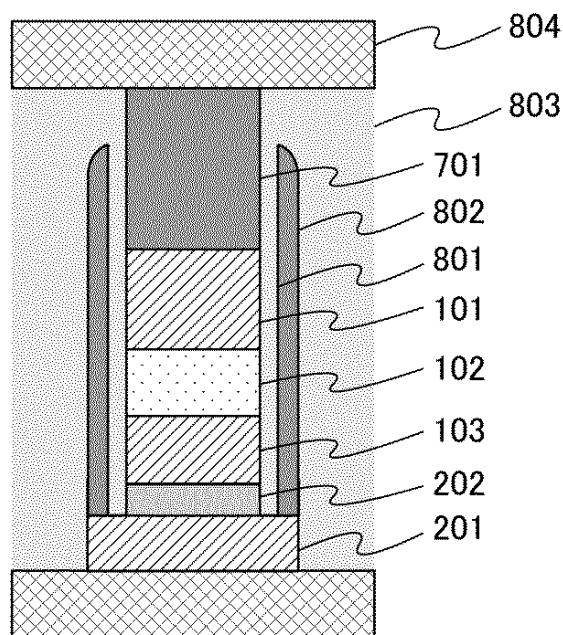

図5A～図5Cまでは同じプロセスフローであるので、説明を省略する。この後、図6Aに示すように、2nm膜厚の側壁堆積層801及び3nm膜厚の側壁金属（Ta）マスク層802をこの順に積層する。その後、これらの側壁堆積層801及び側壁金属マスク層802をマスクとしてプラズマエッティングで第3の強磁性層201を加工する。プラズマエッティングによる加工後の断面形状を図6Bに示す。さらに層間絶縁膜803をCVDによって堆積し、CMPやエッティングバック処理によってハードマスク層701の上部をコントラクト開口し、上部電極804を作製してプロセスが完了する。プロセス完了後の断面形状を図6Cに示す。

10

#### 【0034】

磁性膜との選択比が大きい側壁金属マスクを用いることで、加工中のマスクの後退を最小限に抑えられ、加工後の形状における側壁エッティング角度が90度により近くなる。また、側壁金属マスク層802は、第3の強磁性層201を加工した後に除去しても良い。側壁金属マスク層802のTaを酸化後に、シウウ酸によるウェットエッティングで除去可能である。側壁金属マスク層802を残しておくと、側壁金属マスク層802がショートパスとしてMTJ素子の短絡原因になる可能性があるため、側壁金属マスク層802を除去することによりMTJ素子で短絡が生じるおそれを低減できる。

20

#### 【0035】

第1、第2のプロセスは、図4に示したMTJ素子の作製にも適用できる。この場合は、素子の構造にあわせて、下部電極上に、第1の磁性多層膜層、第1の非磁性層、第2の磁性多層膜層、第2の非磁性層、第2の強磁性層、障壁層、第1の強磁性層を下から順に積層し、さらに加工のためのハードマスク層を積層して積層膜とする。その後の加工は、どちらのプロセスについてもほぼ同様である。図4の構造では、第2の磁性多層膜層と第1の磁性多層膜層との間に段差を設けるため、図5Cに示したプラズマエッティングの工程においては第1の磁性多層膜層の表面または第1の非磁性層の途中（第1の磁性多層膜層の表面に達する前）で停止するようとする。

30

#### 【0036】

以上の実施の形態では、積層フェリ型参照層を構成する2つの強磁性層の物理的な面積を異ならせることにより段差を作製する例を示した。これに対して、物理的な面積差をつけて段差を設けるのではなく、2つの強磁性層の間で磁性体として有効に作用する面積を異ならせることで同様の効果を奏するMTJ素子の構造及びその作製方法を説明する（第3のプロセス）。

40

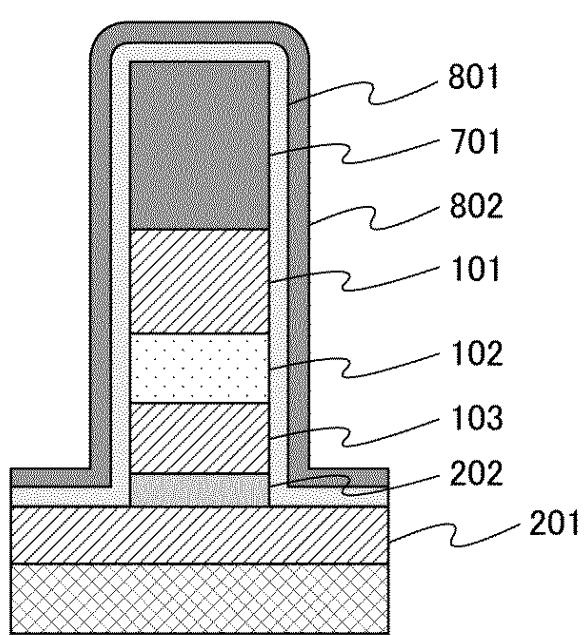

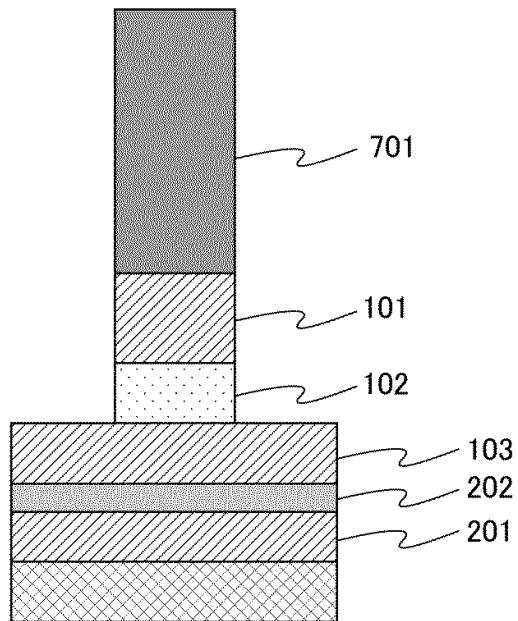

#### 【0037】

図5A～図5Bまでは同じプロセスフローであるので、説明を省略する。その後、プラズマエッティングを用いて、ハードマスク層701をマスクとして、第1の強磁性層101、障壁層102の順に加工を施す。図7Aはプラズマエッティングによる加工を施した後の断面形状である。図7Aでは、プラズマエッティングは第2の強磁性層103の表面で停止したように示しているが、実際は、第2の強磁性層103の途中（第1の非磁性層202の表面に達する前）で停止しても良い。

#### 【0038】

次の工程では、第2の強磁性層103に対して、障壁層102直下部分の磁化は残し、残りの部分の磁化を消失させる。磁化を消失させる方法の一つは酸化である。酸化の方法と

50

しては自然酸化、プラズマ酸化などが考えられる。自然酸化の場合は、酸素導入可能な処理室にMTJ素子を移してから酸素を導入する。この際、大気曝露せずに処理室に移動できるほうが望ましい。また、プラズマ酸化の場合、酸素ラジカルのみ導入する場合と、酸素イオンを導入する場合が考えられる。どちらの場合も、酸化処理をプラズマエッティング室と別の処理室で酸化する場合は、大気曝露を避けるほうが望ましい。

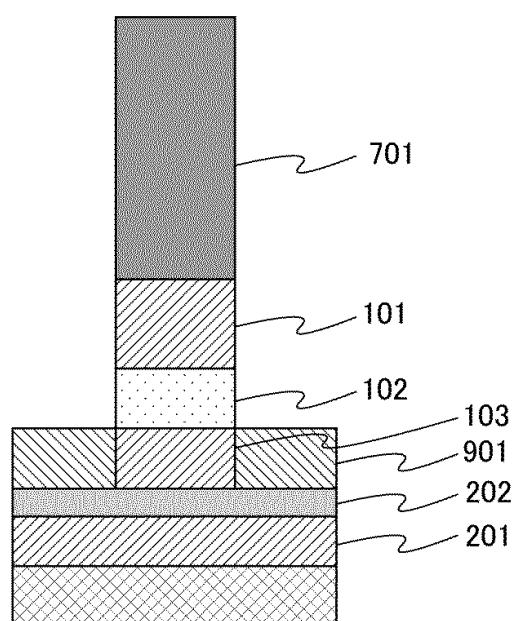

#### 【0039】

一般的に酸素ラジカルの場合は、酸素イオンを導入する場合と比較してダメージが小さいことが利点である。一方、酸素イオンを導入する場合、イオンが加速されるためダメージが大きいが、第2の強磁性層103に向かって上方からイオンが注入されるため酸化を促進しやすいという利点もある。このような工程を経ることによって、図7Bに示したように、障壁層102直下部分の磁化は残し、残りの部分の磁化を消失させ磁化消失層901とすることが可能である。

10

#### 【0040】

このプロセスでは、第1の強磁性層101及び障壁層102をプラズマエッティングする際にMTJ素子側壁に付着する側壁再付着物も、第2の強磁性層103の酸化プロセスにおいて同時に酸化して不導体化することにより、側壁からのリーク電流を抑制できる利点がある。

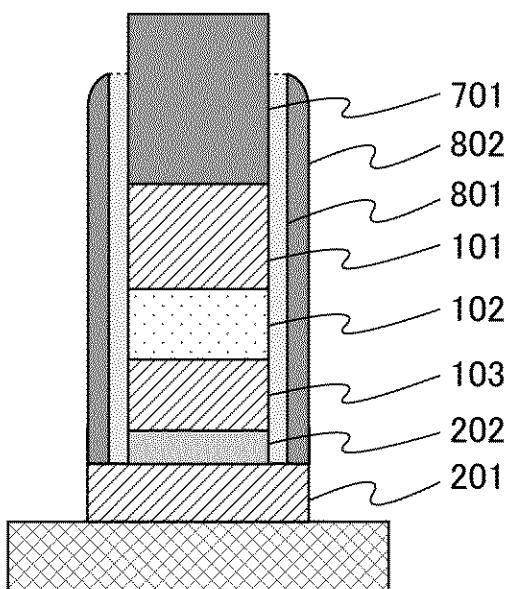

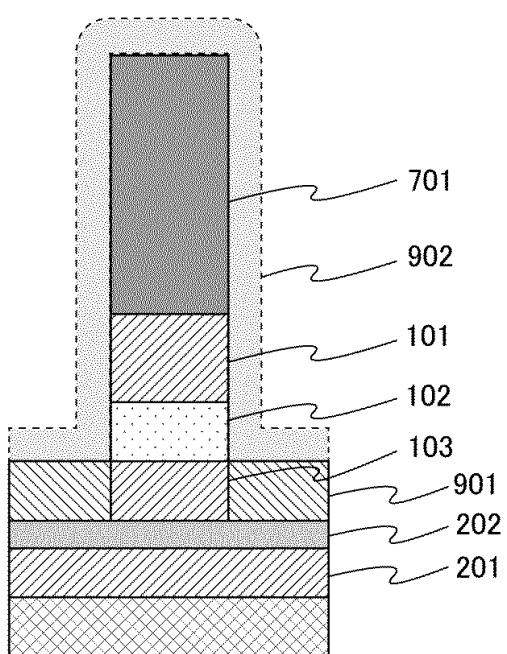

#### 【0041】

酸化工程の後、図7Cに示すように、5nmの膜厚の側壁堆積層902をCVDによって積層する。その後、側壁堆積層902をマスクとしてプラズマエッティングで磁化消失層901、第1の非磁性層202、第3の強磁性層201を加工する。プラズマエッティングによる加工後の断面形状を図7Dに示す。さらに層間絶縁膜903をCVDによって堆積し、CMPやエッティングバック処理によってハードマスク層701の上部をコンタクト開口し、上部電極904を作製してプロセスが完了する。プロセス完了後の断面形状を図7Eに示す。このように、積層フェリ型参照層を構成する各層の面積は同じであるが、上層において強磁性層としての有効面積が狭められたことにより、物理的に段差を設けたのと同様の効果を得ることができる。なお、酸化工程の後、第2のプロセスのように側壁堆積層に金属層を形成し、側壁堆積層及び側壁金属マスク層をマスクとしてプラズマエッティングを行うようにしてもよい。

20

#### 【0042】

上述のプロセスでは磁化消失層901を作製するために酸化処理を施したが、イオン注入により高エネルギーのイオンを照射することにより磁化を消失させることも可能である。この方法を用いる場合は、イオンが第2の強磁性層103に進入する深さを制御できるため、磁化消失層901の厚さ制御が容易になる。

30

#### 【0043】

このように第3のプロセスで形成されたMTJ素子は、第1の強磁性層101が第1の径を有する第1の円柱形状をなし、第1の円柱を積層方向に投影した領域と同じ大きさの断面を有する第2の強磁性層103、及び少なくとも第2の強磁性層103が第1の非磁性層202に接する面において第2の強磁性層103の全周を覆うように形成された磁化消失層901が、第1の径よりも大きい第2の径を有する第2の円柱形状をなし、第3の強磁性層201は、第2の円柱を積層方向に投影した領域と同じ大きさの断面を有する。

40

#### 【0044】

第3のプロセスもまた、図4に示したMTJ素子の作製にも適用できる。この場合は、素子の構造にあわせて、下部電極上に、第1の磁性多層膜層、第1の非磁性層、第2の磁性多層膜層、第2の非磁性層、第2の強磁性層、障壁層、第1の強磁性層を下から順に積層し、さらに加工のためのハードマスク層を積層して積層膜とする。その後の加工は、どちらのプロセスについてもほぼ同様である。図4の構造では、図7Bに示したプラズマエッティングの工程においては第2の磁性多層膜層の表面または途中（第1の非磁性層の表面に達する前）で停止するようにする。

#### 【0045】

50

このように第3のプロセスで形成されたMTJ素子は、第1の強磁性層101、障壁層102、第2の強磁性層103が第1の径を有する第1の円柱形状をなし、第1の円柱を積層方向に投影した領域と同じ大きさの断面を有する第2の磁性多層膜層403、及び少なくとも第2の磁性多層膜層403が第1の非磁性層402に接する面において第2の磁性多層膜層403の全周を覆うように形成された磁化消失層901が、第1の径よりも大きい第2の径を有する第2の円柱形状をなし、第1の磁性多層膜層401は、第2の円柱を積層方向に投影した領域と同じ大きさの断面を有する。

#### 【実施例2】

#### 【0046】

実施例1のMTJ素子は、記録層が参照層の上方に位置する構造（「ボトムピン型構造」という）であった。同様に、記録層が参照層の下方に位置する構造（「トップピン型構造」という）においても、参照層を積層フェリ型参照層とし、2つの強磁性層の面積を異ならせることにより、同様の効果を得ることができる。

10

#### 【0047】

トップピン型構造とする利点について説明する。MRAMでは1個のMTJ素子に対して1個の選択トランジスタが直列に接続されている。図8にMRAMの1ビットの鳥瞰図を示す。シリコン基板300に選択トランジスタ301が形成され、選択トランジスタ301のドレイン電極302とビット線303との間にMTJ素子304が形成されている。図に示されるように、選択トランジスタ301はMTJ素子304の下層に配置される。この場合、図8に示すように、MTJ素子への書き込み時に選択トランジスタが供給できる電流は、選択トランジスタからMTJ素子に流れるとき((b),(d))に小さく、MTJ素子から選択トランジスタに流れるとき((a),(c))に大きい。一方、MTJ素子の磁化反転動作を行うために必要な電流は、一般的に平行状態から反平行状態への書き込みの場合が大きい。MTJ素子がボトムピン型構造の場合は、平行状態から反平行状態への書き込みの電流方向が選択トランジスタからMTJ素子方向となるため、必要な電流を流すために選択トランジスタの電流供給能力を高める必要がある。MTJ素子がトップピン構造の場合は、電流がMTJ素子から選択トランジスタに流れる場合に平行状態から反平行状態への書き込みとなるため、より電流供給能力の低い選択トランジスタでも反平行状態への書き込みが問題なく行えることとなり、有利である。

20

#### 【0048】

トップピン構造としたMTJ素子の構造(第3の構造例)について図9を用いて説明する。図9はMTJ素子(第3の構造例)の断面図である。第1の強磁性層501、障壁層502、第2の強磁性層503、第1の非磁性層504、第3の強磁性層505を下部電極の上に下から順に積層した積層膜を加工して作製される。第2の強磁性層503、第1の非磁性層504、第3の強磁性層505は積層フェリ型参照層506を構成する。第2の強磁性層503の磁化508、及び第3の強磁性層505の磁化509が互いに反平行に結合するように、第1の非磁性層504の材料と膜厚が決定される。第1の強磁性層501は記録層として動作する。

30

#### 【0049】

MTJ素子は柱状に加工され、積層フェリ型参照層506を構成する第2の強磁性層503と第3の強磁性層505の面積が異なるように加工されている。図9の例では、第2の強磁性層503の面積が、第3の強磁性層505より小さくなるように加工されている。これにより、第2の強磁性層503と第3の強磁性層505との間で段差がある構造となる。

40

#### 【0050】

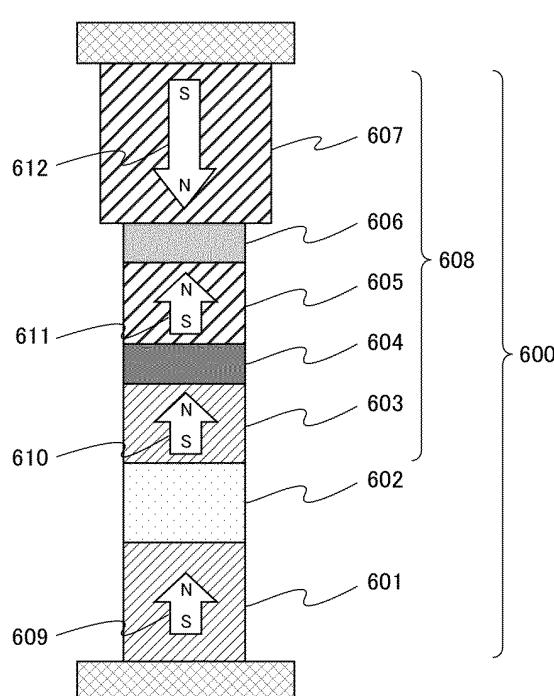

同様に、Co/Pt多層膜を用いた場合のトップピン構造も作製可能である。Co/Pt多層膜を用いたトップピン構造のMTJ素子600の断面図を図10に示す。第1の強磁性層601、障壁層602、第2の強磁性層603、第2の非磁性層604、第2の磁性多層膜層605、第1の非磁性層606、第1の磁性多層膜層607を下部電極の上に下から順に積層した積層膜を加工して作製される。第2の強磁性層603、第2の非磁性層

50

604、第2の磁性多層膜層605、第1の非磁性層606、第1の磁性多層膜層607は積層フェリ型参照層608を構成する。第2の強磁性層603の磁化610、及び第2の磁性多層膜層605の磁化611は互いに平行に結合するように、第2の非磁性層604の材料と膜厚が決定される。第2の磁性多層膜層605の磁化611、及び第1の磁性多層膜層607の磁化612は互いに反平行に結合するように、第1の非磁性層606の材料と膜厚が決定される。第1の強磁性層601は記録層として動作する。

#### 【実施例3】

##### 【0051】

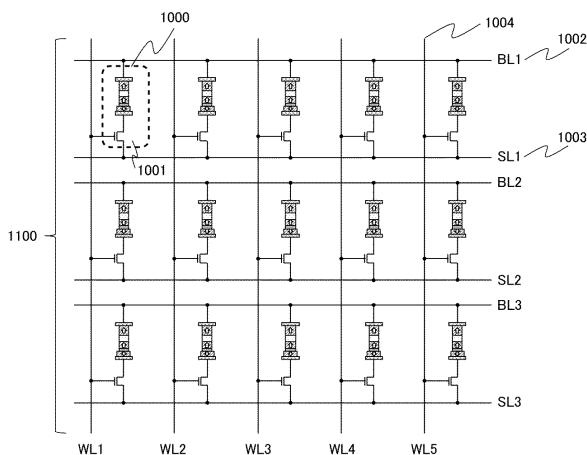

以上説明したMTJ素子をメモリセルの記憶素子としてMRAMを構成することができる。図11にMRAMのメモリアレイ1100を示す。図8に示したようにメモリセル1000は、MTJ素子とそのソース・ドレイン経路がMTJ素子に直列接続される選択トランジスタとで構成される。ここでは、MTJ素子として図2に示したMTJ素子200を用いている。

10

##### 【0052】

メモリセル1000のMTJ素子200は、第3の強磁性層201の下部に配置されている下部電極が選択トランジスタ1001のドレイン電極と電気的に接続されている。また、第1の強磁性層101の上部に配置されている上部電極はビット線(BL)1002に電気的に接続されている。選択トランジスタ1001のソース電極は、ビット線1002と平行に配置されるソース線(SL)1003に電気的に接続されている。選択トランジスタ1001のゲート電極は、ビット線及びソース線と直交するように配置されるワード線(WL)1004に接続されている。

20

##### 【0053】

図11に示される通り、ビット線1002、ソース線1003、及びワード線1004は複数配置され、ビット線1002及びソース線1003とワード線1004とが交差する各点に、メモリセル1000が配置される。各ビット線1002、ソース線1003、ワード線1004はそれぞれ独立に電圧を制御する機構が設置されている。

##### 【0054】

特定のメモリセル1000を選択するときは、そのメモリセル1000が電気的に接続しているビット線1002及びソース線1003の電圧を制御し、そのMTJ素子が接続しているワード線1004に電圧を印加することで選択トランジスタ1001に電流が印加される状態となる。例えば、MTJ素子200を低抵抗状態に書き込みする場合、ソース線1003の電位と比較してビット線1002の電位が高くなるように設定する。この状態でワード線1004に電圧を印加すると、MTJ素子200の上部電極から下部電極に向かって電流が流れ。電流がMTJ素子200の書き込み閾値電流を超えるとMTJ素子200は低抵抗状態になる。

30

##### 【0055】

なお、MTJ素子を使用するデバイス例として、MRAMメモリアレイ1100を示したが、磁気センサ等、他のデバイスにも適用することが可能である。

##### 【0056】

以上、本発明について説明したが、実施の形態に限定されるものではなく、様々な変形例が含まれる。実施の形態は本発明を分かりやすく説明するために詳細に説明したものであり、必ずしも説明した全ての構成を備えるものに限定されるものではない。また、実施の形態の構成の一部について、他の構成の追加、削除、置換をすることも可能である。

40

#### 【符号の説明】

##### 【0057】

100, 200, 400: MTJ素子、101: 第1の強磁性層、102: 障壁層、103: 第2の強磁性層、201: 第3の強磁性層、202: 第1の非磁性層、203, 405: 積層フェリ型参照層、401: 第1の磁性多層膜層、402: 第1の非磁性層、403: 第2の磁性多層膜層、404: 第2の非磁性層、500, 600: MTJ素子、501, 601: 第1の強磁性層、502, 602: 障壁層、503, 603: 第2の強磁性層

50

層、504：第1の非磁性層、505：第3の強磁性層、506，608：積層フェリ型参照層、604：第2の非磁性層、605：第2の磁性多層膜層、606：第1の非磁性層、607：第1の磁性多層膜層、700：積層膜、701：ハードマスク層、702，801，902：側壁堆積層、703，803，903：層間絶縁膜、704，804，904：上部電極、802：側壁金属マスク層、901：磁化消失層、1000：メモリセル、1001：選択トランジスタ、1002：ビット線、1003：ソース線、1004：ワード線、1100：メモリアレイ。

【図面】

【図1A】

【図1B】

10

図1A

図1B

20

30

40

50

【図 2】

図2

【図 3】

図3

10

20

【図 4】

図4

【図 5 A】

図5A

30

40

50

【図 5 B】

図5B

【図 5 C】

図5C

10

20

30

【図 5 D】

図5D

【図 5 E】

図5E

40

50

【図 5 F】

図5F

【図 6 A】

図6A

10

20

【図 6 B】

図6B

【図 6 C】

図6C

30

40

50

【図 7 A】

図7A

【図 7 B】

図7B

10

20

【図 7 C】

図7C

【図 7 D】

図7D

30

40

50

【図 7 E】

図 7 E

【図 8】

図 8

| MTJ<br>素子      | ボトムピン型構造                  |                           | トップピン型構造                  |                           |

|----------------|---------------------------|---------------------------|---------------------------|---------------------------|

|                | BL<br>記録層<br>参照層<br>Drain | BL<br>参照層<br>記録層<br>Drain | BL<br>参照層<br>記録層<br>Drain | BL<br>記録層<br>参照層<br>Drain |

| 電流<br>方向       | (a)<br>BL<br>↓<br>Drain   | (b)<br>BL<br>↑<br>Drain   | (c)<br>BL<br>↓<br>Drain   | (d)<br>BL<br>↑<br>Drain   |

| 磁化<br>反転<br>動作 | 反平行 →<br>平行               | 平行 →<br>反平行               | 平行 →<br>反平行               | 反平行 →<br>平行               |

10

20

30

40

【図 9】

図 9

【図 10】

図 10

50

【図 1 1】

図11

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

H 0 1 L 43/12 (2006.01)

F I

H 0 1 L 43/12

(56)参考文献

特表 2 0 0 9 - 5 1 4 2 1 1 ( J P , A )

特開 2 0 1 3 - 0 9 3 3 4 9 ( J P , A )

米国特許出願公開第 2 0 1 7 / 0 2 2 2 1 3 2 ( U S , A 1 )

特開 2 0 1 7 - 0 5 9 6 9 0 ( J P , A )

特開 2 0 1 4 - 2 2 9 7 5 8 ( J P , A )

(58)調査した分野 (Int.Cl., DB名)

H 0 1 L 2 1 / 8 2 3 9

H 0 1 L 2 9 / 8 2

H 0 1 L 4 3 / 0 8

H 0 1 L 4 3 / 1 0

H 0 1 L 4 3 / 1 2