**(19) 대한민국특허청(KR)**

**(12) 특허공보(B1)**

(51) Int. Cl.<sup>6</sup>

G05B 19/04

(45) 공고일자 1996년02월08일

(11) 공고번호 특 1996-0001977

|           |                |           |                |

|-----------|----------------|-----------|----------------|

| (21) 출원번호 | 특 1992-0014743 | (65) 공개번호 | 특 1993-0018342 |

| (22) 출원일자 | 1992년08월17일    | (43) 공개일자 | 1993년09월21일    |

(30) 우선권주장 92-25594 1992년02월13일 일본(JP)

(71) 출원인 고요 덴시 고교 가부시끼가이샤 요꼬따니 노부히로

일본국 도오쿄도 고다이라시 덴진쵸 1죠메 171반지

(72) 발명자 가즈히코 구도

일본국 도오쿄도 고다이라시 덴진쵸 1죠메 171반지 고요 덴시 고교 가부

시끼가이샤 나이

(74) 대리인 이병호, 최달용

**심사관 : 김성운 (책자공보 제4327호)**

**(54) 프로그램가능 제어기의 제어방법**

**요약**

내용 없음.

**대표도**

**도1**

**영세서**

[발명의 명칭]

프로그램가능 제어기의 제어방법

[도면의 간단한 설명]

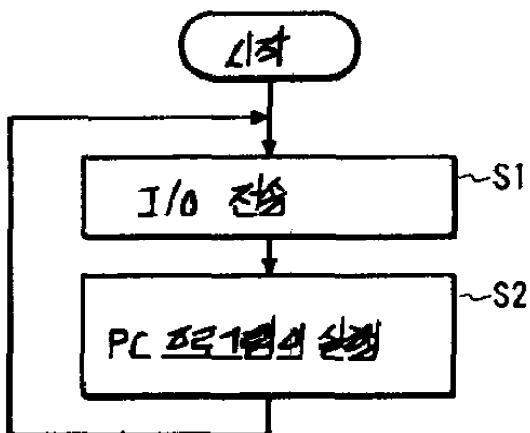

제1도는 본 발명의 일실시예에 따른 프로그램가능 제어기(PC)의 제어 방법을 도시하는 프로우챠트.

제2도는 제1도의 제어방법을 실시하기 위한 하드웨어 구성을 도시하는 블록도.

제3도는 실시예에서 I/O 맵 정도 설명도.

제4도는 상기 실시예에서 사용자 프로그램과 목적 프로그램이 어떻게 RAM에 격납되는가에 대한 설명도.

제5도는 종래의 PC의 시컨스 제어 방법을 도시하는 플로우챠트.

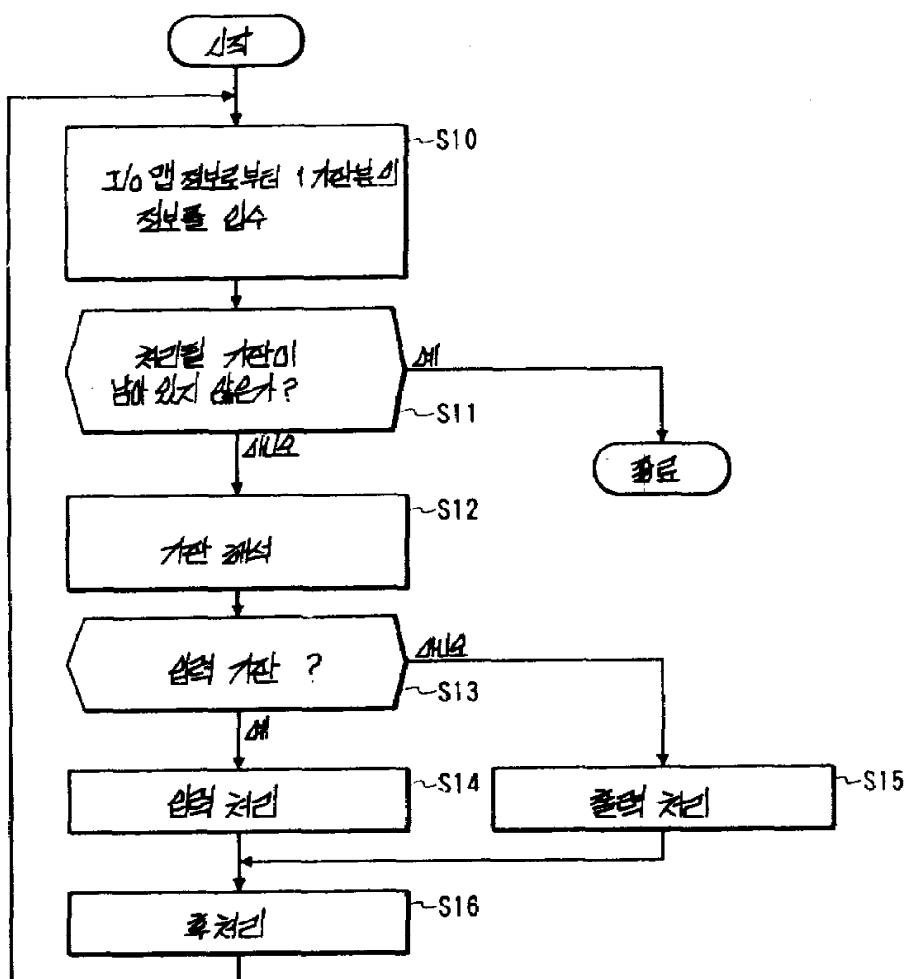

제6도는 종래의 I/O 전송 처리를 도시하는 플로우챠트.

제7도는 종래의 PC 프로그램 실행 처리를 도시하는 플로우챠트.

\* 도면의 주요부분에 대한 부호의 설명

1 : 중앙처리장치(CPU)

2 : ROM

3 : RAM

10, 12, 13 : 입력기판

11, 14 : 출력기판

[ 발명의 상세한 설명 ]

[발명의 배경]

본 발명은 프로그램가능 제어기의 제어 방법, 특히, 프로그램가능 제어기의 처리 속도의 향상에 관한 것이다.

제5도는 종래의 프로그램가능 제어기(이하 "PC"라고 약자로 씀)가 동작하는 동안 수행된 처리를 도시하는 플로우챠트이다. 도시된 바와같이, I/O 전송(S1) 및 PC 프로그램(S2)의 실행으로 이루어져 있는 시컨스 제어 처리가 반복적으로 수행된다.

제6도는 I/O 전송 처리의 상세를 도시하는 플로우챠트이며, 상기 I/O 전송 처리의 입력 상태 정보는 PC에 접속된 입력 회로 기판으로부터 수신되고 PC 프로그램의 실행 결과는 출력 회로 기판에 출력된

다.

단계(S10)에서, 1개의 회로 기판분의 정보는 PC의 메모리 장치내에 격납된 I/O 맵 정보(즉, PC에 접속된 회로 기판상의 정보)로부터 핀업된다. 그다음, 처리될 회로 기판이 남아있지 않은지를 단계(S11)에 사 판단한다.

회로 기판(또는 판)이 남아있다면, 상기 핀업된 기판의 종류는 단계(S12)에서 해석되고, 회로 기판이 입력 회로 기판인지 또는 아닌지의 여부가 단계(S13)에서 판단된다. 만약, 상기 판단이 긍정적이라면, 단계(S14)에서 입력 회로 기판으로부터 입력 상태 정보를 수신하도록 입력 처리가 수행된다. 다른 한편, 수행이 부정적이라면, 즉, 회로 기판이 출력 회로 기판이라면, 단계(S15)에서, 핀업된 출력 회로 기판에 PC프로그램의 실행 결과를 제공하도록 출력 처리가 수행된다. 입력 처리 또는 출력 처리가 완료된 후, 단계(S16)에서, I/O 맵 정보의 판독 어드레스를 다시 시작하도록 후 처리가 수행되고, 그 처리는 단계(S10)로 되돌아간다. 상기 방법으로, 각각의 회로 기판의 종류의 판단에 기초로 해서 모든 기판에 대해 입력 처리 및 출력 처리가 수행되며, 즉, 단계(S11)의 판단이 긍정적일 때까지 반복된다.

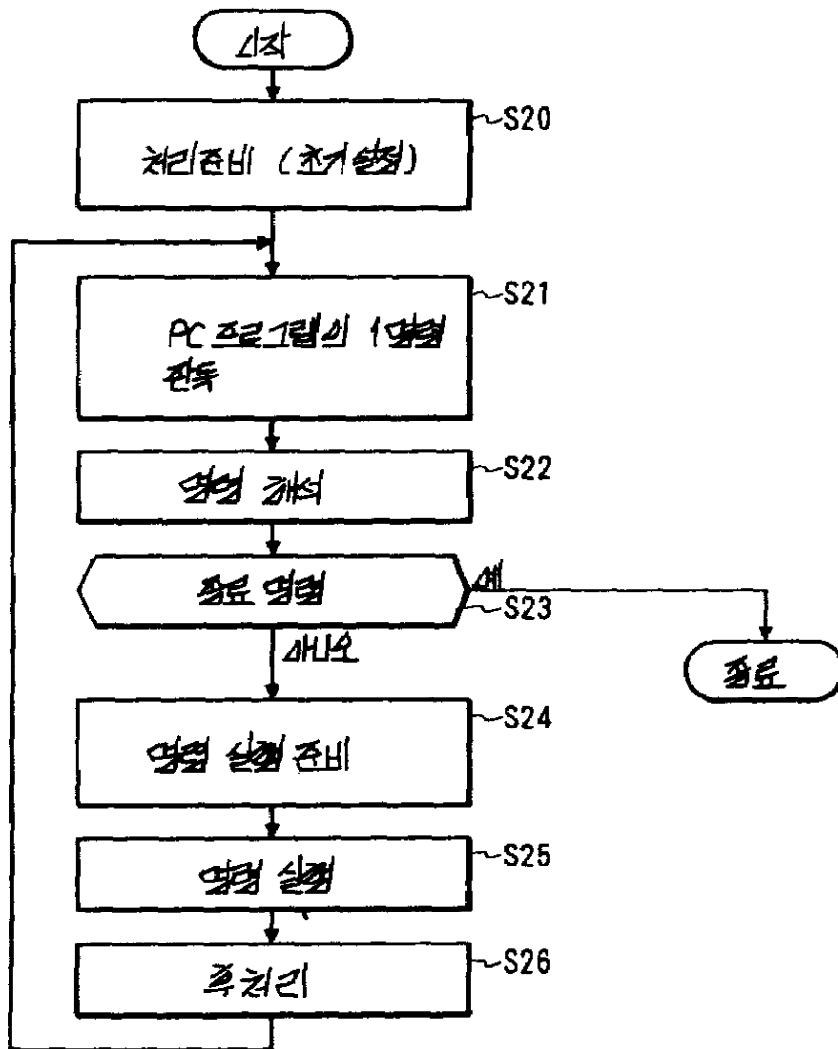

제7도는 PC 프로그램 실행 처리의 상세를 도시하는 플로우챠트이며, 이는 PC 프로그램 실행 처리의 사용자가 작성한 시컨스 제어의 사용자 프로그램이 실행된다. 초기 설정 등의 처리 준비가 단계(S20)에서 먼저 수행된다. 그다음, PC 프로그램의 1명령이 단계(S21)에서 메모리 장치로부터 판독되고, 단계(S22)에서 해석된다. 그 다음, 상기 명령이 종료 명령인지의 여부가 단계(S23)에서 판단된다. 만약, 상기 판단이 부정적이라면, 판독 명령의 실행 준비는 단계(S24)에서 수행되고, 그 명령이 단계(S25)에서 실제로 실행된다. 최종적으로, 단계(S26)에서 PC 프로그램의 판독 어드레스를 갱신하도록 후 처리가 수행되고, 그 처리가 단계(21)로 되돌아간다. 상기 처리는 종료 명령이 단계(S23)에서 판독되어졌다고 판단될 때까지 반복된다.

그러나, 종래의 PC들에서 수행된 상기 I/O 전송 처리 및 PC 프로그램 실행 처리의 상세를 조사한다면, 시컨스 제어에 절대적으로 필요한 것과 전혀 다른 처리, 즉, I/O 처리 및 명령 실행 처리가 또한 수행된다는 것을 알 수 있다. 이는 부수적인 처리 시간을 불가피하게 필요로 할 것이다.

#### [발명의 개요]

본 발명은 기술적으로 상기 문제점을 감안하여 구성되어졌고 시컨스 제어의 처리 시간을 단축시킬 수 있는 프로그램가능 제어기(PC)의 제어 방법을 제공하는데 목적이 있다.

본 발명에 따르면, 입출력 전송 처리 및 프로그램가능 제어기 프로그램의 동작 처리를 포함하는 시컨스제어 처리가 순환적으로 수행되는 프로그램가능 제어기의 제어 방법은, 입출력 전송 처리의 적어도 하나의 실행 순서 및 중앙 처리 장치에 의해서 직접 실행될 수 있는 기계어 프로그램의 형태로 프로그램가능 제어기 프로그램을 작성하는 단계와 ; 상기 기계어 프로그램을 메모리 장치에 격납하는 단계와 ; 상기 격납된 기계어 프로그램을 기초로 하여 중앙처리장치에 의해서 순환적으로 시컨스제어 처리를 수행하는 단계를 포함한다.

#### [양호한 실시예에 대한 설명]

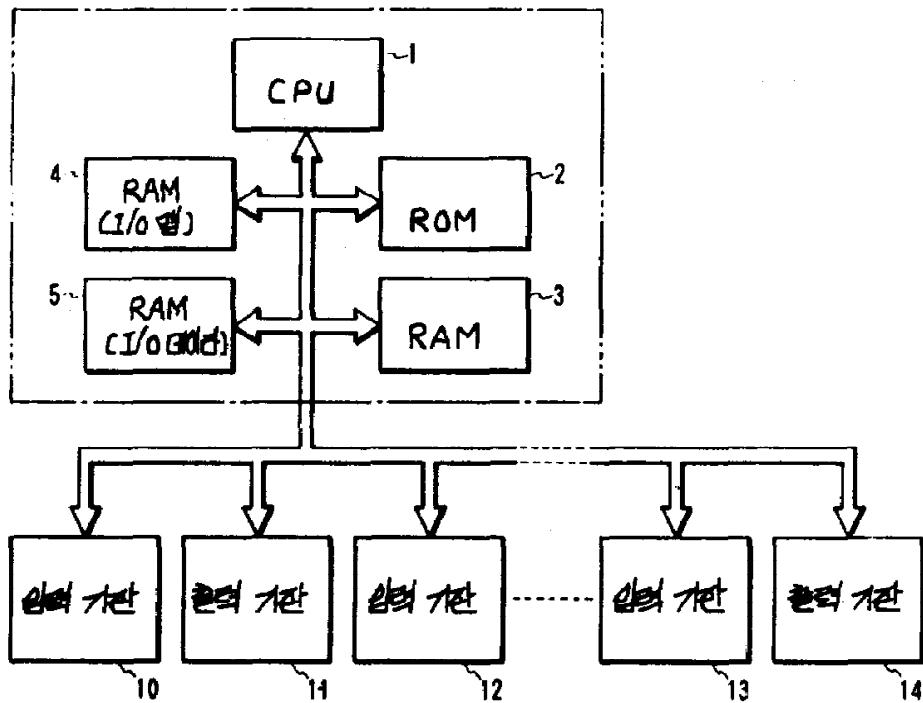

제2도는 본 발명의 실시예에 따라서 프로그램가능제어기(PC)의 하드웨어 구성을 도시하는 블록도이다. 동 도면에서, (1)은 중앙처리장치(CPU)를 나타내고, (2)는 CPU(1)의 시스템 프로그램을 격납하기 위한 ROM이고, (3)은 사용자 프로그램 등을 격납하기 위한 RAM이고, (4)은 I/O 맵 정보 등을 격납하기 위한 RAM이며, (5)는 입력 회로 기판과 출력 회로 기판에 대응하는 I/O 데이터를 격납하기 위한 RAM이다. (10 내지 14)는 입력 회로 기판과 출력 회로 기판을 나타낸다.

제3도는 RAM(4)에 격납된 I/O 맵 정보의 설명도이다. 상기 I/O 맵 정보는 PC에 접속된 각 슬롯마다의 회로 기판의 종류(즉, 입력 회로 기판 또는 출력 회로 기판)와 그 자체의 입력 또는 출력점의 수를 표시하는 정보를 포함한다.

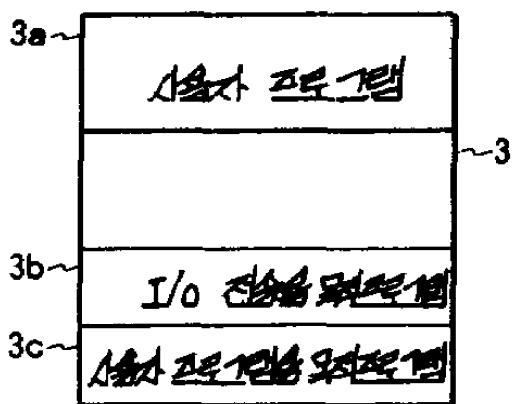

제4도는 사용자 프로그램(3a) 및 목적 프로그램(3b 및 3c), (여기서 3b, 3c의 프로그램은 후술하는 연산처리에 의해서 작성됨)이 어떻게 RAM(3)에 격납되는가를 도시한다.

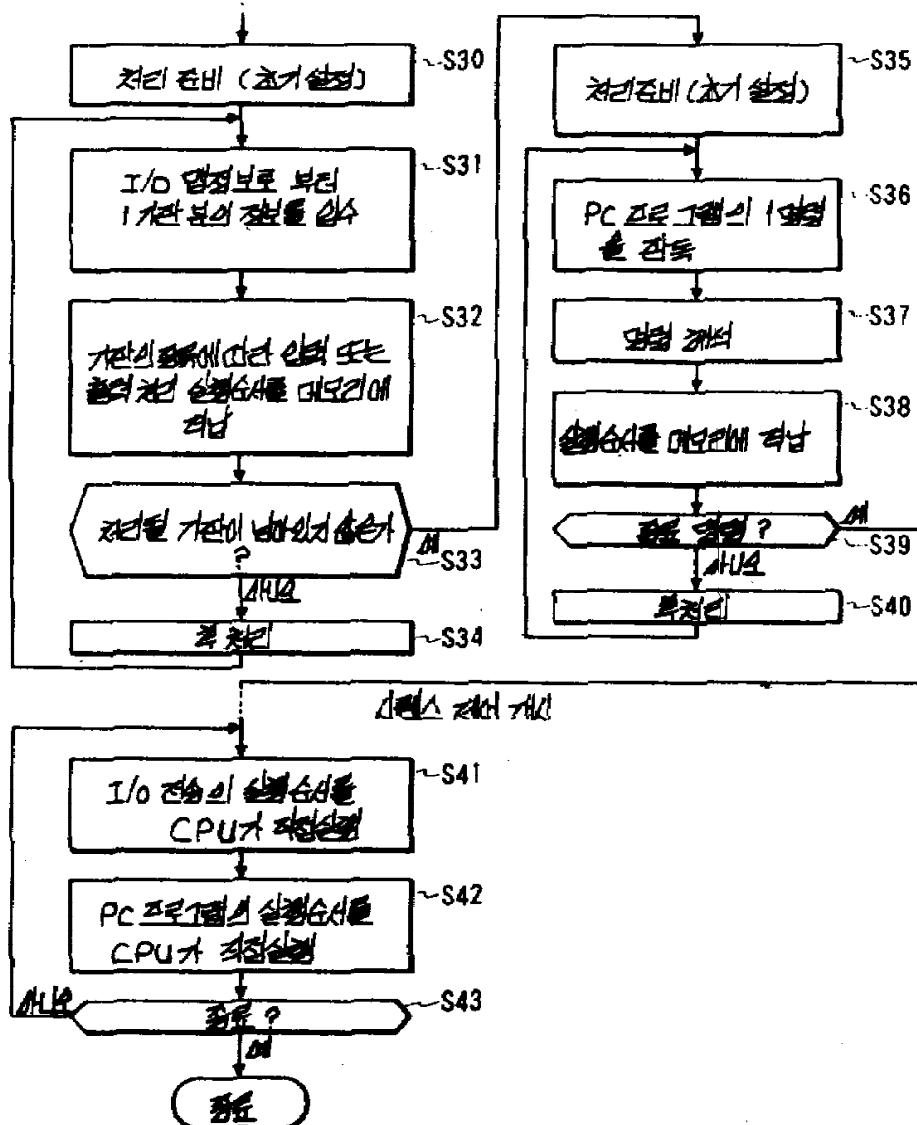

제1도는 제2도의 PC가 동작 상태에 있는 동안 수행된 처리의 상세를 도시하는 플로우챠트도이다.

먼저, PC는 I/O 전송의 실행 순서를 변환하는 처리를 수행한다. 단계(S30)에서, 처리 준비로서, I/O 맵 정보의 판독 개시 어드레스(예컨대, 선두 어드레스)의 설정을 포함하는 초기 설정이 수행된다. 그 다음, 단계(S31)에서, 상기 맵 정보의 선두 어드레스에서 위치된 1개의 회로 기판분의 정보가 RAM(4)으로부터 판독된다. 단계(S32)에서, 회로 기판의 종류에 따라서, 입력 처리 실행 순서 또는 출력 처리 실행 순서는 CPU(1)에 의해서 직접 실행될 수 있는 기계어 프로그램의 형태로 작성되고, RAM(3)의 사용자 프로그램 영역 이외의 영역에 격납된다. 또한, 단계(S32)에서, 처리될 회로 기판이 전혀 없다면, 후처리의 실행 순서는 CPU(1)에 의해서 직접 실행될 수 있는 기계어 프로그램 형태로 작성되고, 입력 처리 실행 순서의 상기에서 작성된 기계어 프로그램 후의 어드레스에 격납된다. 상기 후처리는, 예컨대, 점프 명령에 의해서 메인 루틴으로 되돌아가는 처리나 또는 그다음에 액세스될 어드레스를 특정하는 처리이다. 그다음, 단계(S33)에서, 처리될 회로 기판이 전혀 없는지의 여부를 판단한다. 만약, 회로 기판(또는 기판들)이 남아 있다고 판단되었다면, 단계(S34)에서, I/O 맵 정보의 판독 어드레스와 실행 순서의 격납 어드레스를 갱신하도록 후처리가 수행되고, 그 처리는 단계(S31)로 되돌아간다. 상기 처리는 모든 회로 기판이 처리될 때까지, 즉, 단계(S33)의 판단이 긍정적으로 될 때까지 반복된다.

다음에, PC는 PC 프로그램을 변환시키는 처리를 수행한다. 단계(S35)에서, 처리 준비로서, RAM(3)에 격납된 PC 프로그램의 판독 개시 어드레스의 설정과, 현재 변환되어지고 RAM(3)에 격납될 실행 순서의 격납 개시 어드레스의 설정을 포함하는 초기 설정이 수행된다. 그 다음에, PC 프로그램의 선두에 위치된 1명령이 단계(S36)에서 RAM(3)으로부터 판독되고, 단계(S37)에서 해석된다. 단계(38)에서,

상기 명령의 실행 순서는 CPU(1)에 의해서 직접 실행될 수 있는 기계어 프로그램으로 변환되고, 상술한 I/O 전송 실행순서 이후의 RAM(3)의 어드레스에 격납된다. 또한, 단계(S38)에서, 만약, 상기 명령이 종료 명령이라면, 후처리 실행 순서는 CPU(1)에 의해서 직접 실행될 수 있는 기계어의 형태로 작성되고, 사전 명령의 기계어 프로그램 이후의 어드레스에 차례로 격납된다.

상기 후처리는 예컨대, 점프 명령에 의해서 메인 루틴으로 되돌아가는 처리이다, 그 다음, 단계(S39)에서 상기 명령이 종료 명령인지의 여부가 판단된다. 만약, 종료 명령이 아니라면, PC 프로그램의 판독 어드레스와 실행 순서의 격납 어드레스를 갱신하도록 단계(S40)에서 후처리가 수행되고, 그 처리는 단계(S36)으로 되돌아간다. 상기 처리는 종료 명령(프로그램 완료 명령)이 판독될 때까지, 즉 단계(S39)의 판단이 긍정적으로 될 때까지 반복된다.

상기 처리의 실행후, I/O 전송 처리의 실행 순서 및 PC 프로그램은 CPU(1)에 의해서 직접 실행될 수 있는 기계어 프로그램(목적 프로그램), (3b 및 3c)로 변환되어지고 제4도에 도시된 바와같이, RAM(3)에 격납된다.

시컨스 제어가 개시될 때, 단계(S41)에서, CPU(1)는 I/O 전송 처리의 실행 순서가 격납되어 있는 RAM(3)의 어드레스를 액세스하고 입력 또는 출력 처리를 수행하도록 그들의 기계어 프로그램을 직접 실행한다. I/O 전송 실행 순서의 모든 기계어 프로그램의 실행 후, 단계(S42)에서, CPU(1)는 PC 프로그램의 실행 순서가 격납되어 있는 어드레스를 액세스하고 PC 프로그램의 연산 처리를 수행하도록 그들의 기계어 프로그램을 직접 실행한다. 상기 I/O 전송 처리와 PC 프로그램의 연산 처리는 종료 명령이 내려질 때까지, 즉, 단계(S43)의 판단이 긍정적으로 될 때까지 반복적으로 수행된다.

상술한 실시예에서 있어서, 단계(S32)에서, 회로 기판이 전혀 남아있지 않았을 때, 후처리 실행 순서는 기계어 프로그램의 형태로 작성된다. 대안적으로, 단계(S33)의 긍정적인 판단후에 작성될 수도 있다. 유사하게, 단계(S38)의 경우에서도, 후처리 실행 순서는 상기 명령이 단계(S39)에서 종료 명령이 판단되어진후 기계어 프로그램의 형태로 작성될 수도 있다.

상기 실시예에서, I/O 전송 처리와 PC 프로그램 연산 처리의 실행 순서가 기계어 프로그램으로 변환되어지는 동안, 상기 2개의 처리중 1개만의 실행 순서가 기계어 프로그램으로 변환될 수도 있다. 후자의 경우에는 언제든지, 처리 속도가 종래의 제어 방법과 비교하여 개선될 수 있다. 또한, 이들 양쪽의 처리의 실행 순서가 기계어로 변환되는 경우에서, 양쪽의 처리중 실행 순서를 변환하는 순서는 제1도의 순서로 한정되는 것은 아니며, 제1도의 순서와 역으로 될 수도 있다.

상술한 바와같이, 본 발명에 의하면, 한쪽 또는 양쪽의 I/O 전송 처리 및 PC 프로그램 연산 처리의 실행 순서는 기계어 프로그램(목적 프로그램)으로 미리 변환되고 그 다음에 실제로 실행된다. 그 결과로서, PC의 처리 속도가 개선될 수 있다. PC가 CPU 및 메모리 장치로 구성될 수 있고 특별히 설계된 하드웨어가 필요로 되지 않기 때문에, 본 발명은 염가적으로 실현될 수 있다.

### (57) 청구의 범위

#### 청구항 1

입출력 전송 처리 및 프로그램가능 제어기의 프로그램의 연산 처리를 구비하는 시컨스 제어 처리가 순환적으로 수행되는 프로그램가능 제어기의 제어 방법에 있어서, 중앙처리장치에 의해서 직접 실행될 수 있는 기계어 프로그램의 형태로 입출력 전송 처리의 실행 순서를 작성하는 단계와, 상기 기계어 프로그램을 메모리 장치에 격납하는 단계와, 상기 격납된 기계어 프로그램을 기초로 하여 상기 중앙처리장치에 의해서 순환적으로 시컨스 제어 처리를 수행하는 단계를 포함하는 것을 특징으로 하는 프로그램가능 제어기의 제어방법.

#### 청구항 2

입출력 전송 처리 및 프로그램가능 제어기의 프로그램의 연산 처리를 구비하는 시컨스 제어 처리가 순환적으로 수행되는 프로그램가능 제어기의 제어 방법에 있어서, 중앙처리장치에 의해서 직접 실행될 수 있는 기계어 프로그램의 형태로 프로그램가능 제어기의 프로그램의 실행 순서를 작성하는 단계와, 상기 기계어 프로그램을 메모리 장치에 격납하는 단계와, 상기 격납된 기계어 프로그램을 기초로 하여 중앙처리장치에 의해서 순환적으로 시컨스 제어 처리를 수행하는 단계를 포함하는 것을 특징으로 하는 프로그램가능 제어기의 제어 방법.

#### 청구항 3

입출력 전송 처리 및 프로그램가능 제어기 프로그램의 연산 처리를 구비하는 시컨스 제어 처리가 순환적으로 수행되는 프로그램가능 제어기의 제어 방법에 있어서, 중앙처리장치에 의해서 직접 실행될 수 있는 각각의 기계어 프로그램의 형태로 입출력 전송 처리 및 프로그램가능 제어기 프로그램의 실행 순서를 작성하는 단계와, 상기 기계어 프로그램을 메모리 장치에 격납하는 단계와, 상기 격납된 기계어 프로그램을 기초로 하여 중앙처리장치에 의해서 순환적으로 시컨스 제어 처리를 수행하는 단계를 포함하는 것을 특징으로 하는 프로그램가능 제어기의 제어 방법.

#### 청구항 4

제1항에 있어서, 상기 작성 단계는 기계어 프로그램의 일부분으로서 프로그램 가능 제어기 프로그램의 연산 처리 및 입출력 전송 처리의 후처리의 실행 순서를 작성하는 단계를 구비하는 것을 특징으로 하는 프로그램가능 제어기의 제어 방법.

#### 청구항 5

제2항에 있어서, 상기 작성 단계는 기계어 프로그램의 일부분으로서 프로그램 가능 제어기 프로그램의 연산 처리 및 입출력 전송 처리의 후처리의 실행 순서를 작성하는 단계를 구비하는 것을 특징으로 하는 프로그램가능 제어기의 제어 방법.

로 하는 프로그램가능 제어기의 제어 방법.

### 청구항 6

제3항에, 있어서, 상기 작성 단계는 기계어 프로그램의 일부분으로서 프로그램 가능 제어기 프로그램의 연산 처리 및 입출력 전송 처리의 후처리의 실행 순서를 작성하는 단계를 구비하는 것을 특징으로 하는 프로그램가능 제어기의 제어 방법.

### 도면

#### 도면1

도면2

도면3

| 기반 프로그램 |    | 점수 |

|---------|----|----|

| 슬롯 1    | 입력 | 8  |

| 슬롯 2    | 출력 | 8  |

| ~       | ~  | ~  |

| 슬롯 n    | 출력 | 8  |

| 종료 코드   |    |    |

도면4

도면5

도면6

도면7