(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-33381

(P2006-33381A)

(43) 公開日 平成18年2月2日(2006.2.2)

(51) Int.CI.

HO4N 5/335 (2006.01)

F 1

HO4N 5/335

HO4N 5/335

テーマコード(参考)

5C024

Z

E

審査請求 未請求 請求項の数 11 O L (全 13 頁)

(21) 出願番号

特願2004-208878 (P2004-208878)

(22) 出願日

平成16年7月15日 (2004.7.15)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(72) 発明者 宮成 洋

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内F ターム(参考) 5C024 CX47 CX54 CX61 GY31 HX02

HX58

(54) 【発明の名称】撮像装置及び制御方法

## (57) 【要約】

【課題】 動画撮影時のダイナミックレンジを拡大すること。

【解決手段】 画素が2次元に配置されたCMOSセンサ(69)と、動画撮影時に、前記CMOSセンサを、少なくとも1行おきに画素信号を読み出す走査を複数回行うことにより、前記CMOSセンサから1画面分の画素信号を読み出すと共に、各走査毎に異なる行を走査し、且つ、電荷蓄積時間が異なるように前記CMOSセンサを駆動制御する制御手段(71、74)と、前記各走査毎に読み出された画素信号を記憶する画像メモリ(72)と、前記画像メモリに記憶された画素信号を用いて、ダイナミックレンジを拡大するダイナミックレンジ拡大手段(73、74)とを有する。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

画素が2次元に配置された撮像手段と、

動画撮影時に、前記撮像手段を、少なくとも1行おきに画素信号を読み出す走査を複数回行うことにより、前記撮像手段から1画面分の画素信号を読み出すと共に、各走査毎に異なる行を走査し、且つ、電荷蓄積時間が異なるように前記撮像手段を駆動制御する制御手段と、

前記各走査毎に読み出された画素信号を記憶する記憶手段と、

前記記憶手段に記憶された画素信号を用いて、ダイナミックレンジを拡大するダイナミックレンジ拡大手段と

を有することを特徴とする撮像装置。

**【請求項 2】**

前記撮像手段はC M O S センサであって、前記制御手段は、スリットローリングシャッター方式により前記C M O S センサを駆動制御することを特徴とする請求項1に記載の撮像装置。

**【請求項 3】**

前記ダイナミックレンジ拡大手段は、

前記記憶手段に記憶された1画面分の画素信号のうち、所定回目の走査により得られた画素信号と所定の閾値とを比較し、前記閾値を超える画素信号を有する画素を検出する検出手段と、

前記閾値を超える画素信号が検出された場合に、検出された画素に隣接し、且つ、異なる走査で得られた画素信号を用いて、前記閾値を超えた画像信号の代わりに用いる代替画素信号を演算する演算手段と、

前記閾値を超える画素信号を、前記演算手段により得られた代替画素信号に置き換える置き換え手段とを有し、

前記閾値は、画素が飽和した状態で得られる画素信号値より所定値分小さい値であることを特徴とする請求項1または2に記載の撮像装置。

**【請求項 4】**

前記置き換え手段による画素信号の置き換え後、前記所定回目の走査により得られた画素信号を前記複数回ずつ出力する出力手段を更に有することを特徴とする請求項3に記載の撮像装置。

**【請求項 5】**

前記制御手段は1行おきに2回走査を行い、前記所定回目の走査は電荷蓄積時間が長い方の走査であって、前記演算手段は、検出された画素に隣接し、且つ、異なる走査で得られた画素信号を電荷蓄積時間に応じて増幅することにより、画素信号値を算出することを特徴とする請求項3に記載の撮像装置。

**【請求項 6】**

前記制御手段は2行おきに3回走査を行い、前記所定回目の走査は電荷蓄積時間が中間の走査であって、前記検出手段は更に、所定の第2の閾値と前記所定回目の走査により得られた画素信号とを比較して、前記第2の閾値を下回る画素信号値を有する画素を検出し、

前記演算手段は、前記閾値を超える画素信号値が検出された場合に、検出された画素に隣接し、且つ、電荷蓄積時間が短い走査により得られた画素信号を電荷蓄積時間に応じて増幅することにより代替画素信号値を算出し、また、前記第2の閾値を下回る画素信号値が検出された場合に、検出された画素に隣接し、且つ、電荷蓄積時間が長い走査により得られた画素信号を電荷蓄積時間に応じて削減することにより代替画素信号値を算出することを特徴とする請求項3に記載の撮像装置。

**【請求項 7】**

ダイナミックレンジの拡大を行って動画を撮影する第1のモードと、ダイナミックレンジの拡大を行わずに動画を撮影する第2のモードとを設定する設定手段を更に有し、

10

20

20

30

40

50

前記第1のモードが設定された場合に、前記制御手段、記憶手段、ダイナミックレンジ制御手段の動作を行うことを特徴とする請求項1乃至6のいずれかに記載の撮像装置。

【請求項8】

スリットローリングシャッター方式での画素リセットを全フレームで行うことを特徴とする請求項2に記載の撮像装置。

【請求項9】

画素が2次元に配置された撮像手段を有する撮像装置の制御方法であって、

動画撮影時に、前記撮像手段を、少なくとも1行おきに画素信号を読み出す走査を複数回行うことにより、前記撮像手段から1画面分の画素信号を読み出すと共に、各走査毎に異なる行を走査し、且つ、電荷蓄積時間が異なるように前記撮像手段を駆動制御する制御工程と、

前記各走査毎に読み出された画素信号を記憶する記憶工程と、

前記記憶手段に記憶された画素信号を用いて、ダイナミックレンジを拡大するダイナミックレンジ拡大工程と

を有することを特徴とする制御方法。

【請求項10】

請求項9に記載の制御方法を実現するためのプログラムコードを有することを特徴とする情報処理装置が実行可能なプログラム。

【請求項11】

請求項10に記載のプログラムを記憶したことを特徴とする情報処理装置が読み取り可能な記憶媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はデジタルカメラ等で固体撮像素子としてCMOSセンサの動画撮影時の信号読み出しに関し、特に、動画撮影時のダイナミックレンジの拡大に関するものである。

【背景技術】

【0002】

従来、撮像装置において、CMOSセンサを固体撮像素子として用いたものがある（例えば、特許文献1及び2参照）。撮像装置が機械的な遮光部材であるメカニカルシャッタを有する場合、静止画撮影時にはメカニカルシャッタによりCMOSセンサを遮光し、遮光した状態で全画素のリセットを行ってから適切な露光量となるようにシャッタを開いてCMOSセンサを露光し、所定時間後にシャッタを閉じてから信号読み出しを行うことにより、静止画を撮影することができる。しかしながら、メカニカルシャッタの駆動速度には限界があるため、より短秒時の露光を行う場合は、メカニカルシャッタを用いずに電子シャッタ機能を用いて実現する。なお、その際にはメカニカルシャッタを開き、CMOSセンサが常に露光されている状態にしておく。

【0003】

まず、画素又はライン毎に、画素に蓄積された不要電荷を除去する走査すなわちリセット走査を実行し、その後、画素又はライン毎に、それぞれ所定の時間を経過してから信号電荷を読み出す走査を行うことで電子シャッタ動作を実現することができる。このような電子シャッタを、以下、「ローリング電子シャッタ」と呼ぶ。

【0004】

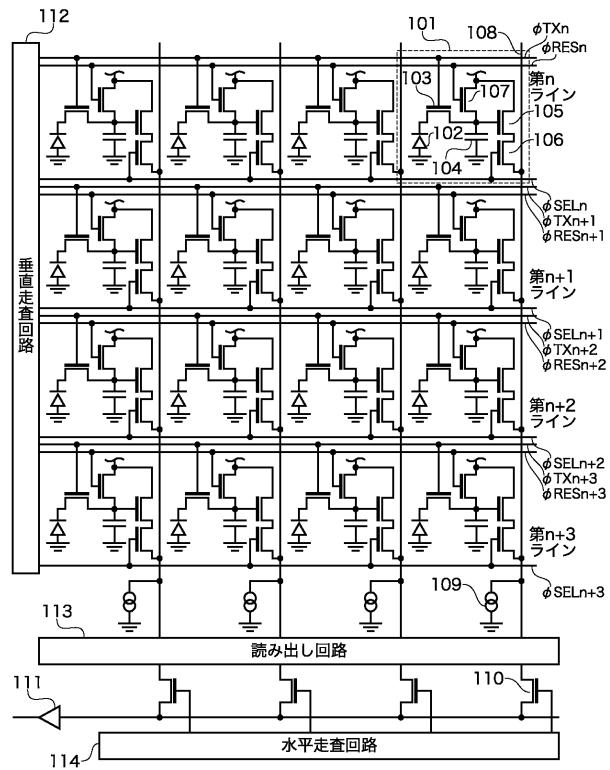

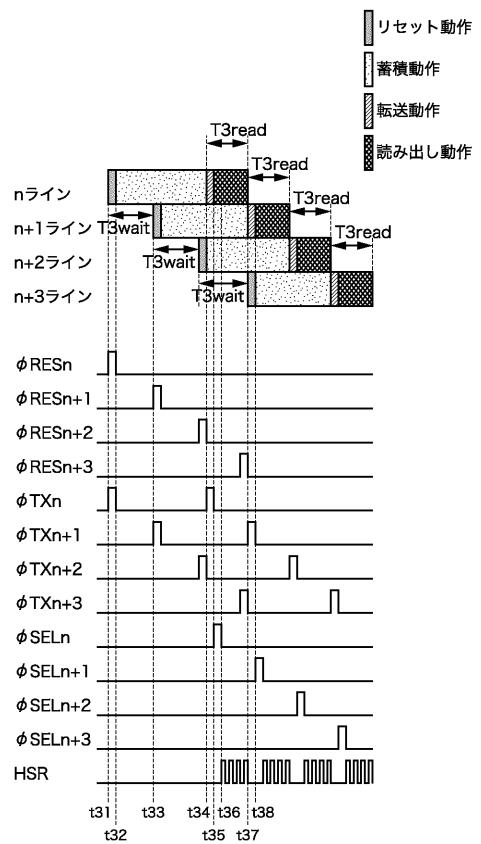

図7は従来のXYアドレス型の走査方法を採るCMOSセンサの概略構成例を示す回路図、図8は従来の電子シャッタを実現するためのCMOSセンサの駆動方法を示すタイミングチャートである。

【0005】

図7はXYアドレス型の走査方法を採る撮像素子の構成を示したものである。図7において、101は単位画素である。なお、図7では図の簡略化のために、画素101を4行×4列のみ示しているが、実際には非常に多数（例えば、数百万）の画素101が2次元

10

20

30

40

50

に配置されている。また、102は光を電荷に変換するフォトダイオード(PD)、103は転送パルスTXによってPD102で発生した電荷を後述する蓄積領域(フローティングデフェュージョン:FD)に転送する転送スイッチ、104は電荷を一時的に蓄積しておく蓄積領域(FD)であり、105はソースフォロアとして機能する増幅MOSアンプである。106は選択パルスSELによって画素を選択する選択スイッチであり、107はリセットパルスRESによってFD104に蓄積された電荷を除去するリセットスイッチである。FD104、増幅MOSアンプ105、及び後述する定電流源109でフローティングディフェュージョンアンプが構成され、選択スイッチ106で選択された画素の信号電荷が電圧に変換され、信号出力線108を経て読み出し回路113に出力される。109は増幅MOSアンプ105の負荷となる定電流源である。110は読み出し回路113から出力信号を選択する選択スイッチであり、水平走査回路114によって駆動される。111は信号を撮像素子外部に出力するための出力アンプである。また、112はスイッチ103、106、107を選択するための垂直走査回路(シフトレジスタ)である。

10

#### 【0006】

なお、パルス信号TX、RES、SELそれぞれについて、垂直走査回路112によって走査選択された、例えばn番目の走査ラインに印加するパルス信号をTXn、RESn、SELnと記述する。

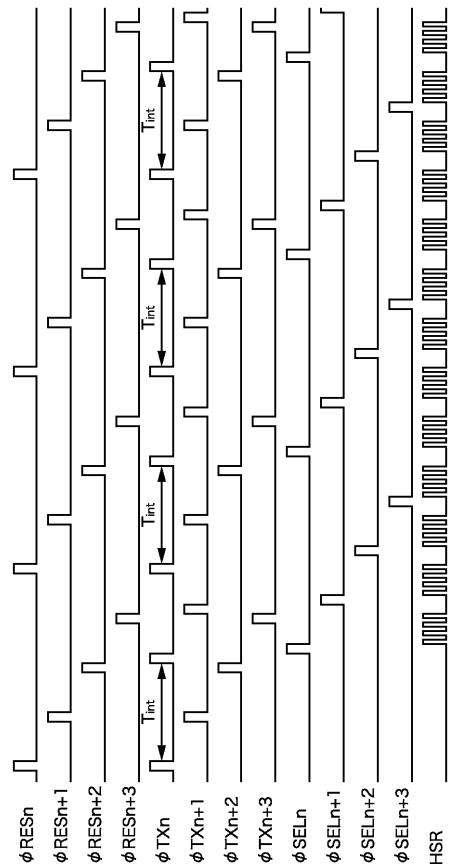

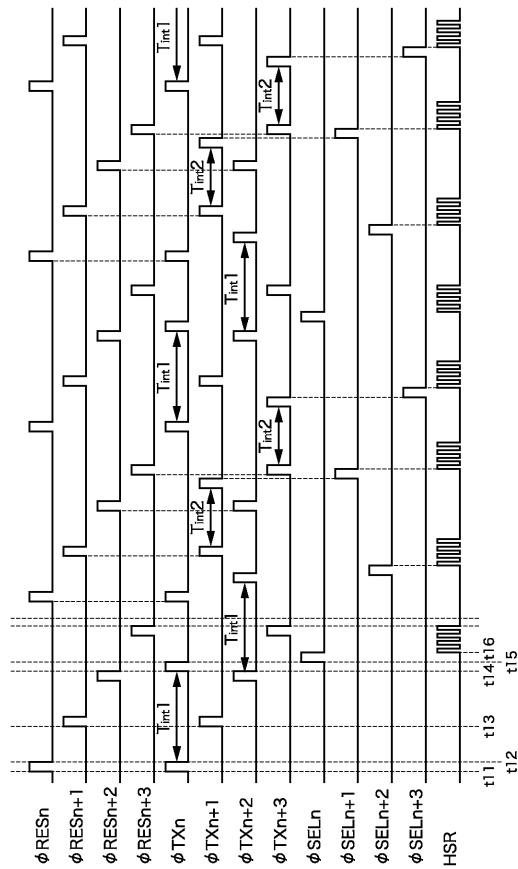

#### 【0007】

図8はローリング電子シャッタ動作における駆動パルスと動作シーケンスを示したものである。なお図8では説明を簡略にするために垂直走査回路112によって走査選択されたnラインからn+3ラインの4行分の駆動制御に関して記述する。

20

#### 【0008】

nラインにおいて、まず時刻t31からt32の期間、RESnとTXnを印加して、転送スイッチ103及びリセットスイッチ107をオンにし、nライン目のPD102とFD104に蓄積されている不用電荷を除去するリセット動作を行う。時刻t32で転送スイッチ103がオフになり、PD102で発生した光電荷が蓄積される蓄積動作が開始される。次に時刻t34においてTXnを印加して、転送スイッチ103をオンにし、PD102に蓄積された光電荷をFD104に転送する転送動作を行う。なお、リセットスイッチ107は、この転送動作に先んじてオフする必要があり、図8に示す駆動制御では、時刻t32で転送スイッチ103と同時にオフにしている。上述したように、リセット動作終了の時刻t32から、転送終了の時刻t35までが蓄積時間となる。

30

nライン目の転送動作終了後、SELnを印加して選択スイッチ106をオンにすることにより、FD104に保持した電荷が電圧に変換され、読み出し回路113に出力される。読み出し回路113で一時的に保持された信号が水平走査回路112によって時刻t36より順次出力される。時刻t34の転送開始から時刻t37の読み出し終了までの時間をT3readとし、時刻t31から時刻t33までの時間をT3waitとする。他のラインにおいても同様に、転送開始から読み出し終了までの時間がT3readとなり、あるラインのリセット開始から次のラインのリセット開始までの間の時間がT3waitとなる。

40

#### 【0009】

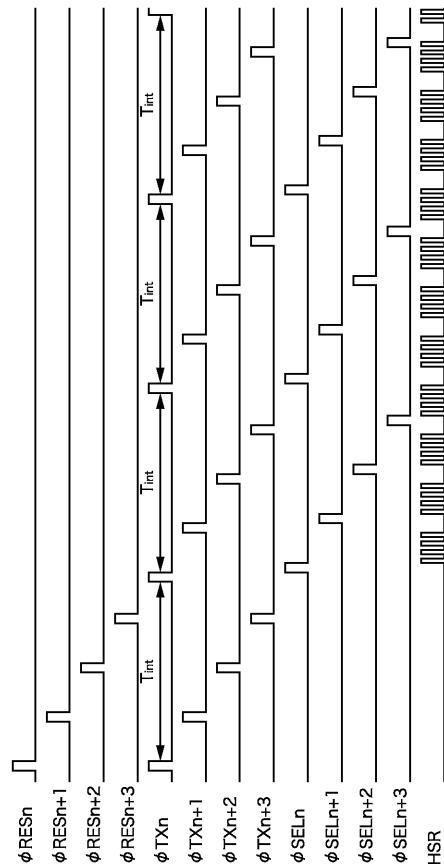

上記記載の駆動方法によるローリング電子シャッタでは静止画を撮影可能であるが、図9に示すように、リセットに続く2回目のTXn+3及びSELn+3印加後、リセットを行わずにTXn～TXn+3、SELn～SELn+3の信号を繰り返し印加することで、信号読み出しの間隔を蓄積時間Tintとする動画像用の信号を得ることができる。

#### 【0010】

また、CMOSセンサの構成/駆動方法の別の文献としては特許文献1、2等がある。

#### 【0011】

一方、撮像装置が高解像モードと通常モードとを有し、高解像度モード時にはプログレ

50

ツシップスキャンを行って全画素を読み出し、通常モードではインターレーススキャンを行って画素加算または画素間引きによりリアルタイムなビデオ信号を出力することを可能にした撮像装置が提案されている（例えば、特許文献3参照）。

#### 【0012】

またこのような比較的高速なフレームレートで読み出しても偽信号が発生しないようにする提案も行われている（例えば、特許文献4参照）。

#### 【0013】

【特許文献1】特開2000-201300号公報

【特許文献2】特開2002-209144号公報

【特許文献3】特開平7-298111号公報

10

【特許文献4】特開2000-134550号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0014】

しかし、ローリング電子シャッタでは動画像撮影時の1フレームの蓄積時間 $T_{int}$ は上述したように信号読み出しの間隔となり、被写体の輝度に関わらず固定であるので、適正露出範囲が狭くなってしまう。そこで信号読み出し前に一旦画素をリセットすることで蓄積時間を制御することのできるスリットローリングシャッターという信号読み出し方法がある。このタイミングチャートを図10に示す。図10に示すように、蓄積した信号を読み出した後、所定時間後に一旦信号をリセットすることで、蓄積時間 $T_{int}$ を読み出し間隔よりも短くすることができる。これは1フレームの蓄積時間を1水平ライン走査時間単位で制御できるので、被写体輝度が高い場合は有効な露出制御である。

20

#### 【0015】

しかしながら、スリットローリングシャッターでは全画面一様で且つ被写体輝度の明るい場合には露出の対応ができるが、1画面内に暗い部分と明るい部分が混在する場合には、例えば、主被写体を適正露出に制御できたとしても、その他は飽和したり、暗くなってしまうという問題がある。

#### 【0016】

本発明は上記問題点を鑑みてなされたものであり、動画撮影時のダイナミックレンジを拡大することを目的とする。

30

#### 【課題を解決するための手段】

#### 【0017】

本発明の撮像装置は、画素が2次元に配置された撮像手段と、動画撮影時に、前記撮像手段を、少なくとも1行おきに画素信号を読み出す走査を複数回行うことにより、前記撮像手段から1画面分の画素信号を読み出すと共に、各走査毎に異なる行を走査し、且つ、電荷蓄積時間が異なるように前記撮像手段を駆動制御する制御手段と、前記各走査毎に読み出された画素信号を記憶する記憶手段と、前記記憶手段に記憶された画素信号を用いて、ダイナミックレンジを拡大するダイナミックレンジ拡大手段とを有する。

#### 【0018】

また、画素が2次元に配置された撮像手段を有する撮像装置の本発明の制御方法は、動画撮影時に、前記撮像手段を、少なくとも1行おきに画素信号を読み出す走査を複数回行うことにより、前記撮像手段から1画面分の画素信号を読み出すと共に、各走査毎に異なる行を走査し、且つ、電荷蓄積時間が異なるように前記撮像手段を駆動制御する制御工程と、前記各走査毎に読み出された画素信号を記憶する記憶工程と、前記記憶手段に記憶された画素信号を用いて、ダイナミックレンジを拡大するダイナミックレンジ拡大工程とを有する。

40

#### 【発明の効果】

#### 【0019】

本発明によれば、動画撮影時のダイナミックレンジを拡大することができる。

#### 【発明を実施するための最良の形態】

50

## 【0020】

以下、添付図面を参照して本発明を実施するための最良の形態を詳細に説明する。

## 【0021】

<第1の実施形態>

(撮像装置の構成)

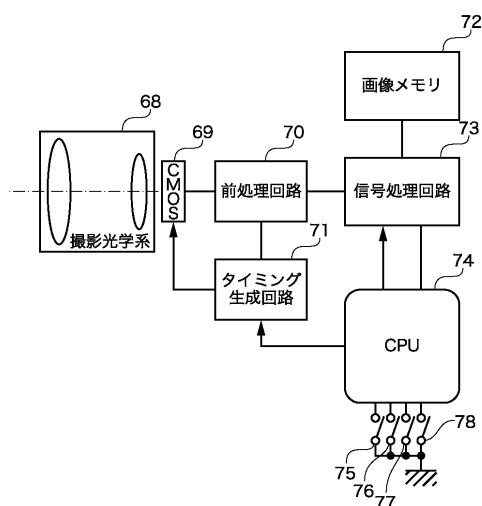

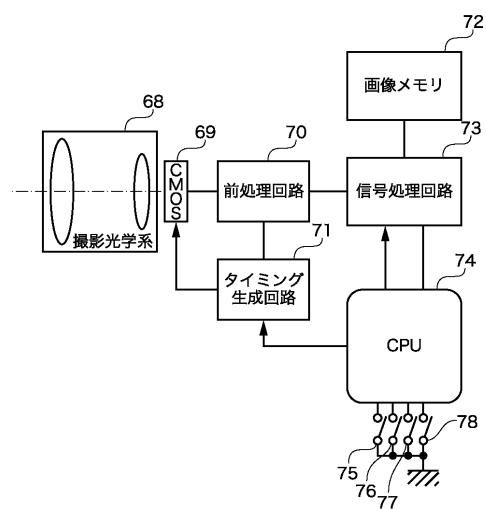

本発明の第1の実施形態における撮像装置の概略構成を図1に示す。

## 【0022】

図1において、73は主たる計算モジュールである信号処理回路、72は複数フレームの撮像信号を格納可能な容量を有する画像メモリ、74はCPUで、信号処理回路73の制御、タイミング生成回路71の制御および撮像シーケンスの制御を行う。

10

## 【0023】

68は撮影光学系、69はイメージセンサであるCMOSセンサである。本第1の実施形態では、図7に示すものと同様の構成のCMOSセンサをCMOSセンサ69として用いるものとし、ここでは説明を省略する。但し、図7でも説明したように、説明を分かりやすくするために4行×4列のみ示しているが、実際には実際には非常に多数(例えば、数百万)の画素101が2次元に配置されている。70は前処理回路でCMOSセンサ69の出力をA/D変換し、CMOSセンサ69が有する固定パターンノイズ等の補正処理を行う。CMOSセンサ69の駆動タイミングはタイミング生成回路71で生成される。

## 【0024】

また、75は動画撮影モードと静止画撮影モードとを切り換えるための動画/静止画切替スイッチ(SW)、76は撮影開始を指示する撮影開始スイッチ(SW)で、動画撮影モード時には撮影終了を指示する機能も兼ねており、撮影開始後、再度撮影開始SW76が操作されると、撮影を終了する。77と78はダイナミックレンジ切替選択SWで、日中や夜景及び室内等の撮影に応じて選択するSWであり、例えば室内での撮影が選択された場合に、後述するように電荷蓄積時間の組み合わせを変更することによりダイナミックレンジが広がるように設定する。なお、このダイナミックレンジの切り換えは、ホワイトバランスの切替と連動させてもよい。

20

## 【0025】

(CMOSセンサの読み出し制御)

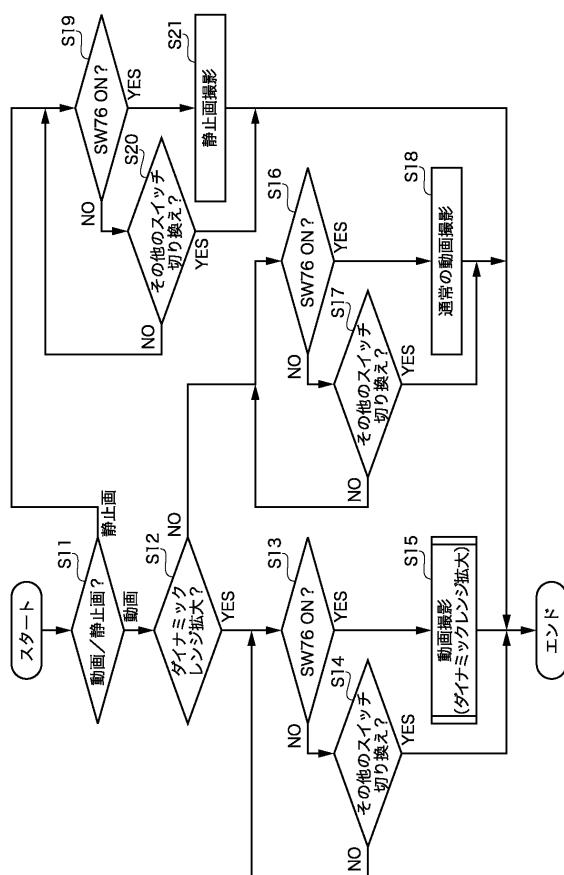

次に、本第1の実施形態における上記構成を有する撮像装置による露光及び読み出し制御のための全体処理について、図2を参照して説明する。

30

## 【0026】

まず、ステップS11において、CPU74は動画/静止画切り替えスイッチSW75の状態を確認し、静止画の場合にはステップS19に進む。

## 【0027】

動画の場合にはステップS12に進み、CPU74はダイナミックレンジ切り替えスイッチ77及び/または78の操作によりダイナミックレンジ拡大が選択されているかどうかを判断する。ダイナミックレンジ拡大が選択されていなければ、ステップS16に進み、ダイナミックレンジ拡大が選択されている場合にはステップS13に進む。

40

## 【0028】

ステップS13、S16、S19それぞれにおいて、撮影開始SW76がONされたかどうかを判断し、ONされると、それぞれステップS15、S18、S21に進む。ステップS15では、本発明の第1の実施形態の特徴である、フレーム毎に蓄積時間を変更して撮影を行うことにより、ダイナミックレンジを拡大した動画を撮影する。また、ステップS18では、通常のスロットローリングシャッター方式による動画の撮影を行い、ステップS21では公知の露光・読み出し制御により静止画の撮影を行う。

## 【0029】

一方、S13、S16、S19において撮影開始SW76がONされていない場合にはそれぞれステップS14、S17、S20に進み、その他のスイッチ75、77、78が操作されたかどうかを判断し、操作されていなければ、ステップS13、S16、S19

50

に戻る処理を繰り返し、撮影開始 SW76 が ONされるのを待つ。また、スイッチ 75、77、78 が操作されると処理を終了し、改めてステップ S11 からの処理が開始される。

### 【0030】

次に、ステップ S15 で行われる、本発明の第1の実施形態におけるダイナミックレンジ拡大した動画を撮影するための露光及び読み出し制御について説明する。本第1の実施形態では、スロットローリングシャッター方式で読み出しを行い、フレーム毎に偶数行と奇数行とを交互に読み出し、かつ、偶数行と奇数行とで電荷を蓄積する時間を異ならすことにより、ダイナミックレンジの拡大を実現する。以下、そのための CMOS センサの駆動方法について、図3及び図7を参照して詳しく説明する。

10

### 【0031】

まず、n ラインにおいて、時刻 t11 から t12 の期間、RESn と TXn を印加して、転送スイッチ 103 及びリセットスイッチ 107 をオンにし、n ライン目の PD102 と FD104 に蓄積されている不用電荷を除去するリセット動作を行う。時刻 t12 で転送スイッチ 103 がオフになると、PD102 で発生した光電荷が蓄積される蓄積動作が開始される。次に所定時間 Tint1 経過後の時刻 t14 において TXn を印加して、転送スイッチ 103 をオンにし、PD102 に蓄積された光電荷を FD104 に転送する転送動作を行う。なお、リセットスイッチ 107 は、この転送動作に先んじてオフする必要があり、図3に示す駆動制御では、時刻 t12 で転送スイッチ 103 と同時にオフしている。上述したように、リセット動作終了の時刻 t12 から、転送終了の時刻 t15 までが蓄積時間となる。

20

### 【0032】

n ライン目の転送動作終了後、SELn を印加して選択スイッチ 106 をオンにすることにより、FD104 に保持した電荷が電圧に変換され、読み出し回路 113 に出力される。読み出し回路 113 で一時的に保持された信号が水平走査回路 112 によって時刻 t16 より順次出力される。

### 【0033】

一方、TXn を印加後、所定時間後 t13 に次の行である n+1 ライン目に対して、RESn+1 と TXn+1 を印加し、n+1 ライン目の PD102 と FD104 に蓄積されている不用電荷を除去するリセット動作を行う。TXn+1 がローになり、転送スイッチ 103 がオフになると、n+1 ライン目の PD102 における蓄積動作が開始されることになる。

30

### 【0034】

n ライン目では、所定時間 Tint1 経過後に転送スイッチ 103 をオンにして蓄積された光電荷を FD104 に転送したが、n+1 ライン目の信号は1フレーム目では読み出さないため、TXn+1 及び SELn+1 はローに保ち、FD104 への転送も、読み出し回路 113 への転送も行わない。

### 【0035】

同様に、TXn+2 を印加後、所定時間後に TXn+2 を、更に所定時間後に TXn+3 を印可するが、n+2 ライン目は読み出すので所定時間 Tint1 後に更に TXn+2 及び SELn+2 の印加して、水平転送を行うが、n+3 ライン目は読み出さないので、TXn+3 及び SELn+3 の印加を行わない。

40

### 【0036】

上記制御により、奇数ラインの信号を所定の蓄積時間（正確には SEL のパルス幅分の時間が異なるが、便宜上 Tint1 と記す。）で読み出すことができる。

### 【0037】

次に、偶数ラインの信号の読み出しを行う。先のフレームで RESn+3 の印加後、所定時間毎に再び RESn~n+3 と TXn~n+3 を順次出力し、各行のリセット動作を行う。このフレームでは、n 行目の読み出しを行わないので、RESn+1 及び TXn+1 の印加後、Tint1 よりも短い所定時間 Tint2 の経過後に再び TX

50

$n + 1$  を印加して転送スイッチ 103 をオンにし、PD102 に蓄積された光電荷を FD104 に転送する転送動作を行う。

【0038】

$n + 1$  ライン目の転送動作終了後、SEL $n + 1$  を印加して選択スイッチ 106 をオンにすることにより、FD104 に保持した電荷が電圧に変換され、読み出し回路 113 に出力される。読み出し回路 113 で一時的に保持された信号が水平走査回路 112 によって時刻 t16 より順次出力される。

【0039】

以下、 $n + 2$  ライン目の電荷は読み出さず、 $n + 3$  ライン目の電荷を読み出すようする。

【0040】

上記制御により、偶数ラインの信号を、蓄積時間 Tint1 よりも短い蓄積時間（正確には SEL のパルス幅分の時間が異なるが、便宜上 Tint2 と記す。）で読み出すことができる。

【0041】

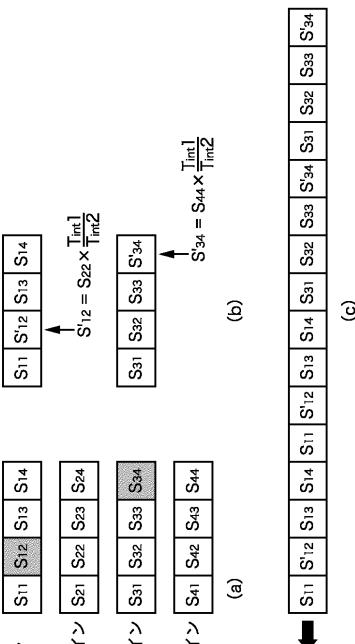

（ダイナミックレンジ拡大処理）

上記のようにして取得した奇数ラインの信号及び偶数ラインの信号は、前処理回路 70 による処理を経て画像メモリ 72 に一旦記憶され、信号処理回路 73 はこれらの信号を用いてダイナミックレンジ拡大処理を行う。図 4 はダイナミックレンジ拡大処理の概念を示す図である。

【0042】

まず、蓄積時間 Tint1 で露光した奇数ラインの信号の内、所定値 Ths を超える信号を検出する。所定値 Ths は、電荷蓄積時に飽和状態になった場合の電荷に対応する信号値であるが、若干低めに設定してもよい。所定値 Ths を超える信号が無い場合には、奇数ラインの信号を 2 回ずつ読み出す（つまり、奇数ラインの信号を 2 行分の信号として用いる）。所定値 Ths を超える信号があった場合には（図 4 (a) では、S<sub>12</sub> と S<sub>34</sub>）、偶数ラインの信号の内、その画素に対応する画素の信号値 S を読み出し（図 4 (a) では、S<sub>22</sub> と S<sub>44</sub>）、以下の式により信号値 S を增幅する。なお、Samp は、増幅後の信号値である。

$$S_{amp} = S \times (T_{int1} / T_{int2})$$

【0043】

例えば、Tint2 が Tint1 の半分の蓄積時間であった場合には、信号値 S が 2 倍にされることになる。

【0044】

このようにして増幅された信号値 Samp を、所定値 Ths を超えた信号値 S と置き換える（図 4 (b)）、置き換えた後の奇数ラインの信号を 2 回ずつ読み出して、2 行分の信号とする（図 4 (c)）。

【0045】

このようにすることにより、垂直方向の解像度は低下するが、スリットローリングシャッター方式で読み出しを行う場合であっても、ダイナミックレンジを拡大することが可能になる。近年ではセンサの画素数が大きく増加する傾向にあるので、垂直方向の解像度が半減したとしても、十分な解像度を得ることができる。

【0046】

なお、上記例では、同じ行の信号を 2 回ずつ読み出して 2 行分の信号とする場合について説明したが、出力先の解像度によっては、1 回読み出すようにしても良い。

【0047】

<第 2 の実施形態>

次に、本発明の第 2 の実施形態について説明する。

【0048】

本第 2 の実施形態は、上記第 1 の実施形態とは、ダイナミックレンジ拡大処理時の動画

撮影方法が異なる。以下、本第2の実施形態におけるダイナミックレンジ拡大処理時の動画撮影方法について、説明する。なお、本第2の実施形態における撮像装置は、図1に示す構成と同様であり、また、CMOSセンサ69も図7に示すものと同様であるため、ここでは説明を省略する。

#### 【0049】

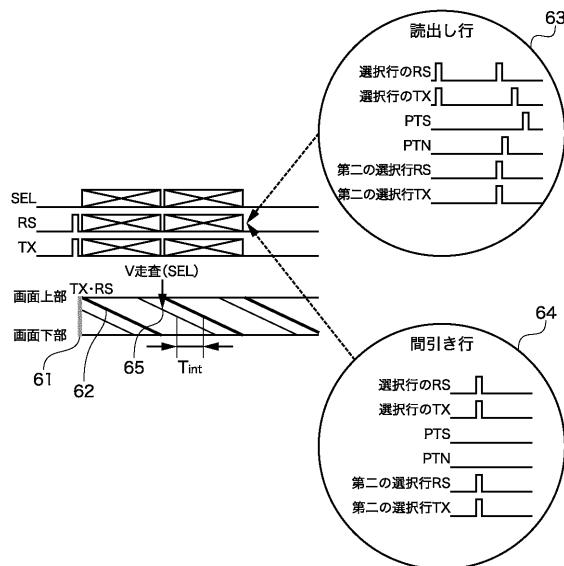

本第2の実施形態におけるCMOSのスリットローリングシャッター読出しの仕組みを図5を使って説明する。

#### 【0050】

先ず読出し行の説明をする。上部の3つの波形はそれぞれ選択信号SELとリセット信号RSと転送信号TXを表す。それぞれの信号は4, 5, 2の各nMOSトランジスタのゲート信号と考えてもよい。

#### 【0051】

その下の図形は画素101の行ごとの動作を時間軸で表したものである。59は画面上部の行を表し、60は画面下部の行を表す。61のタイミングでTXとRSをパルス状に同時にオンすることでPDとFDの一括りセットが行われ、撮影動作が開始される。62の斜線は画面上部から下部までの読出し動作を表す。65は1水平ラインの読出しにおいて、読出し前に予め先行して行われるPDとFDをリセットする画素リセット動作を表している。このタイミングは選択された行の読出し動作時に、第二の選択行に対して行われるものである。このリセット動作から読出し動作の横方向の長さが蓄積時間Tintと言うことになる。

#### 【0052】

次に間引き行の説明をする。間引き行は前述のようにPDとFDをリセットするだけなので、55のようにTXとRSを同時にオンするだけである。同時に第二の選択行のRSとTXをオンすることでPDとFDの画素部をリセットする。その行の走査読み出しありはない。

#### 【0053】

このようにして全行分繰り返し走査することで1フレームの読出しがなる。

#### 【0054】

スリットローリングシャッターは上述のような読出しのため、ローリングシャッターのように蓄積期間を読出しの間に入れることはできない。フレーム毎にリセットタイミングを変更することで前述のローリングシャッターのように同じ間引き行のフレームを組にしてそれらを組合せて読み出すことと同じになる。

#### 【0055】

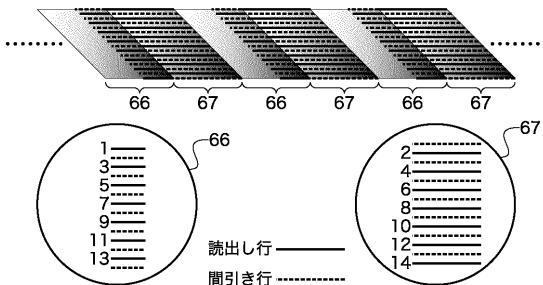

フレーム毎に間引き行を変更することで、図6のように第二のPDとFDリセットを読出しと同じフレームにせずに前の同じ間引き行のフレームの間に設定することも可能になり、フレームを超えた蓄積時間の設定も可能になる。

#### 【0056】

本発明はスリットローリングシャッターにおいてフレーム毎に垂直シフトレジスタで選択する間引き行を変更する。

#### 【0057】

これだけだと前述のように第二のPDとFDリセットと読出しによって蓄積時間は決まる。蓄積時間は最大でも読出し時間となるが、間引き行のPDとFDリセットは垂直シフトレジスタで順次選択した選択行で行わないようすれば、前フレームの第二のPDとFDリセットから現フレームの読出しまでが蓄積時間になりフレームレートを超えた蓄積時間の設定が可能になる。この場合は前フレームの読出し前に次フレームの蓄積は始まっているのでフレーム間の画像のつながりがよくなるという効果もある。

#### 【0058】

なお、上記第1及び第2の実施形態によれば、CMOSセンサ69として図7に示す構成を有する場合について説明したが、これに限るものではないことは言うまでもない。例えば、各垂直読み出しライン毎にリセットレベル(ノイズ成分)を保持する為のキャパシ

10

20

30

40

50

タ C T N と、各画素から読み出した信号を予示するためのキャパシタ C T S を設けてよい。その場合、各画素の信号読み出しに先立ってリセットレベルをキャパシタ C T N に保持しておき、読み出された信号を一旦キャパシタ C T S に保持し、信号成分とリセットレベルとの差を取ることにより、ノイズ成分をキャンセルした、各画素毎の特性に基づくばらつきを軽減した各画素信号を得ることが可能となる。

#### 【 0 0 5 9 】

また、上記第 1 及び第 2 の実施形態では、1 フレーム毎に、信号を読み出す行を奇数行と偶数行というように交互に変更したが、これに限るものではなく、たとえば、1、4、7 … 行目を 1 フレーム目に、2、5、8 … 行目を 2 フレーム目に、3、6、9 … 行目を 3 フレーム目に読み出すといったように 2 行おきの行を 1 フレームで読み出すなど、複数行おきの行を 1 フレームで読み出すようにしても良いことは言うまでもない。その場合には、上記第 1 及び第 2 の実施形態で説明した制御と同様にして、それぞれのフレーム毎に 3 種類の異なる時間となるように制御することが可能である。ただし 1 フレームの読み出しは読み出し行と間引き行が、少なくとも色再現のための情報を得られる画素セットを最小単位として行う必要がある。

#### 【 0 0 6 0 】

上記の通り、本第 1 及び第 2 の実施形態によれば、動画撮影時のダイナミックレンジを拡大することができる。

#### 【 0 0 6 1 】

また、複数の間引き行パターンで全画面を読み出すようにすれば画面内の情報の欠落を無くすことができる。

#### 【 0 0 6 2 】

更に、フレームレートを変更することなく、スリットローリングシャッター方式でダイナミックレンジを広げることができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 6 3 】

【図 1】本発明の実施の形態における撮像装置の概略構成を示すブロック図である。

【図 2】本発明の実施の形態における撮像装置の全体処理を示すフローチャートである。

【図 3】本発明の第 1 の実施形態におけるダイナミックレンジ拡大を伴った動画撮影処理を説明するためのタイミングチャートである。

【図 4】本発明の第 1 の実施形態におけるダイナミックレンジ拡大処理の概念を示す図である。

【図 5】本発明の第 2 の実施形態におけるダイナミックレンジ拡大を伴った動画撮影処理の概念を説明するためのタイミングチャートである。

【図 6】本発明の第 2 の実施形態におけるダイナミックレンジ拡大を伴った動画撮影処理の概念を説明するためのタイミングチャートである

【図 7】XY アドレス型の走査方法を探る C M O S センサの概略構成例を示す回路図である。

【図 8】従来のローリング電子シャッタ動作における静止画撮影時の駆動パルスと動作シーケンスを示すタイミングチャートである。

【図 9】従来のローリング電子シャッタ動作における動画撮影時の駆動パルスと動作シーケンスを示すタイミングチャートである。

【図 10】従来のスリットローリング電子シャッタ動作における動画撮影時の駆動パルスと動作シーケンスを示すタイミングチャートである。

#### 【 符号の説明 】

#### 【 0 0 6 4 】

6 8 撮影光学系

6 9 C M O S センサ

7 0 前処理回路

7 1 タイミング生成回路

10

20

30

40

50

- 7 2 画像メモリ

7 3 信号処理回路

7 4 C P U

7 5 動画 / 静止画切替スイッチ

7 6 撮影開始スイッチ

7 7 、 7 8 ダイナミックレンジ切替選択 S W

【図 1】

【図 2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】