(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7227777号**

**(P7227777)**

(45)発行日 令和5年2月22日(2023.2.22)

(24)登録日 令和5年2月14日(2023.2.14)

(51)国際特許分類

**H 0 4 N 25/772 (2023.01)**

F I

**H 0 4 N 25/772**

請求項の数 8 (全40頁)

|          |                                  |          |                                            |

|----------|----------------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2019-18255(P2019-18255)        | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 平成31年2月4日(2019.2.4)              | (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (65)公開番号 | 特開2020-127122(P2020-127122<br>A) | (72)発明者  | 安田 隆幸<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (43)公開日  | 令和2年8月20日(2020.8.20)             | (72)発明者  | 形川 浩靖<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| 審査請求日    | 令和4年1月25日(2022.1.25)             | (72)発明者  | 岩原 知永<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

|          |                                  | 審査官      | 鈴木 明                                       |

最終頁に続く

(54)【発明の名称】 撮像装置

**(57)【特許請求の範囲】****【請求項1】**

各々が1つのマイクロレンズと、光の入射を受けてパルス信号を発生する複数のアバランシェフォトダイオードと、前記複数のアバランシェフォトダイオードのうちの全てのアバランシェフォトダイオードのパルス信号をカウントする第1のカウンタと、前記複数のアバランシェフォトダイオードのうちの一部のアバランシェフォトダイオードのパルス信号をカウントする第2のカウンタとを備えたカント回路とを有する複数の単位画素と、前記第1のカウンタによるカウント値から、前記第2のカウンタによるカウント値を減算する減算手段と、

を有することを特徴とする撮像装置。

10

**【請求項2】**

前記第1のカウンタにおいてカウントしたカウント値から記録、表示用の画像を生成する画像生成手段をさらに備えることを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記第2のカウンタにおいてカウントしたカウント値と、前記減算手段において得られたカウント値とを用いて焦点検出を行う焦点検出手段をさらに備えることを特徴とする請求項1または2に記載の撮像装置。

**【請求項4】**

前記単位画素は、2つのアバランシェフォトダイオードを有し、前記第1のカウンタは前記2つのアバランシェフォトダイオードのパルス信号をカウントし、前記第2のカウン

20

タは前記 2 つのアバランシェフォトダイオードのうちいずれか一方のパルス信号をカウントすることを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の撮像装置。

**【請求項 5】**

前記単位画素は、4 つのアバランシェフォトダイオードを有し、前記第 1 のカウンタは前記 4 つのアバランシェフォトダイオードのパルス信号をカウントし、前記第 2 のカウンタは、前記 4 つのアバランシェフォトダイオードのうちのいずれか 2 つのパルス信号をカウントすることを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の撮像装置。

**【請求項 6】**

前記第 2 のカウンタは焦点検出を行う領域に位置する前記単位画素のみに配置されることを特徴とする請求項 1 乃至 5 のいずれか 1 項に記載の撮像装置。

10

**【請求項 7】**

前記第 1 のカウンタと前記第 2 のカウンタの両方の信号を出力する第 1 のモードと、前記第 1 のカウンタのみの信号を出力する第 2 のモードとを有することを特徴とする請求項 1 乃至 6 のいずれか 1 項に記載の撮像装置。

**【請求項 8】**

前記第 1 のカウンタの出力信号と前記第 2 のカウンタの出力信号を加算する信号処理部をさらに備えることを特徴とする請求項 1 乃至 7 のいずれか 1 項に記載の撮像装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

20

本発明は、撮像装置において受光素子の信号を加算する技術に関するものである。

**【背景技術】**

**【0002】**

従来より、撮像装置の A F (オートフォーカス) 方式として 1 つのマイクロレンズに対して複数の光電変換部を持った撮像素子により、瞳分割像を取得し、得られた 2 つの瞳分割像の位相差を求めて焦点検出を行う技術が知られている。

**【0003】**

例えば、特許文献 1 では瞳分離した像から位相差を求めて焦点検出を行うとともに、同一マイクロレンズに対応した画素を全て加算して 1 つの画素として取り扱うことが開示されている。これにより従来の撮像素子配列と同じになるように信号を取り出し、従来の信号処理技術により観賞用の画像を作成する。

30

**【0004】**

さらに特許文献 2 では、このような撮像素子の信号読み出し方法として、第 1 の動作で瞳分割されたフォトダイオード 2 画素のうち第 1 画素信号を読み出し、第 2 の動作でリセットせずに第 2 画素を加算して読み出すことが開示されている。そして、第 2 画素信号は加算信号から第 1 画素信号を減算して求める。なお、設定された焦点検出領域のみ第 1 画素信号と第 2 画素信号の両方を読み出し、それ以外は第 2 画素信号のみを読み出すよう必要最小限のデータを伝送することが可能であることも開示されている。これにより、高解像度、高速連写、動画フレームレートの向上といった性能向上の要求に対応することができる。

40

**【0005】**

ところで、特許文献 3 では、画素毎に 1 b i t 型 A D 変換器とカウンタとを有する固体撮像素子が提案されている。受光素子の信号に対し画素毎に A D 変換を行うため、列毎に A D 変換を行う固体撮像素子の持つ走査線数とフレームレートのトレードオフを解消することが可能である。

**【先行技術文献】**

**【特許文献】**

**【0006】**

**【文献】特開 2008 - 134389 号公報**

特開 2013 - 106194 号公報

50

特開 2015 - 173432 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上述の特許文献に開示された従来技術では、以下のような問題が発生する。

【0008】

1 bit 型 A/D 変換器とカウンタとを有する撮像装置において、特許文献 2 に開示されているように、設定された焦点検出領域のみ第 1 画素信号のカウント値と第 2 画素信号のカウント値の両方を読み出す場合を考える。この場合、設定された焦点検出領域以外の領域にも第 1 画素信号のカウンタと、第 2 画素信号のカウンタとを配置すると回路規模が増大する。また、設定された焦点検出領域以外の領域において、第 1 画素信号のカウンタと、第 2 画素信号のカウンタとを駆動させると消費電力が増大する。

10

【0009】

本発明は上述した課題に鑑みてなされたものであり、その目的は、画素ごとに 1 bit 型 A/D 変換器とカウンタとを有する撮像装置において、回路規模と消費電力の増加を抑制することである。

【課題を解決するための手段】

【0010】

本発明に係わる撮像装置は、各々が 1 つのマイクロレンズと、光の入射を受けてパルス信号を発生する複数のアバランシェフォトダイオードと、前記複数のアバランシェフォトダイオードのうちの全てのアバランシェフォトダイオードのパルス信号をカウントする第 1 のカウンタと、前記複数のアバランシェフォトダイオードのうちの一部のアバランシェフォトダイオードのパルス信号をカウントする第 2 のカウンタとを備えたカント回路とを有する複数の単位画素と、前記第 1 のカウンタによるカウント値から、前記第 2 のカウンタによるカウント値を減算する減算手段と、を有することを特徴とする。

20

【発明の効果】

【0011】

本発明によれば、画素ごとに 1 bit 型 A/D 変換器とカウンタとを有する撮像装置において、回路規模と消費電力の増加を抑制することが可能となる。

30

【図面の簡単な説明】

【0012】

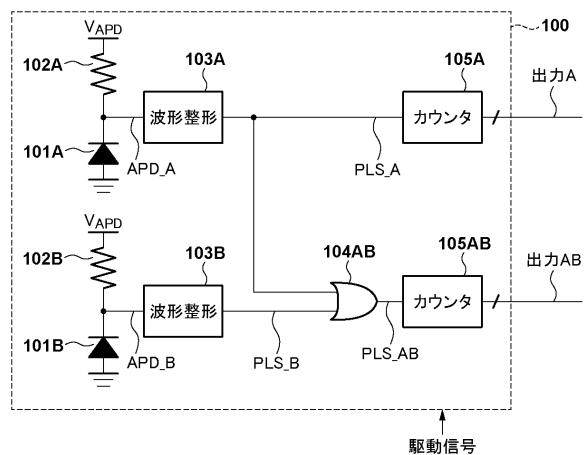

【図 1】本発明の第 1 の実施形態の撮像装置における単位画素の構成を示す図。

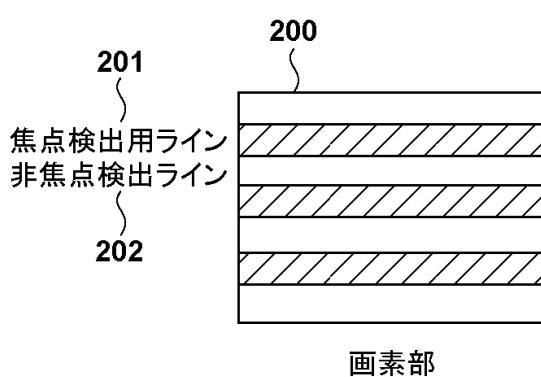

【図 2】本発明の第 1 の実施形態における画素部を示す図。

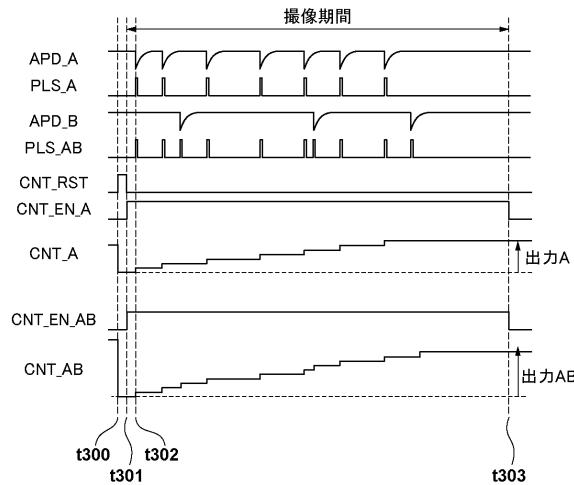

【図 3A】第 1 の実施形態における焦点検出用ラインの単位画素の動作を示すタイミングチャート。

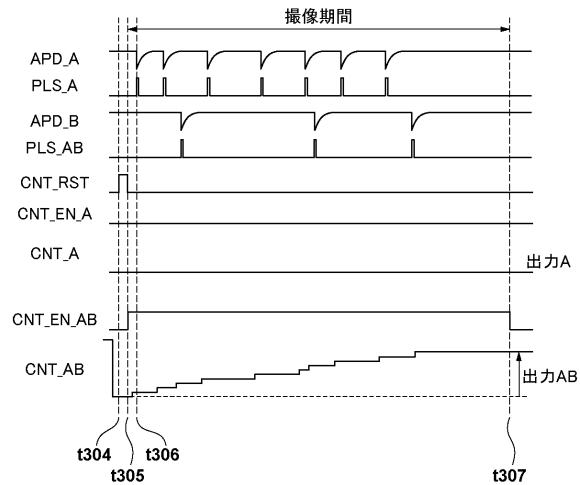

【図 3B】第 1 の実施形態における非焦点検出用ラインの単位画素の動作を示すタイミングチャート。

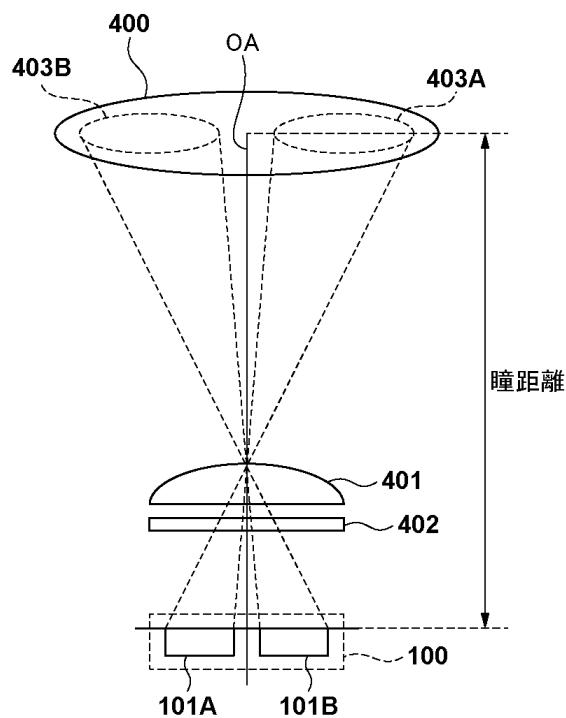

【図 4】第 1 の実施形態における瞳分割方式による焦点検出の原理を説明する図。

【図 5】第 1 の実施形態における固体撮像素子の構成を示す図。

40

【図 6】第 1 の実施形態における撮像装置の構成を示す図。

【図 7】第 2 の実施形態の撮像装置における単位画素の構成を示す図。

【図 8】第 2 の実施形態における画素部を示す図。

【図 9】第 2 の実施形態における非焦点検出用ラインの単位画素の動作を示すタイミングチャート。

【図 10】第 2 の実施形態における固体撮像素子の構成を示す図。

【図 11】第 2 の実施形態における撮像装置の構成を示す図。

【図 12】第 3 の実施形態における撮像装置の単位画素の構成を示す図。

【図 13】第 3 の実施形態における画素部を示す図。

【図 14A】第 3 の実施形態における焦点検出用ラインの単位画素の動作を示すタイミン

50

グチャート。

【図14B】第3の実施形態における非焦点検出用ラインの単位画素の動作を示すタイミングチャート。

【図15】第3の実施形態における瞳分割方式を説明する図。

【図16】第3の実施形態における固体撮像素子の構成を示す図。

【図17】第3の実施形態における撮像装置の構成を示す図。

【図18】第4の実施形態における単位画素の構成を示す図。

【図19】第4の実施形態における撮像素子の上面図。

【図20】第4の実施形態における単位画素の動作を示すタイミングチャート。

【図21】撮影レンズの射出瞳から出た光束が単位画素に入射する概念図。 10

【図22】第4の実施形態における撮像装置の構成を示すブロック図。

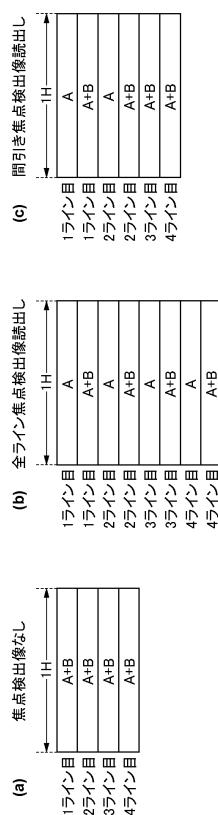

【図23】第4の実施形態における撮像素子の駆動モードと読み出しデータを示す図。

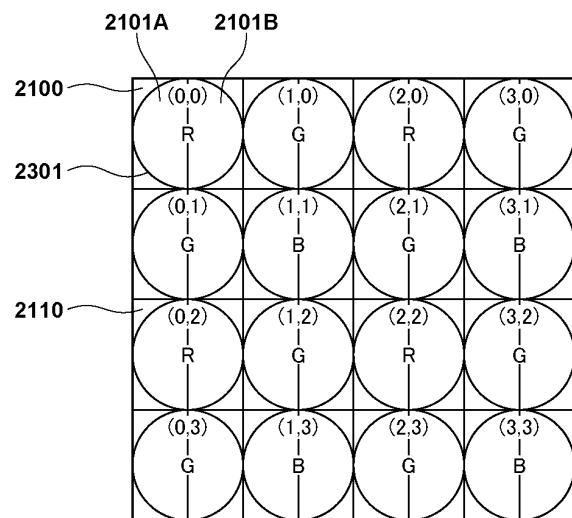

【図24】第4の実施形態におけるセレクタの遷移の様子を示す図。

【図25】第5の実施形態における単位画素の構成を示す図。

【図26】第5の実施形態における撮像素子の上面図。

【図27】第6の実施形態における撮像装置の構成を示す図。

【図28】第6の実施形態における撮像素子の構成を示す図。

【図29】第6の実施形態における単位画素の構成を示す図。

【図30】ガイガーモードの遷移を説明する模式図。

【図31】第6の実施形態における単位画素の構成を示す図。 20

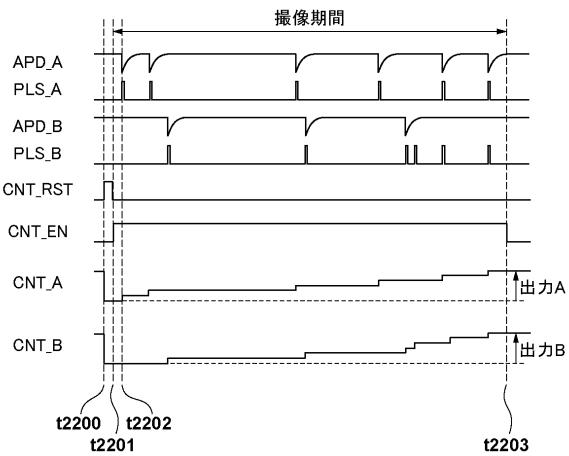

【図32】フォトン入射時のパルス波形とカウント数を示す模式図。

【図33】第6の実施形態の変形例における単位画素の構成を示す図。

【図34】第7の実施形態における単位画素の構成を示す図。

【図35】第8の実施形態における単位画素の構成を示す図。

【図36】第9の実施形態における単位画素の構成を示す図。

【図37】第10の実施形態における電圧駆動の例を示す図。

【発明を実施するための形態】

【0013】

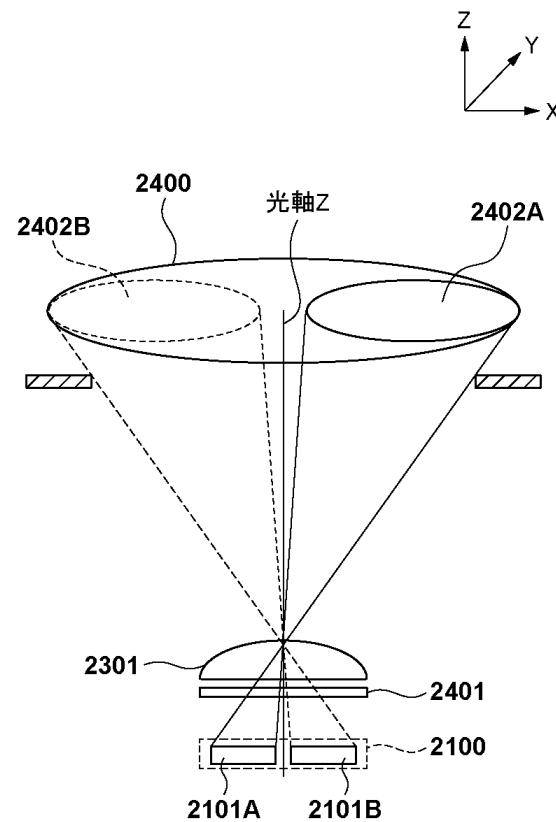

以下、添付図面を参照して実施形態を詳しく説明する。尚、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。 30

【0014】

(第1の実施形態)

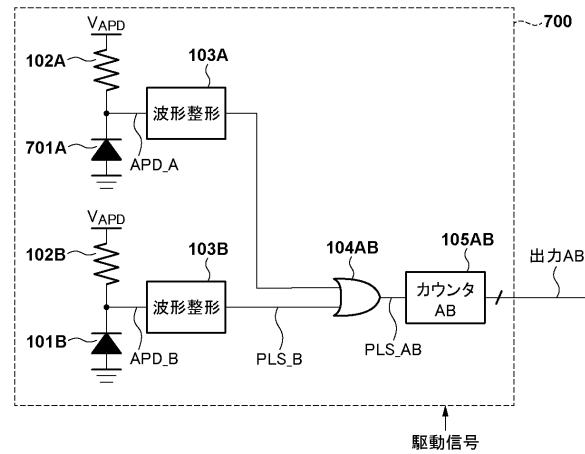

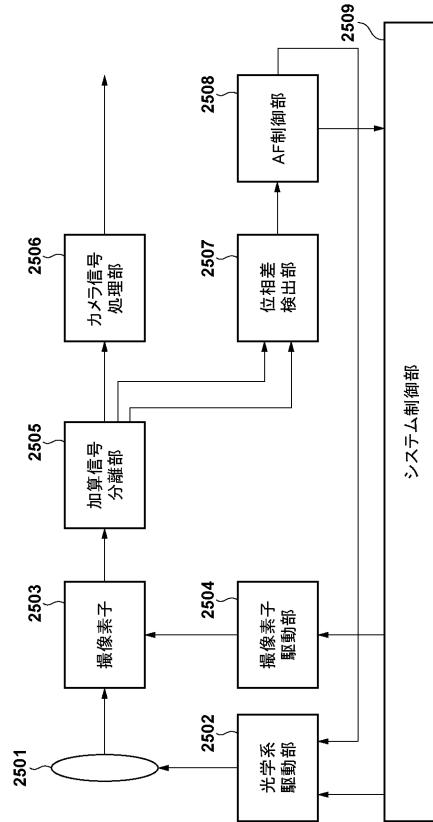

図1は、本発明の第1の実施形態の撮像装置における単位画素100の構成を示す回路図である。図1を参照して、固体撮像素子の構成要素である単位画素100の構成について説明する。

【0015】

単位画素100は、固体撮像素子に複数配列され、アバランシェフォトダイオード(以下、APDとする)101A, 101B、クエンチ抵抗102A, 102B、波形整形回路103A, 103B、OR回路104AB、カウンタ105A, 105ABを備えて構成される。 40

【0016】

単位画素100では、同一のマイクロレンズに対して受光素子としてのAPD101が2つ配置されている。そして、詳細は後述するが、マイクロレンズを透過してAPD101Aが受光した光子の数をカウンタ105Aでカウントすることにより、射出瞳の異なる2つの領域のうちの片方の信号を得ることが可能である。

【0017】

また、APD101AとAPD101Bが受光する光子の数をカウンタ105ABで力 50

ウントすることにより、表示用、記録用の信号を得る（画像生成する）ことが可能である。また、カウンタ 105AB のカウント値から、カウンタ A のカウント値を後段の回路において減算することにより、射出瞳の異なる 2 つの領域のうちのもう片方の信号を得ることが可能である。

#### 【0018】

続いて、単位画素の各々の構成要素に関して詳細に説明する。APD101A, 101B は、クエンチ抵抗 102A, 102B を介して逆バイアス電圧 VAPD と接続されており、光子が入射するとアバランシェ増倍による電荷を発生させる。発生した電荷はクエンチ抵抗 102A, 102B を介して排出される。波形整形回路 103A, 103B は、光子の入射に応じた電荷の生成、排出による電位の変化に対し増幅、エッジ検出を行うことにより、電圧パルス（パルス信号）を生成する。このように APD101、クエンチ抵抗 102、波形整形回路 103 は、光子の入射の有無を電圧パルスに変換することにより、1bit 型 AD 変換器として機能する。

#### 【0019】

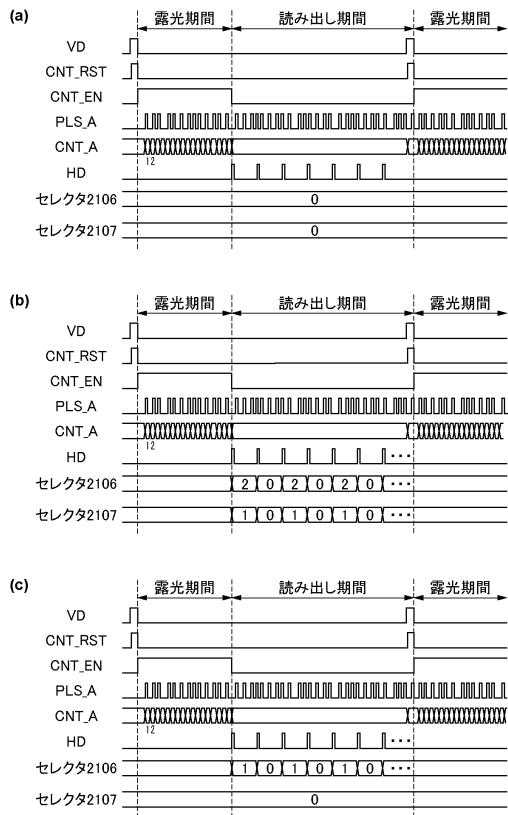

カウンタ 105A には波形整形回路 103A の出力が PLS\_A として入力される。カウンタ 105AB には、波形整形回路 103A の出力である PLS\_A と、波形整形回路 103B の出力である PLS\_B が、OR 回路 104AB を介して、PLS\_AB として入力される。

#### 【0020】

このような構成により、カウンタ 105A では、射出瞳の異なる領域の片方の信号を得ることが可能である。カウンタ 105AB では、射出瞳の異なる領域の両方の信号を加算した、表示用、記録用の画像を得ることが可能である。

#### 【0021】

ここで、後の説明の便宜上、APD101A 及びクエンチ抵抗 102A により生成される波形を APD\_A とし、APD101B 及びクエンチ抵抗 102B により生成される波形を APD\_B とする。また、波形整形回路 103A の出力を PLS\_A とし、OR 回路 104AB の出力を PLS\_AB とする。

#### 【0022】

続いて図 2、図 3A、図 3B を参照して、単位画素 100 の焦点検出用ライン 201 と非焦点検出用ライン 202 の駆動方法について説明する。

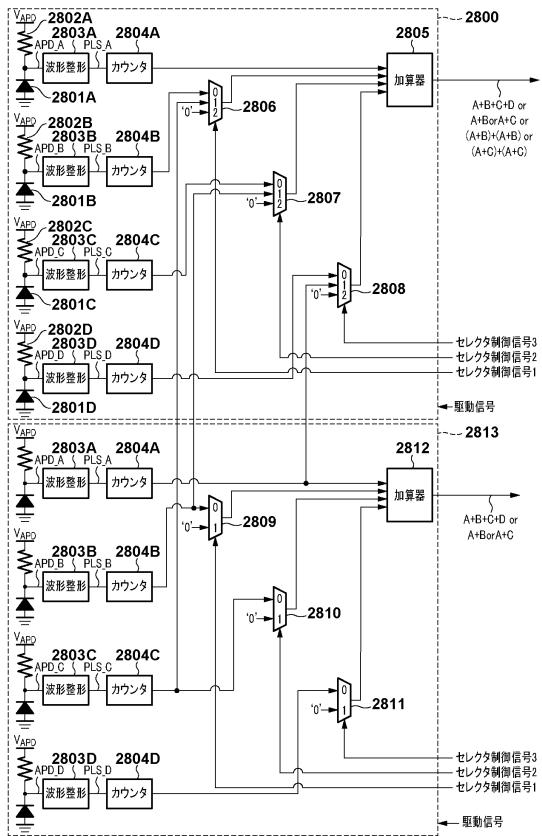

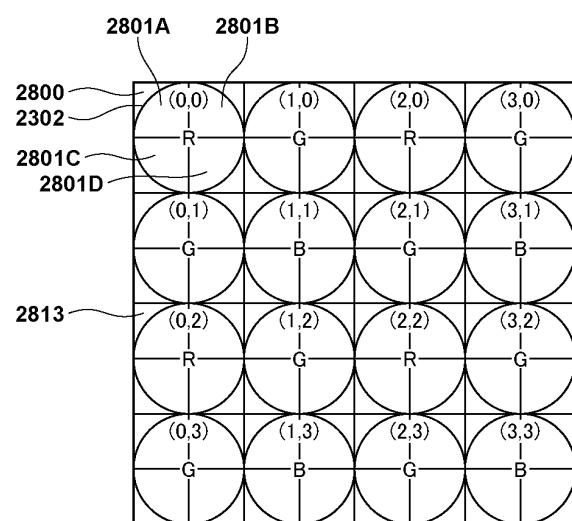

#### 【0023】

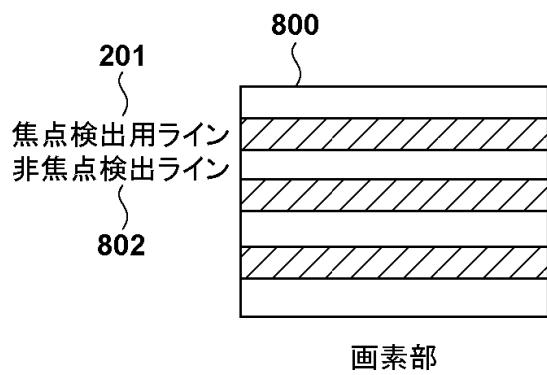

図 2 は、撮像素子において、単位画素 100 が行列状に多数配置された画素部 200 を示す図であり、焦点検出用ライン 201 と非焦点検出用ライン 202 を示している。図 3A は、焦点検出用ライン 201 の単位画素 100 の駆動を示すタイミングチャートである。

#### 【0024】

図 3A は、1 つの単位画素 100 における撮像駆動を示しており、この駆動を複数の単位画素 100 において並列して行うことにより、光学像がデジタル信号に変換される。図中、CNT\_RST、CNT\_EN\_A、CNT\_EN\_AB は駆動信号であり、カウンタ 105A, 105AB の制御を行う。

#### 【0025】

CNT\_RST は High レベル（以下、“H”とする）になることにより、カウンタ 105A, 105AB のカウント値を 0 にリセットする。また、CNT\_EN\_A が “H” となる期間のみ、カウンタ 105A はパルス数をカウントする。また、CNT\_EN\_AB が “H” となる期間のみ、カウンタ 105AB はパルス数をカウントする。CNT\_A 及び CNT\_AB はカウンタ 105A, 105AB のカウント値を表す。図 3A では説明を分かりやすくするために、CNT\_A は 0 ~ 7 の 8 段階でカウント値を表現している。CNT\_AB は PLS\_A と PLS\_B を OR 回路 104AB で加算した PLS\_AB で制御しているため、CNT\_A の 2 倍の、0 ~ 15 の 16 段階でカウント値を表現している。

#### 【0026】

続いてタイミングに沿って、単位画素 100 の駆動について説明する。タイミング t3

10

20

30

40

50

00では、CNT\_RSTが“H”となりカウンタ105A, 105ABのカウント値が0にリセットされる。

#### 【0027】

タイミングt301では、CNT\_RSTがLowレベル(以下、“L”とする)になり、カウンタ105A, 105ABのリセットが終了する。同時にCNT\_EN\_A、及び、CNT\_EN\_ABが“H”となりカウンタ105A, 105ABの電圧パルスのカウントが有効となる。これによりAPD101A, 101Bに入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。

#### 【0028】

タイミングt302では、APD101Aに光子が入射したことにより、アバランシェ増倍された電荷が発生しAPD\_Aの電位が変化する。クエンチ抵抗102Aを介して電荷を排出するので、APD\_Aが再び一定の電位になるまで時間がかかる。波形整形回路103Aでは、APD\_Aの立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスはカウンタ105Aに入力されるとともに、OR回路104ABを介してカウンタ105ABにも入力され、カウンタ105A、カウンタ105ABのカウント値が1となる。

10

#### 【0029】

タイミングt302～t303で、波形整形回路103Aで生成された電圧パルスはカウンタ105A、及び、カウンタ105ABでカウントされ、波形整形回路103Bで生成された電圧パルスはカウンタ105ABでカウントされる。

20

#### 【0030】

タイミングt303で、CNT\_EN\_A、及び、CNT\_EN\_ABが“L”となり、撮像期間が終了する。終了した際のカウンタ105A, 105ABのカウント値を出力A、出力ABとして単位画素100外へと出力する。図3Aに示す駆動により、撮像期間内にAPD101A, 101Bに入射した光子の個数のカウントを行う。その結果、カウンタ105Aでは、射出瞳の異なる領域の片方の信号を得ることが可能である。また、カウンタ105ABでカウントすることにより、射出瞳の異なる領域の両方の信号を得ることが可能であり、表示用、記録用の信号を得ることが可能である。

#### 【0031】

図3Bは、非焦点検出用ライン202の単位画素100の駆動を示すタイミングチャートである。図3Bは1つの単位画素100における撮像駆動を示しており、この駆動を複数の単位画素100において並列して行うことにより、光学像がデジタル信号に変換される。

30

#### 【0032】

タイミングt304では、CNT\_RSTが“H”となりカウンタ105ABのカウント値が0にリセットされる。後述するように、非焦点検出用ラインにおいては、単位画素100のカウンタAはカウントする必要がない。そのため、カウンタAは消費電力の低減のために、クロックGating等によりクロックがOFFされており、CNT\_RSTが“H”となるかならないかに関わらず、値「0」(ゼロ値)をホールドしている。

#### 【0033】

タイミングt305では、CNT\_RSTが“L”となり、カウンタ105ABのリセットが終了する。ここで、カウンタのリセットの後も、CNT\_EN\_Aは“L”的ままであり、カウンタ105Aは消費電力低減のためのクロックGating等によりカウント動作が無効のままである。一方、CNT\_EN\_ABは“H”となりカウンタ105ABの電圧パルスのカウントが有効となる。これによりAPD101A, 101Bに入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。

40

#### 【0034】

タイミングt306では、APD101Aに光子が入射したことにより、アバランシェ増倍された電荷が発生し、APD\_Aの電位が変化する。クエンチ抵抗102Aを介して電荷を排出するので、APD\_Aが再び一定の電位になるまで時間がかかる。波形整形回

50

路 1 0 3 A では、A P D \_ A の立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスはカウンタ 1 0 5 A に入力されるとともに、O R 回路 1 0 4 A B を介してカウンタ 1 0 5 A B にも入力され、カウンタ 1 0 5 A B のカウント値が 1 となる。カウンタ 1 0 5 A は消費電力低減のためのクロック G a t i n g 等によりカウント動作が無効のままでありカウントアップは行われない。

#### 【 0 0 3 5 】

タイミング t 3 0 6 ~ t 3 0 7 では、波形整形回路 1 0 3 A 、及び、波形整形回路 1 0 3 B で生成された電圧パルスはカウンタ 1 0 5 A B でカウントされる。タイミング t 3 0 7 では、C N T \_ E N \_ A B が “ L ” となり、撮像期間が終了する。終了した際のカウンタ 1 0 5 A B のカウント値を出力 A B として単位画素 1 0 0 外へと出力する。

10

#### 【 0 0 3 6 】

図 3 B に示す駆動により、撮像期間内に A P D 1 0 1 A , 1 0 1 B に入射した光子の個数のカウントを行う。一方、カウンタ 1 0 5 A は、クロック G a t i n g 等により動作しない。そのため、消費電力の低減を実現することが可能である。また、カウンタ 1 0 5 A B でカウントすることにより表示用、記録用の信号を得ることができる。

#### 【 0 0 3 7 】

続いて図 4 を参照して、本実施形態における瞳分割方式による焦点検出の原理について説明する。図 4 は、撮影レンズの射出瞳から出た光束が単位画素に入射する概念図である。前述したように、単位画素 1 0 0 には A P D 1 0 1 A 及び A P D 1 0 1 B が配置されている。

20

#### 【 0 0 3 8 】

図 4 に示すように、射出瞳 4 0 0 から出た光束は、光軸 O A を中心として、マイクロレンズ 4 0 1 とカラーフィルタ 4 0 2 を通して単位画素 1 0 0 に入射する。射出瞳 4 0 0 から単位画素 1 0 0 までの距離を瞳距離とする。射出瞳 4 0 0 の一部の領域を示す瞳領域 4 0 3 A と瞳領域 4 0 3 B を通過する光束は、それぞれ A P D 1 0 1 A と A P D 1 0 1 B に入射する。したがって、A P D 1 0 1 A と A P D 1 0 1 B は、それぞれ撮影レンズの射出瞳の異なる領域の光を受光している。これにより、A P D 1 0 1 A の信号と A P D 1 0 1 B の信号を比較することで、位相差の検知が可能となる。

#### 【 0 0 3 9 】

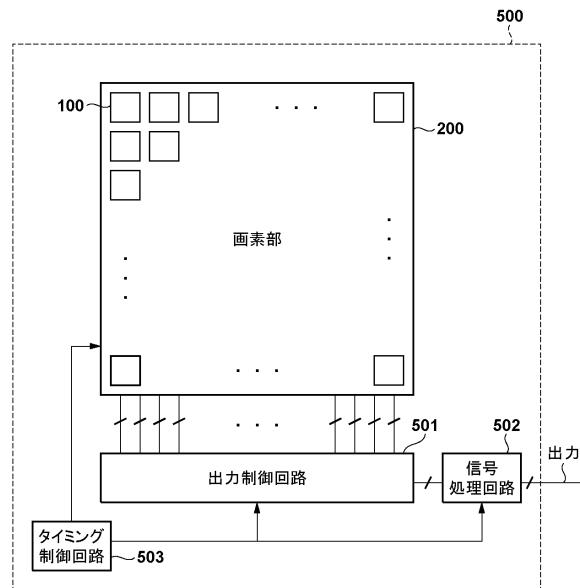

続いて図 5 を用いて、本実施形態における固体撮像素子の構成について説明する。図 5 は、固体撮像素子 5 0 0 の構成を示す回路図である。

30

#### 【 0 0 4 0 】

固体撮像素子 5 0 0 は、単位画素 1 0 0 が行列状に多数配置された画素部 2 0 0 と、出力制御回路 5 0 1 、信号処理回路 5 0 2 、タイミング制御回路 5 0 3 を備えて構成される。

#### 【 0 0 4 1 】

出力制御回路 5 0 1 には、画素部 2 0 0 に配置された単位画素 1 0 0 の出力 A 、出力 B がそれぞれ入力され、信号処理回路 5 0 2 に出力する単位画素 1 0 0 の信号を選択及び制御する。信号処理回路 5 0 2 は、焦点検出用ライン 2 0 1 については、単位画素 1 0 0 の出力 A と、出力 A B とを固体撮像素子 4 0 0 の外部へ出力する。非焦点検出用ライン 2 0 2 については、カウンタ 1 0 5 A はクロック G a t i n g 等により動作させずに、出力 A B のみ固体撮像素子 4 0 0 の外部へ出力する。

40

#### 【 0 0 4 2 】

タイミング制御回路 5 0 3 は、画素部 2 0 0 に駆動信号を出力する他、出力制御回路 5 0 1 、信号処理回路 5 0 2 の駆動タイミングを制御する。カウンタ 1 0 5 A に関して、このような駆動とすることにより、消費電力を低減することが可能となる。

#### 【 0 0 4 3 】

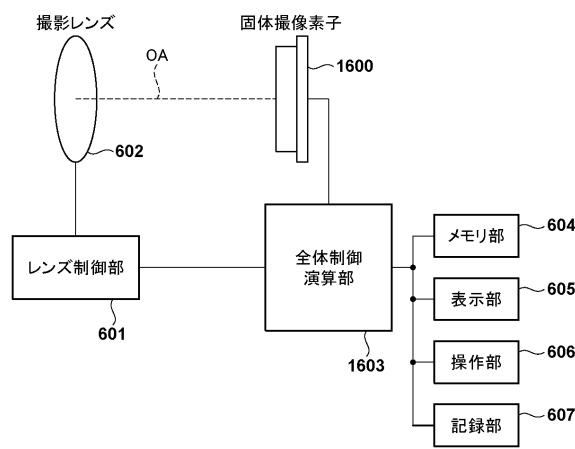

続いて、図 6 を参照して、固体撮像素子 5 0 0 を用いた撮像装置の構成について説明する。

#### 【 0 0 4 4 】

固体撮像素子 5 0 0 は、撮影レンズ 6 0 2 により結像された光学像を電気信号に変換す

50

る。レンズ制御部 601 は全体制御演算部 603 の指示に応じて、撮影レンズ 602 に対してフォーカス駆動、及び絞り駆動を行う。

#### 【0045】

全体制御演算部 603 は、固体撮像素子 500 の制御、固体撮像素子 500 から出力された信号の補正及び現像を含む、撮像装置全体の制御を行う。更には、固体撮像素子 500 内の画素部 200 を焦点検出用ライン 201 として駆動させるか、消費電力を低減させるための、非焦点検出用ライン 202 として駆動させるかを決定する。

#### 【0046】

全体制御演算部 603 は、焦点検出用ライン 201 として駆動させた複数の単位画素 100 の出力 A の信号と、出力 A B から出力 A を減算した信号とから位相差検出を行う。その検出結果に応じてレンズ制御部 601 にフォーカス駆動の制御量を通信する。

10

#### 【0047】

メモリ部 604 は画像データを一時的に保存し、表示部 605 は各種情報や撮影画像の表示を行う。操作部 606 は撮像装置の各種インターフェースであり、操作部 606 の信号を用いて、全体制御演算部 603 は各ブロックを制御する。記録部 607 は画像データの記録や読み出しを行うための、半導体メモリ等の着脱可能な記録部である。

#### 【0048】

このように、画素部 200 内の単位画素 100 において、焦点検出用ライン 201 については、カウンタ 105A、カウンタ 105AB を駆動させて、焦点検出に必要な画素値を取得する。その一方で、非焦点検出用ライン 202 においては、カウンタ 105A をクロック Gating 等により動作させないことにより、消費電力を低減することが可能となる。

20

#### 【0049】

##### (第 2 の実施形態)

以下、本発明の第 2 の実施形態の撮像装置及びその駆動方法について説明する。なお、以下において、第 1 の実施形態と同一構成要素には同じ記号および符号を付しその説明を省略する。

#### 【0050】

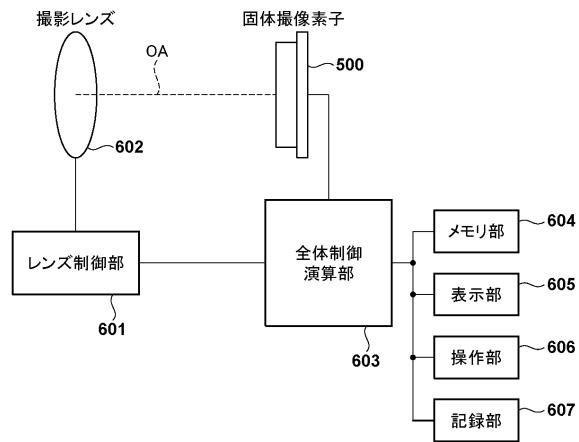

図 7 を参照して、本実施形態における固体撮像素子の構成要素である単位画素 700 の構成について説明する。図 7 は第 2 の実施形態における単位画素 700 の構成を示す回路図である。

30

#### 【0051】

単位画素 700 は、画素部 200 の非焦点検出ライン 802 における画素の構成を示している。画素部 200 の焦点検出ライン 201 における画素の構成は、図 1 に示した単位画素 100 の構成で配置されている。

#### 【0052】

単位画素 700 は、アバランシェフォトダイオード（以下、APD とする）101A, 101B、クエンチ抵抗 102A, 102B、波形整形回路 103A, 103B、OR 回路 104AB、カウンタ 105AB を備えて構成されている。単位画素 700 は、単位画素 100 のようにカウンタ 105A が配置されていないために、焦点検出用の画素としては使用できないが、より回路規模を小さく構成することができる。

40

#### 【0053】

続いて図 8、図 3A、図 9 を参照して、単位画素 700 からなる焦点検出用ライン 201 と非焦点検出用ライン 802（図 8 参照）の駆動方法について説明する。

#### 【0054】

図 8 は、単位画素 700、及び、単位画素 700 が行列状に多数配置された画素部 800 を示しており、更には、焦点検出用ライン 201 は単位画素 100 からなり、非焦点検出用ライン 802 は非焦点検出用画素 700 からなることを示している。

#### 【0055】

図 3A は、第 1 の実施形態と同じく、焦点検出用ライン 201 の単位画素 100 の駆動

50

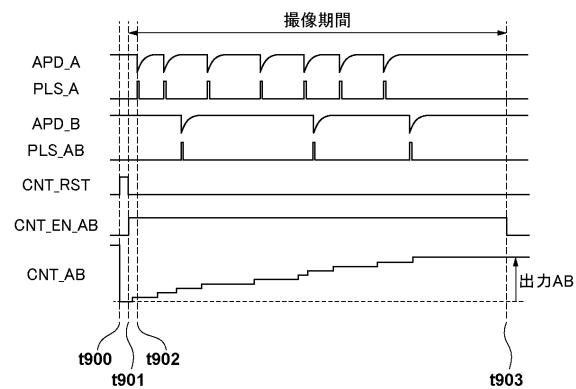

を示すタイミングチャートである。図9は非焦点検出用ライン802の単位画素700の駆動を示すタイミングチャートである。図9は1つの単位画素700における撮像駆動を示しており、この駆動を複数の単位画素700において並列して行うことにより、光学像をデジタル信号に変換する。

#### 【0056】

タイミングt900では、CNT\_RSTが“H”となりカウンタ105ABのカウント値が0にリセットされる。

#### 【0057】

タイミングt901では、CNT\_RSTが“L”となり、カウンタ105ABのリセットが終了する。CNT\_EN\_ABは“H”となりカウンタ105ABの電圧パルスのカウントが有効となる。これによりAPD101A, 101Bに入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。10

#### 【0058】

タイミングt902では、APD101Aに光子が入射したことによりアバランシェ増倍された電荷が発生し、APD\_Aの電位が変化する。クエンチ抵抗102Aを介して電荷を排出するので、APD\_Aが再び一定の電位になるまで時間がかかる。波形整形回路103Aでは、APD\_Aの立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスはOR回路104ABを介してカウンタ105ABに入力され、カウンタ105ABのカウント値が1となる。タイミングt902～t903では、波形整形回路103A、及び、波形整形回路103Bで生成された電圧パルスはカウンタ105ABでカウントされる。タイミングt903で、CNT\_EN\_ABが“L”となり、撮像期間が終了する。終了した際のカウンタ105ABのカウント値を出力ABとして単位画素700外へと出力する。20

#### 【0059】

図9に示す駆動により、非焦点検出ライン802の単位画素700において、撮像期間内にAPD101A, 101Bに入射した光子の個数のカウントを行う。また、図3Aに示す駆動により、焦点検出ライン201の単位画素100において、撮像期間内にAPD101A, 101Bに入射した光子の個数のカウントを行う。その結果、カウンタ105Aでは、射出瞳の異なる領域の片方の信号を得ることが可能である。また、カウンタ105ABでカウントすることにより表示用、記録用の信号を得ることが可能である。30

#### 【0060】

このように、焦点検出ライン201にのみ、単位画素100のように、カウンタA、及び、カウンタABを配置して、非焦点検出ライン802には単位画素700のように、カウンタAを配置しない構成により、回路規模を低減させることが可能となる。一方、単位画素700には、単位画素100と同様に、カウンタ105ABが配置されている。そのため、カウンタ105ABでカウントすることにより表示用、記録用の信号を得ることが可能である。

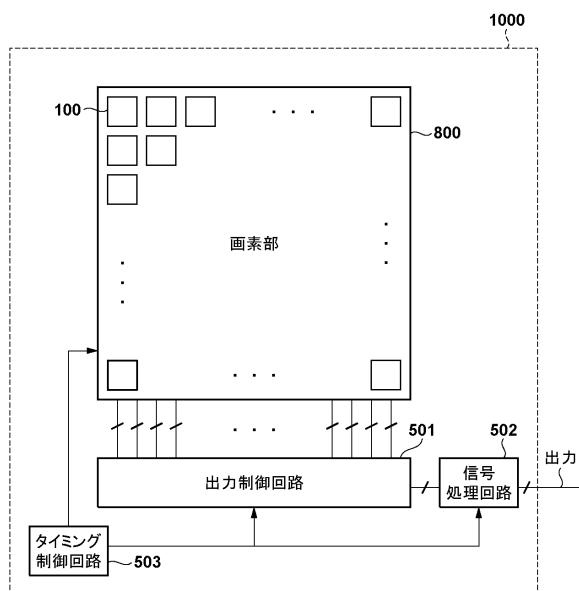

#### 【0061】

続いて図10を用いて、本実施形態における固体撮像素子の構成について説明する。図10は本実施形態における固体撮像素子1000の構成を示す回路図である。40

#### 【0062】

固体撮像素子1000は、焦点検出ライン201には単位画素100が行列状に多数配置され、非焦点検出ライン802には単位画素700が配置されている。また、出力制御回路501、信号処理回路502、タイミング制御回路503を備えて構成される。

#### 【0063】

出力制御回路502には、画素部800に配置された単位画素100の出力A、出力Bがそれぞれ入力され、信号処理回路502に出力する単位画素100、及び、単位画素700の信号を選択及び制御する。信号処理回路502は、焦点検出用ライン201については、単位画素100の出力Aと、出力ABとを固体撮像素子1000の外部へ出力する。非焦点検出用ライン802については、出力ABを固体撮像素子1000の外部へ出50

力する。

**【 0 0 6 4 】**

タイミング制御回路 5 0 3 は、画素部 8 0 0 に駆動信号を出力する他、出力制御回路 5 0 1、信号処理回路 5 0 2 の駆動タイミングを制御する。固体撮像素子 1 0 0 0 に関して、このような画素の配置とすることにより、消費電力を低減することが可能となると共に、より回路規模の低減を図ることができる。

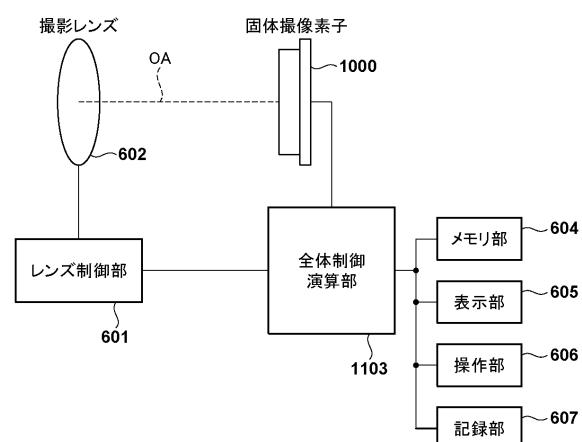

**【 0 0 6 5 】**

続いて、図 1 1 を参照して、固体撮像素子 1 0 0 0 を用いた撮像装置の構成について説明する。

**【 0 0 6 6 】**

固体撮像素子 1 0 0 0 は、撮影レンズ 6 0 2 により結像された光学像を電気信号に変換する。レンズ制御部 6 0 1 は全体制御演算部 1 1 0 3 の通信に応じて、撮影レンズ 6 0 2 に対してフォーカス駆動、及び絞り駆動を行う。

**【 0 0 6 7 】**

全体制御演算部 1 1 0 3 は、固体撮像素子 1 0 0 0 の制御、固体撮像素子 1 0 0 0 から出力された信号の補正及び現像を含む、撮像装置全体の制御を行う。更には、固体撮像素子 1 0 0 0 内の画素部 8 0 0 の焦点検出用ライン 2 0 1 と、回路規模の低減と消費電力の低減が実現された非焦点検出用ライン 8 0 2 とを駆動する。

**【 0 0 6 8 】**

全体制御演算部 1 1 0 3 は、焦点検出用ライン 2 0 1 として駆動させた複数の単位画素 1 0 0 の出力 A の信号と、出力 A B から出力 A を減算した信号とから位相差検出を行う。その検出結果に応じてレンズ制御部 6 0 1 にフォーカス駆動の制御量を通信する。

**【 0 0 6 9 】**

メモリ部 6 0 4 は画像データを一時的に保存し、表示部 6 0 5 は各種情報や撮影画像の表示を行う。操作部 6 0 6 は撮像装置の各種インターフェースであり、操作部 6 0 6 の信号を用いて、全体制御演算部 1 1 0 3 は各ブロックを制御する。記録部 6 0 7 は画像データの記録や読み出しを行うための、半導体メモリ等の着脱可能な記録部である。

**【 0 0 7 0 】**

このように、画素部 8 0 0 において、焦点検出用ライン 2 0 1 については、単位画素 1 0 0 を配置して、カウンタ 1 0 5 A、カウンタ 1 0 5 A B を駆動させて、焦点検出に必要な画素値を取得する。一方で、非焦点検出用ライン 8 0 2 については、単位画素 7 0 0 にカウンタ A 1 0 5 を配置しないことにより、回路規模を低減でき、より消費電力を低減することが可能となる。

**【 0 0 7 1 】**

( 第 3 の実施形態 )

以下、本発明の第 3 の実施形態の撮像装置及びその駆動方法について説明する。なお、以下において、第 1 の実施形態と同一構成要素には同じ記号および符号を付しその説明を省略する。

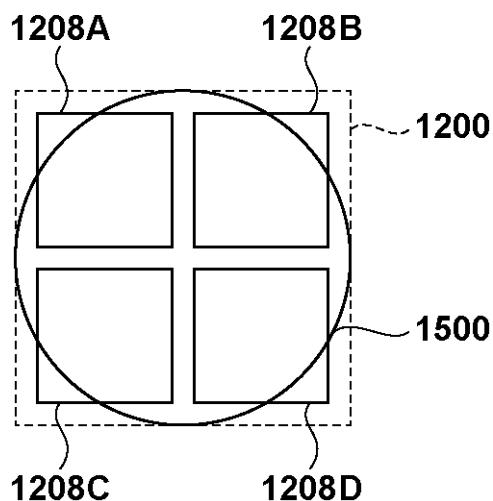

**【 0 0 7 2 】**

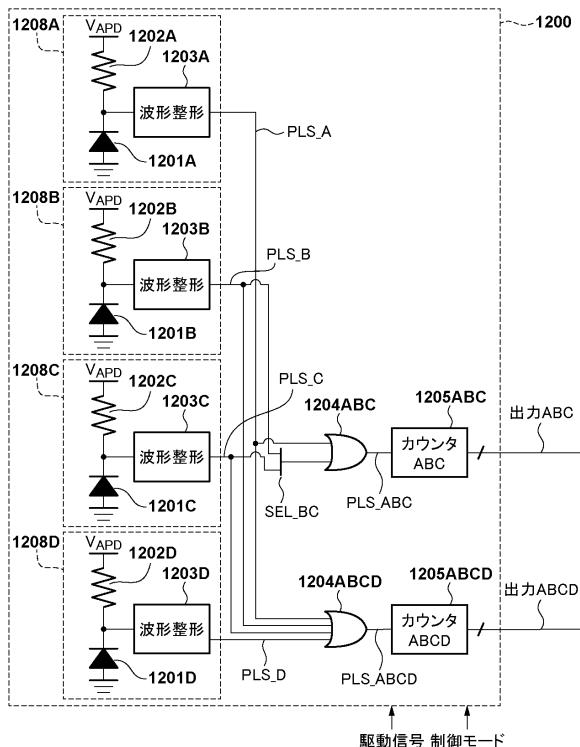

図 1 2 を参照して、本実施形態における固体撮像素子の構成要素である単位画素 1 2 0 0 の構成について説明する。図 1 2 は第 3 の実施形態における単位画素 1 2 0 0 の構成を示す回路図である。

**【 0 0 7 3 】**

単位画素 1 2 0 0 は、アバランシェフォトダイオード（以下、A P D とする）1 2 0 1 A, 1 2 0 1 B, 1 2 0 1 C, 1 2 0 1 D、クエンチ抵抗 1 2 0 2 A, 1 2 0 2 B, 1 2 0 2 C, 1 2 0 2 D を備える。さらに、波形整形回路 1 2 0 3 A, 1 2 0 3 B, 1 2 0 3 C, 1 2 0 3 D、O R 回路 1 2 0 4 A B C、O R 回路 1 2 0 4 A B C D、カウンタ 1 2 0 5 A B C, 1 2 0 5 A B C D、セレクタ S E L \_ B C も備える。

**【 0 0 7 4 】**

単位画素 1 2 0 0 には受光素子としての A P D 1 2 0 1 が 4 つ配置されている。そして

10

20

30

40

50

、同一マイクロレンズを透過して A P D 1 2 0 1 A が受光した光子数と、セレクタ S E L \_ B C で選択される A P D 1 2 0 1 B もしくは A P D 1 2 0 1 C が受光した光子数とをカウンタ 1 2 0 5 A B C でカウントする。これにより、射出瞳の異なる領域の片方の信号を得ることが可能である。

#### 【 0 0 7 5 】

例えば、セレクタ S E L \_ B C により、 A P D 1 2 0 1 B が選択された場合、カウンタ 1 2 0 5 A B C は A P D 1 2 0 1 A と、 A P D 1 2 0 1 B とを加算した値をカウントする。一方で、例えば、セレクタ S E L \_ B C により、 A P D 1 2 0 1 C が選択された場合、カウンタ 1 2 0 5 A B C は A P D 1 2 0 1 A と、 A P D 1 2 0 1 C とを加算した値をカウントする。セレクタ S E L \_ B C の制御については後述する。

10

#### 【 0 0 7 6 】

また、 A P D 1 2 0 1 A 、 A P D 1 2 0 1 B 、 A P D 1 2 0 1 C 、 A P D 1 2 0 1 D が受光する光子数をカウンタ 1 2 0 5 A B C D でカウントすることにより、表示用、記録用の信号を得ることが可能である。また、カウンタ 1 2 0 5 A B C D のカウント値から、カウンタ 1 2 0 5 A B C のカウント値を後段の回路において減算することにより、射出瞳の異なる領域のもう片方の信号を得ることが可能である。

#### 【 0 0 7 7 】

続いて各々の構成要素について詳細に説明する。 A P D 1 2 0 1 A , 1 2 0 1 B , 1 2 0 1 C , 1 2 0 1 D にはクエンチ抵抗 1 2 0 2 A , 1 2 0 2 B , 1 2 0 2 C , 1 2 0 2 D を介して逆バイアス電圧 V A P D が接続されており、光子が入射するとアバランシェ増倍による電荷を発生させる。発生した電荷はクエンチ抵抗 1 2 0 2 A , 1 2 0 2 B , 1 2 0 2 C , 1 2 0 2 D を介して排出される。波形整形回路 1 2 0 3 A , 1 2 0 3 B , 1 2 0 3 C , 1 2 0 3 D は、光子の入射に応じた電荷の生成、排出による電位の変化に対し増幅及びエッジ検出を行うことにより、電圧パルスを生成する。

20

#### 【 0 0 7 8 】

このように A P D 1 2 0 1 、クエンチ抵抗 1 2 0 2 、波形整形回路 1 2 0 3 は、光子の入射の有無を電圧パルスに変換することにより、 1 b i t 型 A D 変換器として機能する。

#### 【 0 0 7 9 】

カウンタ 1 2 0 5 A B C には、波形整形回路 1 2 0 3 A の出力である P L S \_ A と、波形整形回路 1 2 0 3 B の出力である P L S \_ B 及び波形整形回路 1 2 0 3 C の出力である P L S \_ C の一方とを加えたものが、 P L S \_ A B C として入力される。波形整形回路 1 2 0 3 B の出力である P L S \_ B 、もしくは、波形整形回路 1 2 0 3 C の出力である P L S \_ C のいずれが選択されるかは、焦点検出の方向により決定される。詳細は後述する。

30

#### 【 0 0 8 0 】

カウンタ 1 2 0 5 A B C D には、波形整形回路 1 2 0 3 A の出力である P L S \_ A と、波形整形回路 1 2 0 3 B の出力である P L S \_ B と、波形整形回路 1 2 0 3 C の出力である P L S \_ C と、波形整形回路 1 2 0 3 D の出力である P L S \_ D とが、 O R 回路 1 2 0 4 A B C D を介して、 P L S \_ A B C D として入力される。

#### 【 0 0 8 1 】

このような構成により、カウンタ 1 2 0 5 A B C では、射出瞳の異なる領域のうちの片方の信号を得ることが可能である。カウンタ 1 2 0 5 A B C D では、射出瞳の異なる領域の信号を加算した、表示用、記録用の画像を得ることが可能である。

40

#### 【 0 0 8 2 】

ここで、説明を分かりやすくするために、 A P D 1 2 0 1 A 及びクエンチ抵抗 1 2 0 2 A により生成される波形を A P D \_ A とする。以下、同様に、 A P D 1 2 0 1 A 及びクエンチ抵抗 1 2 0 2 B により生成される波形を A P D \_ B とする。 A P D 1 2 0 1 C 及びクエンチ抵抗 1 2 0 2 C により生成される波形を A P D \_ C とする。 A P D 1 2 0 1 D 及びクエンチ抵抗 1 2 0 2 D により生成される波形を A P D \_ D とする。また、 O R 回路 1 2 0 4 A B C の出力を P L S \_ A B C 、 O R 回路 1 2 0 4 A B C D の出力を P L S \_ A B C D とする。また、 A P D 1 2 0 1 A ~ 1 2 0 1 D 、クエンチ抵抗 1 2 0 2 A ~ 1 2 0 2 D

50

、波形整形回路 1203A～1203D の構成要素をそれぞれまとめて、受光部 1208A～1208D とする。

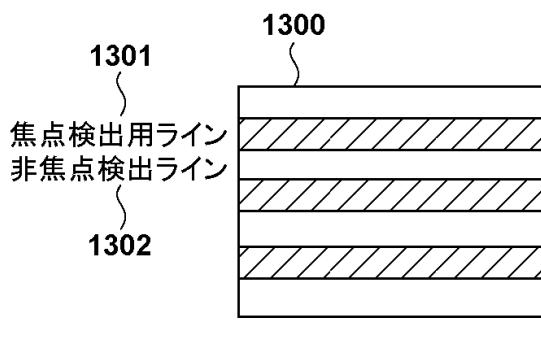

#### 【0083】

続いて図 13、図 14A、図 14B を参照して、画素部 1300 における焦点検出用ライン 1301 と非焦点検出用ライン 1302 の駆動方法について説明する。図 13 は、撮像素子において、単位画素 1200 が行列状に多数配置された画素部 1300 を示しており、更には、焦点検出用ライン 1301 と非焦点検出用ライン 1302 を示している。

#### 【0084】

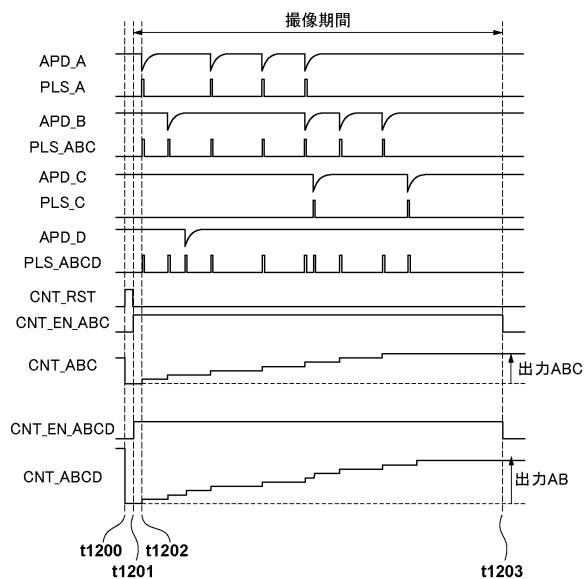

図 14A は、焦点検出用ライン 1301 の単位画素 1200 の駆動を示すタイミングチャートである。本実施形態では、セレクタ SEL\_B\_C により APD1201B が選択された場合、つまりカウンタ 1205ABC が APD1201A と、APD1201B とを加算した値をカウントする場合を示す。図 14A は 1 つの単位画素 1200 における撮像駆動を示しており、この駆動を複数の単位画素 1200 において並列して行うことにより、光学像をデジタル信号に変換する。

10

#### 【0085】

図 14Aにおいて、CNT\_RST、CNT\_EN\_ABC 及び、CNT\_EN\_ABCD は駆動信号であり、カウンタ 1205ABC, 1205ABCD の制御を行う。CNT\_RST は “H” になることにより、カウンタ 1205ABC, 1205ABCD のカウント値を 0 にリセットする。また、CNT\_EN\_ABC が “H” となる期間のみ、カウンタ 1205ABC はパルス数をカウントする。また、CNT\_EN\_ABCD が “H” となる期間のみ、カウンタ 1205ABCD はパルス数をカウントする。CNT\_ABC 及び CNT\_ABCD はカウンタ 1205ABC, 1205ABCD のカウント値を表す。

20

#### 【0086】

図 14A では説明を分かりやすくするために、CNT\_ABC は PLS\_A と、PLS\_B 及び PLS\_C の一方とを OR 回路 1204ABC で加算した PLS\_ABC で駆動しており、0～7 の 8 段階でカウント値を表現している。CNT\_ABCD は PLS\_A、PLS\_B、PLS\_C、PLS\_D を OR 回路 1204ABCD で加算した PLS\_ABCD で制御しているため、CNT\_A の 2 倍の、0～15 の 16 段階でカウント値を表現している。

#### 【0087】

30

続いて、単位画素 1200 の駆動について説明する。

#### 【0088】

タイミング t1200 では、CNT\_RST が “H” となりカウンタ 1205ABC, 1205ABCD のカウント値が 0 にリセットされる。

#### 【0089】

タイミング t1201 では、CNT\_RST が “L” となり、カウンタ 1205ABC, 1205ABCD のリセットが終了する。同時に CNT\_EN\_ABC 及び、CNT\_EN\_ABCD が “H” となりカウンタ 1205ABC, 1205ABCD の電圧パルスのカウントが有効となる。これにより APD1201A, 1201B, 1201C, 1201D に入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。

40

#### 【0090】

タイミング t1202 では、APD1201A に光子が入射したことにより、アバランシェ増倍された電荷が発生し APD\_A の電位が変化する。クエンチ抵抗 1202A を介して電荷を排出するので、APD\_A が再び一定の電位になるまで時間がかかる。波形整形回路 1203A では、APD\_A の立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスはカウンタ 1205ABC に入力されるとともに、OR 回路 1204ABCD を介してカウンタ 1205ABCD にも入力され、カウンタ 1205ABC、カウンタ 1205ABCD のカウント値が 1 となる。

#### 【0091】

本実施形態では、セレクタ SEL\_B\_C により、APD1201B が選択されているの

50

で、カウンタ 1205ABC では、APD1201A と、APD1201B とを加算した値がカウントされる。

#### 【0092】

タイミング t1202 ~ t1203 で、波形整形回路 1203A と、波形整形回路 1203B とで生成された電圧パルスは、カウンタ 1205ABC でカウントされる。また、波形整形回路 1203A、波形整形回路 1203B、波形整形回路 1203C、波形整形回路 1203D で生成された電圧パルスは、カウンタ 1205ABCD でカウントされる。

#### 【0093】

タイミング t1203 で、CNT\_EN\_ABC、及び、CNT\_EN\_ABCD が “L” となり、撮像期間が終了する。終了した際のカウンタ 1205ABC, 1205ABCD のカウント値を出力 ABC、出力 ABCD として単位画素 1200 外へと出力する。10

#### 【0094】

図 14A に示す駆動により、撮像期間内に APD1201A, 1201B, 1201C, 1201D に入射した光子の個数のカウントを行う。その結果、カウンタ 1205ABC では、射出瞳の異なる領域のうちの片方の信号を得ることが可能である。また、カウンタ 1205ABCD でカウントすることにより表示用、記録用の信号を得ることが可能である。

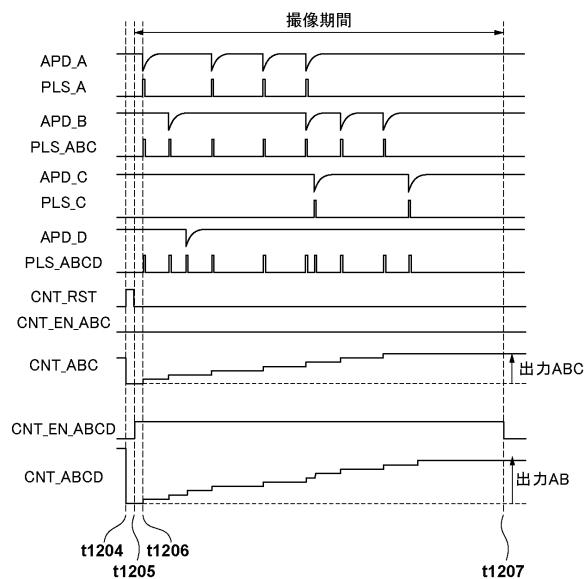

#### 【0095】

図 14B は、非焦点検出用ライン 1302 の単位画素 1200 の駆動を示すタイミングチャートである。図 14B は、1 つの単位画素 1200 における撮像駆動を示しており、この駆動を複数の単位画素 1200 において並列して行うことにより、光学像をデジタル信号に変換する。20

#### 【0096】

タイミング t1204 では、CNT\_RST が “H” となりカウンタ 1205ABCD のカウント値が 0 にリセットされる。後述するように、非焦点検出用ラインにおいては、単位画素 1200 のカウンタ ABC 1205 はカウントする必要がない。そのため、カウンタ ABC 1205 は消費電力低減のために、クロック Gating 等によりクロックが OFF されており、CNT\_RST が “H” となるかならないかに関わらず、値 ‘0’ にホールドされている。

#### 【0097】

タイミング t1205 では、CNT\_RST が “L” になり、カウンタ 1205ABCD のリセットが終了する。この後、CNT\_EN\_ABC は “L” のままで、カウンタ 1205ABC は消費電力低減のためのクロック Gating 等によりカウント動作が無効のままである。一方、CNT\_EN\_ABCD は “H” となりカウンタ 1205ABCD の電圧パルスのカウントが有効となる。これにより APD1201A, 1201B, 1201C, 1201D に入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。30

#### 【0098】

タイミング t1206 では、APD1201A に光子が入射したことにより、アバランシェ増倍された電荷が発生し、APD\_A の電位が変化する。クエンチ抵抗 1202A を介して電荷を排出するので、APD\_A が再び一定の電位になるまで時間がかかる。波形整形回路 1203A では、APD\_A の立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスは OR 回路 1204ABC を介してカウンタ 1205ABC に入力されるとともに、OR 回路 1204ABCD を介してカウンタ 1205ABCD にも入力され、カウンタ 1205ABCD のカウント値が 1 となる。カウンタ 1205ABC は消費電力低減のためのクロック Gating 等によりカウント動作が無効のままでありカウントアップは行われない。40

#### 【0099】

タイミング t1206 ~ t1207 で、波形整形回路 1203A、波形整形回路 1203B、波形整形回路 1203C、波形整形回路 1203D で生成された電圧パルスはカウ

10

20

30

40

50

ンタ 1205ABC でカウントされる。タイミング t1207 で、CNT\_EN\_AB\_CD が “L” となり、撮像期間が終了する。終了した際のカウンタ 1205ABC のカウント値を出力 ABCD として単位画素 100 外へと出力する。

#### 【0100】

図 14B に示す駆動により、撮像期間内に APD1201A, 1201B, 1201C, 1201D に入射した光子の個数のカウントを行う。一方、カウンタ 1205ABC は、クロック Gating 等により動作しない。そのため、消費電力を低減を実現することが可能である。また、カウンタ 1205ABC でカウントすることにより表示用、記録用の信号を得ることが可能である。

#### 【0101】

続いて図 15 を参照して、本発明の第 3 の実施形態における単位画素 1200 の構造について説明する。図 15 は、第 3 の実施形態における単位画素 1200 内の受光部 1208 の配置を示す図である。

#### 【0102】

図 15 に示すように、1つのマイクロレンズ 1500 を透過する光が入射する領域を上下左右の 4 つに分割するように受光部 1208A ~ 1208D が配置されている。このように配置することにより、瞳領域を縦方向に分離した信号と、横方向に分離した信号を得ることが可能となるので、縦方向、横方向の位相差を効果的に検出することができる。例えば、瞳領域を横方向のみに分離した撮像装置では、横方向のコントラスト変化が大きい縦線のような被写体に対しては精度良く撮像面位相差 AF を行うことができる。しかし、横方向のコントラスト変化が小さい横線のような被写体に対しては精度良く位相差 AF を行なうことが難しい。一方、瞳領域を縦方向、横方向の両方に分離可能とした撮像装置では、被写体の変化の大きい方向に合わせて、撮像面位相差 AF に用いる信号を選択できるので、撮像面位相差 AF を高精度に行なうことが可能な被写体条件が広くなる。より具体的には、受光部 1208A, 1208B の電圧パルスのカウント結果を加算した信号と、受光部 1208C, 1208D の電圧パルスのカウント結果を加算した信号を比較することにより横線検出が可能である。一方、受光部 1208A, 1208C の電圧パルスのカウント結果を加算した信号と、受光部 1208B, 1208D の電圧パルスのカウント結果を加算した信号を比較することにより縦線検出が可能である。

#### 【0103】

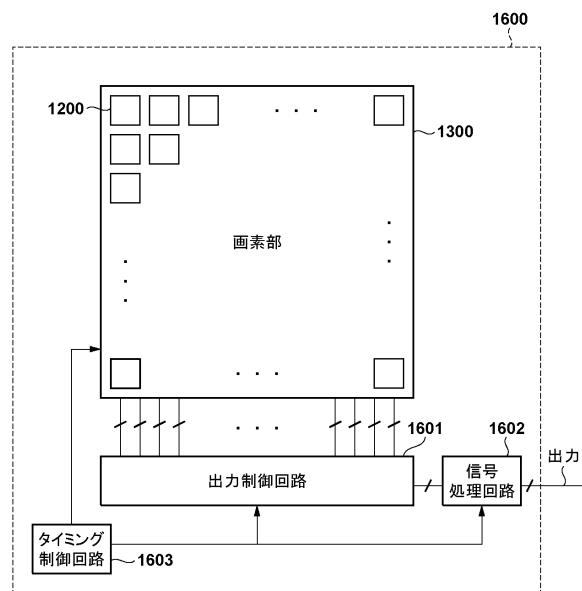

続いて図 16 を用いて、本実施形態における固体撮像素子の構成について説明する。図 16 は、固体撮像素子 1600 の構成を示す回路図である。

#### 【0104】

固体撮像素子 1600 は、単位画素 1200 が行列状に多数配置された画素部 1300 と、出力制御回路 1601、信号処理回路 1602、タイミング制御回路 1603 を備えて構成される。

#### 【0105】

出力制御回路 1601 には、画素部 1300 に配置された単位画素 1200 の出力 ABC, 出力 ABCD がそれぞれ入力され、信号処理回路 1602 に出力する単位画素 1200 の信号を選択及び制御する。信号処理回路 1602 は、焦点検出用ライン 1301 については、単位画素 1200 の出力 ABC と、出力 ABCD とを固体撮像素子 1600 の外部へ出力する。一方、非焦点検出用ラインについては、カウンタ 1205ABC は、クロック Gating 等により動作させずに、出力 ABCD のみ固体撮像素子 1600 の外部へ出力される。

#### 【0106】

タイミング制御回路 1603 は、画素部 1300 に駆動信号を出力する他、出力制御回路 1601, 信号処理回路 1602 の駆動タイミングを制御する。カウンタ 1205ABC に関して、このような駆動とすることにより、消費電力を低減することが可能となる。

#### 【0107】

続いて、図 17 を参照して、固体撮像素子 1600 を用いた撮像装置の構成について説

10

20

30

40

50

明する。

#### 【0108】

固体撮像素子 1600 は、撮影レンズ 602 により結像された光学像を電気信号に変換する。レンズ制御部 601 は全体制御演算部 1603 の指示に応じて、撮影レンズ 602 に対してフォーカス駆動、及び絞り駆動を行う。

#### 【0109】

全体制御演算部 1603 は、固体撮像素子 1600 の制御、固体撮像素子 1600 から出力された信号の補正及び現像を含む、撮像装置全体の制御を行う。更には、固体撮像素子 1600 内の画素部 1200 を焦点検出用ライン 1301 として駆動させるか、消費電力を低減させるための、非焦点検出用ライン 1302 として駆動させるかを決定する。また、画素部 1200 内の SEL\_\_BC を制御して、位相差検出を縦方向に行うか、横方向に行うかを決定する。

10

#### 【0110】

全体制御演算部 1603 は、焦点検出用ライン 1301 として駆動させた複数の単位画素 1200 の出力 ABC の信号と、出力 ABCD から出力 ABC を減算した信号とから位相差検出を行う。その検出結果に応じてレンズ制御部 601 にフォーカス駆動の制御量を通信する。

#### 【0111】

メモリ部 604 は画像データを一時的に保存し、表示部 605 は各種情報や撮影画像の表示を行う。操作部 606 は撮像装置の各種インターフェースであり、操作部 606 の信号を用いて、全体制御演算部 1603 は各ブロックを制御する。記録部 607 は画像データの記録や読み出しを行うための、半導体メモリ等の着脱可能な記録部である。

20

#### 【0112】

このように、画素部 1300 内の単位画素 1200 において、焦点検出用ライン 1301 においては、カウンタ 1205ABC、カウンタ 1205ABCD を駆動させて、焦点検出に必要な画素値を取得する。その一方で、非焦点検出用ライン 1302 においては、カウンタ 1205ABC をクロック Gating 等により動作させないことにより、消費電力を低減することが可能となる。

#### 【0113】

(第4の実施形態)

30

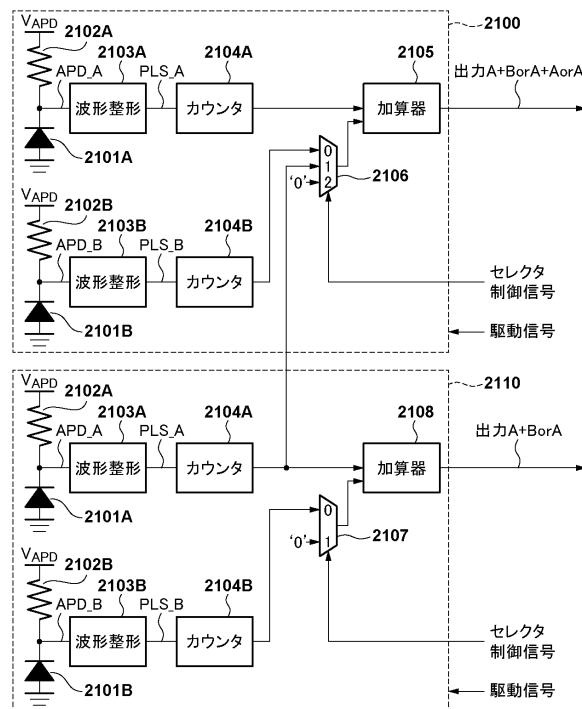

図 18 は、本発明の第4の実施形態における単位画素 2100, 2110 の構成を示す回路図である。単位画素 2100, 2110 は、図 19 に示すように、二次元状に配列されたマイクロレンズ 2301 下の 1 つの画素である。また、1 つのマイクロレンズ 2301 下には 1 つのカラーフィルタが配置されており、左上を R 画素とした Bayer 配列を構成している。単位画素 2100 は左上(0, 0) の R 画素、単位画素 2110 は単位画素 2100 から 2 画素下(0, 2) の R 画素である。単位画素 2100, 2110 は、アバランシェフォトダイオード(以下、APD とする) 2101A, 2101B、クエンチ抵抗 2102A, 2102B、波形整形回路 2103A, 2103B、カウンタ 2104A, 2104B を備える。また、2 つのカウンタのカウント値を加算する加算器 2105, 2108、加算器 2105, 2108 の入力信号を選択するセレクタ 2106, 2107 を備える。

40

#### 【0114】

単位画素 2100, 2110 には、受光素子としての APD 2101 が 2 つ配置されており、同一マイクロレンズを透過した光を APD 2101A, 2101B がそれぞれ受光することにより、射出瞳の異なる領域の信号を得ることが可能である。また、2 つの受光素子の信号を加算器 2105, 2108 により加算することで、撮像画像を生成する。

#### 【0115】

続いて各々の構成要素に関して詳細に説明する。

#### 【0116】

APD 2101A, 2101B は、クエンチ抵抗 2102A, 2102B を介して逆バ

50

イアス電圧 V A P D と接続されており、光子が入射するとアバランシェ増倍による電荷を発生させる。発生した電荷はクエンチ抵抗 2102A, 2102B を介して排出される。波形整形回路 2103A, 2103B は、光子の入射に応じた電荷の生成、排出による電位の変化に対し増幅及びエッジ検出を行うことにより、電圧パルスを生成する。このように A P D 2101、クエンチ抵抗 2102、波形整形回路 2103 は、光子の入射の有無を電圧パルスに変換することにより、1 bit 型 A D 変換器として機能する。

#### 【0117】

波形整形回路 2103A, 2103B の出力である電圧パルスは、それぞれカウンタ 2104A, 2104B に入力される。計数部としてのカウンタ 2104A, 2104B は、電圧パルスの計数を行う。カウンタ 2104A, 2104B は、単位画素に入力される駆動信号により、リセット及び計数のイネーブルが制御される。加算器 2105 はカウンタ 2104A とセレクタ 2106 の出力の 2 つを入力値として加算を行う。加算器 2108 はカウンタ 2104A とセレクタ 2107 の出力の 2 つを入力値として加算を行う。セレクタ 2106 は単位画素に入力される制御信号により、3 つの入力のセレクトを行う。制御信号が “0” の時、カウンタ 2104B のカウント値がセレクトされ、“1” の時、単位画素 2110 のカウンタ 2104A のカウント値がセレクトされ、“2” の時、「0」値がセレクトされる。

#### 【0118】

すなわち、制御信号が “0” の時は、単位画素 2100 の外部へは撮像画像が出力され、“1” の時は単位画素 2100 のカウンタ 2104A と単位画素 2110 のカウンタ 2104A を加算した焦点検出用画素が出力される。また、制御信号が “2” の時は、単位画素 2100 のカウンタ 2104A のみの焦点検出用画素として計数結果が出力される。

#### 【0119】

セレクタ 2107 は、単位画素に入力される制御信号により、2 つの入力のセレクトを行う。制御信号が “0” の時、カウンタ 2104B がセレクトされ、“1” の時、「0」値がセレクトされる。すなわち、制御信号が “0” の時は単位画素 2110 の外部へは撮像画像が出力され、“1” の時は単位画素 2110 のカウンタ 2104A のみの焦点検出用画素として計数結果が出力される。具体的な制御信号の遷移については後述する。

#### 【0120】

また、以後の説明を分かりやすくするために、A P D 2101A 及びクエンチ抵抗 2102A により生成される波形を A P D\_A とし、A P D 2101B 及びクエンチ抵抗 2102B により生成される波形を A P D\_B とする。また、波形整形回路 2103A の出力を P L S\_A とし、波形整形回路 2103B の出力を P L S\_B とする。

#### 【0121】

図 20 は、単位画素 2100, 2110 の駆動を示すタイミングチャートである。図 20 は、1 つの単位画素 2100, 2110 における撮像駆動とカウント値の推移を示しており、この駆動を複数の単位画素 2100, 2110 において並列して行うことにより、光学像をデジタル信号に変換する。

#### 【0122】

図 20 において、C N T\_R S T 及び C N T\_E N は駆動信号であり、カウンタ 2104A, 2104B の制御を行う。C N T\_R S T は “H” になることにより、カウンタ 2104A, 2104B のカウント値を “0” にリセットする。また、C N T\_E N が “H” となる期間のみ、カウンタ 2104A, 2104B はパルス数をカウントする。C N T\_A 及び C N T\_B はカウンタ 2104A, 2104B のカウント値を表す。

#### 【0123】

続いて、単位画素 2100, 2110 の駆動について説明する。

#### 【0124】

タイミング t2200 では、C N T\_R S T が “H” となりカウンタ 2104A, 2104B のカウント値が “0” にリセットされる。

#### 【0125】

10

20

30

40

50

タイミング t<sub>2201</sub>では、C N T \_ R S T が“L”になり、カウンタ 2104A, 2104B のリセットが終了する。同時に C N T \_ E N が“H”となりカウンタ 2104A, 2104B の電圧パルスのカウントが有効となる。これにより A P D 2101A, 2101B に入射した光子に応じた電圧パルスをカウントする期間である撮像期間が開始される。

#### 【0126】

タイミング t<sub>2202</sub>では、A P D 2101A に光子が入射したことにより、アバランシェ増倍された電荷が発生し A P D \_ A の電位が変化する。クエンチ抵抗 2102A を介して電荷を排出するので、A P D \_ A が再び一定の電位になるまで時間がかかる。波形整形回路 2103A では、A P D \_ A の立下りエッジを検出し、短時間の電圧パルスを生成する。この電圧パルスはカウンタ 2104A に入力され、カウンタ 2104A のカウント値が“1”となる。タイミング t<sub>2202</sub> ~ t<sub>2203</sub> の間の期間では、波形整形回路 2103A で生成された電圧パルスはカウンタ 2104A でカウントされ、波形整形回路 2103B で生成された電圧パルスはカウンタ 2104B でカウントされる。

#### 【0127】

タイミング t<sub>2203</sub>では、C N T \_ E N が“L”となり、撮像期間が終了する。終了した際のカウンタ 2104A, 2104B のカウント値は加算器 2105, 2108 を介して単位画素 2100, 2110 外へと出力される。あるいはセレクタ 2106, 2107 に入力され、その後加算器 2105, 2108 を介して単位画素 2100, 2110 外へと出力される。

#### 【0128】

次に、図 19 に戻って、本実施形態における撮像素子の構造について説明する。本実施形態では、マイクロレンズアレイを形成する個々のマイクロレンズ 2301 下を 1 つの画素と定義し、これを単位画素 2100, 2110 とする。また、1 つのマイクロレンズ 2301 に対して複数の分割画素が対応するように配置されている。なお、本実施形態では単位画素 2100, 2110 には分割画素が X 軸方向に 2 個配置されており、これらはそれぞれ A P D 2101A, 2101B に対応する。

#### 【0129】

続いて図 21 を参照して、本実施形態における瞳分割方式による焦点検出の原理について説明する。図 21 は、撮影レンズの射出瞳から出射した光束が単位画素に入射する様子を示す概念図である。前述したように、単位画素 2100 には A P D 2101A 及び A P D 2101B が配置されている。

#### 【0130】

図 21 に示すように、射出瞳 2400 から出射した光束は、光軸 Z を中心として、マイクロレンズ 2301 とカラーフィルタ 2401 を通して単位画素 2100 に入射する。射出瞳 2400 の一部の領域を示す瞳領域 2402A と瞳領域 2402B を通過する光束は、それぞれ A P D 2101A と A P D 2101B に入射する。したがって、A P D 2101A と A P D 2101B は、それぞれ撮影レンズの射出瞳の異なる領域の光を受光している。

#### 【0131】

このように構成される A P D 2101A の信号を X 軸方向に並ぶ複数の単位画素 2100 から取得し、これらの出力信号群で構成した被写体像を A 像とする。同様に A P D 2101B の信号を X 軸方向に並ぶ複数の単位画素 2100 から取得し、これらの出力信号群で構成した被写体像を B 像とする。得られた A 像と B 像に対して相関演算を実施し、像のずれ量（瞳分割位相差）を検出する。さらに像のずれ量に対して焦点位置と光学系から決まる変換係数を乗じることにより、画面内の任意の被写体位置に対応した焦点位置を算出することができる。ここで算出された焦点位置情報に基づいて不図示のフォーカスレンズを制御することにより撮像面位相差 A F が可能となる。なお、A 像信号と B 像信号との足し合わせを A + B 像信号とすることにより、この A + B 像信号を画像データに用いることができる。すなわち、A 像と B 像が焦点検出用画素の信号であり、A + B 像が撮像用画素の信号となる。

10

20

30

40

50

**【 0 1 3 2 】**

図 2 2 は、本実施形態の撮像装置の構成を示すブロック図である。

**【 0 1 3 3 】**

図 2 2 において、光学系 2 5 0 1 は、ズームレンズ、絞り、フォーカスレンズのうち少なくとも 1 つから構成され、被写体像を結像させる。光学系駆動部 2 5 0 2 は、後述する A F 制御部 2 5 0 8 から出力されるフォーカス情報や、システム制御部 2 5 0 9 の光学系駆動情報に応じて光学系 2 5 0 1 を制御する。撮像素子 2 5 0 3 は、被写体像を光電変換により電気信号に変換して、撮像画像または焦点検出用画像を出力する。撮像素子駆動部 2 5 0 4 は、システム制御部 2 5 0 9 からの撮像素子駆動指示情報に応じて、撮像素子 2 5 0 3 を制御する。なお、撮像素子 2 5 0 3 は、撮像素子駆動部 2 5 0 4 から出力されるセレクタ 2 1 0 6 , 2 1 0 7 を制御するための制御信号によって撮像画像信号または焦点検出用画像信号を出力する。

10

**【 0 1 3 4 】**

加算信号分離部 2 5 0 5 には、撮像素子 2 5 0 3 から出力される撮像用画素信号 (A + B 像) と焦点検出用画素信号 (A 像) が入力される。ここでは撮像用画素信号 (A + B 像) から焦点検出用画素信号 (A 像) を減算し、もう一方の焦点検出用画素信号 (B 像) を生成する。そして、2 つの焦点検出用画素信号 (A 像、B 像) が位相差検出部 2 5 0 7 に出力され、撮像用画素信号 (A + B 像) がカメラ信号処理部 2 5 0 6 に出力される。なお、詳細な説明は省略するが、撮像素子 2 5 0 3 からは撮像用画素信号 (A + B 像) 、焦点検出用画素信号 (A 像) のどちらかが順番に出力されるため、加算信号分離部 2 5 0 5 は、減算するにあたって 2 つの像信号を待ち合わせるためのメモリを備えている。

20

**【 0 1 3 5 】**

カメラ信号処理部 2 5 0 6 は、加算信号分離部 2 5 0 5 から得られた画像信号に対し、例えば、色変換処理、ホワイトバランス処理等の既知の画像処理を施す。カメラ信号処理部 2 5 0 6 で各種画像処理が施された画像信号は、不図示の圧縮手段により圧縮符号化され、記録媒体に記録される。ここで記録媒体は、撮像装置に対して着脱可能であってもよいし、撮像装置に内蔵されていてもよい。

**【 0 1 3 6 】**

位相差検出部 2 5 0 7 は、加算信号分離部 2 5 0 5 から得られた 2 つの瞳分割像から、位相差検出を行うための位相差評価値を算出する。A F 制御部 2 5 0 8 は、位相差検出部 2 5 0 7 から出力される位相差評価値に基づいて、光学系 2 5 0 1 のフォーカス位置を制御するためのフォーカス情報を算出する。

30

**【 0 1 3 7 】**

システム制御部 2 5 0 9 は、撮像装置全体を制御する。そして、撮影シーンや撮影モード（撮像モード）などから得られる撮影情報に基づいて、光学系駆動部 2 5 0 2 へズームや絞りなどの光学系の駆動情報を出力する。また、撮像素子駆動部 2 5 0 4 へ露光時間や瞳分割像の信号の読み出し開始位置や読み出し間隔など、撮像素子の駆動情報を出力する。

**【 0 1 3 8 】**

図 2 3 は、第 4 の実施形態における撮像素子 2 5 0 3 の駆動モード別の読み出し信号を示した図である。

40

**【 0 1 3 9 】**

図 2 3 ( a ) は、焦点検出用画素信号 (A 像) を読み出さない駆動モードでの読み出し信号を示した図である。読み出し信号は画像信号 (A + B 像) のみであり、計 4 ラインを読み出す。なお、この駆動モードの場合は、撮像面位相差方式の焦点検出は実施せず、例えば既知のコントラスト方式での焦点検出を行う。

**【 0 1 4 0 】**

図 2 3 ( b ) は、全ラインについて焦点検出用画素信号 (A 像) を読み出す駆動モードでの読み出し信号を示した図である。4 ライン分の焦点検出用画素信号 (A 像) と 4 ライン分の画像信号 (A + B 像) の計 8 ラインを読み出す。

**【 0 1 4 1 】**

50

図23(c)は、焦点検出用画素信号(A像)を間引きながら読み出す駆動モードでの読み出し信号を示した図である。焦点検出用画素信号(A像)を1ライン目と2ライン目のみ読み出して、3ライン目と4ライン目を読み出さないことにより、2ライン分の焦点検出用画素信号と4ライン分の画像信号(A+B像)の計6ラインを読み出す。

#### 【0142】

上記の場合、図23(a)は、読み出し量が最も少ない駆動モードであり、高フレームレートを実現する場合が想定される。図23(b)は、読み出し量が最も多い駆動モードであり、低フレームレートを実現する場合が想定される。図23(c)は、高フレームレートと低フレームレートの中間のフレームレートが想定される。

#### 【0143】

次に、図24を用いて図18のセレクタ2106, 2107の動作について説明する。図24(a)、(b)、(c)で示したセレクタの値は、図23(a)、(b)、(c)の駆動モードでの読み出しにそれぞれ対応している。VDはフレーム同期信号であり、フレーム同期信号VDがHになると、1フレーム分の露光期間が開始される。CNT\_RSTはカウンタ2104のリセット信号であり、“H”になると、カウンタ2104がリセットされ、“L”になるとリセットが解除される。CNT\_EN、PLS\_A、CNT\_Aは図20と同様であるため、説明は省略する。水平同期信号HDは読み出し期間になると供給され、水平同期信号HDが“H”になる毎に、画素領域の画素を1行ずつ順番に選択し、撮像素子2503の外部に信号が出力される。

#### 【0144】

ここで、セレクタ2106、セレクタ2107について説明する。

#### 【0145】

図24(a)は、セレクタ2106, 2107が“0”である場合を示し、図23(a)のA+B像しか読み出さない駆動モードに対応している。そのため、セレクタ2106, 2107は“0”的ままでカウンタ2104Bのカウント値を選択する。加算器2105, 2108では、カウンタ2104Aのカウント値とカウンタ2104Bのカウント値の加算を行い、A+B像を出力する。

#### 【0146】

図24(b)は、セレクタ2106が“2”、“0”、“2”、“0”を繰り返す場合を示し、図23(b)の駆動モードに対応している。具体的には、図23(b)では毎ラインA像とA+B像を読み出す。セレクタ2106を“2”に設定することにより「0」値が選択される。加算器2105にはカウンタAのカウント値と「0」値が入力され、加算器2105の出力はA像となる。一方、セレクタ2107は“1”、“0”、“1”、“0”を繰り返す。セレクタ2107を“1”に設定することにより「0」値が選択される。加算器2108にはカウンタAのカウント値と「0」値が入力され、加算器2108の出力はA像となる。なお、セレクタ2106, 2107が共に“0”に設定されると、加算器2105と加算器2108は、カウンタ2104Aのカウント値とカウンタ2104Bのカウント値の加算を行うこととなり、A+B像を出力する。

#### 【0147】

図24(c)は、セレクタ2106が“1”、“0”、“1”、“0”を繰り返す場合を示し、図23(c)の駆動モードに対応している。具体的には、図23(c)ではA像が間引いて読み出される。セレクタ2106を“1”に設定することにより、垂直方向に2ライン離れた同色のA像が選択される。加算器2105にはカウンタ2104Aのカウント値と垂直方向に2ライン離れた同色のカウンタ2104Aのカウント値が入力され、加算器2105の出力はA+A像となる。セレクタ2107は“0”的ままでカウンタ2104Bのカウント値を選択する。加算器2108にはカウンタAのカウント値とカウンタBのカウント値が入力され、加算器2108の出力はA+B像となる。

#### 【0148】

図24(c)では隣接した同色のA像同士を加算しているため、信号の強度として約2倍となる。一方でランダムノイズに関しては2倍にならないため、S/N比は向上する。

更に、1ライン目では3ライン目のA像を加算したA像、2ライン目では4ライン目のA像を加算したA像が読み出されるため、3ライン目、4ライン目に高コントラストの信号があってもその信号は1ライン目、2ライン目のA像に混ざる。すなわち、低コントラストの位置のみを読み出してしまうような被写体抜けが防止される。

#### 【0149】

以上説明したように、本実施形態の撮像装置では、撮像素子2503の駆動モードに応じて単位画素内の加算器の入力をセレクタで切り替えている。これにより、必要最小限の焦点検出用画素の読み出しを行い、システム負荷の軽減を図ると同時に、焦点検出精度を向上させることが可能となる。

#### 【0150】

##### (第5の実施形態)

図25は、本発明の第5の実施形態における単位画素2800, 2813の構成を示す回路図である。単位画素2800, 2813は、図26に示すように二次元状に配列されたマイクロレンズ2302下の1つの画素である。また、1つのマイクロレンズ2302下には1つのカラーフィルタが配置され、左上をR画素としたBaye配列を構成している。単位画素2800は左上(0, 0)のR画素、単位画素2813は単位画素2800から2画素下(0, 2)のR画素である。単位画素2800, 2813は、それぞれAPD2801A, 2801B, 2801C, 2801D、クエンチ抵抗2802A, 2802B, 2802C, 2802Dを備える。また、波形整形回路2803A, 2803B, 2803C, 2803D、カウンタ2804A, 2804B, 2804C, 2804D、4つのカウント値を加算する加算器2805, 2812を備える。さらに、加算器2805, 2812の入力信号を選択するセレクタ2806, 2807, 2808, 2809, 2810, 2811を備える。

#### 【0151】

単位画素2800, 2813には、受光素子としてのAPD2801が4つ配置されており、同一マイクロレンズを透過した光をAPD2801A, 2801B, 2801C, 2801Dがそれぞれ受光する。これにより、射出瞳の異なる領域の信号を得ることが可能である。また、4つの受光素子の信号を加算器2805, 2812により加算することにより、撮像用画像を生成する。APD、クエンチ抵抗、波形整形回路、カウンタに関しては第4の実施形態と同様であるため、説明を省略する。

#### 【0152】

セレクタ2806は、単位画素2800に入力される制御信号1により、3つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Bのカウント値がセレクトされ、“1”的場合、単位画素2813のカウンタ2804Cのカウント値がセレクトされ、“2”的場合、「0」値がセレクトされる。

#### 【0153】

セレクタ2807は、単位画素2800に入力される制御信号2により、3つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Cのカウント値がセレクトされ、“1”的場合、単位画素2813のカウンタ2804Bのカウント値がセレクトされ、“2”的場合、「0」値がセレクトされる。

#### 【0154】

セレクタ2808は、単位画素2800に入力される制御信号3により、3つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Dのカウント値がセレクトされ、“1”的場合、単位画素2813のカウンタ2804Aのカウント値がセレクトされ、“2”的場合、「0」値がセレクトされる。

#### 【0155】

セレクタ2809は、単位画素2813に入力される制御信号1により、2つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Bのカウント値がセレクトされ、“1”的場合、「0」値がセレクトされる。

#### 【0156】

10

20

30

40

50

セレクタ2810は、単位画素2813に入力される制御信号2により、2つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Cのカウント値がセレクトされ、“1”的場合、「0」値がセレクトされる。

#### 【0157】

セレクタ2811は、単位画素2813に入力される制御信号3により、2つの入力のセレクトを行う。制御信号が“0”的場合、カウンタ2804Dのカウント値がセレクトされ、“1”的場合、「0」値がセレクトされる。

#### 【0158】

ここで、セレクタ2806からセレクタ2811の全てに制御信号“0”が入力されたとする。この場合、加算器2805の入力は、単位画素2800のカウンタ2804A、カウンタ2804B、カウンタ2804C、カウンタ2804Dのカウント値となり、加算した結果、 $A + B + C + D$ 像が生成される。加算器2812も同様に、入力は単位画素2813のカウンタ2804A、カウンタ2804B、カウンタ2804C、カウンタ2804Dのカウント値となり、加算した結果、 $A + B + C + D$ 像が生成される。前述したように4つの受光素子の信号を全て加算することにより、撮像用画素信号が生成されるため、 $A + B + C + D$ 像は撮像用画素信号となる。10

#### 【0159】

次に、セレクタ2806を“2”、セレクタ2807を“0”、セレクタ2808を“2”、セレクタ2809を“1”、セレクタ2810を“0”、セレクタ2811を“1”と設定した場合について説明する。この場合、加算器2805の入力は、単位画素2800のカウンタ2804Aとカウンタ2804Cのみのカウント値となり、加算した結果、 $A + C$ 像が生成される。加算器2812も同様に、入力は単位画素2813のカウンタ2804A、カウンタ2804Cのカウント値となり、加算した結果、 $A + C$ 像が生成される。20

#### 【0160】

撮像素子2503から出力される撮像用画素信号( $A + B + C + D$ 像)と焦点検出用画素信号( $A + C$ 像)が加算信号分離部2505に入力される。加算信号分離部2505によって、撮像用画素信号( $A + B + C + D$ 像)から焦点検出用画素信号( $A + C$ 像)を減算し、もう一方の焦点検出用画素信号( $B + D$ 像)を生成する。2つの焦点検出用画素信号( $A + C$ 像、 $B + D$ 像)を位相差検出部2507に入力し、水平方向に瞳分割された2つの瞳分割像から位相差検出を行うための位相差評価値を算出する。30

#### 【0161】

また、セレクタ2806を“0”、セレクタ2807を“2”、セレクタ2808を“2”、セレクタ2809を“0”、セレクタ2810を“1”、セレクタ2811を“1”と設定した場合について説明する。この場合、加算器2805の入力は、単位画素2800のカウンタ2804Aとカウンタ2804Bのみのカウント値となり、加算した結果、 $A + B$ 像が生成される。加算器2812も同様に、入力は単位画素2813のカウンタ2804A、カウンタ2804Bのカウント値となり、加算した結果、 $A + B$ 像が生成される。

#### 【0162】

こちらも加算信号分離部2505によって、撮像用画素信号( $A + B + C + D$ 像)から焦点検出用画素信号( $A + B$ 像)を減算し、もう一方の焦点検出用画素信号( $C + D$ 像)を生成する。2つの焦点検出用画素信号( $A + B$ 像、 $C + D$ 像)を位相差検出部2507に入力し、垂直方向に瞳分割された2つの瞳分割像から位相差検出を行うための位相差評価値を算出する。40

#### 【0163】

さらに、セレクタ2806を“1”、セレクタ2807を“0”、セレクタ2808を“1”と設定した場合について説明する。この場合、加算器2805の入力は単位画素2800のカウンタ2804Aとカウンタ2804C、単位画素2813のカウンタ2804Aとカウンタ2804Cのカウント値となる。そして、加算した結果、単位画素2800の( $A + C$ 像)+単位画素2813の( $A + C$ 像)となる。このようにセレクタを制御することにより、第4の実施形態と同様に、隣接した同色の $A + C$ 像同士を加算することができ50

、信号の強度として約2倍となる。一方でランダムノイズに関しては2倍にならないため、S/N比は向上する。

#### 【0164】

さらに、1ライン目では3ライン目のA+C像を加算したA+C像、2ライン目では4ライン目のA+C像を加算したA+C像が読み出される。そのため、3ライン目、4ライン目に高コントラストの信号があってもその信号は1ライン目、2ライン目のA+C像に混ざる。すなわち、低コントラストの位置のみを読み出してしまうことによる被写体抜けを防止することができる。

#### 【0165】

図26に戻って、本実施形態における撮像素子の構造について説明する。本実施形態では、マイクロレンズアレイを形成する個々のマイクロレンズ2302下を1つの画素と定義し、これを単位画素2800, 2813とする。また、1つのマイクロレンズ2302に対して複数の分割画素が対応するように配置されている。なお、本実施形態では単位画素2800, 2813には分割画素がX軸方向に2個、Y軸方向に2個配置されており、これらはそれぞれAPD2801A, 2801B, 2801C, 2801Dに対応する。

10

#### 【0166】

1画素が4つの受光素子の信号に分かれているため、撮像素子2503の駆動モードに応じて単位画素内の加算器の入力をセレクタで切り替えることにより、水平方向、垂直方向の位相差検出を行うことも可能となる。

#### 【0167】

以上説明したように、本実施形態の撮像装置は、撮像素子2503の駆動モードに応じて単位画素内の加算器の入力をセレクタで切り替える。これにより、必要最小限の焦点検出用画素の読み出しを行い、システム負荷の軽減を図ると同時に、焦点検出精度を向上させることが可能となる。

20

#### 【0168】

##### (第6の実施形態)

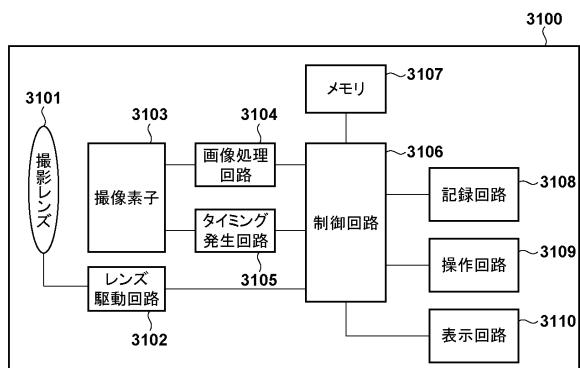

以下、本発明の第6の実施形態について説明する。図27は、本発明の第6の実施形態に係わる撮像装置3100の構成を示すブロック図である。

#### 【0169】

図27において、レンズ部3101は、被写体の光学像を撮像素子3103に結像させる。レンズ部3101は、レンズ駆動回路3102によってズーム制御、フォーカス制御、絞り制御などが行われる。撮像素子3103は、レンズ部3101により結像された被写体像を光電変換して画像信号を出力する。画像処理回路3104は、撮像素子3103から出力される画像信号に各種の補正処理や現像処理を行うとともに、データ圧縮のための演算等を行う。タイミング発生回路3105は、撮像素子3103に各種タイミング信号を出力して駆動する。制御回路3106は、様々な演算などを行い、撮像装置全体の制御と監視を行う。メモリ3107は画像データを一時的に記憶し、制御回路3106の作業領域としても使用される。記録回路3108は、半導体メモリ等の着脱可能な記録媒体に記録または記録媒体から読み出しを行うための回路である。操作回路3109は、ユーザーからの命令を受け付け、それを制御回路3106に伝達する。表示回路3110は、各種情報や撮影画像を表示する。

30

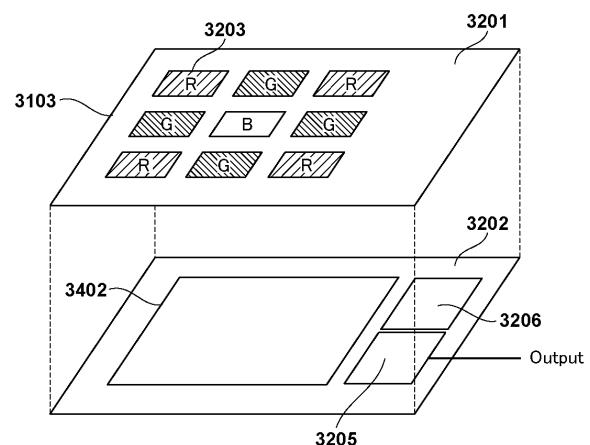

#### 【0170】

次に、図28は、第6の実施形態における撮像素子3103の構成を示す図である。撮像素子3103はセンサ基板3201と回路基板3202を備える積層構造である。なお、同様の機能を備えるならば積層構造に限らず単層構造の素子であってもよい。

#### 【0171】

センサ基板3201には、単位画素3203が行列方向に配置された画素アレイが形成される。この単位画素3203には、色分離のためそれぞれR(赤)、G(緑)、B(青)のカラーフィルタが配置されている。また入射光の集光効率を向上させるための不図示のマイクロレンズも配置されている。なお、単位画素3203の詳細な回路構成について

40

50

は後述する。

#### 【0172】

回路基板3202は、計数部3402、信号処理回路3205、基板メモリ3206を備えて構成される。計数部3402はセンサ基板3201の単位画素毎にバンプ等で電気的に接続され、単位画素3203を駆動する制御信号を出力すると共に、画素からのバッファ出力を受信する。計数部3402は、対応する単位画素毎に、あるしきい値 $V_{th}$ によりフォトンの有無を判定する比較器3304及びカウンタ3305を備え(図29参照)、入射されたフォトンに応じて出力されるパルス数を計測する。計数部3402で計測されたカウント値は、信号処理回路3205によって各種演算処理や外部出力処理が行われる。また基板メモリ3206はDRAM等の揮発性メモリであり、計数部3402からの信号を信号処理回路3205で処理する際に一時的にデータを保持する等の目的で用いられる。10

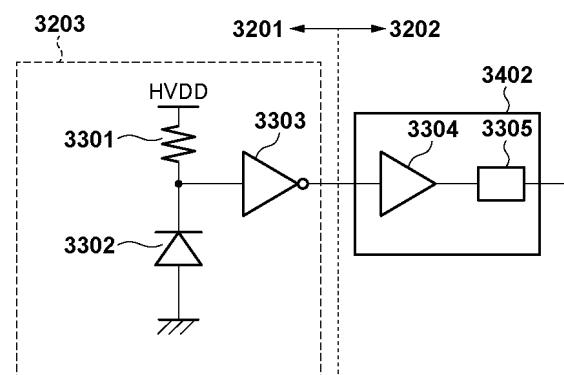

#### 【0173】

次に、図29は、センサ基板3201に形成される単位画素3203の等価回路図である。本実施形態では、アバランシェフォトダイオードを用いた構成を例として説明するが、画素単位でAD変換を実現する形式としてはこれに限定されるものではない。

#### 【0174】

単位画素3203は、クエンチ抵抗3301、アバランシェフォトダイオード(以下、APD)3302、バッファ3303を備えて構成される。APD3302には、クエンチ抵抗を介して電圧HVDによる逆バイアス電圧が印加される。このとき電圧HVDは、APDをガイガーモードにするための降伏電圧以上となるように設定される。バッファ3303の出力は計数部3402内の比較器3304により基準電圧と比較され、比較結果がカウンタ3305に入力される。20

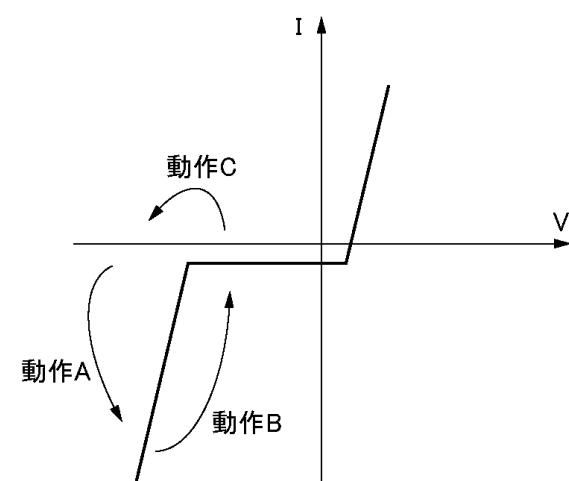

#### 【0175】

ここで図30を用いてフォトン入射時の単位画素3203の動作について説明する。図30はAPDの電流電圧特性を示している。本実施形態では、APD3302のカソードは降伏電圧を超える電圧HVDに接続され、APD3302はガイガーモードとなる。ここでAPD3302にフォトンが入射すると、APD3302ではアバランシェ増幅による大電流(光電流)が流れる(動作A)。この電流が流れると同時にクエンチ抵抗3301によって電圧降下が発生し、APD3302に印加される電圧が降伏電圧未満となり、アバランシェ増幅が止まる(動作B)。アバランシェ増幅が止まると、APD3302のカソードは再び電圧HVDによりチャージされ、ガイガーモードに戻る(動作C)。動作A~Cによるバッファ入力端の電圧変化はバッファ3303によってパルス整形され、較器3304、カウンタ3305によって計測される。これを繰り返すことによりAPD3302に入射したフォトンの数を計測することが可能となる。30

#### 【0176】

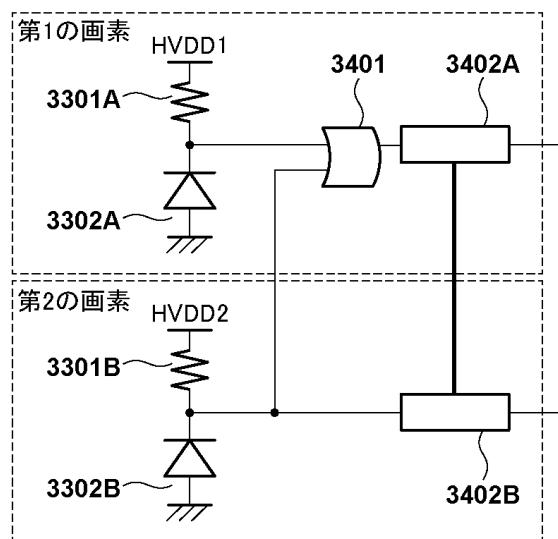

図31は、第6の実施形態における回路構成を示す模式図である。図31は、ベイヤー配列されたセンサ基板3201の同色の単位画素3203を2画素混合する組み合わせにおける接続パターンを示している。

#### 【0177】

ここで、クエンチ抵抗3301A、3301B、APD3302A、3302Bは、図29と同様であり、バッファ3303は図示を省略している。計数部3402Aは第1の画素に対応する計数部(比較器及びカウンタからなるカウンタ部)であり、計数部3402Bは第2の画素に対応する計数部である。ここで計数部3402Aには第1の画素からの信号に加え、第2の画素からの信号がOR回路3401を介して接続されている。なお、計数部3402AはN+1ビット(ビット長)のカウンタを備え、計数部3402BはNビット(ビット長)のカウンタを備える。これは、計数部3402Aは2画素分の信号をカウントするためである。Nは撮像装置に求められる階調性によって決定され、一般的には例えば14や12などである。40

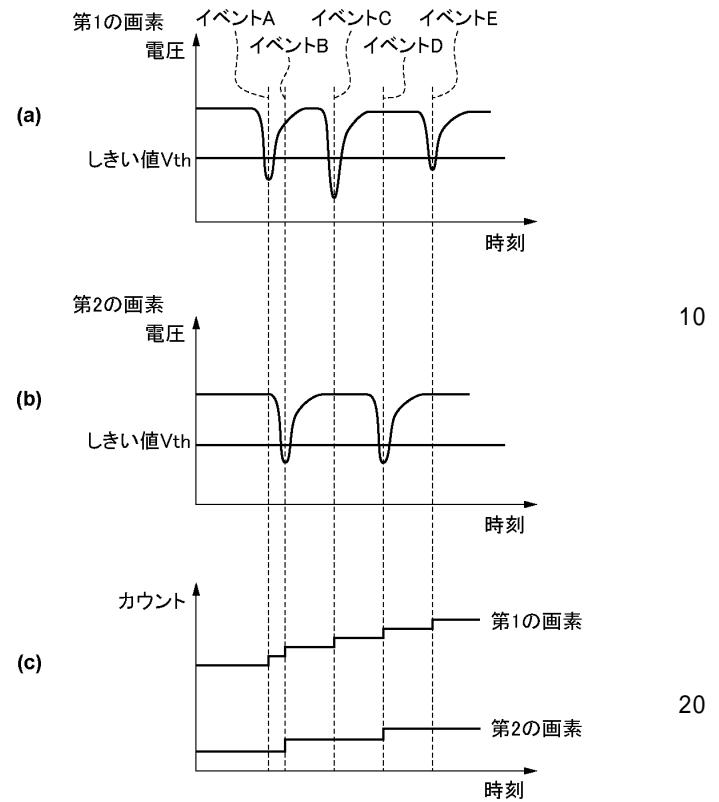

#### 【0178】

続いて、図32を用いて各画素から出力されるパルスとカウントとの関係について説明する。図32は、横軸を時間としてフォトン入射時のパルス波形と計数部3402A、3402Bでカウントされるカウント数を示す模式図である。

#### 【0179】

ここで図32(a)は、第1の画素に光子イベントA、C、Eが入射した場合を表す。また、図32(b)は第2の画素に光子イベントB、Dが入射した場合を表す。それぞれのイベントは、比較器のしきい値 $V_{th}$ を超えるパルスが outputされる程度のアバランシェ増幅を発生させ、それぞれのパルスは時間分解されているとする。

#### 【0180】

まず第1の画素においては、第1の画素による光子イベントA、C、Eと第2の画素による光子イベントB、DがORによって全てカウントされ、この例では5カウントとして出力される。一方、第2の画素においては、第2の画素による光子イベントB、Dのみがカウントされ、この例では2カウントとして出力される。

10

#### 【0181】

上記構成における各画素の信号出力を以下のように表現するものとする。まず第1の画素においては、第1の画素による光子イベントと第2の画素による光子イベントがORによって全てカウントされる。この時のカウントを $A + B$ と置く。一方、第2の画素においては、第2の画素による光子イベントのみがカウントされる。この時のカウントを $B$ と置く。このように、本実施形態では、OR回路を介して他の画素のパルスをカウントすることにより、画素混合( $A + B$ )を第1の画素で実現している。さらに、画素混合出力を得ることのみを目的とするならば、計数部3402Aのみでカウント動作を行えばよいため、計数部3402Bを非動作(停止:パワーセーブ)とすることにより消費電力を削減することができる。

20

#### 【0182】

ここで、本実施形態の形式ではなく通常のNビットの画素で画素混合する場合を考える。この場合、第1の画素(Nビット)と第2の画素(Nビット)の両者を出力して画素混合するため、 $N + N = 2N$ ビットのデータ転送が必要になる。一方、本形態では $N + 1$ ビットで所望の信号が得られるため、データ転送量の削減も図ることができる。

#### 【0183】

なお、計数部3402Aとともに計数部3402Bを動作させ、第1の画素カウント( $A + B$ )から第2の画素カウント( $B$ )を減算することにより、画素混合しない第1の画素のカウント( $A + B - B = A$ )を算出することも可能である。撮像装置においては、前述の画素混合出力(画素混合モード)は主に動画モードで用いられ、画素混合しない信号出力(非画素混合モード)は主に静止画モードで用いられる。

30

#### 【0184】

さらには、第1の画素と第2の画素が一つのマイクロレンズを共有したいわゆる複画素構造においても本実施形態を適用することができる。本発明の主題から離れるため詳細は省略するが、複画素構造は撮像面位相差AFを実現するための構造である。例えば前述の画素混合出力は撮像面位相差AFを行わない通常撮影モードに適用される。また前述の画素混合しない信号出力は瞳分割された各画素の信号を分離して読み出すことができるため、主にAFモード(焦点検出画像の読み出しモード)で用いられる。

40

#### 【0185】

以上のように、本実施形態によれば、画素単位でAD変換を行う構成におけるデータ転送効率を改善し、消費電力を抑制しつつ、画素混合を実現することが可能となる。

#### 【0186】

##### (第6の実施形態の変形例)

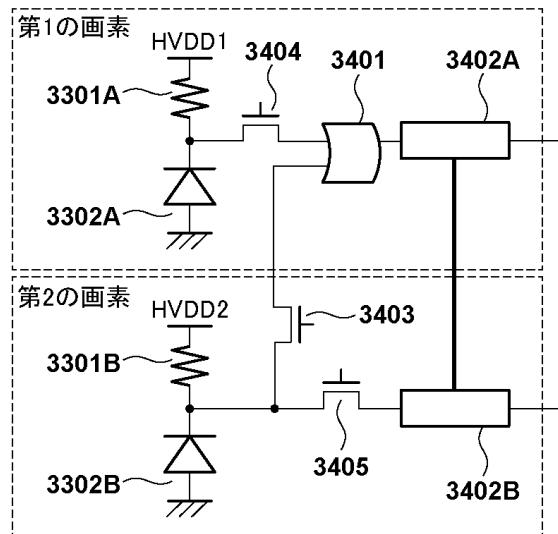

図33は、第6の実施形態の変形例を示す図である。図33は、ベイヤー配列されたセンサ基板3201の同色の単位画素3203を2画素混合する組み合わせにおける接続パターンを示している。

#### 【0187】

50

第6の実施形態を示す図31との違いは、APD3302A及びAPD3302BとOR回路3401との間にそれぞれ切り離しスイッチ3404, 3403を設け、APD3302Bと計数部3402Bとの間に切り離しスイッチ3405を設けた点である。

#### 【0188】

この構成において、切り離しスイッチ3403をオフにすることにより、画素混合しない通常の信号読み出しが可能となる。また、切り離しスイッチ3405をオフとし、計数部3402B(Nビット)のカウンタを計数部3402Aのカウンタ(N+1ビット)に接続する。このように計数部3402Aのカウンタと計数部3402Bのカウンタとを接続して単一のカウンタ(合計のビット数: 2N+1ビット)として機能させることにより、撮像素子のダイナミックレンジ(AD飽和)を拡大させることが可能となる。

10

#### 【0189】

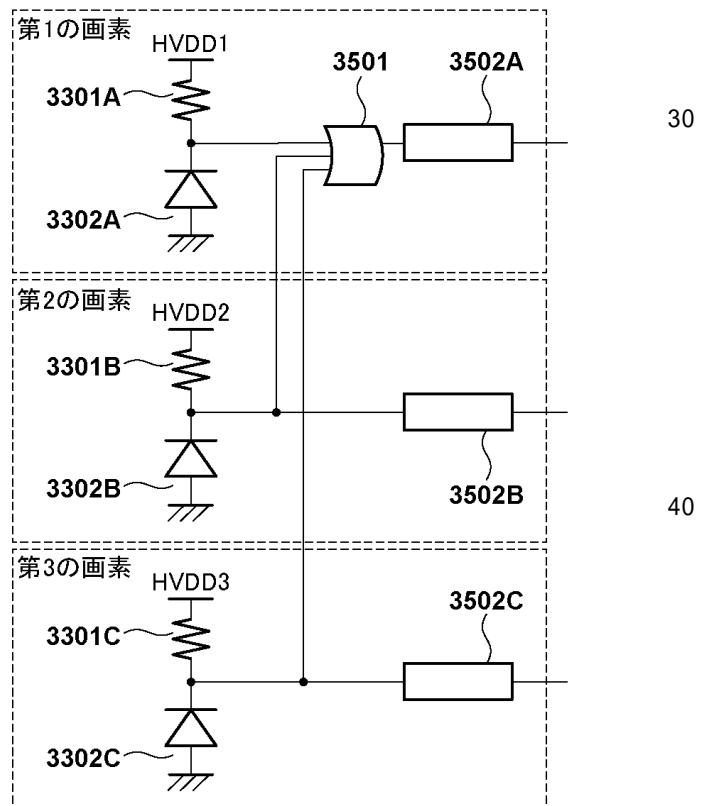

##### (第7の実施形態)

図34は、本発明の第7の実施形態における回路構成を示す模式図である。図34は、ペイヤー配列されたセンサ基板3201の同色の単位画素3203を3画素混合する組み合わせにおける接続パターンを示している。

#### 【0190】

計数部3502Aは、第1の画素に対応する計数部(比較器及びカウンタ)であり、計数部3502B, 3502Cは、それぞれ第2、第3の画素に対応する計数部である。計数部3502Aには、第1の画素からの信号に加え、第2、第3の画素からの信号がOR回路3501を介して接続されている。なお、計数部3502AはN+2ビットのカウンタを備える。また計数部3502B, 3502CはNビットのカウンタを備える。これは、計数部3502Aは3画素分の信号をカウントするためである。

20

#### 【0191】

上記構成における各画素の信号出力を以下のように表現するものとする。まず第1の画素においては、第1の画素による光子イベントと第2、第3の画素による光子イベントがORによって全てカウントされる。この時のカウントをA+B+Cと置く。一方、第2の画素においては、第2の画素による光子イベントのみがカウントされる。この時のカウントをBと置く。同様に第3の画素のカウントをCと置く。このように、本実施形態では、OR回路を介して他の画素のパルスをカウントすることにより、画素混合(A+B+C)を第1の画素で実現している。さらに、画素混合出力を得ることのみを目的とするならば、計数部3502Aのみでカウント動作を行えばよいため、計数部3502B, 3502Cを非動作(パワーセーブ)とすることにより消費電力を削減することができる。

30

#### 【0192】

ここで、本実施形態の形式ではなく通常のNビットの画素で画素混合する場合を考える。この場合、第1の画素(Nビット)と第2、第3の画素(Nビット)の全てを出力して画素混合するため、 $N+N+N=3N$ ビットのデータ転送が必要になる。一方、本実施形態ではN+2ビットで所望の信号が得られるため、データ転送量の削減も図ることができる。

#### 【0193】

なお、計数部3502Aとともに計数部3502B, 3502Cを動作させ、第1の画素カウント(A+B+C)から第2、第3の画素カウント(B, C)を減算することにより、画素混合しない第1の画素のカウント(A+B+C - B - C = A)を算出することも可能である。

40

#### 【0194】

さらには、計数部3502Aとともに混合重心となる計数部3502Bを動作させ、第1の画素カウント(A+B+C)に第2の画素カウント(B)を加算することにより、重みづけ画素混合信号(A+B+C+B = A+2B+C)を算出することも可能である。この場合は、第1から第3の画素すべてを出力してから重みづけ画素混合信号を生成するのに対して、計数部3502Cの消費電力とデータ転送量を削減できる。

#### 【0195】

50

重みづけ加算の他の形態としては、混合重心となる第2の画素のH V D Dを第1、第3の画素のH V D Dより高くし、フォトンの検出確率を増大させる方法を用いてもよい。またO R回路3 5 0 1の論理しきい値や、計数部内の比較器の判定しきい値を第2の画素と第1、第3の画素で変更できる構成としてもよい。

#### 【0196】

以上のように、第7の実施形態によれば、画素単位でA D変換を行う構成におけるデータ転送効率を改善し、消費電力を抑制しつつ、画素混合を実現することが可能となる。

#### 【0197】

##### (第8の実施形態)

図3 5は、第8の実施形態における撮像素子の回路構成を示す図である。図3 5は、ベイダー配列されたセンサ基板3 2 0 1の同色の単位画素3 2 0 3を、2画素または3画素混合する組み合わせにおける接続パターンを示している。

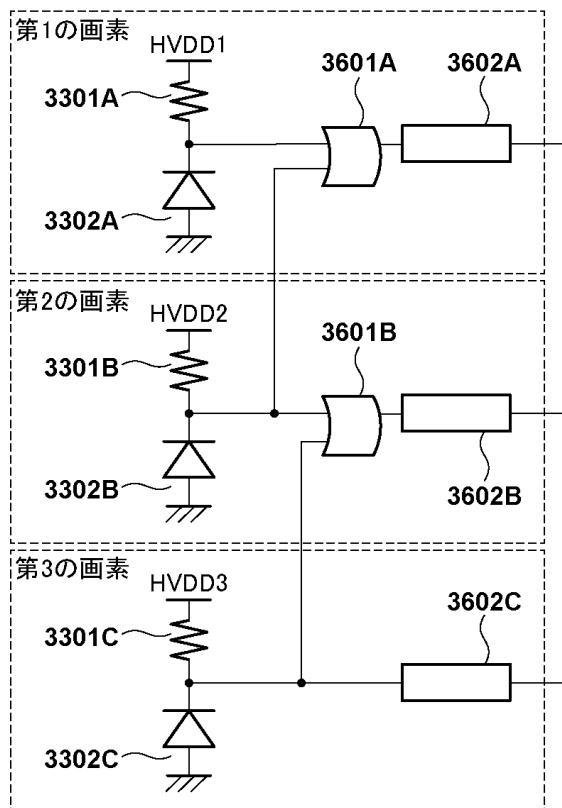

#### 【0198】

計数部3 6 0 2 Aは、第1の画素に対応する計数部(比較器及びカウンタ)であり、計数部3 6 0 2 B, 3 6 0 2 Cは、それぞれ第2、第3の画素に対応する計数部である。計数部3 6 0 2 Aには第1の画素からの信号に加え、第2の画素からの信号がO R回路3 6 0 1 Aを介して接続されている。計数部3 6 0 2 Bには、第2の画素からの信号に加え、第3の画素からの信号がO R回路3 6 0 1 Bを介して接続されている。なお、計数部3 6 0 2 A, 3 6 0 2 BはN + 1ビットのカウンタを備える。また計数部3 6 0 2 CはNビットのカウンタを備える。これは、計数部3 6 0 2 A, 3 6 0 2 Bは2画素分の信号をカウントするためである。

#### 【0199】

上記構成における各画素の信号出力を以下のように表現するものとする。まず第1の画素においては、第1の画素による光子イベントと第2の画素による光子イベントがO Rによって全てカウントされる。この時のカウントをA + Bと置く。一方、第2の画素においては、第2の画素による光子イベントと第3の画素による光子イベントがO Rによって全てカウントされる。この時のカウントをB + Cと置く。一方、第3の画素においては、第3の画素による光子イベントのみがカウントされる。この時のカウントをCと置く。

#### 【0200】

このように、本実施形態では、O R回路を介して他の画素のパルスをカウントすることにより、画素混合(A + BまたはB + C)を第1または第2の画素で実現している。さらに、画素混合出力(A + B)を得ることのみを目的とするならば、計数部3 6 0 2 Aのみでカウント動作を行えばよいため、計数部3 6 0 2 B, 3 6 0 2 Cを非動作(パワーセーブ)とすることにより消費電力を削減することができる。また画素混合出力(B + C)を得ることのみを目的とするならば、計数部3 6 0 2 Bのみでカウント動作を行えばよいため、計数部3 6 0 2 A, 3 6 0 2 Cを非動作(パワーセーブ)とすることにより消費電力を削減することができる。

#### 【0201】

なお、計数部3 6 0 2 Aとともに計数部3 6 0 2 B, 3 6 0 2 Cを動作させ、第2の画素カウント(B + C)から第3の画素カウント(C)を減算することにより、画素混合しない第2の画素のカウント(B + C - C = B)を算出することも可能である。続けて画素混合しない第1の画素のカウント(A + B - B = A)を算出することも可能である。

#### 【0202】

さらには、計数部3 6 0 2 Aとともに混合重心となる計数部3 6 0 2 Bを動作させ、第1の画素カウント(A + B)に第2の画素カウント(B + C)を加算することにより、重みづけ画素混合信号(A + B + B + C = A + 2 B + C)を算出することも可能である。この場合は、第1から第3の画素すべてを出力してから重みづけ画素混合信号を生成するのに対して、計数部3 6 0 2 Cの消費電力とデータ転送量を削減できる。

#### 【0203】

ここで、本実施形態の形式ではなく通常のNビットの画素で画素混合する場合を考える

10

20

30

40

50

。この時、第1、第2の画素（Nビット）と第3の画素（Nビット）の全てを出力して画素混合するため、 $N + N + N = 3N$ ビットのデータ転送が必要になる。一方、本実施形態では画素混合出力（A + B）または画素混合出力（B + C）の場合はN + 1ビット、画素混合出力（A + 2B + C）の場合は $N + 1 + N + 1 = 2N + 2$ ビットで所望の信号が得られるため、データ転送量の削減も図ることができる。

#### 【0204】

以上のように、第8の実施形態によれば、画素単位でAD変換を行う構成におけるデータ転送効率を改善し、消費電力を抑制しつつ、画素混合を実現することが可能となる。

#### 【0205】

（第9の実施形態）

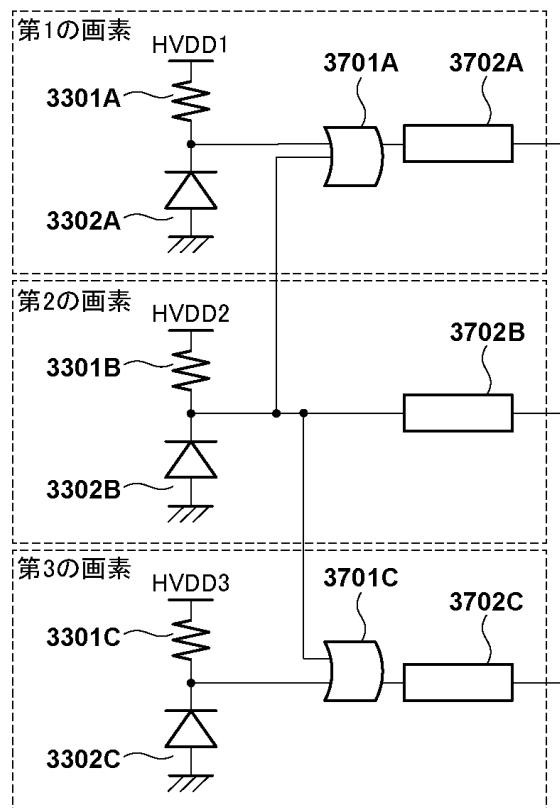

10

図36は、本発明の第9の実施形態における撮像素子の回路構成を示す図である。図36は、ベイラー配列されたセンサ基板3201の同色の単位画素3203を2画素または3画素混合する組み合わせにおける接続パターンを示している。

#### 【0206】

カウンタ3702Aは、第1の画素に対応する計数部（比較器及びカウンタ）であり、計数部3702B, 3702Cは、それぞれ第2、第3の画素に対応する計数部である。計数部3702Aには第1の画素からの信号に加え、第2の画素からの信号がOR回路3701Aを介して接続されている。計数部3702Cには第3の画素からの信号に加え、第2の画素からの信号がOR回路3701Cを介して接続されている。なお、計数部3702A, 3702Cは、N+1ビットのカウンタを備える。また計数部3702BはNビットのカウンタを備える。これは、計数部3702A, 3702Cは2画素分の信号をカウントするためである。

20

#### 【0207】

上記構成における各画素の信号出力を以下のように表現するものとする。まず第1の画素においては、第1の画素による光子イベントと第2の画素による光子イベントがORによって全てカウントされる。この時のカウントをA+Bと置く。第2の画素においては、第2の画素による光子イベントのみがカウントされる。この時のカウントをBと置く。さらに、第3の画素においては、第3の画素による光子イベントと第2の画素による光子イベントがORによって全てカウントされる。この時のカウントをB+Cと置く。

30

#### 【0208】

このように、本実施形態では、OR回路を介して他の画素のパルスをカウントすることで、画素混合（A + BまたはB + C）を第1または第3の画素で実現している。さらに、画素混合出力（A + B）を得ることのみを目的とするならば、計数部3702Aのみでカウント動作を行えばよいため、計数部3702B, 3702Cを非動作（パワーセーブ）とすることで消費電力を削減することができる。また画素混合出力（B + C）を得ることのみを目的とするならば、計数部3702Cのみでカウント動作を行えばよいため、計数部3702A, 3702Bを非動作（パワーセーブ）とすることにより、消費電力を削減することができる。

#### 【0209】

なお、計数部3702Aとともに計数部3702B, 3702Cを動作させ、第1の画素カウント（A + B）から第2の画素カウント（B）を減算することにより、画素混合しない第1の画素のカウント（A + B - B = A）を算出することも可能である。同様に画素混合しない第3の画素のカウント（B + C - B = C）を算出することも可能である。さらには、計数部3702Aとともに計数部3702Cを動作させ、第1の画素カウント（A + B）に第3の画素カウント（B + C）を加算することにより、重みづけ画素混合信号（A + B + B + C = A + 2B + C）を算出することも可能である。この場合は、第1から第3の画素全てを出力してから重みづけ画素混合信号を生成するのに対して、計数部3702Bの消費電力とデータ転送量を削減することができる。

40

#### 【0210】

ここで、本実施形態の形式ではなく通常のNビットの画素で画素混合する場合を考える

50

。この場合、第1、第3の画素（それぞれNビット）と第2の画素（Nビット）の全てを出力して画素混合するため、 $N + N + N = 3N$ ビットのデータ転送が必要になる。一方、本実施形態では、画素混合出力（A+B）または画素混合出力（B+C）の場合はN+1ビット、画素混合出力（A+2B+C）の場合は $N + 1 + N + 1 = 2N + 2$ ビットで所望の信号が得られるため、データ転送量の削減も図ることができる。

#### 【0211】

以上のように、第9の実施形態によれば、画素単位でA/D変換を行う構成におけるデータ転送効率を改善し、消費電力を抑制しつつ、画素混合を実現することができる。

#### 【0212】

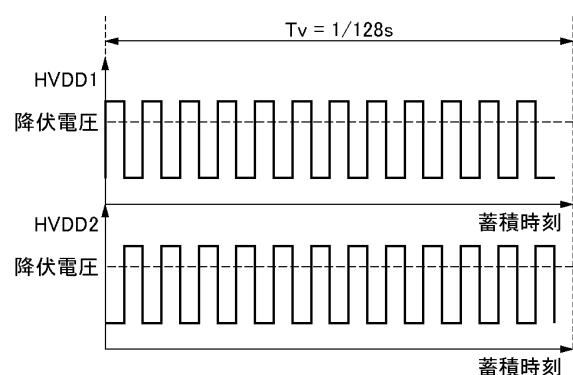

（第10の実施形態）

10

図37は、本発明の第10の実施形態における電圧HVDの供給方法を示す模式図である。図37は、第6の実施形態の第1の画素に供給するHVD1と第2の画素に供給するHVD2の単位蓄積時間当たりの変化を示している。

#### 【0213】

この例では、一つの単位蓄積時間を $T_v = 1 / 128\text{ s}$ としており、この時間内にAPD3302A, 3302Bに入射したフォトンの数を計数する。例えば、フレームレート $120\text{ f p s}$ 相当の動画像を出力する場合はこの蓄積時間を最大蓄積時間として順次読み出しを継続する。なお、蓄積時間は最大蓄積時間の範囲内で任意に決められる。

#### 【0214】

ところで、第6の実施形態での課題は、APD3302A, 3302Bに同時刻にフォトンが入射すると計数部3402Aでパルスの分離ができず、二つのカウントが一つしか計数されないことである。

20

#### 【0215】

この課題を解決するために、本実施形態では、APDに降伏電圧以上の逆バイアス電圧をパルス状に印加するGGM（Gated Geiger Mode）方式を、APD3302A, 3302Bに半位相ずらして適用している。GGM方式は逆バイアス電圧を印加するゲート周期を例えば $10\text{ n s}$ 、振幅 $1\text{ V}$ 以上で2値にAC変調させ、パルスを時間分解する技術である。この逆バイアス電圧は最大では降伏電圧以上であり、最小では降伏電圧以下となる。

#### 【0216】

30

HVDが降伏電圧以上でなければフォトンが入射しても計数可能なパルスは出力されないため、電圧変調によりAPD3302A, 3302Bの計数可能時刻を規定することができる。このようにGGM方式の位相をずらして各画素に適用することにより、入射したフォトンを時間分解するだけでなく、第1と第2の画素で排他計測することが可能となる。

#### 【0217】

なお、第1と第2の画素で位相をずらす構成はHVDのゲーティングのみに限られず、切り離しスイッチ3404, 3405のオンオフやイネーブル回路を設けて時刻差をつける構成等でも構わない。

#### 【0218】

40

また、上記の実施形態では、2画素混合、3画素混合について説明したが、本発明は、2画素混合、3画素混合に限定されるものではない。

#### 【0219】

（他の実施形態）

また本発明は、上述の実施形態の1以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける1つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現できる。また、1以上の機能を実現する回路（例えば、ASIC）によっても実現できる。

#### 【0220】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱すること

50

なく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を添付する。

【符号の説明】

【0221】

100：単位画素、101A, 101B：アバランシェフォトダイオード（APD）、102A, 102B：クエンチ抵抗、103A, 103B：波形整形回路、104AB：OR回路、105A, 105AB：カウンタ

10

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

## 【図 3 A】

## 【図 3 B】

20

30

40

50

【図4】

【図5】

10

20

【図6】

【図7】

30

40

50

【図 8】

【図 9】

10

【図 10】

【図 11】

20

30

40

50

【図 1 2】

【図 1 3】

10

画素部

20

【図 1 4 A】

【図 1 4 B】

30

40

50

【図15】

【図16】

10

【図17】

【図18】

20

30

40

50

【図 19】

【図 20】

10

【図 21】

【図 22】

20

30

40

50

【図23】

【図24】

【図25】

【図26】

【図 2 7】

【図 2 8】

10

【図 2 9】

【図 3 0】

20

30

40

50

【図 3 1】

【図 3 2】

【図 3 3】

【図 3 4】

【図 3 5】

【図 3 6】

10

20

30

【図 3 7】

40

50

---

フロントページの続き

(56)参考文献      特開2012-191400 (JP, A)

特開2016-144183 (JP, A)

特開2016-019157 (JP, A)

特開2018-157387 (JP, A)

特開2015-128215 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H04N 25/00 - 25/79