**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) . Int. Cl.<sup>8</sup>

*H03F 3/04* (2006.01)

(11) 공개번호 10-2006-0016079

(43) 공개일자 2006년02월21일

---

|             |                   |             |                |

|-------------|-------------------|-------------|----------------|

| (21) 출원번호   | 10-2005-7018456   | (87) 국제공개번호 | WO 2004/091095 |

| (22) 출원일자   | 2005년09월29일       | 국제공개일자      | 2004년10월21일    |

| 번역문 제출일자    | 2005년09월29일       |             |                |

| (86) 국제출원번호 | PCT/US2004/010013 |             |                |

| 국제출원일자      | 2004년04월02일       |             |                |

---

(30) 우선권주장 10/406,334 2003년04월03일 미국(US)

(71) 출원인 폐어차일드 세미컨덕터 코포레이션

미국 매인 04106 사우스 포틀랜드 러닝 힐 로드 82

(72) 발명자 테팔코, 존 에이.

미합중국 01752 메사추세츠주 말보로우 퀸즈 뷰 로드 25

시로코브, 미하일 에스.

미합중국 01744 메사추세츠주 메튠 리버사이드 드라이브 945아파트 27

에이

(74) 대리인 손은진

**심사청구 : 없음**

---

**(54) 저감된 차단전류를 가지는 절환가능한 증폭기 회로**

---

**요약**

전류 미러를 가지는 절환가능한 증폭기 회로가 개시된다. 상기 미러는: 기준 전류를 발생하기 위한 제 1 전류원; 입력 전극과 출력 전극을 가지는 출력 트랜지스터; 및 상기 제 1 전류원의 출력과 상기 출력 트랜지스터의 입력 전극 사이에 배치된 전류 이득 기구를 구비한다. 상기 제 1 전류원에 의하여 발생된 기준 전류의 기능인 바이어스 전류가 상기 출력 트랜지스터의 출력 전극을 통하여 발생된다. 제 2 전류원은 기준 전류의 일부인 전류를 제공하고 상기 전류 이득 기구의 입력에 연결된 출력을 가진다. 절환 트랜지스터는: (1) 상기 전류 이득 기구의 입력; 및 (2) 상기 제 2 전류원의 출력에 연결된 출력 전극을 가진다. 상기 절환 트랜지스터는: (1) 상기 제 2 전류원으로부터의 전류가 상기 전류 이득 기구로 통과하는 것을 방지하여 출력 트랜지스터를 비도전 조건으로 구동하는 출력 트랜지스터용 바이어스 전류를 제거하는 상기 절환 트랜지스터에 공급되는 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 저하시키거나; 혹은 (2) 상기 출력 트랜지스터를 도전 상태로 구동하는 상기 절환 트랜지스터에 공급된 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 상기 전류 이득 기구로 통과하게 한다.

**대표도**

도 3

**색인어**

증폭기, 전류 미러, 절환 트랜지스터, 전류원, 전류이득기구

## 명세서

### 기술분야

본 발명은 증폭기들에 대한 것으로서, 보다 상세하게는 절환가능한 전원 증폭기들에 관한 것이다.

### 배경기술

이 기술 분야에서 알려진 바와 같이, 전원 증폭기는 여러 예들에서 사용된다. 이러한 하나의 예는 전지로 작동되는 셀룰러 폰과 같은 무선 주파수(RF) 신호를 증폭하기 위한 전화기이다.

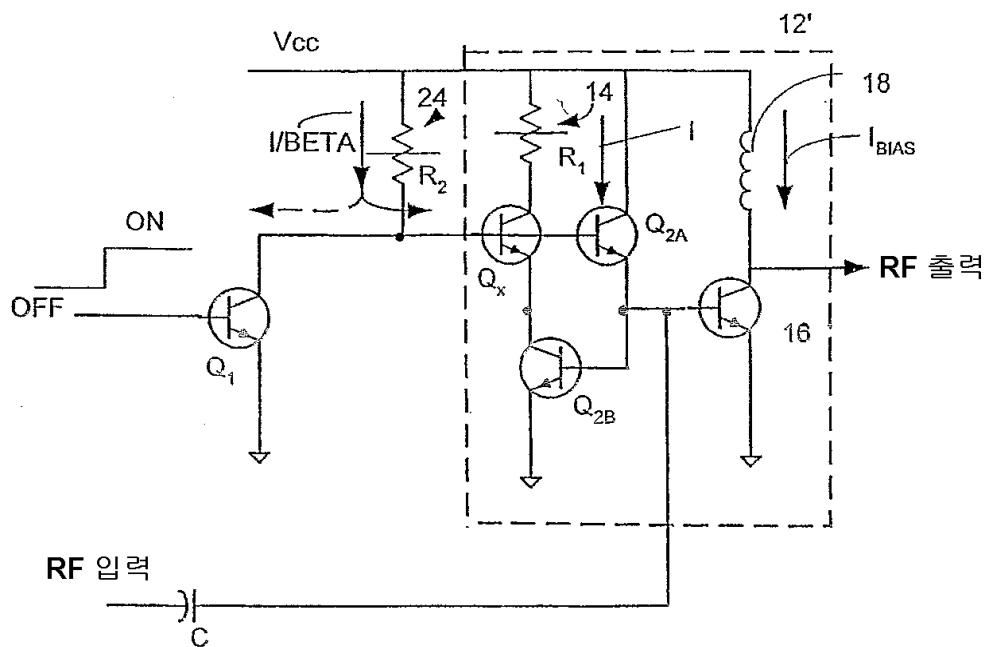

또한, 이 기술 분야에서 알려진 바와 같이, 이러한 RF 증폭기들은 통상 전류 미러(9)를 사용하여 적절한 직류(dc) 작동 지점에 바이어스된다. 이러한 하나의 장치가 도 1에 도시된다. 여기에서, 증폭기는 RF, 접지된 이미터 출력 트랜지스터( $Q_{RF}$ )를 포함한다. RF 트랜지스터의 베이스는 입력 RF 신호들이 입력된다. 출력 트랜지스터의 베이스는 또한 절환 트랜지스터( $Q_1$ )에 연결된다. 다이오드가 연결된 트랜지스터( $Q_2$ )(즉, p-n 접합)는 지상과 RF 출력 트랜지스터( $Q_{RF}$ )의 베이스 사이에 연결된다. 이러한 다이오드 연결 트랜지스터( $Q_2$ )가 전도되면, 고정된 dc 전압이 발생하여 RF 출력 트랜지스터( $Q_{RF}$ )의 베이스에서 dc 전압을 고정한다. 이와 같이, 다이오드 연결된 트랜지스터( $Q_2$ )를 도전시키면, Rf 출력 트랜지스터( $Q_{RF}$ )의 베이스 전극에 고정된 기준 전압이 제공된다. RF 트랜지스터( $Q_{RF}$ )는 그 콜렉터-이미터에 걸쳐 고정된 dc 전류( $I_{BIAS}$ )를 제공함으로써 고정된 dc 작동 지점에 바이어스된다. 여기에서, dc 전류는 도전된 다이오드 연결된 트랜지스터( $Q_2$ )에 고정된 전류를 인가함으로써 발생된다. 고정된 dc 전류는 전류원, 즉 고 임피던스 기구, 여기서는 저항기에 의하여 공급된다. 여기에서 전류원은 I로 표시된 전류를 발생한다. 이와 같이, RF 출력 트랜지스터에 요구되는 dc 바이어스 전류의 양은 전류원에 의하여 제공된 전류(I)의 양을 형성한다. 즉, 다이오드 연결된 트랜지스터와 RF 출력 트랜지스터( $Q_{RF}$ )는 전류원으로부터 다이오드 연결된 트랜지스터( $Q_2$ )에 공급된 전류를 반영하는 RF 트랜지스터의 콜렉터에 걸리는 전류를 가지는 전류 미러(9)로서 배치된다.

RF 출력 트랜지스터( $Q_{RF}$ )를 오프로 절환하는 것이 요구되는 경우, 트랜지스터( $Q_1$ )는 그 베이스로부터 공급된 제어 전압에 의하여 온 구동된다. 이와 같이, 트랜지스터( $Q_1$ )의 온 조건이 RF 출력 트랜지스터( $Q_{RF}$ )의 베이스에서 낮은 전압을 배치한다. 이제 전류원으로부터의 전류(I)는 도전성 트랜지스터( $Q_1$ )를 통과한다. 트랜지스터( $Q_1$ )는 일정한 적용예에서 5 - 10 밀리암페어로 아주 높을 수 있는 전류원 전류(I)를 저하시켜 과도한 배터리 전원 소모를 초래한다.

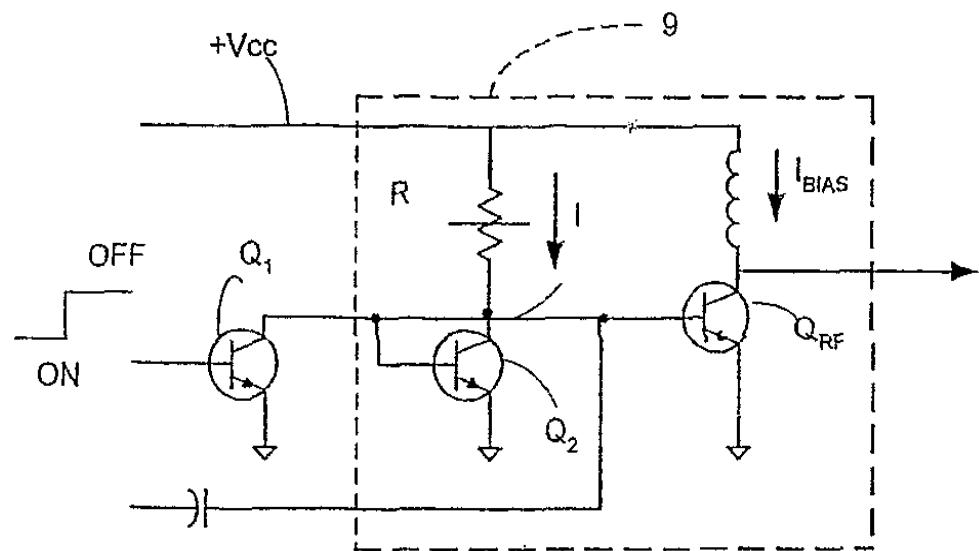

도 2에는 다른 회로가 도시된다. 여기에서, 전류 미러(9')는 한 쌍의 트랜지스터들( $Q_{2A}, Q_{2B}$ )과 RF 트랜지스터( $Q_{RF}$ )에 의하여 제공된다. 여기에서, 전류 미러(9')는 간혹 향상된 전류 미러로 불린다. 향상된 전류 미러를 가지고 이미터 종동 트랜지스터는 RF 트랜지스터가 고 전원, 넓은 신호 조건들 하에서 구동시 요구되는 과도한 베이스 전류를 공급할 수 있다.

여기에서 재차 고정된 dc 전압이 출력 트랜지스터( $Q_{RF}$ )의 베이스에서 발생된다. 이러한 dc 전압은 고정된 dc 전압으로서 RF 트랜지스터의 베이스에 연결됨으로써 RF 출력 트랜지스터에 대한 적절한 dc 바이어스 전류를 제공한다. RF 출력 트랜지스터에 필요한 dc 바이어스 전류의 양은 저항기로 재차 표시되는 전류원으로부터의 전류(I)의 양에 의하여 형성된다. 여기서 재차, RF 출력 트랜지스터를 오프 절환시키는 것이 요구되면, 그 베이스에 공급되는 제어 전압에 의하여 트랜지스터( $Q_1$ )는 구동된다. 이와 같이, 온 조건은 RF 출력 트랜지스터( $Q_{RF}$ )의 베이스에서 낮은 전압을 배치한다. 이제 전류원으로부터의 전류(I)는 도전성 트랜지스터( $Q_1$ )를 통과한다. 트랜지스터( $Q_1$ )는 일정한 적용예에서 5 - 10 밀리암페어로 아주 높을 수 있는 전류원 전류(I)를 저하시켜 과도한 배터리 전원 소모를 초래한다.

### 발명의 상세한 설명

본 발명에 따라 증폭기 회로가 제공된다. 증폭기 회로는 전류 미러 회로를 포함한다. 전류 미러 회로는: 기준 전류를 발생하기 위한 제 1 전류원; 입력 전극과 출력 전극을 가지는 출력 트랜지스터; 및 제 1 전류원의 출력과 출력 트랜지스터의 입력 전극 사이에 배치된 전류 이득 기구를 구비한다. 바이어스 전류가 출력 트랜지스터의 출력 전극을 통하여 발생되며, 이러한 바이어스 전류는 제 1 전류원에 의하여 발생된 기준 전류의 기능이다. 제 2 전류원은 전류 이득 기구의 입력에 연결된 출력을 가진다. 제 2 전류원은 기준 전류의 일부인 전류를 제공한다. 절환 트랜지스터는: (1) 전류 이득 기구의 입력; 및

(2) 제 2 전류원의 출력에 연결된 출력 전극을 가진다. 절환 트랜지스터는: (1) 제 2 전류원으로부터의 전류가 전류 이득 기구로 통과하는 것을 방지하여 출력 트랜지스터를 비도전 조건으로 구동하는 출력 트랜지스터용 바이어스 전류를 제거하는 절환 트랜지스터에 공급되는 입력 신호에 반응하여 제 2 전류원으로부터의 전류를 저하시키거나; 혹은 (2) 출력 트랜지스터를 도전 상태로 구동하는 절환 트랜지스터에 공급된 입력 신호에 반응하여 제 2 전류원으로부터의 전류를 전류 이득 기구로 통과하게 한다.

일 실시예에서 이득 기구는 트랜지스터를 포함한다.

일 실시예에서 출력 트랜지스터를 도전 조건으로 구동하는 절환 트랜지스터에 공급된 입력 신호에 반응하여 절환 트랜지스터가 제 2 전류원으로부터의 전류로 하여금 전류 이득 기구를 통과하게 하는 경우, 이득기구인 트랜지스터가 포화 구동된다.

일 실시예에서, 이득기구의 트랜지스터는 바이폴라 트랜지스터를 포함한다.

본 발명에 따라, 전류원의 출력에서의 고정 전압과 RF 트랜지스터의 베이스 사이에 연결된 콜렉터-이미터를 가지는 트랜지스터가 제공된다. 이 트랜지스터는 베이스가 제 2 전류원 및 이러한 트랜지스터용 스위치에 연결된다. RF 트랜지스터가 통전되려면, 제 2 전류원으로부터의 전류는 트랜지스터의 베이스로 공급되어 트랜지스터를 포화로 바이어스시키며 새로 운 회로가 RF 트랜지스터의 베이스에서 고정된 dc 전압을 발생하여 RF 트랜지스터에 대해 고정된 dc 바이어스 전류를 제공한다. RF 트랜지스터에 필요한 dc 바이어스 전류의 양은 전류원에 필요한 전류의 양을 형성한다. 트랜지스터가 포화이므로 제 2 전류원은 RF 트랜지스터용의 필수 dc 바이어스 전류를 제공하기 위한 제 1 전류원에 의하여 요구되는 전류의 양의 단지 작은 부분이다(1/베타). 스위치가 RF 트랜지스터를 오프시키면, 제 2 전류원으로부터의 더 적은 전류가 스위치에 의하여 저하된다.

본 발명의 하나 이상의 실시예들의 상세한 내용은 첨부 도면들과 이하의 설명에 개시된다. 본 발명의 다른 특징들, 목적들, 및 효과들은 상세한 설명과 도면 및 청구범위로부터 명백해질 것이다.

### 도면의 간단한 설명

도 1은 종래기술에 따른 절환가능한 증폭기의 개략적인 다이아그램;

도 2는 종래기술에 따른 절환가능한 증폭기의 개략적인 다이아그램;

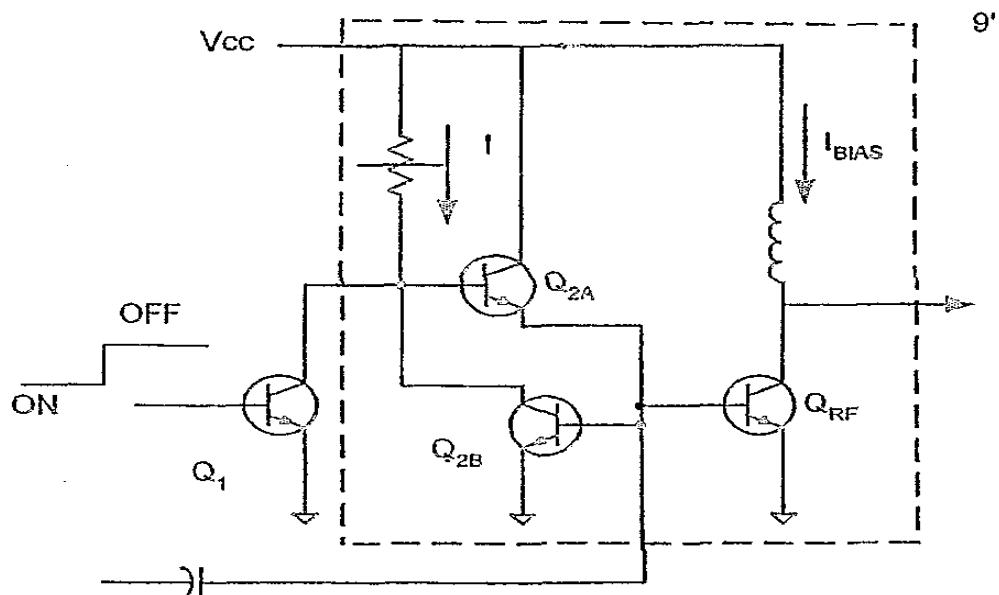

도 3은 본 발명에 따른 절환가능한 증폭기의 개략적인 다이아그램;

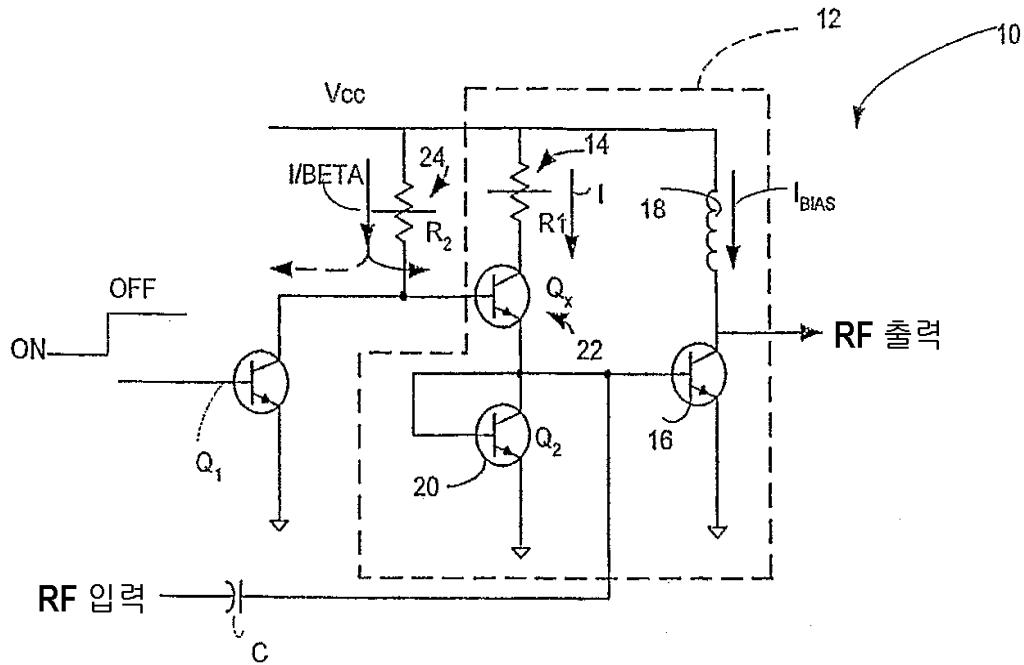

도 4는 본 발명의 다른 실시예에 따른 절환가능한 증폭기의 개략적인 다이아그램이다.

여러 도면들에서 동일한 도면 부호들은 유사한 요소들을 나타낸다.

### 실시예

이제 도 3에 있어서, RF 증폭기 회로(10)가 도시된다. 회로(10)는 전류 미러(mirror) 회로(12)를 포함한다. 전류 미러 회로(12)는 기준 전류(I)를 발생하기 위한 제 1 전류원(14)을 포함한다. 전류원(14)은 고 임피던스 기구로서, 여기서는 저항기(R1)에 의하여 표시된다. 전류 미러 회로(12)는 또한 바이폴라 트랜지스터이며 바람직하게는 이질접합 바이폴라 트랜지스터(HBT) 기구인 RF 출력 트랜지스터(16)를 포함한다. 출력 트랜지스터(16)는 도시된 바와 같이 접지된 이미터 구조로 배치되며 그 콜렉터는 인덕터(18)를 통해 Vcc 공급 전압에 연결된다. RF 출력 트랜지스터(16)에 의하여 증폭하기 위한 RF 입력은 도시된 바와 같이 접속 커패시터(C)를 통하여 RF 출력 트랜지스터(16)의 베이스 전극에 연결된다. 전류 미러 회로(12)는 또한 도시된 바와 같이 지면인 일정한 기준전압 및 출력 트랜지스터(16)의 게이트 전극에 연결된 다이오드 연결 바이폴라 트랜지스터(Q2)(즉, p-n 접합)인 기준 전압 발생기(20)를 포함한다. 전류 미러 회로(12)는 또한 전류원(14)의 출력과; (a) 출력 트랜지스터(16)의 게이트 전극; 및 (b) 기준전압 발생기(20) 사이에 연결된 바이폴라 트랜지스터(Q<sub>x</sub>)인 전류 이득기구(22)를 포함한다.

이러한 구조로서, 전류 미러 회로(12)는 출력 트랜지스터(18)의 콜렉터 전극을 통하여 dc 바이어스 전류( $I_{BIAS}$ )를 제공한다. 바이어스 전류( $I_{BIAS}$ )는 전류원(14)에 의하여 발생된 기준 전류(I)의 기능이다. 즉, 다이오드-연결 트랜지스터(Q2)는 p-n 접합을 제공하며 RF 출력 트랜지스터(16)는, RF 출력 트랜지스터(16)의 콜렉터를 흐르는 전류( $I_{BIAS}$ )가 전류원(14)으로부터의 다이오드-연결 트랜지스터(20)에 공급된 전류(I)를 감시하는 전류 미러(12)로서 배치된다.

증폭기(10)는 바이폴라 트랜지스터( $Q_x$ )인 전류 이득기구(22)의 입력에 연결된 출력을 가지는 저항기(R2)로 표시된 제 2 전류원(24)을 포함한다. 도전시, 트랜지스터( $Q_x$ )는 포화 작동하고 이로써 제 2 전류( $I'$ )는 기준 전류(I)이다. 또한, 트랜지스터( $Q_x$ )가 포화 작동하므로(즉, 트랜지스터( $Q_x$ )의 베이스-이미터 접합과 베이스-콜렉터 접합들이 모두 전방으로 바이어스된), 콜렉터 및 이미터 전극들에 걸쳐비교적 고정된 전압이 걸린다. 즉, 트랜지스터는 I의 제 2 전류원( $I'$ )에 위해 제공된 전류에 대한 비율인 베타(즉, 베타= $I/I'$ )를 가진다. 이와 같이, 예컨대, 베타가 50이면 제 2 전류원은 전류( $I'=I/50$ )를 발생한다.

회로(10)는 (1) 전류 이득기구(22)의 입력; 및 제 2 전류원(24)의 출력에 연결된 출력 전극(콜렉터 전극)을 가지는 접지된 이미터 바이폴라 트랜지스터(Q1)인 절환 트랜지스터를 포함한다. 절환 트랜지스터(Q1)는 베이스 전극에 공급된 제어 신호에 반응하여, (1) 제 2 전류원(24)으로부터의 전류가 전류 이득 기구(22)로 통과하는 것을 방지하여 출력 트랜지스터(16)를 비도전 조건으로 구동하는 출력 트랜지스터(16)용 바이어스 전류를 제거하는 절환 트랜지스터(Q1)의 베이스에 공급되는 입력 신호에 반응하여 제 2 전류원으로부터의 전류( $I'$ )(점선 화살표로 표시)를 저하시키거나; 혹은 (2) 출력 트랜지스터(16)를 도전 조건으로 구동하는 절환 트랜지스터(Q1)의 베이스에 공급된 제어 신호에 반응하여 제 2 전류원(24)으로부터의 전류(실선 화살표로 표시)를 전류 이득 기구(22)로 통과하게 한다.

이제 도 4에 있어서, 다른 절환 증폭기(10')가 도시된다. 여기에서, 전류 미러(12')는 향상된 전류 미러이며 RF 출력 트랜지스터(16)의 베이스에서 고정된 dc 기준 전압을 제공하기 위하여 한 쌍의 트랜지스터들( $Q_{2A}$ ,  $Q_{2B}$ )을 포함한다. dc 전압은 고정된 dc 전압으로서 RF 트랜지스터의 베이스에 연결되며 이로써 RF 출력 트랜지스터용의 적절한 dc 바이어스 전류를 제공한다. RF 출력 트랜지스터(16)에 필요한 dc 바이어스 전류의 양은 저항기(R1)로 표시되는 전류원(14)으로부터의 전류(I)의 양에 의하여 형성된다. 여기서, 재차 RF 출력 트랜지스터(16)를 오프로 절환시키는 것이 요구되면, 트랜지스터(Q1)는 그 베이스에 공급된 제어 전압에 의하여 온 구동된다.

증폭기(10')는 바이폴라 트랜지스터( $Q_x$ )인 전류이득기구(22)의 입력에 연결된 출력을 가지는 저항기(R2)에 의해 대표되는 제 2 전류원(24)을 포함한다. 도전시, 트랜지스터( $Q_x$ )는 포화 작동되어 제 2 전류( $I'$ )는 기준 전류(I)의 일부가 된다. 즉, 트랜지스터는 I의 제 2 전류원( $I'$ )에 의해 제공된 전류에 대한 비율인 베타(즉, 베타= $I/I'$ )를 가진다. 이와 같이, 예컨대, 베타가 50이면 제 2 전류원은 전류( $I'=I/50$ )를 발생한다.

회로(10')는 (1)전류 이득기구(22)의 입력; 및 (2)제 2 전류원(24)의 출력에 연결된 출력 전극(콜렉터 전극)을 가지는 접지된 이미터 바이폴라 트랜지스터(Q1)인 절환 트랜지스터를 포함한다. 절환 트랜지스터(Q1)는 베이스 전극에 공급된 제어 신호에 반응하여, (1) 제 2 전류원(24)으로부터의 전류가 전류 이득 기구(22)로 통과하는 것을 방지하여 출력 트랜지스터(16)를 비도전 조건으로 구동하는 출력 트랜지스터(16)용 바이어스 전류를 제거하는 절환 트랜지스터(Q1)의 베이스에 공급되는 입력 신호에 반응하여 제 2 전류원으로부터의 전류( $I'$ )(점선 화살표로 표시)를 저하시키거나; 혹은 (2) 출력 트랜지스터(16)를 도전 조건으로 구동하는 절환 트랜지스터(Q1)의 베이스에 공급된 제어 신호에 반응하여 제 2 전류원(24)으로부터의 전류(실선 화살표로 표시)를 전류 이득 기구(22)로 통과하게 한다.

### 산업상 이용 가능성

따라서, 본 발명에 따르면, 과도한 배터리의 파워 소모를 방지할 수 있다.

본 발명의 여러 실시예들이 설명되었다. 그럼에도 불구하고, 본 발명의 사상과 기술 범위를 벗어남이 없이 여러 변경들이 이루어질 수 있음은 명확하다. 따라서, 다른 실시예들도 이하의 청구범위의 범위 내에 있다.

### (57) 청구의 범위

**청구항 1.**

증폭기 회로로서:

- (a) ( i )기준 전류를 발생하기 위한 제 1 전류원;

- ( ii )입력 전극과 출력 전극을 가지는 출력 트랜지스터;

(iii)상기 제 1 전류원의 출력과 상기 출력 트랜지스터의 입력 전극 사이에 배치된 전류 이득 기구를 구비하며; ( v )여기에서 상기 제 1 전류원에 의하여 발생된 기준 전류의 기능인 바이어스 전류가 상기 출력 트랜지스터의 출력 전극을 통하여 발생되는 전류 미러 회로;

(b) 상기 전류 이득 기구의 입력에 연결된 출력을 가지며, 기준 전류의 일부인 전류를 제공하는 제 2 전류원; 및

(c) (1)상기 전류 이득 기구의 입력; 및 (2)상기 제 2 전류원의 출력에 연결된 출력 전극을 가지는 절환 트랜지스터로서:

(1)상기 제 2 전류원으로부터의 전류가 상기 전류 이득 기구로 통과하는 것을 방지하여 출력 트랜지스터를 비도전 조건으로 구동하는 출력 트랜지스터용 바이어스 전류를 제거하는 상기 절환 트랜지스터에 공급되는 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 저하시키거나; 혹은 (2)상기 출력 트랜지스터를 도전 상태로 구동하는 상기 절환 트랜지스터에 공급된 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 상기 전류 이득 기구로 통과하게 하는 절환 트랜지스터를 구비하는 것을 특징으로 하는 증폭기 회로.

**청구항 2.**

제 1 항에 있어서, 상기 이득 기구는 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 3.**

제 2 항에 있어서, 상기 이득기구의 트랜지스터는, 상기 출력 트랜지스터를 도전 조건으로 구동하는 상기 절환 트랜지스터에 공급된 입력 신호에 반응하여 상기 절환 트랜지스터가 상기 제 2 전류원으로부터의 전류로 하여금 상기 전류 이득 기구를 통과하게 하면 포화 구동되는 것을 특징으로 하는 증폭기 회로.

**청구항 4.**

제 3 항에 있어서, 상기 이득기구의 트랜지스터는 바이폴라 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 5.**

제 2 항에 있어서, 상기 이득기구의 트랜지스터는 바이폴라 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 6.**

제 1 항에 있어서, 상기 절환 트랜지스터는 바이폴라 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 7.**

제 6 항에 있어서, 상기 출력 트랜지스터는 바이폴라 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 8.**

제 7 항에 있어서, 상기 절환 트랜지스터는 바이폴라 트랜지스터를 포함하는 것을 특징으로 하는 증폭기 회로.

**청구항 9.**

증폭기 회로로서:

(a) 전류 미러 회로로서: (i) 기준 전류를 발생하기 위한 제 1 전류원;

(ii) 입력 전극과 출력 전극을 가지는 출력 트랜지스터;

(iii) 상기 제 1 전류원의 출력과 상기 출력 트랜지스터의 입력 전극 사이에 배치된 바이폴라 트랜지스터를 구비하며;

(iv) 여기에서 상기 제 1 전류원에 의하여 발생된 기준 전류의 기능인 바이어스 전류가 상기 출력 트랜지스터의 출력 전극을 통하여 발생되는 전류 미러 회로;

(b) 상기 바이폴라 트랜지스터의 입력에 연결된 출력을 가지며, 기준 전류의 일부인 전류를 제공하는 제 2 전류원; 및

(c) (1) 상기 전류 이득기구의 입력; 및 (2) 상기 제 2 전류원의 출력에 연결된 출력 전극을 가지는 절환 트랜지스터로서: (1) 상기 제 2 전류원으로부터의 전류가 상기 바이폴라 트랜지스터로 통과하는 것을 방지하여 출력 트랜지스터를 비도전 조건으로 구동하는 출력 트랜지스터용 바이어스 전류를 제거하는 상기 절환 트랜지스터에 공급되는 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 저하시키거나; 혹은 (2) 상기 출력 트랜지스터를 도전 상태로 구동하는 상기 절환 트랜지스터에 공급된 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 상기 바이폴라 트랜지스터로 통과하게 하여 상기 바이폴라 트랜지스터를 포화 구동시키는 절환 트랜지스터를 구비하는 증폭기 회로.

**청구항 10.**

증폭기 회로로서: (a) 기준 전류를 발생하기 위한 제 1 전류원;

(b) 입력 전극과 출력 전극을 가지는 출력 트랜지스터;

(c) 상기 제 1 전류원의 출력과 (1) 상기 출력 트랜지스터의 입력 전극, 및 (2) p-n 접합 사이에 연결된 바이폴라 트랜지스터를 구비하며;

(d) 여기에서 상기 제 1 전류원에 의하여 발생된 기준 전류 기능인 바이어스 전류가 상기 출력 트랜지스터의 출력 전극을 통하여 발생되는 전류 미러 회로;

(e) 상기 전류이득기구의 입력에 연결된 출력을 가지며, 기준 전류의 일부인 전류를 제공하는 제 2 전류원; 및

(f) (1) 상기 바이폴라 트랜지스터의 입력; 및 (2) 상기 제 2 전류원의 출력에 연결된 출력 전극을 가지는 절환 트랜지스터로서: (1) 상기 제 2 전류원으로부터의 전류가 상기 바이폴라 트랜지스터로 통과하는 것을 방지하여 출력 트랜지스터를 비도전 조건으로 구동하는 출력 트랜지스터용 바이어스 전류를 제거하는 상기 절환 트랜지스터에 공급되는 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 저하시키거나; 혹은 (2) 상기 출력 트랜지스터를 도전 상태로 구동하는 상기 절환 트랜지스터에 공급된 입력 신호에 반응하여 상기 제 2 전류원으로부터의 전류를 포화 작동하는 상기 바이폴라 트랜지스터로 통과하게 하는 절환 트랜지스터를 구비하는 증폭기 회로.

**도면**

도면1

도면2

도면3

도면4