(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6025875号

(P6025875)

(45) 発行日 平成28年11月16日(2016.11.16)

(24) 登録日 平成28年10月21日(2016.10.21)

(51) Int.Cl.

F 1

|        |       |           |

|--------|-------|-----------|

| HO 1 L | 23/12 | (2006.01) |

| HO 1 L | 25/10 | (2006.01) |

| HO 1 L | 25/11 | (2006.01) |

| HO 1 L | 25/18 | (2006.01) |

|        |       |         |

|--------|-------|---------|

| HO 1 L | 23/12 | 5 O 1 P |

| HO 1 L | 25/14 | Z       |

請求項の数 5 (全 39 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-558769 (P2014-558769)  |

| (86) (22) 出願日 | 平成25年2月14日 (2013.2.14)        |

| (65) 公表番号     | 特表2015-508240 (P2015-508240A) |

| (43) 公表日      | 平成27年3月16日 (2015.3.16)        |

| (86) 國際出願番号   | PCT/US2013/026126             |

| (87) 國際公開番号   | W02013/126269                 |

| (87) 國際公開日    | 平成25年8月29日 (2013.8.29)        |

| 審査請求日         | 平成27年4月21日 (2015.4.21)        |

| (31) 優先権主張番号  | 13/752,485                    |

| (32) 優先日      | 平成25年1月29日 (2013.1.29)        |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 13/405,125                    |

| (32) 優先日      | 平成24年2月24日 (2012.2.24)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 309034272<br>インヴェンサンス・コーポレイション<br>アメリカ合衆国 カリフォルニア州 95<br>134、サン・ホセ、オーチャード・パー<br>クウェイ 3025 |

| (74) 代理人  | 100099623<br>弁理士 奥山 尚一                                                                    |

| (74) 代理人  | 100096769<br>弁理士 有原 幸一                                                                    |

| (74) 代理人  | 100107319<br>弁理士 松島 鉄男                                                                    |

| (74) 代理人  | 100114591<br>弁理士 河村 英文                                                                    |

| (74) 代理人  | 100125380<br>弁理士 中村 純子                                                                    |

最終頁に続く

(54) 【発明の名称】超小型電子パッケージを作製する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

超小型電子パッケージを作製する方法であって、

a) 所定の長さを有する金属ワイヤセグメントをボンディングツールのキャピラリから送り出すステップと、

b) 前記ボンディングツールを使用するステップであって、前記金属ワイヤの一部分を基板の第1の表面において露出する導電性素子に結合し、それにより、前記導電性素子上にワイヤボンドのベースを形成する、使用するステップと、

c) 前記ワイヤの一部分を前記ボンディングツール内に固定するステップと、

d) 前記固定された部分と前記ベースとの間の場所において前記金属ワイヤを切断するステップであって、前記ワイヤボンドの端面を少なくとも部分的に画定し、前記ベースと前記端面との間に前記ワイヤボンドのエッジ面が画定される、切断するステップと、

e) ステップ(a)～ステップ(d)を繰り返すステップであって、前記基板の複数の前記導電性素子への複数のワイヤボンドを形成する、繰り返すステップと、

f) その後、前記基板の前記表面の上に重なる誘電体封止層を形成するステップであって、前記封止層は、前記基板の前記表面及び前記ワイヤボンドの一部分を少なくとも部分的に被覆するように形成され、それにより、前記封止層によって被覆されない前記ワイヤボンドの端面又はエッジ面のうちの少なくとも一方の一部分によって、前記ワイヤボンドの封止されない部分が画定される、形成するステップと、

を含み、

10

20

前記金属ワイヤセグメントは前記ボンディングツール上に取り付けられるレーザを用いて切断され、

前記ボンディングツールはキャピラリを含み、該キャピラリは前記ワイヤボンドが送り出される際に通る該キャピラリの面を画定し、前記キャピラリは該キャピラリの側壁内に形成される開口部を含み、前記レーザは、前記開口部を通して、前記キャピラリ内に位置決めされる前記ワイヤセグメントの場所に切断ビームを誘導するように、前記ボンディングツール上に取り付けられる、超小型電子パッケージを作製する方法。

【請求項 2】

前記レーザは  $\text{CO}_2$ 、Nd:YAG 又は Cu 蒸気レーザのうちの 1 つである、請求項 1 に記載の方法。

10

【請求項 3】

前記金属ワイヤは部分的にのみ切込みを入れられ、前記ボンディングツールは、前記ワイヤの前記部分が固定されたまま、前記基板の前記表面から遠ざけられ、それにより、前記ワイヤが前記切込みの場所において断線し、前記端面は前記切込み及び前記断線によって形成される、請求項 1 に記載の方法。

【請求項 4】

前記金属ワイヤは、前記ワイヤボンドの前記エッジ面に対して実質的に垂直な方向において前記ワイヤセグメントを完全に貫通して切断され、前記ワイヤボンドの前記端面は前記切断によって形成される、請求項 1 に記載の方法。

【請求項 5】

20

超小型電子パッケージを作製する方法であって、

a) 金属ワイヤをボンディングツールのキャピラリを通して送り出すステップと、

b) 前記ボンディングツールを使用するステップであって、前記金属ワイヤの一部分を基板の第 1 の表面において露出する導電性素子に結合し、それにより、前記導電性素子にワイヤボンドのベースを形成する、使用するステップと、

c) 前記ワイヤの一部分を前記ボンディングツール内に固定するステップと、

d) 前記キャピラリ内の前記金属ワイヤを前記固定された部分と前記ベースとの間の場所において切断するステップであって、前記ワイヤボンドの前記ベースから所定の距離において前記ワイヤボンドの端面を少なくとも部分的に画定し、前記金属ワイヤは前記ボンディングツール上に取り付けられるレーザを用いて切断され、該レーザの切断ビームは前記キャピラリの壁の開口部を通って、前記キャピラリ内に及び前記キャピラリ内の前記金属ワイヤに達する、切断するステップと、

30

を含む、超小型電子パッケージを作製する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書における本発明の実施形態は、パッケージオンパッケージアセンブリにおいて用いることができる超小型電子パッケージを作製する種々の構造及び方法に関し、より詳細には、パッケージオンパッケージ接続の一部分としてワイヤボンドを組み込むそのような構造に関する。

40

【0002】

【関連出願の相互参照】

本出願は 2013 年 1 月 29 日に出願の米国特許出願第 13/752,485 号の継続出願であり、その特許出願は、2012 年 2 月 24 日に出願の米国特許出願第 13/405,125 号、現在、2013 年 2 月 12 日に発行の米国特許第 8,372,741 号の継続出願であり、それらの特許文献の開示は引用することにより本明細書の一部をなすものとする。

【背景技術】

【0003】

50

半導体チップ等の超小型電子デバイスは、通常、他の電子構成要素への多数の入出力接続を必要とする。半導体チップ又は他の同等のデバイスの入出力コンタクトは、通例、デバイスの表面を実質的に被覆するグリッド状のパターン（一般に「エリアアレイ」と呼ばれる）、若しくはデバイスの前面の各縁に平行にかつ隣接して延在することができる細長い列に配置されるか、又は前面の中央に配置される。通常、チップ等のデバイスはプリント回路基板等の基板上に物理的に実装されなくてはならず、デバイスのコンタクトは回路基板の導電性機構に電気的に接続されなくてはならない。

#### 【 0 0 0 4 】

半導体チップは一般に、チップを製造し、回路基板又は他の回路パネル等の外部基板に実装する間のそのチップの取扱いを容易にするパッケージにおいて提供される。例えは、多くの半導体チップは、表面実装に適したパッケージにおいて提供される。この一般的なタイプの多数のパッケージが種々の用途について提案されている。最も一般的には、そのようなパッケージは、誘電体上にめっき又はエッチングされた金属構造体として形成された端子を有する、一般に「チップキャリア」と呼ばれる誘電体素子を含む。これらの端子は通常、チップキャリア自体に沿って延在する薄いトレース等の機構によって、及びチップのコンタクトと端子又はトレースとの間に延在する微細なリード線又は配線によって、チップ自体のコンタクトに接続される。表面実装動作において、パッケージは、パッケージ上の各端子が回路基板上の対応するコンタクトパッドと位置合わせされるように回路基板上に配置される。端子とコンタクトパッドとの間にはんだ又は他の結合剤が提供される。はんだを溶かすか若しくは「リフロー」させるようにアセンブリを加熱するか又は他の形で結合剤を活性化させることによって、パッケージを定位置に永久結合することができる。

#### 【 0 0 0 5 】

多くのパッケージが、パッケージの端子に取り付けられた、直径が約 0 . 1 mm 及び約 0 . 8 mm ( 5 ミル及び 30 ミル ) のはんだボールの形態のはんだ塊を含む。パッケージの底面から突出するはんだボールのアレイを有するパッケージは、一般にボールグリッドアレイすなわち「 B G A 」パッケージと呼ばれる。ランドグリッドアレイすなわち「 L G A 」パッケージと呼ばれる他のパッケージは、はんだから形成される薄い層又はランドによって基板に固定される。このタイプのパッケージは非常に小型にすることができる。一般に「チップスケールパッケージ」と呼ばれる或る特定のパッケージは、パッケージに組み込まれたデバイスのエリアに等しいか又はそれよりも僅かにしか大きくない回路基板のエリアを占有する。これによりアセンブリの全体サイズが低減し、基板上の様々なデバイス間で短い相互接続を用いることが可能になり、ひいてはデバイス間の信号伝搬時間が制限され、このためアセンブリの高速動作が容易になるという点でこれは有利である。

#### 【 0 0 0 6 】

パッケージングされた半導体チップは、多くの場合に「積層」構成において提供される。積層構成では、1つのパッケージが例えば回路基板上に設けられ、別のパッケージが第1のパッケージの上に実装される。これらの構成によって、回路基板上の単一の接地面積内に複数の異なるチップが実装されることを可能にすことができ、パッケージ間の短い相互接続を提供することによって高速動作を更に容易にすことができる。多くの場合に、この相互接続距離は、チップ自体の厚みよりも僅かにしか大きくない。チップパッケージの積層内で相互接続を達成するために、（最上部のパッケージを除いて）各パッケージの両側において機械的接続及び電気的接続のための構造を与えることが必要である。これは例えば、チップが実装される基板の両側にコンタクトパッド又はランドを設けることによって行われ、パッドは導電性ビア等によって基板を通じて接続される。下側の基板の上部のコンタクトと次に高い基板の底部のコンタクトとの間の間隙を埋めるのにはんだボール等が用いられてきた。はんだボールは、コンタクトを接続するために、チップの高さよりも高くなくてはならない。積層チップ構成及び相互接続構造の例が、米国特許出願公開第 2010 / 0232129 号（「 129 号公開 」）において提供されている。この文献の開示内容は引用することによりその全体が本明細書の一部をなすものとする。

10

20

30

40

50

## 【0007】

超小型電子パッケージを回路基板に接続するために、及び超小型電子パッケージングにおける他の接続のために、細長いポスト又はピンの形態のマイクロコンタクト素子を用いることができる。幾つかの例では、マイクロコンタクトは、1つ又は複数の金属層を含む金属構造体をエッチングしてマイクロコンタクトを形成することによって形成されている。エッチングプロセスによってマイクロコンタクトのサイズが制限される。従来のエッチングプロセスは通常、本明細書において「アスペクト比」と呼ばれる高さ対最大幅の比が大きいマイクロコンタクトを形成することができない。かなりの高さ及び隣接するマイクロコンタクト間の非常に小さなピッチ又は間隔を有するマイクロコンタクトのアレイを形成することは、困難又は不可能であった。さらに、従来のエッチングプロセスによって形成されるマイクロコンタクトの構成は限られている。

10

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0008】

当該技術分野における上述したあらゆる進歩にもかかわらず、超小型電子パッケージの作製及び試験における更なる改善が依然として望ましい。

## 【課題を解決するための手段】

## 【0009】

超小型電子アセンブリが、反対に位置する第1の表面と第2の表面とを有する基板を含むことができる。超小型電子素子が第1の表面の上に重なることができ、第1の導電性素子が第1の表面又は第2の表面のうちの少なくとも一方において露出することができる。第1の導電性素子のうちの幾つかは超小型電子素子に電気的に接続される場合がある。ワイヤボンドが導電性素子に接合されるベースと、基板及びベースから離れた端面とを有する。各ワイヤボンドはベースと端面との間に延在するエッジ面を画定することができる。封止層が第1の表面から延在し、ワイヤボンド間の空間を満たすことができ、それにより、封止層によってワイヤボンドを分離することができる。封止層によって被覆されないワイヤボンドの端面の少なくとも一部によって、ワイヤボンドの封止されない部分を画定することができる。

20

## 【0010】

導電性素子、例えば、基板上の導電性パッドから上方に延在する垂直接続部として機能するワイヤボンドを組み込む種々のパッケージ構造が本明細書で開示される。こうしたワイヤボンドは、超小型電子パッケージが誘電体封止の表面に載った状態でパッケージオンパッケージ電気接続部を作製するときに使用することができる。さらに、超小型電子パッケージ又は超小型電子アセンブリを作製する方法の種々の実施形態が本明細書で開示される。

30

## 【0011】

したがって、本発明の一態様による超小型電子パッケージを形成する方法は、

a ) 所定の長さを有する金属ワイヤセグメントをボンディングツールのキャピラリから送り出すステップと、

b ) 前記ボンディングツールを使用するステップであって、前記金属ワイヤの一部分を基板の第1の表面において露出する導電性素子に結合し、それにより、前記導電性素子上にワイヤボンドのベースを形成する、使用するステップと、

40

c ) 前記ワイヤの一部分を前記ボンディングツール内に固定するステップと、

d ) 前記固定された部分と前記ベースとの間の場所において前記金属ワイヤを切断するステップであって、前記ワイヤボンドの端面を少なくとも部分的に画定し、前記ベースと前記端面との間に前記ワイヤボンドのエッジ面が画定される、切断するステップと、

e ) ステップ (a) ~ ステップ (d) を繰り返すステップであって、前記基板の複数の前記導電性素子への複数のワイヤボンドを形成する、繰り返すステップと、

e ) その後、前記基板の前記表面の上に重なる誘電体封止層を形成するステップであって、前記封止層は、前記基板の前記表面及び前記ワイヤボンドの一部分を少なくとも部分

50

的に被覆するように形成され、それにより、前記封止層によって被覆されない前記ワイヤボンドの端面又はエッジ面のうちの少なくとも一方の一部分によって、前記ワイヤボンドの封止されない部分が画定される、形成するステップと、

を含むことができる。

#### 【0012】

したがって、本発明の一態様によれば、所定の長さを有する金属ワイヤセグメントをボンディングツールのキャピラリから送り出すことができる。ボンディングツールを用いて、金属ワイヤの一部分を基板の第1の表面において露出する導電性素子に結合することができる。そのようなボンディングは、導電性素子上にワイヤボンドのベースを形成することができる。導電性素子とのボンドを形成した後に、ワイヤの一部分を固定することができる。固定されたワイヤの部分はボンディングツール内に存在することができる。固定された部分とベースとの間の場所において金属ワイヤを切断することができ、ワイヤを切断することによって、ワイヤボンドの端面を少なくとも部分的に画定することができる。ベースと端面との間にワイヤボンドのエッジ面を画定することができる。上記のことを繰り返して、基板の複数の導電性素子への複数のワイヤボンドを形成することができる。その後、基板の表面の上に重なる誘電体封止層を形成することができる。封止層は、基板の表面とワイヤボンドの一部分とを少なくとも部分的に被覆するように形成することができる。封止層によって被覆されない端面又はエッジ面のうちの少なくとも一方の一部分によって、ワイヤボンドの封止されない部分を画定することができる。

#### 【0013】

一例では、金属ワイヤは部分的にのみ切込みを入れることができる。ワイヤの一部分が固定されたまま、基板の表面からボンディングツールを遠ざけることができる。そのようなプロセスにおいて、切込みの場所においてワイヤを断線させることができる。切込み及び断線によって端面を形成することができる。

#### 【0014】

一例では、切込みは、ワイヤボンドのエッジ面に対して実質的に垂直な方向においてワイヤセグメントを完全に貫通するように作製することができる。その切込みによって、ワイヤボンドの端面を形成することができる。

#### 【0015】

一例では、少なくとも1つの超小型電子素子が基板の第1の表面の上に重なることができる。基板は、第1の領域及び第2の領域を有することができ、超小型電子素子は第1の領域内に、例えば、第1の領域の上に重なるように位置することができる。導電性素子は、第2の領域内に、例えば、その中の第1の表面において露出する導電性素子として位置することができる。導電性素子は、少なくとも1つの超小型電子素子に電気的に接続することができる。誘電体封止層は、基板の少なくとも第2の領域において基板の第1の表面の上に重なるように形成することができるが、第1の領域及び第2の領域において第1の表面の少なくとも一部の上に重なることもできる。

#### 【0016】

一例では、パッケージは、ワイヤボンドのうちの第1のワイヤボンドが第1の信号電位を搬送するようになっており、ワイヤボンドのうちの第2のワイヤボンドが第1の信号電位とは異なる第2の信号電位を同時に搬送するようになっているように構成することができる。

#### 【0017】

一例では、金属ワイヤセグメントはボンディングツール上に取り付けられるレーザを用いて切断することができる。そのような例では、ボンディングツールのキャピラリは、ワイヤセグメントが送り出される際に通るそのキャピラリの面を画定することができる。ボンディングツールのその面とワイヤボンドのベースとの間に位置決めされるワイヤセグメントの場所に切断ビームを向けることができるよう、レーザは、ボンディングツール上に、又はボンディングツールとともに取り付けることができる。

#### 【0018】

10

20

30

40

50

一例では、ボンディングツールは、ワイヤセグメントが送り出される際に通るそのキャピラリの面を画定するキャピラリを含むことができる。キャピラリはその側壁において開口部を含むことができ、切断ビームがその開口部を通ってキャピラリ内に位置決めされるワイヤセグメントの場所に達することができるよう、レーザは、ボンディング上に、又はボンディングとともにレーザを取り付けることができる。

【0019】

一例では、レーザはCO<sub>2</sub>、Nd:YAG又はCu蒸気レーザのうちの1つとすることができます。

【0020】

一例では、金属ワイヤは、キャピラリ内に延在する切断エッジを用いて切断することができる。一例では、切断エッジは、ワイヤセグメントの反対に位置するキャピラリの壁に向かう方向に延在することができる。一例では、金属ワイヤは、この切断エッジを第1の切断エッジとして、キャピラリ内に延在する第2の切断エッジと組み合わせて切断エッジを用いて切断することができる。第2の切断エッジは、第1の切断エッジの反対側に位置決めすることができる。

10

【0021】

一例では、キャピラリは、ワイヤセグメントを送り出す際に通ることができる面を画定することができる。金属ワイヤは、反対に位置する第1の切断エッジ及び第2の切断エッジを有する切断器具を用いて切断することができる。ボンディングツールのその面とワイヤボンドのベースとの間に位置決めされた場所においてワイヤを切断することができるよう、切断器具は、ボンディングツール上に、又はボンディングツールとともに取り付けることができる。

20

【0022】

その方法の一例が、基板の上方にステンシルを位置決めすることを含むことができる。ステンシルは、その中に複数の開口部を有することができ、開口部は、導電性素子の少なくとも一部の上に重なり、当該少なくとも一部を露出させる。開口部は、基板の上方の第1の高さに位置決めされるそれぞれのエッジを規定することができる。ワイヤセグメントは、ステンシル開口部のエッジに対して、ワイヤを横方向に移動することによって切断することができる。

【0023】

30

本発明の一態様による超小型電子パッケージを作製する方法は、第1の表面と、そこから離れた第2の表面とを有する基板を含む処理中ユニットの上方にステンシルを位置決めすることを含むことができる。基板の第1の表面に超小型電子素子を実装することができる。第1の表面において複数の導電性素子を露出させることができる。一例では、導電性素子のうちの少なくとも幾つかを超小型電子素子に電気的に接続することができる。ステンシルは、その中に複数の開口部を有することができ、開口部は、導電性素子の少なくとも一部の上に重なり、当該少なくとも一部を露出させる。開口部は、基板の上方の第1の高さに位置決めされるそれぞれのエッジを画定することができる。

【0024】

40

そのような態様によれば、その方法は、所定の長さがキャピラリの面を越えて延在し、金属ワイヤセグメントを画定するように、金属ワイヤをボンディングツールのキャピラリから送り出すことを含むプロセスによってワイヤボンドを形成することを含むことができる。ワイヤセグメントの一部分を複数の導電性素子のうちの1つの導電性素子に接合し、ワイヤボンドのベースを形成することができる。ステンシル開口部のエッジに対してワイヤを横方向に移動し、ワイヤの残りの部分からワイヤボンドを切り離すことによって、金属ワイヤセグメントの少なくとも一部を、そのセグメントに接続されるワイヤの別の部分から剪断することができる。金属ワイヤの剪断は、ワイヤボンドの端面を画定することができ、ワイヤボンドはベースと端面との間に延在するエッジ面を有する。上記のような、金属ワイヤから送り出すこと、結合すること、及び金属ワイヤを剪断することは、複数の導電性素子上に複数のワイヤボンドを形成するために、ステンシルの1つ又は複数の開口

50

部を用いて複数回繰り返すことができる。

【0025】

そのような方法の一例では、処理中ユニット上に誘電体封止層を形成することができ、封止層は、第1の表面と、ワイヤボンドの一部分とを少なくとも部分的に被覆するよう形成される。封止層によって被覆されないワイヤボンドの端面又はエッジ面の少なくとも一方の一部分によって、ワイヤボンドの封止されない部分を画定することができる。

【0026】

そのような方法の一例では、キャピラリの面を越えて延在し、金属ワイヤの剪断後に残る金属ワイヤの部分が、後続のワイヤボンドの少なくともベースを形成するのに十分な長さからなることができる。

10

【0027】

その方法の一例では、ステンシルは、穴のうちの1つの穴から延在する軸の方向、例えば、基板の表面から遠ざかる垂直方向において厚みを画定することができる。穴のうちの幾つか又は全てがステンシルの厚みを通して一貫した、すなわち一定の直径を有することができる。

【0028】

その方法の一例では、ステンシルは、穴又は開口部のうちの1つの穴又は開口部の軸の方向、例えば、基板の表面から遠ざかる垂直方向において厚みを画定することができる。ステンシル内の穴又は開口部のうちの幾つか又は全てを、開口部内の露出したエッジにおける第1の幅又は小さな直径から、穴又は開口部内の、基板に近い別の場所における第2の大きな幅又は大きな直径までテーパを付けることができる。

20

【0029】

一例では、ステンシルは、基板の厚みの方向において第1の厚みを有し、基板の1つ又は複数のエッジに沿って延在するエッジ部材を含むことができる。第1の厚みは第1の高さを画定することができる。中央部分が穴又は開口部を含むことができ、エッジ部材によって囲むことができる。中央部分は基板から離れて面する外面を有することができる。外面は第1の高さに配置することができる。中央部分は第1の厚み未満の厚みを有することができる。

【図面の簡単な説明】

【0030】

30

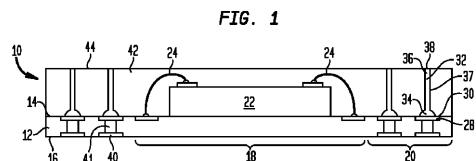

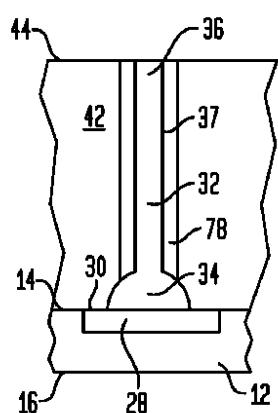

【図1】本発明の一実施形態による、超小型電子パッケージを示す図である。

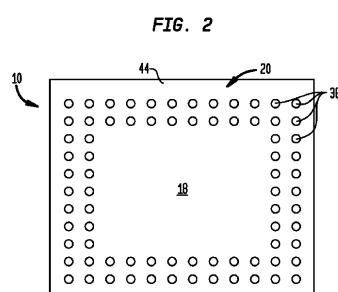

【図2】図1の超小型電子パッケージの上からの平面図である。

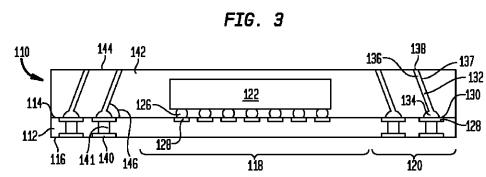

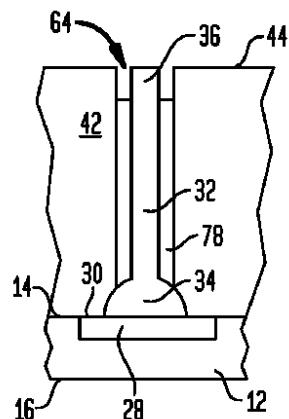

【図3】本発明の代替の実施形態による、超小型電子パッケージを示す図である。

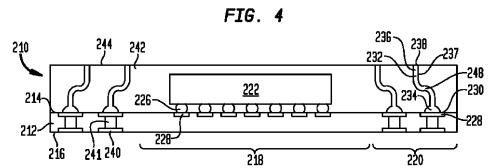

【図4】本発明の代替の実施形態による、超小型電子パッケージを示す図である。

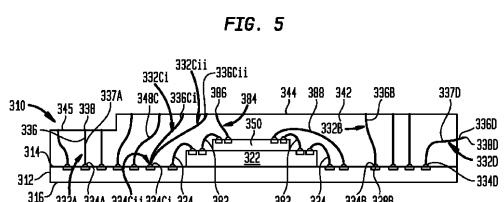

【図5】本発明の代替の実施形態による、超小型電子パッケージを示す図である。

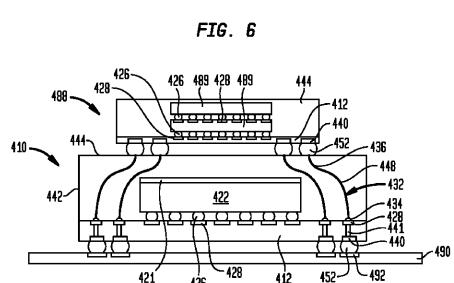

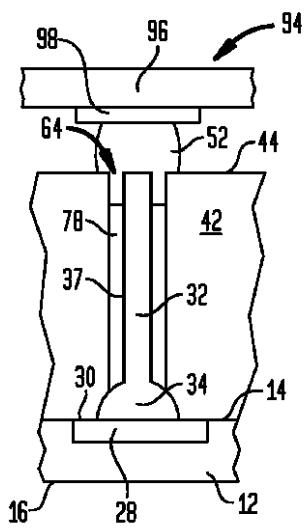

【図6】本発明の一実施形態による、超小型電子パッケージを含む積層された超小型電子アセンブリを示す図である。

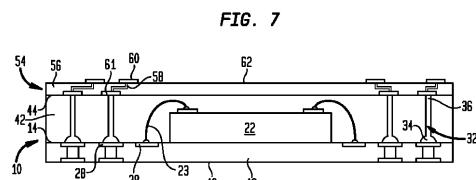

【図7】本発明の代替の実施形態による、超小型電子パッケージを示す図である。

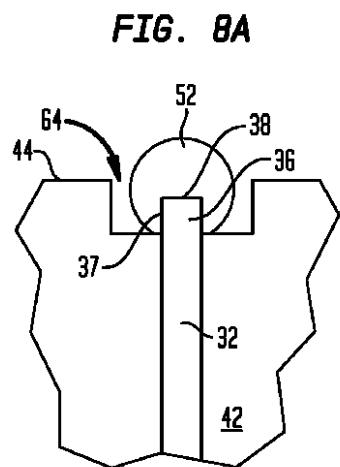

【図8A】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

40

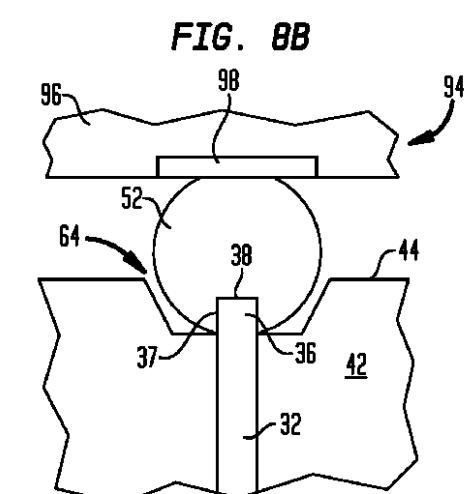

【図8B】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

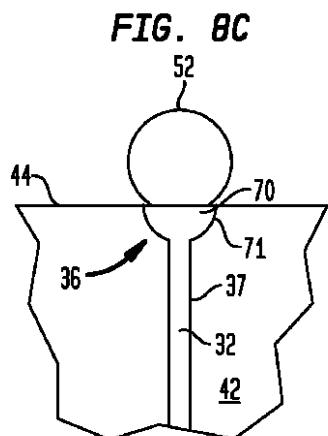

【図8C】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

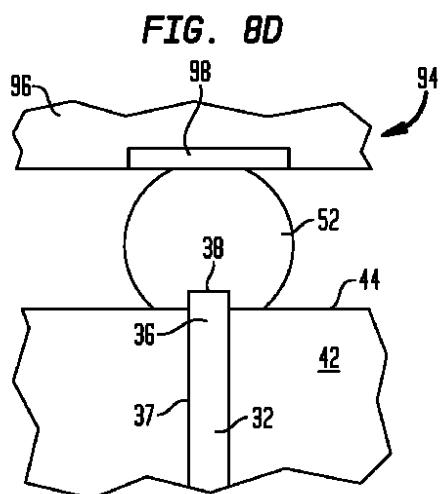

【図8D】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

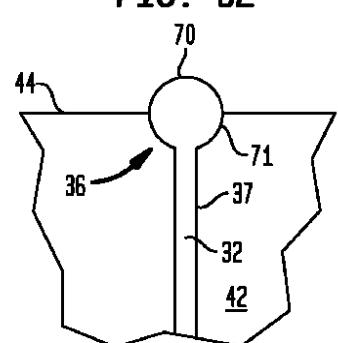

【図8E】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

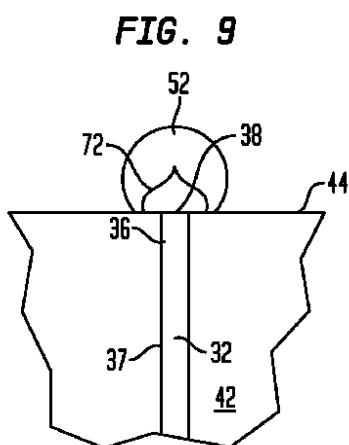

【図9】本発明の代替の実施形態による、超小型電子パッケージの一部分の詳細図である。

。

50

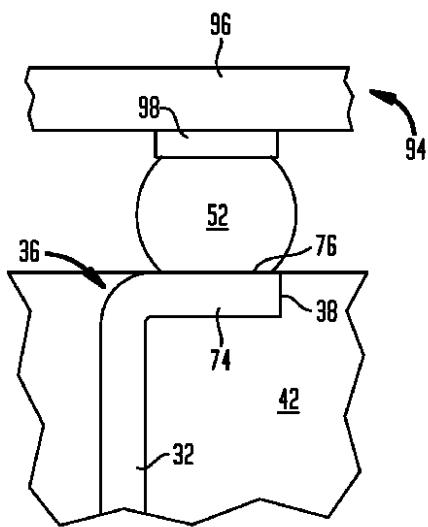

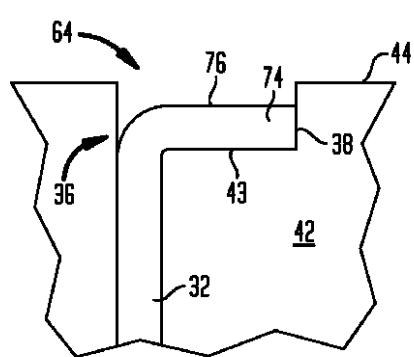

【図10A】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

【図10B】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

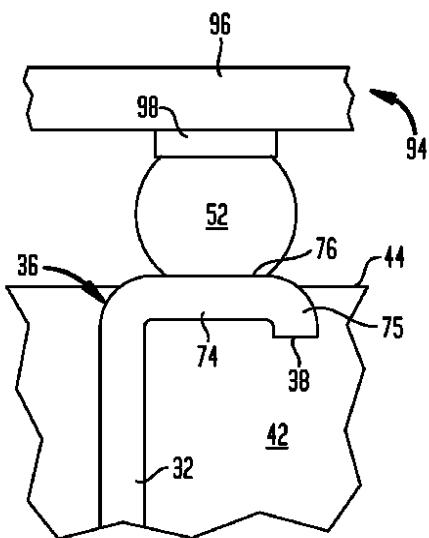

【図10C】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

【図10D】本発明の種々の実施形態による、超小型電子パッケージの一部分の詳細図である。

【図11】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージを示す図である。 10

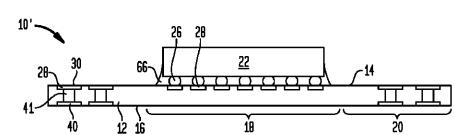

【図12】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージを示す図である。

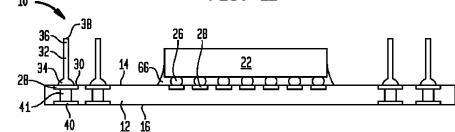

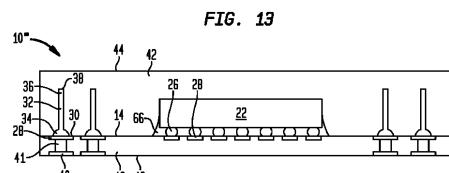

【図13】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージを示す図である。

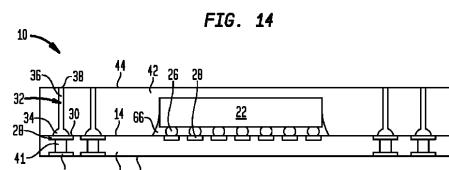

【図14】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージを示す図である。

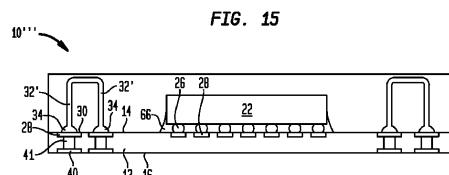

【図15】本発明の代替の実施形態による、製造ステップ中の超小型電子パッケージを示す図である。

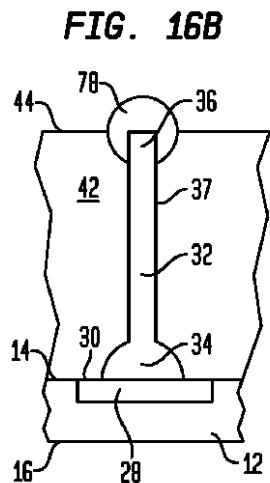

【図16A】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。 20

【図16B】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。

【図16C】本発明の一実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。

【図17A】本発明の代替の実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。

【図17B】本発明の代替の実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。

【図17C】本発明の代替の実施形態による、超小型電子パッケージの種々の製造ステップ中の超小型電子パッケージの一部分の詳細図である。 30

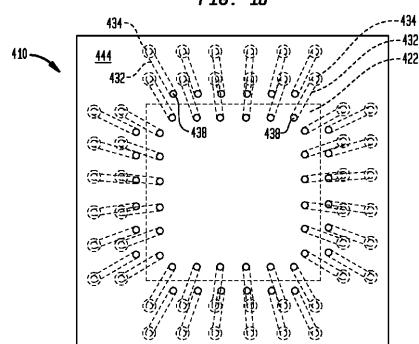

【図18】本発明の代替の実施形態による、超小型電子パッケージの上からの平面図である。

【図19】本発明の代替の実施形態による、超小型電子パッケージの一部分の上からの平面図である。

【図20】本発明の更なる代替の実施形態による、超小型電子パッケージの上面図である。

【図21】請求項20の超小型電子パッケージの正面図である。

【図22】本発明の更なる代替の実施形態による、超小型電子パッケージの正面図である。

【図23】本発明の更なる実施形態による、システムを示す図である。 40

【図24】本発明の更なる代替の実施形態による、超小型電子パッケージの正面図である。

【図25】本発明の更なる代替の実施形態による、超小型電子パッケージの正面図である。

【図26】図25の実施形態の変形形態による、超小型電子パッケージの上面図である。

【図27】本発明の更なる代替の実施形態による、超小型電子パッケージの正面図である。

【図28】図27の実施形態の変形形態による、超小型電子パッケージの上面図である。

【図29】更なる実施形態による、超小型電子パッケージの断面図である。

【図30】別の実施形態による、超小型電子パッケージの断面図である。 50

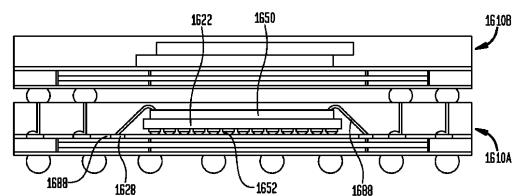

【図31A】更なる実施形態による、超小型電子パッケージの実施形態の例を示す断面図である。

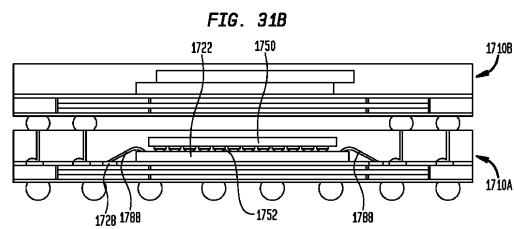

【図31B】更なる実施形態による、超小型電子パッケージの実施形態の例を示す断面図である。

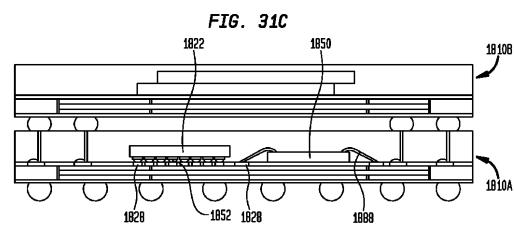

【図31C】更なる実施形態による、超小型電子パッケージの実施形態の例を示す断面図である。

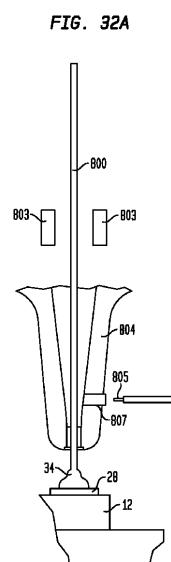

【図32A】本開示の別の実施形態による方法の種々のステージにおいて種々のワイヤボンドビアを形成する際に用いることができる機械の一部分を示す図である。

【図32B】本開示の別の実施形態による方法の種々のステージにおいて種々のワイヤボンドビアを形成する際に用いることができる機械の一部分を示す図である。

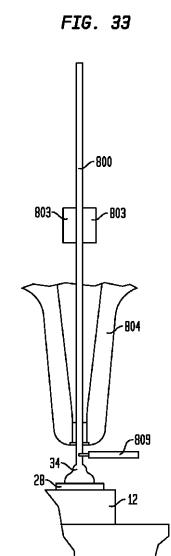

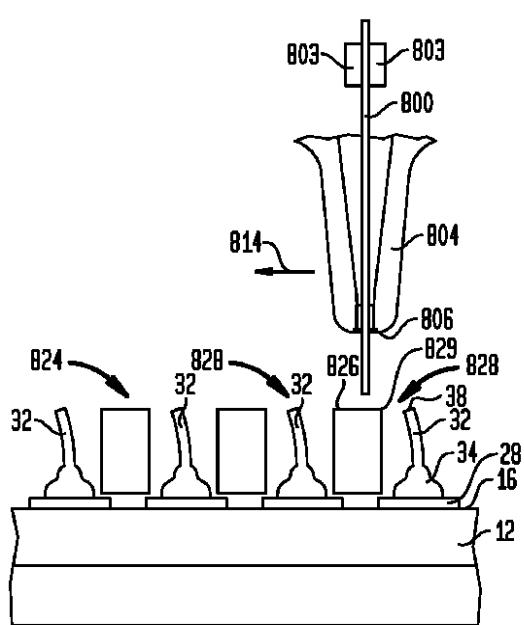

【図33】本開示の別の実施形態による方法に従って種々のワイヤボンドビアを形成する際に用いることができる機械の一部分を示す図である。

【図34A】本開示の一実施形態による、ワイヤボンドを作製する方法において用いることができる器具の種々の形態を示す図である。

【図34B】本開示の一実施形態による、ワイヤボンドを作製する方法において用いることができる器具の種々の形態を示す図である。

【図34C】本開示の一実施形態による、ワイヤボンドを作製する方法において用いることができる器具の種々の形態を示す図である。

【発明を実施するための形態】

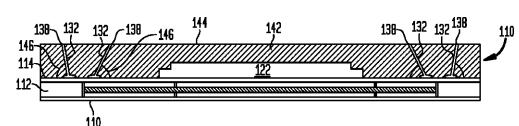

【0031】

次に、図面を参照すると、図1に、本発明の一実施形態による超小型電子アセンブリ10が示されている。図面では同様の機構を示すのに同様の数字符号が用いられる。図1の実施形態は、コンピュータ又は他の電子用途において用いられる半導体チップアセンブリ等のパッケージングされた超小型電子素子の形態の超小型電子アセンブリである。

【0032】

図1の超小型電子アセンブリ10は、第1の表面14及び第2の表面16を有する基板12を備える。基板12は、通常、実質的に平坦である誘電体素子の形態である。誘電体素子は、シート状とすることができる、薄いものとすることができる。特定の実施形態では、誘電体素子は、限定はしないが、ポリイミド、ポリテトラフルオロエチレン(「PTFE」)、エポキシ、エポキシガラス、FR-4、BT樹脂、熱可塑性又は熱硬化性プラスチック材料等の有機誘電体材料又は複合誘電体材料の1つ又は複数の層を含むことができる。第1の表面14及び第2の表面16は互いに実質的に平行であることが好ましく、表面14、16に対し垂直に或る距離離間し、基板12の厚みを画定する。基板12の厚みは、本出願のために通例受け入れ可能な厚みの範囲内にあることが好ましい。一実施形態では、第1の表面14と第2の表面16との間の距離はおよそ25μmと500μmとの間にある。この論考の目的で、第1の表面14は第2の表面16と反対側に又は遠隔に位置決めされているものとして説明することができる。そのような説明は、本明細書において用いられる素子の垂直位置又は水平位置を指す、そのような素子の相対位置の任意の他の説明とともに、図面内の素子の位置と一致するように説明の目的のみで行われ、限定するものではない。

【0033】

好ましい実施形態では、基板12は第1の領域18及び第2の領域20に分割されるものとみなされる。第1の領域18は第2の領域20の内側にあり、基板12の中央部分を含み、そこから外側に延在する。第2の領域20は第1の領域18を実質的に取り囲み、そこから基板12の外縁へ外側に延在する。この実施形態では、基板自身の特定の特性が2つの領域を物理的に分割していないが、これらの領域は、その領域に適用されるか又はその領域内に含まれる処理又は特徴部に関して本明細書において論考する目的で区切られている。

【0034】

超小型電子素子22を、第1の領域18内の基板12の第1の表面14に取り付けるこ

10

20

30

40

50

とができる。超小型電子素子 2 2 は半導体チップ又は別の同等のデバイスとすることができる。図 1 の実施形態では、超小型電子素子 2 2 は、従来のすなわち「表面を上にした (face-up)」形式として知られる形式で第 1 の表面 1 4 に取り付けられる。そのような実施形態では、ワイヤリード線 2 4 を用いて、超小型電子素子 2 2 を第 1 の表面 1 4 において露出している複数の導電性素子 2 8 のうちの幾つかに電気的に接続することができる。ワイヤリード線 2 4 はまた、基板 1 2 内のトレース (図示せず) 又は他の導電性機構に接合することができ、トレース (図示せず) 又は他の導電性機構は、次に、導電性素子 2 8 に接続される。

#### 【 0 0 3 5 】

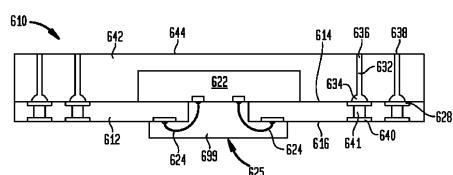

導電性素子 2 8 は、基板 1 2 の第 1 の表面 1 4 において露出するそれぞれの「コンタクト (contact)」又はパッド 3 0 を含む。本説明で使用されるように、導電性素子が、誘電体構造を有する別の要素の表面「において露出する (exposed at)」ものとして述べられるとき、それは、導電性構造が、誘電体構造の外側から誘電体構造の表面に向かって誘電体構造の表面に垂直な方向に移動する理論的ポイント (theoretical point) に接触するのに利用可能であることを示す。そのため、誘電体構造の表面において露出する端子又は他の導電性構造は、こうした表面から突出することができるか、こうした表面と同一平面上にあることができるか、又は、こうした表面に対して凹み、誘電体内の穴又は窪みを通して露出することができる。導電性素子 2 8 は、平坦で薄い要素ができる、導電性素子 2 8 において、パッド 3 0 が、基板 1 2 の第 1 の表面 1 4 において露出する。一実施形態では、導電性素子 2 8 は、実質的に円形ができる、また、互いの間で、又は、トレース (図示せず) によって超小型電子素子 2 2 に相互接続することができる。導電性素子 2 8 は、少なくとも基板 1 2 の第 2 の領域 2 0 内で形成することができる。加えて、或る特定の実施形態では、導電性素子 2 8 は、第 1 の領域 1 8 内に形成することができる。こうした配置構成は、「フリップチップ (flip-chip)」構成として知られるものにおいて、超小型電子素子 1 2 2 (図 3) を基板 1 1 2 に実装するときに特に有用であり、フリップチップ構成では、超小型電子素子 1 2 2 上のコンタクトは、超小型電子素子 1 2 2 の下に位置決めされるはんだバンプ 1 2 6 等によって、第 1 の領域 1 1 8 内の導電性素子 1 2 8 に接続することができる。図 2 2 に示されるような別の構成では、超小型電子素子 6 2 2 が、基板 6 1 2 上に下向きに実装され、基板 6 1 2 の表面 6 1 6 等の、外側に面する表面にわたって延在するワイヤリード 6 2 4 によってチップ上の導電性機構に電気的に接続される。図示される実施形態では、ワイヤリード 6 2 5 は基板 6 1 2 内の開口部 6 2 5 を通り抜け、オーバーモールド 6 9 9 によって封止することができる。

#### 【 0 0 3 6 】

一実施形態では、導電性素子 2 8 は、銅、金、ニッケル、又は、こうした用途にとって容認できる他の材料等の固体金属材料から形成される。他の材料には、銅、金、ニッケル、又はその組み合わせの 1 つ又は複数を含む種々の合金が含まれる。

#### 【 0 0 3 7 】

導電性素子 2 8 のうちの少なくとも幾つかは、基板 1 2 の第 2 の表面 1 6 において露出している導電性パッド等の対応する第 2 の導電性素子 4 0 に相互接続することができる。そのような相互接続は、導電性素子 2 8 及び 4 0 と同じ材料からなることができる導電性金属でライニング又は充填することができる基板 1 2 内に形成されるビア 4 1 を用いて完成させることができる。オプションで、導電性素子 4 0 は基板 1 2 上のトレースによって更に相互接続することができる。

#### 【 0 0 3 8 】

超小型電子アセンブリ 1 0 は、導電性素子 2 8 のパッド 3 0 等の導電性素子 2 8 の少なくとも幾つかに接合された複数のワイヤボンド 3 2 を更に含む。ワイヤボンド 3 2 がそのベース 3 4 において導電性素子 2 8 に接合され、それぞれのベース 3 4 及び基板 1 2 から離れた自由端 3 6 まで延在することができる。ワイヤボンド 3 2 の端部 3 6 は、超小型電子素子 2 2 、又は、超小型電子アセンブリ 1 0 内にあり、ひいては超小型電子素子 2 2 に接続される任意の他の導電性機構に電気接続されないか又はその他の方法で接合されない

10

20

30

40

50

点で自由であるとみなされる。換言すれば、自由端 36 は、アセンブリ 10 の外部の導電性機構に対して、はんだボール又は本明細書で論じる他の機構を通して直接的又は間接的に電気接続するのに利用可能である。端部 36 が、例えば封止層 42 によって所定の位置に保持されるか又は別の導電性機構にその他の方法で接合又は電気接続されることは、任意のこうした機構が超小型電子素子 22 に電気接続されない限り、端部が、本明細書で述べる「自由 (free)」でないことを意味しない。逆に、ベース 34 は、本明細書で述べるように、超小型電子素子 22 に直接的又は間接的に電気接続されるため自由でない。図 1 に示すように、ベース 34 は、形状が実質的に丸みを帯び、ベース 34 と端部 36 との間で画定されるワイヤボンド 32 のエッジ面 37 から外側に延在することができる。ベース 34 の特定のサイズ及び形状は、ワイヤボンド 32 を形成するために使用される材料のタイプ、ワイヤボンド 32 と導電性素子 28 との間の接続部の所望の強度、又はワイヤボンド 32 を形成するために使用される特定のプロセスに応じて変動することができる。ワイヤボンド 28 を作製する例示的な方法は、Otrembaに対する米国特許第 7,391,121 号及び米国特許出願公開第 2005/0095835 号（或る形態のワイヤボンディングであると考えることができるウェッジボンディングプロシージャを記載している）に記載されており、それらの開示はともに、引用することによりその全体が本明細書の一部をなすものとする。ワイヤボンド 32 が、付加的に又は代替的に、ワイヤボンド 32 から離れて延在する、基板 12 の第 2 の表面 16 において露出する導電性素子 40 に接合される代替の実施形態が可能である。

## 【0039】

ワイヤボンド 32 は、銅、金、ニッケル、はんだ又はアルミニウム等の導電性材料から作製することができる。さらに、ワイヤボンド 32 は、銅又はアルミニウム等の導電性材料のコアに、例えばコーティングがコアを覆って塗布されたもの等の、材料の組み合わせから作製することができる。コーティングは、アルミニウム、ニッケル等の第 2 の導電性材料からなることができる。代替的に、コーティングは、絶縁ジャケット等の絶縁材料からなることができる。一実施形態では、ワイヤボンド 32 を形成するために用いられるワイヤは、約 15  $\mu\text{m}$  ~ 約 150  $\mu\text{m}$  の厚み、すなわち、ワイヤの長さを横切る寸法での厚みを有することができる。ウェッジボンディングが用いられる実施形態を含む、他の実施形態では、ワイヤボンド 32 は、約 500  $\mu\text{m}$  までの厚みを有することができる。一般的に、ワイヤボンドは、当該技術分野において既知である特殊な装置を用いて、導電性素子 28、パッド、トレース等の導電性素子上に形成される。ワイヤセグメントの先端は加熱され、ワイヤセグメントが結合する受容面に対して押圧され、通常、導電性素子 28 の表面に接合されるボール又はボール状ベース 34 を形成する。ワイヤボンドを形成する所望の長さのワイヤセグメントがボンディングツールから引き出され、その後、ボンディングツールは、所望の長さにおいてワイヤボンドを切断することができる。例えば、アルミニウムのワイヤボンドを形成するために用いることができるウェッジボンディングは、表面に対して概ね平行に存在するウェッジを形成するように、ワイヤの加熱された部分が受容面にわたって引っ張られるプロセスである。ウェッジボンディングされたワイヤボンドは、その後、必要に応じて上方に曲げ、所望の長さ又は位置まで延長し、その後、切断することができる。特定の実施形態では、ワイヤボンドを形成するために用いられるワイヤは、円柱形の断面を有することができる。それ以外の場合には、ワイヤボンド又はウェッジボンディングされるワイヤボンドを形成するようにツールから送り出されるワイヤは、例えば、長方形又は台形等の多角形の断面を有することができる。

## 【0040】

ワイヤボンド 32 の自由端 36 は端面 38 を有する。端面 38 は、コンタクトの少なくとも一部を複数のワイヤボンド 32 のそれぞれの端面 38 によって形成されるアレイで形成することができる。図 2 は、端面 38 によって形成されるこうしたコンタクトのアレイについての例示的なパターンを示す。こうしたアレイは、エリアアレイ構成で形成することができ、その変形形態は、本明細書で述べる構造を使用して実施することができる。こうしたアレイは、超小型電子アセンブリ 10 を、プリント回路基板（「PCB」）又は他

10

20

30

40

50

のパッケージングされた超小型電子素子（その例が図6に示される）等の別の超小型電子構造に電気的及び機械的に接続するのに使用することができる。こうした積層式配置構成では、ワイヤボンド32並びに導電性素子28及び40は、それぞれが異なる信号電位を有する複数の電子信号を、それらを通して搬送して、異なる信号が、単一積層体内の異なる超小型電子素子によって処理されることを可能にすることができる。はんだ塊52は、端面38を導電性素子40に電気的及び機械的に取付けること等によってこうした積層体内で超小型電子アセンブリを相互接続するのに使用することができる。

#### 【0041】

超小型電子アセンブリ10は、誘電体材料から形成される封止層42を更に含む。図1の実施形態では、封止層42は、超小型電子素子22又は導電性素子28によって普通なら被覆又は占有されない基板12の第1の表面14の部分を覆って形成される。同様に、封止層42は、ワイヤボンド32によって普通なら被覆されない、導電性素子28のパッド30を含む導電性素子28の部分を覆って形成される。封止層42はまた、超小型電子素子22、ベース34及びワイヤボンドのエッジ面37の少なくとも一部を含むワイヤボンド32を実質的に被覆することができる。ワイヤボンド32の一部分は、封止層42によって被覆されないままであることができ、このことは非封止とも呼ぶことができる。それにより、ワイヤボンドが、封止層42の外側に位置する特徴部又は要素に電気接続するのに利用可能にされる。一実施形態では、ワイヤボンド32の端面38は、封止層42の主表面44内で封止層42によって被覆されないままである。端面38を封止層42によって被覆されないままにすることに加えて又はその代替として、エッジ面37の一部分が封止層42によって被覆されない他の実施形態が可能である。換言すれば、封止層42は、端面38、エッジ面37、又はこれら2つの組み合わせ等のワイヤボンド36の一部分を除いて、第1の表面14の上で超小型電子アセンブリ10の全てを被覆することができる。図に示す実施形態では、封止層42の主表面44等の表面は、基板12の第1の表面14から、超小型電子素子22を被覆するのに十分に長い距離に離間することができる。したがって、ワイヤボンド32の端部38が表面44と同一平面上にある超小型電子アセンブリ10の実施形態は、超小型電子素子22より高いワイヤボンド32及びフリップチップ接続のために下にある任意のはんだバンプを含むであろう。しかし、封止層42についての他の構成が可能である。例えば、封止層は、高さが異なる複数の表面を有することができる。こうした構成では、端部38がその中に位置決めされる表面44は、超小型電子素子22がその下に位置付けられる、上方に面する表面より高く又は低くすることができる。

#### 【0042】

封止層42は、超小型電子アセンブリ10、特にワイヤボンド32内の他の素子を保護する役割を果たす。これによって、構造体を試験することによる損傷、又は他の超小型電子構造体への移送若しくは組立て中の損傷をより受けにくい、より強固な構造体が可能になる。封止層42は、米国特許出願公開第2010/0232129号に記載されている誘電体材料等の、絶縁特性を有する誘電体材料から形成することができる。この特許文献は引用することにより本明細書の一部をなすものとする。

#### 【0043】

図3は、ワイヤボンド132を有する超小型電子アセンブリ110の一実施形態を示す。このワイヤボンド132は、それぞれのベース34の真上に配置されない端部136を有する。すなわち、或る平面を実質的に画定するように2つの横方向に延在するものとして基板112の第1の表面114を考えると、端部136又はワイヤボンド132のうちの少なくとも1つのワイヤボンド132は、ベース134の対応する横位置からこれらの横方向の少なくとも一方の方向に変位される。図3に示すように、ワイヤボンド132は、図1の実施形態の場合と同様に、ワイヤボンド132の縦軸に沿って実質的に真っ直ぐであることができ、縦軸は、基板112の第1の表面114に対して角度146で角度付けされる。図3の断面図は第1の表面114に垂直な第1の平面を通して角度146を示すだけであるが、ワイヤボンド132はまた、その第1の平面と第1の表面114との両

10

20

30

40

50

方に垂直な別の平面内で第1の表面114に対して角度付けすることができる。こうした角度は、角度146と実質的に等しいか又は異なることができる。すなわち、ベース134に対する端部136の変位は、2つの横方向にあることができ、それらの方向のそれぞれの方向に同じ距離又は異なる距離であることができる。

#### 【0044】

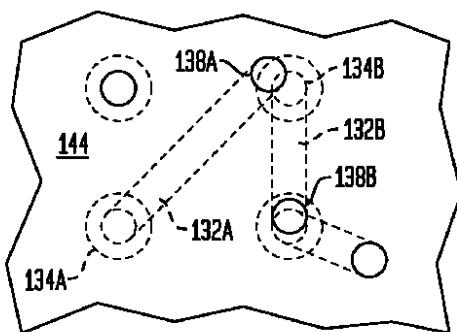

一実施形態では、ワイヤボンド132の種々のワイヤボンドは、アセンブリ110全体を通して異なる方向に異なる量だけ変位することができる。こうした配置構成は、アセンブリ110が、基板12のレベルと比較して表面144のレベルで異なるように構成されるアレイを有することを可能にする。例えば、アレイは、基板112の第1の表面114におけるものと比較して、第1の表面114のレベルにおいてよりも表面144上でより小さな全体エリアを被覆するか又はより小さなピッチを有することができる。さらに、幾つかのワイヤボンド132は、異なるサイズのパッケージングされた超小型電子素子の積層式配置構成を収容するように超小型電子素子122の上方に位置決めされる端部136を有することができる。図19に示す別の例では、ワイヤボンド132は、1つのワイヤボンド132Aの端面138Aが別のワイヤボンド132Bのベース134Bの上に実質的に位置決めされ、そのワイヤボンド132Bの端面138Bが他の所に位置決めされるように構成することができる。こうした配置構成は、第2の表面116上の対応するコンタクトアレイの位置と比較して、コンタクトのアレイ内でコンタクト端面138の相対的位置を変更するものとして参照することができる。こうしたアレイ内で、コンタクト端面の相対的位置は、超小型電子アセンブリの用途又は他の要件に応じて所望に応じて変更又は変動することができる。

#### 【0045】

図30に示される更なる例では、ベース134が或るピッチを有する第1のパターンにおいて配置されるように、ワイヤボンド132を配置することができる。端面138を含むその封止されない部分139を、導電性素子128に取り付けられるワイヤボンドのそれぞれの隣接するベース134間の最小ピッチより大きな最小ピッチを有する封止層142の主面144上の位置に、或るパターンにおいて配置することができるよう、ワイヤボンド132を構成することができる。したがって、封正面146における隣接するワイヤボンド間の最小ピッチは、ワイヤボンドが取り付けられる基板の導電性素子128間の対応する最小ピッチより大きくすることができる。

#### 【0046】

これを果たすために、図30に示されるように、ワイヤボンドに角度を付けることができるか、又は端面138が、上記で論じられたようにベース134から1つ又は複数の横方向に変位するように、例えば、図4に示されるように、ワイヤボンドを湾曲させることができる。図30に更に示されるように、導電性素子128及び端面138は、それぞれの行又は列に配置することができ、1つの行内の端面138の横方向変位は別の行内より大きくすることができる。これを果たすために、ワイヤボンド132は、例えば、基板112の表面116に対して異なる角度146A、146Bをなすことができる。

#### 【0047】

図4は、ベース234に対して変位した横位置に端部236を有するワイヤボンド232を有する超小型電子サブアセンブリ210の更なる実施形態を示す。図4の実施形態では、ワイヤボンド132は、ワイヤボンド132内に湾曲部分248を含むことによって、この横変位を達成する。湾曲部分248は、ワイヤボンド形成プロセス中の更なるステップにおいて形成することができ、例えばワイヤ部分が所望の長さまで引き出されている間にもたらすことができる。このステップは、単一機械の使用を含むことができる入手可能なワイヤボンディング機器を使用して実施することができる。

#### 【0048】

湾曲部分248は、必要に応じて種々の形状をとって、ワイヤボンド232の端部236の所望の位置を達成することができる。例えば、湾曲部分248は、図4で示す形状又は(図5に示す形状等の)より平滑な形状等の種々の形状のS字形状湾曲として形成する

10

20

30

40

50

ことができる。さらに、湾曲部分 248 は、端部 236 よりベース 234 の近くに配置することができ、その逆も同様である。湾曲部分 248 はまた、螺旋若しくはループの形態にすることができるか又は複数の方向若しくは異なる形状若しくは特徴の湾曲を含む複合体にすることができる。

【0049】

図 5 は、ベース 334 と端部 336 との間で種々の相対的横変位をもたらす種々の形状を有するワイヤボンド 332 の組み合わせを有する超小型電子パッケージ 310 の更なる例示的な実施形態を示す。ワイヤボンド 332A の幾つかは、実質的に真っ直ぐであり、端部 336A がそれぞれのベース 334A の上方に配置され、一方、他のワイヤボンド 332B は、僅かに湾曲した部分 348B を含み、端部 336B とベース 334B との間に多少の相対的横変位をもたらす。さらに、幾つかのワイヤボンド 332C は、スイープ形状を有する湾曲部分 348C を含み、関連ベース 334C から横方向に、端部 334B の距離より長い距離に変位される端部 336C をもたらす。図 5 はまた、こうしたワイヤボンド 332Ci 及び 332Cii の例示的な対を示し、ワイヤボンド 332Ci 及び 332Cii は、基板レベルアレイの同じ行内に位置決めされるベース 334Ci 及び 334Cii 並びに対応する表面レベルアレイの異なる行内に位置決めされる端部 336Ci 及び 336Cii を有する。

【0050】

その側面 47 上で封止層 342 によって被覆されないように構成されるワイヤボンド 332D の更なる変形形態が示される。図示する実施形態では、自由端 336D は被覆されていないが、付加的に又は代替的に、エッジ面 337D の一部分を、封止層 342 によって被覆しないことができる。こうした構成は、適切な機構に対する電気接続によって超小型電子アセンブリ 10 を接地するため、又は、超小型電子アセンブリ 310 の横方向に配設された他の機構に機械的かつ電気的に接続するのに使用することができる。さらに、図 5 は、主表面 342 に比べて基板 12 の近くに配置される窪んだ表面 345 を画定するために、エッチング除去されるか、モールドされるか、又はその他の方法で形成された封止層 342 のエリアを示す。ワイヤボンド 332A 等の 1 つ又は複数のワイヤボンドは、窪んだ表面 345 に沿うエリア内で被覆されない可能性がある。図 5 に示す例示的な実施形態では、端面 338A 及びエッジ面 337A の一部分は、封止層 342 によって被覆されない。こうした構成は、はんだボール等による、別の導電性素子への接続を、はんだが、端面 338 に接合することに加えて、エッジ面 337A に沿ってウェーブティングし、エッジ面 337A に接合することを可能にすることによって提供することができる。ワイヤボンドの一部分が、窪んだ表面 345 に沿って封止層 342 によって被覆されない可能性がある他の構成が可能であり、その構成は、端面が窪んだ表面 345 と実質的に同一平面上にある構成又は封止層 342 の任意の他の表面に関して本明細書で示す他の構成を含む。同様に、ワイヤボンド 332D の一部分が、側面 347 に沿って封止層 342 によって被覆されない他の構成は、封止層の主表面の変形に関して本明細書の他の所で論じる構成と同様であることができる。

【0051】

図 5 は、例示的な配置構成で 2 つの超小型電子素子 322 及び 350 を有する超小型電子アセンブリ 310 を更に示し、その配置構成では、超小型電子素子 350 は、超小型電子素子 322 上に上向きで積層される。この配置構成では、リード線 324 が、超小型電子素子 322 を基板 312 上の導電性機構に電気接続するのに使用される。種々のリード線が、超小型電子素子 350 を超小型電子アセンブリ 310 の種々の他の特徴部に電気接続するために使用される。例えば、リード線 380 は、超小型電子素子 350 を基板 312 の導電性機構に電気接続し、リード線 382 は、超小型電子素子 350 を超小型電子素子 322 に電気接続する。さらに、ワイヤボンド 332 の種々のワイヤボンドと構造が類似することができるワイヤボンド 384 が、超小型電子素子 350 に電気接続される封止層 342 の表面 344 上のコンタクト表面 386 を形成するのに使用される。これは、封止層 342 の上方から、別の超小型電子アセンブリの機構を超小型電子素子 350 に直接

10

20

30

40

50

電気接続するために使用することができる。超小型電子素子 322 に接続されるこうしたリード線もまた含まれる場合があり、それは、こうした超小型電子素子が、その超小型電子素子に固着した第 2 の超小型電子素子 350 なしで存在するときを含む。開口（図示せず）を、封止層 342 内に形成することができ、その開口は、封止層 342 の表面 344 から、例えばリード線 380 に沿う地点まで延在し、それにより、表面 344 の外側に位置する要素によってリード線 380 に電気接続するためにリード線 380 に対するアクセスを提供する。同様な開口は、自身の端部 336C から離れた地点のワイヤボンド 332C の上等、他のリード線又はワイヤボンド 332 の任意のものの上に形成することができる。こうした実施形態では、端部 336C は、表面 344 の下に位置決めすることができ、開口は、端部 336C に電気接続するための唯一のアクセスを提供する。

10

### 【0052】

図 6 は、超小型電子アセンブリ 410 及び 488 の積層式パッケージを示す。こうした配置構成では、はんだ塊 452 は、アセンブリ 410 の端面 438 をアセンブリ 488 の導電性素子 440 に電気的及び機械的に接続する。積層式パッケージは、更なるアセンブリを含むことができ、最終的に、電子デバイス内で使用するために PCB 490 等の上のコンタクト 492 に取り付けることができる。こうした積層式配置構成では、ワイヤボンド 432 及び導電性素子 430 は、両者を通してそれぞれが異なる信号電位を有する複数の電子信号を搬送して、異なる信号が、単一積層体内の、超小型電子素子 422 又は超小型電子素子 489 等の異なる超小型電子素子によって処理されることを可能にすることができます。

20

### 【0053】

図 6 の例示的な構成では、ワイヤボンド 432 は、湾曲部分 448 を有するように構成され、それにより、ワイヤボンド 432 の端部 436 の少なくとも幾つかは、超小型電子素子 422 の主表面 424 の上に重なるエリア内に延在する。こうしたエリアは、超小型電子素子 422 の外周によって画定され、超小型電子素子 422 から上方に延在することができる。こうした構成の例は、図 18 で基板 412 の第 1 の表面 414 の方に面する図から示され、ワイヤボンド 432 は、超小型電子素子 422 の後主表面に載り、超小型電子素子 422 は、超小型電子素子 422 の前面 425 で基板 412 にフリップチップボンディングされる。別の構成（図 5）では、超小型電子素子 422 は、基板 312 に上向きで実装することができ、前面 325 は基板 312 に面さず、少なくとも 1 つのワイヤボンド 336 は、超小型電子素子 322 の前面の上に重なる。一実施形態では、こうしたワイヤボンド 336 は、超小型電子素子 322 に電気接続されない。基板 312 にボンディングされるワイヤボンド 336 はまた、超小型電子素子 350 の前面又は後面の上に重なることができる。図 18 に示す超小型電子アセンブリ 410 の実施形態は、導電性素子 428 が第 1 のアレイを形成するパターンで配列され、そのパターンでは、導電性素子 428 が、超小型電子素子 422 を囲む行及び列で配列され、個々の導電性素子 428 間に所定のピッチを有することができる。ワイヤボンド 432 は、ワイヤボンド 432 のそれぞれのベース 434 が導電性素子 428 によって構成された第 1 のアレイのパターンに従うように導電性素子 428 に接合される。しかし、ワイヤボンド 432 は、ワイヤボンド 432 のそれぞれの端部 436 が、第 2 のアレイ構成による、異なるパターンで配列することができるように構成される。図示する実施形態では、第 2 のアレイのピッチは、第 1 のアレイのピッチと異なることができ、また場合によっては第 1 のアレイのピッチより微細であることができる。しかし、第 2 のアレイのピッチが第 1 のアレイより大きい他の実施形態又は導電性素子 428 が所定のアレイで配置されるのではなく、ワイヤボンド 432 の端部 436 が所定のアレイで配置される他の実施形態が可能である。またさらに、導電性素子 428 は、基板 412 全体を通して位置決めされるアレイのセットで構成することができ、ワイヤボンド 432 は、端部 436 が異なるアレイのセット又は単一アレイであるように構成することができる。

30

### 【0054】

図 6 は、超小型電子素子 422 の表面に沿って延在する絶縁層 421 を更に示す。絶縁

40

50

層421は、ワイヤボンドを形成する前に、誘電体材料又は他の電気絶縁性材料から形成することができる。絶縁層421は、超小型電子素子が、超小型電子素子にわたって延在するワイヤボンド423の任意のワイヤボンドに接触することを防止することができる。特に絶縁層421は、ワイヤボンド間の電気的短絡及びワイヤボンドと超小型電子素子422との電気的短絡を回避することができる。こうして、絶縁層421は、ワイヤボンド432と超小型電子素子422との間の意図しない電気的接触による誤動作又は考えられる損傷を回避するのに役立つことができる。

#### 【0055】

図6及び図18に示すワイヤボンド構成は、例えば超小型電子アセンブリ488及び超小型電子素子422の相対的なサイズが普通なら許容しない或る特定の事例において、超小型電子アセンブリ410が、超小型電子アセンブリ488等の別の超小型電子アセンブリに接続することを可能にすることができます。図6の実施形態では、超小型電子アセンブリ488は、コンタクトパッド440の幾つかが、超小型電子素子422の前面424又は後面426のエリアより小さいエリア内のアレイ内にあるようにサイズ決定される。ワイヤボンド432の代わりにピラー等の実質的に垂直な導電性機構を有する超小型電子アセンブリでは、導電性素子428とパッド440との間の直接接続が可能でないことになる。しかし、図6に示すように、適切に構成された湾曲部分448を有するワイヤボンド432は、超小型電子アセンブリ410と超小型電子アセンブリ488との間で必要な電気接続を行うのに適切な位置に端部436を有することができる。こうした配置構成は、積層式パッケージを作製するために使用することができ、超小型電子アセンブリ418は、例えば、所定のパッドアレイを有するDRAMチップ等であり、また、超小型電子素子422は、DRAMチップを制御するように構成されるロジックチップである。これによつて、ワイヤボンド432がDRAMチップとの所望の接続を行う必要がある所ではどこにでも位置決めされる端部436を有することができるので、単一タイプのDRAMチップが、DRAMチップより大きいサイズを含む、種々のサイズの幾つかの異なるロジックチップとともに使用されることを可能にすることができます。代替の実施形態では、超小型電子パッケージ410は、別の構成のプリント回路基板490上に実装することができ、ワイヤボンド432の非封止表面436は、回路基板490のパッド492に電気接続される。さらに、こうした実施形態では、パッケージ488の変更形態等の別のマクロ電子パッケージが、パッド440に接合されたはんだボール452によってパッケージ410上に実装することができる。

#### 【0056】

複数の超小型電子素子を有する超小型電子パッケージについての更なる配置構成は、図31A～図31Cに示される。これらの配置構成は、例えば図5に示すワイヤボンド配置構成に関連して、また、以下で更に論じる図6の積層式パッケージ配置構成で使用することができる。具体的には、図31Aは、下側超小型電子素子1622が、基板1612の表面1614上の導電性素子1628にフリップチップボンディングされる配置構成を示す。第2の超小型電子素子1650は、第1の超小型電子素子1622の上に上向きに実装され、ワイヤボンド1688を通して更なる導電性素子1628に接続される。図31Bは、第1の超小型電子素子1722が表面1714上に上向きに実装され、ワイヤボンド1788を通して導電性素子1728に接続される構成を示す。第2の超小型電子素子1750は、第1の超小型電子素子1722の前面に面し、その前面上の対応するコンタクトに接合される、第2の超小型電子素子1750の1組のコンタクト1726を通して、第1の超小型電子素子1722の上にフリップチップ実装される。第1の超小型電子素子1722のこれらのコンタクトは更に、第1の超小型電子素子1722の回路パターンを通して接続することができ、ワイヤボンド1788のうちの幾つかによって、基板1712上の導電性素子1728に接続することができる。

#### 【0057】

図31Cは、第1の超小型電子素子1822及び第2の超小型電子素子1850が、基板1812の表面1814上で並んで実装される配置構成を示す。超小型電子素子(及び

10

20

30

40

50

更なる超小型電子素子)の一方又は両方は、本明細書で述べる上向き又はフリップチップ構成で実装することができる。さらに、こうした配置構成で使用される超小型電子素子の任意の超小型電子素子は、こうした超小型電子素子の一方若しくは両方上の、又は基板上の、又はその両方の上の回路パターンを通して互いに接続することができ、回路パターンは、超小型電子素子が電気接続されるそれぞれの導電性素子 1828 を電気接続する。

#### 【0058】

図 7 は、再分配層 54 が封止層 42 の表面 44 に沿って延在している、図 1 に示されるタイプの超小型電子アセンブリ 10 を示す。図 7 に示されるように、トレース 58 が、ワイヤボンド 32 の端面 38 に電気的に接続される内部コンタクトパッド 61 に電気的に接続され、再分配層 54 の基板 56 を貫通して、基板 56 の表面 62 上に露出するコンタクトパッド 60 まで延在する。その後、更なる超小型電子アセンブリをはんだ塊等によってコンタクトパッド 60 に接続することができる。再分配層 54 に類似の構造が、ファンアウト層として知られる構造において基板 12 の第 2 の表面 16 に沿って延在することができる。ファンアウト層によって、超小型電子アセンブリ 10 は、その層がない場合に可能であった導電性素子 40 のアレイとは異なる構成のアレイに接続できるようになる。

#### 【0059】

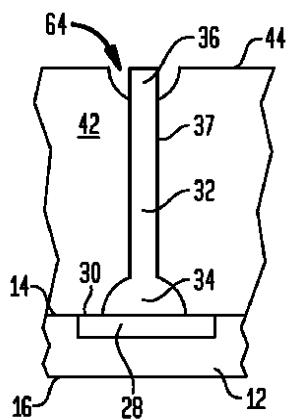

図 8 A ~ 図 8 E は、図 1 ~ 図 7 に類似の構造内のワイヤボンド 32 の端部 36 の構造、又はその端部 36 付近の構造において実現することができる種々の構成を示す。図 8 A は、ワイヤボンド 32 の端部 36 がキャビティ 64 において封止層の小面 43 より上方に突出するように、キャビティ 64 が封止層 42 の一部分に形成される構造を示す。図示される実施形態では、端面 38 は、封止層 42 の主面 44 より下方に位置決めされ、キャビティ 64 は、表面 44 において端面 38 を露出させるように構造化され、電子構造が端面に接続できるようにする。端面 38 が表面 44 と実質的に同一平面をなすか、又は表面 44 の上方に位置する他の実施形態も可能である。さらに、キャビティ 64 は、キャビティ 64 内の封止層 42 によって、ワイヤボンド 32 の端部 36 付近のワイヤボンド 32 のエッジ面 37 の部分が被覆されない形態を示す。これにより、端面 38 と、端部 36 付近のエッジ面 37 の被覆されない部分との両方から、はんだ接続等の、アセンブリ 10 の外部からワイヤボンド 32 への接続を実施できるようになる。そのような接続が図 8 B に示されており、はんだ塊 52 を用いて第 2 の基板 94 へのより強固な接続を設けることができる。一実施形態では、キャビティ 64 は、表面 44 の下に約 10 μm ~ 約 50 μm の深さを有することができ、約 100 μm ~ 約 300 μm の幅を有することができる。図 8 B は、図 8 A の構造に類似の構造を有するが、側壁 65 がテーパを付けられているキャビティを示す。さらに、図 8 B は、その基板の表面 98 において露出するコンタクトパッド 96 においてはんだ塊 52 によってワイヤボンド 32 に電気的及び機械的に接続される第 2 の超小型電子アセンブリ 94 を示す。

#### 【0060】

キャビティ 64 は、キャビティ 64 の所望のエリアにおいて封止層 42 の一部分を除去することによって形成することができる。これは、レーザエッティング、ウェットエッティング、ラッピング等を含む既知のプロセスによって果たすことができる。代替的には、封止層 42 が射出成形によって形成される実施形態では、キャビティ 64 は、型内に対応する機構を含むことによって形成することができる。そのようなプロセスが米国特許出願公開第 2010/0232129 号において論じられており、その特許出願公開は引用することによりその全体が本明細書の一部をなすものとする。図 8 B に示されるキャビティ 64 のテーパを付けられた形状は、その形成時に用いられる特定のエッティングプロセスの結果とすることができる。

#### 【0061】

図 8 C 及び図 8 E は、ワイヤボンド 32 上に実質的に丸みを帯びた端部分 70 を含む端部構造を示す。丸みを帯びた端部分 70 は、ベース 34 と端部 36 との間のワイヤボンド 32 の部分の断面より広い断面を有するように構成される。更なる丸みを帯びた端部分 70 は、エッジ面 71 を含み、エッジ面 71 は、ワイヤボンド 32 のエッジ面 37 と端部分

10

20

30

40

50

70との間の移行部においてワイヤボンド32のエッジ面37から外側に延在する。丸みを帯びた端部分70を組み込むことは、固着機構を設けることによって、封止層42内にワイヤボンド32を固定するように作用することができ、表面71の方向における変化が、封止層42に、3方から端部70を包囲する場所を与える。これは、ワイヤボンド32が基板12上の導電性素子28から分離し、結果として、電気的に接続し損なうのを防ぐのに役立つことができる。さらに、丸みを帯びた端部分70は、電子的接続を実施することができる、表面44内の封止層42によって被覆されない表面積を増やすことができる。図8Eに示されるように、丸みを帯びた端部分70は、さらに、表面44の上方に延在することができる。代替的には、図8Cに示されるように、丸みを帯びた端部分70は、表面44と実質的に同一平面をなす表面を設けるように研削することができるか、又は別の方法で平坦化することができ、ワイヤボンド32の断面より広い面積を有することができる。

#### 【0062】

丸みを帯びた端部分70は、ワイヤボンド32を作製するために用いられるワイヤの端部において火炎又は火花の形で局所化された熱を当てることによって形成することができる。既知のワイヤボンディング機を変更して、このステップを実行することができ、このステップは、ワイヤを切断した直後に行うことができる。このプロセスにおいて、熱は、その端部においてワイヤを溶解する。この局所化された液体金属部分が、その表面張力によって丸くされ、金属が冷えるときに保持される。

#### 【0063】

図8Dは、超小型電子アセンブリ10のための構成を示しており、ワイヤボンド32の端部36が封止層42の主面44の上方の空間内に位置する表面38を含む。そのような構成は、具体的には、封止層42によって被覆されないエッジ面37の部分に沿って表面44の上方にウィッキングするはんだ塊68とのより強固な接続を設けることによって、上記でキャビティ64に関して論じられたものと類似の利点を与えることができる。一実施形態では、端面38は、約10μm～約50μmの距離だけ表面42の上方の空間内に位置することができる。さらに、図8Dに示される実施形態、及びエッジ面37の一部分が封止層42の表面の上方において封止層42によって被覆されない他の実施形態のいずれかにおいて、端部は、その上に形成された保護層を含むことができる。そのような層は、金から形成される層、酸化物コーティング又はOSPを含む、酸化保護層を含むことができる。

#### 【0064】

図9は、ワイヤボンド32の端面38上にスタッドバンプ72が形成されている超小型電子アセンブリ10の実施形態を示す。スタッドバンプ72は、端面44の上に別の、変更されたワイヤボンドを付着させ、オプションで、表面44の一部分に沿って引き伸ばすことによって、超小型電子アセンブリ10を作製した後に形成することができる。変更されたワイヤボンドは、ワイヤの長さを引き出すことなく、そのベースの付近で切断されるか、又は別の方法で切られる。UBM等の結合層を最初に被着することなく、特定の金属を含むスタッドバンプ72を端部38に直接付着させることができ、それゆえ、はんだによって直接ぬらすことができないボンドパッドへの導電性相互接続を形成する方法を与えることができる。これは、ワイヤボンド32がぬらすことができない金属から形成されるときに役に立つ可能性がある。一般的に、銅、ニッケル、銀、プラチナ及び金のうちの1つ又は複数から基本的になるスタッドバンプをこのように付着させることができる。図9は、更なる超小型電子アセンブリへの電子的又は機械的接続のために、スタッドバンプ72上に形成されるはんだ塊68を示す。

#### 【0065】

図10A～図10Dは、曲げられた、又は湾曲した形状を含むワイヤボンド32の端部36のための構成を示す。各実施形態において、ワイヤボンド32の端部36は、エッジ面76の少なくとも一部が、例えば、主面44によって被覆されないようにその部分74が封止層42の表面44に対して実質的に平行に延在するように曲げられる。エッジ面3

10

20

30

40

50

7のこの部分は、表面44の外側上方に延在することができるか、又は表面44と実質的に同一平面に延在するように研削するか、若しくは別の方法で平坦化することができる。図10Aの実施形態は、表面44に対して平行であり、表面44に対して実質的に垂直である端面38において終端する、端部36の部分74において、ワイヤボンド32内の急な曲がりを含む。図10Bは、表面44に対して平行である端部36の部分74付近において、図10Aに示されるよりも緩やかな曲線を有する端部36を示す。図3、図4又は図5に示される構成によるワイヤボンドの部分が、表面44に対して実質的に平行な部分を有し、表面44内の場所において封止層42によって被覆されないエッジ面の部分を有する端部を含む構成を含む、他の構成も可能である。さらに、図10Bの実施形態は、ワイヤボンドの端部において鉤状の部分75を含み、その部分は、端面38を封止層42内の表面44の下方に位置決めする。これは、封止層42内に、除去される可能性が小さい、端部36のためのより強固な構造を与えることができる。図10C及び図10Dは、それぞれ図10A及び図10Bに示す構造に類似であるが、封止層42内に形成されるキャビティ64によって、表面44に沿った或る場所において封止層42によって被覆されない構造を示す。これらのキャビティは、図8A及び図8Bに関して上記で論じられた構造に、構造的に類似することができる。表面44に対して平行に延在する部分74を含む端部36を含むことは、延長された被覆されないエッジ面75があることにより、その端部と接続するための表面積を増やすことができる。そのような部分74の長さは、ワイヤボンド32を形成するために用いられるワイヤの断面の幅より長くすることができる。

## 【0066】

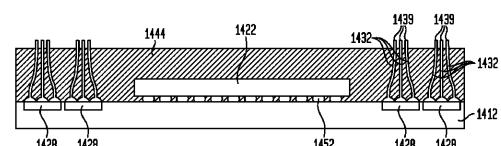

図29に示される更なる例では、単一の導電性素子1428上に複数のワイヤボンド1432を接合することができる。そのような一群のワイヤボンド1432を用いて、封止層1442上に、導電性素子1428との電気的接続のための更なる接続点を作製することができる。共通接合ワイヤボンド1432の露出した部分1439は、例えば、概ね導電性素子1428自体のサイズのエリア、又はワイヤボンド1432群との外部接続を作製するためのボンディング塊の意図したサイズを近似する別のエリアにおいて、封止層1442の表面1444上で1つのグループにまとめることができる。そのようなワイヤボンド1432は、図示されるように、ボールボンディングすることができるか、上記のように、導電性素子1428上にエッジボンディングすることができる。基板上の導電性素子への複数のワイヤボンドを形成するとき、例えば、レーザ又は他の切断器具によって、ワイヤボンディングプロセス中に金属ワイヤを切るために本明細書において記述される種々の技法を利用することができる。

## 【0067】

図11～図15は、超小型電子アセンブリの製造方法の種々のステップにおける超小型電子アセンブリ10を示す。図11は、超小型電子素子22が第1の表面14上、かつ第1の表面14の第1の領域18内で基板12に電気的及び機械的に接続されたステップにおける超小型電子アセンブリ10'を示す。超小型電子素子22は、図11において、例えば、基板の向かい合う表面14上の対応するコンタクトに面し、接合される超小型電子素子22上のコンタクトを通して、フリップチップ構成において基板12上に実装されるよう示される。例えば、超小型電子素子のコンタクトと基板のコンタクトとの間の接合部は、塊状物26、例えば、導電性ペースト、導電性マトリックス材料、はんだ塊等の導電性材料を通して作製することができ、コンタクトは、数ある中でも、パッド、ポスト、例えば、マイクロピラー、スタッドバンプ等の任意の適切な構成からなることができる。本明細書において、「フリップチップボンディング」は、超小型電子素子及び基板の対応するコンタクト間、又は超小型電子素子と別の超小型電子素子との間の対面の電気的結合の構成を意味するために用いられる。

## 【0068】

代替的には、図1の例において見られるように、代わりに、超小型電子素子のコンタクトと基板との上向きのワイヤボンディングを用いることができる。図11に示す方法ステップの実施形態では、誘電体アンダーフィル層66は、超小型電子素子22と基板12と

10

20

30

40

50

の間に設けることができる。

【0069】

図12は、基板12の第1の表面14において露出する導電性素子28のパッド30にワイヤボンド32が付着されている超小型電子アセンブリ10'を示す。論じられたように、ワイヤボンド32は、ワイヤセグメントの端部を加熱して、端部を軟化させることによって付着させることができ、それにより、ワイヤボンドは、導電性素子28上に押し付けられると、導電性素子28に対して堆積ボンドを形成し、ベース34を形成する。ワイヤは、その後、導電性素子28から引き出され、ワイヤボンド32の端部36及び端面38を形成するために切断されるか又はその他の方法で切られる前に、所望される場合、指定された形状になるよう操作される。代替的に、ワイヤボンド32は、例えば、ウェッジボンディングによってアルミニウムワイヤから形成することができる。ウェッジボンディングは、ワイヤボンドの端部に隣接するワイヤの一部分を加熱し、そのワイヤの一部分を、導電性素子28に圧力を加えた状態で導電性素子28に沿って引き抜くことによって形成される。こうしたプロセスは、米国特許第7,391,121号に更に記載され、その開示は、引用することによりその全体が本明細書の一部をなすものとする。

【0070】

図13では、封止層42は、基板の第1の表面14を覆って付着されることによって超小型電子アセンブリ10'に付加されており、封止層42は基板から上方にかつワイヤボンド32のエッジ面37に沿って延在する。封止層42はまた、アンダーフィル層66を被覆する。封止層42は、図12に示す超小型電子アセンブリ10'を覆って樹脂を堆積させることによって形成することができる。これは、アセンブリ10'を受け取ることができる封止層42の所望の形状のキャビティを有する適切に構成されたモールド内にアセンブリ10'を配置することによって行うことができる。こうしたモールド及びそのモールドによって封止層を形成する方法は、米国特許出願公開第2010/0232129号に示し記載されているようなものとすることができる、その開示は、引用することによりその全体が本明細書の一部をなすものとする。代替的に、封止層42は、少なくとも部分的にコンプライアントな材料から所望の形状に事前作製することができる。この構成では、誘電体材料のコンプライアントな特性は、封止層42が、ワイヤボンド32及び超小型電子素子22を覆った位置に圧入されることを可能にする。こうしたステップでは、ワイヤボンド32は、コンプライアント材料に貫入し、その材料内のそれぞれの穴を形成し、その穴に沿って、封止層42がエッジ面37に接触する。さらに、超小型電子素子22は、コンプライアント材料内に受け取ることができるようコンプライアント材料を変形することができる。コンプライアント誘電体材料は、圧縮されて、外側表面44上で端面38を露出させることができる。代替的に、どんな過剰なコンプライアント誘電体材料も、封止層から除去して、ワイヤボンド32の端面38がその上で被覆されない表面44を形成することができるか、又は、表面63内の場所で端面38を被覆しないキャビティ64を形成することができる。

【0071】

図13に示す実施形態では、封止層は、最初に封止層の表面44がワイヤボンド32の端面38の上で離間するように形成される。端面38を露出させるために、端面38の上有する封止層42の部分を除去し、図14に示すように、端面42と実質的に同一平面上にある新しい表面44'を露出させることができる。代替的に、図8A及び図8Bに示すキャビティ等の、端面38が封止層42によって被覆されないキャビティ64を形成することができる。更なる代替形態では、封止層42は、表面44が既に端面48と実質的に同一平面上にあるように、又は、図8Dに示すように、表面44が端面48の下に配置されるように形成することができる。封止層42の一部分の除去は、必要がある場合、研削、ドライエッティング、レーザエッティング、ウェットエッティング、ラッピング等によって達成することができる。所望される場合、ワイヤボンド32の端部36の一部分はまた、同じステップ又は更なるステップで除去されて、表面44と実質的に同一平面上にある実質的に平坦な端面38を達成することができる。所望される場合、キャビティ64を、こう

したステップ後に形成することもできるか、又は、図10に示すように、スタッダードバンプを付着させることもできる。結果得られる超小型電子アセンブリ10は、その後、PCB上に固着させることができると又はそうでなければ、図6に示すように、更なるアセンブリ、例えば積層式パッケージ内に組み込むことができる。

#### 【0072】

図15に示される代替の実施形態では、ワイヤボンド32は最初に、ワイヤループ86の部分32'として、対をなして形成される。この実施形態では、ループ86は、上記で論じられたように、ワイヤボンドの形に作製される。ワイヤセグメントは、上方に引き上げられ、その後、曲げられ、基板13の第1の表面14の方向の少なくとも1つの構成要素を有する方向に、隣接する導電性素子28の上に実質的に重なる位置まで引き下げられる。その後、ワイヤは隣接する導電性素子28付近の位置まで実質的に下方に引き下げられ、その後、切断されるか、別の方法で切られる。その後、ワイヤは加熱され、堆積ボンディング等によって隣接する導電性素子28に接続され、ループ86を形成する。その後、ループ86を実質的に被覆するように、封止層42が形成される。その後、プロセスによる研削、エッティング等によって封止層42の一部分が除去される。このプロセスは、ループが切られ、2つの部分32'に分割されるようにループ86の一部分も除去し、それにより、封止層42上に形成された表面44上の場所に、封止層42によって被覆されない端面38を有するワイヤボンド32を形成する。その後、上記で論じられたように、アセンブリ10に後続の仕上げステップを適用することができる。

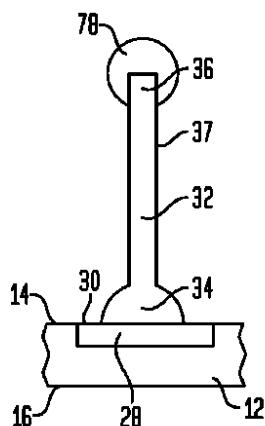

#### 【0073】

図16A～図16Cは、上記で論じられたように、ワイヤボンド32の端部36を包囲するキャビティ64を作製するための代替の実施形態におけるステップを示す。図16Aは、図1～図6に関して上記で論じられた一般的なタイプのワイヤボンド32を示す。ワイヤボンド32は、その端部36上に付着する犠牲材料78の塊状物を有する。犠牲材料塊78は、その形成中に材料の表面張力から生じる可能性がある実質的に球の形状をなすことができるか、又は当業者によって理解される他の所望の形状をなすことができる。犠牲材料塊78は、ワイヤボンド32の端部36をはんだペースト内に浸し、その端部をコーティングすることによって形成することができる。ウェッギング及び表面張力によって端部36に接着するはんだ塊の量を制御するために、浸す前にはんだペーストの粘性を調整することができる。したがって、これは、端部36に付着する塊状物78のサイズに影響を及ぼすことができる。代替的には、塊状物78は、ワイヤボンド32の端部36上に可溶性材料を堆積することによって形成することができる。他の可能な塊状物78は、端部上の個々のはんだボール若しくは他の塊状物とすることができますか、又は超小型電子構成要素の製造中に用いられ、後に除去することができる、銅又は金フラッシング等の他の材料を用いる他の手段によることができる。

#### 【0074】

図16Bにおいて、ワイヤボンド32のエッジ面37に沿った上方を含めて、アセンブリ10に加えられた誘電体層42が示される。また、誘電体層は、犠牲材料塊78の表面の一部分に沿って延在し、それにより、誘電体層はワイヤボンド32の端部36から離間して位置される。その後、犠牲材料塊78は、溶媒内での洗浄又はすぎ、溶解、化学エッティング又は他の技法等によって除去され、それにより、誘電体層42内に、除去する前の塊状物78の鋳型形状(negative shape)のキャビティ64を実質的に残し、ワイヤボンド32の端部36付近のエッジ面37の一部分を露出させる。

#### 【0075】

代替的には、犠牲材料塊78は、ワイヤボンドのエッジ面37に沿って延長することによって、ワイヤボンド32の実質的に全てをコーティングするように形成することができる。この構成が図17Aに示される。そのようなコーティングは、上記で論じられたように、アセンブリ10上での形成後にワイヤボンド32上に付着させることができるか、又はワイヤボンド32を作製するために用いられるワイヤにコーティングとして付着させることができる。これは、基本的には、コーティングされたワイヤ、又は、例えば、銅の内

10

20

30

40

50

側コアとはんだコーティングとを有する二重ワイヤの形をとることになる。図17Bは、犠牲塊78のエッジ面79に沿って延在し、それにより、実質的にその長さに沿ってワイヤボンド32から誘電体層42を離隔するように、ワイヤボンド32及び犠牲塊78上に被着された誘電体層42を示す。

【0076】

図17Cは、犠牲材料塊78の一部分を除去して、端部36の周囲にキャビティ64を形成し、エッジ面37の一部分を露出させることから生じる構造を示す。そのような実施形態において、犠牲材料塊78の大部分、又は少なくとも一部を誘電体層42とワイヤボンド32との間の場所に残すことができる。図17Cは、ワイヤボンド32を別の超小型電子構造10Aのコンタクトパッド40Aに電気的及び機械的に接続するはんだ塊52を更に示す。

10

【0077】

ワイヤセグメントを形成し、ワイヤセグメントを導電性素子にボンディングして、特に上記で論じたボールボンドタイプのワイヤボンドを形成した後、ワイヤボンド（例えば、図1の32）は、その後、キャピラリ（図32の804等）内のワイヤの残りの部分から分離される。これは、ワイヤボンド32のベース34から遠隔の任意の場所で行うことができ、好ましくは、ワイヤボンド32の所望の高さを規定するのに少なくとも十分な距離だけベース34から遠隔の場所で行われる。こうした分離は、面806とワイヤボンド32のベース34との間で、キャピラリ804内に配設されるか又はキャピラリ804の外部に配設される機構によって実施することができる。一方法では、ワイヤセグメント800は、所望の分離点でワイヤ800を効果的に溶け落とさせることによって分離することができ、それは、ワイヤ800にスパーク又は火炎を印加することによって行うことができる。ワイヤボンド高さのより高い精度を達成するために、ワイヤセグメント800を切断する異なる形態を実装することができる。本明細書で述べるように、切断は、所望の場所でワイヤを弱化させることができる部分的切断又は残りのワイヤセグメント800からワイヤボンド32を全体的に分離させるための、ワイヤを貫通する完全な切断を記述するために使用することができる。

20

【0078】

図32に示す一例では、切断ブレード805は、キャピラリ804内等の、ボンドヘッドアセンブリに一体化することができる。図示するように、切断ブレード805がそこを通って延在することができる開口807が、キャピラリ804の側壁820内に含まれることができる。切断ブレード805は、キャピラリ804の内部に入る／から出るよう移動可能であることができるため、切断ブレード805が、交互に、ワイヤ800がキャピラリ804を自由に通過することを可能にするか又はワイヤ800に係合することができる。したがって、切断ブレード805がキャピラリ内部の外側の位置にある状態で、ワイヤ800を引き出し、ワイヤボンド32を形成して、導電性素子28にボンディングすることができる。ボンド形成後、ワイヤセグメント800を、ボンドヘッドアセンブリ内に一体化されたクランプ803を使用して固定し、ワイヤの位置を固定することができる。切断ブレード803を、その後、ワイヤセグメントに向けて移動して、ワイヤを完全に切断するか、又は部分的に切断する、すなわちワイヤを弱化させることができる。完全な切断により、ワイヤボンド32の端面38を形成することができる。この時点で、キャピラリ804はワイヤボンド32から離れて、例えば、別のワイヤボンドを形成することができる。同様に、ワイヤセグメント800が切断ブレード805によって弱化されている場合、ワイヤクランプ803によって依然として保持されているワイヤとともにボンドヘッドユニットを移動させることにより、部分的な切断によって弱化されたエリアにおいてワイヤ800を破断することによって分離を引き起こすことができる。

30

【0079】

切断ブレード805の移動は、空気圧又はオフセットカムを使用するサーボモータによって作動することができる。他の例では、切断ブレード805の移動は、バネ又はダイヤフラムによって作動することができる。切断ブレード805作動のためのトリガー用信号

40

50

は、ボールボンドの形成からカウントダウンする時間遅延に基づくことができるか、又は、ワイヤボンドベース34の上の所定の高さまでのキャピラリ804の移動によって作動することができる。こうした信号は、任意の後続のボンド形成の前に切断ブレード805の位置をリセットすることができるようボンディング機械を動作させる他のソフトウェアにリンクすることができる。切断機構は、その両側からワイヤを切断するためにブレード805の反対に位置する第2のブレード(図示せず)も含むことができる。

#### 【0080】

別の例では、レーザ809は、ボンドヘッドユニットとともに組み立て、ワイヤセグメントを切断するように位置決めすることができる。図33に示すように、レーザヘッド809は、キャピラリ804又はキャピラリ804を含むボンドヘッドユニット上の別の地点に実装すること等によってキャピラリ804の外部に位置決めすることができる。図32の切断ブレード805に関して上記で論じたような所望の時間にレーザを作動して、ワイヤ800を切断し、ベース34の上の所望の高さにワイヤボンド32の端面38を形成することができる。他の実装態様では、レーザ809は、キャピラリ804自体を通して又はその中に切断ビームを向けるように位置決めすることができ、また、ボンドヘッドユニットの内部にあることができる。或る例では、二酸化炭素レーザを使用することができるか、又は代替として、Nd:YAGレーザ又はCu蒸気レーザを使用することができる。

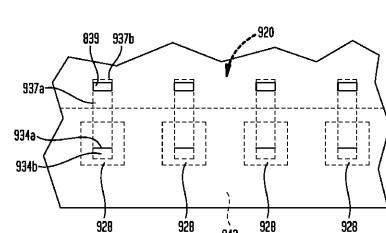

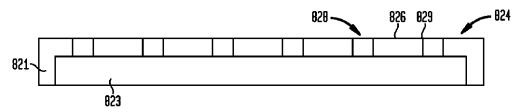

#### 【0081】

別の実施形態では、図34A～図34Cに示すステンシルユニット824を用いて、ワイヤボンド32を残りのワイヤセグメント800から分離することができる。図34Aに示すように、ステンシル824は、ワイヤボンド32の所望の高さで又はその近くで上側表面826を画定する本体を有する構造であることができる。ステンシル824は、導電性素子28、又は導電性素子28間の基板12の任意の部分に接触するように構成することができる。ステンシルは、導電性素子28等を被覆する等、ワイヤボンド32用の所望の場所に対応することができる複数の穴828を含む。穴828は、ボンドヘッドユニットのキャピラリ804を穴828に受容するサイズにすることによって、キャピラリは、導電性素子28にワイヤ800をボンディングするための、導電性素子28に対する位置まで穴の中に延在して、例えばボールボンディング等によってベース34を形成することができる。キャピラリ804は、その後、ワイヤセグメントを所望の長さまで引き出しながら、穴828から外に垂直に移動させることができる。穴828から取り除かれると、ワイヤセグメントは、クランプ803等によってボンドヘッドユニット内に固定することができ、キャピラリ804は、横方向に(ステンシル824の表面826に平行に等)移動して、穴828の表面及びステンシル824の外側表面826の交差によって画定されるステンシル824の縁部829に接触するようワイヤセグメント800を移動させることができる。こうした移動は、キャピラリ804内に依然として保持されるワイヤセグメント800の残りの部分からワイヤボンド32の分離を引き起こすことができる。このプロセスは、所望の場所に所望の数のワイヤボンド32を形成するために繰り返すことができる。或る実装態様では、キャピラリは、ワイヤ分離の前に垂直に移動することができ、それにより、残りのワイヤセグメントは、後続のボールボンドを形成するのに十分な距離802だけキャピラリ804の面806を超えて突出する。図34Bは、穴828が、表面826の第1の直径から、表面826から離れたより大きな直径まで増加する直径を有するように、穴828がテーパを付けられるステンシル824の変形形態を示す。別の変形形態では、図34Cに示すように、ステンシルは、基板12から所望の距離に表面826を離間させるのに十分な厚さを有する外側フレーム821を有するものとして形成することができる。フレーム821は、基板12に隣接して位置決めされるように構成されるキャビティ823を少なくとも部分的に囲むことができ、ステンシル824の厚さは、表面826と開口エリア823との間に延在しており、穴828を含むステンシル824の部分が、基板12上に位置決めされると基板12から離間するようになっている。

#### 【0082】

10

20

30

40

50

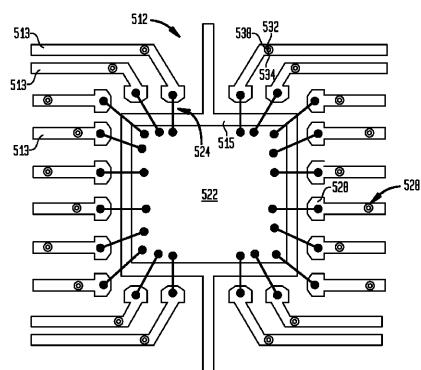

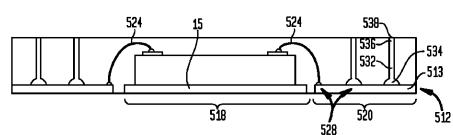

図20及び図21は、ワイヤボンド532がリードフレーム構造上に形成される超小型電子アセンブリ510の更なる実施形態を示す。リードフレーム構造の例は、米国特許第7,176,506号及び第6,765,287号に示され、記載されており、それらの開示は、引用することにより本明細書の一部をなすものとする。一般に、リードフレームは、銅等の導電性金属のシートから形成される構造であり、この構造は複数のリード線を含むセグメントになるようパターニングされ、パドル及びフレームを更に含むことができる。フレームを用いて、アセンブリの作製中に、リード線及び使用される場合パドルを固定する。一実施形態では、ダイ又はチップ等の超小型電子素子は、ワイヤボンドを使用して、パドルに上向きに接合し、リード線に電気接続することができる。代替的に、超小型電子素子は、超小型電子素子の下に延在することができるリード線に直接実装することができる。こうした実施形態では、超小型電子素子上のコンタクトは、はんだボール等によつてそれぞれのリード線に電気接続することができる。その後、リード線を用いて、超小型電子素子へノットから信号電位を搬送するために種々の他の導電性構造に対する電気接続部を形成することができる。構造を覆つて封止層を形成することを含むことができる、その構造の組立てが終了すると、フレームの一時的な要素をリードフレームのリード線及びパドルから除去して、個々のリード線を形成することができる。本開示において、個々のリード線513及びパドル515は、基板512であつて、基板512と一体に形成される部分内に導電性素子528を含む、基板512を全体として形成するものの区分化された部分であると考えられる。さらに、この実施形態では、パドル515は、基板512の第1の領域518内にあると考えられ、リード線513は、第2の領域520内にあると考えられる。図21の平面図でも示すワイヤボンド524は、パドル515上で担持される超小型電子素子22をリード線515の導電性素子528に接続する。ワイヤボンド532は、ワイヤボンド532のベース534において、リード線515上の更なる導電性素子528に更に接合することができる。封止層542は、アセンブリ510上に形成され、ワイヤボンド532の端部538を表面544内の場所で被覆されないままにする。ワイヤボンド532は、本明細書の他の実施形態に関して述べた構造に対応する構造内で、封止層542によって被覆されない更なる又は代替の部分を有することができる。

#### 【0083】

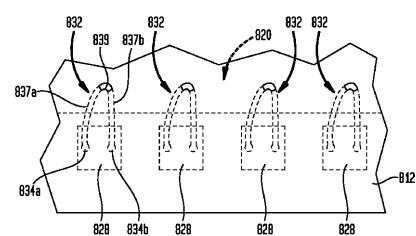

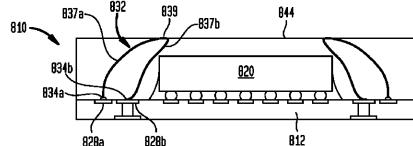

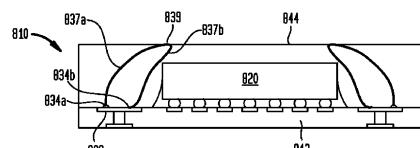

図24～図26は、閉ループワイヤボンド832を有する超小型電子パッケージ810の更に別の実施形態を示す。この実施形態のワイヤボンド832は、図24に示されるように、隣接する導電性素子828a及び828bに接合することができる2つのベース834a及び834bを含む。代替的には、ベース834a、834bはいずれも、図25及び図26に示されるように、共通の導電性素子828上に接合することができる。そのような実施形態では、ワイヤボンド832は、エッジ面837がベースから基板812の上方の封止層842の表面844における頂点839までそれぞれの部分837a及び837bにおいて上方に延在するように、ループ内で2つのベース834a、834b間に延在するエッジ面837を画定する。封止層842は、エッジ面部分837a、837bの少なくとも部分に沿つて延在し、互いに、かつパッケージ810内の他のワイヤボンド832から、それぞれの部分を分離する。頂点839において、エッジ面837の少なくとも一部が封止層842によって被覆されず、それにより、ワイヤボンド832は別の構成要素との電気的相互接続のために利用可能であり、別の構成要素は、別の超小型電子構成要素、又は他の構成要素、例えば、キャパシタ又はインダクタ等の個別要素とすることができます。図24～図26に示されるように、ワイヤボンド832は、頂点839が基板812の表面にわたつて少なくとも一方の横方向において導電性素子828からオフセットされるように形成される。一例では、頂点839は、超小型電子素子820の主面の上に重なることができるか、又はそうでなければ、超小型電子素子820が位置合わせされる基板812の第1の領域の上に重なることができる。頂点839が他の実施形態において論じられたワイヤボンドの端面の場所のいずれかに位置決めされる構成を含む、ワイヤボンド832のための他の構成も可能である。さらに、頂点839は、図8Aに示されるように、穴内で被覆されないことができる。さらには、頂点839は延長することができる

10

20

30

40

50

でき、図10A～図10D内のエッジ面に関して図示されたように、その長さにわたって延在する表面844において被覆されないようにすることができる。1つではなく、2つのベース834a、834b間に延在するワイヤボンド832によって支持される頂点839を包囲する被覆されないエッジ面837の形として接続機構を設けることによって、主面844によって規定される方向における接続機構のより正確な配置を達成することができる。

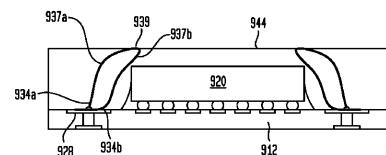

#### 【0084】

図27及び図28は図24～図26の実施形態の変形形態を示しており、ワイヤボンド834の代わりにボンドリボン934が用いられる。ボンドリボンは、ワイヤボンドを形成するために上記で論じられた材料のいずれか等の導電性材料からなる、全体的に平坦な材料片とすることができます。ボンドリボン構造は、断面を概ね円形にすることができます。ワイヤボンドとは対照的に、太くではなく、幅広くすることができます。図27に示されるように、ボンドリボン934はそれぞれ、導電性素子928の一部分に沿って延在して結合することができる第1のベース934aを含む。リボンボンド932の第2のベース934bは第1のベース934aの一部分に接合することができる。エッジ面937が、頂点939への2つの対応する部分937a及び937bにおいて、ベース934aと934bとの間に延在する。頂点939のエリア内のエッジ面の部分は、その主面944の一部分に沿って封止材942によって被覆されない。本明細書において開示された他の実施形態において用いられたワイヤボンドに関して記述されたような、更なる変形形態も可能である。

10

20

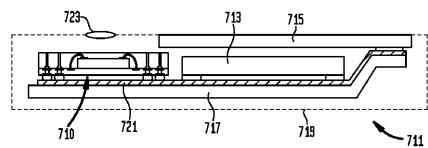

#### 【0085】

上記で論じられた構造は、多様な電子システムを構成する際に利用することができる。例えば、本発明の更なる実施形態によるシステム711は、他の電子構成要素713及び715とともに、上記のような超小型電子アセンブリ710を含む。図示される例では、構成要素713は半導体チップであるのに対して、構成要素715は表示画面であるが、任意の他の構成要素を用いることもできる。当然、明確に例示するため、図23には2つの更なる構成要素しか示されないが、そのシステムは任意の数のそのような構成要素を含むことができる。上記のような超小型電子アセンブリ710は、例えば、図1に関連して上記で論じられたような超小型電子アセンブリ、又は図6を参照しながら論じられたような複数の超小型電子アセンブリを組み込む構造とすることができます。アセンブリ710は、図2～図22において記述された実施形態のうちのいずれか1つを更に含むことができる。更なる変形形態では、複数の変形を与えることができ、任意の数のそのような構造を用いることができる。

30

#### 【0086】

超小型電子アセンブリ710並びに構成要素713及び715は、破線において概略的に表される、共通のハウジング719内に実装され、所望の回路を形成するために必要に応じて互いに電気的に相互接続される。図示される例示的なシステムでは、そのシステムは、フレキシブルプリント回路基板等の回路パネル717を含み、回路パネルは、構成要素を互いに相互接続する多数の導体721を含み、そのうちの1つだけが図23に示される。しかしながら、これは例示にすぎず、電気的接続を作製するのに適した任意の構造を用いることができる。

40

#### 【0087】

ハウジング719は、例えば、携帯電話又は携帯情報端末において使用可能なタイプのポータブルハウジングとして示されており、画面715はハウジングの表面に露出する。超小型電子アセンブリ710が撮像チップ等の感光性素子を含む場合、光をその構造まで送るために、レンズ723又は他の光学デバイスも設けることができる。ここでもまた、図23に示される簡略化されたシステムは例示にすぎない。デスクトップコンピュータ、ルータ等の一般的に固定構造と見なされるシステムを含む他のシステムも、上記で論じられた構造を用いて作製することができる。

#### 【0088】

50

本発明の上述した実施形態及び変形形態は、具体的に上述した以外の方法で組み合わせることができる。本発明の範囲及び趣旨内にある全ての変形形態を包含することが意図される。

**【0089】**

本発明は特定の実施形態を参照しながら本明細書において説明されてきたが、これらの実施形態は本発明の原理及び応用形態を例示するにすぎないことは理解されたい。それゆえ、添付の特許請求の範囲によって規定されるような本発明の趣旨及び範囲から逸脱することなく、例示的な実施形態に数多くの変更を加えることができること、及び他の構成を考案することができることは理解されたい。

**[実施形態例]**

10

**[実施形態1]**

超小型電子パッケージを作製する方法であって、

a) 所定の長さを有する金属ワイヤセグメントをボンディングツールのキャピラリから送り出すステップと、

b) 前記ボンディングツールを使用するステップであって、前記金属ワイヤの一部分を基板の第1の表面において露出する導電性素子に結合し、それにより、前記導電性素子上にワイヤボンドのベースを形成する、使用するステップと、

c) 前記ワイヤの一部分を前記ボンディングツール内に固定するステップと、

d) 前記固定された部分と前記ベースとの間の場所において前記金属ワイヤを切断するステップであって、前記ワイヤボンドの端面を少なくとも部分的に画定し、前記ベースと前記端面との間に前記ワイヤボンドのエッジ面が画定される、切断するステップと、

e) ステップ(a)～ステップ(d)を繰り返すステップであって、前記基板の複数の前記導電性素子への複数のワイヤボンドを形成する、繰り返すステップと、

e) その後、前記基板の前記表面の上に重なる誘電体封止層を形成するステップであって、前記封止層は、前記基板の前記表面及び前記ワイヤボンドの一部分を少なくとも部分的に被覆するように形成され、それにより、前記封止層によって被覆されない前記ワイヤボンドの端面又はエッジ面のうちの少なくとも一方の一部分によって、前記ワイヤボンドの封止されない部分が画定される、形成するステップと、

を含む、超小型電子パッケージを作製する方法。

**[実施形態2]**

20

前記金属ワイヤは部分的にのみ切込みを入れられ、前記ボンディングツールは、前記ワイヤの前記部分が固定されたまま、前記基板の前記表面から遠ざけられ、それにより、前記ワイヤが前記切込みの場所において断線し、前記端面は前記切込み及び前記断線によって形成される、実施形態1に記載の方法。

**[実施形態3]**

前記切込みは前記ワイヤボンドの前記エッジ面に対して実質的に垂直な方向において前記ワイヤセグメントを完全に貫通して作製され、前記ワイヤボンドの前記端面は前記切込みによって形成される、実施形態1に記載の方法。

**[実施形態4]**

30

少なくとも1つの超小型電子素子が前記基板の前記第1の表面の上に重なり、前記基板は第1の領域及び第2の領域を有し、前記超小型電子素子は前記第1の領域内に位置し、前記導電性素子は前記第2の領域内に位置し、前記少なくとも1つの超小型電子素子に電気的に接続され、前記誘電体封止層は、少なくとも前記基板の前記第2の領域において該基板の前記第1の表面の上に重なるように形成される、実施形態1に記載の方法。

**[実施形態5]**

40

前記パッケージは、前記ワイヤボンドのうちの第1のワイヤボンドが第1の信号電位を搬送するようになっており、前記ワイヤボンドのうちの第2のワイヤボンドが前記第1の信号電位とは異なる第2の信号電位を同時に搬送するようになっているように構成される、実施形態4に記載の方法。

**[実施形態6]**

50

前記金属ワイヤセグメントは前記ポンディングツール上に取り付けられるレーザを用いて切断される、実施形態 1 に記載の方法。

[実施形態 7]

前記キャピラリは、前記ワイヤボンドが送り出される際に通る該キャピラリの面を画定し、前記レーザは前記ポンディングツールの前記面と前記ワイヤボンドの前記ベースとの間に位置決めされる前記ワイヤセグメントの場所に切断ビームを誘導するように前記ポンディングツール上に取り付けられる、実施形態 6 に記載の方法。

[実施形態 8]

前記ポンディングツールはキャピラリを含み、該キャピラリは前記ワイヤボンドが送り出される際に通る該キャピラリの面を画定し、前記キャピラリは該キャピラリの側壁内に形成される壁を含み、前記レーザは、前記開口部を通して、前記キャピラリ内に位置決めされる前記ワイヤセグメントの場所に切断ビームを誘導するように、前記ポンディングツール上に取り付けられる、実施形態 6 に記載の方法。

10

[実施形態 9]

前記レーザは C O 2 、 N d : Y A G 又は C u 蒸気レーザのうちの 1 つである、実施形態 6 に記載の方法。

[実施形態 10]

前記金属ワイヤは、前記キャピラリ内に延在する切断エッジを用いて切断される、実施形態 1 に記載の方法。

20

[実施形態 11]

前記切断エッジは、前記ワイヤセグメントの反対に位置する前記キャピラリの壁に向かう方向に延在する、実施形態 10 に記載の方法。

[実施形態 12]

前記金属ワイヤは、前記切断エッジを第 1 の切断エッジとして、該第 1 の切断エッジの反対に位置するように前記キャピラリ内に延在する第 2 の切断エッジと組み合わせて前記切断エッジを用いて切断される、実施形態 10 に記載の方法。

[実施形態 13]

前記キャピラリは、前記ワイヤセグメントが送り出される際に通る該キャピラリの面を画定し、前記金属ワイヤは、反対に位置する第 1 の切断エッジ及び第 2 の切断エッジを有する切断器具を用いて切断され、前記切断器具は、前記ポンディングツールの前記面と前記ワイヤボンドの前記ベースとの間に位置決めされる場所において前記ワイヤセグメントを切断するように前記ポンディングツール上に取り付けられる、実施形態 1 に記載の方法

30

。

[実施形態 14]

前記基板の上にステンシルを位置決めするステップを更に含み、前記ステンシルは前記導電性素子の少なくとも一部の上に重なり、該少なくとも一部を露出させる複数の開口部を有し、該開口部は前記基板の上方の第 1 の高さに位置決めされるそれぞれのエッジを画定し、前記ワイヤセグメントは、前記ステンシル開口部の前記エッジに対する前記ワイヤの横方向への移動によって切断される、実施形態 1 に記載の方法。

40

[実施形態 15]

超小型電子パッケージを作製する方法であって、

a ) 第 1 の表面と、該第 1 の表面から離れた第 2 の表面とを有する基板と、前記基板の前記第 1 の表面に実装される超小型電子素子と、前記第 1 の表面において露出する複数の導電性素子とを含む処理中ユニットの上にステンシルを位置決めするステップであって、前記導電性素子のうちの少なくとも幾つかは前記超小型電子素子に電気的に接続され、前記ステンシルは、前記導電性素子の少なくとも一部の上に重なり、該少なくとも一部を露出させる複数の開口部を有し、該開口部は前記基板の上方の第 1 の高さに位置決めされるそれぞれのエッジを画定する、位置決めするステップと、

b ) 所定の長さを有する金属ワイヤセグメントをポンディングツールのキャピラリから送り出すことと、前記ワイヤセグメントの一部分を前記導電性素子のうちの 1 つに接合し

50

、ワイヤボンドのベースを形成することと、前記ステンシル開口部の前記エッジに対して前記ワイヤを横方向に移動することにより、前記ワイヤセグメントを剪断して、前記ワイヤボンドを前記ワイヤセグメントの残りの部分から分離し、前記ワイヤボンド上の端面を画定することとを含むプロセスによって、前記ワイヤボンドを形成するステップであって、前記ワイヤボンドは前記ベースと前記端面との間に延在するエッジ面を画定する、形成するステップと、

c )ステップ( b )を繰り返すステップであって、複数の前記導電性素子上に複数のワイヤボンドを形成する、繰り返すステップと、

を含む、超小型電子パッケージを作製する方法。

[実施形態 16 ]

10

前記処理中ユニット上に誘電体封止層を形成するステップを更に含み、前記封止層は、前記第1の表面と、前記ワイヤボンドの一部分とを少なくとも部分的に被覆するよう形成され、それにより、前記封止層によって被覆されない前記ワイヤボンドの前記端面又は前記エッジ面のうちの少なくとも一方の一部分によって、前記ワイヤボンドの封止されない部分が画定される、実施形態 15 に記載の方法。

[実施形態 17 ]

前記キャピラリの面を越えて延在する前記ワイヤセグメントの残りの部分は、後続のワイヤボンドの少なくともベースを形成するのに十分な長さからなる、実施形態 15 に記載の方法。

[実施形態 18 ]

20

前記ステンシルは、前記穴のうちの1つの穴の軸の方向において厚みを画定し、前記穴のうちの少なくとも幾つかは前記ステンシルの厚みを通して一貫した直径からなる、実施形態 15 に記載の方法。

[実施形態 19 ]

前記ステンシルは前記穴のうちの1つの穴の軸の方向において厚みを画定し、前記穴のうちの少なくとも幾つかは、前記エッジ付近の小さな直径から、前記エッジと前記基板との間の場所における大きな直径までテーパを付けられる、実施形態 15 に記載の方法。

[実施形態 20 ]

前記ステンシルは、前記基板の1つ又は複数のエッジに沿って延在する前記基板の厚みの方向において第1の厚みを有するエッジ部材であって、前記第1の厚みは前記第1の高さを画定する、エッジ部材と、前記穴を含み、前記エッジ部材によって囲まれる中央部分であって、該中央部分は前記基板から離れて面する外面を有し、該外面は前記第1の高さに配置され、該中央部分は前記第1の厚みより薄い厚みを更に有する、中央部分とを含む、実施形態 15 に記載の方法。

30

[実施形態 21 ]

超小型電子パッケージを作製する方法であって、

a )金属ワイヤをボンディングツールのキャピラリを通して送り出すステップと、

b )前記ボンディングツールを使用するステップであって、前記金属ワイヤの一部分を基板の第1の表面において露出する導電性素子に結合し、それにより、前記導電性素子にワイヤボンドのベースを形成する、使用するステップと、

40

c )前記ワイヤの一部分を前記ボンディングツール内に固定するステップと、

d )前記キャピラリ内の前記金属ワイヤを前記固定された部分と前記ベースとの間の場所において切断するステップであって、前記ワイヤボンドの前記ベースから所定の距離において前記ワイヤボンドの端面を少なくとも部分的に画定する、切断するステップと、

を含む、超小型電子パッケージを作製する方法。

[実施形態 22 ]

e )ステップ( a )～( d )を繰り返すステップであって、前記基板の複数の導電性素子への複数のワイヤボンドを形成する、繰り返すステップと、

f )その後、前記基板の前記第1の表面の上に重なる誘電体封止層を形成するステップであって、前記封止層は、前記基板の前記第1の表面と、前記ワイヤボンドの一部分とを

50

少なくとも部分的に被覆するように形成され、それにより、前記封止層によって被覆されない前記端面及び前記ワイヤポッドの前記ベースと前記端面との間に延在するエッジ面のうちの少なくとも一方の一部分によって、前記ワイヤボンドの封止されない部分が画定される、形成するステップと、

を更に含む、実施形態 2 1 に記載の方法。

[実施形態 2 3 ]

前記金属ワイヤは部分的にのみ切込みを入れられ、前記ボンディングツールは、前記ワイヤの前記部分が固定されたまま、前記基板の前記第一の表面から遠ざけられ、それにより、前記ワイヤが前記切込みの場所において断線し、前記端面は前記切込み及び前記断線によって形成される、実施形態 2 1 に記載の方法。

10

[実施形態 2 4 ]

前記切込みは、前記ベースと前記端面との間に延在する前記ワイヤボンドのエッジ面に対して実質的に垂直な方向において前記金属ワイヤを完全に貫通して作製され、前記ワイヤボンドの前記端面は前記切込みによって形成される、実施形態 2 1 に記載の方法。

[実施形態 2 5 ]

少なくとも 1 つの超小型電子素子が前記基板の前記第 1 の表面の上に重なり、前記基板は第 1 の領域及び第 2 の領域を有し、前記超小型電子素子は前記第 1 の領域内に位置し、前記導電性素子は前記第 2 の領域内に位置し、前記少なくとも 1 つの超小型電子素子に電気的に接続され、前記誘電体封止層は、少なくとも前記基板の前記第 2 の領域において該基板の前記第 1 の表面の上に重なるように形成される、実施形態 2 2 に記載の方法。

20

[実施形態 2 6 ]

前記パッケージは、前記ワイヤボンドのうちの第 1 のワイヤボンドが第 1 の信号電位を搬送するようになっており、前記ワイヤボンドのうちの第 2 のワイヤボンドが前記第 1 の信号電位とは異なる第 2 の信号電位を同時に搬送するようになっているように構成される、実施形態 2 5 に記載の方法。

[実施形態 2 7 ]

前記金属ワイヤは前記ボンディングツール上に取り付けられるレーザを用いて切断される、実施形態 2 1 に記載の方法。

[実施形態 2 8 ]

前記金属ワイヤは、前記キャピラリ内に延在する切断エッジを用いて切断される、実施形態 2 1 に記載の方法。

30

[実施形態 2 9 ]

前記切断エッジは、前記キャピラリの壁に向かう方向に延在する、実施形態 2 8 に記載の方法。

[実施形態 3 0 ]

前記キャピラリは、前記ワイヤが送り出される際に通る該キャピラリの面を画定し、前記金属ワイヤは、反対に位置する第 1 の切断エッジ及び第 2 の切断エッジを有する切断器具を用いて切断され、前記切断器具は、前記キャピラリ内の前記ワイヤを切断するよう前に前記ボンディングツール上に取り付けられる、実施形態 2 1 に記載の方法。

[実施形態 3 1 ]

40

超小型電子パッケージを作製する方法であって、

a ) 処理中ユニットの基板に関連付けられる構造の表面を設けるステップであって、前記基板は、第 1 の表面と、該第 1 の表面から離れた第 2 の表面とを有し、複数の導電性素子が前記第 1 の表面において露出し、前記構造は、前記導電性素子の少なくとも一部の上に重なり、該少なくとも一部を露出させる複数の開口部を有する、設けるステップと、

b ) 金属ワイヤをボンディングツールのキャピラリを通して送り出すことと、前記ワイヤの一部を前記導電性素子のうちの 1 つに接合し、ワイヤボンドのベースを形成することと、前記ワイヤボンドの前記ベースに対して前記ボンディングツールを移動し、前記ワイヤボンドのための所定の長さの前記ワイヤを設けることと、前記構造の前記基板に対する前記ボンディングツールの移動を通して、前記ワイヤボンドを前記ワイヤの残りの部分

50

から分離し、前記ワイヤボンドの前記ベースから離れた前記ワイヤボンドの自由端を画定することとを含むプロセスによって、前記ワイヤボンドを形成するステップと、

を含む、超小型電子パッケージを作製する方法。

[実施形態 3 2]

前記構造は、取外し可能ステンシルである、実施形態 3 1 に記載の方法。

[実施形態 3 3]

前記構造は前記基板の前記第 1 の表面の上に位置決めされる、実施形態 3 1 に記載の方

法。

[実施形態 3 4]

前記構造の前記表面は前記開口部のうちの少なくとも 1 つにおいてエッジを含み、前記

ワイヤは、前記ワイヤボンドが前記ワイヤから分離されるまで、前記エッジに対して前記

ワイヤを移動することによって剪断される、実施形態 3 1 に記載の方法。

10

[実施形態 3 5]

前記基板の前記第 1 の表面に超小型電子素子が実装され、前記導電性素子の少なくとも

幾つかは前記超小型電子素子に電気的に接続される、実施形態 3 1 に記載の方法。

[実施形態 3 6]

c ) ステップ ( b ) を繰り返すステップであって、複数の前記導電性素子上に複数のワ

イヤボンドを形成する、繰り返すステップを更に含む、実施形態 3 1 に記載の方法。

[実施形態 3 7]

前記処理中ユニット上に誘電体封止層を形成するステップを更に含み、前記封止層は、

前記第 1 の表面と、前記ワイヤボンドの一部分とを少なくとも部分的に被覆するように形

成され、それにより、前記封止層によって被覆されない前記自由端又は前記ワイヤボンド

の前記ベースと前記端面との間に延在するエッジ面のうちの少なくとも一方の一部分によ

つて、前記ワイヤボンドの封止されない部分が画定される、実施形態 3 6 に記載の方法。

20

[実施形態 3 8]

前記キャビラリの面を越えて延在する前記ワイヤの残りの部分は、後続のワイヤボンド

の少なくともベースを形成するのに十分な長さからなる、実施形態 3 1 に記載の方法。

[実施形態 3 9]

前記構造は前記開口部のうちの 1 つの開口部の軸の方向において厚みを画定し、前記開

口部のうちの少なくとも幾つかは前記構造の前記厚みを通して一貫した直径からなる、実

施形態 3 1 に記載の方法。

30

[実施形態 4 0]

前記構造は前記開口部のうちの 1 つの開口部の軸の方向において厚みを画定し、前記開

口部のうちの少なくとも幾つかは、前記基板の上方の第 1 の高さに位置決めされる前記構

造の前記表面のエッジ付近の小さな直径から、前記エッジと前記基板との間の場所にお

ける大きな直径までテーパを付けられる、実施形態 3 1 に記載の方法。

[実施形態 4 1]

前記構造は、前記基板の 1 つ又は複数のエッジに沿って延在する前記基板の厚みの方向

において第 1 の厚みを有するエッジ部材であって、前記第 1 の厚みは、前記構造の前記表

面のエッジが前記基板の上方に位置決めされる第 1 の高さを画定する、エッジ部材と、前

記開口部を含み、前記エッジ部材によって囲まれる中央部分とであって、該中央部分は前

記基板から離れて面する外面を有し、該外面は前記第 1 の高さに配置され、該中央部分は

前記第 1 の厚みより薄い厚みを更に有する、中央部分とを含む、実施形態 3 1 に記載の方

法。

40

【 図 1 】

【 図 2 】

【 図 3 】

【 図 7 】

【図 8 A】

【図4】

【 図 5 】

〔 6 〕

【図 8 B】

【図 8 C】

【図 8 D】

【図 8 E】

【図 9】

【図 10 A】

FIG. 10A

【図 10 B】

FIG. 10B

【図 10 C】

FIG. 10C

【図 10 D】

FIG. 10D

【図 11】

FIG. 11

【図 12】

FIG. 12

【図13】

【図14】

四 五

【図16B】

【図16A】

FIG. 16A

【図16C】

FIG. 16C

【図 17A】

FIG. 17A

【図 17B】

FIG. 17B

【図 17C】

FIG. 17C

【図 18】

FIG. 18

【図 19】

FIG. 19

【図20】

FIG. 20

【図21】

FIG. 21

【図22】

FIG. 22

【図26】

FIG. 26

【図27】

FIG. 27

【図28】

FIG. 28

【図23】

FIG. 23

【図24】

FIG. 24

【図25】

FIG. 25

【図29】

FIG. 29

【図30】

FIG. 30

【図31A】

FIG. 31A

【図31B】

【図31C】

【図32A】

【図32B】

【図33】

【図 3 4 A】

FIG. 34A

【図 3 4 C】

FIG. 34C

【図 3 4 B】

FIG. 34B

---

フロントページの続き

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100166268

弁理士 田中 祐

(74)代理人 100170379

弁理士 徳本 浩一

(74)代理人 100161001

弁理士 渡辺 篤司

(74)代理人 100179154

弁理士 児玉 真衣

(74)代理人 100180231

弁理士 水島 亜希子

(74)代理人 100184424

弁理士 増屋 徹

(72)発明者 コー, レイナルド

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5

(72)発明者 マーカリミ, ローラ

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5

審査官 豊島 洋介

(56)参考文献 米国特許出願公開第 2009 / 0085205 (U.S., A1)

特開 2010 - 192928 (JP, A)

特開平 04 - 346436 (JP, A)

特開 2007 - 234845 (JP, A)

特開平 11 - 260856 (JP, A)

特開平 10 - 135220 (JP, A)

特開平 10 - 135221 (JP, A)

特開 2008 - 166439 (JP, A)

特開 2008 - 171938 (JP, A)

特開平 10 - 065054 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 447 - 21 / 449

21 / 60 - 21 / 607

23 / 12 - 23 / 15

25 / 00 - 25 / 07

25 / 10 - 25 / 11

25 / 16 - 25 / 18