SCHWEIZERISCHE EidGENOSSENSCHAFT

BUNDESAMT FÜR GEISTIGES EIGENTUM

51 Int. Cl. 3: H 03 K 13/02

G 06 F 3/04

**Erfindungspatent für die Schweiz und Liechtenstein**

Schweizerisch-liechtensteinischer Patentschutzvertrag vom 22. Dezember 1978

**(12) PATENTSCHRIFT A5**

⑪

**626 480**

②1 Gesuchsnummer: 11933/77

③ Inhaber:

Gulf & Western Industries, Inc., New York/NY

(US)

②2 Anmeldungsdatum: 29.09.1977

②3 Erfinder:

Jess F. Fauchier, Bettendorf/IA (US)

William Seipp, Bettendorf/IA (US)

Stephen Whiteside, Davenport/IA (US)

②4 Patent erteilt: 13.11.1981

④5 Patentschrift

veröffentlicht: 13.11.1981

⑦4 Vertreter:

Bovard & Cie., Bern

**56 Vorrichtung zur Abgabe von Analogsignalen entsprechenden Digitaldaten über Datenleitungen einer programmierbaren Steuereinrichtung.**

57 Eine programmierbare Steuereinrichtung (A) liefert über Datenleitungen ( $D_0 - D_7$ ) von Analogsignalen abhängige Digitaldaten. Die Steuereinrichtung umfasst eine durch einen Mikroprozessor gebildete Zentraleinheit (10) mit Adressleitungen ( $A_0 - A_{15}$ ), den Datenleitungen und Steuerleitungen zur Abgabe eines Schreibsignals. Beim Auftreten des Schreibsignals werden die auf den Datenleitungen erscheinenden Digitaldaten zu Datenaufnahmeeinrichtungen geleitet. Die Zentraleinheit ist mit einem Analog-Digital-Umsetzmodul (100) verbunden. Dieses Modul setzt ein ihm zugeführtes Analogsignal in ein Digitalsignal für die Datenleitungen um, wenn es ein Umsetzsignal (ADC) empfängt. Das genannte Modul ist mit einer Anzahl von Analog-Signal-Eingabemodulen (120, 122, 124) verbunden, denen von der Zentraleinheit (10) Adressen abgegeben werden, um die in die Digitaldaten umzusetzenden Analogsignale an das Umsetzmodul (100) weiterzuleiten. Mit der oben angegebenen Vorrichtung lassen sich Analogsignale auf besonders einfache und sichere Weise in Digitaldaten umsetzen.

## PATENTANSPRÜCHE

1. Vorrichtung zur Abgabe von Analogsignalen entsprechenden Digitaldaten über Datenleitungen einer programmierbaren Steuereinrichtung, die eine Zentraleinheit mit Adressleitungen, mit bidirektional betriebenen Datenleitungen ( $D_0-D_7$ ) und mit Steuerleitungen zur Abgabe eines Schreibsignals umfasst, auf dessen Auftreten hin auf den Datenleitungen auftretende Digitaldaten zu ausgewählten adressierten Datenaufnahmeeinrichtungen hinleitbar sind, dadurch gekennzeichnet, dass mit der Zentraleinheit (10) ein gesondertes Analog-Digital-Umsetzmodul (100) verbunden ist, welches ein ihm eingangsseitig zugeführtes Analogsignal in ein Digitaldatensignal für die Abgabe an die Datenleitungen erst auf die Aufnahme eines gesonderten Umsetzsignals (ADC) umsetzt und welches erst auf die Beendigung einer Analog-Digital-Umsetzung hin ein die Umsetzung eines weiteren Analogsignals in ein Digitaldatensignal ermöglichtes Abschlussignal erzeugt, und dass mit dem Analog-Digital-Umsetzmodul (100) eine Anzahl von Analog-Signal-Eingabemodulen (120, 122, 124) verbunden ist, die für die Abgabe von in Digitaldaten umzusetzenden Analogsignalen an das Analog-Digital-Umsetzmodul (100) durch Abgabe entsprechender Adressen von der Zentraleinheit (10) her freigebar sind.

2. Vorrichtung nach Anspruch 1, dadurch gekennzeichnet, dass die Analog-Signal-Eingabemodulen (120, 122, 124) mit dem Analog-Digital-Umsetzmodul (100) über eine selektiv betätigebare Schalteranordnung (126, 128) verbunden sind.

3. Vorrichtung nach Anspruch 1 oder 2, dadurch gekennzeichnet, dass das Umsetzsignal (ADC) aus dem Auftreten der das jeweilige Analog-Signal-Eingabemodul (120, 122, 124) bezeichnenden Adresse abgeleitet ist.

4. Vorrichtung nach einem der Ansprüche 1 bis 3, dadurch gekennzeichnet, dass ein das jeweilige Analogsignal darstellendes Stromsignal vor einer Analog-Digital-Umsetzung in ein entsprechendes Spannungssignal umgesetzt wird.

5. Vorrichtung nach einem der Ansprüche 1 bis 4, dadurch gekennzeichnet, dass jedes Analog-Signal-Eingabemodul (120, 122, 124) einen adressierbaren Verriegelungsdecoder (210) enthält, der auf ein von der Zentraleinheit (10) abgegebenes Schreibsignal Verknüpfungssignale liefert, die Analog-Signal-Abgabeeinrichtungen (TC0, TC7) einstellen, nachdem dem Verriegelungsdecoder zuvor ein von dem betreffenden Schreibsignal abgeleitetes Löschsignal zugeführt ist.

Die Erfindung bezieht sich auf eine Vorrichtung gemäß dem Oberbegriff des Patentanspruches 1.

Es sind zwar bereits Analogsignale in entsprechende Digitaldaten umsetzende Wandlerschaltungen bekannt, die nach unterschiedlichen Umsetzprinzipien arbeiten, wie nach dem Zählerprinzip und dem Iterativprinzip. Bisher sind jedoch keinerlei Wandlerschaltungen bekannt geworden, die in Verbindung mit einer programmierbaren Steuereinrichtung betrieben werden, welche eine insbesondere durch einen Mikroprozessor gebildeten Zentraleinheit mit Adressleitungen, mit bidirektional betriebenen Datenleitungen und mit Steuerleitungen zur Abgabe eines Schreibsignals umfasst, auf dessen Auftreten hin auf den Datenleitungen auftretende Digitaldaten zu ausgewählten adressierten Datenaufnahmeeinrichtungen hinleitbar sind.

Ein programmierbares Steuereinrichtungssystem, bei dem die vorliegende Erfindung besonders geeignet ist, ist an anderer Stelle näher beschrieben (US-Patentanmeldung, Serial No. 701 858, vom 1.7.76).

Der Erfindung liegt nun die Aufgabe zugrunde, einen Weg zu zeigen, wie bei einer Vorrichtung der eingangs genannten

Art eine besonders einfache und dennoch sichere Umsetzung der von einer Anzahl von Analog-Signal-Eingabeeinrichtungen abgegebenen Analogsignale in Digitaldaten vorgenommen werden kann.

5 Gelöst wird die vorstehend aufgezeigte Aufgabe bei einer Vorrichtung der eingangs genannten Art erfahrungsgemäß durch die im kennzeichnenden Teil des Patentanspruches 1 angeführten Merkmale.

Die Erfindung bringt den Vorteil mit sich, dass auf relativ einfache Weise eine sichere Umsetzung der von einer Anzahl von Analog-Signal-Eingabeeinrichtungen abgegebenen Analogsignale in Digitaldaten vorgenommen wird. Dabei können die von den Analog-Signal-Eingabemodulen abgegebenen Analogsignale nach dem Multiplexprinzip in Digitaldaten umgesetzt werden, wozu vorzugsweise eine besonders leicht erhältliche programmierbare Steuereinrichtung, nämlich ein Mikroprozessor herangezogen werden kann.

Weitere zweckmässige Ausgestaltungen der vorliegenden Erfindung ergeben sich aus den abhängigen Ansprüchen.

20 Anhand von Zeichnungen wird die Erfindung nachstehend beispielsweise näher erläutert.

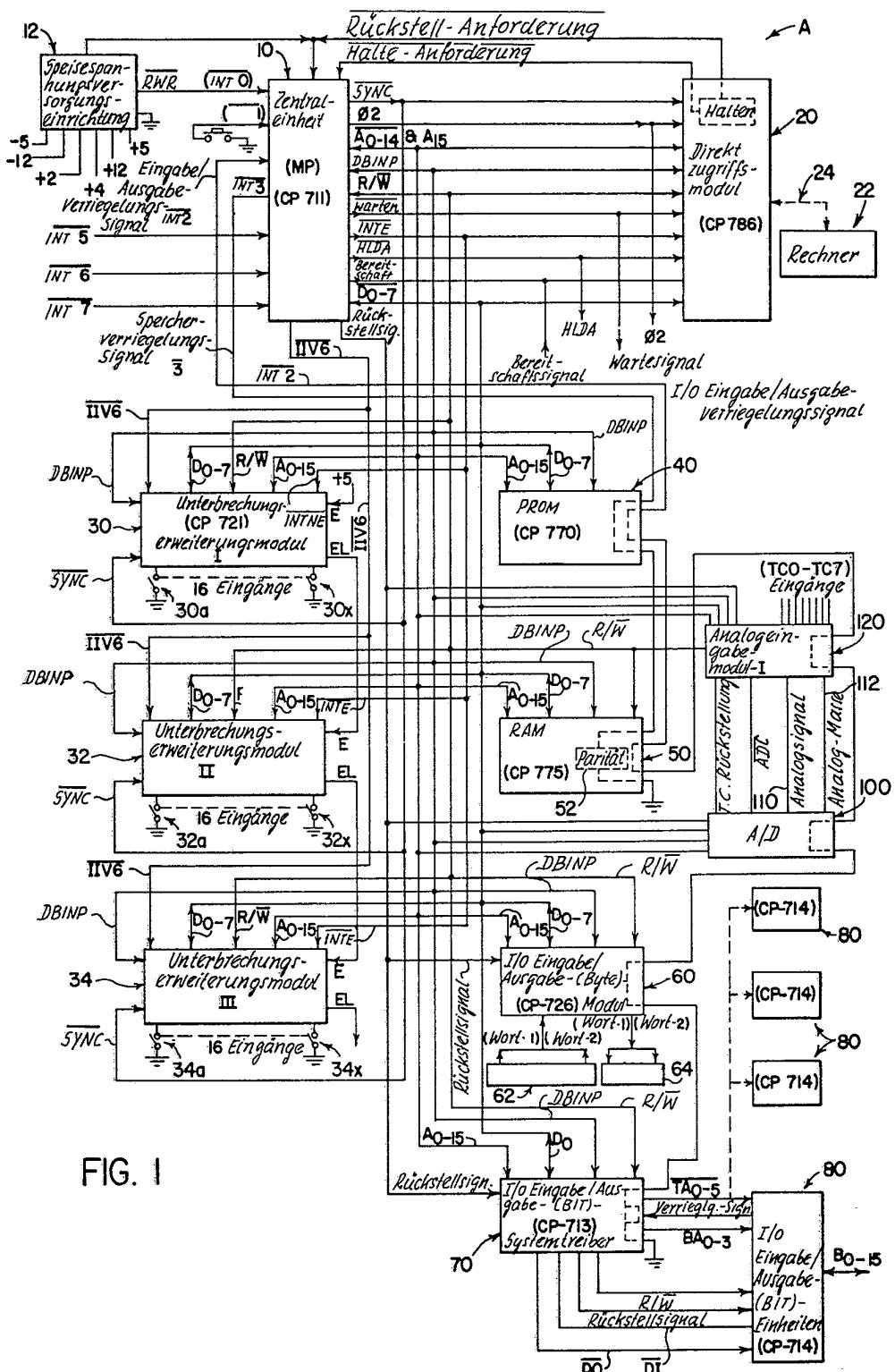

Fig. 1 zeigt schematisch in einem Schaltplan eine programmierbare Steuereinrichtung, die einen Mikroprozessor als Zentraleinheit verwendet, auf die die vorliegende Erfindung insbesondere anwendbar ist, wobei schematisch eine Art veranschaulicht ist, in der die bevorzugte Ausführungsform der vorliegenden Erfindung in die programmierbare Steuereinrichtung einbezogen ist.

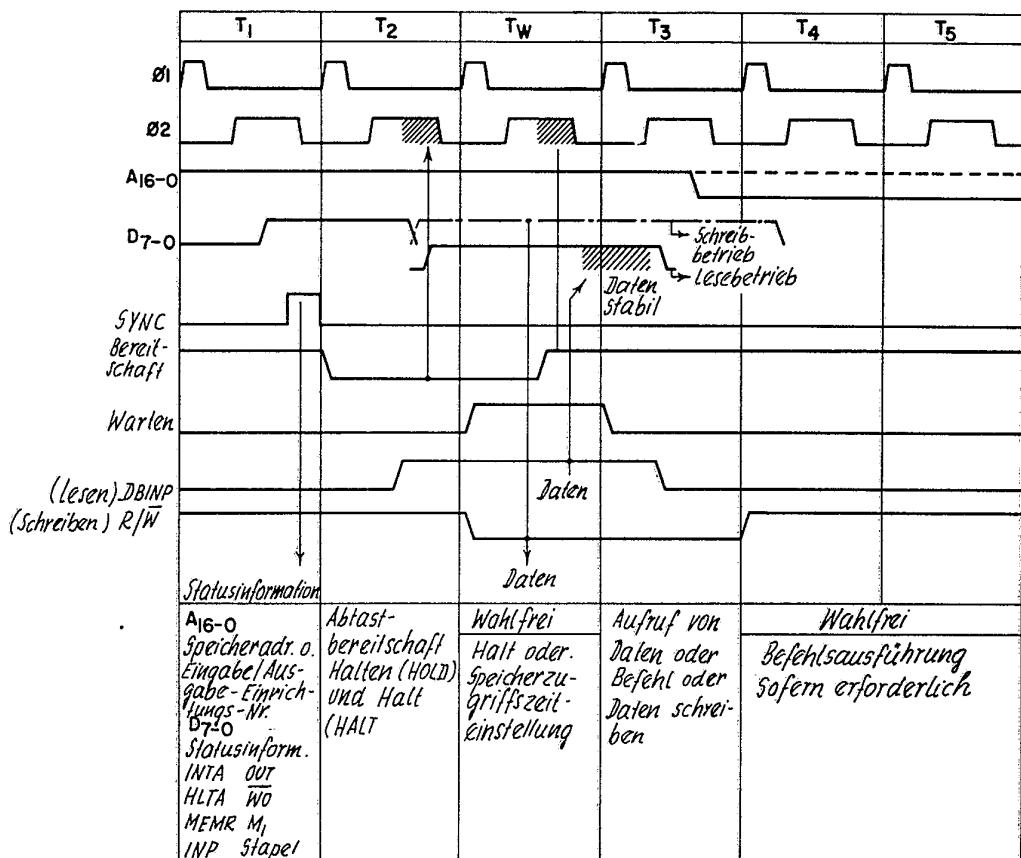

Fig. 2 zeigt ein Statusdiagramm für einen in dem in Fig. 1 dargestellten System benutzten Standard-Mikroprozessor des Typs 8080 der Firma Intel.

Fig. 3 veranschaulicht in einem Standard-Impulsdiagramm die auf verschiedenen Leitungen eines für die Verwendung in dem in Fig. 1 dargestellten System in Betracht gezogenen 35 Mikroprozessors des Typs Intel 8080 auftretenden Verknüpfungssignale.

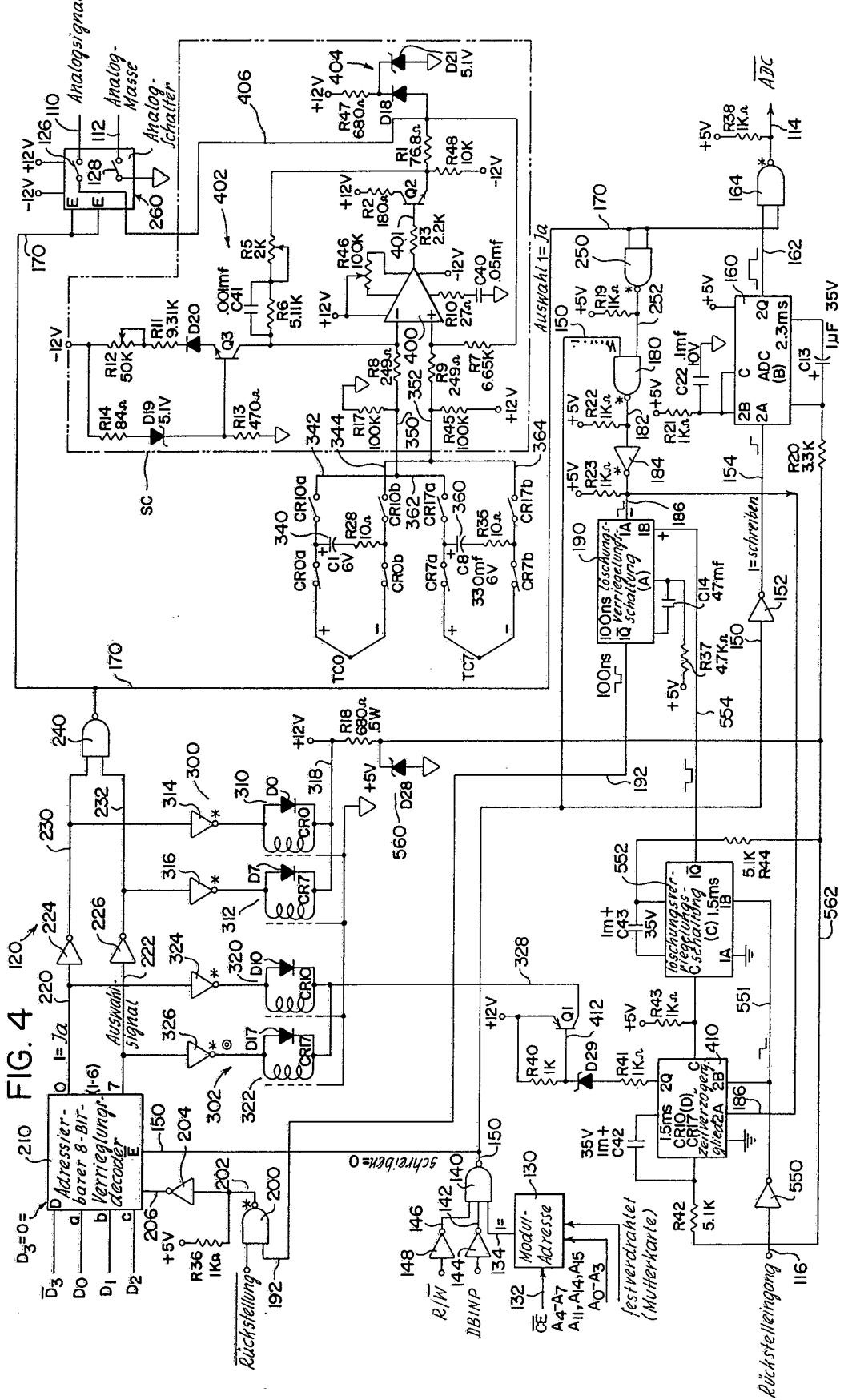

Fig. 4 veranschaulicht in einem Schaltungsdiagramm die bevorzugte Ausführungsform der vorliegenden Erfindung für die Erzeugung eines ausgewählten Analog-Ausgangssignals.

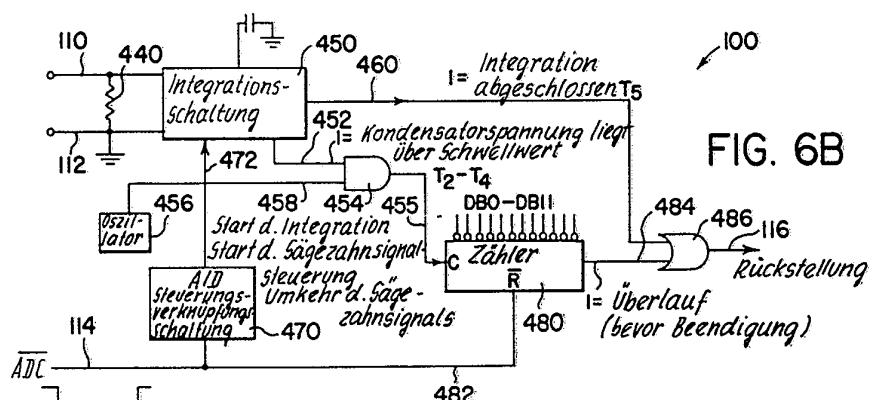

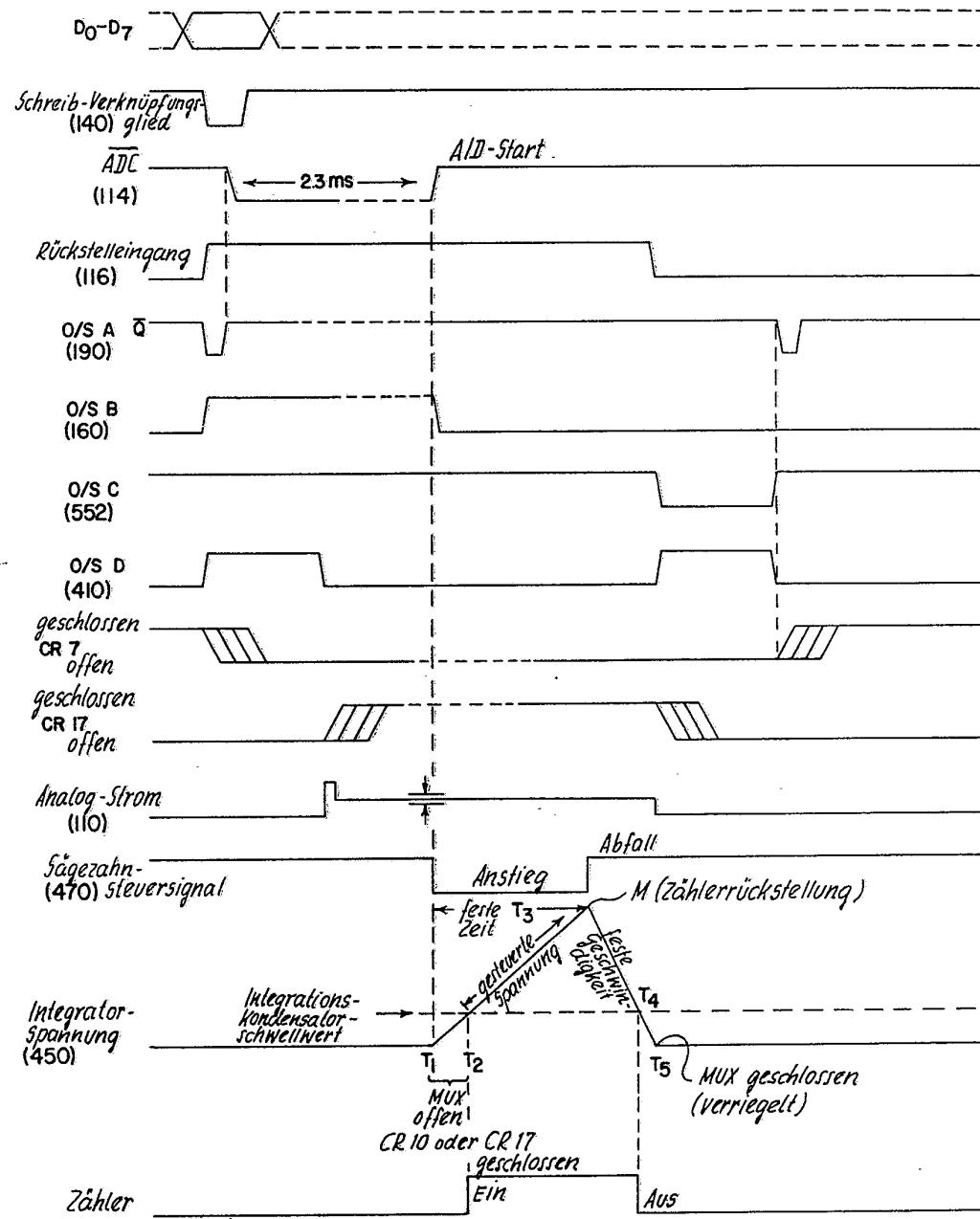

40 Fig. 5 veranschaulicht in einem Impuls- und Spannungsdiagramm bestimmte Impulse und Spannungen, wie sie bei der in Fig. 4 dargestellten bevorzugten Ausführungsform der Erfindung auftreten bzw. benutzt werden, sowie einige Spannungen, die in in Fig. 6A, 6B und 6C dargestellten Schaltungen auftreten.

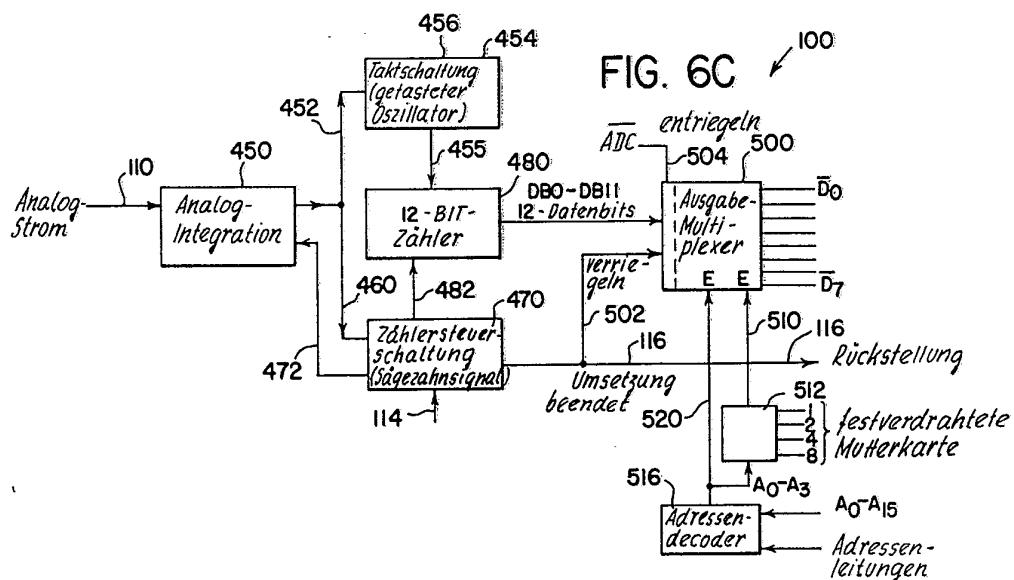

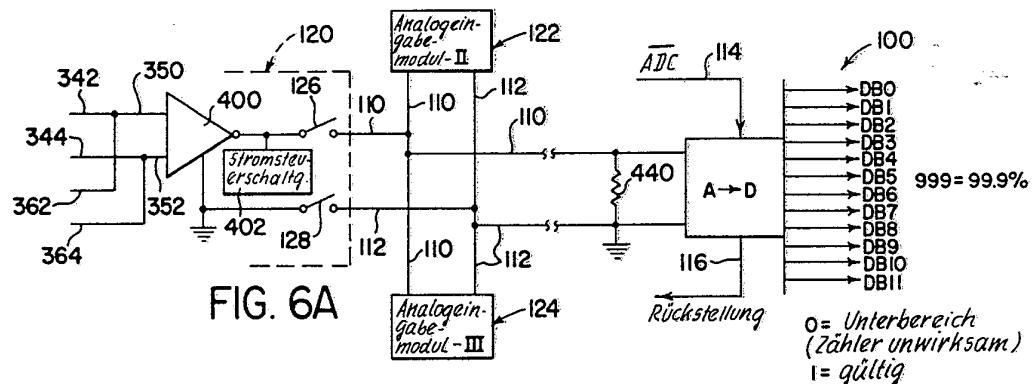

Fig. 6A, 6B und 6C veranschaulichen insgesamt eine Analog-Digital-Umsetzungsschaltung, die für die Verwendung bei der in Fig. 4 veranschaulichten bevorzugten Ausführungsform der Erfindung vorgesehen ist.

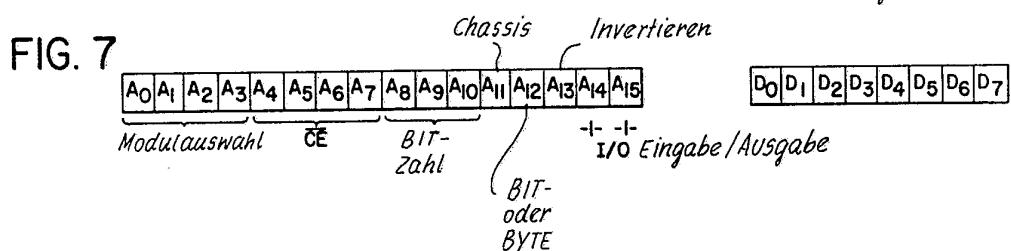

50 Fig. 7 zeigt schematisch eine Adresse des Typs, der beim Betrieb der in Fig. 4 dargestellten bevorzugten Ausführungsform benutzt ist.

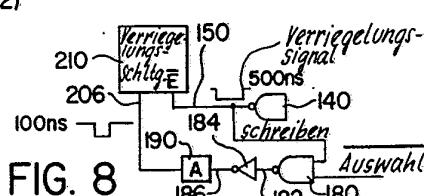

Fig. 8 veranschaulicht in einem vereinfachten Verknüpfungsdiagramm, wie bestimmte Impulse bei der in Fig. 4 dargestellten bevorzugten Ausführungsform der Erfindung die Eingabedaten-Verriegelung bei dieser Ausführungsform steuern.

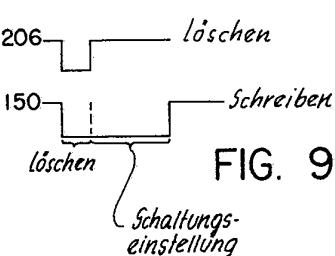

Fig. 9 veranschaulicht in einem Impulsdiagramm einen Lösch- und Freigabe- bzw. Schreibimpuls, der die in Fig. 8 dargestellte Verknüpfungsanordnung sowie eine entsprechende Verknüpfungsanordnung bei der in Fig. 4 dargestellten bevorzugten Ausführungsform der Erfindung steuert.

Im folgenden sei die generelle Steuereinrichtung näher erläutert. Die Fig. 1, 2 und 3 dienen zum Zwecke der Veranschaulichung einer programmierbaren Steuereinrichtung A,

65 welche zur Steuerung von Maschinen, Prozessen und anderen Systemen auf Eingabeinformationen von Eingängen her und auf existierende Zustände oder andere Parameter dient. Diese Steuereinrichtung benutzt den Modul und das Verfahren

gemäss der vorliegenden Erfindung. Die Eingangssignale, Zustände und Parameter werden der Steuereinrichtung A von verschiedenen externen Anschlüssen und Plätzen her zugeführt, die imstande sind, eine binäre Information als Einzelbit oder als Mehrzahl von Bits, das sind Bytes, bereitzustellen. Diese externen Anschlüsse können Schalter, Codierscheiben bzw. Decodierscheiben, Lampen, decodierte Analog-Daten und binär codierte Zustände sein. Gemäss der üblichen Praxis enthält die Steuereinrichtung Speicherplätze, und die Verarbeitung erfolgt entsprechend einem Programm, das als Vielzahl von Schritten oder Befehlen in einem derartigen Systemspeicher gespeichert ist. Zur Speicherung der Zwischeninformation oder Daten sind bestimmte Speicher mit wahlfreiem Zugriff vorgesehen. Diese Speicher können außerdem für eine gewisse Programmspeicherung benutzt werden, obwohl im allgemeinen ein Programm-Festwertspeicher zur Speicherung der Programminformation oder Programmschritte verwendet wird.

Wie in Fig. 1 dargestellt, ist die programmierbare Steuereinrichtung A ein digitales Verarbeitungssystem, welches eine Vielzahl von gesonderten und unterschiedlichen Einsteckmodulen enthält, die über eine Vielzahl von Steuerleitungen miteinander verbunden sind, welche im allgemeinen in einem Mutterplatten-Verbindungssystem enthalten sind. Eine Ausnahme hiervon bilden jedoch fern liegende Eingabe/Ausgabe-Modulen. Die Grundmodulen und die Steuerleitungen für diese Modulen sind schematisch in Fig. 1 veranschaulicht, in der ein Zentraleinheits-Modul (CPU) 10 oder Modul C711 einen Standard-Mikroprozessor als seine Zentraleinheit verwendet. Dieser Mikroprozessor ist ein bekannter, in MOS-Integrationstechnik ausgeführter Schaltungschip, der interne Register, Zähler, Zeiger und die zugehörige Verknüpfungsschaltung in an sich bekannter Weise enthält. Der Mikroprozessor weist eine Anzahl von Ausgabe-Adressenanschlüssen, eine Anzahl von bidirektionalen Datenanschlüssen, Einstelleinrichtungen, die den Chip in eine Vielzahl von bekannten Zuständen einzustellen gestatten, und Einrichtungen auf, die zu Beginn jedes gesonderten Befehls auf den Datenleitungen einen Statuscode bereitstellen. Obwohl eine Vielzahl von Mikroprozessoren mit diesen Standardeigenschaften verwendet werden könnte, ist für die durch die Fig. 1, 2 und 3 veranschaulichte Ausführungsform die Verwendung eines Mikroprozessors des Typs Intel 8080 vorgesehen, der sechzehn Adressenanschlüsse und acht bidirektionale Datenanschlüsse aufweist. Die Steuereinrichtung A schliesst die verschiedenen Konzepte bezüglich der Verwendung eines Mikroprozessors zur Verarbeitung einer Eingabe- und Ausgabeinformation zum Zwecke der Steuerung einer vorprogrammierten Reihe von Ereignissen einer Maschine, eines Prozesses usw. ein. Die Eingabeinformation ist bei der dargestellten Ausführungsform eine digitale Information, und zwar sowohl am Eingang als auch am Ausgang. Zur Ausführung von Umsetzvorgängen zwischen Analog-Signalen und Digital-Signalen könnten jedoch Umsetzer an der Schnittstelle zwischen der in Fig. 1 dargestellten Vorrichtung und den verschiedenen Analog-Eingängen und/oder Analog-Ausgängen verwendet werden. Der Zentraleinheitsmodul 10 steht mit den anderen Modulen in Verbindung, um die Eingabe- und Ausgabeinformation auf den Leitungen D<sub>0</sub> bis D<sub>7</sub> zu verarbeiten. Eine kurze Erläuterung der gesonderten Modulen dürfte ausreichen, um deren beabsichtigte Verwendung in Verbindung mit dem Zentraleinheitsmodul 10 sowie die Gesamtoperation der programmierbaren Steuereinrichtung A zu veranschaulichen.

Um die Steuereinrichtung A zunächst zu programmieren und auszutesten, ist ein Modul 20 mit direktem Zugriff vorgesehen, welches die Steuerung der an dem Zentraleinheitsmodul 10 angeschlossenen verschiedenen Steuerleitungen übernimmt. Damit ist es möglich, direkt die Speicher der Steuereinrichtung A durch eine externe Einrichtung zu programmieren,

wie sie schematisch durch einen Digital-Rechner 22 veranschaulicht ist. Bei dem dargestellten Ausführungsbeispiel ist der Rechner über schematisch dargestellte Leitungen 24 mit dem Direktzugriffs-Modul 20 verbunden. Wenn ein Halteanforderungssignal von dem Modul 20 an den Zentraleinheitsmodul 10 abgegeben wird, erhalten der Rechner 22 oder andere externe Steuereinrichtungen die Steuerung über die Adressenleitungen, die Eingabe-Kennzeichnungsleitung DBINP, die Lese/Schreib-Leitung und die Datenleitungen D<sub>0</sub> bis D<sub>7</sub> sowie über andere Leitungen, die in Fig. 1 durch Pfeile angedeutet sind. Wenn dies geschieht, ist der Zentraleinheitsmodul im wesentlichen von dem übrigen Teil der Steuereinrichtung abgetrennt und der Rechner 22 kann Speicher laden, d.h. die Steuereinrichtung programmieren, und tatsächlich die Steuerung betreiben, wie beim Austesten und bei der Fehlersuche. Der Direktzugriffs-Modul wird dazu herangezogen, sämtliche Speicher des Systems A mit der gewünschten Logik zu laden, Eingänge und Ausgänge in die gewünschten Zustände einzustellen, den Inhalt des Speichers oder der verschiedenen Eingabe- und Ausgabeschaltungen selektiv zu lesen, die Steuereinrichtung A zurückzustellen, Zwischen-Stop- und Ablaufoperationen für die Steuereinrichtungen A bereitzustellen und den Status sämtlicher Speicherpositionen und Register der Steuereinrichtung A, einschliesslich der Register des Mikroprozessors MP in dem Zentraleinheitsmodul 10, zu prüfen. Der Direktzugriffs-Modul wird für den Datenfluss zu und von dem System A unter der Steuerung einer externen Einheit benutzt, zu der ein Rechner, externe Bandleseeinrichtungen, ein Fernschreiber usw. gehören.

Um die Übertragung der Steuerung auf den Modul 20 zu bewirken, wird der Mikroprozessor MP des Moduls 10 in den Haltezustand (HOLD) gebracht, worauf weiter unten noch eingegangen werden wird. Die externe Programmierungseinrichtung, wie ein Rechner oder ein Bandleser, sendet über die Datenleitungen D<sub>0</sub> bis D<sub>7</sub> Daten zu und von der Steuereinrichtung A aus, und die Lage der Daten wird durch die Adressenleitungen A<sub>0</sub> bis A<sub>15</sub> gesteuert. Dadurch, dass der Mikroprozessor des Moduls 10 in den Haltezustand (HOLD) gebracht wird anstatt in den Halt-Zustand (HALT), können die Funktionen des Mikroprozessors durch ein programmiertes Signal oder eine programmierte Anforderung von dem Modul 20 übernommen werden. Außerdem kann die Steuerung durch den Mikroprozessor mittels eines einfachen Befehls wieder hergestellt werden, ohne dass eine komplizierte Programmierung erforderlich ist, wenn der Mikroprozessor in einen Halt-Zustand (HALT) übergeht. Es ist nicht notwendig, einen Auslöseimpuls bereitzustellen, um die Steuerung über das System A durch den Modul 10 wieder zu erhalten. Sobald der Haltezustand (HOLD) ausgelöst ist, übernimmt der Zentraleinheitsmodul 10 wieder die Steuerung über die in Fig. 1 dargestellten Leitungen. Dies stellt eine geeignete Art dar, um der Steuereinrichtung A einen direkten Zugriff für die Programmierung und für das Durchtesten zu geben und sodann für die Freigabe der Steuerung der Steuereinrichtung, die von dem Modul 20 getrennt ist.

Der Zentraleinheitsmodul 10 kann durch externe Zustände unterbrochen werden, um das Programm zu unterbrechen und um die Steuerung über den Mikroprozessor auf eine im Speicher gespeicherte Subroutine zu übertragen. Dies stellt eine Standard-Unterbrechungseigenschaft der meisten 8-Bit-Mikroprozessoren dar. Die Steuereinrichtung A enthält jedoch eine Vielzahl von gesonderten Unterbrechungs-Erweiterungsmodulen, von denen drei schematisch als Unterbrechungserweiterungsmodulen I, II, III bzw. 30, 32, 34 angedeutet sind. Der Unterschied zwischen dem ersten Erweiterungsmodul und den nachfolgenden Erweiterungsmodulen besteht darin, dass der Freigabeanschluss E des Moduls 30 mit einem Verknüpfungssignal 1 belegt ist, bei dem es sich in der Praxis um eine Spannung von 5 V in der Steuereinrichtung oder in dem System A handelt. Die

nachfolgenden Modulen 32, 34 und jegliche zusätzlichen Modulen enthalten an dem Anschluss E ein Eingabe-Freigabe-Verknüpfungssignal, welches durch den Zustand der vorhergehenden Unterbrechungserweiterungsmodulen gesteuert ist. Diese Verbindungsanordnung stellt ein Prioritätsebenensystem dar, bei dem die Unterbrechungs-Eingangssignale des Moduls 30 Vorrang über die Unterbrechungs-Eingangssignale der nachfolgend angeschlossenen Erweiterungsmodulen 32, 34 usw. besitzen. In jedem der Unterbrechungserweiterungsmodulen bei der dargestellten Ausführungsform sind 16 gesonderte Unterbrechungeingänge vorhanden, die schematisch als Vielzahl von einpoligen, an Masse bzw. an Erde liegenden Schaltern 30a-30x, 32a-32x bzw. 34a-34x veranschaulicht sind. Diese Unterbrechungeingänge können Verknüpfungseingänge sein, die eine Information erhalten, welche den Übergang des Moduls 10 in den Unterbrechungszustand zum Zwecke der Verarbeitung einer ausgewählten Subroutine fordert. Demgemäß veranlasst die Ansteuerung eines Eingangs den Mikroprozessor MP des Moduls 10, eine Unterbrechung auszuführen und auf die Subroutine überzugehen, die zu bearbeiten bzw. verarbeiten ist. Sodann wird die Steuerung auf das Ausführungsprogramm der Steuereinrichtung oder des Systems A zurückgeführt. Durch Verwendung dieser Unterbrechungserweiterungsanordnung kann eine grosse Anzahl von auswählbaren Subroutinen bereitgestellt und durch Abgabe einer Unterbrechungsanforderung an einen der in einer Mehrzahl schematisch dargestellten Verknüpfungseingänge aufgehoben werden. Das Ausführungs- bzw. Organisationsprogramm des Systems A erfordert die Verarbeitung eines «Nachseh»-Befehls oder einer Ablauffolge für jene Daten oder Verknüpfungseingangssignale und -ausgangssignale unter der Unterbrechungssteuerung lediglich dann, wenn eine Unterbrechungsanforderung aufgenommen worden ist, die anzeigt, dass ein bestimmter Anschluss oder bestimmte Anschlüsse abgetastet und/oder aktualisiert werden sollten.

Wenn eine Unterbrechungsanforderung durch den Zentral-einheitsmodul von einem Anschluss eines Erweiterungsmoduls aufgenommen wird, geht der Mikroprozessor in einen Unterbrechungszustand über, und durch Daten von dem Erweiterungsmodul her wird eine bestimmte Subroutine durch eine auf den Leitungen D<sub>0</sub>-D<sub>7</sub> auftretende Adresse ausgewählt oder «aufgehoben». Sodann wird das Aufruf-Eingangssignal oder -Ausgangssignal in Übereinstimmung mit der gewünschten und geforderten Unterbrechungs-Subroutine verarbeitet. Danach nimmt die Subroutine einen Befehlsübergang zu dem Hauptprogramm zurück vor. Wenn keine Unterbrechungsanforderung vorhanden ist, wird das Organisationsprogramm wiederholt abgearbeitet, ohne dass die Unterbrechungs-Subroutinen bearbeitet werden. Demgemäß werden die Subroutinen lediglich bei Bedarf aufgerufen und bearbeitet. Die Anzahl der Erweiterungsanschlüsse der Modulen 30 bis 34 kann auf grössere Werte gesteigert werden. Die einzigen praktischen Begrenzungen sind die Speicherkapazität, die auf verschiedene Kapazitäten ausgedehnt werden kann, und die für die Bearbeitung der Unterbrechungs-Subroutinen verfügbare Zeit.

Durch die Bereitstellung der Unterbrechungserweiterungsmodulen kann der Mikroprozessor des Systems oder der Steuereinrichtung A in einer wesentlich grösseren Häufigkeit unterbrochen werden, als dies bei bekannten Mikroprozessoren der Fall ist. Demgemäß kann das normale Mikroprozessor-Unterbrechungskonzept der Prioritätsauswertung und des Sprungens auf eine Subroutine, die durch eine bestimmte Unterbrechung gefordert wird, für viele gesonderte Eingangssignale oder Zustände benutzt werden. Dadurch wird Programmierzeit gespart, und ferner ist die Verwendung von Subroutinen, die in den Speichern der Einrichtung A gespeichert sein können, für einen lediglich periodischen Zweck ermöglicht. Die Vielseitigkeit der Einrichtung A ist dadurch stark ausgedehnt, während

dennoch ein leicht erhältlicher, relativ billiger Mikroprozessor verwendet wird.

Der Modul 40 ist ein programmierbarer Festwertspeichermodul, der im folgenden auch als PROM-Modul bezeichnet wird. Dieser PROM-Modul wird in dem System A dazu benutzt, dauernd den durch die Verknüpfungssignale auf den Leitungen A<sub>0</sub> bis A<sub>15</sub> festgelegten Verknüpfungszustand an den verschiedenen adressierten Stellen festzuhalten. In der Praxis werden im allgemeinen das Organisationsprogramm und die verschiedenen Subroutinen an den verschiedenen adressierten Speicherplätzen innerhalb des PROM-Moduls 40 bleibend gespeichert. Dieser Speichermodul wird für eine Langzeit- oder permanente Speicherung des Programms benutzt; er verwendet MOS-Speicherchips, die durch Belichtung mit ultraviolettem Licht lösbar und die durch gesonderte Einrichtungen, wie durch einen Rechner 22 oder durch eine Bandleseeinrichtung über den Direktzugriffsmodul 20 programmierbar sind. In der Praxis besitzt der PROM-Modul eine Kapazität von 4096 8-Bit-Wörtern. Die Anzahl der in dem Festwertspeichermodul 20 verfügbaren Wörter kann sich in Übereinstimmung mit der gewünschten Kapazität der Einrichtung A ändern. In der Praxis werden auf Grund der in dem Modul 40 benutzten Speicher-technologie statische, mit Silicium-Gate versehene löscharbe und elektrisch wieder programmierbare Festwertspeicher-chips auf MOS-Basis verwendet.

Während des normalen Betriebs der Steuereinrichtung A werden Daten von dem Modul 40 über die Leitungen D<sub>0</sub> bis D<sub>7</sub> abgegeben. Die Parallelübertragung von Binärdaten über diese Leitungen führt zur Abgabe eines 8-Bit-Wortes, welches durch die Verknüpfungssignale auf den Leitungen A<sub>0</sub>-A<sub>15</sub> adressiert ist. In Fig. 1 ist angedeutet, dass die Datenleitungen D<sub>0</sub>-D<sub>7</sub> bei dem PROM-Modul 40 bidirektional sind. Dies dient lediglich zum Zwecke des Ladens des Speichers während der Programmierungs- und Austestoperation über den Direktzugriffsmodul 20. Die Speicherchips des Moduls 40 sind in der Praxis unter normalen Umständen nicht löscharbe. Deshalb ist die ständige Spannungszufuhr zu diesem bestimmten Modul nicht erforderlich, um die gespeicherte Verknüpfung bzw. die gespeicherten Verknüpfungssignale festzuhalten. Selbstverständlich könnte eine Vielzahl von unterschiedlichen Arten von Festwertspeichern dazu verwendet werden, die Programminformation für das System A zu speichern, wie dies in Fig. 1 schematisch dargestellt ist.

Unter besonderer Bezugnahme auf den einen Speicher mit wahlfreiem Zugriff (RAM) umfassenden Speichermodul 50 sei darauf hingewiesen, dass dieser Speichermodul periodisch während der Benutzung der Steuereinrichtung A aktualisiert werden kann. In dem System könnten verschiedene Speichermodulen mit wahlfreiem Zugriff verwendet werden. Der Speichermodul 50 mit wahlfreiem Zugriff enthält eine gewisse Standard-Paritätsprüfschaltung 52, wie sie in Fig. 1 schematisch dargestellt ist. Dadurch wird die zu den und von den Speicherchips mit wahlfreiem Zugriff geleitete Information bezüglich der Parität überprüft, und zwar in Übereinstimmung mit der üblichen Praxis, um eine Fehlerbestimmung vorzunehmen. In der Praxis verwendet der Modul 50 Festkörper-Speicherchips mit wahlfreiem Zugriff, und zwar mit einer Kapazität von 4096 8-Bit-Wörtern. In diesem Modul wird eine externe Batteriespeisung benutzt, um die Information oder die Daten an den verschiedenen Speicherplätzen in dem Modul 50 festzuhalten, bis die Information oder die Daten in beabsichtigter Weise durch den Betrieb der Steuereinrichtung A geändert werden. Die in dem Modul 50 benutzte Halbleiterspeicher-technologie ist eine zu einem statischen Speicher mit wahlfreiem Zugriff führende N-MOS-Technologie. Der Modul 50 ist sowohl für das Lesen als auch für das Schreiben durch die Verknüpfungssignale auf den Leitungen A<sub>0</sub>-A<sub>15</sub> adressierbar. Diese Verknüpfungssignale bzw. Adresse wählt die gewünschte Adresse für den PROM-

Modul aus und leitet das in Frage kommende 8-Bit-Wort aus der entsprechenden Speicherstelle parallel zu den Datenleitungen D<sub>0</sub>-D<sub>7</sub> hin. das DBINP-Verknüpfungssignal und das R/W-Verknüpfungssignal legen fest, ob Daten in den Modul 50 einzuführen sind oder nicht oder ob Daten aus dem betreffenden Modul zu lesen sind oder nicht. Die Operation eines Speichers mit wahlfreiem Zugriff in Verbindung mit einem Mikroprozessor oder einer anderen Art einer digital programmierbaren Steuereinrichtung ist bekannt; demgemäß können verschiedene Systeme verwendet werden.

Neben dem PROM-Modul 40 und dem RAM-Modul 50 ist es möglich, einen zusätzlichen Speicher vorzusehen, der als PROM-Speicher und/oder als RAM-Speicher ausgeführt sein kann. Die Paritätsschaltung 52 ist in der Praxis durch einen solchen Schaltungstyp gebildet, der ein 9-Bit-Wort liefert und der eine Schaltungsanordnung umfasst, die erforderlich ist, um ein Bit für eine ungerade Parität je Wort zu erzeugen und zu prüfen. Wenn ein 8-Bit-Wort in den Speicher eingeschrieben wird, überprüft der Paritätsgenerator das Wort und erzeugt ein neuntes Bit, welches entweder als Verknüpfungssignal «1» oder «0» auftritt, so dass es sich ergebende 9-Bit-Wort stets eine ungerade Anzahl von «1»-Verknüpfungszuständen bzw. -Verknüpfungssignalen enthält. Wenn ein Wort aus dem Speicher ausgelesen ist, nimmt die Paritätsprüfungsschaltung eine Überprüfung vor, um festzustellen, ob das betreffende Wort noch eine ungerade Anzahl von «1»-Verknüpfungssignalen enthält. Wenn die Prüfungsschaltung eine gerade Anzahl von «1»-Verknüpfungssignalen ermittelt, wird der Prozessor in Übereinstimmung mit der üblichen Mikroprozessorpraxis unterbrochen. Es können auch andere Paritätsprüfungsschaltungen oder -systeme verwendet werden, so dass Fehler in der Information festgestellt werden können, zu der ein Zugriff erfolgt ist.

Die programmierbare Steuereinrichtung A verwendet einen Standard-Mikroprozessor, der acht Datenanschlüsse und sechzehn Adressenanschlüsse aufweist. Dadurch kann ein 8-Bit-Wort oder ein Byte gleichzeitig von dem Mikroprozessor bearbeitet werden. Diese Kapazität bringt eindeutige Vorteile im Hinblick auf ein Ablesen von verschiedenen Eingängen und dem Schreiben an verschiedenen Ausgängen mit sich. Die verknüpfungsmässige Verarbeitung eines einzigen Bits innerhalb eines 8-Bit-Wortes, wie eine undmässige, odermässige oder invertierende Verarbeitung, bringt jedoch eine erhebliche Schwierigkeit mit sich. Ein nennenswerter Teil der Software-Programmierung ist erforderlich, um eine verknüpfungsmässige Verarbeitung eines einzigen Bits eines 8-Bit-Wortes oder Bytes vorzunehmen. Dies erfordert Speicherplatz und eine umfangreiche Programmierung. Dieser Nachteil wird sogar noch schwerwiegender bei der Steuerung von Maschinen und eines Prozesses, da nämlich eine grosse Anzahl von einfachen Verknüpfungsfunktionen erforderlich ist. Mit der Verdopplung eines herkömmlichen Relais-Verknüpfungsdiagramms oder Leiterdiagramms stellt der grösste Anteil der Verarbeitung eine Verknüpfungsverarbeitung einer einzelnen Bitinformation dar. Um diese Einzelbit-Information bei einer 8-Bit-Datenkapazität zu verarbeiten, tritt somit eine erhebliche Zunahme des Programmspeicherplatzes und der Steuerungskomplexität auf. Wenn beispielsweise ein einzelnes Eingangssignal mit einem einzelnen Ausgangssignal zu vergleichen ist, stellt die Ausnutzung einer 8-Bit-Eingangsinformation einen Nachteil dar. Wenn Speicheradressen oder binärcodierte Daten übertragen oder verarbeitet werden, ist die grosse Anzahl von Datenleitungen von Vorteil. Um die mit der Verknüpfungsverarbeitung verbundenen Nachteile, die durch die Erhöhung der Kapazität des Mikroprozessors hervorgerufen werden, zu überwinden, wird durch das Steuereinrichtungssystem A eine Schaltungsanordnung bereitgestellt, durch die eine Ein-Bit-Information erhalten wird, welche auf einer ausgewählten Datenleitung, wie der Datenleitung D<sub>0</sub>, in ähnlicher Weise

verknüpfungsmässig verarbeitet werden kann wie bei einem Einzelbit-Datenprozessor. Damit ist es relativ einfach möglich, einen UND-, ODER- und Invertierungs-Verknüpfungsprozess an verschiedenen Eingängen und Ausgängen auszuführen, um 5 Verknüpfungsfunktionen zu realisieren, die mit dem Aufkommen des erweiterten 8-Bit-Mikroprozessors als komplexer betrachtet werden. Um die Anwendung sowohl der Byte-Betriebsart als auch der Bit-Betriebsart zu veranschaulichen, sind ein Byte-Eingabe- und Byte-Ausgabemodul 60 und ein Bit-Eingabe- und Bit-Ausgabemodul 70 veranschaulicht. Der 10 Modul 60 weist eine Reihe von Eingabewörtern auf, deren jedes acht Datenbits umfasst. Diese Wörter werden durch verschiedene Eingabeeinrichtungen erzeugt, wie durch ein Codierscheibennetzwerk 62. In entsprechender Weise sind die Ausgabebewörter von dem Modul 60 als Anzeigesignale in einer Anzeigeeinheit 64 veranschaulicht. Demgemäß wird der Modul 60 dazu herangezogen, ein Informationsbyte als ein 8-Bit-Wort an den verschiedenen Eingabe- oder Ausgabestellen einzugeben bzw. auszugeben.

Ein einzelnes Informationsbit wird von der Treiberschaltung oder dem Modul 70 auf der Einzeldatenleitung D<sub>0</sub> eingegeben oder ausgegeben. Wenn ein Bit-Operationsbetrieb durch die Schaltungsanordnung ausgewählt ist, die gemäß der vorliegenden Erfindung aufgebaut bzw. ausgebildet ist, dann wird 25 lediglich das auf der Leitung D<sub>0</sub> auftretende Verknüpfungssignal somit verarbeitet. Die Verknüpfungssignale auf den übrigen bidirektionalen Datenleitungen werden unberücksichtigt gelassen bzw. ignoriert. Um zu bestimmen, ob ein Einzel-Informationsbit zu den Ausgabeeinheiten 80 über die Treiberschaltung 30 70 geleitet wird oder nicht, wird die System-Treiberschaltung durch das auf der Eingabeleitung DBINP und der Lese/Schreib-Leitung R/W auftretende Verknüpfungssignal gesteuert. Eine Speisespannungsquelle 12 gibt eine Gleichspannung von 5 V für den Betrieb der Verknüpfungsanordnung in dem System A 35 und eine Gleichspannung von 12 V für den Betrieb von bestimmten anderen Komponenten ab. Die 2-V- und 4-V-Leitungen von der Speisespannungsquelle 12 her werden zur Abgabe von Spannungen benutzt, durch die die Verknüpfungssignale des RAM-Speichers aufrechterhalten werden, wenn die 40 Speisespannungsversorgung in unbeabsichtigter Weise unterbrochen wird. Diese beiden Leitungen werden durch wieder-aufladbare Batterien gesteuert. Selbstverständlich könnte eine Vielzahl von anderen Speisespannungseinrichtungen in Übereinstimmung mit den gewünschten Speisespannungsanforderungen der programmierbaren Steuereinrichtung A verwendet werden.

Im folgenden seien einige Definitionen bezüglich der Steuerleitungen gegeben. Unter erneuter Bezugnahme auf Fig. 1 sei bemerkt, dass dort eine Anzahl von Steuerleitungen 50 dargestellt ist, die eine Verbindung zwischen dem Zentraleinheitsmodul 10 und den verschiedenen anderen Modulen herstellen, welche die programmierbare Steuereinrichtung A darstellen bzw. umfassen. Diese Steuerleitungen befinden sich ausserhalb des Zentraleinheitsmoduls. In vielen Fällen entsprechen sie jedoch bestimmten Verbindungsanschlüssen des Mikroprozessors vom Typ Intel 8080 bzw. sind jenen Anschlüssen des Mikroprozessors verknüpfungsmässig zugehörig, wie er bei der dargestellten Ausführungsform einer die vorliegende Erfindung umfassenden programmierbaren Steuereinrichtung verwendet ist. Unter Berücksichtigung der allgemeinen Operation der programmierbaren Steuereinrichtung A sei die Grundfunktion jeder der in Fig. 1 dargestellten Leitungen gesondert erläutert. Im Zuge der Beschreibung wird durch die invertierte Form einer Leitungsbezeichnung angegeben, dass ein niedriger Verknüpfungszustand – ob Impulszustand oder Dauerzustand – vorhanden oder ein «Jax»-Zustand vorhanden ist. So zeigt beispielsweise die mit R/W bezeichnete Lese/Schreib-Leitung an, dass ein Lesezustand bei einem Verknüpfungssignal «1» vor-

liegt und dass ein Schreibzustand bei einem Verknüpfungssignal «0» vorliegt. Diese Übereinkunft wird in den meisten, Mikroprozessoren und ähnliche digital gesteuerte numerische Verarbeitungseinrichtungen verwendenden Anlagen benutzt.

Auf der Synchronisiersignalleitung SYNC tritt ein negativer oder ein niedriges Potential besitzender 100-ns-Verknüpfungsimpuls auf, der den Beginn des jeweiligen 8080-Maschinenzyklus anzeigt. Dieser Impuls ist nicht programmierbar; er wird dazu herangezogen, das Statuswort in der jeweiligen Komponente oder dem jeweiligen Modul zu verriegeln, welches eine Statusinformation von der Zentraleinheit für die Verwendung während eines gesamten Maschinenzyklus benötigt, der ein oder mehrere Wörter enthalten bzw. umfassen kann.

Der externe Taktimpuls  $\bar{O}2$  wird von dem internen Zentraleinheits-Taktgenerator erzeugt; er kann dazu herangezogen werden, die Operation der verschiedenen Modulen zu synchronisieren. Dieser Impuls bzw. dieses Signal kann außerdem als ein genaues Zeitbasissignal benutzt werden. In der Praxis besitzt dieses Taktsignal entweder eine Frequenz von 2,0 MHz oder von 3,0 MHz.

Die Adressenleitungen  $A_0$ - $A_{15}$  führen mit Ausnahme der Adressenleitung  $A_{15}$  tatsächlich alle das Verknüpfungssignal «0». Das Verknüpfungssignal auf diesen Leitungen wird im übrigen dazu herangezogen, die Adresse für sämtliche Speicher und Eingabe/Ausgabe-Modulen für das Steuersystem A bereitzustellen. Diese Adressenleitungen sind von dem Modul 10 her im allgemeinen Ausgabeleitungen. Wenn der Direktzugriffsmodul 20 benutzt wird, sind die betreffenden Leitungen jedoch bidirektionale Leitungen, die die Eingabe von Adressen in den Modul 10 ermöglichen. Mit  $A_0$  ist das Adressenbit niedrigster Wertigkeit auf den Adressenleitungen bezeichnet.

Auf der DBINP-Leitung wird die Übertragungsrichtung der Datenleitungen  $D_0$ - $D_7$  bezeichnet. Diese Steuerleitung wird dazu herangezogen, Daten auf den Datenbusleitungen von dem jeweiligen Modul der Einrichtung A zu tasten bzw. weiterzuleiten.

Die R/W-Leitung wird in der Einrichtung A dazu herangezogen, Daten auf den Datenbusleitungen zu den adressierten Speicherplätzen hin zu tasten bzw. hinzuleiten. Mit Rücksicht auf die Ähnlichkeit zwischen der DBINP-Leitung und der R/W-Leitung werden diese Leitungen im allgemeinen gemeinsam benutzt. Die DBINP-Leitung wird dabei dazu herangezogen, die Richtung des Datenflusses zu bestimmen und die Daten auf die Datenbusleitungen zu tasten bzw. zu leiten. Die Lese/Schreib-Leitung R/W wird dazu herangezogen zu bestimmen, ob diese Daten geschrieben oder gelesen werden. Durch Bereitstellung dieser beiden Steuerleitungen sind die Daten auf der Datenbusleitung oder den Leitungen  $D_0$ - $D_7$  während des impulsweisen Lesens und Schreibens auf der R/W-Leitung stabil.

Die Warte-Leitung wird in Verbindung mit der Bereitschafts-Leitung benutzt. Diese Leitungen stehen mit dem Mikroprozessor in Verbindung, der eine zusätzliche Zeitspanne für das Ablesen von langsameren Speicher- oder Eingabe/Ausgabe-Stellen ermöglicht. Wenn während einer adressierten Ausgabe der Modul 10 nicht einen Verknüpfungszustand bzw. ein Verknüpfungssignal «1» auf der Bereitschaftsleitung aufnimmt, dann tritt der Mikroprozessor in den Wartezustand ein, und zwar solange, wie die Bereitschaftsleitung ein niedriges Verknüpfungssignal führt. In diesem Zustand wird auf der Warte-Leitung ein Verknüpfungssignal «0» erzeugt. Sobald das Bereitschafts-Eingangssignal aufgenommen ist, gelangt der Mikroprozessor aus dem Warte-Zustand heraus, und auf der Warte-Leitung tritt ein Verknüpfungssignal «1» auf. Dieses Merkmal ist in Fig. 2 klar dargestellt, die sich auf die Operation des Mikroprozessors vom Typ Intel 8080 bezieht.

Der Ausgang INT<sub>E</sub> bezeichnet den Inhalt eines internen Unterbrechungs-Freigabe-Flip-Flops in dem Mikroprozessor

vom Typ Intel 8080. Dieses interne Flip-Flop kann durch Freigabe- und Sperr-Unterbrechungsbefehle gesetzt oder zurückgestellt sein und bewirkt die Sperrung der Aufnahme bzw. Annahme nachfolgender Unterbrechungsaufforderungen

- 5 durch den Mikroprozessor, wenn sich das betreffende Flip-Flop im Rückstellzustand befindet. Das interne Flip-Flop, welches auf dem Chip selbst gebildet ist, wird automatisch zurückgestellt, um weitere Unterbrechungen zum Zeitpunkt  $T_1$  eines Befehlsabrufzyklus M<sub>1</sub> zu sperren und dann, wenn eine Unterbrechung von dem Mikroprozessor angenommen worden ist.

- 10 Die HLDA-Leitung ist die Halte- bzw. Festhaltequittungsleitung. Das auf dieser Leitung auftretende Verknüpfungssignal geht in ein Verknüpfungssignal «0» dann über, wenn eine Halte- bzw. Festhalteanforderung (HOLD REQUEST) von dem Mikroprozessor MP bestätigt wird. Diese Halteanforderung wird von der Halteanforderungs-Leitung beliefert, wie dies in Fig. 1 veranschaulicht ist. Der Haltezustand (HOLD) des Mikroprozessors überführt die Adressen- und Datenanschlüsse des Mikroprozessors in einen Zustand hoher Impedanz, so dass diese Anschlüsse die Steuerung über die Adressenleitungen  $A_0$ - $A_{15}$  sowie über die Datenleitungen  $D_0$ - $D_7$  freigeben. Diese Leitungen können durch den Zugriffsmodul 20 während der Programmierung und während des Durchtestens gesteuert werden. Das Signal auf der HLDA-leitung beginnt zum Zeitpunkt  $T_3$  für einen Lese-Speicher- oder Einabezyklus. Für einen Speichereinschreib- oder Ausgabezyklus bzw. für eine entsprechende Operation erfolgt eine Verschiebung auf der HLDA-Leitung mit der Taktperiode im Anschluss an die  $T_3$ -Taktperiode. In der Praxis ist es bekannt, dass das Signal auf der HLDA-Leitung, welches nach einer Anstiegsflanke eines Impulses 01-Impulses auf den eine hohe Impedanz besitzenden Adressenleitungen und Datenleitungen erscheint, nach der folgenden Flanke eines 02-Impulses auftritt. Das auf der Halteanforderungs-Leitung (HOLD REQUEST) auftretende Signal zeigt an, dass eine externe Anforderung dafür vorliegt, die Zentraleinheit und insbesondere den Mikroprozessorchip in den Haltezustand (HOLD) überzuführen. In diesem Haltezustand können externe Einrichtungen die Adressen- und Datenleitungen steuern, sobald der Zentraleinheitsmodul seine Ausnutzung dieser Leitungen bezüglich der Bearbeitung des existierenden oder vorliegenden Maschinenzyklus abgeschlossen hat. Die Steuerung wird von dem Zentraleinheitsmodul über die DBINP-Leitung und die R/W-Leitung auch wieder aufgegeben. Mit anderen Worten ausgedrückt heisst dies, dass diese Leitungen durch den Direktzugriffsmodul 20 für Programmierungs- oder andere externe Steuerfunktionen gesteuert werden können. Zusammenfassend ist anzumerken, dass dann, wenn ein Haltezustand (HOLD) gefordert ist, der Mikroprozessor in den Haltezustand (HOLD) übergeht und ein Ausgabesignal über die HLDA-Leitung abgibt, um eben diesen Haltezustand (HOLD) anzuzeigen. Dieser Zustand tritt nach einem gewissen Aufräumen bzw. einer gewissen Fertigstellung während eines bearbeiteten Maschinenzyklus auf. Der betreffende Haltezustand wird beim nächsten Maschinenzyklus zum Tragen kommen und die existierende interne Verknüpfung hinsichtlich der Registerzustände des Mikroprozessorchips festhalten.

Eine entsprechende Anordnung wird für die Rücksteloperation benutzt. Eine Rückstellenforderung wird von der Speisespannungsversorgung 12 oder von dem Direktzugriffsmodul 20 auf der Rückstellenforderungs-Leitung erzeugt.

Wenn diese Anforderung von dem Modul 10 aufgenommen wird, wird der Mikroprozessor zurückgestellt. In diesem Zustand wird der Inhalt des internen Programmzählers des 8080-Mikroprozessors gelöscht. Nach Auftreten des Rückstellimpulses wird das Programm an einer Stelle mit dem Wort 0 in dem Speicher beginnen. Die internen INT<sub>E</sub>- und HLDA-Flip-Flops des Mikroprozessorchips werden ebenfalls zurückgestellt. Der interne Akkumulator, der Stapelzeiger und die Regi-

ster werden nicht gelöscht. Wenn in den Rückstellzustand eingetreten wird, erfolgt eine Verschiebung bzw. Veränderung des Verknüpfungssignals auf der Rückstelleitung (RESET), wodurch die verschiedenen Flip-Flops und andere Verknüpfungseinrichtungen innerhalb des Systems A zurückgestellt werden. Dies dient dazu, das Steuereinrichtungssystem A in Betrieb zu setzen.

Die bidirektionalen Datenbusleitungen oder Leitungen D<sub>0</sub> bis D<sub>7</sub> stellen eine 8-Bit-Datenverbindung zu dem Zentraleinheitsmodul 10 her. Derüber hinaus sind diese Leitungen mit den verschiedenen Speichermodulen und Eingabe/Ausgabe-Modulen verbunden. Die Modulen, die lediglich Bit-Funktionen ausführen, und zwar im Unterschied zu Byte-Funktionen, benutzen lediglich eine dieser Leitungen, zumindest für die Datenausgabe. Bei der bevorzugten Ausführungsform handelt es sich dabei um die Leitung D<sub>0</sub>. Während des ersten Taktzyklus jedes Maschinenzyklus des Mikroprozessors gibt der Zentraleinheitsmodul ein Statuswort über die Datenleitung oder die Busleitung D<sub>0</sub>-D<sub>7</sub> ab. Dieses Statuswort ist ein 8-Bit-Wort, welches den gegenwärtigen Maschinenzyklus beschreibt. Bei diesem Statuswort führt die Leitung D<sub>0</sub> bei der bevorzugten Ausführungsform das Bit niedrigester Wertigkeit. Die vorliegende Erfindung bezieht sich dabei auf einen Mikroprozessor des Typs, der acht Datenbits verwendet. Es kann jedoch eine andere Anzahl von Datenbits ohne Abweichung vom Zweck der vorliegenden Erfindung benutzt werden. Bei Verwendung eines 8-Daten-Bit-Mikroprozessors kann jedoch das Statuswort acht Bits aufweisen, die von dem Mikroprozessor entsprechend dem Befehl oder der Instruktion erzeugt worden sind, der bzw. die von dem Programm her erhalten worden ist.

In den nunmehr verfügbaren Mikroprozessoren existiert eine Unterbrechungseigenschaft, wie sie oben kurz beschrieben worden ist. Eine Unterbrechungseigenschaft bzw. -möglichkeit des Mikroprozessors gestattet es, dessen vorliegende Einstellung bzw. Position in einem Programm zu speichern, zu einer aufgerufenen Subroutine hinzuspringen, die Subroutine zu bearbeiten und dann zu der richtigen Stelle in dem Programm zurückzuspringen, das zuvor bearbeitet worden war. Um diese Funktion auszuführen, weist der Mikroprozessor einen Eingang INT auf, und der Modul 10 besitzt verschiedene Unterbrechungsanforderungsanschlüsse INT0-INT7. Das an dem INT-Anschluss auftretende Verknüpfungssignal überführt den Mikroprozessor in den Unterbrechungszustand. Zu diesem Zeitpunkt wird der Anschluss INTE (INTE-Leitung) gespeist, um nachfolgende Unterbrechungen zu vermeiden, bis die ausgewählte Subroutine den INTE-Anschluss zu dem in Frage kommenden Zeitpunkt zurückgestellt hat. Eine Unterbrechung höherer Priorität kann den Betrieb der Steuereinrichtung übernehmen, bevor eine Unterbrechungs-Subroutine niederer Prioritätsebene beendet ist, sofern der INTE-Anschluss durch die verarbeitete Subroutine zurückgestellt worden ist. Bisher ist bei einem Mikroprozessor verwendenden Verarbeitungssystemen die Möglichkeit vorhanden gewesen, lediglich eine endliche, relativ begrenzte Anzahl von Unterbrechungsanforderungen aufzunehmen. Diese Beschränkung ist durch die Beschränkungen der verschiedenen Codes festgelegt gewesen, die für die Subroutinenauswahl oer «Subroutinenaufladung» verfügbar waren. Das System A benutzt ein System, welches acht Unterbrechungseingänge enthält, über die der Mikroprozessor in den Unterbrechungszustand überführt wird. In Fig. 1 sind die Unterbrechungsanschlüsse INT0-INT3 sowie INT5-INT7 veranschaulicht. In der Praxis sind diese Unterbrechungsanschlüsse externen Zuständen, Anschläßen oder Parametern zugeordnet, die Eingabe- oder Ausgabesignale sein können. Die Priorität der Unterbrechungsanforderungen verläuft in umgekehrter Reihenfolge zu der Numerierung, womit die höchste Priorität die niedrigste Nummer bzw. Zahl besitzt. Die niedrigste Priorität besitzt die höchste Zahl. Demgemäß stellt

der PWR-Zustand – der durch ein Verknüpfungssignal Null gebildet ist, wenn die Speisespannungsversorgung abgeschaltet worden ist – die Unterbrechung mit der höchsten Priorität dar. Bei Vorliegen dieses Zustands wird das Programm unabhängig von anderen Unterbrechungszuständen zu der Subroutine «Speisespannungsversorgung abgeschaltet» übergehen, die sich an einer ausgewählten Speicherstelle in dem Speicher befindet; in der Praxis ist diese Speicherstelle durch den Oktalwert 010 gegeben. Das nächste Unterbrechungs-Eingangssignal ist in der Praxis das Signal BOOT, welches eine Unterbrechungsanforderung INT2 für einen Speicherplatz in dem Speicher erzeugt. Auf diese Art und Weise steht ein Minimalprogramm für die einleitende Operation der Einrichtung A zur Verfügung. Dieses einleitende Minimalprogramm ist unter der Oktaladresse 020 des Speichers untergebracht; es wird durch verschiedene Einrichtungen «aufgerufen», die in Fig. 1 schematisch als Drucktastenschalter bzw. Drucktasten angedeutet sind. Die Unterbrechungsanforderung INT3 legt den Modul-Verriegelungs- und Paritätszustand fest, der in Übereinstimmung mit der bekannten Praxis bearbeitet wird, um die Kontinuität der verschiedenen Modulen aufrechtzuerhalten. Bei der Unterbrechungsanforderung INT4 handelt es sich um eine echte Taktunterbrechungsanforderung, durch die das Programm zu dem durch die Oktaladresse 040 bezeichneten Speicherplatz in dem Speicher übergeführt wird. Dies wird im Hinblick auf die Unterbrechungsfunktionen des Systems A noch im einzelnen erläutert werden. Die Unterbrechung bzw. Unterbrechungsanforderung INT5 ist eine Übertragungsunterbrechung bei der bevorzugten Ausführungsform der Erfindung. Durch diese Unterbrechung wird eine Speicherzelle mit der Oktalbezeichnung 050 in dem Speicher bezeichnet. Dies ermöglicht eine Verbindung von externen Einrichtungen her, wie von dem Direktzugriffsmodul 20. Die Unterbrechung INT7, die die niedrigste Priorität besitzt, überführt den Mikroprozessor in den Unterbrechungszustand, um von externen Einrichtungen, wie Codierscheiben bzw. Codierräder, Lampen, Schaltern und visuellen Anzeigeeinrichtungen her zu lesen oder in diesen externen Einrichtungen zu schreiben. Damit bleibt noch die Unterbrechung INT6 übrig, die in Verbindung mit den Modulen 30, 32 und 35 dazu herangezogen wird, den Umfang der Unterbrechungsmöglichkeit in der Einrichtung A auszuweiten. Von dem IIV6-Ausgang erfolgt die Quittierung der Aufnahme und Verarbeitung einer Unterbrechungsanforderung INT6. Diese Signalleitung verbleibt im Zustand niedrigen Verknüpfungspiegels, während die Unterbrechungseinrichtung eine Anforderung von einem der Modulen 30 bis 34 an den Zentraleinheitsmodul 10 überträgt. Der Aufrufbefehl wird synchron mit einem 02-Taktsignal übertragen; er liefert die Adresse in dem Speicher, unter der ein Aufruf während einer ausgewählten zusätzlichen Unterbrechung untergebracht ist, die von den hinzugefügten Modulen beliefert wird, von denen lediglich drei dargestellt sind.

Diese Beschreibung der grundsätzlichen Leitungen oder Befehlswege, die zu und von dem Zentraleinheitsmodul 10 verlaufen, dürfte genügen für ein vollständiges Verständnis der Erfindung, bei der die Verwendung eines verbesserten Moduls vorgesehen ist, welcher in Verbindung mit einer einen Mikroprozessor verwendenden programmierbaren Steuereinrichtung des in Fig. 1 schematisch dargestellten Typs verwendet wird. Diese Ausgabe- und Eingabeleitungen entsprechen der Nomenklatur, die von der Firma Intel Corporation für deren Mikroprozessorchip mit der Bezeichnung 8080 verwendet ist, der bei der bevorzugten Ausführungsform der vorliegenden Erfindung benutzt wird. Eine entsprechende Nomenklatur wird auch in anderen kommerziell erhältlichen Mikroprozessorchips benutzt, die die Eigenschaften besitzen, die hier als Hintergrundinformation sowie als auf dem betreffenden Gebiet an sich bekannte erläuternde Information gegeben worden ist. Die

Eigenschaften dieses Mikroprozessorchips sind an sich bekannt. Der Modul 10 könnte einen I-STROBE- bzw. I-Tastimpuls auf einer Steuerleitung erzeugen, und zwar für die softwaremässige Lieferung eines Tastimpulses für die verschiedenen Eingaben und Ausgaben, sofern dies erforderlich sein sollte.

Nunmehr sei das Statuswort für den Mikroprozessor näher betrachtet. In dem Mikroprozessor, wie er in dem Modul 10 verwendet wird, tritt wie bei den meisten Mikroprozessoren ein Statuswort an den Datenanschlüssen als erstes Wort des jeweiligen Maschinenzyklus auf. Dieses Statuswort zeigt die von dem Mikroprozessor während des laufenden Maschinenzyklus auszuführende Operation an. Obwohl eine Vielzahl von Statuscodes und Status-Zuständen bereitgestellt werden könnte, sind in dem Diagramm gemäss Fig. 2 die zehn Statuswörter veranschaulicht, die bei dem Mikroprozessor des Typs Intel 8080 verwendet sind. Die Datenanschlüsse führen dabei eine Codierung, wie sie in den vertikalen Spalten für jeden der verschiedenen Typen von Maschinenzyklen während des einleitenden Teiles des jeweiligen Zyklus angegeben ist. Der binäre Statuscode an den Anschlüssen D<sub>0</sub>-D<sub>7</sub> wird in einer Status-Verriegelungsschaltung mit dem einleitenden Synchronisierimpuls auf der SYNC-Leitung verriegelt.

Wenn der Maschinenzyklus gegeben ist durch eine Befehlsabholung, dann wird das auf den Datenleitungen D<sub>0</sub>-D<sub>7</sub> auftretende Codewort, welches in der Status-Verriegelungsschaltung festgehalten bzw. verriegelt wird, gegeben sei mit 01000101. Der an jedem der Datenanschlüsse während des einleitenden Teiles des Zyklus auftretende Binärkode zeigt einen Zustand an, wie dies in der Spalte «Statusinformation» angegeben ist. Entsprechend der beim Mikroprozessor des Typs Intel 8080 benutzten Terminologie stellt das Verknüpfungssignal der Datenbusleitung D<sub>0</sub> das Unterbrechungs-Quittungssignal (INTA) dar. Dieses Verknüpfungssignal zeigt an, ob eine Unterbrechungsanforderung bestätigt bzw. quittiert worden ist; es kann dazu herangezogen werden, einen Neustart-Befehl auf die Datenbusleitungen zu tasten, wenn die DBIN- oder DBINP-Leitung aktiv bzw. wirksam ist. Das auf der Leitung D<sub>1</sub> während des einleitenden Teiles des Maschinenzyklus auftretende Verknüpfungssignal zeigt an, ob eine Schreibfunktion vorliegt oder nicht. Dieser Status ist mit W bezeichnet; der betreffende Status ist durch ein Verknüpfungssignal 0 gekennzeichnet, wenn in dem Maschinenzyklus Daten in den Speicher oder in eine Ausgabestelle eingeschrieben werden. Wenn auf der Befehlsleitung D<sub>1</sub> ein Verknüpfungssignal 1 auftritt und in der Status-Verriegelungsschaltung festgehalten bzw. verriegelt wird, dann wird aus einem Speicher oder von einer Eingabestelle gelesen. Ein auf der Leitung D<sub>2</sub> während des Befehlslese-Teiles des Zyklus auftretendes Verknüpfungssignal 1 zeigt an, dass die Adressenbusleitungen A<sub>0</sub>-A<sub>15</sub> die Rückstapeladresse von dem Stapelzeiger des Mikroprozessors festhalten. Dieser Status, der mit STACK bzw. mit Stapel bezeichnet ist, ist lediglich während eines Stapellese-Maschinenzyklus oder während eines Stapschreib-Maschinenzyklus wirksam.

Wenn auf der Datenleitung D<sub>3</sub> während des anfänglichen Mikrozyklus eines Maschinenzyklus ein Verknüpfungssignal 1 auftritt, zeigt dies an, dass ein Anhalten HALT bestätigt worden ist. Wie aus Fig. 2 ersehen werden kann, tritt dies während des Halt-Quittungsmaschinenzyklus oder während eines Maschinenzyklus auf, währenddessen eine Unterbrechungsquittung während des Anhalteis erfolgt. Ansonsten wird während des einleitenden Mikrozyklus, der mit T<sub>1</sub> in Fig. 3 bezeichnet ist, diese Datenbusleitung D<sub>3</sub> ein Verknüpfungssignal 0 führen. Während einer Ausgabefunktion ist das Verknüpfungssignal auf der Leitung D<sub>4</sub> gegeben durch ein Verknüpfungssignal 1. Dieses Verknüpfungssignal tritt dann auf, wenn sich der Maschinenzyklus in einem Ausgabe-Schreibzyklus befindet. Ein auf der Datenleitung D<sub>4</sub> auftretendes Verknüpfungssignal 1 zeigt an, dass die Adressenbusleitungen die Adresse einer Aus-

gabeeinrichtung enthalten bzw. führen und dass die Datenbusleitung schliesslich während des Zyklus die Ausgabedaten enthält bzw. führt, wenn die Leitung R/W ein Verknüpfungssignal 0 führt. Das auf der Datenleitung D<sub>5</sub> auftretende Verknüpfungssignal stellt ein Signal dar, welches anzeigen, dass sich der Mikroprozessor in dem Abhol- bzw. Abrufzyklus für das erste Byte eines Befehls befindet. Demgemäß zeigt eine auf der Leitung D<sub>5</sub> während des einleitenden Teiles des Maschinenzyklus auftretendes Verknüpfungssignal 1 an, dass ein Befehl von dem Speicher oder einer anderen Stelle her zu erhalten ist. Dies stellt den Status M<sub>1</sub> dar, wie er in Fig. 2 veranschaulicht ist. Der Status INP wird auf der Datenleitung D<sub>6</sub> erhalten. Ein auf dieser Leitung während des Statusteiles eines Maschinenzyklus auftretendes Verknüpfungssignal 1 zeigt an, dass die Adressenbusleitungen die Adresse einer Eingabeeinrichtung führen bzw. enthalten und dass die Eingabedaten auf die Datenbusleitungen gegeben werden sollten, wenn der DBIN-Ausgang des Mikroprozessors aktiv ist. Dieser Ausgang entspricht selbstverständlich der DBINP-Leitung des Zentraleinheitsmoduls 10. Das Verknüpfungssignal MEMR tritt auf der Datenbusleitung D<sub>7</sub> auf. Ein auf dieser Busleitung während des Statusinformations-Teiles des Zyklus auftretendes Verknüpfungssignal 1 zeigt an, dass die Datenbusleitungen für eine Speicherlesoperation benutzt werden.

Während des Statusteiles irgendeines Zyklus stellt das auf den Datenleitungen D<sub>0</sub>-D<sub>7</sub> auftretende Verknüpfungssignal die in Fig. 2 angedeuteten Codes dar. Dieses Verknüpfungssignal ergibt sich aufgrund einer dem Mikroprozessor des Typs Intel 8080 eigenen Funktion. Die betreffende Codierung wird hier lediglich zum Zwecke eines leichteren Verständnisses der bevorzugten Ausführungsform der vorliegenden Erfindung angegeben.

Nunmehr sei der Grundbefehlszyklus für den Zentraleinheitsmodul näher betrachtet. Der bei der bevorzugten Ausführungsform der vorliegenden Erfindung verwendete Mikroprozessor besitzt einen Grundbefehlszyklus, wie er in Fig. 3 veranschaulicht ist. Die zeitliche Steuerung des Mikroprozessors erfolgt durch die Eingangsimpulse 01, 02. Der erstgenannte Eingangsimpuls legt dabei den einleitenden Teil eines Mikrozyklus fest; dieser Zyklusteil ist mit T<sub>1</sub>-T<sub>3</sub> bezeichnet. Der Mikrozyklus T<sub>W</sub> wird zum Zwecke der Bezeichnung eines Wartezustands benutzt, worauf weiter oben im Zusammenhang mit dem Zusammenwirken zwischen der Lese-Verknüpfungsanordnung und der Warte-Verknüpfungsanordnung eingegangen worden ist. Wenn ein Speicher nicht bereitsteht, dann geht der Mikroprozessor in einen Wartezustand über, wie dies durch das Auftreten eines Verknüpfungssignals 1 auf der Warte-Leitung charakterisiert ist. Dies bedeutet, dass ein Verknüpfungssignal 0 auf der Leitung WARTEN auftritt. Wenn der Speicher dann bereitsteht, tritt auf der Warte-Leitung wieder ein Verknüpfungssignal 0 auf, und der Mikroprozessor fährt im Mikrozyklus T<sub>3</sub> weiter. Für jeden Maschinenzyklus ist ein mit SYNC bezeichneter Synchronisierimpuls vorhanden. Dieser Synchronisierimpuls entspricht im wesentlichen dem internen Synchronisierimpuls des Mikroprozessors vom Typ Intel 8080. Der Impuls ist dabei etwas geformt. Die in Fig. 3 dargestellten Impulse sind jene Impulse, die in den Modul 10 eingeführt und aus diesem herausgeführt werden. Dabei handelt es sich jedoch grundsätzlich um die Impulse von dem Mikroprozessor selbst. Während jedes der Mikrozyklen läuft die im unteren Teil der Fig. 3 angegebene Funktion ab. Zuweilen werden drei Mikrozyklen benutzt. In anderen Fällen sind viele Mikrozyklen für einen bestimmten Befehl erforderlich. Wenn beispielsweise beim Mikroprozessor des Typs Intel 8080 ein Speicherzugriff erfolgt, dann können bis zu 18 Mikrozyklen beim Normalbetrieb benutzt werden. Während der Mikrozyklus T<sub>1</sub> eines Maschinenzyklus wird das Verknüpfungssignal auf den Leitungen D<sub>0</sub>-D<sub>7</sub> gelesen. Die Adresse auf den Leitungen A<sub>0</sub>-A<sub>15</sub> (an

den Adressenanschlüssen des Mikroprozessors MP) wird entweder von dem internen Programmzähler oder von einem anderen Register innerhalb des Mikroprozessors geliefert. Diese Adresseninformation wird in den Programmzähler oder in das Programmregister während eines vorangegangenen Maschinenzyklus eingeführt. Die DBINP-Leitung entspricht der internen DBIN-Leitung. Über diese Leitung wird festgelegt, ob Daten an die Datenleitungen D<sub>0</sub>-D<sub>7</sub> in einem nachfolgenden Teil oder Mikrozyklus des Maschinenzyklus abzugeben sind oder nicht. Während des anfänglichen Teiles zeigen die Daten an den Datenanschlüssen des Mikroprozessors den Typ des während des Maschinenzyklus zu verarbeitenden Zyklus an, der mehrere Mikrozyklen erfordern kann. Das auf den in Fig. 3 bezeichneten Leitungen auftretende Verknüpfungssignal ändert sich entsprechend dem Typ des zu bearbeitenden Befehls, und zwar in Übereinstimmung mit der an sich bekannten Praxis auf dem Gebiet der Mikroverarbeitung. Diese Verknüpfungszustände werden im Zuge der Beschreibung der bevorzugten Ausführungsform der vorliegenden Erfindung verwendet.

Unter Bezugnahme auf Fig. 1 sei angemerkt, dass das System A ein Analog-Digital-Umsetzermodul oder eine A/D-Schaltung 100 enthält, wie sie am besten in Fig. 6A, 6B und 6C dargestellt ist. Diese Schaltung umfasst in gewisser Hinsicht übliche Konzepte hinsichtlich der Umsetzung einer Analog-Eingangsspannung in Digital-Ausgangsdaten bzw. Digital-Ausgabedaten. Gemäss der bevorzugten Ausführungsform der Erfindung wird das erzielte oder umgesetzte digitale Datensignal im Multiplexbetrieb über die Datenleitungen D<sub>0</sub>-D<sub>7</sub> des Systems A in einer noch zu beschreibenden Art und Weise geleitet. Ein umzuwendelndes Analog-Signal wird über die Leitungen 110, 112 zugeführt. Ein Umsetz- bzw. Wandlersignal ADC wird auf der Leitung 114 bereitgestellt, um die Operation der Umsetzschaltung 100 am Ende dieses Impulses beginnen zu lassen. Nachdem die Umsetzung der Analog-Signale in die Digital-Daten durch die Schaltung 100 abgeschlossen worden ist, tritt ein Verknüpfungssignal 1 auf der Rückstelleitung 116 auf. Demgemäß wird ein Analog-Signal zusammen mit einem Umsetz-Signal auf der Leitung 114 zu der Schaltung 100 geleitet. Danach wird auf der Rückstelleitung 116 ein Abschluss-Verknüpfungssignal 1 erzeugt. Der Multiplexmodul 120 ist in dem System A vorhanden, wie dies in Fig. 1 gezeigt ist. Dabei könnten verschiedene Moduln dieser Moduln dazu herangezogen werden, im Multiplexbetrieb eine grosse Anzahl von Analog-Eingangssignalen zu der Schaltung 100 zu leiten. Bei der dargestellten Ausführungsform ist der Modul 120 als Eingabemodul I angedeutet, worauf noch im Zusammenhang mit Fig. 4 im einzelnen eingegangen werden wird. Dieser Modul ist schematisch in Fig. 6A mit Analog-Eingabemodulen 122 und 124 veranschaulicht. Selbstverständlich könnten mehrere Moduln verwendet werden, um die Möglichkeiten der Analogeingabe zu steigern. Bei diesen Moduln handelt es sich stets um dieselben Moduln, die jeweils acht gesonderte Analog-Eingangsschaltungen bzw. Eingangskreise TC0-TC7 umfassen. Selbstverständlich könnte irgendein Analog-Signal einem der Eingangskreise TC0-TC7 ohne eine Änderung des Betriebs des Eingabemoduls 120 zugeführt werden. Die Eingabeleitungen oder die Eingangskreise TC0-TC7 leiten Analog-Zustandssignale zu dem Modul 120 hin. Diese Zustandssignale können durch ein Temperatursignal, ein Geschwindigkeitssignal, ein Beschleunigungssignal, ein Stellungssignal oder durch irgendein anderes Signal gebildet sein, welches von Hause aus ein Analog-Signal ist. Bezugnehmend auf Fig. 6A sei bemerkt, dass die übrigen Eingabemoduln 122, 124 parallel an den Leitungen 110, 112 angeschlossen sind, um ausgewählte Analog-Signale an die Umsetzschaltung 100 hinzuleiten, und zwar durch selektives Schliessen der Schalter 126, 128 eines Moduls. Wie in Fig. 4 angedeutet, sind lediglich die Eingangsschaltungen bei TC0 und

TC7 im einzelnen der Klarheit wegen dargestellt. In der Praxis sind jedoch acht gesonderte Eingänge bzw. Eingangsschaltungen TC0-TC7 je Analog-Eingabemodul vorgesehen.

Zurückkommend auf Fig. 6A sei bemerkt, dass im Betrieb die verschiedenen Analog-Eingangsschaltungen bzw. -Eingänge TC0-TC7 der Analog-Eingabemoduln 120, 122 und 124 mit den verschiedenen zu lesenden und in Digital-Daten für die Verwendung in dem System A umzusetzenden Analog-Signalen beaufschlagt werden. Durch eine geeignete Adresse des in Fig. 7 dargestellten Typs wird eines der Moduln 120, 122 und 124 adressiert und wirksam gemacht. Dadurch wird ein ADC-Umsetzsignal auf der Leitung 114 bereitgestellt, die von den wirksam gemachten Moduln 120, 122 oder 124 zu der Analog-Digital-Schaltung 100 verläuft. Der Eingabemodul 120 liest das aus den Datenleitungen D<sub>0</sub>-D<sub>3</sub> auftretende Verknüpfungssignal und decodiert es. Diese decodierte Information bewirkt die Auswahl eines der Analog-Eingänge TC0-TC7 und führt zur Abgabe des ausgewählten Signals über die Analog-Signalleitungen 110, 112. Nach erfolgter Beendigung der Umsetzung tritt ein Verknüpfungssignal 1 auf der Rückstelleitung 116 auf, die mit sämtlichen Moduln 120, 122 und 124 verbunden ist. Das Auftreten dieses Verknüpfungssignals führt zur Rückstellung sämtlicher Moduln für die anschliessende Auswahl und Operation. Auf diese Art und Weise können mehrere Eingabemoduln im Multiplexbetrieb mit der Umsetzschaltung 100 verbunden werden, und zwar zum Zwecke der Erzeugung von Digital-Daten, die einem ausgewählten Eingabe-Analogzustand von den adressierten Analog-Eingabemoduln her entsprechen.

Nunmehr sei auf Fig. 4 Bezug genommen, in der die bevorzugte Ausführungsform der Analog-Eingabemoduln 120, 122 und 124 schematisch in lediglich zwei Analog-Eingangskreisen TC0-TC7 veranschaulicht ist. In der Praxis kann eine grössere Anzahl von Eingabemoduln verwendet werden, und jeder Modul enthält in der Praxis acht gesonderte Analog-Eingangskreise TC0-TC7. Zum Zwecke der Beschreibung der Operation des Moduls 120 sind die beiden Eingangskreise TC0 und TC7 dargestellt; damit dürfte die Hinzufügung von weiteren Eingangskreisen parallel zu den betreffenden Eingangskreisen ersichtlich sein.

Der Modul 120 wird in Verbindung mit einem Zyklus zur Auswahl und Abgabe eines Analog-Signals an die Umsetzschaltung 100 erläutert werden. Diese Beschreibung des Betriebs des Moduls 120 wird in Verbindung mit den bei der bevorzugten Ausführungsform verwendeten Komponenten klar die erfindungsgemässen Konzepte der vorliegenden Erfindung veranschaulichen. In Fig. 7 ist eine Adresse veranschaulicht, wie sie zur Auswahl eines vorgegebenen Moduls und der Datenleitungen benutzt wird, über die eine der Schaltungen bzw. Eingangskreise TC0-TC7 ausgewählt wird. Die Adressenleitungen A<sub>0</sub>-A<sub>15</sub> werden dazu herangezogen, das Chassis auszuwählen, in welchem die Moduln 120, 122, 124 untergebracht sind, und den bestimmten Modul während eines Eingabe/Ausgabe-Befehls von dem in Fig. 1 dargestellten System A her. Die Adresse des Moduls ist durch dessen Position in bzw. auf dem Chassis bestimmt, und zwar durch die Ausnutzung der fest verdrahteten Digitaldaten, die an den verschiedenen Chassisstellen bereitgestellt werden. Dies stellt eine Eingabe/Ausgabe, d. h. eine Eingabe/Ausgabe-Adresse dar, die zu unterscheiden ist von einer Speicheradresse, welche dazu herangezogen wird, Daten von den Leitungen D<sub>0</sub>-D<sub>7</sub> zu speichern. Die Adressenleitungen A<sub>8</sub>-A<sub>10</sub>, A<sub>12</sub>, A<sub>13</sub> beziehen sich auf den Typ der Operation für die Verarbeitung von Daten, der nicht in dem Modul 120 enthalten ist. Von dem System A werden Daten über die Datenleitungen D<sub>0</sub>-D<sub>7</sub> dann abgegeben, wenn ein Schreibzyklus durch den Schreibimpuls auf der Schreibleitung R/W aktiviert ist. Eine Modul-Decodier- oder Adressierungsschaltung 130 ist an der Eingangsseite des Moduls 120 vorgesehen. Die Adresse auf den Leitungen A<sub>4</sub>-A<sub>7</sub> und A<sub>11</sub>, A<sub>14</sub>, A<sub>15</sub> führt zum

Auftreten eines Verknüpfungssignals 0 auf der  $\overline{CE}$ -Leitung 132, wenn das Chassis wirksam zu machen ist, in welchem der Modul 120 untergebracht ist. Das auf den Adressenleitungen  $A_0$ - $A_3$  auftretende Verknüpfungssignal wird mit einem fest verdrahteten Verknüpfungssignal in der Mutterkarte an der Befestigungsstelle des Moduls 120 verglichen, um ein Vergleichssignal an die Adressenschaltung 130 abzugeben. Unter der Annahme, dass die Addressierung richtig ist, tritt ein Verknüpfungssignal 1 auf der Ausgabeleitung 134 von der Addressierungsschaltung 130 her auf. Durch dieses Verknüpfungssignal wird der Modul 120 aktiviert. Ein Schreib-Verknüpfungsglied 140, bei dem es sich um NAND-Verknüpfungsglied handelt, ist mit einem ersten Eingang 142 über einen Inverter 144 an der DBINP-Leitung angeschlossen. Der zweite Eingang 146 des Verknüpfungsgliedes 140 ist über einen Inverter 148 an der Leitung R/W angeschlossen. Ein auf dieser Leitung auftretender Impuls erzeugt ein Schreibsignal für den Modul 120. Unter der Annahme, dass der Modul 120 adressiert worden ist und dass die Zentraleinheit des Systems A einen Befehl dahingehend erhalten hat, auf den Ausgabebefehl hin einen Schreibvorgang zu bearbeiten, führt die DBINP-Leitung ein Verknüpfungssignal 0. Schliesslich führt die Schreibleitung R/W wieder ein Schreibsignal, d. h. ein Verknüpfungssignal «0» für den Eingang des Inverters 148. Zu diesem Zeitpunkt führen sämtliche Eingangsleitungen des Verknüpfungsgliedes 140 ein Verknüpfungssignal 1. Demgemäß kehrt der Ausgang 150 dieses Verknüpfungsgliedes in den Verknüpfungszustand 0 über, womit ein Schreibbetrieb angezeigt ist. Der Schreibimpuls, wie er in Fig. 3 veranschaulicht ist, besitzt im allgemeinen eine Länge von 500 ns. Demgemäß wird auf der Leitung 150 ein durch ein Verknüpfungssignal 0 gebildeter Schreibimpuls mit einer Dauer von 500 ns erzeugt. Ein Inverter 152 verbindet die Leitung 150 mit der Leitung 154 an dem Taktanschluss 2A einer monostabilen Einrichtung 160. Diese Einrichtung besitzt eine bekannte Zeitverzögerung von 2,3 ms, wie dies durch die Vorspannungsschaltungen festgelegt ist. Ein positiver Spannungssprung auf der Leitung 154 bewirkt das Auftreten eines positiven Impulses an dem Q-Anschluss der Leitung 162 der monostabilen Einrichtung 160. Dadurch wird ein Verknüpfungsimpuls 1 mit einer Dauer von 2,3 ms dem einen Eingang des NAND-Gliedes 164 zugeführt. Der Ausgang dieses Verknüpfungsgliedes ist mit der ADC-Leitung 114 verbunden. Soweit beschrieben, tritt auf der Leitung 170 kein Auswahlsignal auf. Demgemäß ist das Ausgangssignal des Verknüpfungsgliedes 164 ein Verknüpfungssignal 1, welches nicht umgeschaltet worden ist, um die Schaltung 100 auszulösen bzw. zu betätigen.

Über die Schreibleitung 150 wird ausserdem das Verknüpfungsglied 180 gesteuert. Ein an diesem Eingang des Verknüpfungsgliedes 180, bei dem es sich um ein NAND-Glied handelt, auftretendes Verknüpfungssignal 0 führt zur Abgabe eines Verknüpfungssignals 1 auf der Ausgangsleitung bzw. Ausgabeleitung 182. Dieses Verknüpfungssignal 1 wird durch den Inverter 184 invertiert und führt zur Abgabe eines Verknüpfungssignals 0 auf der Leitung 186, die mit dem negativen Taktanschluss 1A einer monostabilen Einrichtung 190 verbunden ist. Diese monostabile Einrichtung gibt einen negativen Impuls mit einer Dauer von 100 ns an dem mit der Leitung 192 verbundenen Ausgangsanschluss  $\bar{Q}$  ab. Wenn somit ein Schreibsignal auf der Leitung 150 vorhanden ist, wird ein auf der Leitung 192 auftretender negativer 100-ns-Impuls einem NAND-Glied 200 zugeführt, welches einen Rückstell-Eingang besitzt. Die System-Rückstell-Leitung führt während des Betriebs des Systems A ein Verknüpfungssignal 1. Demgemäß bewirkt ein auf der Leitung 192 auftretendes Verknüpfungssignal 0 die Abgabe eines Verknüpfungsimpulses 1 mit einer Dauer von 100 ns vom Ausgang 202 des Verknüpfungsgliedes 100. Der Inverter 204 invertiert dieses Verknüpfungssignal und liefert einen Verknüpfungsimpuls 0 an die Löschleitung 206, die mit dem Löschanschluss CL eines

herkömmlichen adressierbaren 8-Bit-Verriegelungsdecoders 210 verbunden ist. Dieser Decoder wird gelöscht, um während des Auftretens eines Löschimpulses auf der Leitung 206 an sämtlichen Ausgangsanschlüssen 0-7 Nullen zu erzeugen. Das auf der Datenleitung  $D_3$  auftretende Verknüpfungssignal steuert den Decoder 210. Ein an dem Anschluss E auftretendes Verknüpfungssignal 0 verhindert das Auftreten eines Auswahl-Verknüpfungssignals an irgendeinem Anschluss 0-7. Der Anschluss  $\bar{E}$  des Verriegelungsdecoders 210 dient zur Verriegelung bzw. zum Festhalten eines Verknüpfungssignals 1 an einem der Ausgangs- bzw. Ausgabeanschlüsse 0-7, und zwar in Übereinstimmung mit dem binären Verknüpfungssignal auf den Eingabeleitungen  $D_0$ ,  $D_1$  und  $D_2$ , die mit den Eingangsanschlüssen a, b bzw. c des Verriegelungsdecoders 120 verbunden sind. Dabei ist angenommen, dass das Verknüpfungssignal auf der Leitung  $D_3$  in Verknüpfungssignal 0 ist. Wenn auf der Leitung 150 ein Schreibimpuls mit einer Dauer von etwa 500 ns auftritt, wird der Verriegelungsdecoder 210 verriegelt, um das Verknüpfungssignal auf den Leitungen  $D_0$ - $D_2$  zu decodieren. Der Löschanchluss CL führt jedoch zu einem Überlaufen bzw. Übersteuern des Verriegelungsanschlusses  $\bar{E}$  während des Auftretens des 100-ns-Löschimpulses auf der Leitung 206. Dieses Konzept ist in Fig. 8 und 9 veranschaulicht. Wenn demgemäß eine Adresse, wie sie in Fig. 7 veranschaulicht ist, auftritt und wenn die Zentraleinheit ein Schreibsignal erzeugt, wird der Verriegelungsdecoder 210 zunächst gelöscht. Während dieses selben Schreibsignals wird ein Verknüpfungssignal 1 an einem der Ausgabeanschlüsse 0-7 des Decoders 210 festgehalten bzw. verriegelt. Der ausgewählte Anschluss ist dabei durch eine 1-aus-8-Decodierung des Verknüpfungssignals auf den Leitungen  $\bar{D}_0$ - $\bar{D}_2$  festgelegt. Diese Verriegelung eines Anschlusses führt zur Betätigung bzw. zum Wirksamwerden einer der Eingangskreise TC0-TC7. Bei dieser dargestellten Ausführungsform sind lediglich die Eingangskreise TC0 und TC7 veranschaulicht. Demgemäß sind lediglich die Anschlüsse 0 und 7 am Ausgang des Decoders 210 dargestellt. Die Auswahlleitung 220 ist an dem Ausgangsanschluss 0 angeschlossen, und die Leitung 222 ist an dem Ausgangsanschluss 7 angeschlossen. Die Inverter 224, 226 inertieren das auf den Leitungen 220 bzw. 222 auftretende Verknüpfungssignal, um entgegengesetzte Verknüpfungssignale auf den Leitungen 230 bzw. 232 zu erzeugen. Diese zuletzt genannten Leitungen, von denen bei der bevorzugten Ausführungsform acht Leitungen verwendet sind, sind an dem Eingang eines Auswahl-NAND-Gliedes 240 angeschlossen. Das auf der Datenleitung  $D_3$  während einer Modulaadressierung auftretende Verknüpfungssignal steuert die Gesamtoperation des Verriegelungsdecoders 210. Wenn die Leitung  $D_3$  ein Verknüpfungssignal 0 führt, führt die Leitung  $\bar{D}_3$ , bei der es sich um die Datenleitung des Systems A handelt, am Anschluss D des Verriegelungsdecoders 210 ein Verknüpfungssignal 1. Dadurch wird das Verknüpfungsglied 210 freigegeben, ein Verknüpfungssignal 1 an einem seiner Ausgänge zu speichern. Im Zuge dieser Erläuterung der bevorzugten Ausführungsform des Moduls 120 ist angenommen, dass der Decoder 210 durch ein Verknüpfungssignal 1 an dem Anschluss E freigegeben ist.

Wenn keine der Schaltungen am Ausgang des Verriegelungsdecoders 210 in dem Modul 120 unwirksam zu machen ist, wird das Verknüpfungssignal auf den Leitungen  $\bar{D}_3$  zu einem Verknüpfungssignal 0 gemacht, um ein Verknüpfungssignal 0 an dem ausgewählten Ausgang des Decoders 210 zu erzeugen. Ein an sämtlichen Ausgangsanschlüssen des Verriegelungsdecoders 210 jeweils auftretendes Verknüpfungssignal 0 führt zur Erzeugung eines Verknüpfungssignals 1 an sämtlichen Eingängen des Auswahl-Verknüpfungsgliedes 240 und eines Verknüpfungssignals 0 auf einer Auswahlleitung 170. Dieses Verknüpfungssignal 0 wird ausserdem während des Löscheinzyklus des Decoders 210 erzeugt. Wenn einer der Ausgangsanschlüsse

0-7 während eines Schreibbefehls durch das decodierte Verknüpfungssignal der Leitungen  $\bar{D}_0$ - $\bar{D}_2$  ausgewählt worden ist, geht der Zustand der Auswahlleitung 170 über zu einem Verknüpfungssignal 1. Dieses Verknüpfungssignal führt in Verknüpfung mit dem Verknüpfungssignal auf der Leitung 162 zur Erzeugung eines negativen Impulses auf der ADC-Leitung 114. Dadurch wird schliesslich die Umsetzschaltung 100 veranlasst, das Analog-Signal zwischen den Leitungen 110, 112 in einen Digital-Ausgabecode umzuwandeln, und zwar in einer nachstehend noch näher zu beschreibenden Art und Weise.

Über die Auswahlleitung 170 wird ferner ein Inverter 250 gesteuert, durch den ein Verknüpfungssignal 0 auf der Leitung 252 dann erzeugt wird, wenn eine Auswahl durch den Decoder 210 erfolgt ist. Dieses Verknüpfungssignal 0 hält das Auftreten eines Verknüpfungssignals 1 auf der Leitung 182 auch dann aufrecht, wenn der Schreibimpuls auf der Leitung 150 schliesslich während des Bearbeitungszyklus verschwindet. Demgemäß wird während eines einzigen Schreibbefehls die monostabile Einrichtung 190 an einen von der Leitung 186 her gesteuerten negativen Anschluss 1A nicht wieder getaktet.

Wenn der Verknüpfungszustand auf der Leitung 170 während des Auftretens einer Schreibadresse in einen Auswahl-Verknüpfungszustand 1 übergeht, bewirkt dieser Verknüpfungszustand bzw. dieses Verknüpfungssignal 1 die Freigabe der beiden Transistorschalter 126, 128 in dem Schaltkreis 260. Demgemäß werden die Schalter 126, 128 des Moduls 120 geschlossen, wodurch der ausgewählte Analogzustand von dem Modul 120 her zu dem Eingang der Umsetzschaltung 100 durchgeschaltet wird. Um ein Analogsignal für die Verwendung auf den Leitungen 110, 112 zu erhalten, sind Relaissteuerernetzwerke 300, 302 vorgesehen. Das Netzwerk 300 steuert die Schaltungseingangsschalter CRO<sub>a</sub>, CRO<sub>b</sub>, CR7<sub>a</sub> und CR7<sub>b</sub>. Das Netzwerk 302 steuert die Ausgangs- bzw. Ausgabeschalter CR10<sub>a</sub>, CR10<sub>b</sub>, CR17<sub>a</sub> und CR17<sub>b</sub>. Die Übertragung von Analog-Daten an die Leitungen 110, 112 von einer ausgewählten Schaltung der Schaltungen TR0, TC7 wird durch die Operation der Relaissteuerernetzwerke bestimmt. Bei der dargestellten Ausführungsform sind lediglich zwei Eingangsschaltungen dargestellt. Jede dieser Schaltungen 300, 302 enthält lediglich zwei Relaissteuerschaltungen. In der Praxis werden jedoch acht gesonderte Eingangsschaltungen verwendet, und jedes der Netzwerke 300, 302 enthält acht gesonderte Relaischaltungen. Im Hinblick auf das Netzwerk 300 sei angemerkt, dass dieses Netzwerk dazu herangezogen wird, einen ausgewählten Satz von Eingabeschaltern CRO<sub>a</sub>, CRO<sub>b</sub>, CR7<sub>a</sub> und CR7<sub>b</sub> in den Eingangsschaltungen TC0, TC7 zu öffnen. Die Relaischaltung 310 öffnet auf ihre Speisung hin die relaisgesteuerten Schalter CR0<sub>a</sub>, CR0<sub>b</sub> in der Eingangsschaltung TC0. Die Relaischaltung 312 öffnet auf entsprechende Speisung hin die Kontakte CR7<sub>a</sub>, CR7<sub>b</sub>. Wenn eine bestimmte Analog-Eingangsschaltung TC0, TC7 durch den Verriegelungsdecoder 210 ausgewählt ist, tritt demgemäß ein Verknüpfungssignal 0 an der Eingangsseite eines der Inverter 314, 316 auf. Dadurch tritt ein Verknüpfungssignal 0 am Ausgang des betreffenden Inverters und am Eingang einer der Schaltungen 310 bzw. 312 auf.

Die Schaltungen 310, 312 sind an der +12-V-Leitung 318 angeschlossen. Bei der ausgewählten Schaltung TC0 oder TC7 schaltet demgemäß ein Verknüpfungssignal 1 eine der Relaischaltungen 310, 312 aus. Da die Schalter der Relaischaltungen durch ein Verknüpfungssignal 0 oder durch das Fehlen eines Auswahlzustandes an den Invertern 314, 316 geschlossen gehalten werden, öffnen die Eingangsschalter, die durch die unwirksam gemachte Relaischaltung gesteuert sind. Im Hinblick auf die in der Praxis verwendeten und in Fig. 4 schematisch angedeuteten Relaischaltungen sei angemerkt, dass lediglich eine Relaischaltung des Netzwerks 300 unwirksam gemacht werden wird. Die übrigen Relaischaltungen bleiben wirksam, um die Eingangskontakte der nicht ausgewählten

Schaltung TC0-TC7 im geschlossenen Zustand zu halten.

Die Relaischaltungen 320, 322 des Netzwerks 302 speisen die ausgewählte Relaischaltung anstatt des Unwirksamchens der ausgewählten Relaischaltung. Die Inverter 324, 326 invertieren das auf den Leitungen 320 bzw. 322 auftretende Verknüpfungssignal. Demgemäß erzeugen die durch den Verriegelungsdecoder 210 ausgewählten Analogzustände ein Verknüpfungssignal 0 am Ausgang eines der Inverter 324, 326. Dieses Verknüpfungssignal 0 führt zur Aktivierung der ausgewählten Relaischaltungen 320, 322 und bewirkt das Schliessen der Ausgangs- bzw. Ausgabeschalter CR10<sub>a</sub>, CR10<sub>b</sub> oder der Ausgangs- bzw. Ausgabeschalter CR17<sub>a</sub>, CR17<sub>b</sub>. Die Kondensatoren 340 der Schaltungen TC0, TC7 werden auf die durch das Thermoelement oder durch die anderen, durch Wandler gesteuerten Schaltungen TC0, TC7 bestimmte Spannung aufgeladen. Wenn einer der Analogzustände ausgewählt ist, werden die Eingabeschalter geöffnet, indem eine der Relaischaltungen 310, 312 unwirksam bzw. aberregt wird. In entsprechender Weise werden die Ausgabeschalter der ausgewählten Schaltung geschlossen, indem eine entsprechende Relaischaltung der Relaischaltungen 320, 322 gespeist bzw. erregt wird.

Die auf dem Kondensator 340 der Eingangsschaltung TC0 gespeicherte Spannung wird selektiv an die Leitungen 342, 344 abgegeben, wenn die Schalter CR10<sub>a</sub>, CR10<sub>b</sub> geschlossen werden. Die Ausgabeleitungen 342, 344 sind parallel mit den Leitungen 350, 352 verbunden, die die Eingangsleitungen der Signalerzeugungsschaltung SC des Moduls 120 darstellen. Über die Ausgabeschalter CR17<sub>a</sub>, CR17<sub>b</sub> wird die auf dem Kondensator 360 der Eingangsschaltung TC7 gespeicherte Spannung an die Leitungen 350, 352 an der Signalerzeugungsschaltung SC angeschlossen. Die übrigen sechs Schaltungen sind bei Auswahl durch den Decoder 210 ebenfalls an den Leitungen 350, 352 angeschlossen.