(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-133351

(P2007-133351A)

(43) 公開日 平成19年5月31日(2007.5.31)

|                                      |                              |                                                     |

|--------------------------------------|------------------------------|-----------------------------------------------------|

| (51) Int.CI.                         | F 1                          | テーマコード (参考)                                         |

| <b>G09G 3/30</b>                     | <b>(2006.01)</b>             | G 09 G 3/30 J 5 C 08 O                              |

| <b>G09G 3/20</b>                     | <b>(2006.01)</b>             | G 09 G 3/20 6 4 1 D                                 |

|                                      |                              | G 09 G 3/20 6 2 4 B                                 |

|                                      |                              | G 09 G 3/20 6 2 1 A                                 |

|                                      |                              | G 09 G 3/20 6 4 2 P                                 |

| 審査請求 未請求 請求項の数 9 O L (全 22 頁) 最終頁に続く |                              |                                                     |

| (21) 出願番号                            | 特願2006-97995 (P2006-97995)   | (71) 出願人 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日                             | 平成18年3月31日 (2006.3.31)       | (74) 代理人 100090538<br>弁理士 西山 恵三                     |

| (31) 優先権主張番号                         | 特願2005-297639 (P2005-297639) | (74) 代理人 100096965<br>弁理士 内尾 裕一                     |

| (32) 優先日                             | 平成17年10月12日 (2005.10.12)     | (72) 発明者 郷田 達人<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

| (33) 優先権主張国                          | 日本国 (JP)                     | (72) 発明者 中村 恒一<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内    |

最終頁に続く

(54) 【発明の名称】表示装置、アクティブマトリクス装置およびそれらの駆動方法

## (57) 【要約】

【課題】 E-L素子などの電気光学素子に流れる電流のばらつきを抑制し、輝度ばらつきを低減させる。

【解決手段】 表示装置は、電気光学素子に電流を供給するための画素回路2が行方向および列方向にマトリクス状に複数配置された画像表示部9と、画像表示部9の行毎に共通に接続された複数の行選択線20と、画像表示部9に列毎に共通に接続された複数のデータ線14と、画像表示部9の列数に応じて配置され、かつ、入力される映像信号をデータ信号に変換して複数のデータ線14に列毎に同時に outputする複数の列駆動回路1と、を有し、列駆動回路1の出力先となるデータ線14を選択する選択手段34と、列駆動回路1のデータ信号出力先となるデータ線14を単位水平走査期間毎に順次変更するよう、選択手段34を制御する制御手段35と、を有する。

【選択図】 図6

**【特許請求の範囲】****【請求項 1】**

複数の電気光学素子を有する画素がマトリクス状に配置された表示部と、

前記表示部の行毎に共通に接続された複数の行選択線と、

前記表示部に列毎に共通に接続された複数のデータ線と、

前記表示部の列に対応して設けられ、入力される映像信号を前記画素に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

を有する表示装置において、

前記列駆動回路の出力先となるデータ線を選択するための選択回路と、

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更するように、前記選択回路を制御する制御回路と、

を有することを特徴とする表示装置。

10

**【請求項 2】**

前記複数の列駆動回路の出力を検出し、検出結果に基づいて前記列駆動回路に入力される映像信号を複数の列毎に補正する補正手段をさらに有することを特徴とする請求項1に記載の表示装置。

**【請求項 3】**

前記電気光学素子は、エレクトロルミネセンス素子であることを特徴とする請求項1または2に記載の表示装置。

**【請求項 4】**

共通のデータ線に接続された隣接行の画素には、1フレーム走査期間内に同じ列駆動回路からの出力が供給されないように、インターレース走査により行を選択することを特徴とする請求項1乃至3に記載の表示装置。

20

**【請求項 5】**

3水平走査期間毎に、少なくとも3つの前記列駆動回路の出力先が3色の画素のデータ線となるように、前記選択回路を制御する請求項1乃至4のいずれか1項に記載の表示装置。

**【請求項 6】**

複数の画素回路がマトリクス状に配置されたマトリクス回路部と、

前記マトリクス回路部の行毎に共通に接続された複数の行選択線と、

前記マトリクス回路部に列毎に共通に接続された複数のデータ線と、

前記マトリクス回路部の列に対応して設けられ、入力される映像信号を前記画素回路に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

を有するアクティブマトリクス装置において、

前記列駆動回路の出力先となるデータ線を選択するための選択回路と、

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更するように、前記選択回路を制御する制御回路と、

を有することを特徴とするアクティブマトリクス装置。

30

**【請求項 7】**

複数の電気光学素子を有する画素がマトリクス状に配置された表示部と、

前記表示部の行毎に共通に接続された複数の行選択線と、

前記表示部に列毎に共通に接続された複数のデータ線と、

前記表示部の列に対応して設けられ、入力される映像信号を前記画素に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

を有する表示装置の駆動方法において、

前記列駆動回路の出力先となるデータ線を選択する工程と、

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更する工程と、

を含むことを特徴とする表示装置の駆動方法。

40

50

**【請求項 8】**

共通のデータ線に接続された隣接行の画素には、1フレーム走査期間内に同じ列駆動回路からの出力が供給されないように、インターレース走査により行を選択する工程を含むことを特徴とする請求項7に記載の表示装置の駆動方法。

**【請求項 9】**

複数の画素回路がマトリクス状に配置されたマトリクス回路部と、

前記マトリクス回路部の行毎に共通に接続された複数の行選択線と、

前記マトリクス回路部に列毎に共通に接続された複数のデータ線と、

前記マトリクス回路部の列に対応して設けられ、入力される映像信号を前記画素回路に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

10 を有するアクティブマトリクス装置の駆動方法において、

前記列駆動回路の出力先となるデータ線を選択する工程と、

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更する工程と、

を含むことを特徴とするアクティブマトリクス装置の駆動方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、電気光学素子又は画素回路をマトリクス状に配置した表示装置及びアクティブマトリクス装置と、それらの駆動方法に関する。 20

**【背景技術】****【0002】**

近年、次世代ディスプレイとして電気光学素子を用いたディスプレイ等が注目されている。ここでは、素子に流れる電流によって発光輝度が制御される電流制御型の発光素子である有機エレクトロルミネッセンス(EL)素子を例に挙げて説明する。

**【0003】**

周辺回路を含んだ有機ELディスプレイでは、表示領域に限らず、周辺回路においても薄膜トランジスタ(TFT)が用いられている。このような自発光素子であるEL素子を画像表示素子に利用し、その表示領域および周辺回路にTFTを用いた画像表示パネルについて、以下、図面を参照して説明する。 30

**【0004】**

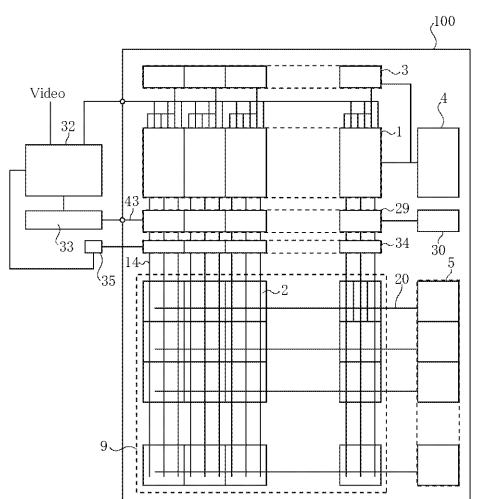

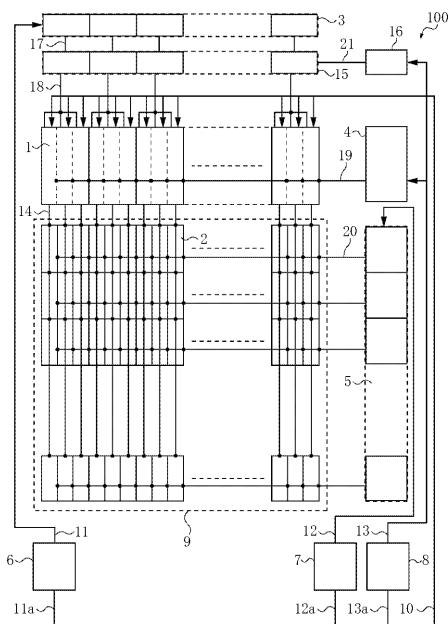

図16に示すELパネル100には、RGB原色数のEL素子と、このEL素子に入力される電流を制御するためのTFTから構成される画素(画素回路)2とがN列×M行の2次元状に配列された画素表示部9と、その周辺回路とが配置される。周辺回路のうち、入力回路6には、外部より水平走査制御信号11aが入力される。また、入力回路7には、外部より垂直走査制御信号12aが入力される。さらに、入力回路8には、外部より補助列制御信号13aが入力される。

**【0005】**

入力回路6にて変換された水平走査制御信号11(水平クロック信号と水平走査開始信号)は、列シフトレジスタ3に入力される。また、入力回路7にて変換された垂直走査制御信号12は、行シフトレジスタ5に入力される。行シフトレジスタ5の各出力端子から出力された行走査信号は、行選択線20としての走査線を介して各行の画素回路2に入力される。 40

**【0006】**

また、入力回路8にて変換された補助列制御信号13は、ゲート回路4、16にそれぞれ入力される。水平シフトレジスタ3の各端子から出力される水平サンプリング信号17は、ゲート回路16にて変換された制御信号21と共に、水平サンプリング信号ゲート回路15に入力される。水平サンプリング信号ゲート回路15にて変換される水平サンプリング信号18は、外部より入力された映像信号(電圧信号)10と、ゲート回路4にて変 50

換された制御信号 19と共に、列駆動回路 1に入力される。列駆動回路 1にて映像信号から変換された電流信号である列制御信号 14は、データ線を介して各列の画素回路 2に入力される。

#### 【0007】

列駆動回路 1は、画素回路 2の各列の原色数（例えば、赤、緑、青の3色）に応じて複数配置され、各原色数の入力映像信号 10に対応するように構成される。この列駆動回路 1は、1画素毎の時系列に入力される点順次電圧映像信号を行単位で同時に出力可能な線順次電流映像信号に変換する電圧電流変換回路を用いている。

#### 【0008】

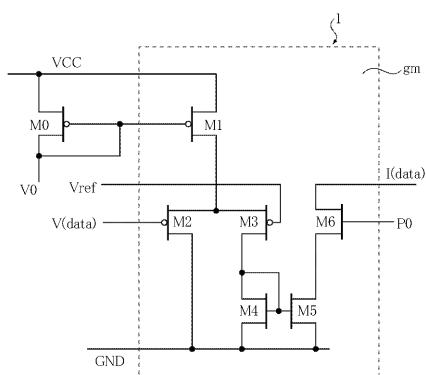

図 17は、列駆動回路 1に用いられる電圧電流変換回路の構成例である。

10

#### 【0009】

図 17において、gmは電圧電流変換回路、M0乃至M3はpチャンネル型 TFT、M4乃至M6はnチャンネル型 TFT、V(data)は電圧電流変換回路 gmに入力される映像信号電圧、I(data)は電圧電流変換回路 gmからデータ線に出力される電流信号（データ信号）、VCCは電源、V0は基準電流バイアス値、Vrefは基準電圧、P0は制御信号である。M2とM3はソース結合回路、M4とM5はカレントミラー回路を構成する。

#### 【0010】

図 17に示す電圧電流変換回路 gmにおいて、映像信号電圧 V(data)が TFT (M2) のゲート G に入力される。すると、TFT (M1) のドレイン電流を基準電流として、ソース結合回路、カレントミラー回路を介して、映像信号電圧 V(data) の電圧値に応じた電流値をもつ電流信号 I(data) が生成され、データ線に出力される。

20

#### 【0011】

この回路では、電圧電流変換ゲインは、M0とM1、M2とM3、M4とM5の各々で互いに相関性がある場合、M1のドレイン電流と、M2、M3の駆動能力によって決定される。なお、列駆動回路 1の他の回路構成や駆動方法は、特許文献 1に記載の図 1、図 2に示されている。

#### 【0012】

しかしながら、上記 TFT は、非単結晶半導体を活性層に用いているため、その特性上、単結晶を活性層に用いたトランジスタに比べて素子間のばらつきが大きく、近接的にもばらつきに相関性が保証できない。TFT の閾値やキャリア移動度等のばらつきにより、列駆動回路の電圧電流変換ゲインが素子間で異なると、EL 素子に供給される電流値が画素間でばらつく。そうすると、EL 素子が所望の輝度で発光することができない。その結果、表示領域において輝度のばらつきとなって表れる。

30

#### 【0013】

そのため、特許文献 2には、輝度ばらつきを抑制するための回路構成が記載されている。この回路構成によれば、画素回路を駆動する列駆動回路の出力電流を検出して基準電流データと比較して補正係数を演算し、その補正係数を用いて列駆動回路へ入力される映像信号を補正して輝度ばらつきを軽減している。

40

【特許文献 1】特開 2004-145296 号公報

【特許文献 2】特開 2004-295081 号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0014】

しかしながら、特許文献 2に記載されているような、列駆動回路の出力電流を検出して補正をする方法では、画素密度が増え、列駆動回路の出力が小さくなる場合には、充分な S/N 比をもつ検出信号が得られないことがある。また、列駆動回路の数が増えるにつれて、検出に費やす時間及び補正処理に費やす時間が無視できなくなる。

#### 【0015】

また、特許文献 1に記載されているような、従来の表示装置においては、1つの列駆動

50

回路の電流出力先は、1フレーム走査期間中常に同じデータ線である。つまり、1つの列駆動回路の電流出力先は、1フレーム走査期間中常に同じ列の画素回路2に入力される。

#### 【0016】

従って、電気光学素子や画素回路にはらつきが全く無いものと仮定した場合、全画素に同じ輝度レベルの1フレームの表示画像信号を入力し、これを表示したときに、列毎に輝度がばらつくことがある。

#### 【0017】

本発明は、複数列のEL素子などの電気光学素子に流れる電流のはらつきを時間的に平均化することで、輝度ばらつきを低減させる表示装置およびその駆動方法を提供することを目的とする。

10

#### 【課題を解決するための手段】

#### 【0018】

上記目的を達成するため、本発明に係る表示装置は、複数の電気光学素子を有する画素がマトリクス状に配置された表示部と、

前記表示部の行毎に共通に接続された複数の行選択線と、

前記表示部に列毎に共通に接続された複数のデータ線と、

前記表示部の列に対応して設けられ、入力される映像信号を前記画素に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

を有する表示装置において、

前記列駆動回路の出力先となるデータ線を選択するための選択回路と、

20

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更するように、前記選択回路を制御する制御回路と、

を有することを特徴とする。

#### 【0019】

本発明に係わるアクティブマトリクス装置は、複数の画素回路がマトリクス状に配置されたマトリクス回路部と、

前記マトリクス回路部の行毎に共通に接続された複数の行選択線と、

前記マトリクス回路部に列毎に共通に接続された複数のデータ線と、

前記マトリクス回路部の列に対応して設けられ、入力される映像信号を前記画素回路に供給されるデータ信号に変換して前記複数のデータ線に行毎に同時に出力する複数の列駆動回路と、

30

を有するアクティブマトリクス装置において、

前記列駆動回路の出力先となるデータ線を選択するための選択回路と、

前記列駆動回路の出力先となるデータ線を一垂直走査期間より短い単位水平走査期間毎に順次変更するように、前記選択回路を制御する制御回路と、

を有することを特徴とする。

#### 【0020】

本発明において、前記画素回路は、前記映像信号の表示色を決める3つの原色画素に対応して配置され、前記複数のデータ線は、前記3つの原色画素に対応する列に配置される3つのデータ線を有し、前記複数の列駆動回路は、3つの列駆動回路であり、前記選択手段は、前記3つの原色画素のうち任意の原色画素に対応する列に配置されたデータ線に対して前記3つの列駆動回路のうち1つの列駆動回路からのデータ信号を出力可能に選択する手段であってもよい。

40

#### 【0021】

本発明において、前記複数の列駆動回路の総和出力電流を検出し、検出された前記総和出力電流に基づいて前記列駆動回路に入力される映像信号を列毎に補正する補正手段をさらに有してもよい。前記電流制御型表示素子は、エレクトロルミネセンス素子であってもよい。

#### 【0022】

本発明においては、共通のデータ線に接続された隣接行の画素回路には、1フレーム走

50

査期間内に同じ列駆動回路からの出力が供給されないように、インターレース走査により行を選択することも好ましいものである。

#### 【0023】

また、本発明においては、3単位水平ライン周期で、少なくとも3つの前記列駆動回路の前記データ信号出力先が3色のデータ線となるように、前記選択手段を制御することも好ましいものである。

#### 【0024】

本発明に係る表示装置及びアクティブマトリクス装置の駆動方法は、

前記列駆動回路の出力先となるデータ線を選択する工程と、

前記列駆動回路のデータ信号出力先となるデータ線を一垂直走査期間より短い単位水平

ライン周期で順次変更する工程と、

を含むことを特徴とする。

10

#### 【発明の効果】

#### 【0025】

本発明によれば、列駆動回路の出力先のデータ線を順次変更しながら、その出力を画素

或いは画素回路に供給するように構成する。こうして、画素或いは画素回路に供給される

電流の値のばらつきを時間的に平均化、換言すれば空間的に分散させることができる。よ

って、画面に現れる縦筋のような、表示画像の不均一性を視覚的に低減できる。

#### 【発明を実施するための最良の形態】

#### 【0026】

以下、本発明に係る表示装置或いはアクティブマトリクス装置を実施するための最良の

形態について、図面を参照して具体的に説明する。

#### 【0027】

本発明に用いられる電気光学素子としては、有機EL素子、無機EL素子、電子放出素

子を用いた発光素子、発光ダイオードなどが挙げられる。

#### 【0028】

画素は、上記電気光学素子からなるパッシブマトリクス回路であってもよく、或いは、

画素は、少なくとも1つのトランジスタを有するアクティブマトリクス回路を構成してい

てもよい。

#### 【0029】

本発明に用いられる列駆動回路は、映像信号をデータ信号に変換する回路が好ましく用

いられる。映像信号としては、アナログ電圧信号、デジタル信号などが好適に用いられる

。データ信号としては、画素の輝度を決定するためのアナログ電流信号が好ましく用いられ

れる。

#### 【0030】

そして、列駆動回路は、パッシブマトリクス回路を構成する電気光学素子に供給される

データ信号を供給する回路、或いは、アクティブマトリクス回路を構成する画素回路に供

給されるデータ信号を供給する回路となる。

#### 【0031】

列駆動回路を構成する電圧電流変換回路は、一列に1個設けられる場合以外に、一列に

2個づつ設けられ、1水平走査期間毎に切り替えて用いられてもよい。或いは、4つの列

駆動回路を3列のデータ線毎に設け、そのうち、2つの列駆動回路を一つのデータ線に接

続する構成であってもよい。

#### 【0032】

本発明は、列駆動回路を構成するトランジスタに製造プロセスに起因する特性ばらつき

が生じやすい回路に有效地に働くため、非単結晶半導体を活性層に用いたTFTにて構成さ

れた列駆動回路に好適に用いられる。非単結晶半導体とは非晶質シリコン、多結晶シリコ

ン、微結晶シリコンである。或いは、単結晶シリコンのような単結晶半導体を活性層に用

いたトランジスタであっても、特性ばらつきが無視し得ない回路であれば、本発明が適用

可能である。

## 【0033】

本発明のデータ信号は、マトリクス回路の画素又は画素回路のうち同じ行選択線により選択可能な同一行の画素又は画素回路に同時に供給される。この行選択期間は水平走査期間に相当し、全ての行を順次選択することで1フレーム走査期間におけるデータ信号の出力が完了する。

## 【0034】

本発明においては、列駆動回路の出力先となるデータ線を単位水平走査期間毎に順次変更する。ここで単位水平走査期間とは1水平走査期間或いは2乃至3水平走査期間ように、所定の水平走査期間であればよいが、好ましくは1水平走査期間であることが望まれる。

10

## 【0035】

本発明は、電気光学素子を用いたマトリクス型表示装置に適用されているが、EL素子のような電気光学素子を形成する前のアクティブマトリクス装置にも好ましく用いられる。

## 【0036】

本実施形態に係る表示装置は、電気光学素子およびTFTを含む画素回路がマトリクス状に配置された表示部（アクティブマトリクス部）を有する。そして、データ線にデータ信号を出力するデータ線駆動回路と、行選択線（走査線）に走査信号を出力する走査線駆動回路とを有する。また、映像信号や制御信号の入力、および電源供給を行う端子部と、各画素の電気光学素子と接続された共通配線と、を有する。共通配線は、表示領域の周辺を囲んで配置されており、配線引出部から配線を引いて端子部の一部と接続される。

20

## 【0037】

本発明においては、必要に応じて、複数の列駆動回路の出力電流を検出し、それを評価して、当該複数の列駆動回路へ入力される映像信号を補正する補正回路を有することも好ましいものである。

## 【0038】

また、本発明においては、列駆動回路の出力先が単位水平走査期間毎に変更されるため、列駆動回路に入力される映像信号は、その変更を考慮してサンプリングされるか、映像信号の供給順序を列単位で並び替える必要がある。具体的には、列駆動回路への入力サンプリングを制御するか、映像信号を供給する回路（補正回路）側で供給順序を列単位で並び替える制御を行えばよい。

30

## 【0039】

本実施形態によれば、列駆動回路の出力先のデータ線を順次変更し、電気光学素子に供給される電流の値のばらつきを時間的に平均化する。換言すれば、空間的にばらつきを分散することで、表示画像の不均一性を視覚的に低減できる。

## 【0040】

そして、列駆動回路の出力先のデータ線を変更する周期を一垂直走査期間より短い単位水平走査期間毎とする。垂直走査期間とは一フィールド走査期間または一フレーム走査期間である。即ち単位水平ライン周期として、単位フレーム周期と比較して、出力先のデータ線を変更する周期が短いため、視覚的な画素間ばらつきをさらに低減できる。

40

## 【0041】

（第1の実施形態）

図1は、第1の実施形態による表示装置の構成を示す模式図である。

## 【0042】

なお、前述した図16に示す従来例と同様の構成要素については、同一符号を付している。また、図16で記載した入力回路6、7、8については省略している。

## 【0043】

図1に示す表示装置は、表示パネル100を有する。表示パネル100の共通基板には、RGB原色数のEL素子と、このEL素子に入力される電流を制御するためのTFTから構成される画素回路2とがN列×M行の2次元状に配列された画像表示部9と、周辺回

50

路とが配置される。周辺回路には、前述した図16に示す従来例と同様の列駆動回路1、列シフトレジスタ3、行シフトレジスタ5、ゲート回路4を備える。その他、本実施形態では、列駆動回路1と画素回路2の間に、列駆動回路1より出力された電流信号を総和電流として出力する総和電流出力回路29と、本発明の主要部を構成する選択回路34とを備える。総和電流出力回路1の制御信号入力側には、ゲート回路30が接続される。総和電流出力回路1の出力側には、総和電流を検出する総和電流検出回路33が接続される。総和電流検出回路33の出力側には、検出された総和電流が入力される補正回路32が接続される。映像信号電圧Videoは、補正回路32を介して列駆動回路1に入力される。

## 【0044】

上記構成のうち、選択回路34及び制御回路35以外の回路、即ち列駆動回路1、画素回路2、総和電流出力回路29、補正回路32については、前述した特許文献1、2等の先行技術文献に開示されている回路構成を適用可能である。

## 【0045】

まず、前述した列駆動回路以外の各回路の構成および動作について順次説明する。

## 【0046】

(総和電流出力回路)

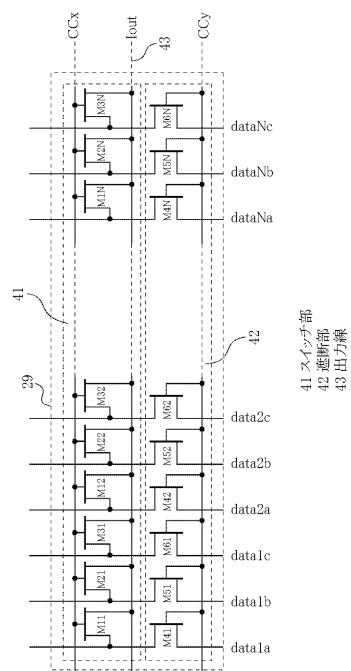

図2は、本実施例の総和電流出力回路29の回路構成例を示す。

## 【0047】

図中、43は列駆動回路1の出力が共通に接続される電流信号出力線、41は列駆動回路1の出力と電流信号出力線43との接続関係を制御するスイッチ部、42は列駆動回路1と画素側との接続関係を制御するスイッチ部である遮断部、data1a乃至dataNcはデータ線、M11乃至M3N、M41乃至M6NはスイッチとしてのTFT、Ioutは総和電流、CCx, CCyは総和電流検出用制御信号である。

## 【0048】

総和電流出力回路29より総和電流を出力して映像信号の補正を行うには、通常の動作期間の前に補正期間を設ける。この補正期間において、総和電流出力回路29のスイッチ部41のM11乃至M3NをCCxにより全てオンにし、遮断部42のM41乃至M6NをCCyにより全てオフとする。以上の動作により、列駆動回路1から出力された電流信号は、画素回路2には流れず、全て出力線43より出力される。

## 【0049】

そして、R、G、Bの3列のスイッチM11、M21、M31に対応する列駆動回路に検出用の所定の明レベルの入力電圧を与え、他の全列の列駆動回路には例えば最大暗レベルの入力電圧を与える。すると、3列のスイッチM11、M21、M31に対応する列駆動回路から加算された検出電流信号が得られ、これが基準データと比較され、スイッチM11、M21、M31に対応する列駆動回路一組の補正係数k1が算出される。

## 【0050】

続いて、R、G、Bの3列のスイッチM12、M22、M32に対応する列駆動回路に検出用の所定の明レベルの入力電圧を与え、他の全列の列駆動回路には例えば最大暗レベルの入力電圧を与える。すると、スイッチM12、M22、M32に対応する列駆動回路の3列から加算された検出電流信号が得られ、これが基準データと比較され、スイッチM12、M22、M32に対応した列駆動回路一組の補正係数k2が算出される。この動作を時系列的に順次、水平方向に選択される列駆動回路一組を変更しながら、補正係数k1、k2・・・kNを算出する。このように、一つの列駆動回路から順次検出信号を得るのではなく、所定個数(ここでは3つ)の列駆動回路をまとめて、それらの加算値として検出信号を得ている。よって、検出時間は3分の1に短縮され、また、所望のSN比の検出信号を得ることができる。

## 【0051】

また、補正回路32において補正に必要な演算時間も3分の1に短縮されるので、映像信号の高速処理が可能となる。

10

20

30

40

50

## 【0052】

ここで、一つの列駆動回路としては、特許文献1の図1の回路を採用することも好ましいものである。この場合、補正のための検出時には、一対の電圧電流変換回路に同じ検出用の所定の明レベルの入力電圧を与え、これら一対の電圧電流変換回路からの出力電流を加算して同時に検出するようにしている。このように、本実施形態によれば、6つ( $2 \times RGB$ )の電圧電流変換回路から同時に検出信号を加算して得てもよい。

## 【0053】

なお、図2中、スイッチを構成するトランジスタをNチャネル型としたが、それに限らない。

## 【0054】

## (補正回路)

本実施形態の補正回路32は、R、G、B3本のデータ線からなる組毎に検出された電流信号と、基準となる電流信号とで演算処理を行い、補正係数 $k_1$ 乃至 $k_N$ を得て、その補正係数 $k_1$ 乃至 $k_N$ を記憶する。R、G、Bの3つの入力信号Vi deoが補正回路32に記憶された共通の補正係数 $k_1$ 乃至 $k_N$ を用いて補正される。こうして補正された映像信号がR、G、Bの3つの列駆動回路1に順次入力される。列駆動回路1の出力電流は、データ線を介して画素回路2に入力される。ここで、隣接する3つの列駆動回路1に入力されるR、G、Bの信号は総和電流により得られた補正係数で補正されているため、各列駆動回路毎の近接的なばらつき、例えば隣合う列のEL素子に流れ込む電流に関しては不十分である。本実施形態は、その対策として、後述する選択回路34を用いるものである、という見方もできる。

## 【0055】

RGB各色画素毎の画素データをシリアルに転送する構成の補正回路を採用する場合には、上述したように、列駆動回路の出力先の変更に併せて、RGB各色画素データの出力順序を変更した映像信号を供給することもできる。

## 【0056】

## (画素回路)

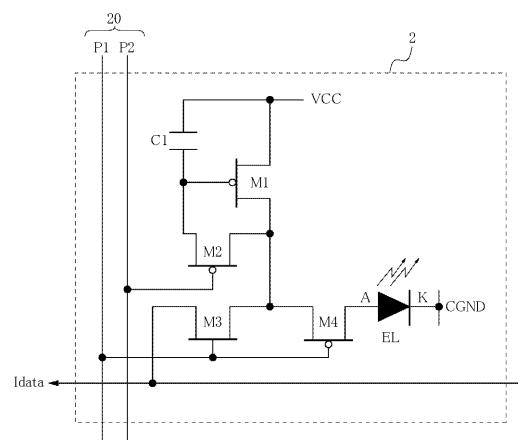

図3は、本実施例のEL素子を含む画素回路2の構成例を示す。

## 【0057】

図3において、P1及びP2が行選択線20に印加される走査信号であり、データ信号として電流データI dataが入力される。EL素子の陽極(アノード)はTFT(M4)のドレイン端子に接続されており、陰極(カソード)は接地電位CGNDに接続されている。M1、M2、M4がP型TFTであり、M3がN型TFTである。

## 【0058】

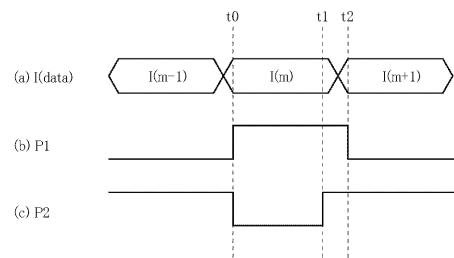

図4は、画素回路2の駆動方法を説明するタイミングチャートである。図4において、I(m-1)、I(m)、I(m+1)は、m-1行(1行前)、m行(対象行)、m+1行(1行後)の対象列の画素回路2に入力される電流データI dataを示す。

## 【0059】

まず、時刻t0前の時点では、対象行の画素回路2には、走査信号P1にはLowレベルの信号が、P2にはHighレベルの信号が入力され、トランジスタM2がOFF、M3がOFF、M4がONの状態である。この状態では、対象行であるm行の画素回路2には、1行前の電流データI dataに対応するI(m-1)は入力されない。

## 【0060】

次いで、時刻t0では、P1にはHighレベルの信号が、P2にはLowレベルの信号が入力され、トランジスタM2、M3がON、M4はOFFとなる。この状態で、m行の画素回路2に該当行の電流データI dataに対応するI(m)が入力される。このとき、M4は導通状態でないため、EL素子には電流が流れない。入力されたI dataによりM1の電流駆動能力に応じた電圧が、M1のゲート端子と電源電位VCCの間に配置された容量C1に生じる。つまり、画素回路で一旦電流電圧変換を行う。

**【 0 0 6 1 】**

次いで、時刻  $t_1$  では、P2 に High レベルの信号が入力され、M2 が OFF の状態となる。さらに、時刻  $t_2$  では、P1 に Low レベルの信号が入力され、M3 が OFF、M4 が ON となる。この状態では、M4 が導通状態であるため、C1 に生じた電圧により、M1 の電流駆動能力に応じた電流が EL 素子に供給される。つまり、ここで再び電流に変換される。これにより、供給された電流に応じた輝度で EL 素子が発光する。

**【 0 0 6 2 】**

本実施例においては画素回路として、図3の構成を一例に挙げたが、これに限るものではない。

**【 0 0 6 3 】**

(選択回路)

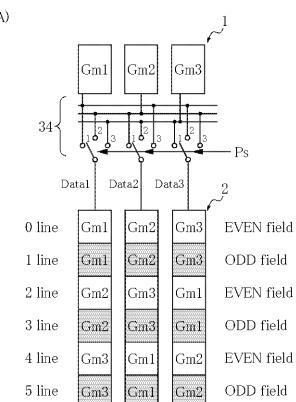

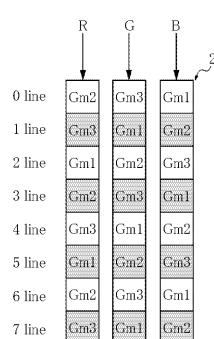

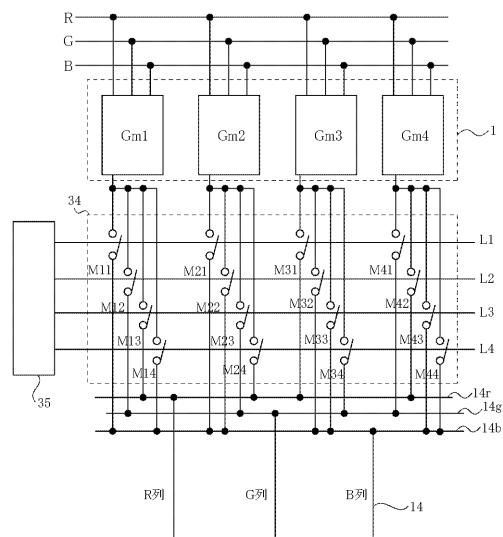

次に、本実施例の選択回路34について、図5および図6を参照して説明する。ここでは、R(赤)、G(緑)、B(青)に割当てた画素回路で構成された画素を例にして説明する。

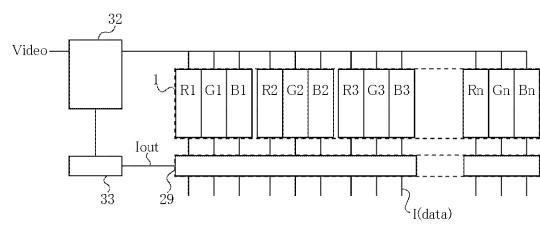

**【 0 0 6 4 】**

図5は、R、G、Bそれぞれの列と1対1に対応した列駆動回路1と、総和電流出力回路29の概略図である。図中の例では、R1、G1、B1は1列目の画素に、またR2、G2、B2は2列目の画素に、さらにR3、G3、B3は3列目の画素に、以下同様にRn、Gn、Bnはn列目の画素にそれぞれ対応する列駆動回路1を示す。

**【 0 0 6 5 】**

前述の補正回路により得られた補正係数k1乃至kNで補正をかけた出力電流のばらつきをさらに低減するために、本実施形態では、列駆動回路1と画素回路2の間に選択回路34を備え、この選択回路34により列駆動回路1とデータ線14を単位水平走査期間毎に順次切り替える制御を行う。

**【 0 0 6 6 】**

例えば、上記の手段のように列駆動回路1の総和出力電流を用いて3列の列駆動回路1の補正係数k1を得た場合、3列の列駆動回路1それぞれの出力とそれに対応する3つのデータ線の接続関係を順次切り替える。これにより、画素回路2には時間的に平均化された電流が入力されるようになる。

**【 0 0 6 7 】**

以上の構成を持つことにより、画素間でのばらつきと近接的なばらつきを低減させることができ可能である。なお、データ線の切り替えを3列の列駆動回路1で説明したが、本発明はそれに限らない。

**【 0 0 6 8 】**

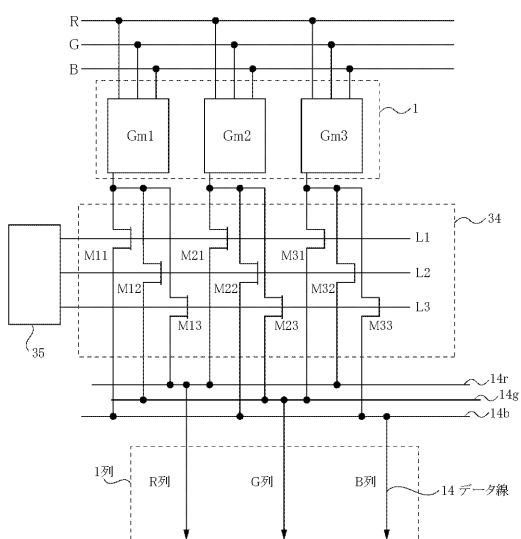

図6は、列電流を時間的に平均化する選択回路34の概略図である。図6では、不図示であるが、列駆動回路1と選択回路34との間に、前述した総和電流出力回路29が必要に応じて設けられている。

**【 0 0 6 9 】**

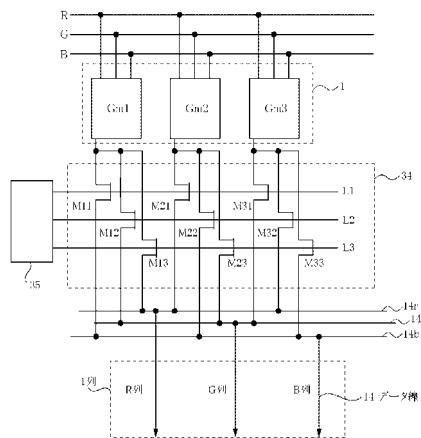

図6において、R、G、Bは各色に対応する入力映像信号Vide o、Gm1乃至Gm3は1列の画素を構成するR、G、Bの画素回路に対応する3列の列駆動回路1を示す。M11乃至M13、M21乃至M23、M31乃至M33は、Gm1、Gm2、Gm3の出力側の接続されるスイッチとしてのトランジスタを示す。

**【 0 0 7 0 】**

L1は、M11、M21、M31のゲート端子に、L2はM12、M22、M32のゲート端子に、L3はM13、M23、M33のゲート端子にそれぞれ接続されるON/OFF制御用の制御信号を示す。14r、14g、14bは、1列の画素を構成するR、G、Bの各画素回路に接続されるR列、G列、B列の各データ線14のそれぞれに接続される共通線を示す。なお、L1乃至L3の制御信号は、選択回路34の外部(又は内部)に設けた制御回路としてのゲート回路(ロジック回路)35から、予め設定された動作タイミングで出力されるようになっている。

10

20

30

40

50

**【 0 0 7 1 】**

つまり、制御信号 L 1 乃至 L 3 を出力する回路は、単結晶半導体を用いた集積回路で表示パネルの外部に設けられた回路、或いは、非単結晶半導体を用いて、表示パネルと同じ基板上に TFT で形成された薄膜半導体集積回路であってもよい。

**【 0 0 7 2 】**

図 6において、Gm1、Gm2、Gm3 の各入力端には、R、G、B 各色の映像信号の配線に個別に接続されている。そして、列駆動回路の出力先の変更に応じて、各列駆動回路がサンプリングする映像信号の種類（色）も変更される。

**【 0 0 7 3 】**

Gm1 の出力端には、スイッチ M11、M12、M13 及びそれらの接続配線と、共通線 14r、14g、14b を介して、R、G、B 各色のデータ線 14 が接続されている。Gm2 の出力端には、スイッチ M21、M22、M23 及びそれらの接続配線と、共通線 14r、14g、14b を介して、R、G、B 各色のデータ線 14 が接続されている。Gm3 の出力端には、スイッチ M31、M32、M33 及びそれらの接続配線と、共通線 14r、14g、14b を介して、R、G、B 各色のデータ線 14 が接続されている。

**【 0 0 7 4 】**

上記構成により、選択回路 34 内のトランジスタのスイッチ ON / OFF 制御により、例えば、Gm1 の出力先のデータ線 14 を R 列 G 列 B 列、G 列 B 列 R 列、B 列 R 列 G 列のように、単位水平走査期間毎に切り替えることが可能である。

**【 0 0 7 5 】**

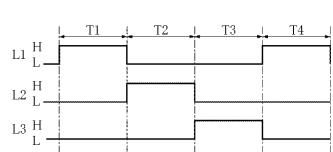

次に、図 7 および図 8 を参照して、選択回路 34 の動作を説明する。

**【 0 0 7 6 】**

図 7 は制御回路 35 の出力タイミングチャート、図 8 はその駆動シーケンスを示す。図 7 のタイミングチャートは、選択回路 34 のトランジスタで構成されたスイッチのゲート端子に入力される L1 乃至 L3 の信号の電位を示す。また、T1 乃至 T4 は、予め設定された単位水平走査期間（単位水平ライン周期）を示す。図 8において、No. は駆動シーケンス番号、ON\_SW は ON 状態のトランジスタ、OFF\_SW は OFF 状態のトランジスタを示す。I(gm1)、I(gm2)、I(gm3) はそれぞれ Gm1、Gm2、Gm3 の電流信号を示す。

**【 0 0 7 7 】**

図 7において、まず、第 1 の単位水平ライン周期 T1 では、L1 のみに High レベルの信号が入力され、L2 および L3 には Low レベルの信号が入力される。このとき、選択回路 34 の M11、M21、M31 のトランジスタのみが ON となり、他のトランジスタは OFF である。この状態では、Gm1 は B の電流信号 I(gm1) を、Gm2 は R の電流信号 I(gm2) を、Gm3 は G の電流信号 I(gm3) を、それぞれ共通線 14b、14r、14g を介して、B 列、G 列、R 列の各データ線 14 に出力する。この周期 T1 は、図 8 に示す駆動シーケンス No. 1 に対応する。

**【 0 0 7 8 】**

次いで、第 2 の単位水平ライン周期 T2 では、L2 のみに High レベルが入力され、L1 および L3 は Low レベルの信号が入力される。このとき選択回路 34 の M12、M22、M32 のトランジスタが ON となり、他のトランジスタは OFF である。この状態では、Gm1 は G の電流信号 I(gm1) を、Gm2 は B の電流信号 I(gm2) を、Gm3 は R の電流信号 I(gm3) を、それぞれ共通線 14g、14b、14r を介して、G 列、B 列、R 列の各データ線 14 に出力する。この周期 T2 は、図 8 に示す駆動シーケンス No. 2 に対応する。

**【 0 0 7 9 】**

次いで、第 3 の単位水平ライン周期 T3 では、L3 のみ High レベルが入力され、L1 および L2 は Low レベルの信号が入力される。このとき選択回路 34 の M13、M23、M33 のトランジスタが ON となり、他のトランジスタは OFF である。この状態では、Gm1 は R の電流信号 I(gm1) を、Gm2 は G の電流信号 I(gm2) を、

10

20

30

40

50

Gm3はBの電流信号I(gm3)を、それぞれ共通線14r、14g、14bを介して、R列、G列、B列の各データ線14に出力する。この周期T3は、図8に示す駆動シーケンスNo.3に対応する。

#### 【0080】

次いで、第4の周期T4では、第1の周期T1と同様の動作が行われ、これ以降、上記と同様の動作が繰り返し実行される。

#### 【0081】

以上のように選択回路34と制御回路35により、列駆動回路1の出力先を順次変更する。

#### 【0082】

なお、説明の中で図6中の選択回路34のトランジスタをNチャネル型としたがそれに限らない。また、画素構成をRGBの3色一組としたがそれに限らない。従って、本実施形態によれば、TFT等の絶縁ゲート型電界効果トランジスタの素子特性ばらつきによるEL素子に流れる電流ばらつきを大幅に低減できる。加えて、隣接する列毎の特性ばらつきを時間的に平均化することで、表示装置の視覚的なムラやスジ等といった課題を軽減することが出来る。

#### 【0083】

(実施形態2)

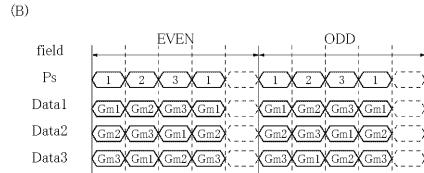

本実施形態は、2つのフィールド(EVEN/ODDフィールドとする)からなるインターレース走査方式で表示を行う表示装置の例である。

#### 【0084】

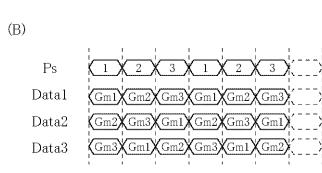

図9は、6行3列の画素回路のマトリクスに0行から5行まで順次行を選択しながらノンインターレース走査を行う場合を示している。

#### 【0085】

この場合、選択回路34によって、データ線Data1に接続される列駆動回路1の順序は、Gm1、Gm2、Gm3、Gm1、Gm2、Gm3の順となる。

#### 【0086】

しかしながら、このように動作する選択回路34を用いて、インターレース走査を行う場合には、改善すべき課題がある。

#### 【0087】

図10に示すように、EVEN/ODDフィールドで同じ分散順序(列駆動回路とデータ線の接続順序)では、隣接する2行(EVEN/ODD)の画素には同じ列駆動回路から電流データ信号が供給されることになる。すると、分散周期が長くなり分散周期が視認されやすくなる。

#### 【0088】

そこで、本実施形態では、偶数行を表示する第1のフィールドと奇数行を表示する第2のフィールドによって1フレームを表示するインターレース走査方式で表示を行う。そして、列駆動回路の出力先となるデータ線を単位水平走査期間毎に順次変更しながら、選択されたデータ線を介して列駆動回路からのデータ信号を画素回路に供給し、第1のフィールドと第2のフィールドではデータ線を順次選択する順序を異ならしめる。

#### 【0089】

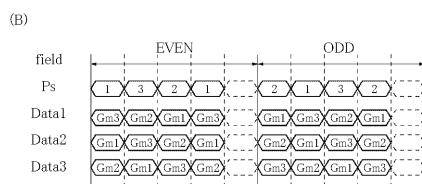

本実施形態における表示装置の駆動方法について図11を用いて説明する。簡略化のため表示画素を6行×3列の18画素とする。Gm1乃至Gm3は列駆動回路を示し、映像信号電圧に応じた電流データ信号を出力する。34は選択回路であり、列駆動回路の出力となるデータ線を選択する。Psは選択回路34を制御する選択制御信号であり、制御回路35から出力される。

#### 【0090】

選択信号Psによりスイッチの接点を単位走査期間毎に切り替え、列駆動回路を順次変更しながら、データ線を介して列駆動回路からの電流データ信号を同じ列の画素回路に供給する。

10

20

30

40

50

**【 0 0 9 1 】**

図11において選択回路34の接点(1、2、3)を選択する順序は、EVENフィールドにおいては1 3 2 1 ……、ODDフィールドにおいては2 1 3 2 ……としている。ただし、選択する順序はこの限りではない。各画素に記載されたGm1乃至Gm3は該画素に電流データ信号を供給する列駆動回路を示している。このように各列の画素には、行毎に3つの列駆動回路を切り替え、かつフィールド毎に変更順序を変えて電流データ信号が供給される。

**【 0 0 9 2 】**

また、この分散表示において前記複数のデータ線を選択するときに、3つの原色画素のうち任意の原色画素に対応する列に配置されたデータ線に対して3つの列駆動回路のうち1つの列駆動回路からの電流データ信号を出力可能に選択することが好みしい。10

**【 0 0 9 3 】**

また、複数の列駆動回路のうち2つ以上の列駆動回路を、前記複数のデータ線のうち1つのデータ線に共通に接続し、かつ、当該1つのデータ線に対して前記データ信号を出力してもよい。例えば、画素回路が映像信号の表示色を決める3つの原色画素に対応して配置され、複数のデータ線は、前記3つの原色画素に対応する列に配置される3つのデータ線を有し、前記3つのデータ線に切り替え可能に接続された4つ以上の列駆動回路を有し、そのうちの2つ以上の列駆動回路は、前記3つの原色画素のうち所定の原色画素に対応する列に配置された1つのデータ線に共通に接続され、当該1つのデータ線に対して前記データ信号を出力してもよい。20

**【 0 0 9 4 】**

本実施形態によれば、インターレース走査方式による表示を行う場合に、列駆動回路の出力先のデータ線を順次切り替えて選択する周期を単位水平ライン周期としてEVEN/ODDフィールド毎に分散順序を異ならせることによって、EVEN/ODDフィールドでの分散順序が同一の場合と比較して同じ列駆動回路Gmで電流データ信号を供給する画素をより分散して配置できるため列駆動回路1の電圧電流変換ゲインばらつきによる輝度ばらつきを視覚的にさらに低減できる。

**【 0 0 9 5 】**

ここで、本実施形態による表示装置の動作をより詳しく説明する。

**【 0 0 9 6 】**

基本的な構成は前述した実施形態1と同じであり、異なる点は選択回路34及びその制御回路35の動作である。30

**【 0 0 9 7 】**

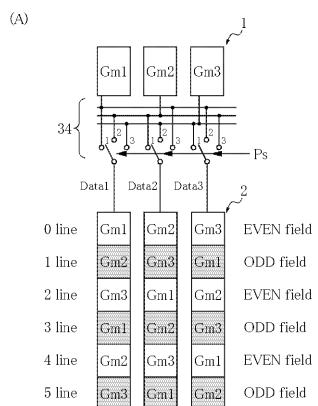

図12は選択回路34の動作タイミングチャートを示している。この図12のタイミングチャートは、選択回路34のトランジスタで構成されたスイッチ(SW)のゲート端子に入力されるL1乃至L3の信号の電位を示す。(A)はEVENフィールド時、(B)はODDフィールド時のタイミングチャートを示している。また、T1乃至T4は、予め設定された単位水平ライン期間(単位水平走査期間)を示す。

**【 0 0 9 8 】**

まず、図12(A)に示されるEVENフィールド時の動作について説明する。

**【 0 0 9 9 】**

第1の単位水平ライン期間T1では、L1のみにHighレベルの信号が入力され、L2およびL3にはLowレベルの信号が入力される。このとき、選択回路34のM11、M21、M31のトランジスタのみがONとなり、その他のトランジスタはOFFである。図6の回路図の結線によれば、この状態では、Gm1はBの電流信号I(gm1)を、Gm2はRの電流信号I(gm2)を、Gm3はGの電流信号I(gm3)を、それぞれ共通線14b、14r、14gを介して、B列、R列、G列の各データ線14に出力する。この期間T1は、図8に示す駆動シーケンスNo.1に対応する。

**【 0 1 0 0 】**

次いで、第2の単位水平ライン期間T2では、L3のみHighレベルの信号が入力さ50

れ、L<sub>1</sub>およびL<sub>2</sub>はL<sub>o</sub>wレベルの信号が入力される。このとき選択回路34のM<sub>1</sub>3、M<sub>2</sub>3、M<sub>3</sub>3のトランジスタがONとなり、その他のトランジスタはOFFである。図6の回路図の結線によれば、この状態では、Gm1はRの電流信号I(gm1)を、Gm2はGの電流信号I(gm2)を、Gm3はBの電流信号I(gm3)を、それぞれ共通線14r、14g、14bを介して、R列、G列、B列の各データ線14に出力する。この期間T<sub>2</sub>は、図8に示す駆動シーケンスNo.3に対応する。

#### 【0101】

次いで、第3の単位水平ライン期間T<sub>3</sub>では、L<sub>2</sub>のみにH<sub>i</sub>ghレベルの信号が入力され、L<sub>1</sub>およびL<sub>3</sub>はL<sub>o</sub>wレベルの信号が入力される。このとき選択回路34のM<sub>1</sub>2、M<sub>2</sub>2、M<sub>3</sub>2のトランジスタがONとなり、その他のトランジスタはOFFである。

10 図6の回路図の結線によれば、この状態では、Gm1はGの電流信号I(gm1)を、Gm2はBの電流信号I(gm2)を、Gm3はRの電流信号I(gm3)を、それぞれ共通線14g、14b、14rを介して、G列、B列、R列の各データ線14に出力する。この期間T<sub>2</sub>は、図8に示す駆動シーケンスNo.2に対応する。

#### 【0102】

次いで、第4の期間T<sub>4</sub>では、第1の期間T<sub>1</sub>と同様の動作が行われ、これ以降、上記と同様の動作が繰り返し実行される。

#### 【0103】

次に、図12(B)に示されるODDフィールド時の動作について説明する。

#### 【0104】

第1の単位水平ライン期間T<sub>1'</sub>では、L<sub>2</sub>のみにH<sub>i</sub>ghレベルの信号が入力され、L<sub>1</sub>およびL<sub>3</sub>はL<sub>o</sub>wレベルの信号が入力される。このとき選択回路34のM<sub>1</sub>2、M<sub>2</sub>2、M<sub>3</sub>2のトランジスタがONとなり、その他のトランジスタはOFFである。図6によれば、この状態では、Gm1はGの電流信号I(gm1)を、Gm2はBの電流信号I(gm2)を、Gm3はRの電流信号I(gm3)を、それぞれ共通線14g、14b、14rを介して、G列、B列、R列の各データ線14に出力する。この期間T<sub>1'</sub>は、図8に示す駆動シーケンスNo.2に対応する。

20

#### 【0105】

次いで、第2の単位水平ライン期間T<sub>2'</sub>では、L<sub>1</sub>のみにH<sub>i</sub>ghレベルの信号が入力され、L<sub>2</sub>およびL<sub>3</sub>にはL<sub>o</sub>wレベルの信号が入力される。このとき、選択回路34のM<sub>1</sub>1、M<sub>2</sub>1、M<sub>3</sub>1のトランジスタのみがONとなり、その他のトランジスタはOFFである。

30 図6によれば、この状態では、Gm1はBの電流信号I(gm1)を、Gm2はRの電流信号I(gm2)を、Gm3はGの電流信号I(gm3)を、それぞれ共通線14b、14r、14gを介して、B列、R列、G列の各データ線14に出力する。この期間T<sub>2'</sub>は、図8に示す駆動シーケンスNo.1に対応する。

#### 【0106】

次いで、第3の単位水平ライン期間T<sub>3'</sub>では、L<sub>3</sub>のみH<sub>i</sub>ghレベルの信号が入力され、L<sub>1</sub>およびL<sub>2</sub>はL<sub>o</sub>wレベルの信号が入力される。このとき選択回路34のM<sub>1</sub>3、M<sub>2</sub>3、M<sub>3</sub>3のトランジスタがONとなり、その他のトランジスタはOFFである。

40 図6によれば、この状態では、Gm1はRの電流信号I(gm1)を、Gm2はGの電流信号I(gm2)を、Gm3はBの電流信号I(gm3)を、それぞれ共通線14r、14g、14bを介して、R列、G列、B列の各データ線14に出力する。この期間T<sub>3'</sub>は、図8に示す駆動シーケンスNo.3に対応する。

#### 【0107】

次いで、第4の期間T<sub>4'</sub>では、第1の期間T<sub>1'</sub>と同様の動作が行われ、これ以降、上記と同様の動作が繰り返し実行される。

#### 【0108】

以上の駆動シーケンスによれば、EVENフィールドでは、R列の画素群に注目すると、T<sub>1</sub> T<sub>2</sub> T<sub>3</sub> T<sub>4</sub> . . . と単位水平ライン期間が切り替わる毎に、Gm2 Gm1 Gm3 Gm2 . . . の順で列駆動回路1から電流データ信号が供給される。

50

列の画素群に注目すると、G m 3 G m 2 G m 1 G m 3 … の順で列駆動回路 1 から電流データ信号が供給される。B 列の画素群に注目すると、G m 1 G m 3 G m 2 G m 1 … の順で列駆動回路 1 から電流データ信号が供給される。

#### 【0109】

また、O D D フィールドでは、R 列の画素群に注目すると、T 1' T 2' T 3' T 4' … と単位水平ライン期間が切り替わる毎に、G m 3 G m 2 G m 1 G m 3 … の順で列駆動回路 1 から電流データ信号が供給される。G 列の画素群に注目すると、G m 1 G m 3 G m 2 G m 1 … の順で列駆動回路 1 から電流データ信号が供給される。B 列の画素群に注目すると、G m 2 G m 1 G m 3 G m 2 … の順で列駆動回路 1 から電流データ信号が供給される。

10

#### 【0110】

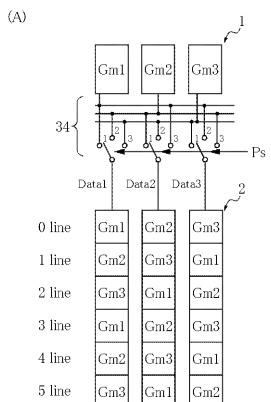

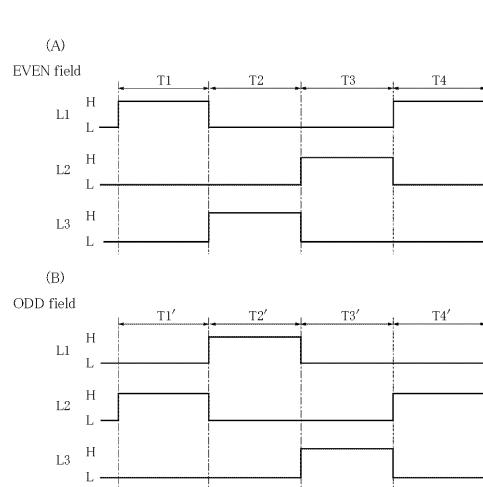

したがって、E V E N フィールドにおいて、T 1 では第 0 行、T 2 では第 2 行、T 3 では第 4 行、T 4 では第 6 行を表示し、O D D フィールドにおいて、T 1' では第 1 行、T 2' では第 3 行、T 3' では第 5 行、T 4' では第 7 行を表示することとすると、画素とその画素に電流データ信号を供給する列駆動回路との関係は、図 13 に示される配置となる。図 13 には画素 2 の配列とその画素に電流データ信号を供給する列駆動回路との対応関係が示されている。

#### 【0111】

以上のように、E V E N フィールドと O D D フィールドにおいて列駆動回路 1 の出力先を順次選択してデータ線に出力する順序を変えて分散順序を異ならせることで、図 13 に示すように、同一の列駆動回路 1 から電流データ信号が供給される画素を分散して配置することができるため、列駆動回路 1 の電圧電流変換ゲインばらつきによる輝度ばらつきを視覚的に低減することが可能となる。なお、画素構成を R G B の 3 色一組としたがそれに限らない。

20

#### 【0112】

##### (実施形態 3)

3 つ以上の列駆動回路のうち 2 つ以上の列駆動回路を、前記複数のデータ線のうち 1 つのデータ線に共通に接続し、かつ、当該 1 つのデータ線に対して 2 つの列駆動回路から前記データ信号を出力してもよい。

30

#### 【0113】

図 14 は、本実施形態による表示装置の列駆動回路 1、選択回路 34、制御回路 35 に注目した回路図である。画素回路を 3 つの原色画素 (R、G、B) の色毎に列を分けて配置し、3 つの原色画素 (R G B) に対応する列に配置される 3 つのデータ線 14 に対して選択回路 34 で切り替え可能に 4 つの列駆動回路 (G m 1、G m 2、G m 3、G m 4) を接続する。この構成によれば、4 つの列駆動回路のうちの 2 つの列駆動回路が、前記 3 つの原色画素のうち所定の原色画素 (ここでは輝度が低い傾向にある青色画素) に対応する列に配置された 1 つのデータ線に共通に接続される。こうして、青色画素の列では、1 つのデータ線に対して複数の列駆動回路から前記データ信号を出力することになる。

#### 【0114】

従って、本実施例によれば、T F T 等のトランジスタの素子特性ばらつきによる E L 素子に流れる電流ばらつきによる表示装置の視覚的なムラやスジ等といった問題を軽減することが出来る。

40

#### 【0115】

上述した各実施形態の表示装置は各種電子機器に適用できる。

#### 【0116】

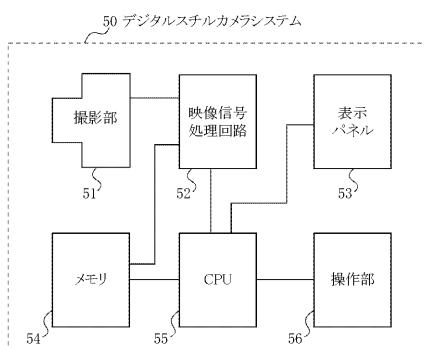

図 15 は、本発明が用いられる電子機器としてのデジタルスチルカメラシステムのブロック図である。図中、50 はデジタルスチルカメラシステム、51 は撮影部、52 は映像信号処理回路、53 は表示パネル、54 はメモリ、55 は C P U 、56 は操作部を示す。

#### 【0117】

図 15 において、撮影部 51 で撮影した映像または、メモリ 54 に記録された映像を、

50

映像信号処理回路 5 2 で信号処理し、表示パネル 5 3 で見ることができる。C P U 5 5 では、操作部 5 6 からの入力によって、撮影部 5 1 、メモリ 5 4 、映像信号処理回路 5 2 などを制御して、状況に適した撮影、記録、再生、表示を行う。また、表示パネル 5 3 は、この他にも各種電子機器の表示部として利用できる。

#### 【産業上の利用可能性】

#### 【0 1 1 8】

本発明の情報表示装置は、例えば携帯電話、携帯コンピュータ、スチルカメラもしくはビデオカメラのいずれかの形態をとる。もしくは、それらの各機能の複数を実現する装置である。情報表示装置は、情報入力部を備えている。例えば、携帯電話の場合には情報入力部は、アンテナを含んで構成される。P D A や携帯 P C の場合には、情報入力部は、ネットワークに対するインターフェース部を含んで構成される。スチルカメラやムービーカメラの場合には、情報入力部は C C D や C M O S などによる光センサ部を含んで構成される。

10

#### 【図面の簡単な説明】

#### 【0 1 1 9】

【図 1】本発明の一実施形態に係る表示装置の構成を示すブロック図である。

【図 2】本発明に用いられる信号検出回路の回路図である。

【図 3】本発明に用いられる画素回路の回路図である。

【図 4】図 3 に示す画素回路の動作を説明するためのタイミングチャートである。

20

【図 5】本発明に用いられる補正回路を説明するためのブロック図である。

【図 6】本発明に用いられる選択回路の回路図である。

【図 7】図 6 に示す選択回路の動作を説明するためのタイミングチャートである。

【図 8】図 6 に示す選択回路の駆動シーケンスを説明する図である。

【図 9】本発明の実施形態に係る表示装置の基本動作を説明するための模式図である。

【図 1 0】比較例による表示動作を説明するための模式図である。

【図 1 1】本発明の別の実施形態による表示装置の表示動作を説明するための模式図である。

【図 1 2】本発明の別の実施形態による選択回路の動作を説明するためのタイミングチャートである。

30

【図 1 3】本発明の別の実施形態による表示状態を示す模式図である。

【図 1 4】本発明の更に別の実施形態による選択回路を示す回路図である。

【図 1 5】本発明が用いられる電子機器のブロック図である。

【図 1 6】従来例の表示装置の全体構成を示す図である。

【図 1 7】列駆動回路の回路図である。

40

#### 【符号の説明】

#### 【0 1 2 0】

1 列駆動回路

2 画素回路

3 列シフトレジスタ

4 ゲート回路

5 行シフトレジスタ

6 、 7 、 8 入力回路

9 画像表示部

1 0 映像信号線

1 1 水平走査制御信号

1 2 垂直走査制御信号

1 3 副制御信号

1 4 データ線

1 5 水平サンプリング信号ゲート回路

1 6 ゲート回路

50

- |       |                |

|-------|----------------|

| 1 7   | 水平サンプリング信号     |

| 1 8   | 水平サンプリング信号     |

| 1 9   | 制御信号           |

| 2 0   | 行選択線           |

| 2 1   | 制御信号           |

| 2 9   | 総和電流検出回路       |

| 3 0   | ゲート回路          |

| 3 2   | 補正回路           |

| 3 3   | 総和電流出力回路       |

| 3 4   | 選択回路           |

| 3 5   | 制御回路           |

| 4 1   | スイッチ部          |

| 4 2   | 遮断部            |

| 4 3   | 出力線            |

| 5 0   | デジタルスチルカメラシステム |

| 5 1   | 撮影部            |

| 5 2   | 映像信号処理回路       |

| 5 3   | 表示パネル          |

| 5 4   | メモリ            |

| 5 5   | C P U          |

| 5 6   | 操作部            |

| 1 0 0 | 表示パネル          |

10

20

【 図 1 】

|            |             |             |

|------------|-------------|-------------|

| 1 列制御回路    | 5 行シフトレジスタ  | 32 補正回路     |

| 2 画素回路     | 9 画像表示部     | 33 総和電流流出回路 |

| 3 列シフトレジスタ | 29 総和電流検出回路 | 34 選択回路     |

| 4 ゲート回路    | 30 ゲート回路    | 35 制御回路     |

【 図 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

| No. | ON_SW | OFF_SW | R列    | G列    | B列    |

|-----|-------|--------|-------|-------|-------|

| 1   | L1    | L2,L3  | [Gm2] | [Gm3] | [Gm1] |

| 2   | L2    | L1,L3  | [Gm3] | [Gm1] | [Gm2] |

| 3   | L3    | L2,L3  | [Gm1] | [Gm2] | [Gm3] |

【図8】

【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 2 N |

| G 0 9 G | 3/20 | 6 2 3 D |

| G 0 9 G | 3/20 | 6 2 2 D |

| G 0 9 G | 3/20 | 6 4 2 A |

| G 0 9 G | 3/30 | K       |

(72)発明者 井関 正己

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 川野 藤雄

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 川崎 素明

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

F ターム(参考) 5C080 AA06 BB05 CC03 DD05 EE28 EE29 FF11 JJ02 JJ03 JJ04

KK43