(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5995416号

(P5995416)

(45) 発行日 平成28年9月21日(2016.9.21)

(24) 登録日 平成28年9月2日(2016.9.2)

(51) Int.CI.

H01L 27/14 (2006.01)

F 1

H01L 27/14

D

請求項の数 6 (全 13 頁)

(21) 出願番号 特願2011-183076 (P2011-183076)

(22) 出願日 平成23年8月24日 (2011.8.24)

(65) 公開番号 特開2013-45907 (P2013-45907A)

(43) 公開日 平成25年3月4日 (2013.3.4)

審査請求日 平成26年7月31日 (2014.7.31)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像素子及び撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

マイクロレンズを共有し、且つ分離層にて複数の領域に分割された光電変換部と、前記マイクロレンズにて集光された光束を前記光電変換部に導くとともに前記分離層には導かない光導波路と、電極が配置され前記分離層を覆う絶縁層と、を有する撮像素子であって、

前記分離層は前記光電変換部で発生した電荷を転送するための転送電極を備え、

前記絶縁層は前記光導波路内の光を反射するための境界面を有し、

前記光導波路は、前記複数の領域に分割された光電変換部の各々の上面に積層され、

前記光導波路上に前記絶縁層が積層され、

前記絶縁層上に前記マイクロレンズが積層され、

光入射方向において、前記光導波路の各々の前記光電変換部側の面は、前記分離層に備わる前記転送電極を覆わずに前記光電変換部の光入射面を覆い、

光入射方向において、前記光導波路の各々の前記絶縁層と接する側の面は、平面であり、

前記分離層と前記光電変換部の光入射面を覆っていることを特徴とする撮像素子。

## 【請求項 2】

前記光導波路は、前記マイクロレンズの結像位置の近傍に配置されることを特徴とする

請求項 1 に記載の撮像素子。

## 【請求項 3】

前記光導波路は、前記マイクロレンズの結像位置より後方に配置されることを特徴とす

10

20

る請求項 1 又は 2 に記載の撮像素子。

【請求項 4】

前記光導波路の各々の前記絶縁層側の面は、その周縁部が前記マイクロレンズの光軸上で接しており、

前記マイクロレンズに入射した光束は、前記光導波路の各々の前記絶縁層側の面に集光し、

前記光導波路の各々に入射した光束は、前記複数の領域に分割された光電変換部の各々に到達することを特徴とする請求項 1 乃至 3 のいずれか 1 項に記載の撮像素子。

【請求項 5】

前記電極は、前記光電変換部から転送された電荷を選択的に出力する第 1 の電極、第 2 の電極及び第 3 の電極を含み、

10

前記絶縁層は、前記第 1 の電極と前記第 2 の電極の間、及び、前記第 2 の電極と前記第 3 の電極の間に配置されていることを特徴とする請求項 1 乃至 4 のいずれか 1 項に記載の撮像素子。

【請求項 6】

撮影レンズと、

前記撮影レンズを介した光束を受光する請求項 1 乃至 5 のいずれか 1 項に記載の撮像素子と、を備えることを特徴とする撮像装置。

【発明の詳細な説明】

【技術分野】

20

【0001】

本発明は、マイクロレンズを共有する複数に分割された光電変換部を有する撮像素子に関する。

【背景技術】

【0002】

従来、固体メモリ素子を有するメモリカードを記録媒体として、CCD や CMOS 等の固体撮像素子で撮像した静止画像や動画像を記録及び再生する電子カメラ等の撮像装置は多く存在する。

【0003】

特許文献 1, 2 には、撮像装置に搭載される固体撮像素子を構成する複数画素のうち一部ないし全ての画素の光電変換部を複数に分割したものが提案されている。

30

【0004】

このような撮像素子の用途としては、分割された光電変換部のそれぞれの像信号からの出力信号をもとに、瞳分割方式の焦点検出を行うことや、立体画像を生成することなどが挙げられる。当然、分割画素の出力を加算することで、通常の撮像信号として使用することも可能である。

【0005】

また、撮像装置に搭載される固体撮像素子に関する技術の一例として、光入射面と光電変換手段との間に、光入射側の開口率が大きな光導波路を設け、集光特性を高めた撮像素子が、特許文献 4 などにおいて提案されている。

40

【先行技術文献】

【特許文献】

【0006】

【特許文献 1】特開 2003-244712 号公報

【特許文献 2】特開平 06-163866 号公報

【特許文献 3】特開 2009-158800 号公報

【特許文献 4】特開平 05-283661 号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

50

しかしながら、前述のような分割画素を有する個体撮像素子を用いた撮像装置における通常の撮像信号としての撮影においては、以下のような課題がある。すなわち、

特許文献1, 2のように分割画素を構成する際、各分割画素の間には、様々な画素構成要素が配置される可能性がある。例えば、感度向上のためにフォトダイオードの面積を大きくしたい場合、各分割画素毎にフローティングディフュージョン(以下、FD)や出力信号線を配置するのではなく、複数の分割画素で共有するFDなどを使用する構成が好ましい。この際、共有するFDは、各分割画素の中心に配置することが望ましい。このように、各分割画素間に、FDなどの画素構成要素を配置するために、各分割画素のフォトダイオード間には、感度を持たない分離領域が存在することになる。

【0008】

10

また、仮に各分割画素の間に配置する構成要素をなくしたとしても、画素部の製造精度やアライメント精度等から、各分割画素のフォトダイオード間の隙間を全くなくすことは困難である。

【0009】

このような理由により、撮像に使用する画素を構成する複数の分割画素の間には、各分割画素を分離する分離領域が必要となっている。

【0010】

しかし、感度を持たない分離領域があるために、各分割画素の出力信号を加算して、1つの撮像信号として画素信号を使用する際には、画素を分割しない構成の場合と比べて、分離領域の分だけ感度が低下してしまう。

20

【0011】

また、分離領域が感度を持たないため、分離領域に到達する光束は出力信号には現れなくなるが、撮影レンズの状態や、絞り量、入射光の角度等によって画素が受光する光量に対する分離領域に到達する光量が変動してしまう。このため、出力信号に絞り依存性や、入射角依存性などが生じてしまう。

【0012】

このような分割画素の感度低下を低減するために、特許文献2のように分割画素のフォトダイオードの前方に層内レンズを配置し集光する方法が提案されている。しかし、層内レンズはその形状や曲率の制約から、画素に入射した光束を全て、分離領域を避けていずれかの分割画素のフォトダイオードに集光することは困難であり、結果として、画素を分割しない構成の場合と比べて感度が低下してしまう。

30

【0013】

また、特許文献3のように分割画素への入射光の分離を目的として、分割画素の前方に隙間を設ける方法も提案されている。しかし、分割画素前方に配する隙間自体が分離領域に相当するため、画素を分割しない構成の場合と比べて、感度の低下や入射角特性の劣化を発生させてしまう。

【0014】

本発明は、上記課題に鑑みてなされ、その目的は、分割画素を有する撮像素子において、画素分離領域の影響による撮像信号の感度低下や入射角特性の劣化等を発生させない構造を実現することである。

40

【課題を解決するための手段】

【0015】

上記課題を解決し、目的を達成するために、本発明は、マイクロレンズを共有し、且つ分離層にて複数の領域に分割された光電変換部と、前記マイクロレンズにて集光された光束を前記光電変換部に導くとともに前記分離層には導かない光導波路と、電極が配置され前記分離層を覆う絶縁層と、を有する撮像素子であって、前記分離層は前記光電変換部で発生した電荷を転送するための転送電極を備え、前記絶縁層は前記光導波路内の光を反射するための境界面を有し、前記光導波路は、前記複数の領域に分割された光電変換部の各々の上面に積層され、前記光導波路上に前記絶縁層が積層され、前記絶縁層上に前記マイクロレンズが積層され、光入射方向において、前記光導波路の各々の前記光電変換部側の

50

面は、前記分離層に備わる前記転送電極を覆わずに前記光電変換部の光入射面を覆い、光入射方向において、前記光導波路の各々の前記絶縁層と接する側の面は、平面であり、前記分離層と前記光電変換部の光入射面を覆っている。

**【発明の効果】**

**【0016】**

本発明によれば、分割画素を有する撮像素子において、画素分離領域の影響による撮像信号の感度低下や入射角特性の劣化等を発生させない構造を実現できる。

**【図面の簡単な説明】**

**【0017】**

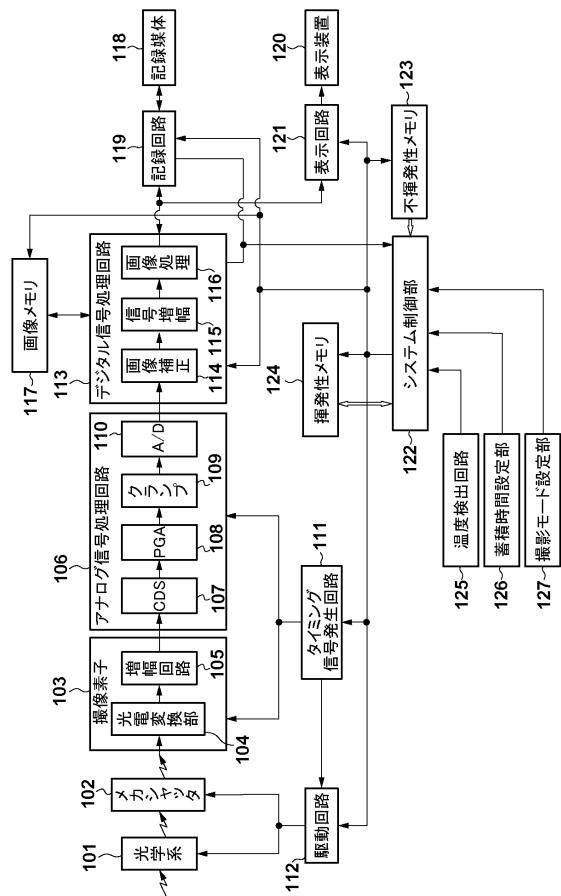

【図1】本発明に係る実施形態の撮像装置の構成を示すブロック図。

10

【図2】本実施形態に係る撮像素子の画素配列を示す図

【図3】実施形態1に係る撮像素子の断面図。

【図4】本実施形態に係る撮像素子の一部の概略断面図。

【図5】本実施形態に係る撮像素子の回路図。

【図6】本実施形態に係る第1の駆動タイミングを示すタイミングチャート。

【図7】本発明の実施形態に係る第2の駆動タイミングを示すタイミングチャート。

**【発明を実施するための形態】**

**【0018】**

以下に、本発明を実施するための形態について詳細に説明する。尚、以下に説明する実施の形態は、本発明を実現するための一例であり、本発明が適用される装置の構成や各種条件によって適宜修正又は変更されるべきものであり、本発明は以下の実施の形態に限定されるものではない。また、後述する各実施形態の一部を適宜組み合わせて構成しても良い。

20

**【0019】**

<装置構成>図1を参照して、本発明に係る実施形態の撮像装置の構成について説明する。

**【0020】**

図1において、光学系101はレンズおよび絞りからなる。シャッタ102は機械的に作動するメカニカルシャッタ(以下、メカシャッタ)である。撮像素子103は、光学系101を通じた入射光を電気信号に変換するCMOSセンサであり、撮像素子103の内部において入射光を電気信号に変換する光電変換部104と、撮像素子103の内部において電気信号を增幅させる信号增幅回路105とを有する。

30

**【0021】**

アナログ信号処理回路106は、撮像素子103から出力される画像信号に対してアナログ信号処理を行う。アナログ信号処理回路106は、回路内部で相關二重サンプリングを行うCDS回路107、アナログ信号を增幅させる信号増幅器108、水平OBクランプを行うクランプ回路109、アナログ信号をデジタル信号に変換するA/D変換器110を有する。

**【0022】**

タイミング信号発生回路111は、撮像素子103およびアナログ信号処理回路106を動作させる信号を発生する。駆動回路112は、光学系101、メカシャッタ102を駆動する。

40

**【0023】**

デジタル信号処理回路113は、撮影した画像データに必要なデジタル信号処理を行う。デジタル信号処理回路113は、回路内部で画像データに対し必要な補正処理を行う画像補正回路114、デジタル信号を增幅させる信号増幅回路115、画像データに対し必要な画像処理を行う画像処理回路116を有する。

**【0024】**

画像メモリ117は、信号処理された画像データを記憶する。記録媒体118は撮像装置に対して着脱可能であり、記録回路119は信号処理された画像データを記録媒体11

50

8に記録する。表示装置120は、信号処理された画像データを表示するLCDなどからなり、表示回路121は、表示装置120に画像を表示する。

【0025】

システム制御部122は、撮像装置全体を制御する。不揮発性メモリ(ROM)123は、システム制御部122で実行される制御プログラムやプログラムを実行する際に使用されるパラメータやテーブル等の制御データ、および、キズアドレス等の補正データを記憶する。揮発性メモリ(RAM)124は、不揮発性メモリ123から転送される制御プログラム、制御データや補正データを記憶し、システム制御部122が撮像装置を制御する際に使用する。

【0026】 10

温度検出回路125は、撮像素子103やその周辺回路の温度を検出する。蓄積時間設定部126は、撮像素子103の電荷蓄積時間を設定する。撮影モード設定部127は、ISO感度設定などの撮影条件設定や、静止画撮影と動画撮影の切り替えなどを行う。

【0027】

＜動作説明＞次に、図1の構成を有する撮像装置による撮影動作及び再生動作について説明する。

【0028】

撮影動作に先立ち、電源投入時等のシステム制御部122の起動時において、不揮発性メモリ123から必要なプログラム、制御データおよび補正データが転送されて、揮発性メモリ124に記憶される。また、これらのプログラムやデータは、システム制御部122の制御に使用すると共に、必要に応じて追加のプログラムやデータをメモリ123からメモリ124に転送したり、システム制御部122が直接不揮発性メモリ123のデータを読み出して使用する。 20

【0029】

まず、光学系101は、システム制御部122からの制御信号により、絞りとレンズを駆動して、適切な明るさに設定された被写体像を撮像素子103上に結像させる。次に、メカシャッタ102は、静止画像撮影の際には、システム制御部122からの制御信号に応じて、必要な露光時間となるように撮像素子103の電荷蓄積動作に合わせて撮像素子103を遮光するように駆動される。この場合、撮像素子103が電子シャッタ機能を有する場合は、メカシャッタ102と併用して、必要な露光時間を確保してもよい。またメカシャッタ102は、動画撮影の際には、システム制御部122からの制御信号により、撮影中は常に撮像素子103が露光されているように開放状態で維持される。 30

【0030】

撮像素子103は、システム制御部122により制御されるタイミング信号発生回路111が発生する動作パルスをもとにした駆動パルスで駆動される。撮像素子103の光電変換部104は被写体像を光電変換により電気信号に変換し、信号增幅回路105は入射光量に応じて設定された増幅率のゲインを電気信号にかけ、アナログ画像信号として出力する。

【0031】

撮像素子103から出力されたアナログ画像信号は、システム制御部122により制御されるタイミング信号発生回路111が発生する動作パルスにより、アナログ信号処理回路106において、CDS回路107がクロック同期性ノイズを除去し、PGA回路108が入射光量に応じて設定された増幅率のゲインをかけ、クランプ回路109が水平OB領域の信号出力を基準電圧としてクランプし、A/D変換器110がデジタル画像信号に変換する。 40

【0032】

次に、アナログ信号処理回路106から出力されたデジタル画像信号に対して、システム制御部122に制御されるデジタル信号処理回路113は、色変換、ホワイトバランス、ガンマ補正等の画像処理、解像度変換処理、画像圧縮処理等を行う。まず画像補正回路114がキズ補正、ダークシェーディング補正などの各種画像補正処理を施す。次いで信

号增幅回路 115 は入射光量に応じて設定された增幅率のゲインをかけ、画像処理回路 116 が色変換、ホワイトバランス、ガンマ補正等の画像処理、解像度変換処理、画像圧縮処理等の各種画像処理を行う。

【0033】

画像メモリ 117 は、信号処理中のデジタル画像信号を一時的に記憶したり、信号処理されたデジタル画像信号である画像データを記憶する。

【0034】

デジタル信号処理回路 113 で信号処理された画像データや画像メモリ 117 に記憶されている画像データは、記録回路 119 で記録媒体 118 に適したデータ形式（例えば階層構造を持つファイルシステムデータ）に変換されて記録媒体 118 に記録される。また、デジタル信号処理回路 113 で解像度変換処理が実施された後、表示回路 121 において表示装置 120 に適した信号（例えばNTSC 方式のアナログ信号等）に変換されて表示装置 120 に表示される。10

【0035】

ここで、デジタル信号処理回路 113 は、システム制御部 122 からの制御信号により信号処理をせずにデジタル画像信号をそのまま画像データとして、画像メモリ 117 や記録回路 119 に出力してもよい。また、デジタル信号処理回路 113 は、システム制御部 122 から要求があった場合に、信号処理の過程で生じたデジタル画像信号や画像データの情報、例えば、画像の空間周波数、指定領域の平均値、圧縮画像のデータ量等の情報、あるいは、それらから抽出された情報をシステム制御部 122 に出力する。さらに、記録回路 119 は、システム制御部 122 から要求があった場合に、記録媒体 118 の種類や空き容量等の情報をシステム制御部 122 に出力する。20

【0036】

次に、記録媒体 118 に画像データが記録されている場合の再生動作について説明する。。

【0037】

システム制御部 122 からの制御信号により記録回路 119 は、記録媒体 118 から画像データを読み出す。同様にシステム制御部 122 からの制御信号によりデジタル信号処理回路 113 は、画像データが圧縮画像であった場合には、伸長処理を行い、画像メモリ 117 に記憶する。画像メモリ 117 に記憶されている画像データは、デジタル信号処理回路 113 で解像度変換処理を実施した後、表示回路 121 において表示装置 120 に適した信号に変換されて表示装置 120 に表示される。30

【0038】

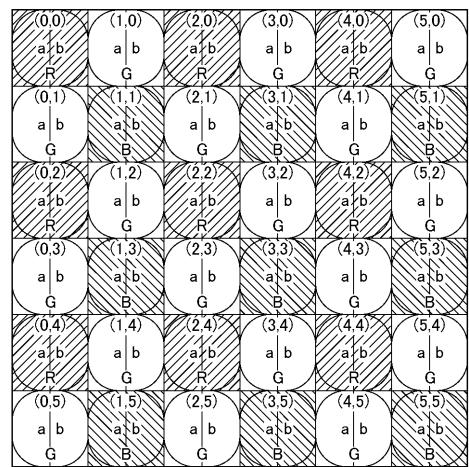

＜画素配列の説明＞図 2 を参照して、本実施形態の撮像素子の画素配列について説明する。

【0039】

図 2 において、図中 (0, 0)、(1, 0)、(0, 1) 等で示される各領域は、撮像信号における 1 画素を示している。また、この撮像信号における 1 画素毎に、1 つのマイクロレンズが配置されている。本明細書では、1 つのマイクロレンズ毎にある、撮像信号に用いる単位画素を、撮像画素と呼ぶ。40

【0040】

また、図中の a 及び b で示される各領域は、それぞれ異なる光電変換部である。本明細書では、このように撮像画素を複数に分割したそれぞれの光電変換部を分割画素と呼ぶ。図 2 に示す実施形態では、撮像画素は、 $2 \times 1$  配列された分割画素 2 画素で構成されており、各領域 a 及び b は、同一の記号の領域は、マイクロレンズとの位置関係において同じ象現にあることを意味する。

【0041】

また、図中の各領域に記された「R」、「G」、「B」の文字は、各画素上に形成されるカラーフィルタの色相を表す。

【0042】

10

20

30

40

50

図2に示す画素配列を有する像素子を用いた撮像装置においては、撮像信号を生成する場合は、各分割画素の「a, b領域の出力信号の和」を持って撮像画素1画素の出力信号とする。

【0043】

また、像素子の出力を焦点検出用信号もしくは立体画像生成用信号として使用する場合には、「a領域の出力信号」と「b領域の出力信号」の2つの信号を生成するなどして利用する。

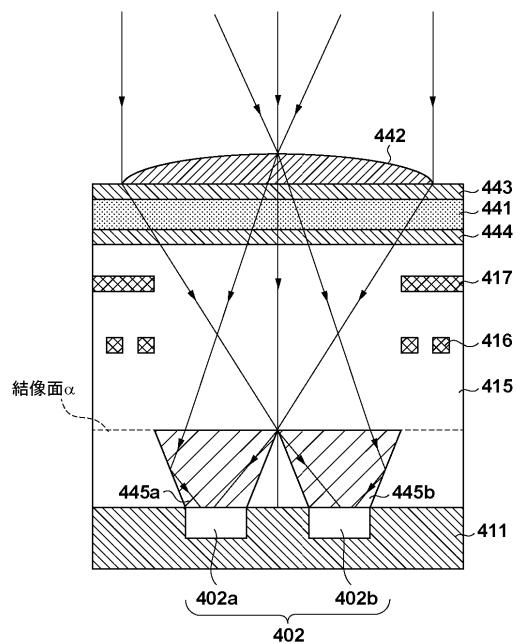

【0044】

＜各画素の像素子断面構造＞図3を参照して、図2に示す各画素の像素子の断面構造について説明する。

10

【0045】

図3に示す画素は、図2で説明した、像素子103における2つの分割画素で構成される1つの撮像画素であり、光電変換部402が2つの領域(402a及び402b)に分割されている。光電変換部402の周辺には、光電変換部402で発生した電荷を転送するためのポリシリコンで構成された不図示の第1の電極が配置される。

【0046】

また、転送された電荷を選択的に外部に出力するためのアルミニウムで構成された第2の電極416及び第3の電極417が配置される。第1の電極と第2の電極416との間、及び、第2の電極416と第3の電極417との間には、層間絶縁膜415が配置される。第1の電極と第2の電極416、及び、第2の電極416と第3の電極417とは、タンゲステンで構成された不図示の第1のプラグ及び第2のプラグでそれぞれ接続されている。

20

【0047】

光電変換部402の光入射側には、光導波路445a及び445bが形成される。光導波路445a及び445bの光入射側には、層間絶縁膜415が配置される。層間絶縁膜415の光入射側には、平坦化層444を介してカラーフィルタ441が形成される。

【0048】

カラーフィルタ441の上には、平坦化層443を介してマイクロレンズ442が形成される。マイクロレンズ442の厚さは、不図示の撮影レンズの瞳と光導波路445a及び445bの上面(図3の結像面)とが略結像関係になるレンズパワーになるように設定されている。

30

【0049】

次に、本実施形態に係る像素子103に入射する光について説明する。

【0050】

図3に示す画素構造では、マイクロレンズ442に入射した焦点検出光束は集光され、カラーフィルタ441で一部吸収され、光導波路445a及び445bの表面(結像面)近傍に集光する。マイクロレンズ442によって、不図示の撮影レンズの瞳と光導波路445a及び445bの表面(結像面)とが略結像関係になっており、光導波路445a及び445bに入射した光束は光電変換領域402a及び402bに到達する。このため、光電変換領域402a及び402bは、各光電変換領域を撮影レンズの瞳側に逆投影した瞳領域の光束を受光可能になっている。

40

【0051】

光導波路445a及び445bに入射した光束は、光導波路445a及び445bと層間絶縁膜415との境界面で全反射して、光電変換領域402a及び402bに導かれる。

【0052】

以上説明した像素子の構造においては、本来、光電変換領域402aと402bの間に有る、分割画素の分離領域に集光されるはずの光束も、光導波路445a及び445bを介して光電変換領域402a及び402bに集光可能となっている。

【0053】

50

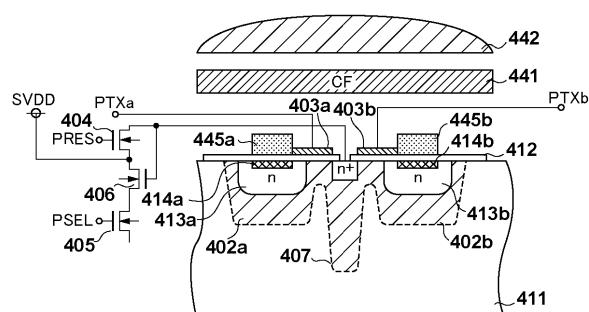

図4は本実施形態の撮像素子の部分断面図である。

【0054】

図4において、411はP型ウェル、412はSiO<sub>2</sub>膜で構成されたゲート絶縁膜である。414a及び414bは、P型ウェル411の表面に形成されたP+層であり、n層413a及び413bと共に光電変換領域402a及び402bを構成する。403a及び403bは、光電変換領域402a及び402bで発生した信号電荷をフローティングディフィュージョン部(以下、FD部)407へ転送するための転送ゲートである。441はカラーフィルタ、442はマイクロレンズ(オンチップレンズ)であり、マイクロレンズ442は、不図示の撮影レンズ(光学系101)の瞳と撮像素子103の光電変換領域402a及び402bとが略共役になるような形状及び位置に形成される。

10

【0055】

また、光電変換領域402a及び402bとカラーフィルタ441との間であって、マイクロレンズ442の結像位置の近傍又は後方には、それぞれ光導波路445a及び445bが配置される。

【0056】

また、この画素では、FD部407を挟んで2つの領域に光電変換領域402a、402bがそれぞれ形成される。さらに、各光電変換領域402a、402bで発生した信号電荷をそれぞれFD部407へ転送する転送ゲート403a、403bが形成される。

【0057】

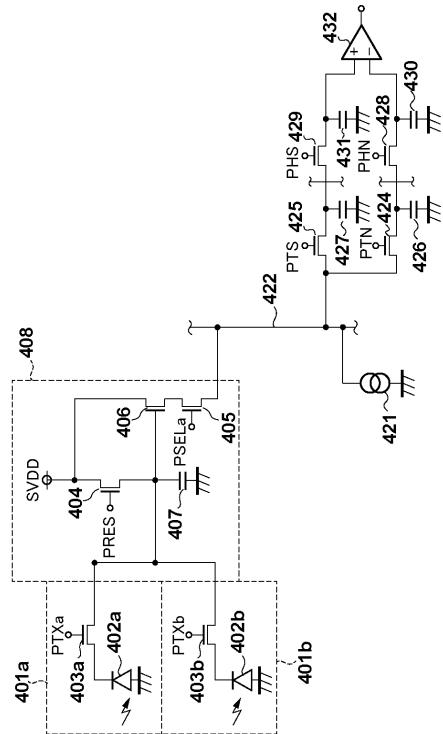

図5は本実施形態の撮像素子を構成するCMOS回路図である。

20

【0058】

図5において、撮像素子は、2つの分割画素401に対し、1つの浮遊拡散層FD407が接続される構成とする。撮像素子103の画素領域は、1画素毎に配置される分割画素401と、2つの分割画素毎に配置される画素共通部408により構成される。分割画素401は、光電変換素子であるフォトダイオード402、フォトダイオード402の光電変換によって生成された電荷をパルスPTXによって転送する転送スイッチ403で構成されている。

【0059】

画素共通部408は、各分割画素401の各転送スイッチ403によって転送された電荷を蓄積する浮遊拡散層FD407、画素アンプ406のゲートと接続された浮遊拡散層FD407をリセットパルスPREによって電位SVDDのレベルにリセットするリセットスイッチ404、浮遊拡散層FD407に蓄積された電荷をソースフォロワとして増幅する画素アンプ406、不図示の垂直走査回路により選択される行画素を選択パルスPSELにより選択する行選択スイッチ405を有する。

30

【0060】

なお、図5に示す撮像素子の画素部においては、フォトダイオード402a、402bで光電変換された電荷は、転送スイッチ403a、403bを制御することによって、いずれも浮遊拡散層FD407に転送されるような構成としている。

【0061】

行選択スイッチ405によって選択された行画素の電荷は、負荷電流源421にソースフォロワにより垂直出力線422に出力され、信号出力パルスPTSにより転送ゲート425をONとして転送容量CTS427に蓄積され、ノイズ出力パルスPTNにより転送ゲート424をONとして転送容量CTN426に蓄積される。

40

【0062】

続けて不図示の水平走査回路からの制御信号PHS、PHNにより転送スイッチ428、429を介してノイズ成分は容量CHN430に、信号成分は容量CHS431に蓄えられ、両者の差分を差動増幅器432によって画素信号として出力する。

【0063】

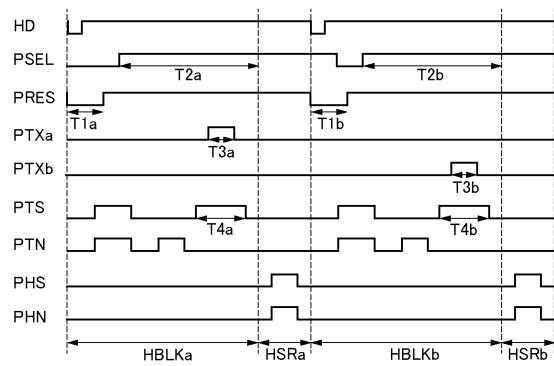

図6は本実施形態における第1の駆動タイミングを示している。

【0064】

50

図6において、第1の駆動タイミングは、図2に示す分割画素それぞれの出力信号を独立に読み出すための駆動タイミングである。この第1の駆動タイミングによる信号読み出しを行う場合には、出力信号をデジタル信号処理回路113において焦点検出用信号もしくは立体画像生成用信号と加工して利用することが可能となる。

【0065】

第1の駆動においては、分割画素a, bの順に読み出すような構成としている。

【0066】

まず、HBLKa + HSRaの期間に、単位画素901aの信号の読み出しを行う。1水平走査期間の開始を示す信号HDの立下りに伴い、不図示の回路により垂直出力線422は定電位にリセットされる。その後、PRES信号でMOSトランジスタ404aがONされることにより、T1aの期間にMOSトランジスタ406aのゲートに設けられたフローティングの容量407に蓄積された電荷が定電位SVDになるようにリセットされる。

10

【0067】

続いてPRES信号をハイレベルとしMOSトランジスタ406をOFFとした後、PSEL信号をハイレベルにする。これにより、MOSトランジスタ405と負荷電流源421で構成されたソースフォロワ回路が動作状態になり、垂直出力線422上にMOSトランジスタ406のフローティングゲートリセット電位に応じたノイズ出力がなされる。このPSELがハイレベルの期間にPTN信号をハイレベルにすることで、ノイズ成分を蓄積する蓄積容量CTN424が垂直出力線422と接続され、この蓄積容量CTN424はノイズ成分の信号を保持するようになる。

20

【0068】

続いて実行するのは、光電変換素子で発生した光電荷とノイズ成分の混合信号の蓄積である。まず垂直出力線422は、不図示の回路により、定電位にリセットされる。その後PTXa信号がハイレベルにされ、光電変換素子402aに蓄積された光電荷がT3aの期間に転送MOSトランジスタ403aのONにより、MOSトランジスタ406のフローティングゲートに転送される。その際、PSEL信号はハイレベルのままであるために、ソースフォロワ回路が動作状態となり、垂直出力線422上にMOSトランジスタ406のフローティングゲートの電位に応じた「光信号+ノイズ信号」の出力がなされる。このT3aの期間を内包する期間T4aの間に、今回はPTS信号をハイレベルにする。これにより、「光電荷成分+ノイズ成分」を蓄積する蓄積容量CTS427が垂直出力線422と接続され、この蓄積容量CTS427は光電荷成分+ノイズ成分の信号を保持するようになる。

30

【0069】

上述のように、1行分のノイズ成分と、フォトダイオードで発生した光信号+ノイズ成分が、それぞれCTN426, CTS427に蓄積される。

【0070】

次に、HSRaの期間に、これら2信号の並びを不図示の水平シフトレジスタにより制御される制御パルスPHS, PHNによってそれぞれ容量CHN430, CHS431に転送する。そして容量CHN430, CHS431に蓄積されたノイズ成分と光信号+ノイズ成分は、差動アンプ432によって、(光信号+ノイズ成分) - ノイズ成分、すなわち光信号となって出力される。

40

【0071】

続けて、HBLKb + HSRbの期間に、制御信号PTXb, PRES, PSELを制御し、分割画素401bの信号の読み出しを行う。分割画素401bの信号読み出しタイミングは、先に説明した分割画素401aの信号読み出しタイミングと同様のため、説明は省略する。

【0072】

以上のように読み出し動作を行うことで、2つの分割画素401a, 401bの信号読み出しを完了する。

50

## 【0073】

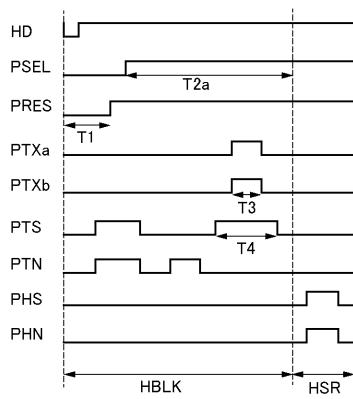

図7は本実施形態の第2の駆動タイミングを示している。

## 【0074】

図7において、第2の駆動タイミングは、図2に示す分割画素それぞれの出力信号を一括で読み出すための駆動タイミングである。この第2の駆動タイミングによる信号読み出しを行う場合には、通常撮像時など、個々の分割画素の出力信号が不要な場合などに、高速に読み出すことが可能となる。

## 【0075】

第2の駆動タイミングにおいて、PSEL信号がハイレベルの期間にPTN信号をハイレベルにすることで、蓄積容量CTN424にノイズ成分の信号を保持するようにするところまでは、図6で説明した第1の駆動タイミングと同じである。

10

## 【0076】

続いて実行するのは、光電変換素子で発生した光電荷とノイズ成分の混合信号の蓄積である。まず垂直出力線422は、不図示の回路により、定電位にリセットされる。その後PTXa、PTXb信号が同時にハイレベルにされ、光電変換領域402a, 402bに蓄積された光電荷がT3の期間に転送MOSトランジスタ403のONにより、MOSトランジスタ406のフローティングゲートに転送される。その際、PSEL信号はハイレベルのままであるために、ソースフォロワ回路が動作状態となり、垂直出力線422上にMOSトランジスタ406のフローティングゲートの電位に応じた「光信号+ノイズ信号」の出力がなされる。

20

## 【0077】

このT3の期間を内包する期間T4の間に、今回はPTS信号をハイレベルにする。これにより、「光電荷成分+ノイズ成分」を蓄積する蓄積容量CTS427が垂直出力線422と接続され、この蓄積容量CTS427は光電荷成分+ノイズ成分の信号を保持するようになる。

## 【0078】

上述のように、1行分のノイズ成分と、フォトダイオードで発生した光信号+ノイズ成分が、それぞれCTN426, CTS427に蓄積される。

## 【0079】

次に、HSRの期間に、これら2信号の並びを不図示の水平シフトレジスタにより制御される制御パルスPHS, PHNによってそれぞれ容量CHN430, CHS431に転送する。そして容量CHN430, CHS431に蓄積されたノイズ成分と光信号+ノイズ成分は、差動アンプ432によって、(光信号+ノイズ成分)-ノイズ成分、すなわち光信号となって出力される。

30

## 【0080】

以上、図1乃至図7を参照しつつ本実施形態にかかる撮像装置について説明してきたが、本発明はこれに限定されず、様々な形態をとることが可能である。

## 【0081】

例えば、図2乃至図5で説明した画素構成について、画素の構造をわかりやすく説明するため、マイクロレンズを共有する分割画素を2分割の構成としたが、本発明はこれに限定されず、2×2の4分割など、3分割以上の分割画素を有する構成としてもよい。

40

## 【0082】

また、図3で説明した撮像素子の各画素の素子断面構造については、光導波路445の光入射面(結像面)は、第2の電極416や第3の電極417よりも光電変換部402に近い側として説明したが、本発明はこれに限定されない。すなわち、結像面及び結像面が撮影レンズの瞳と略結像関係になるようにマイクロレンズ442の曲率を構成していれば、光導波路445とその他の構成要素との位置関係は、どのような態様でも構わない。例えば、マイクロレンズ442の曲率を変えて、第3の電極層中で結像するように、光導波路を第3の電極層中から形成することで、光電変換層を下方にシフトさせなくてもよい構造となる。

50

【図1】

【 図 2 】

【図3】

【 図 4 】

【 図 5 】

【 四 6 】

【図7】

---

フロントページの続き

(72)発明者 鈴木 聰史

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 上田 智志

(56)参考文献 特開2009-158800 (JP, A)

特開2011-159967 (JP, A)

特開2008-141014 (JP, A)

特開2002-076312 (JP, A)

特開平05-090551 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14