### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2013/147936 A1

(43) International Publication Date 3 October 2013 (03.10.2013)

(51) International Patent Classification: *G11C 11/56* (2006.01) *G11C 16/10* (2006.01) *G11C 16/04* (2006.01)

(21) International Application Number:

PCT/US2012/066610

(22) International Filing Date:

27 November 2012 (27.11.2012)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

13/430,494 26 March 2012 (26.03.2012)

US

- (71) Applicant (for all designated States except US): SANDISK TECHNOLOGIES, INC. [US/US]; Two Legacy Town Center, 6900 North Dallas Parkway, Plano, TX 75024 (US).

- (72) Inventors; and

- (71) Applicants (for US only): LAI, Chun-Hung [—/JP]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). SATO, Shinji [JP/JP]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). LEE, Shih-Chung [JP/JP]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US). HEMINK, Gerrit Jan [NL/JP]; 601 McCarthy Boulevard, Milpitas, CA 95035 (US).

- (74) Agent: MAGEN, Burt; Vierra Magen Marcus & DeNiro, LLP, 575 Market Street, Suite 2500, San Francisco, CA 94105 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

— with international search report (Art. 21(3))

(54) Title: SELECTED WORD LINE DEPENDENT SELECT GATE DIFFUSION REGION VOLTAGE DURING PROGRAMN-MING

FIG. 19

(57) Abstract: Methods and devices for operating non-volatile storage are disclosed. One or more programming conditions depend on the location of the word line that is selected for programming. Applying a selected word line dependent program condition may reduce or eliminate program disturb. The voltage applied to a common source line may depend on the location of the word line that is selected for programming. This may prevent or reduce punch-through conduction, which may prevent or reduce program disturb. The voltage applied to bit lines of unselected NAND strings may depend on the location of the word line that is selected for programming. This may prevent or reduce punch-through conduction.

-1-

# SELECTED WORD LINE DEPENDENT SELECT GATE DIFFUSION REGION VOLTAGE DURING PROGRAMMING

### BACKGROUND

[0001] The present disclosure relates to non-volatile storage.

[0002] Semiconductor memory has become increasingly popular for use in various electronic devices. For example, non-volatile semiconductor memory is used in cellular telephones, digital cameras, personal digital assistants, mobile computing devices, non-mobile computing devices and other devices. Electrically Erasable Programmable Read Only Memory (EEPROM) and flash memory are among the most popular non-volatile semiconductor memories. With flash memory, also a type of EEPROM, the contents of the whole memory array, or of a portion of the memory, can be erased in one step, in contrast to the traditional, full-featured EEPROM.

[0003] Both the traditional EEPROM and the flash memory utilize a floating gate that is positioned above and insulated from a channel region in a semiconductor substrate. The floating gate is positioned between the drain and source diffusion regions. A control gate is provided over and insulated from the floating gate. The threshold voltage  $(V_{TH})$  of the transistor thus formed is controlled by the amount of charge that is retained on the floating gate. That is, the minimum amount of voltage that must be applied to the control gate before the transistor is turned on to permit conduction between its drain and source is controlled by the level of charge on the floating gate.

[0004] In a NAND architecture, memory cells are arranged as NAND strings. A NAND string includes memory cells (each including a floating gate) connected in series over a substrate. At each end of the NAND string there is a select transistor (also referred to as a select gate). One of the

-2-

select transistors (source side select transistor) connects/disconnects the NAND string to a source line that is common to a large group of NAND strings. Each NAND string is associated with one bit line. The other select transistor (drain side select transistor) connects/disconnects its NAND string to a bit line. In one approach, a memory cell on a NAND string may be read by applying a voltage to its control gate and sensing a signal on the bit line.

[0005] Typically, a program voltage  $V_{PGM}$  applied to the control gate during a program operation is applied as a series of pulses that increase in magnitude as programming progresses. In one possible approach, the magnitude of the pulses is increased with each successive pulse by a predetermined step size, e.g., 0.2-0.4 V.  $V_{PGM}$  can be applied to the control gates of flash memory cells. In the periods between the program pulses, verify operations are carried out. That is, the programming level of each element of a group of cells being programmed in parallel is read between successive programming pulses to determine whether it is equal to or greater than a verify level to which the element is being programmed.

[0006] After a given memory cell on the word line selected for programming reaches its intended threshold voltage, programming may be inhibited for that memory cell. In one approach, programming is inhibited by applying an inhibit voltage to the bit line associated with the NAND string. The voltage applied to the gate of the drain side select transistor should be low enough to keep the transistor off, such that the channel of an inhibited NAND string may float. Likewise, the voltage applied to the gate of the source side select transistor should be low enough to keep the transistor off, such that the channel of an inhibited NAND string may float. Also, a voltage is applied to control gates of unselected memory cells, which boosts the voltage in the channel region of the memory cells on inhibited NAND strings. This boosted channel voltage helps to reduce or eliminate program disturb.

[0007] However, it is possible for the channel voltage of the inhibited NAND strings to drop, which can result in program disturb. One possible reason for the drop in channel voltage is leakage of current from a boosted channel. For example, the current could leak across the channel of either select transistor.

[0008] One type of leakage is due to punch-through conduction across a select transistor. Punch-through conduction may occur due to the difference in the drain to source voltage across the channel of a select gate transistor. As memory arrays continue to scale down in size, the channel length of select gate transistors is getting shorter. Therefore, short channel effects such as punch-through conduction may become more problematic.

[0009] Another type of leakage from the channel of inhibited NAND strings may arise due to drain induced barrier lowering (DIBL). DIBL may cause the  $V_{TH}$  of the select transistors to drop. If the  $V_{TH}$  of a select transistor of an inhibited NAND string is lowered enough, it may turn on, at least weakly. If this happens, then current may leak from the boosted channel across the channel of the select transistor, thereby discharging the voltage of the NAND string channel. Consequently, program disturb could occur.

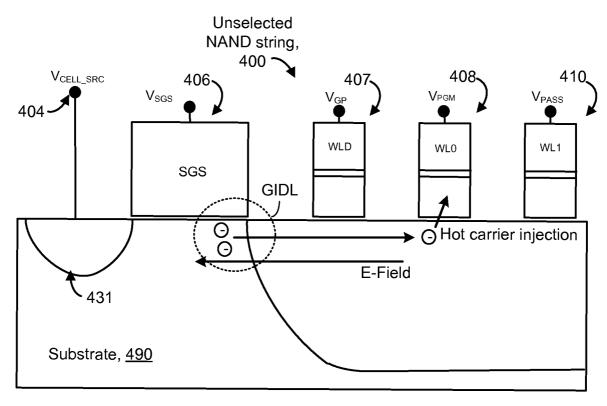

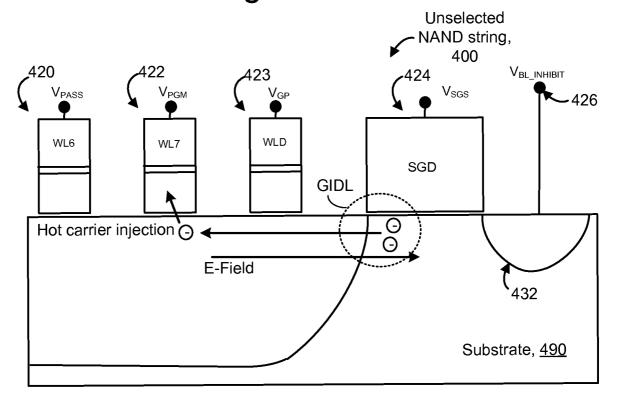

[0010] Gate induced drain leakage (GIDL) is another problem that may cause program disturb. GIDL refers to charge carriers leaking into the channel from a select transistor as a result of a voltage applied to the gate of one of the select transistors. These charge carriers (e.g., electrons) may be accelerated in an E-field in the channel of the NAND string. Program disturb may result due to hot carrier injection of the electrons from the channel to a floating gate of a memory cell.

[0011] It is desirable to prevent or reduce program disturb, which may arise from a variety of causes including, but not limited to, punch-through conduction, DIBL, and GIDL.

## BRIEF DESCRIPTION OF THE DRAWINGS

- [0012] FIG. 1A is a top view of a NAND string.

- [0013] FIG. 1B is an equivalent circuit diagram of the NAND string of FIG. 1A.

- [0014] FIG. 2 is a circuit diagram depicting three NAND strings.

- [0015] FIG. 3 depicts a cross-sectional view of a NAND string formed on a substrate.

- [0016] FIG. 4 illustrates a non-volatile storage device.

- [0017] FIG. 5A depicts an exemplary structure of memory cell array.

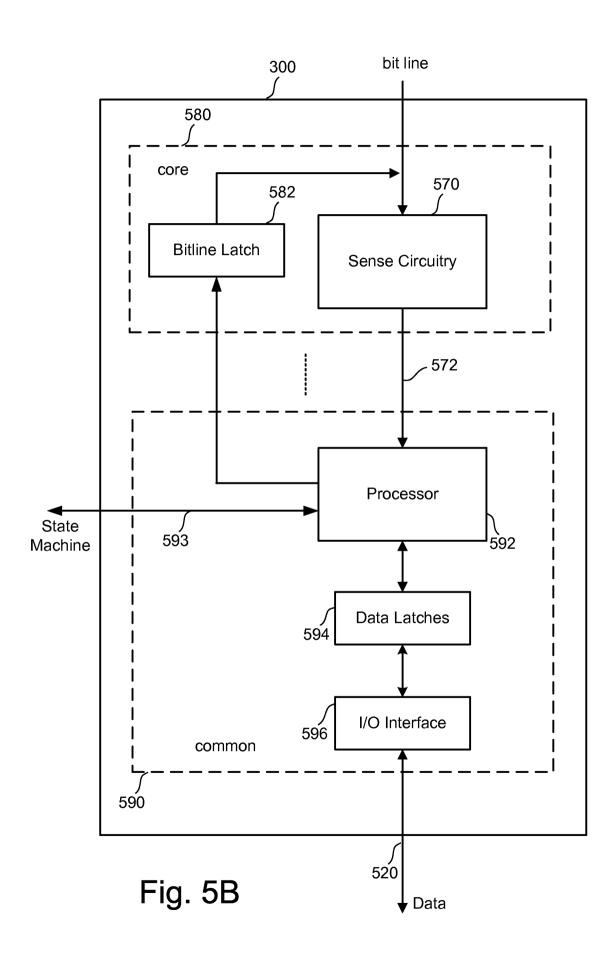

- [0018] FIG. 5B is a block diagram of an individual sense block.

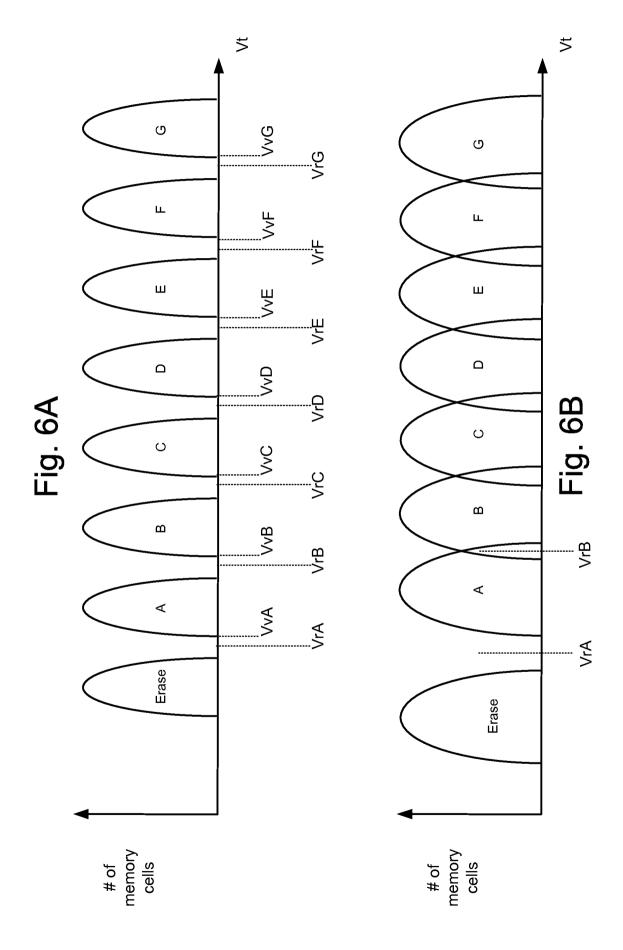

- [0019] FIG. 6A depicts an example set of Vt distributions.

- [0020] FIG. 6B depicts an example set of Vt distributions.

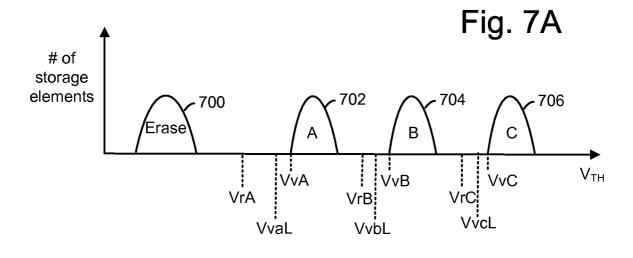

- [0021] FIG. 7A depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data.

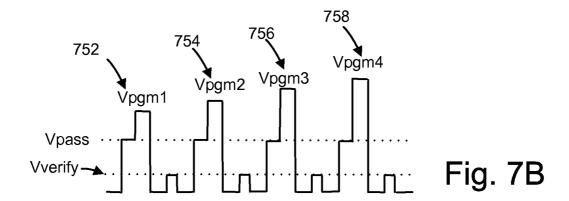

- [0022] FIG. 7B shows a series of program pulses that may be used to program a distribution of FIG 7A.

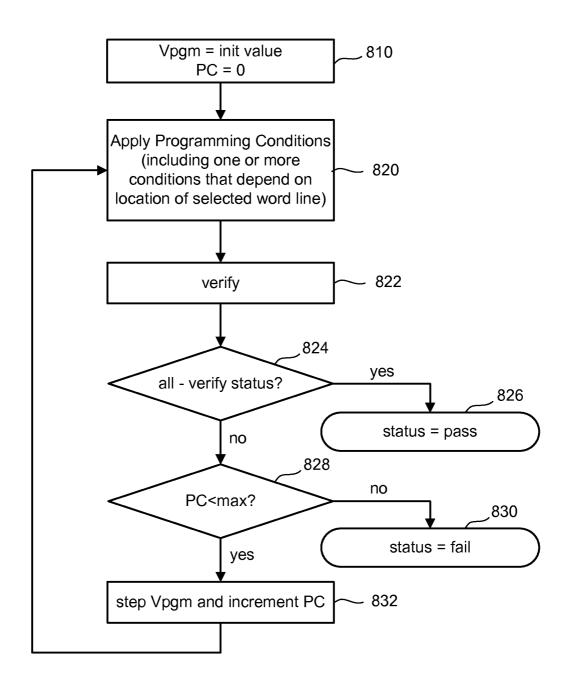

- [0023] FIG. 8 is a flowchart describing one embodiment of a programming process.

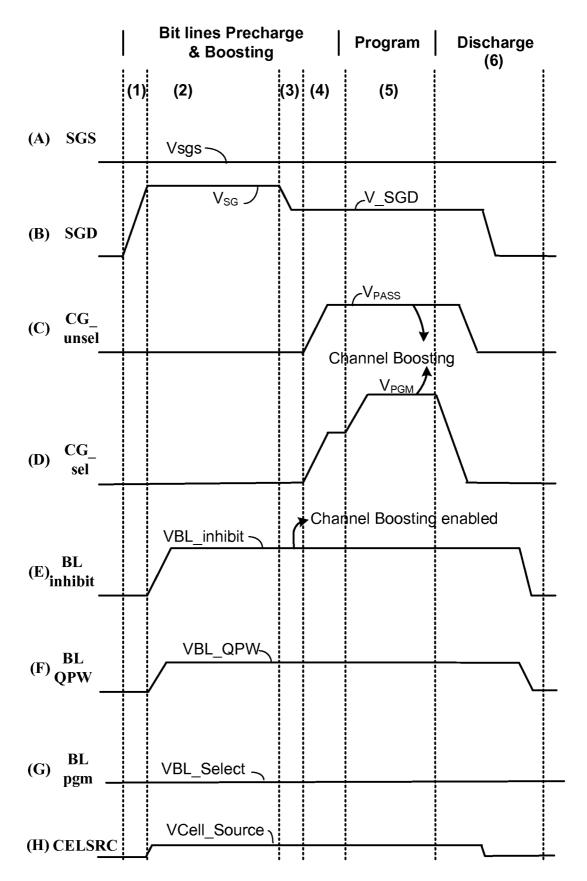

- [0024] FIGs. 9(A) 9(H) are timing diagrams illustrating voltages during program operations, according to one embodiment.

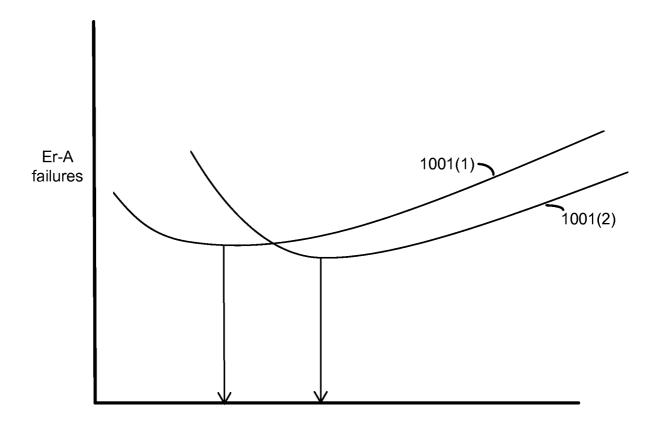

- [0025] FIG. 10 is a graph that shows Erase-to-A failures versus program pulse width for selected word lines in various positions along a NAND string.

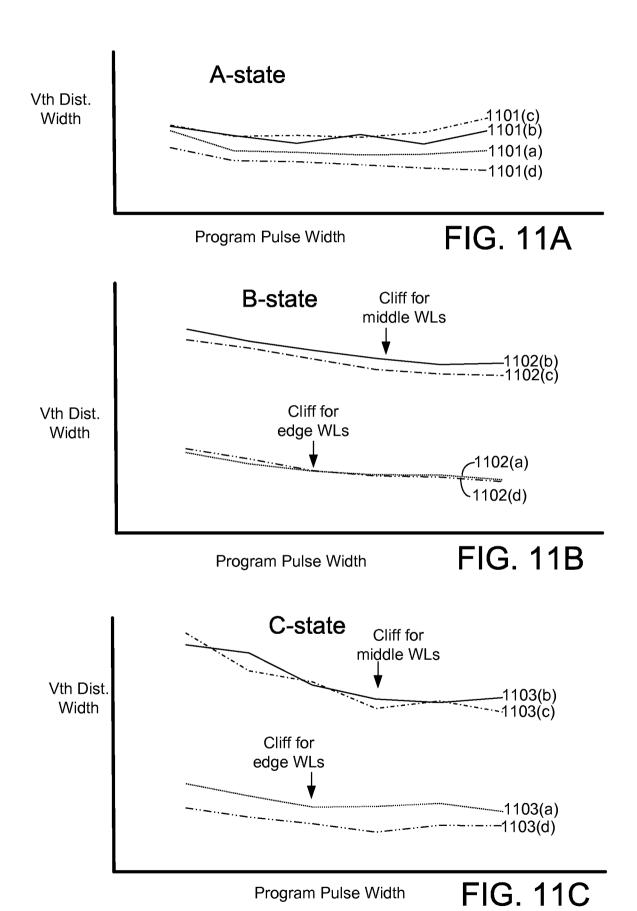

- [0026] FIG. 11A, FIG. 11B, and FIG. 11C show example graphs of Vth distribution widths versus program pulse widths.

- [0027] FIG. 12 shows a graph of program loop count versus program pulse width.

- [0028] FIGs. 13A and 13B are graphs that show word lines RC dependence

- [0029] FIG. 14 is a flowchart of one embodiment of a process of programming non-volatile storage using a programming voltage having a pulse width that depends on the width of the selected word line.

- [0030] FIG. 15 is a flowchart of one embodiment of a process of programming non-volatile storage using a programming voltage having a pulse width that depends on the location of the selected word line.

- [0031] FIG. 16 is a flowchart of one embodiment of a process of programming non-volatile storage that involves determining a width of a program pulse.

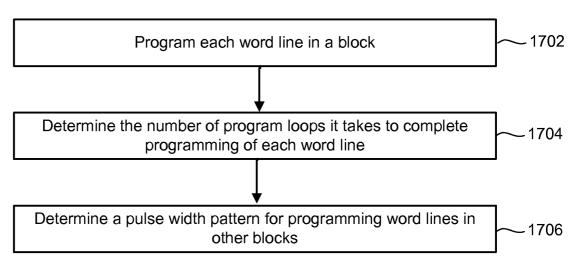

- [0032] FIG. 17 is a flowchart of a process of determining suitable pulse widths for programming signals for word lines, depending on their position.

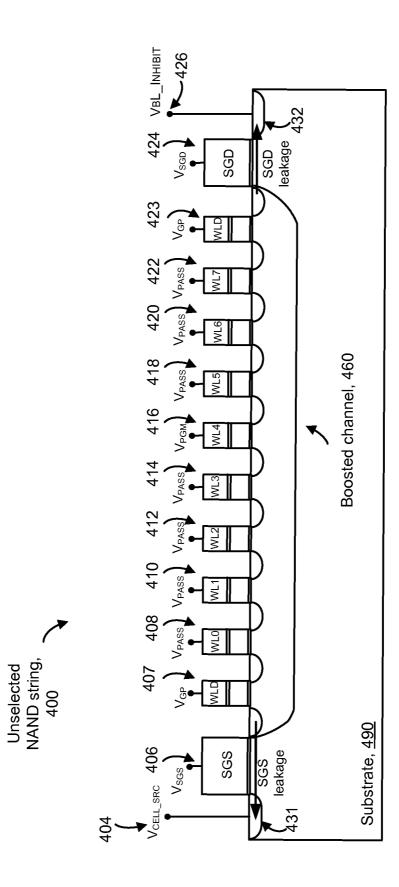

- [0033] FIG. 18A shows a boosted NAND string having SGS leakage current and SGD leakage current.

- [0034] FIG. 18B shows a portion of the NAND string near the SGS transistor to shows GIDL effect.

- [0035] FIG. 18C shows a portion of the NAND string near the SGD transistor to shows GIDL effect.

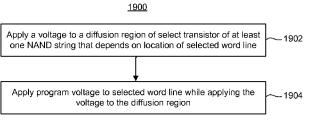

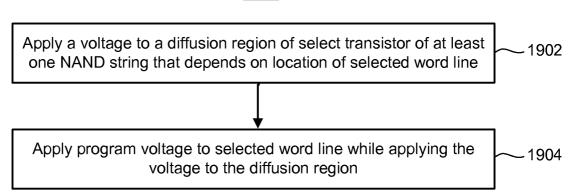

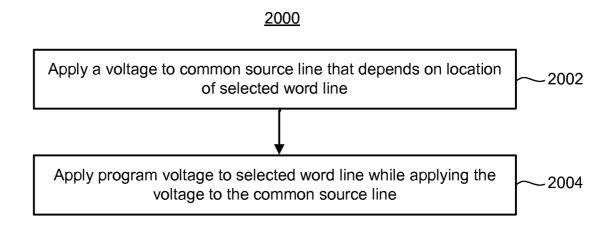

- [0036] FIG. 19 is a flowchart of one embodiment of programming non-volatile storage that may counteract punch-through leakage.

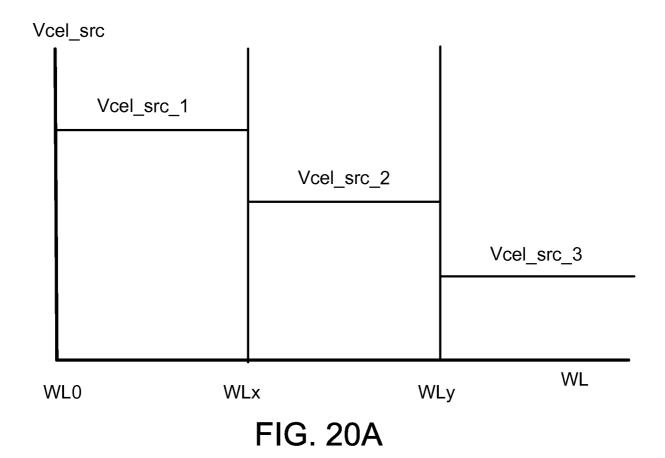

- [0037] FIG. 20A shows relative values for Vcel\_src versus word lines in accordance with one embodiment.

[0038] FIG. 20B depicts a flowchart of one embodiment of a process of programming non-volatile storage in which the voltage applied to the common source line depends on the location of the selected word line.

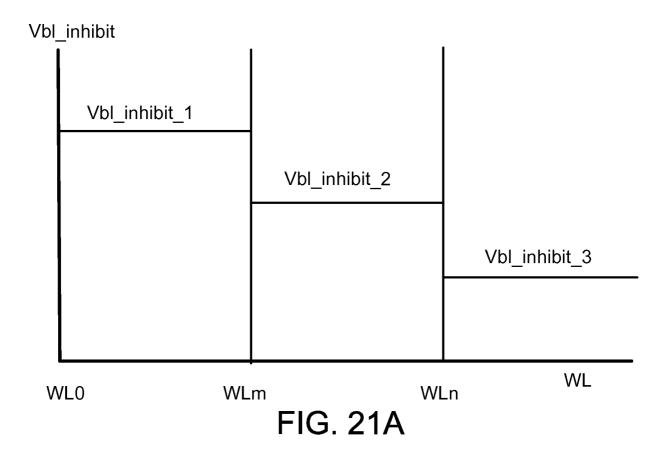

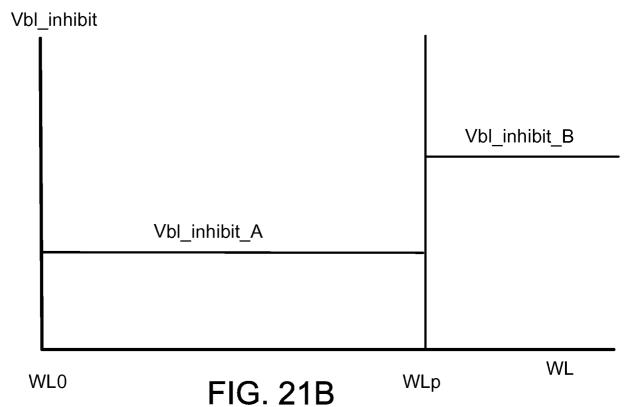

[0039] FIG. 21A shows inhibited bit line voltage versus word line for one embodiment.

[0040] FIG. 21B shows inhibited bit line voltage versus word line for one embodiment.

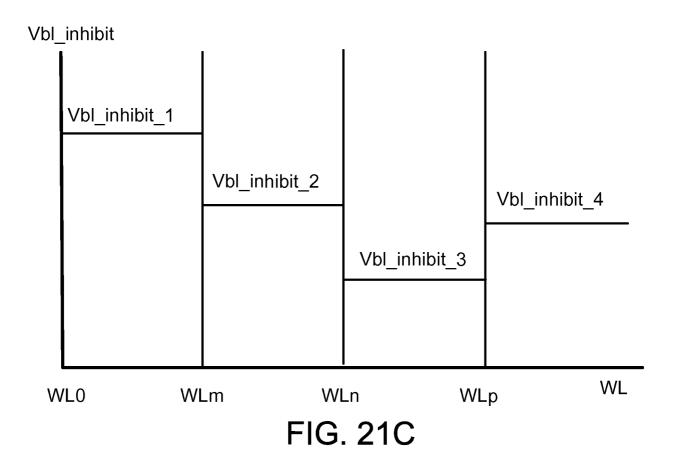

[0041] FIG. 21C shows inhibited bit line voltage versus word line for one embodiment.

[0042] FIG. 21D shows an inhibited NAND string with a boosting scheme referred to as Erase Area Self Boosting (EASB).

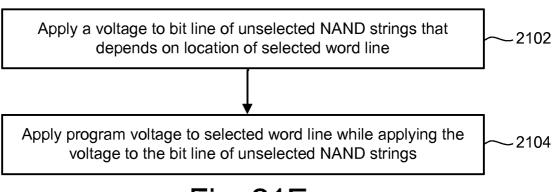

[0043] FIG. 21E depicts a flowchart of one embodiment of a process of programming non-volatile storage in which a bit line voltage depends on the selected word line.

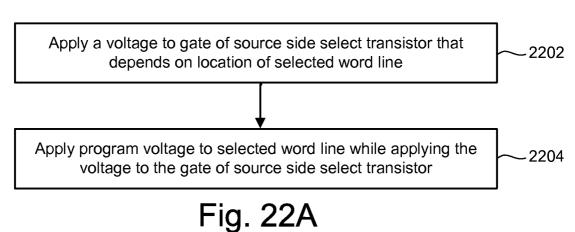

[0044] FIG. 22A depicts a flowchart of one embodiment of a process of programming non-volatile storage in which the magnitude of the voltage SGS depends on the location of the selected word line.

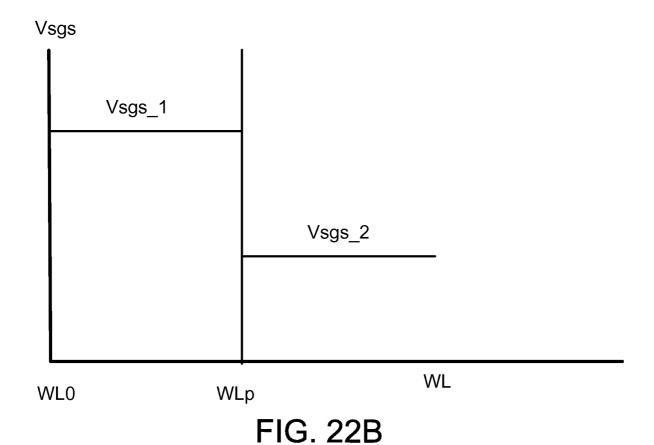

[0045] FIG. 22B shows voltage applied to a gate of a source side select transistor versus word line for one embodiment.

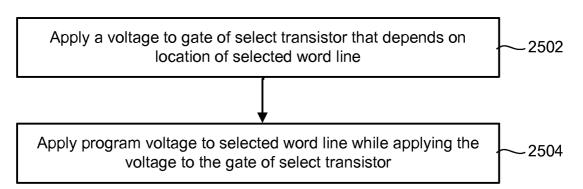

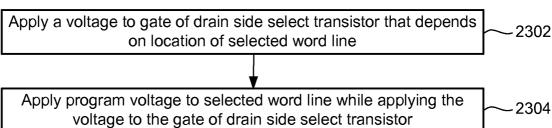

[0046] FIG. 23A depicts a flowchart of one embodiment of a process of programming non-volatile storage in which the magnitude of the voltage SGD depends on the location of the selected word line.

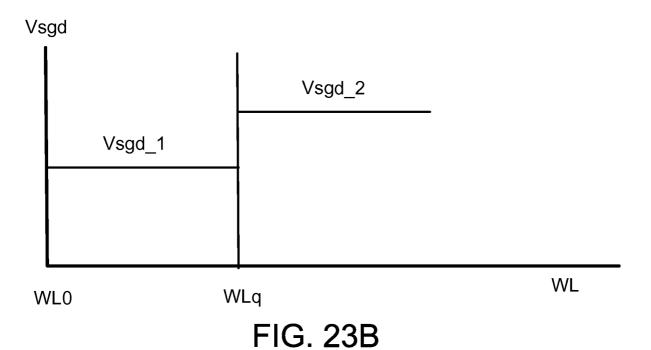

[0047] FIG. 23B shows voltage applied to a gate of a drain side select transistor versus word line for one embodiment.

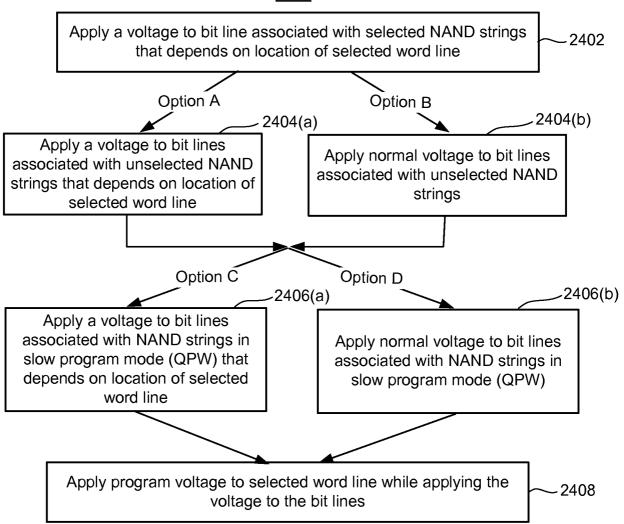

[0048] FIG. 24 depicts a flowchart of one embodiment of a process of programming non-volatile storage in which a voltage applied to bit lines depends on the location of the selected word line.

[0049] FIG. 25 depicts a flowchart of one embodiment of a process of programming non-volatile storage in which the voltage applied to a gate of a select transistor depends on the location of the selected word line.

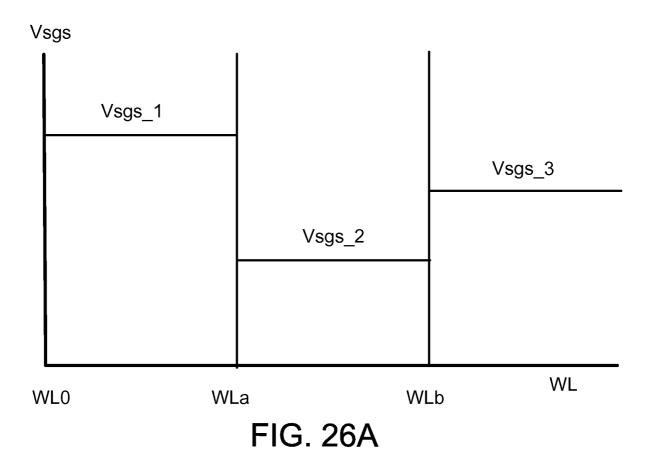

[0050] FIG. 26A shows relative values for Vsgs versus word lines in accordance with one embodiment.

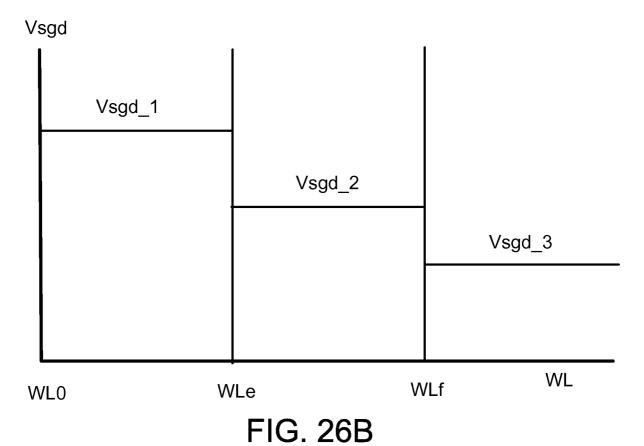

[0051] FIG. 26B shows relative values for Vsgd versus word lines in accordance with one embodiment.

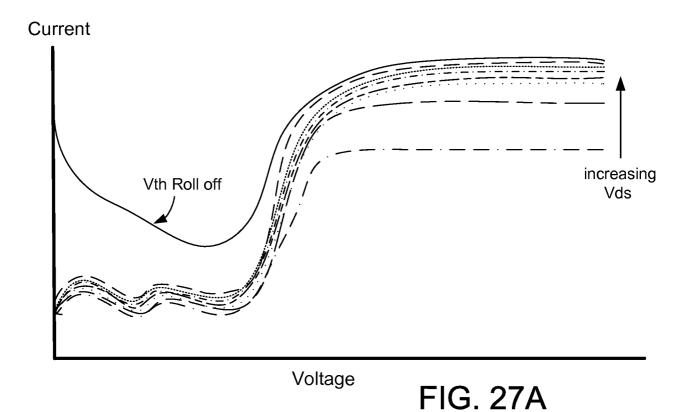

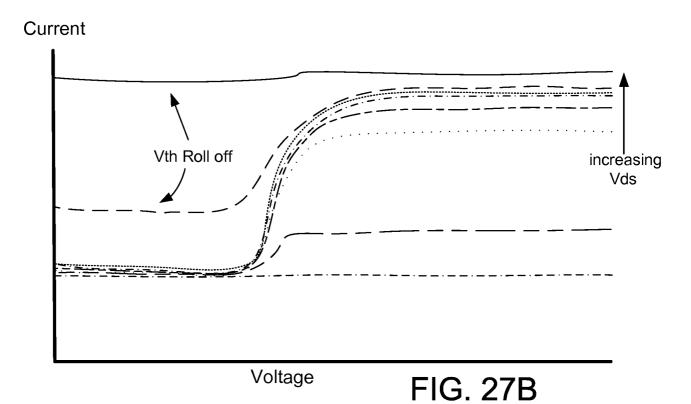

[0052] FIG. 27A and FIG. 27B shows possible effects of DIBL on the Vth of SGS transistors.

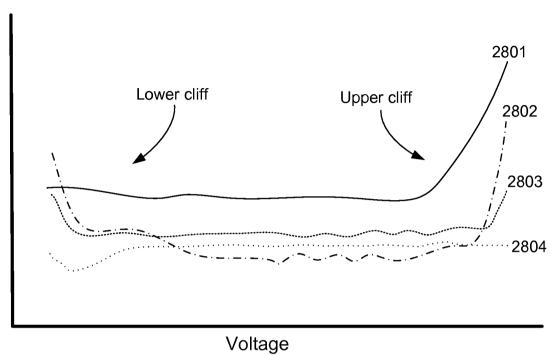

[0053] FIG. 28 shows a possible Vsgd window.

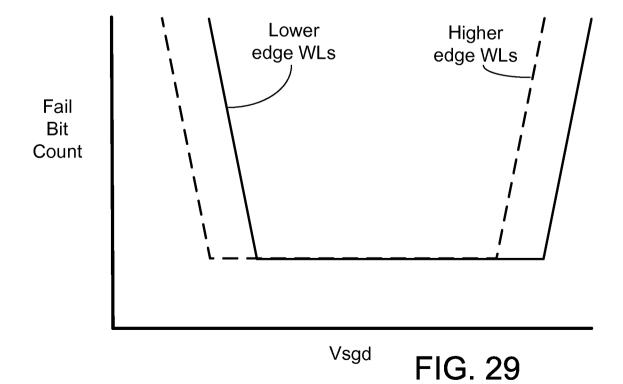

[0054] FIG. 29 shows possible word line dependence of the lower-cliff and upper-cliff of Vsgd window.

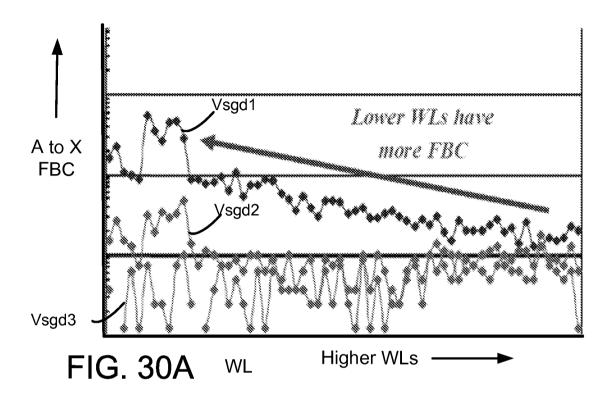

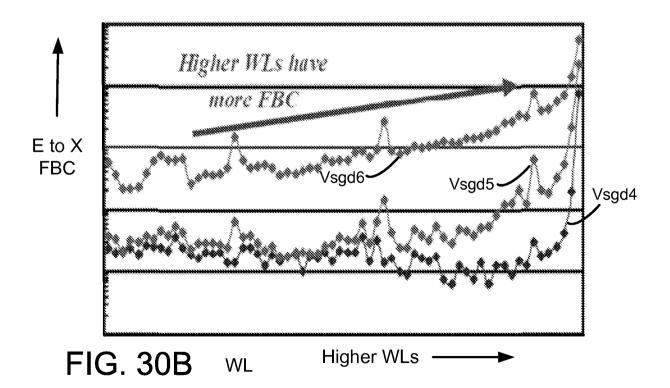

[0055] FIG. 30A and FIG. 30B show possible failure bit count versus word line.

## **DETAILED DESCRIPTION**

[0056] The present disclosure provides methods and devices for operating non-volatile storage. In some embodiments, one or more programming conditions depend on the location of the word line that is selected for programming. Applying selected word line dependent program conditions may reduce or eliminate program disturb.

[0057] A word line may be considered to be an "edge word line" or a "middle word line." An "edge word line" is defined herein as those within "n" word lines of the lowest or highest word line that is used to store user or system data. At least the lowest and highest word lines used to store user or system data are considered to be edge word lines. There may be one or more edge word lines at each end of a NAND string. The word lines that are considered to be edge word lines are not necessarily fixed for a given

-8-

memory array. Rather, the particular context may determine whether a word line is considered to be an edge word line. A "middle word line" is defined herein as any word line that is used to store user or system data other than edge word lines.

[0058] In one embodiment, the width (or duration) of a programming pulse depends on the word line that is selected for programming. In one embodiment, the duration of a programming pulse depends on a physical characteristic of the selected word line, such as its width. In one embodiment, the duration of a programming pulse depends on the location of the selected word line on a NAND string. As one example, a shorter pulse width may be used for the programming signal when programming edge word lines.

[0059] In one embodiment, the voltage applied to a common source line depends on the location of the word line that is selected for programming. This may prevent or reduce punch-through conduction, which may depend on the location of the selected word line. In one embodiment, the voltage applied to the common source line is higher for lower selected word lines than the voltage used for higher selected word lines.

[0060] In one embodiment, the voltage applied to bit lines of unselected NAND strings depends on the location of the word line that is selected for programming. This may prevent or reduce punch-through conduction, which may depend on the location of the selected word line. In one embodiment, the voltage applied to bit lines associated with unselected NAND strings is higher for lower selected word lines than the voltage used for higher selected word lines. In one embodiment, a higher voltage is used when programming edge word lines that are near the drain end of the NAND string.

-9-

[0061] In one embodiment, the voltage applied to the gate of a select transistor of a NAND string depends on the location of the word line that is selected for programming. This could be either a source side or drain side select transistor. This may prevent or reduce program disturb that could result due to DIBL. In one embodiment, a negative bias is applied to the gate of a source side select transistor when programming at least some of the word lines. In one embodiment, progressively lower voltages are used for the gate of the drain side select transistor when programming progressively higher word lines.

[0062] In one embodiment, the voltage applied to the gate of a source side select transistor depends on the location of the word line that is selected for programming. This may prevent or reduce GIDL, which may depend on the location of the selected word line. In one embodiment, the voltage applied to the gate of a drain side select transistor depends on the location of the word line that is selected for programming. This may prevent or reduce GIDL, which may depend on the location of the selected word line. In one embodiment, a higher voltage is applied to the gate of a select transistor when the selected word line is an edge word line near that select transistor.

[0063] In one embodiment, the voltage applied to one or more bit lines depends on the location of the word line that is selected for programming. This may further help to prevent or reduce program disturb associated with GIDL. In one embodiment, the voltage applied to one or more bit lines associated with selected NAND strings depends on the location of the word line that is selected for programming. In one embodiment, the voltage applied to one or more bit lines associated with unselected NAND strings depends on the location of the word line that is selected for programming. In one embodiment, the voltage applied to one or more bit lines associated with NAND strings in a slow programming mode depends on the location of the word line that is selected for programming.

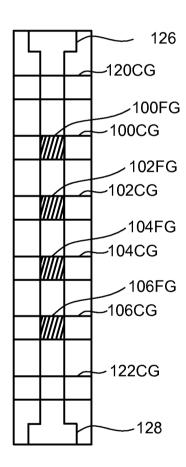

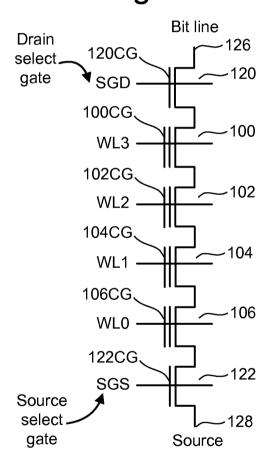

[0064] One example of a memory system suitable for implementing embodiments uses a NAND flash memory structure, which includes arranging multiple transistors in series between two select gates. transistors in series and the select gates are referred to as a NAND string. FIG. 1A is a top view showing one NAND string. FIG. 1B is an equivalent circuit thereof. The NAND string depicted in FIGs. 1A and 1B includes four transistors, 100, 102, 104 and 106, in series and sandwiched between a first select gate 120 and a second select gate 122. Select gate 120 gates the NAND string connection to bit line 126. Select gate 122 gates the NAND string connection to source line 128. Select gate 120 is controlled by applying the appropriate voltages to control gate 120CG. Select gate 122 is controlled by applying the appropriate voltages to control gate 122CG. Each of the transistors 100, 102, 104 and 106 has a control gate and a floating gate. Transistor 100 has control gate 100CG and floating gate Transistor 102 includes control gate 102CG and floating gate 100FG. 102FG. Transistor 104 includes control gate 104CG and floating gate 104FG. Transistor 106 includes a control gate 106CG and floating gate 106FG. Control gate 100CG is connected to (or is) word line WL3, control gate 102CG is connected to word line WL2, control gate 104CG is connected to word line WL1, and control gate 106CG is connected to word line WLO. In one embodiment, transistors 100, 102, 104 and 106 are each storage elements, also referred to as memory cells. In other embodiments, the storage elements may include multiple transistors or may be different than that depicted in FIGs. 1A and 1B. Select gate 120 is connected to select line SGD. Select gate 122 is connected to select line SGS. In one embodiment, select gates 120 and 122 are each implemented with a "select transistor." Thus, select gate 120 may be referred to as a "drain side select transistor," (or SGD transistor) and select gate 122 may be referred to as a "source side select transistor" (or SGS transistor).

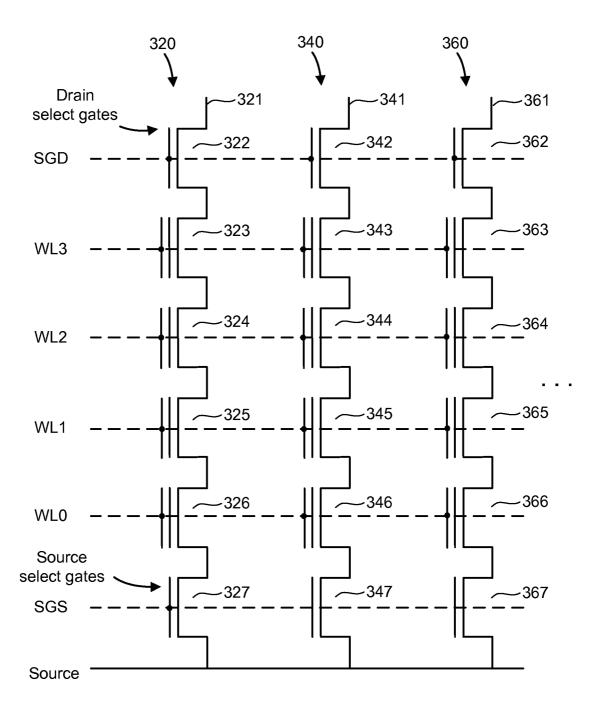

[0065] FIG. 2 is a circuit diagram depicting three NAND strings. A typical architecture for a flash memory system using a NAND structure will include several NAND strings. For example, three NAND strings 320, 340 and 360 are shown in a memory array having many more NAND strings. Each of the NAND strings includes two select gates and four storage elements. While four storage elements are illustrated for simplicity, modern NAND strings can have thirty-two, sixty-four, or more storage elements, for instance.

[0066] For example, NAND string 320 includes select gates 322 and 327, and storage elements 323-326, NAND string 340 includes select gates 342 and 347, and storage elements 343-346, NAND string 360 includes select gates 362 and 367, and storage elements 363-366. Each NAND string is connected to the source line by its select gates (e.g., select gates 327, 347 or 367). A selection line SGS is used to control the source side select gates. In one embodiment, the various NAND strings 320, 340 and 360 are connected to respective bit lines 321, 341 and 361, by select transistors. In one embodiment, the select transistors are in the select gates 322, 342, 362, etc. In one embodiment, the select transistors form the select gates 322, 342, 362. These select transistors are controlled by a drain select line SGD. In other embodiments, the select lines do not necessarily need to be in common among the NAND strings; that is, different select lines can be provided for different NAND strings. Word line WL3 is connected to the control gates for storage elements 323, 343 and 363. Word line WL2 is connected to the control gates for storage elements 324, 344 and 364. Word line WL1 is connected to the control gates for storage elements 325, 345 and 365. Word line WL0 is connected to the control gates for storage elements 326, 346 and 366. As can be seen, each bit line and the respective NAND string comprise the columns of the array or set of storage elements. The word lines (WL3, WL2, WL1 and WL0) comprise the rows of the array or set. Each word line connects the control gates of each storage element in

the row. Or, the control gates may be provided by the word lines themselves. For example, word line WL2 provides the control gates for storage elements 324, 344 and 364. In practice, there can be thousands of storage elements on a word line.

[0067] Each storage element can store data. For example, when storing one bit of digital data, the range of possible threshold voltages (V<sub>TH</sub>) of the storage element is divided into two ranges which are assigned logical data "1" and "0." In one example of a NAND type flash memory, the  $V_{TH}$  is negative after the storage element is erased, and defined as logic "1." The V<sub>TH</sub> after a program operation is positive and defined as logic "0." When the V<sub>TH</sub> is negative and a read is attempted, the storage element will turn on to indicate logic "1" is being stored. When the V<sub>TH</sub> is positive and a read operation is attempted, the storage element will not turn on, which indicates that logic "0" is stored. A storage element can also store multiple levels of information, for example, multiple bits of digital data. In this case, the range of V<sub>TH</sub> value is divided into the number of levels of data. For example, if four levels of information are stored, there will be four  $V_{TH}$ ranges assigned to the data values "11", "10", "01", and "00." In one example of a NAND type memory, the V<sub>TH</sub> after an erase operation is negative and defined as "11". Positive V<sub>TH</sub> values are used for the states of "10", "01", and "00." The specific relationship between the data programmed into the storage element and the threshold voltage ranges of the element depends upon the data encoding scheme adopted for the storage elements. For example, U.S. Patents 6,222,762 and 7,237,074, both of which are incorporated herein by reference in their entirety, describe various data encoding schemes for multi-state flash storage elements.

[0068] Relevant examples of NAND type flash memories and their operation are provided in U.S. Patent Nos. 5,386,422; 5,570,315; 5,774,397;

6,046,935; 6,456,528; and 6,522,580, each of which is incorporated herein by reference.

[0069] When programming a flash storage element, a program voltage is applied to the control gate of the storage element, and the bit line associated with the storage element is grounded. Electrons from the channel are injected into the floating gate. When electrons accumulate in the floating gate, the floating gate becomes negatively charged and the V<sub>TH</sub> of the storage element is raised. To apply the program voltage to the control gate of the storage element being programmed, that program voltage is applied on the appropriate word line. As discussed above, one storage element in each of the NAND strings share the same word line. For example, when programming storage element 324 of FIG. 2, the program voltage will also be applied to the control gates of storage elements 344 and 364.

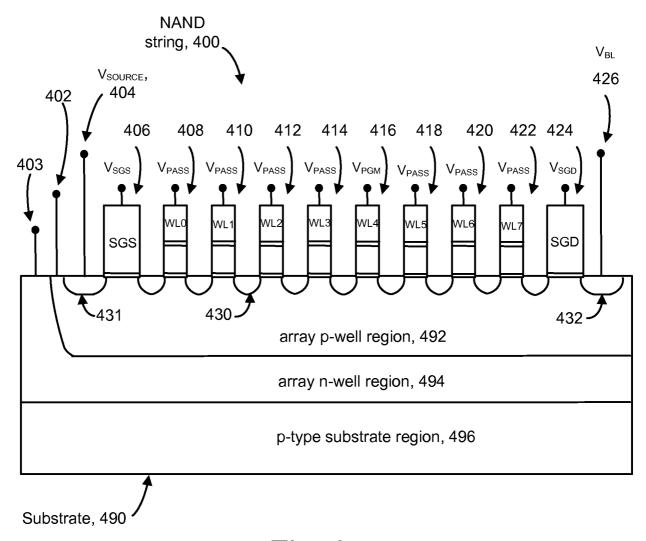

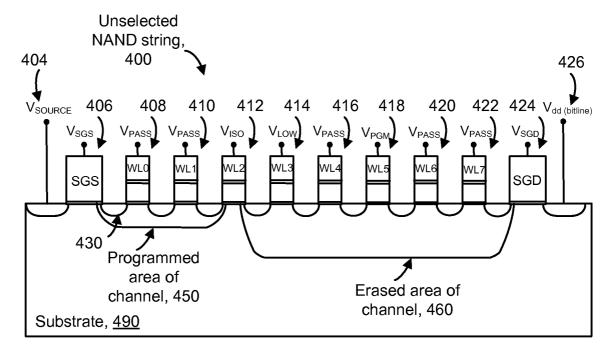

[0070] FIG. 3 depicts a cross-sectional view of a NAND string formed on a substrate. The view is simplified and not to scale. The NAND string 400 includes a source-side select gate (or SGS transistor) 406, a drain-side select gate (or SGD transistor) 424, and eight storage elements 408, 410, 412, 414, 416, 418, 420 and 422, formed on a substrate 490. A number of source/drain regions, one example of which is source drain/region 430, are provided on either side of each storage element. In one embodiment, the substrate 490 employs a triple-well technology which includes an array p-well region 492 within an array n-well region 494, which in turn is within a p-type substrate region 496. The NAND string and its non-volatile storage elements can be formed, at least in part, on the array p-well region 492.

[0071] A voltage  $V_{SOURCE}$  is provided to a source line contact 404. The source line contact has an electrical connection to the diffusion region 431 of SGS transistor 406. A bit line voltage  $V_{BL}$  is supplied to bit line contact 426, which is in electrical contact with the diffusion region 432 of SGD transistor 424. Note that diffusion region 431 may be referred to herein as a

source. Note that diffusion region 432 may be referred to herein as a drain; however, it will be understood that under some conditions (such as when the voltage of the channel of the NAND string is boosted) the diffusion region 432 may be at a lower voltage than the terminal on the other side of the channel of the SGD transistor 424. Voltages, such as body bias voltages, can also be applied to the array p-well region 492 via a terminal 402 and/or to the array n-well region 494 via a terminal 403.

[0072] During a program operation, a control gate voltage  $V_{PGM}$  is provided on a selected word line, in this example, WL3, which is associated with storage element 414. Further, recall that the control gate of a storage element may be provided as a portion of the word line. For example, WL0, WL1, WL2, WL3, WL4, WL5, WL6 and WL7 can extend via the control gates of storage elements 408, 410, 412, 414, 416, 418, 420 and 422, respectively. A pass voltage,  $V_{PASS}$  is applied to the remaining word lines associated with NAND string 400, in one possible boosting scheme.  $V_{SGS}$  and  $V_{SGD}$  are applied to the select gates 406 and 424, respectively.

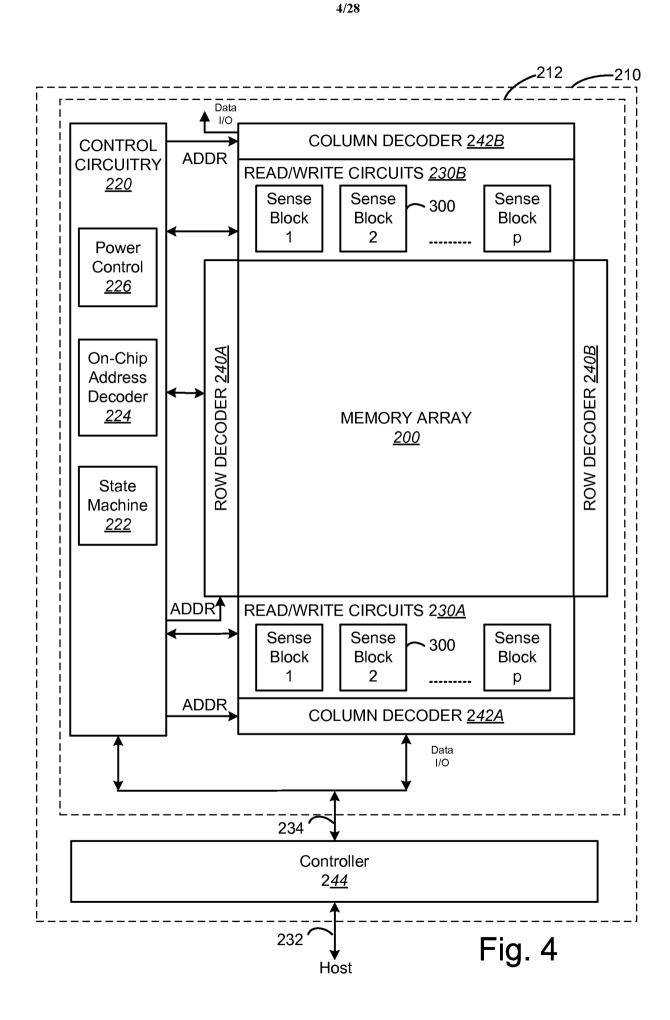

[0073] FIG. 4 illustrates a non-volatile storage device 210 that may include one or more memory die or chips 212. Memory die 212 includes an array (two-dimensional or three dimensional) of memory cells 200, control circuitry 220, and read/write circuits 230A and 230B. In one embodiment, access to the memory array 200 by the various peripheral circuits is implemented in a symmetric fashion, on opposite sides of the array, so that the densities of access lines and circuitry on each side are reduced by half. The read/write circuits 230A and 230B include multiple sense blocks 300 which allow a page of memory cells to be read or programmed in parallel. The memory array 200 is addressable by word lines via row decoders 240A and 240B and by bit lines via column decoders 242A and 242B. In a typical embodiment, a controller 244 is included in the same memory device 210 (e.g., a removable storage card or package) as the one or more memory die

-15-

212. Commands and data are transferred between the host and controller 244 via lines 232 and between the controller and the one or more memory die 212 via lines 234. One implementation can include multiple chips 212.

[0074] Control circuitry 220 cooperates with the read/write circuits 230A and 230B to perform memory operations on the memory array 200. The control circuitry 220 includes a state machine 222, an on-chip address decoder 224 and a power control module 226. The state machine 222 provides chip-level control of memory operations. The on-chip address decoder 224 provides an address interface to convert between the address that is used by the host or a memory controller to the hardware address used by the decoders 240A, 240B, 242A, and 242B. The power control module 226 controls the power and voltages supplied to the word lines and bit lines during memory operations. In one embodiment, power control module 226 includes one or more charge pumps that can create voltages larger than the supply voltage.

[0075] In one embodiment, one or any combination of control circuitry 220, power control circuit 226, decoder circuit 224, state machine circuit 222, decoder circuit 242A, decoder circuit 242B, decoder circuit 240A, decoder circuit 240B, read/write circuits 230A, read/write circuits 230B, and/or controller 244 can be referred to as one or more managing circuits.

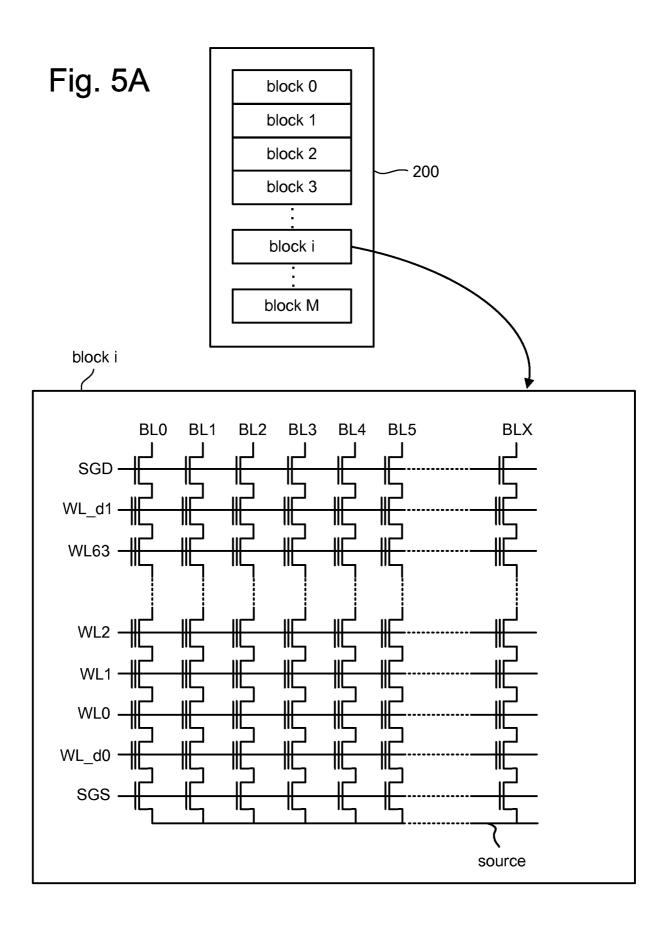

[0076] FIG. 5A depicts an example structure of memory cell array 200. In one embodiment, the array of memory cells is divided into M blocks of memory cells. As is common for flash EEPROM systems, the block is the unit of erase. That is, each block contains the minimum number of memory cells that are erased together. Each block is typically divided into a number of pages. A page is a unit of programming. One or more pages of data are typically stored in one row of memory cells. A page can store one or more sectors. A sector includes user data and overhead data. Overhead data typically includes an Error Correction Code (ECC) that has been calculated

from the user data of the sector. A portion of the controller (described below) calculates the ECC when data is being programmed into the array, and also checks it when data is being read from the array. In one embodiment, the controller 244 is able to correct a certain number of misreads, based on the ECC.

[0077] Alternatively, the ECCs and/or other overhead data are stored in different pages, or even different blocks, than the user data to which they pertain. A sector of user data is typically 512 bytes, corresponding to the size of a sector in magnetic disk drives. A large number of pages form a block, anywhere from 8 pages, for example, up to 32, 64, 128 or more pages. Different sized blocks and arrangements can also be used.

[0078] In another embodiment, the bit lines are divided into odd bit lines and even bit lines. In an odd/even bit line architecture, memory cells along a common word line and connected to the odd bit lines are programmed at one time, while memory cells along a common word line and connected to even bit lines are programmed at another time.

[0079] FIG. 5A shows more details of block i of memory array 200. Block i includes X+1 bit lines and X+1 NAND strings. Block i also includes 64 data word lines (WL0-WL63), 2 dummy word lines (WL\_d0 and WL\_d1), a drain side select line (SGD) and a source side select line (SGS). One terminal of each NAND string is connected to a corresponding bit line via a drain select gate (connected to select line SGD), and another terminal is connected to the source line via a source select gate (connected to select line SGS). Because there are sixty four data word lines and two dummy word lines, each NAND string includes sixty four data memory cells and two dummy memory cells. In other embodiments, the NAND strings can have more or fewer than 64 data memory cells and two dummy memory cells. Data memory cells can store user or system data. Dummy memory

cells are typically not used to store user or system data. Some embodiments do not include dummy memory cells.

[0080] FIG. 5B is a block diagram of an individual sense block 300 partitioned into a core portion, referred to as a sense module 580, and a common portion 590. In one embodiment, there will be a separate sense module 580 for each bit line and one common portion 590 for a set of multiple sense modules 580. In one example, a sense block will include one common portion 590 and eight sense modules 580. Each of the sense modules in a group will communicate with the associated common portion via a data bus 572. For further details, refer to U.S. Patent Application Publication 2006/0140007, which is incorporated herein by reference in its entirety.

[0081] Sense module 580 comprises sense circuitry 570 that determines whether a conduction current in a connected bit line is above or below a predetermined threshold level. In some embodiments, sense module 580 includes a circuit commonly referred to as a sense amplifier. Sense module 580 also includes a bit line latch 582 that is used to set a voltage condition on the connected bit line. For example, a predetermined state latched in bit line latch 582 will result in the connected bit line being pulled to a state designating program inhibit (e.g.,  $V_{\rm DD}$ ).

[0082] Common portion 590 comprises a processor 592, a set of data latches 594 and an I/O Interface 596 coupled between the set of data latches 594 and data bus 520. Processor 592 performs computations. For example, one of its functions is to determine the data stored in the sensed memory cell and store the determined data in the set of data latches. The set of data latches 594 is used to store data bits determined by processor 592 during a read operation. Data latches 594 may also be used to store data bits imported from the data bus 520 during a program operation. The imported data bits represent write data meant to be programmed into the memory. I/O

interface 596 provides an interface between data latches 594 and the data bus 520.

[0083] During read or sensing, the operation of the system is under the control of state machine 222 that controls the supply of different control gate voltages to the addressed cell. As it steps through the various predefined control gate voltages corresponding to the various memory states supported by the memory, the sense module 580 may trip at one of these voltages and an output will be provided from sense module 580 to processor 592 via bus 572. At that point, processor 592 determines the resultant memory state by consideration of the tripping event(s) of the sense module and the information about the applied control gate voltage from the state machine via input lines 593. It then computes a binary encoding for the memory state and stores the resultant data bits into data latches 594. In another embodiment of the core portion, bit line latch 582 serves double duty, both as a latch for latching the output of the sense module 580 and also as a bit line latch as described above.

[0084] It is anticipated that some implementations will include multiple processors 592. In one embodiment, each processor 592 will include an output line (not depicted in Fig. 5) such that each of the output lines is wired-OR'd together. In some embodiments, the output lines are inverted prior to being connected to the wired-OR line. This configuration enables a quick determination during the program verification process of when the programming process has completed because the state machine receiving the wired-OR line can determine when all bits being programmed have reached the desired level. For example, when each bit has reached its desired level, a logic zero for that bit will be sent to the wired-OR line (or a data one is inverted). When all bits output a data 0 (or a data one inverted), then the state machine knows to terminate the programming process. In embodiments where each processor communicates with eight sense

modules, the state machine may (in some embodiments) need to read the wired-OR line eight times, or logic is added to processor 592 to accumulate the results of the associated bit lines such that the state machine need only read the wired-OR line one time.

[0085] During program or verify, the data to be programmed is stored in the set of data latches 594 from the data bus 520. The program operation, under the control of the state machine, comprises a series of programming voltage pulses (with increasing magnitudes) applied to the control gates of the addressed memory cells. Each programming pulse is followed by a verify process to determine if the memory cell has been programmed to the desired state. Processor 592 monitors the verified memory state relative to the desired memory state. When the two are in agreement, processor 592 sets the bit line latch 582 so as to cause the bit line to be pulled to a state designating program inhibit. This inhibits the cell coupled to the bit line from further programming even if it is subjected to programming pulses on its control gate. In other embodiments the processor initially loads the bit line latch 582 and the sense circuitry sets it to an inhibit value during the verify process. In one embodiment, the magnitude of the inhibit value depends on the location of the selected word line.

[0086] Data latch stack 594 contains a stack of data latches corresponding to the sense module. In one embodiment, there are 3-5 (or another number) data latches per sense module 580. In one embodiment, the latches are each one bit. In some implementations (but not required), the data latches are implemented as a shift register so that the parallel data stored therein is converted to serial data for data bus 520, and vice versa. In one embodiment, all the data latches corresponding to the read/write block of M memory cells can be linked together to form a block shift register so that a block of data can be input or output by serial transfer. In particular, the bank of read/write modules is adapted so that each of its set of data

latches will shift data in to or out of the data bus in sequence as if they are part of a shift register for the entire read/write block.

[0087] Additional information about the read operations and sense amplifiers can be found in (1) United States Patent 7,196,931, "Non-Volatile Memory And Method With Reduced Source Line Bias Errors,"; (2) United States Patent 7,023,736, "Non-Volatile Memory And Method with Improved Sensing,"; (3) United States Patent 7,046,568, "Memory Sensing Circuit and Method for Low Voltage Operation; (4) U.S. Patent 7,196,928, "Compensating for Coupling During Read Operations of Non-Volatile Memory," and (5) United States Patent 7,327,619, "Reference Sense Amplifier For Non-Volatile Memory". All five of the immediately abovelisted patent documents are incorporated herein by reference in their entirety.

[0088] At the end of a successful programming process (with verification), the threshold voltages of the memory cells should be within one or more distributions of threshold voltages for programmed memory cells or within a distribution of threshold voltages for erased memory cells, as appropriate. FIG. 6A illustrates example Vt distributions corresponding to data states for the memory cell array when each memory cell stores three bits of data. Other embodiment, however, may use more or fewer than three bits of data per memory cell. FIG. 6A shows eight Vt distributions corresponding to an Erase state and programmed states A-G. In one embodiment, the threshold voltages in the Erase state are negative and the threshold voltages in the programmed states A-G are positive.

[0089] However, the threshold voltages in one or more of programmed states A-G may be negative. Thus, in one embodiment, at least VrA is negative. Other voltages such as VvA, VrB, VvB, etc., may also be negative.

[0090] Between each of the data states are read reference voltages used for reading data from memory cells. For example, FIG. 6A shows read reference voltage VrA between the erase state and the A-state, and VrB between the A-state and B-state. By testing whether the threshold voltage of a given memory cell is above or below the respective read reference voltages, the system can determine what state the memory cell is in.

[0091] At or near the lower edge of each programmed state are verify reference voltages. For example, FIG. 6A shows VvA for the A-state and VvB for the B-state. When programming memory cells to a given state, the system will test whether those memory cells have a threshold voltage greater than or equal to the verify reference voltage.

[0092] FIG. 6B illustrates that Vt distributions can partially overlap since the error correction algorithm can handle a certain percentage of cells that are in error. Note that in some embodiments, at one point in time the threshold voltage distribution may resemble FIG. 6A and at another time the threshold voltage distributions may overlap, as in FIG. 6B. For example, just after programming, the threshold voltage distribution may resemble FIG. 6A. However, over time, the threshold voltages of memory cells may shift, such that there may be overlap.

[0093] Also note that contrary to the equal spacing/width of the depicted threshold voltage distributions, various distributions may have different widths/spacings in order to accommodate varying amounts of susceptibility to data retention loss.

[0094] In some embodiments, a "verify low" and a "verify high" reference voltage is used. FIG. 7A depicts an example set of threshold voltage distributions for a four-state memory device in which each storage element stores two bits of data. A first threshold voltage distribution 700 is provided for erased (Erased-state) storage elements. Three threshold voltage distributions 702, 704 and 706 represent programmed states A, B

and C, respectively. In one embodiment, the threshold voltages in the Erased-state are negative, and the threshold voltages in the A-, B- and C-states are positive.

[0095] Read reference voltages, VrA, VrB and VrC, are also provided for reading data from storage elements. By testing whether the threshold voltage of a given storage element is above or below VrA, VrB and VrC, the system can determine the state, e.g., the storage element is in.

[0096] Further, verify reference voltages, VvA, VvB, and VvC are provided. When programming storage elements to the A-state, B-state or C-state, the system will test whether those storage elements have a threshold voltage greater than or equal to VvA, VvB or VvC, respectively. In one embodiment, "verify low" reference voltages, VvaL, VvbL, and VvcL are provided. Similar "verify low" reference voltages could also be used in embodiments with a different number of states.

[0097] In full sequence programming, storage elements can be programmed from the Erased-state directly to any of the programmed states A, B or C. For example, a population of storage elements to be programmed may first be erased so that all storage elements in the population are in the Erased-state. A series of program pulses such as depicted in FIG. 7B is used to program storage elements directly into the A-, B- and C-states. While some storage elements are being programmed from the Erased -state to the A-state, other storage elements are being programmed from the Erased-state to the B-state and/or from the Erased-state to the C-state. Note that using a full sequence programming is not required.

[0098] One example of a slow programming mode uses low (offset) and high (target) verify levels for one or more data states. For example, VvaL and VvA are offset and target verify levels, respectively, for the A-state, and VvbL and VvB are offset and target verify levels, respectively, for the B-

state. During programming, when the threshold voltage of a storage element which is being programmed to the A-state as a target state (e.g., an A-state storage element) exceeds VvaL, its programming speed is slowed, such as by raising the bit line voltage to a level, e.g., 0.6-0.8 V, which is between a nominal program or non-inhibit level, e.g., 0 V and a full inhibit level, e.g., 2-3 V. The middle value may be referred to as a quick pass write (QPW) value. This provides greater accuracy by avoiding large step increases in threshold voltage. In some embodiments, values for one or more of the nominal program value, QPW value, and/or the inhibit value depend on the location of the word line that is selected for programming.

[0099] When the threshold voltage reaches VvA, the storage element is locked out from further programming. Similarly, when the threshold voltage of a B-state storage element exceeds VvbL, its programming speed is slowed, and when the threshold voltage reaches VvB, the storage element is locked out from further programming. In one approach, a slow programming mode is not used for the highest state since some overshoot is typically acceptable. Instead, the slow programming mode can be used for the programmed states, above the erased state, and below the highest state.

[00100] Moreover, in the example programming techniques discussed, the threshold voltage of a storage element is raised as it is programmed to a target data state. However, programming techniques can be used in which the threshold voltage of a storage element is lowered as it is programmed to a target data state. Programming techniques which measure storage element current can be used as well. The concepts herein can be adapted to different programming techniques.

[00101] FIG. 7B depicts a series of program and verify pulses which are applied to a selected word line during a programming operation. A programming operation may include multiple programming iterations, where each iteration applies one or more program pulses (voltages) followed

by one or more verify voltages, to a selected word line. In one possible approach, the program voltages are stepped up in successive iterations. Moreover, the program voltages may include a first portion which has a pass voltage (Vpass) level, e.g., 6-8 V, followed by a second portion at a program level, e.g., 12-25 V. For example, first, second, third and fourth program pulses 752, 754, 756 and 758 have program voltages of Vpgm1, Vpgm2, Vpgm3 and Vpgm4, respectively, and so forth. A set of one or more verify voltages may be provided after each program pulse. In some embodiments, there may be two or more verify pulses between the program pulses. For example, one pulse might be used to verify the A-state and the B-state, a second may be used to verify the C-state and a D-state, etc. In some cases, one or more initial program pulses are not followed by verify pulses because it is not expected that any storage elements have reached the lowest program state (e.g., A-state). Subsequently, program iterations may use verify pulses for the A-state, followed by program iterations which use verify pulses for the A- and B-states, followed by program iterations which use verify pulses for the B- and C-states, for instance.

[00102] FIG. 8 is a flowchart describing one embodiment of a programming process, which includes one or more verification steps. In one embodiment, the process is used to program memory cells on a selected word line. In one embodiment, the process is used to program every memory cell on the selected word line. In one embodiment, the process is used to program every other memory cell (e.g., odd/even programming) on the selected word line.

[00103] In step 810, the program voltage (Vpgm) is set to an initial value. In one embodiment, the magnitude of the program voltage depends on which word line is selected for programming. In one embodiment, the initial magnitude of Vpgm is lower when programming an edge word line. Also, in step 810, a program counter (PC) is initialized to zero.

[00104] In step 820, programming conditions are applied. One or more of the programming conditions may depend on the location of which word line is selected for programming. FIG. 9, to be discussed below, shows some examples of programming conditions that may be applied during step 820.

[00105] Applying the programming conditions includes applying a programming signal (e.g., voltage pulse) to a selected word line. In one embodiment, the width of the voltage pulse depends on the location of the selected word line on the NAND string. In one embodiment, the voltage pulse has a shorter width when an edge word line is selected for programming than when one of the middle word lines is selected.

[00106] Step 820 may also include applying an appropriate voltage to bit lines. In one embodiment, a first voltage (e.g., a low voltage) is applied to bit lines associated with NAND strings having a memory cell presently undergoing normal (or fast) programming, a second voltage (e.g., a medium voltage) is applied to bit lines associated with NAND strings having a memory cell presently undergoing slow programming, and a third voltage (e.g., a high voltage) is applied to bit lines associated with NAND strings having a memory cell presently inhibited from or locked out from further programming. In one embodiment, the magnitude of the first voltage depends on the location of the selected word line along the NAND string. In one embodiment, the magnitude of the second voltage depends on the location of the selected word line along the NAND string. In one embodiment, the magnitude of the third voltage depends on the location of the selected word line along the NAND string.

[00107] Step 820 may also include applying an appropriate voltage to a common source line. In one embodiment, the magnitude of the voltage to a common source line depends on the location of the selected word line along the NAND string. Note that the common source line may be in electrical

contact with diffusion regions 431 of SGS transistors 406. Thus, in one embodiment, the magnitude of the voltage applied to the (source) diffusion region 431 of an SGS transistor 406 depends on the location of the selected word line along the NAND string.

[00108] Step 820 may also include applying an appropriate voltage to a gate of a select gate of a NAND string. Stated another way, step 820 may include applying an appropriate voltage to select line of a NAND string. The select gate may be for either a SGS transistor 406 or a SGD transistor 424. Thus, the select line may be either a source side select line (e.g., SGS) or a drain side select line (e.g., SGD). In one embodiment, the magnitude of the voltage to the gate of a select transistor of a NAND string depends on the location of the selected word line along the NAND string. In other words, the magnitude of the voltage to a select line (SGS and/or SGG) of a NAND string depends on the location of the selected word line along the NAND string.

[00109] Applying the program conditions in step 820 may also include applying a pass voltage to unselected word lines. The magnitude of the pass voltage for each unselected word line may depend on which boosting scheme is being used. A variety of boosting schemes including, but not limited to, self-boosting (SB), local self-boosting (LSB), and erase area self-boosting (EASB) may be used. As is known to those of ordinary skill in the art, the magnitude of the pass voltage may be different for different unselected word lines. Also, the magnitude of the pass voltage for a given unselected word line may depend on the relative location of that unselected word line to the word line that is selected for programming. The pass voltage may help to reduce program disturb by boosting the voltage of the channel below the memory cell. Applying programming conditions that depend on the location of the selected word line may prevent or reduce

leakage of the boosted channel potential. Therefore, program disturb may be prevented or reduced.

[00110]In step 822, a verification process is performed. In one embodiment, the verification is a concurrent coarse/fine verify. Referring to FIG. 7A, as one example, some memory cells that are being programmed to the A-state are verified using the VvaL level, and others that are being programmed to the A-state are verified using the Vva level. During the initial programming steps in which the memory cell's threshold is well below the final level (Vva), course programming may be applied. However, after the memory cell's threshold voltage reaches VvaL, fine programming may be used. Thus, some memory cells are verified for coarse programming, whereas other memory cells are verified for fine programming. Note that when a particular memory cell has been verified as being programmed to its intended state, it may be locked out from further programming. Note that using coarse/fine programming is not required. In one embodiment, the intermediate verify levels (e.g., VvaL, VvbL, etc.) are not used.

[00111] In step 824, it is determined whether all or almost all of the memory cells have verified that their threshold voltages are at the final target voltage for that memory cell. If so, the programming process is completed successfully (status = pass) in step 826. If all or almost all of the memory cells are not verified to have reached their final target levels, then it is determined whether the program counter (PC) is less than a maximum value such as 20. If the program counter (PC) is not less than max (step 828), then the program process has failed (step 830). If the program counter (PC) is less than a maximum value (e.g., 20), then the program counter (PC) is incremented by one and the program voltage is stepped up to the next pulse in step 832. Subsequent to step 832, the process loops back to step 820 and the next program pulse is applied to the memory cells.

**[00112]** Figures 9(A) - 9(H) are timing diagrams illustrating voltages during program operations, according to one embodiment. The timing diagram depicts one embodiment of programming conditions that are applied during step 820 of process 800. In various embodiments, one or more of the programming conditions depends on the location of the selected word line. In some embodiments, the magnitude of a voltage depends on the location of the selected word line. In one embodiment, the duration of the program voltage depends on the location of the selected word line.

[00113] The voltages shown are applied to various select lines, word lines, bit lines, and the common source line of the memory array, for NAND strings under fast programming, slow programming, and program inhibition. The program operation can be grouped into a Bit Lines Precharge Phase, a Program Phase and a Discharge Phase.

[00114] Bit Lines Precharge Phase: During phase (1), the SGS transistors 406 are turned off by SGS being at Vsgs (Fig. 9(A)) while the SGD transistors 424 are turned on by SGD going high to Vsg (Fig. 9(B)), thereby allowing a bit line to access a NAND string. In one embodiment, the magnitude of Vsgs depends on the location of the selected word line. In one embodiment, the magnitude of Vsgs is higher when lower word lines are being programmed to prevent or reduce GIDL. In one embodiment, the magnitude of Vsgs is negative when middle word lines or higher word lines are being programmed to prevent or reduce program disturb associated with DIBL.

[00115] During phase (2), the bit line voltage of a program-inhibited NAND string is allowed to rise to a predetermined voltage given by VBL\_inhibit (Fig. 9(E)). When the bit line voltage of the program-inhibited NAND string rises to VBL\_inhibit, the program-inhibited NAND string will float when the gate voltage on the SGD transistor 424 drops to V SGD. In

one embodiment, the voltage VBL\_inhibit depends on which word line is selected for programming.

[00116] At the same time, the bit line voltage of a programming NAND string is either pulled down to VBL\_Select or maintained at VBL\_Select if already there (Fig. 9(G)). In one embodiment, the voltage VBL\_Select depends on which word line is selected for programming.

[00117] Also during phase (2), the bit line voltage of NAND strings that are undergoing slow programming is set to an intermediate voltage given by VBL\_QPW (Fig. 9(F)). The voltage VBL\_QPW is between VBL\_Select and VBL\_inhibit. The voltage VBL\_QPW allows the selected memory cell to program, but at a slower rate than if VBL\_Select were used. In one embodiment, the voltage VBL\_QPW depends on which word line is selected for programming.

[00118] Also during phase (2), the voltage on the common source line is set to voltage given by V\_Cell\_Source (Fig. 9(H)). In one embodiment, the voltage V\_Cell\_Source depends on which word line is selected for programming.

[00119] During phase (3), the drain select line (SGD) connecting to the SGD transistors 424 of NAND strings has its voltage lowered to V\_SGD. In one embodiment, this will float only those program-inhibited NAND strings where their bit line voltage is comparable to V\_SGD, since their SGD transistors 424 are turned off (Figs. 9(B) & 9(E)). As for the NAND strings containing a memory cell to be programmed, their SGD transistors 424 will not be turned off relative to the bit line voltage (e.g., near 0V) at their drain. In one embodiment, the voltage V\_SGD depends on which word line is selected for programming. In one embodiment, the voltage V\_SGD depends on the location of the selected word line in order to prevent or eliminate effects of DIBL. For example, the SGD transistors 424 of unselected NAND strings may be kept off despite their Vth being lowered

by DIBL. In one embodiment, the magnitude of V\_SGD is lower for higher selected word lines, which may keep the SGD transistors 424 turned off despite possible DIBL.

[00120] In one embodiment, the magnitude of V\_SGD depends on the location of the selected word line in order to prevent or eliminate effects of GIDL. For example, the magnitude of V\_SGD may be higher when the selected word line is near the SGD transistors 424 (relative to when the selected word line is a middle word line, for example). This increase in V\_SGD may prevent leakage of charge from the boosted channel due to GIDL.

programmed have their control gate voltage set to VPASS (Fig. 9(C)). Also, the memory cell being programmed may have its control gate voltage set to VPASS (Fig. 9(C)). Since a program-inhibited NAND string is floating, the VPASS applied to the control gates of the memory cells boosts up the voltages of their channels. For the sake of discussion, the entire NAND string may be considered to have a channel. Thus, it may be stated that VPASS boosts the channel voltage of the NAND string. VPASS may be set to some intermediate voltage (e.g., ~10V) relative to Vpgm (e.g., ~15–24V). Depending on the boosting scheme being used, the value of VPASS is not required to be the same for each unselected word line.

[00122] Program Phase: During phase (5), a programming voltage Vpgm is applied to the control gate of a memory cell selected for programming (Fig. 9(D)). This may be achieved by applying Vpgm to the selected word line. The memory cells under program inhibition (e.g., with boosted channels) will not be programmed. The memory cells under programming will be programmed. Note that Vpgm may also contribute to channel boosting. Applying program conditions that depend on which word line is

selected may prevent or substantially reduce the boosted channel voltage from reducing during the program phase.

[00123] In one embodiment, the duration of the program pulse (e.g., duration of phase 5) depends on the location of the selected word line. This may help to reduce or eliminate program disturb.

[00124] In the Discharge Phase: During phase (6), the various control lines and bit lines are allowed to discharge.

[00125] Any combination of the selected word line dependent signals discussed in connection with FIG. 9 may be used together when programming non-volatile storage.

SELECTED WORD LINE DEPENDENT PROGRAMMING VOLTAGE PULSE WIDTH

[00126] In one embodiment, the width (or duration) of a programming pulse depends on the location of the word line that is selected for programming. As one example, a shorter width may be used when programming edge word lines. Using a shorter width for the programming pulse for edge word lines may reduce program disturb on those word lines. If the programming pulse used for other word lines is too short, then a problem such as poor programming for the far end of the word line may occur.

[00127] Each word line does not necessarily have the same physical characteristics. For example, some word lines may be wider than others. As a specific example, edge word lines may be wider than other word lines. A possible reason for this is due to limitations of the lithography process used to form the word lines. There may also be differences in doping profiles used in the substrate near edge word lines compared to other word lines. Differences in physical characteristics (not necessarily those physical

characteristics just mentioned) may result in different optimum widths for programming voltages.

[00128] In one embodiment, the pulse width for each selected word line is such that Er-A failures are minimized, or at least close to the minimum. FIG. 10 is a graph that shows Er-to-A failures versus program pulse width for selected word lines in various positions along a NAND string. Referring to FIG. 10, for any given word line there may be an optimum program pulse width to reduce Er-A failures. Curve 1001(1) is for edge word lines, whereas curve 1001(2) is for middle word lines. As the programming pulse width is made shorter, the Er-A failures may be reduced up to a point. However, at some point, the Er-A failures may become greater as the program pulse width is further reduced. Also note that the optimum pulse width for edge word lines may be shorter than for middle word lines.

[00129] A possible reason for higher Er-A fails when the program pulse width is too short is that a higher magnitude of program voltage may be needed to complete the programming of the word line. Needing to use a higher magnitude program voltage can increase program disturb, which counters the beneficial effect of a shorter program pulse width.

[00130] In one embodiment, a program pulse width is determined for each word line position based on how many program loops it takes to complete programming each word line. This may help to reduce failures due to problems such as program disturb.

[00131] In one embodiment, the program pulse width depends on the selected word line. In one embodiment, the program pulse width depends on the width of the selected word line. In one embodiment, a shorter program pulse width is used for edge word lines. In one embodiment, a program pulse width is determined for each word line position based on the number of program loops it takes to complete programming each word line. Prior to discussing various program processes in which the program pulse

width depends on the selected word line, some word line dependent characteristics will be discussed.

[00132] FIGs. 11A, 11B, and 11C show example graphs of Vth distribution widths versus program pulse widths. FIG. 11A is for the Astate, FIG. 11B is for the B-state, and FIG. 11C is for the C-state. Each graph shows two example curves for edge word lines and two examples for "middle word lines." In FIG. 11A, 1101(a) is for the lowest edge word line, 1101(b) and 1101(c) are middle word lines, 1101(d) is the highest edge word line. In FIG. 11B, 1102(a) is for the lowest edge word line, 1102(b) and 1102(c) are for middle word lines, 1102(d) is for the highest edge word line. In FIG. 11C, line 1103(a) is for the lowest edge word line, 1103(b) and 1103(c) are for middle word lines, 1103(d) is for the highest edge word line. The middle word lines may be about in the midpoint of the NAND string.

[00133] These graphs in FIG. 11B and 11C show that the Vth distribution may become wider with shorter programming pulse width for all word lines, at least for the B- and C-states. The Vth distribution width for the A-state might not depend on program pulse width as heavily as it does for other data states, although for some devices and programming processes this may be a possibility.

[00134] Referring to FIGs. 11A-11C, the edge word lines may have a tighter Vth distribution for a given pulse width than the middle word lines. Also, the "cliff" may occur at a lower program pulse width for the edge word lines than for the middle word lines (see FIGs. 11B and 11C). The cliff refers to the point at which the Vth distribution widening begins to increase rapidly with shorter program pulse width. Since the cliff may be lower for the edge word lines (at least for some data states), the edge word lines may be more tolerant to shorter program pulse widths.

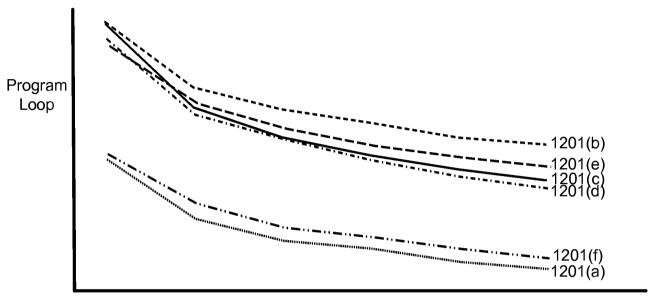

[00135] FIG. 12 shows a graph of program loop count versus program pulse width. The graph shows two curves for edge word lines (1201(a),

1201(f)) and four curves for middle word lines (1201(b), 1201(c), 1201(d), 1201(e)). These edge word lines may be WL0 and WL63, as one example. However, there may be more or fewer word lines. The middle word lines may be WL1, WL32, WL33, and WL62. Thus, in this example, there is one edge word line at each end of the NAND string. As noted earlier, in some contexts there may be more than one edge word line at each and of the NAND string. The number of program loops may increase with decreasing program pulse width. Note that the edge word lines may program faster than the middle word lines across all program pulse widths. In one embodiment, to achieve the same program loop (program performance) for edge WLs and middle WLs, a shorter program pulse width may be used on edge WLs.

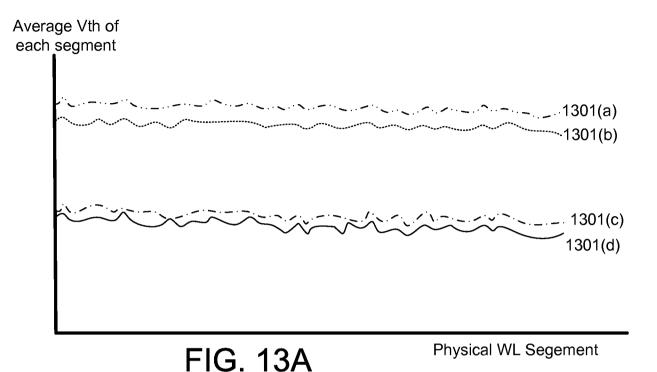

[00136] FIG. 13A and 13B are graphs that show word lines RC dependence. FIG. 13A is for a relatively long program pulse width. FIG. 13B is for a relatively moderate program pulse width. Curves 1301(a) and 1301(b) are for edge word lines. Curves 1301(c) and 1301(d) are for middle word lines. Each curve 1301(a) – 1301(d) shows the average Vth of memory cells at different points along the selected word line. In this example, each word line may be programmed pulse by pulse without verify. The memory cells may be grouped into segments, based on physical location. For example, memory cells may be grouped into 72 segments (segments 0 - 71) for purposes of analysis. The Vth for each memory cell in a given segment may be averaged to produce an average Vth for that segment. The Vth difference between segment 0 and segment 71 may be a measure of RC delay along the word line.

[00137] Note that when the program pulse width is shorter (FIG. 13B), the middle word lines 1301(c), 1301(d) show a significant drop in Vth for the higher segments. This may be due to significant RC delay when programming the middle word lines. However, the edge word lines 1301(a),

1301(b) do not show as much of a drop in Vth for higher segments. This may be due to there being less RC delay for edge word lines. Word line width may affect RC delay. As one example, edge word lines may be wider, thus having less RC delay. For some devices, even word lines and odd word lines have different widths. Therefore, even and odd word lines may have different RC delay.

[00138] Referring now to FIG. 13A, neither the edge 1301(a), 1301(b) nor the middle word lines 1301(c), 1301(d) show as much of a drop in Vth for the higher segments. As noted, the program pulse width is longer in this case. Therefore, the RC delay along the word line may not be as important since the pulse width is longer.

[00139] Characteristics of the lithographic process used to form the word lines may determine the width of word lines. For example, the intent may be to form all word lines with the same width, edge word lines may end up wider than middle word lines. A possible reason for this is that the edge word lines are near select lines, which may be intended to be significantly wider than word lines. For some lithographic processes when parallel lines are formed, the process may work best if the lines are of the same width. However, since an edge word line is located between relatively narrow middle word lines and a relatively wide selected line, the edge word line may end up larger than middle word lines.

[00140] In view of the difference in RC delay for different word lines, programming in accordance with one embodiment uses shorter program pulse widths for word lines having less RC delay. In one embodiment, edge word lines have less RC delay than middle word lines. For some devices, the word lines with less RC delay may be otherwise. One factor in having less RC delay may be the width of word lines. However, there may be other factors.

[00141] FIG. 14 is a flowchart of one embodiment of a process 1400 of programming non-volatile storage. In step 1402, a programming voltage is applied to a selected word line that has a duration that depends on the width of the selected word line. The duration of the program voltage may be defined as a program voltage pulse width. Process 1400 may be used to implement a portion of step 820 from FIG. 8. Specifically, applying a program voltage to a selected word line is one of the program conditions of step 820. Referring to FIG. 9(D), step 1402 is one embodiment of applying Vpgm during the program phase. Thus, the time duration of phase (5) depends on the selected word line, in one embodiment. Various other signals depicted in FIG. 9 may also be applied during process 1400. Zero or more of these signals may have its value depend on the selected word line.

[00142] Step 820 may be performed multiple times to program the selected word line. In one embodiment, the same program pulse width is used for each program loop when programming the selected word line. However, the program pulse width could be changed with the number of program loops.

[00143] In one embodiment, a shorter pulse width is used in step 1402 for wider word lines (and wider for more narrow word lines). In one embodiment, edge word lines are wider than middle word lines. Thus, a shorter program pulse width may be used for edge word lines than for middle word lines.

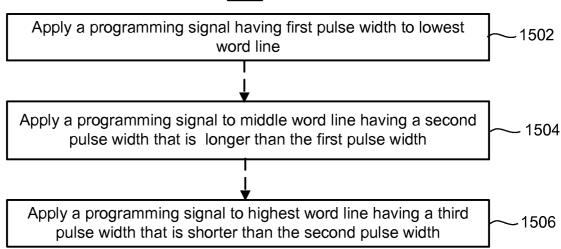

[00144] FIG. 15 is a flowchart of one embodiment of a process 1500 of programming non-volatile storage. Process 1500 describes programming a lowest word line, a middle word line, and a highest word line. By a lowest word line, it is meant the lowest word line for which user or system data is stored. There may also be one or more dummy word lines in between the lowest word line and the source side select line. Likewise, by a highest word line, it is meant the highest word line for which user or system data is

stored. There may also be one or more dummy word lines in between the highest word line and the drain side select line. The lowest and highest word lines may be referred to as "edge" word lines. For memory devices in which the edge word lines are wider than the middle word lines, process 1500 is one implementation of step 1402 from process 1400.

[00145] Process 1500 describes programming signals that are applied to three different word lines for the same point in the programming process when different word lines are selected for programing. As noted, the programming process has a number of program loops (or steps). By the same point it is meant the loop (or program step). This could be the initial program loop or some other program loop.

[00146] In step 1502, a programming signal having a first pulse width is applied to a lowest word line. Referring to FIG. 2, this may be applied to WLO. Referring to FIG. 3, this may be applied to WLO. Referring to FIG. 5A, this may be applied to WLO. Step 1502 is one embodiment of step 820 from process 800. In one embodiment, step 1502 is for the first program pulse that is applied to the lowest word line (e.g., first iteration of process 800). Referring to FIG. 9(D), step 1502 is one embodiment of applying Vpgm during the program phase.

[00147] There is a dashed line between step 1502 and 1504 to indicate that other programming signals may be applied to the lowest word line to complete its programing before proceeding on to program the middle word line. In step 1504, a programming signal having a second pulse width is applied to a middle word line. In one embodiment, the programming signal is applied to any word line between the lowest and highest word lines. However, there may be more than one edge word line at each end of the string of memory cells (e.g., NAND string). For example, there might be two or three edge word lines at each end. Thus, the middle word line is not necessarily any word line between the lowest and highest word lines. The

second pulse width is longer than the first pulse width. In one embodiment, step 1504 is for the first program pulse that is applied to the middle word line (e.g., first iteration of process 800). Referring to FIG. 9(D), step 1504 is one embodiment of applying Vpgm during the program phase.

[00148] In step 1506, a programming signal having a third pulse width is applied to a "highest" word line. Again, the dashed line between steps 1504 and 1506 indicates that other programming signals may be applied to the middle word line to complete its programming prior to going on to program the highest word line. Also, note that numerous middle word lines may be programmed. The highest word line may be the word line that is closest to the SGD transistor 424, and that is used to store user or system data. Referring to FIG. 2, this may be applied to WL3. Referring to FIG. 3, this may be applied to WL7. Referring to FIG. 5A, this may be applied to WL63. The third pulse width is shorter than the second pulse width. The third pulse width may be the same, shorter than, or longer than the first pulse width. In one embodiment, step 1306 is for the first program pulse that is applied to the highest word line (e.g., first iteration of process 800). Referring to FIG. 9(D), step 1506 is one embodiment of applying Vpgm during the program phase. Various other signals depicted in FIG. 9 may also be applied during process 1500. Zero or more of these signals may have its value depend on the selected word line.

[00149] Thus, in one embodiment, process 1500 includes applying a programming signal for a given program loop having a shorter pulse width when either the lowest word line or the highest word line is selected for programming than the pulse width used to program at least one other word line of the plurality of word lines.

[00150] For some devices, the lowest word line and the highest word line may be wider than middle word lines. In this case, process 1500 may be used to implement step 1402. In other words, process 1500 may result in

applying a program voltage whose duration depends on the width of the selected word line. One possible reason for the edge word lines being wider than others is due to the lithographic process used to form the word lines. For some devices, the select lines (e.g., SGD and SGS in FIG. 5A) are wider than the word lines. For some lithographic processes, this may result in edge word lines printing somewhat wider than other word lines. Note that for other lithographic processes other word lines could be wider.

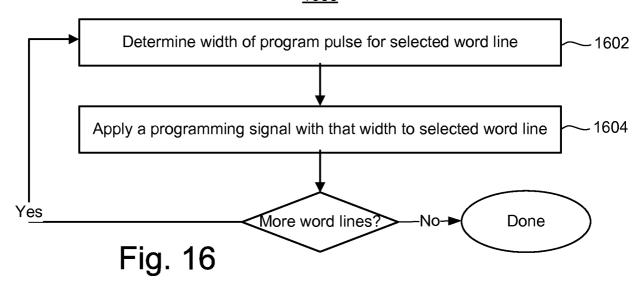

[00151] FIG. 16 is a flowchart of one embodiment of a process 1600 of programming non-volatile storage that involves determining a width of a program pulse. Referring to FIG. 9, process 1600 may be used to determine the time duration of the program phase.

[00152] In step 1602, a width of a program pulse for the selected word line is determined. In one embodiment, this determination is made by accessing a table. FIG. 17 shows details of one embodiment of a process 1700 for determining a width for a particular word line. Process 1700 may be used to create the table accessed in step 1602.

[00153] In step 1604, a programming signal with the width (or time duration) determined in step 1602 is applied to the selected word line. Step 1604 may be repeated until all memory cells on the selected word line are programmed. Various other signals depicted in FIG. 9 may also be applied during process 1600. Zero or more of these signals may have its value depend on the selected word line.

[00154] If there are more word lines to program, then process 1600 returns to step 1402. In one embodiment, word lines in a block are programming sequentially from lowest to highest. However, word lines may be programmed in any order.

[00155] FIG. 17 is a flowchart of a process 1700 of determining suitable pulse widths for programming signals for word lines, depending on their position. The process 1700 may be performed on a sample block, with the

results being used to program other blocks. The sample block may be in the same storage device as the other blocks, but this is not required. Some storage devices have more than one memory die. In this case, the sample block may be on the same memory die or another memory die.