(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-32929

(P2009-32929A)

(43) 公開日 平成21年2月12日(2009.2.12)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 21/3205 (2006.01)

H01L 23/12

S O 1 P

テーマコード(参考)

H01L 23/52 (2006.01)

H01L 21/88

T

5 F O 3 3

審査請求 未請求 請求項の数 6 O L (全 11 頁)

(21) 出願番号

特願2007-195820 (P2007-195820)

(22) 出願日

平成19年7月27日 (2007.7.27)

(71) 出願人 000001889

三洋電機株式会社

大阪府守口市京阪本通2丁目5番5号

(71) 出願人 506227884

三洋半導体株式会社

群馬県邑楽郡大泉町坂田一丁目1番1号

(74) 代理人 100131071

弁理士 ▲角▼谷 浩

(72) 発明者 北川 勝彦

群馬県邑楽郡大泉町坂田一丁目1番1号

(72) 発明者 篠木 裕之

群馬県邑楽郡大泉町坂田一丁目1番1号

三洋半導体株式会社内

三洋半導体株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置及びその製造方法

## (57) 【要約】

【課題】 信頼性の高い半導体装置及びその製造方法を提供する。

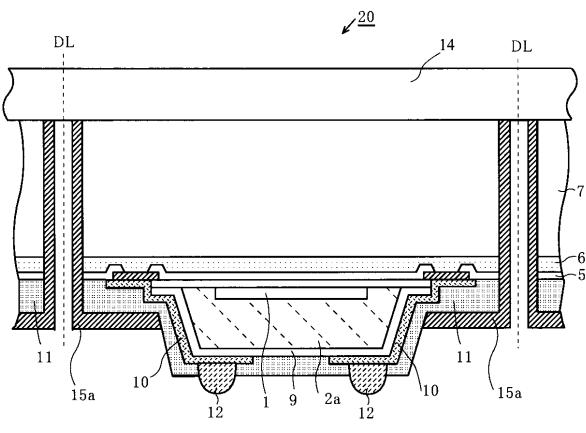

【解決手段】 半導体チップ2a内の回路素子に接続され、当該半導体チップ2a上の側面部近傍に形成されたパッド電極4と、前記パッド電極4上に形成された支持体7と、前記半導体チップ2aの側面部及び裏面部に形成された絶縁膜9と、前記パッド電極4の裏面に接続され、前記絶縁膜9に接するようにして前記半導体チップ2aの側面部から裏面部に延在する配線層10と、前記支持体7の側面部に形成された第2の保護膜15aとを有することを特徴とする。

【選択図】 図9

15a: 第2の保護膜 20: 半導体装置

**【特許請求の範囲】****【請求項 1】**

半導体チップ内の回路素子に接続され、当該半導体チップ上に形成されたパッドと、

前記パッド上に形成された支持体と、

前記半導体チップの側面部及び裏面部に形成された絶縁膜と、

前記パッドの裏面に接続され、前記絶縁膜に接するようにして前記半導体チップの側面部から裏面部に延在する配線と、

前記支持体の側面部に形成された保護膜とを有することを特徴とする半導体装置。

**【請求項 2】**

前記保護膜が前記支持体の側面部から前記配線を含めた半導体チップの裏面を被覆するよう<sup>10</sup>

に形成されていることを特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

前記配線を被覆する保護膜に形成された開口部を介して前記配線に電気的に接続される導

電端子とを有することを特徴とする請求項 2 に記載の半導体装置。

**【請求項 4】**

パッドが形成された半導体基板を用意し、

前記パッドを含む前記半導体基板上に支持体を形成する工程と、

前記半導体基板をその裏面側から一部除去して前記パッドを露出するための開口部を形成する工程と、

前記パッドの裏面に接続し、かつ前記半導体基板の裏面に延在する配線を形成する工程<sup>20</sup>

と、

ダイシングテープに前記支持体を保持させて、前記半導体基板と支持体をダイシングする工程と、

前記ダイシングされた支持体と支持体との間の領域に保護膜を形成する工程と、

前記保護膜をダイシングして、前記支持体の側面部に保護膜が形成された半導体チップを形成する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 5】**

第 1 の絶縁膜を介してパッドが形成された半導体基板を用意し、

前記パッドを含む前記半導体基板上に支持体を形成する工程と、

前記半導体基板をその裏面側から一部除去して前記第 1 の絶縁膜を露出させる工程と、<sup>30</sup>

前記半導体基板の裏面全体に第 2 の絶縁膜を形成する工程と、

前記第 1 及び第 2 の絶縁膜を一部除去して前記パッドを露出させる工程と、

前記パッドの裏面に接続し、かつ前記半導体基板の裏面に延在する配線を形成する工程

と、

前記配線を含む半導体基板の裏面全体に第 1 の保護膜を形成する工程と、

ダイシングテープに前記支持体を保持させて、前記半導体基板と支持体をダイシングする工程と、

前記ダイシングされた支持体と支持体との間の領域に第 2 の保護膜を形成する工程と、

前記第 2 の保護膜をダイシングして、前記支持体の側面部に第 2 の保護膜が形成された半導体チップを形成する工程とを有することを特徴とする半導体装置の製造方法。<sup>40</sup>

**【請求項 6】**

前記第 1 の保護膜に形成された開口部を介して前記配線に電気的に接続される導電端子を形成する工程を有することを特徴とする請求項 4 または請求項 5 に記載の半導体装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体装置及びその製造方法に関し、特に C S P ( C h i p S i z e P a c k a g e ) 型の半導体装置及びその製造方法に関するものである。

**【背景技術】**

10

20

30

40

50

**【0002】**

近年、新たなパッケージ技術としてCSPが注目されている。CSPとは、半導体チップの外形と略同一直径の外形を有する小型のパッケージをいう。そして、CSPの一型としてBGA(Ball Grid Array)型の半導体装置が知られている。BGA型の半導体装置は、ハンダ等の金属材料から成るポール状の導電端子がパッケージの一方の面上に複数配列されたものである。

**【0003】**

また、実装密度を高めるために、半導体チップの薄型化が要求されており、この要求を満たすためにも半導体基板を薄くする必要がある。しかしながら、半導体基板が薄くなると、製造工程において強度低下による反りや破損が生じるために搬送が不可能になってしまう。そのため、ガラス基板や保護テープ等の支持体を半導体基板の一方の面に貼り合わせ、支持体の貼り合わされていない面を研削して半導体基板を薄くすることが行われている。

10

**【0004】**

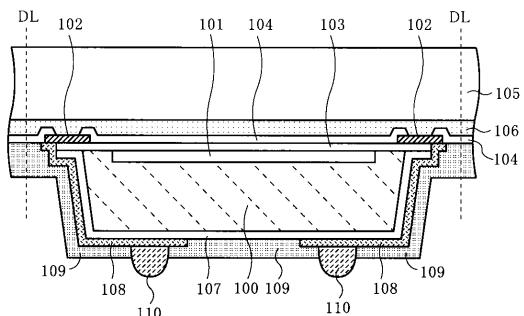

図10は、従来のBGA型であって、支持体を備える半導体装置の概略を示す断面図である。シリコン(Si)等から成る半導体基板100の表面には、CCD(Charge Coupled Device)型イメージセンサやCMOS型イメージセンサ等の素子から成る半導体集積回路101が形成され、更に、半導体集積回路101と電気的に接続されたパッド電極102が絶縁膜103を介して形成されている。パッド電極102は、シリコン窒化膜等から成るパッシベーション膜104で被覆されている。

20

**【0005】**

半導体基板100の表面上には、ガラス基板から成る支持体105がエポキシ樹脂等から成る接着層106を介して貼り合わされている。支持体105は、製造工程の中で薄型化される半導体基板100を強固に保持するため、及び支持体105自身の反りや破損を防止するために厚く、例えば薄型化後の半導体基板100の厚みが100μm程度とすると、支持体105の厚みは400μm程度である。

**【0006】**

半導体基板100の側面及び裏面上にはシリコン酸化膜やシリコン窒化膜等から成る絶縁膜107が形成されている。絶縁膜107上には、パッド電極102と電気的に接続された配線層108が、半導体基板100の側面及び裏面に沿って形成されている。また、絶縁膜107及び配線層108を被覆して、ソルダーレジスト等から成る保護膜109が形成されている。保護膜109の所定領域には開口部が形成され、この開口部を通して配線層108と電気的に接続されたポール状の導電端子110が形成されている。

30

**【0007】**

このような半導体装置は、個々の半導体装置の境界である所定のダイシングラインDLに沿って支持体105及び保護膜109等をダイシングブレードで個別に切り分ける工程(いわゆるダイシング工程)を経ることによって製造されていた。

**【0008】**

上述した技術は、例えば以下の特許文献に記載されている。

**【特許文献1】特開2006-93367号公報**

40

**【発明の開示】****【発明が解決しようとする課題】****【0009】**

上記半導体装置では、ガラス基板から成る支持体105がダイスカットされたままの剥き出しの状態であった。

**【0010】**

そのため、ダイスカットによりダメージの入ったガラス側面が露出することから、外部からの物理的な衝撃によりガラスが欠ける、割れるといった恐れがあった。

**【0011】**

また、照度センサー用途では、特定波長の光をカットするためガラス面にIRカットコ

50

ートを形成しているが、ガラス側面からの入斜光がある場合、干渉型のIRカットコートでは斜め光のカット特性が悪く、デバイス特性が悪化する恐れがあった。特に、チップサイズが小型化されることで、チップ端部と受光素子との距離が短くなることで、上記影響が懸念されきていている。

【0012】

そこで本発明は、上記課題を解決し、信頼性の高い半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明は上記課題に鑑みてなされたものであり、その主な特徴は以下のとおりである。

すなわち、本発明の半導体装置は、半導体チップ内の回路素子に接続され、当該半導体チップ上に形成されたパッドと、前記パッド上に形成された支持体と、前記半導体チップの側面部及び裏面部に形成された絶縁膜と、前記パッドの裏面に接続され、前記絶縁膜に接するようにして前記半導体チップの側面部から裏面部に延在する配線と、前記支持体の側面部に形成された保護膜とを有することを特徴とする。

10

【0014】

また、前記保護膜が前記支持体の側面部から前記配線を含めた半導体チップの裏面を被覆するように形成されていることを特徴とする。

【0015】

更に、前記配線を被覆する保護膜に形成された開口部を介して前記配線に電気的に接続される導電端子とを有することを特徴とするものである。

20

【0016】

また、本発明の半導体装置の製造方法は、パッドが形成された半導体基板を用意し、前記パッドを含む前記半導体基板上に支持体を形成する工程と、前記半導体基板をその裏面側から一部除去して前記パッドを露出するための開口部を形成する工程と、前記パッドの裏面に接続し、かつ前記半導体基板の裏面に延在する配線を形成する工程と、ダイシングテープに前記支持体を保持させて、前記半導体基板と支持体をダイシングする工程と、前記ダイシングされた支持体と支持体との間の領域に保護膜を形成する工程と、前記保護膜をダイシングして、前記支持体の側面部に保護膜が形成された半導体チップを形成する工程とを有することを特徴とする。

30

【0017】

更に、本発明の半導体装置の製造方法は、第1の絶縁膜を介してパッドが形成された半導体基板を用意し、前記パッドを含む前記半導体基板上に支持体を形成する工程と、前記半導体基板をその裏面側から一部除去して前記第1の絶縁膜を露出させる工程と、前記半導体基板の裏面全体に第2の絶縁膜を形成する工程と、前記第1及び第2の絶縁膜を一部除去して前記パッドを露出させる工程と、前記パッドの裏面に接続し、かつ前記半導体基板の裏面に延在する配線を形成する工程と、前記配線を含む半導体基板の裏面全体に第1の保護膜を形成する工程と、ダイシングテープに前記支持体を保持させて、前記半導体基板と支持体をダイシングする工程と、前記ダイシングされた支持体と支持体との間の領域に第2の保護膜を形成する工程と、前記第2の保護膜をダイシングして、前記支持体の側面部に第2の保護膜が形成された半導体チップを形成する工程とを有することを特徴とする。

40

【0018】

また、前記第1の保護膜に形成された開口部を介して前記配線に電気的に接続される導電端子を形成する工程を有することを特徴とするものである。

【発明の効果】

【0019】

本発明によれば、支持体の側面部を被覆するように保護膜を形成しているため、外部からの物理的な衝撃が直接、支持体に加わることを防止できる。また、支持体を介して入射してくる斜め光を保護膜により遮断することで、デバイス特性が向上する。

50

【発明を実施するための最良の形態】

【0020】

次に、本発明の一実施形態について図面を参照しながら説明する。図1乃至図9は、それぞれ製造工程順に示した断面図または平面図である。なお、以下に説明する製造工程は、ウェハ状の半導体基板を用いて行われるものであり、所定のダイシングラインDLを境界として多数の半導体装置がマトリクス状に多数形成されることになるが、便宜上その一つの半導体装置が形成される工程を説明する。

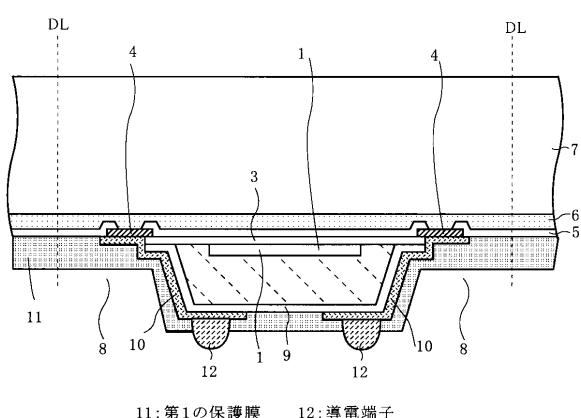

【0021】

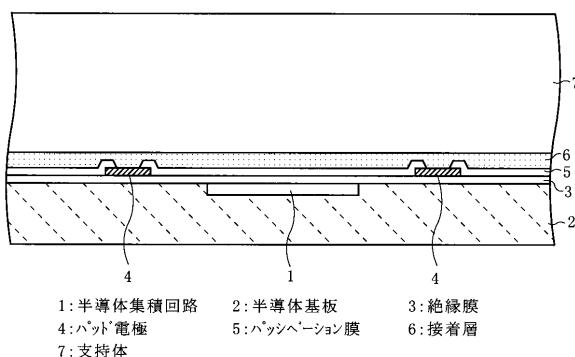

まず、図1に示すように、その表面に半導体集積回路1（例えば、CCDセンサー、CMOSセンサー、照度センサー等の受光素子や発光素子、トランジスタ等の半導体素子が集積されて構成されたドライバ回路やロジック回路、それらと接続された配線等）が形成されたシリコン（Si）等から成るウェハ状の半導体基板2を準備する。半導体基板2は、例えば $300\text{ }\mu\text{m} \sim 700\text{ }\mu\text{m}$ 程度の厚さになっている。そして、半導体基板2の表面上に絶縁膜3（例えば、熱酸化法やCVD法等によって形成されたシリコン酸化膜）を例えば $2\text{ }\mu\text{m}$ の膜厚に形成する。

10

【0022】

次に、スパッタリング法やメッキ法、その他の成膜方法によりアルミニウム（Al）やアルミニウム合金や銅（Cu）等の金属層を形成し、その後不図示のレジスト層をマスクとして当該金属層をエッチングし、絶縁膜3上にパッド電極4を例えば $1\text{ }\mu\text{m}$ の膜厚に形成する。パッド電極4は、半導体集積回路1やその周辺素子と不図示の配線を介して電気的に接続された外部接続用の電極である。そして、後述する導電端子12からパッド電極4を介して電源電圧や接地電圧あるいは種々の信号が半導体集積回路1や半導体基板2等に供給される。なお、パッド電極4の配置位置に限定はなく、半導体集積回路1上に配置することもできる。

20

【0023】

次に、半導体基板2の表面側にパッド電極4の一部上あるいは全部を被覆するパッシベーション膜5（例えば、CVD法により形成されたシリコン酸化膜、シリコン窒化膜等）を形成する。図1では、パッド電極4の一部上を被覆するようにしてパッシベーション膜5が形成されている。

30

【0024】

次に、パッド電極4を含む半導体基板2の表面上に、エポキシ樹脂やポリイミド（例えば感光性ポリイミド）、レジスト、アクリル等から成る接着層6を介してウェハ状の支持体7を貼り合わせる。本実施形態では、支持体7の半導体基板2側の面を表面、他方の面を表面とする。なお、半導体集積回路1が受光素子や発光素子を含む場合には、接着層6は半導体集積回路1から放射される光、あるいは半導体集積回路1に入射される光の通り道になるため、透明であって光を透過させる性状の良好な材料から成ることが好ましい。

40

【0025】

ここで、前記支持体7は、例えばガラスを用いている。なお、ガラス以外にも石英、セラミック、金属等の剛性の基板から成るものでもよい。そして、前記支持体7は、半導体基板2を支持すると共にその素子表面を保護する機能を有するものであり、その膜厚は例えば約 $400\text{ }\mu\text{m}$ 程度である。なお、半導体集積回路1が受光素子や発光素子を含む場合には、支持体7は透明もしくは半透明の材料から成り、光を透過させる性状を有するものである。更に、本発明の半導体装置が照度センサー用途では、図示した説明は省略するが、特定波長の光をカットするために支持体7としてのガラス面に干渉型のIRカットコートが形成されている。

40

【0026】

次に、半導体基板2の裏面に対して裏面研削装置（グラインダー）を用いてバックグランドを行い、半導体基板2を所定の厚さ（例えば $100\text{ }\mu\text{m}$ 程度）まで薄くする。なお、当該研削工程はエッチング処理でもよいし、グラインダーとエッチング処理の併用でもよい。なお、最終製品の用途や仕様、準備した半導体基板2の当初の厚みによっては、当

50

該研削工程を行う必要がない場合もある。

【0027】

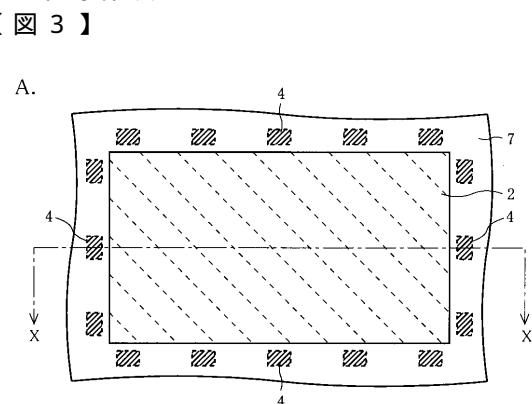

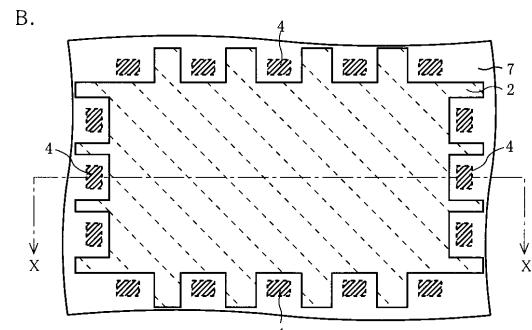

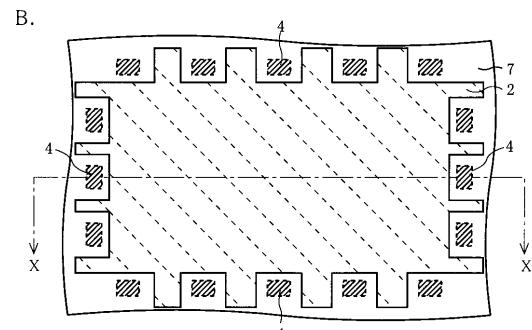

次に、図2に示すように、半導体基板2のうちパッド電極4に対応する所定の領域のみを、半導体基板2の裏面側から選択的にエッティングし、絶縁膜3を一部露出させる。以下、この露出部分を開口部8とする。これによりウェハ状の半導体基板2は、図3A,Bに示すような島状に分割される。

【0028】

当該半導体基板2の選択的なエッティングについて、図3A,Bを参照して説明する。図3A,Bは、半導体基板2側から見た概略平面図であり、図2は図3A,BのX-X線に沿った断面図に対応するものである。

10

【0029】

図3Aに示すように、半導体基板2を支持体7の幅よりも狭い、略長方形の形状にエッティングすることもできる。また、図3Bに示すように、パッド電極4が形成された領域のみをエッティングすることで、半導体基板2の外周が凹凸状になるように構成することもできる。後者の方が、半導体基板2と支持体7の重畳する面積が大きく、支持体7の外周近くまで半導体基板2が残る。そのため、半導体基板2に対する支持体7の支持強度を向上させる観点からは、後者の構成が好ましい。また、後者の構成によれば、半導体基板2と支持体7の熱膨張率の差異による支持体7の反りが防止できるため、半導体装置のクラックや剥離が防止できる。なお、図3A,Bで示した平面形状とは別の形状に半導体基板2をデザインすることも可能である。なお、以後は半導体基板2を図3Aで示したようにエッティングした場合の製造工程を説明する。

20

【0030】

また、本実施形態では半導体基板2の横幅が表面側に近付くほど広がるように、半導体基板2の側壁が斜めにエッティングされているが、半導体基板2の幅が一定であり、その側壁が支持体7の正面に対して垂直となるようにエッティングすることもできる。

【0031】

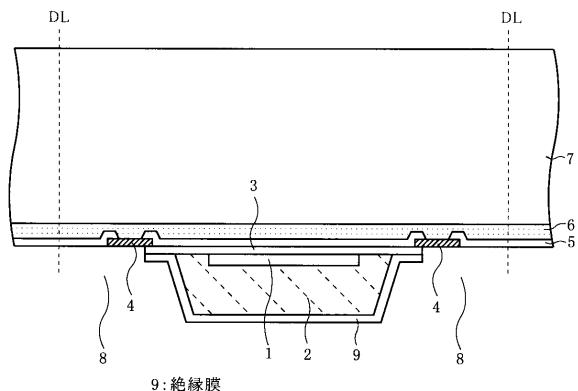

次に、開口部8内を含め、半導体基板2の側面及び裏面上にプラズマCVD法等によって形成されたシリコン酸化膜やシリコン窒化膜等の絶縁膜9を形成する。次に、不図示のレジスト層をマスクとして、絶縁膜3及び絶縁膜9を図4に示すように選択的にエッティングする。このエッティングにより、パッド電極4の一部上からダイシングラインDLに至る領域にかけて形成された絶縁膜3及び絶縁膜9が選択的に除去され、開口部8の底部においてパッド電極4の少なくとも一部が露出される。

30

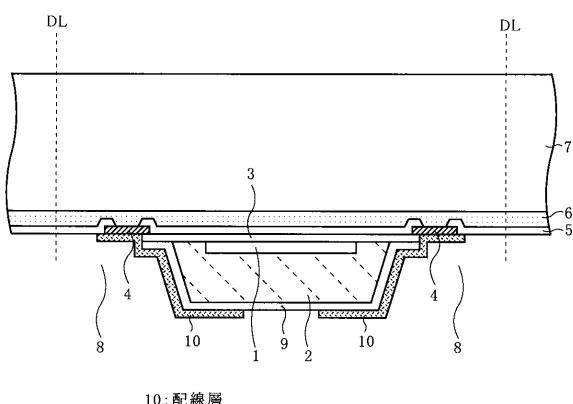

【0032】

次に、スパッタリング法やメッキ法、その他の成膜方法により、配線層10となるアルミニウム(A1)や銅(Cu)等の金属層を例えば1μmの膜厚で形成する。その後、不図示のレジスト層をマスクとして当該金属層を選択的にエッティングする。このエッティングによって当該金属層は、図5に示すように、パッド電極4と接続され、半導体基板2の側面及び裏面上に形成された配線層10となる。

【0033】

次に、配線層10を被覆する不図示の電極接続層(例えば、ニッケル層と金層の積層)を形成する。電極接続層を形成するのは、アルミニウム等から成る配線層10と、ハンダ等から成る導電端子12は接合しにくいという理由や、導電端子12の材料が配線層10側に流入してくることを防止するという理由による。

40

【0034】

そして、前記配線層10を被覆するように半導体基板2の裏面側に第1の保護膜11を形成する。なお、前記第1の保護膜11の形成後に、前記電極接続層を形成することも可能である。

【0035】

次に、第1の保護膜11の開口部から露出した電極接続層上に導電材料(例えばハンダ)をスクリーン印刷し、この導電材料を熱処理でリフローさせることで、図6に示すよう

50

にボール状の導電端子 12 を形成する。なお、導電端子 12 の形成方法は上記に限定されることはなく、電解メッキ法や、ディスペンサを用いてハンダ等を所定領域に塗布するいわゆるディスペンス法等で形成することもできる。このようにして、パッド電極 4 は配線層 10 を介して導電端子 12 と電気的に接続される。

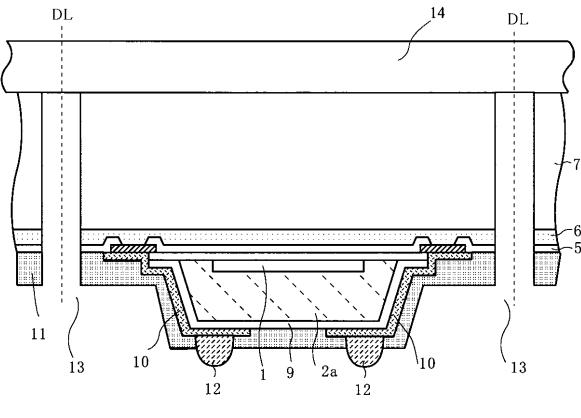

【0036】

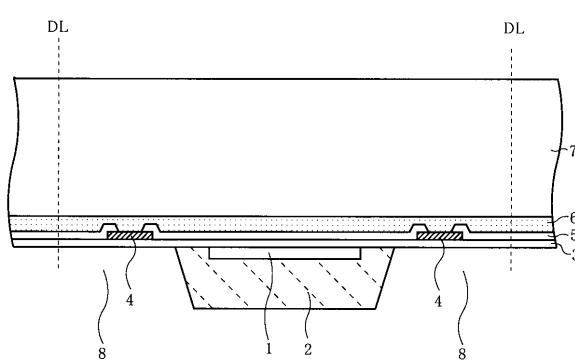

次に、前記支持体 7 の裏面側にダイシング用テープ（例えば、UV テープ 14）を貼り付けた状態で、ダイシングブレードやドライエッチングによって、個々の半導体装置の境界（ダイシングライン DL）に沿って、半導体基板 2 側から第 1 の保護膜 11、絶縁膜 5，接着層 6 及び支持体 7 を一部除去して、開口部 13 を形成する。これによって、半導体基板 2 は半導体チップに分断される。以下、半導体チップ 2a として説明を続ける。10

【0037】

なお、開口部 13 の断面形状は、図 7 に示すような垂直形状に限定されず、任意の形状とすることができる。

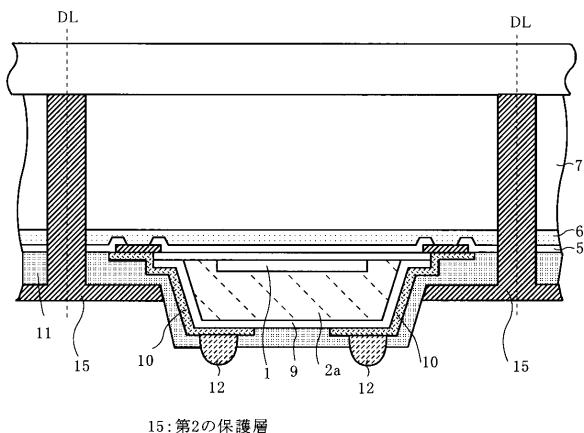

【0038】

次に、図 8 に示すように前記開口部 13 から半導体チップ 2a の側面にかけて第 2 の保護膜 15 を形成する。なお、前記半導体チップ 2a 全体を第 2 の保護膜 15 で被覆するものであってもよい。

【0039】

ここで、前記第 2 の保護膜 15 の形成は、例えば以下のように行う。まず、例えばディスペンス（塗布）法を用いて、前記開口部 13 内を含め、半導体チップ 2a の側面にかけて樹脂封止する。20

【0040】

また、前記第 2 の保護膜 15 の材料として、ポリイミド系樹脂、ソルダーレジスト膜等の有機系材料を用いてもよい。

【0041】

更に、可視光や赤外線等を吸収する吸収材料を用いてもよい。また、前記第 2 の保護膜 11 の形成方法として、開口部 13 の深さ次第では、スクリーン印刷法により塗布するものであってもよい。

【0042】

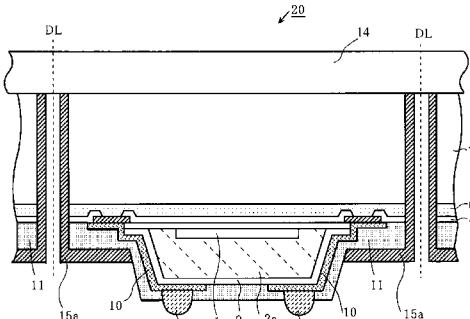

続いて、前記開口部 13 の幅よりも狭い幅を有したダイシングブレードを用いて、前記第 2 の保護膜 15 を分断することで、図 9 に示すように、前記支持体 7 の側面部に第 2 の保護膜 15a が形成されたチップサイズパッケージ型の半導体装置 20 が完成する。そして、UV テープ 14 から剥離された半導体装置 20 は、前記導電端子 12 を介してプリント基板等に実装される。30

【0043】

本発明の半導体装置 20 では、第 2 の保護膜 15a を支持体 7 の側面部に形成したこと、支持体 7 としてのガラスがダイスカットされたままの剥き出しの状態にならず、外部からの物理的な衝撃等によりガラスが欠ける、割れるといった不具合を防止できる。

【0044】

また、照度センサー用途においては、第 2 の保護膜 15a の存在により、干渉型の IR カットコートではカット特性が悪かった斜め光の入射を防止でき、信頼性の高い半導体装置を提供することできる。40

【0045】

また、本発明は上記実施形態に限定されることはなく、その要旨を逸脱しない範囲で変更が可能であることは言うまでもない。例えば、上記実施形態では、ボール状の導電端子を有する BGA (Ball Grid Array) 型の半導体装置について説明したが、本発明は LGA (Land Grid Array) 型やその他の CSP (Chip Size Package) 型の半導体装置に適用するものであっても構わない。

【0046】

また、上記実施形態では、前記導電端子 12 が前記配線層 10 を介して半導体基板の裏

10

20

30

40

50

面上に形成されていたが、例えば前記配線層10を介することなく、導電端子が直接パッド電極4に接続するようにして、当該導電端子を半導体基板の側面に隣接するように配置しても構わない。

#### 【0047】

更に、例えば前記半導体基板2の裏面からパッド電極4が露出するように開口部を設け、当該開口部を介して貫通電極を構成する半導体装置に、本発明を適用するものでもよい。

#### 【図面の簡単な説明】

#### 【0048】

【図1】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。 10

【図2】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図3】本発明の一実施形態に係る半導体装置の製造方法を説明する平面図である。

【図4】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図5】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図6】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図7】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図8】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図9】本発明の一実施形態に係る半導体装置の製造方法を説明する断面図である。

【図10】従来の半導体装置を説明する断面図である。

#### 【符号の説明】

#### 【0049】

|           |                |            |              |       |

|-----------|----------------|------------|--------------|-------|

| 1 半導体集積回路 | 2 半導体基板        | 2 a 半導体チップ | 3 絶縁膜        | 4     |

| パッド電極     | 5 パッセーション膜     | 6 接着層      | 7 支持体        | 8 開口部 |

| 9 絶縁膜     | 10 配線層         | 11 第1の保護膜  | 12 導電端子      | 13 開  |

| 口部        | 15, 15a 第2の保護膜 | 20 半導体装置   | D L ダイシングライン |       |

#### 【図1】

1:半導体集積回路

2:半導体基板

3:絶縁膜

4:パッド電極

5:パッセーション膜

6:接着層

7:支持体

【図3】

#### 【図2】

8:開口部

A.

B.

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

|            |                |

|------------|----------------|

| 100: 半導体基板 | 101: 半導体集積回路   |

| 102: バット電極 | 103: 絶縁膜       |

| 105: 支持体   | 104: バッシベーション膜 |

| 108: 配線層   | 106: 接着層       |

|            | 107: 絶縁膜       |

|            | 109: 保護層       |

|            | 110: 導電端子      |

---

フロントページの続き

F ターム(参考) 5F033 HH08 HH11 JJ01 KK08 KK11 PP15 PP26 QQ07 QQ08 QQ09

RR04 RR06 SS11 SS15 VV07