(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294518

(P2005-294518A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

**H01L 21/768**

**H01L 21/8242**

**H01L 21/8247**

**H01L 27/108**

**H01L 27/115**

F 1

H01L 21/90

H01L 27/10 434

H01L 27/10 625A

H01L 27/10 651

H01L 27/10 681B

テーマコード(参考)

5FO33

5FO83

5F1O1

審査請求 未請求 請求項の数 5 O L (全 26 頁) 最終頁に続く

(21) 出願番号

特願2004-107154 (P2004-107154)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(71) 出願人 598082433

中部東芝エンジニアリング株式会社

愛知県名古屋市中区栄1-16-6 名古屋三蔵東邦生命ビル6階

(74) 代理人 100071135

弁理士 佐藤 強

(74) 代理人 100119769

弁理士 小川 清

(72) 発明者

渡野邊 恒

三重県四日市市山之一色町800番地 株式会社東芝四日市工場内

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】 (修正有)

**【課題】** 上部導電層および下部導電層を接続する接続配線層の外周面にスペーサを使用したとしてもスペーサの機能を生かしながら上部導電層および接続配線層間の接触面積を増加させることができ、接触部分の抵抗を低減できるようにする。

**【解決手段】** 第3の多結晶シリコン層3の上板部3aの上面部3aaおよび上側面部3abにおいてチタン層15が第3の多結晶シリコン層3に接触するようになっている。これにより第3の多結晶シリコン層3およびチタン層15間の接触面積を増加させることができるようになる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

上部導電層および下部導電層間に形成された第1の絶縁膜と、

前記上部導電層と上面部において接触すると共に前記下部導電層と接触するように形成され、前記上部導電層および下部導電層間を電気的に接続する接続配線層と、

前記接続配線層の側壁外周面に対して前記第1の絶縁膜とは異なる材質により隣接する接続配線層との間のスペーサとして形成された第2の絶縁膜とを備え、

前記接続配線層は、当該接続配線層の上面部および上側面部において前記上部導電層と接触するように構成されていることを特徴とする半導体装置。

**【請求項 2】**

半導体基板と、

この半導体基板上に形成された複数のゲート電極と、

このゲート電極上に形成された第1の絶縁膜と、

この第1の絶縁膜上に形成されたビット線と、

前記半導体基板の表面の隣接するゲート電極間に形成された拡散層と、

前記ビット線と前記拡散層とを電気的に接続する接続配線層であって、隣接するゲート電極に挟まれた下配線部とこの下配線部の上に位置し側端が前記ゲート電極の上面に張り出した上配線部とを有し、この上配線部の上面および側面の上部が前記ビット線に接続した接続配線層と、

前記下配線部と前記ゲート電極との間および前記側面の下部と前記ビット線との間に設けられた第2の絶縁膜とを具備したことを特徴とする半導体装置。 20

**【請求項 3】**

下部導電層の上層側に第1の絶縁膜を形成する工程と、

前記下部導電層の上部に対して接続配線層を少なくとも第1の絶縁膜の上方まで埋込み形成する工程と、

隣接する接続配線層との間のスペーサとして前記接続配線層の側壁外周面に第2の絶縁膜を形成する工程と、

前記接続配線層の側壁外周面について当該接続配線層上面部から下方にかけて形成された前記第2の絶縁膜の上部を除去する工程と、

この第2の絶縁膜が除去された位置において前記接続配線層の上側面部に接触するよう上部導電層を形成する工程とを備えたことを特徴とする半導体装置の製造方法。 30

**【請求項 4】**

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上のゲート電極形成領域にゲート電極を形成する工程と、

このゲート電極を覆うようにゲート電極分離用絶縁膜を形成する工程と、

前記ゲート電極分離用絶縁膜の上部にビット線コンタクト形成領域を除いて第1の絶縁膜を形成する工程と、

複数の前記ゲート電極分離用絶縁膜間に位置するビット線コンタクト形成領域に対して隣接するビット線コンタクト形成領域との間のスペーサとして第2の絶縁膜を形成する工程と、 40

前記ビット線コンタクト形成領域において下部導電層と接触すると共に前記ゲート電極分離用絶縁膜の上方まで上面部が形成されるように接続配線層を前記第2の絶縁膜内に埋込み形成する工程と、

前記接続配線層の上面部から下方に上面が位置するように第1の絶縁膜を除去する工程と、

前記接続配線層の上面部から下方まで当該接続配線層の上側面部に形成された前記第2の絶縁膜を除去する工程と、

前記第1および第2の絶縁膜の除去された前記接続配線層の上側面部に接触するように上部導電層を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

**【請求項 5】**

半導体基板上にゲート絶縁膜を形成する工程と、

前記ゲート絶縁膜上のゲート電極形成領域に前記ゲート電極を形成する工程と、

このゲート電極を覆うようにゲート電極分離用絶縁膜を形成する工程と、

前記ゲート電極分離用絶縁膜の上部にピット線コンタクト形成領域を除いて第1の絶縁膜を形成する工程と、

複数の前記ゲート電極分離用絶縁膜間に位置するピット線コンタクト形成領域に対して隣接するピット線コンタクト形成領域との間のスペーサとして第2の絶縁膜を形成する工程と、

前記ピット線コンタクト形成領域において下部導電層と接触すると共に前記ゲート電極分離用絶縁膜の上方まで上面部が形成されるように接続配線層を前記第2の絶縁膜内に埋込み形成する工程と、

前記接続配線層の上面部から下方まで当該接続配線層の上側面部について前記第2の絶縁膜を除去する工程と、

前記接続配線層の上面部から下方に上面部が位置するように第1の絶縁膜を除去する工程と、

前記第1および第2の絶縁膜の除去された前記接続配線層の上側面部に接触するように上部導電層を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、上部導電層および下部導電層を電気的に接続する接続配線層構造を備えた半導体装置およびその製造方法に関する。

#### 【背景技術】

#### 【0002】

近年の設計ルールの縮小化に伴い、隣接する接続配線層との間の接触（ショート）や電気的相互作用を防ぐため、接続配線層の外周面に絶縁膜を形成しスペーサを設ける技術が開発されている。具体的には、複数の配線層間を接続する接続配線層の構造として例えば特許文献1に開示された技術が知られている。この特許文献1に開示されている技術によれば、配線層（接続配線層に相当）の周囲に構成した絶縁膜（第2の絶縁膜に相当）により配線層同士あるいは配線層と基板が接触するのを防ぐと共に、腐食による信頼性低下を抑制している。またこの絶縁膜をCVD法を使用して形成することにより配線層の上側だけでなく、側面、裏面にも被着させることで有効な絶縁構造を構成している。

#### 【0003】

他方、複数の配線層間を接続する接続配線層の構造として例えば特許文献2に開示された技術が知られている。この特許文献2に開示されている技術によれば、導電体層を接続する埋込み配線について絶縁膜を選択的に後退させることで導電体層の表面を露出させることにより接觸面積を増加させている。

#### 【特許文献1】特開平6-310612号公報（第5頁，図1）

#### 【特許文献2】特開2002-198421（第6頁）

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0004】

しかしながら、配線層の外周に絶縁膜をスペーサとして形成すると、その後、別工程で上部導電層を形成する場合には、接続配線層および上部導電層間の接觸面は接続配線層の上面部とのみしか接觸させることができない。

近年、さらに設計ルールが縮小化しているため、接続配線層および上部導電層の接觸面が接続配線層の上面部のみに限られると接觸面積を増加させることができず、接觸抵抗を低減することができない。さらに、特許文献2に開示された技術を適用したとしても、スペーサを選択的に後退させて接続配線層との間の接觸面積を増加させることができるもの

10

20

30

40

50

の、スペーサを構成する絶縁膜を後退させる場所によってはスペーサとしての機能を十分に発揮できなくなってしまう。

#### 【0005】

本発明は、上記事情に鑑みてなされたものであり、その目的は、上部導電層および下部導電層を接続する接続配線層の側壁外周面にスペーサを使用したとしてもスペーサの機能を生かしながら上部導電層および接続配線層間の接触面積を増加させることができ、接触部分の抵抗を低減できる半導体装置およびその製造方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0006】

本発明の半導体装置は、上部導電層および下部導電層間に形成された第1の絶縁膜と、上部導電層と上面部において接触すると共に下部導電層と接触するように形成され上部導電層および下部導電層間を電気的に接続する接続配線層と、接続配線層の側壁外周面に対して第1の絶縁膜とは異なる材質により隣接する接続配線層との間のスペーサとして形成された第2の絶縁膜とを備え、接続配線層は、接続配線層の上面部および上側面部において上部導電層と接触するように構成されていることに特徴を有している。

#### 【0007】

このような構成によれば、接続配線層が、当該接続配線層の上面部および上側面部において上部導電層と接触するため、接続配線層の上面部のみで上部導電層と接触する構成に比較して接触部分の抵抗値が低減される。したがって、たとえ上部導電層および下部導電層を接続するための接続配線層の側壁外周面にスペーサを使用したとしても、接続配線層の上側面外周部以外についてはスペーサとして機能するようになるため、スペーサの機能を生かしながら上部導電層および接続配線層間の接触面積を増加させることができ、接触部分の抵抗を低減できるという効果を奏する。

#### 【0008】

しかもリソグラフィ技術により上部導電層を形成する場合にマスクの合わせずれが少なからず生じるが、このマスクの合わせずれに起因して上部導電層および接続配線層の上面部間の接触面積が減少しても、上部導電層および接続配線層は当該接続配線層の上面部のみに関わらず上側面部でも接触するため、接触面積の減少に伴う接触部分の高抵抗化を抑制できるようになる。

#### 【0009】

本発明の半導体装置は、半導体基板と、この半導体基板上に形成された複数のゲート電極と、このゲート電極上に形成された第1の絶縁膜と、この第1の絶縁膜上に形成されたビット線と、半導体基板の表面の隣接するゲート電極間に形成された拡散層と、ビット線と拡散層とを電気的に接続する接続配線層であって、隣接するゲート電極に挟まれた下配線部とこの下配線部の上に位置し側端がゲート電極の上面に張り出した上配線部とを有し、この上配線部の上面および側面の上部がビット線に接続した接続配線層と、下配線部とゲート電極との間および側面の下部とビット線との間に設けられた第2の絶縁膜とを具備したことを特徴としている。

#### 【0010】

本発明の半導体装置の製造方法は、下部導電層の上層側に第1の絶縁膜を形成する工程と、下部導電層の上部に対して接続配線層を少なくとも第1の絶縁膜の上方まで埋込み形成する工程と、隣接する接続配線層との間のスペーサとして前記接続配線層の側壁外周面に第2の絶縁膜を形成する工程と、接続配線層の側壁外周面について当該接続配線層上面部から下方にかけて形成された第2の絶縁膜の上部を除去する工程と、この第2の絶縁膜が除去された位置において接続配線層の上側面部に接触するように上部導電層を形成する工程とを備えたことを特徴としている。

#### 【0011】

このような半導体装置の製造方法によれば、スペーサとしての第2の絶縁膜が形成された接続配線層の側壁外周面のうち接続配線層上面部から下方にかけて形成された第2の絶縁膜の上部を除去し、この第2の絶縁膜の除去位置において接続配線層の上側面部に接触

10

20

30

40

50

するように上部導電層を形成するため、この接続面として形成される接続配線層の上側面外周部以外ではスペーサとして機能するようになり、スペーサの機能を維持しながら上部導電層および接続配線層間の接触面積を増加させることができ、接触部分の抵抗を低減できる。

【0012】

本発明の半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上のゲート電極形成領域にゲート電極を形成する工程と、このゲート電極を覆うようにゲート電極分離用絶縁膜を形成する工程と、ゲート電極分離用絶縁膜の上部にビット線コンタクト形成領域を除いて第1の絶縁膜を形成する工程と、複数のゲート電極分離用絶縁膜間に位置するビット線コンタクト形成領域に対して隣接するビット線コンタクト形成領域との間のスペーサとして第2の絶縁膜を形成する工程と、ビット線コンタクト形成領域において下部導電層と接触すると共にゲート電極分離用絶縁膜の上方まで上面部が形成されるように接続配線層を第2の絶縁膜内に埋込み形成する工程と、接続配線層の上面部から下方に上面が位置するように第1の絶縁膜を除去する工程と、接続配線層の上面部から下方まで当該接続配線層の上側面部に形成された第2の絶縁膜を除去する工程と、第1および第2の絶縁膜の除去された接続配線層の上側面部に接触するように上部導電層を形成する工程とを備えたことを特徴としている。

【0013】

このような半導体装置の製造方法によれば、第1および第2の絶縁膜が除去された接続配線層の上側面部に接触するように上部導電層を形成しているので、接触面積を増加させることができ、接触抵抗を低減することができるようになると共に、上部導電層、下部導電層およびゲート電極について相互の絶縁性を保つことができるようになる。

本発明の半導体装置の製造方法は、半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上のゲート電極形成領域にゲート電極を形成する工程と、このゲート電極を覆うようにゲート電極分離用絶縁膜を形成する工程と、ゲート電極分離用絶縁膜の上部にビット線コンタクト形成領域を除いて第1の絶縁膜を形成する工程と、複数のゲート電極分離用絶縁膜間に位置するビット線コンタクト形成領域に対して隣接するビット線コンタクト形成領域との間のスペーサとして第2の絶縁膜を形成する工程と、接続配線層の上面部から下方まで当該接続配線層の上側面部について第2の絶縁膜を除去する工程と、接続配線層の上面部から下方に上面部が位置するように第1の絶縁膜を除去する工程と、第1および第2の絶縁膜の除去された接続配線層の上側面部に接触するように上部導電層を形成する工程とを備えたことに特徴を有している。

【0014】

このような半導体装置の製造方法によれば、第1および第2の絶縁膜の除去された接続配線層の上側面部に接触するように上部導電層を形成するため、接触面積を増加させることができ、接触部分の抵抗を低減できると共に、上部導電層、下部導電層およびゲート電極について相互の絶縁性を保つことができるようになる。

【発明の効果】

【0015】

本発明によれば、上部導電層および下部導電層を接続する接続配線層の側壁外周面にスペーサを使用したとしてもスペーサの機能を生かしながら上部導電層および接続配線層間の接触面積を増加させることができるという優れた効果を奏する。

【発明を実施するための最良の形態】

【0016】

(第1の実施形態)

以下、本発明をNAND型フラッシュメモリ装置に適用した第1の実施形態について図1～図19を参照しながら説明する。

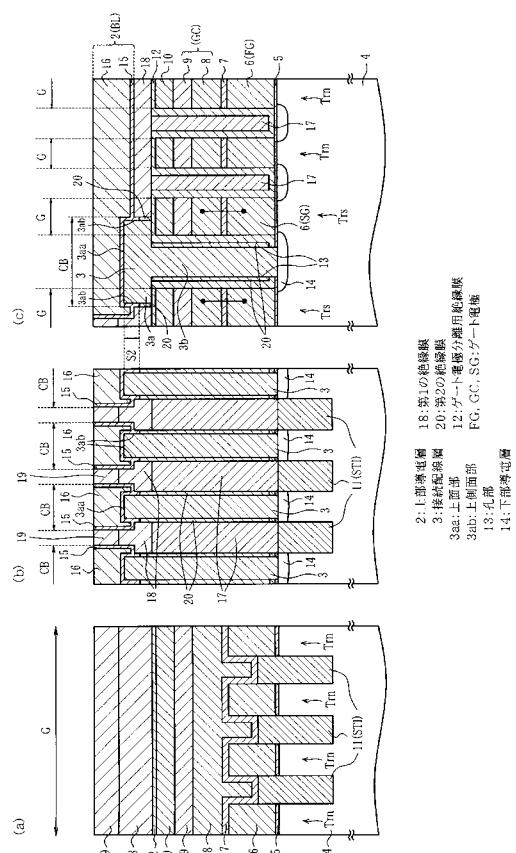

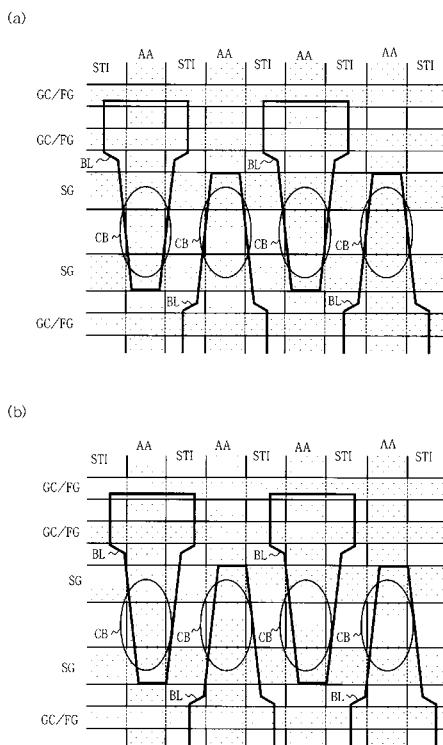

NAND型フラッシュメモリ装置(不揮発性記憶装置、半導体記憶装置、半導体装置)は、メモリセル領域および周辺回路領域に区画されている。図2は、メモリセル領域におけるメモリセルアレイの配置形態の一例を示している。メモリセルアレイArrは、ビット

10

20

30

40

50

線 B L 側やソース線 S 側にそれぞれ接続された選択ゲートトランジスタ T r s および T r s と、これらの選択ゲートトランジスタ T r s および T r s 間に複数個直列接続されたメモリセルトランジスタ T r n とから構成されている。これらのメモリセルアレイ A r が図 2 に示すように縦列方向に配列されることによりメモリセル領域が形成される。

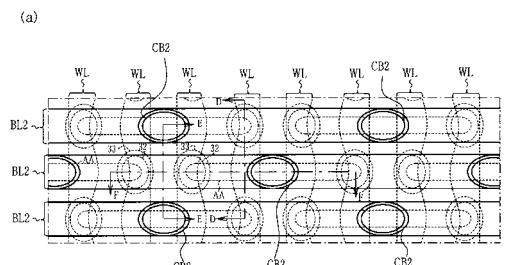

#### 【0017】

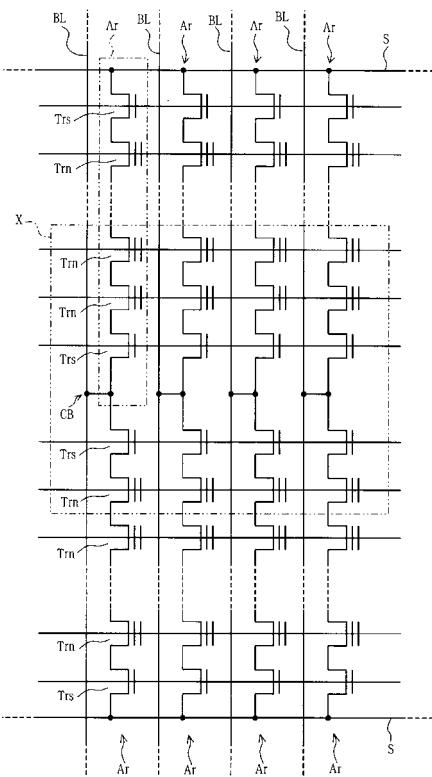

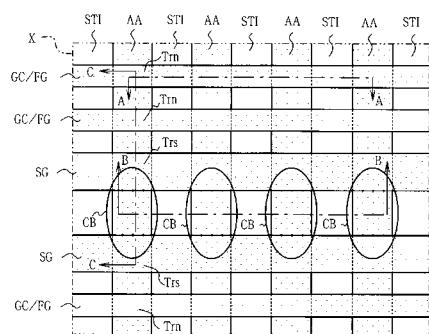

図 1 は、この回路例におけるメモリセルアレイの概略配置の一部（図 2 の X 領域）を模式的な平面図により示している。この図 3 において、G C はコントロールゲート電極配線、F G はフローティングゲート電極、S G は選択ゲート配線、C B はビット線コンタクト形成領域、A A はアクティブエリア（活性領域）、S T I は素子分離領域を示している。

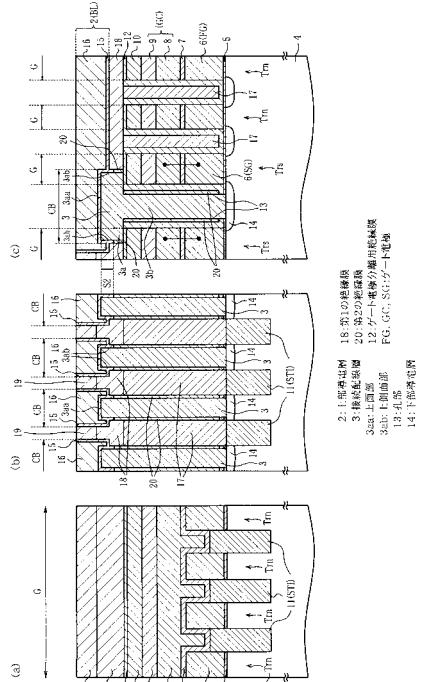

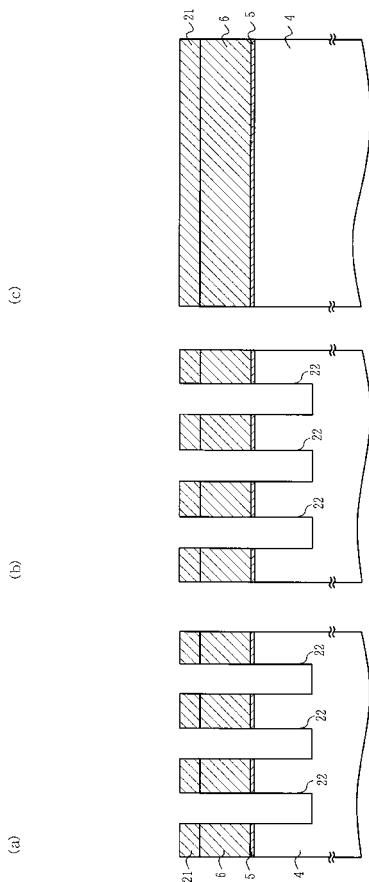

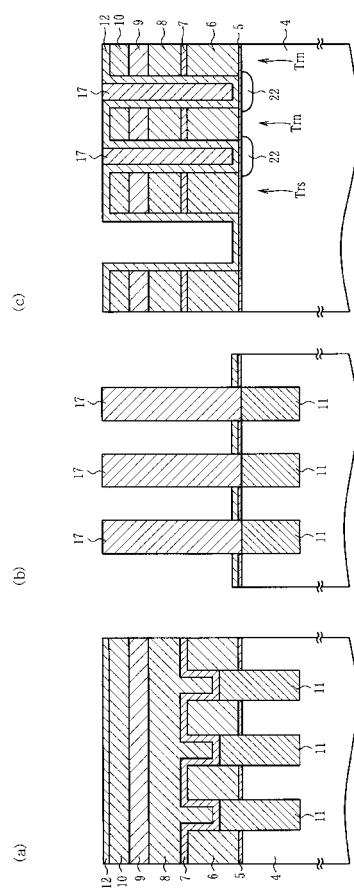

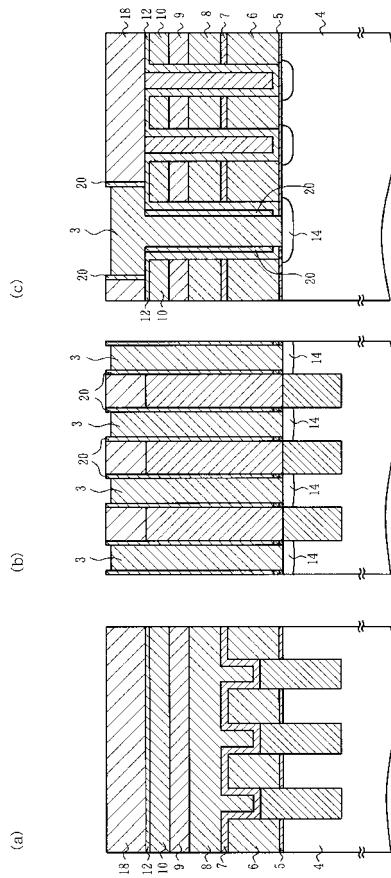

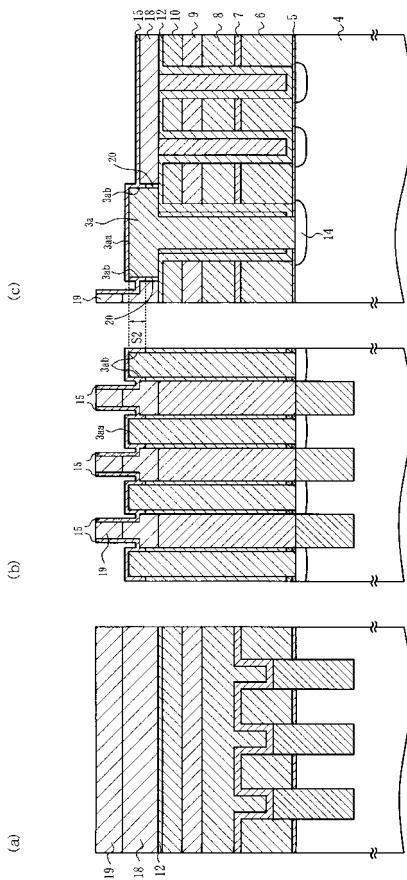

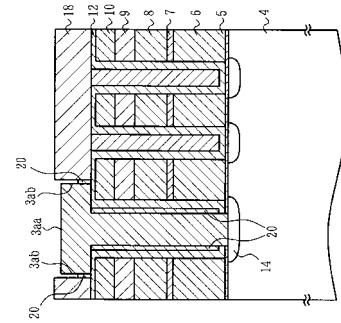

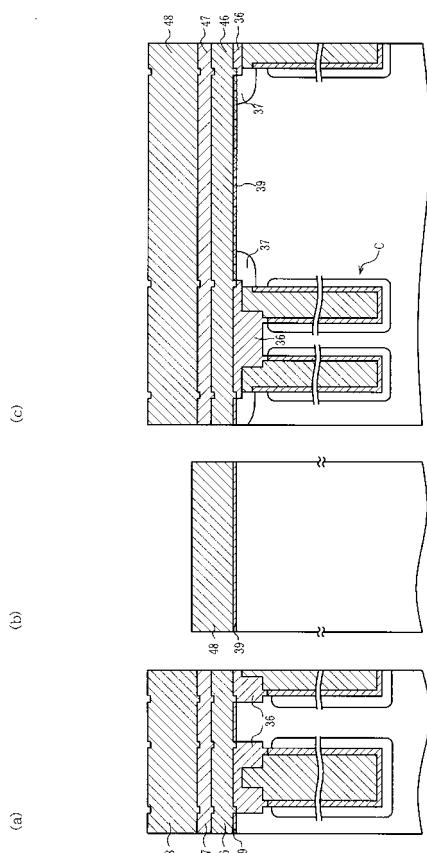

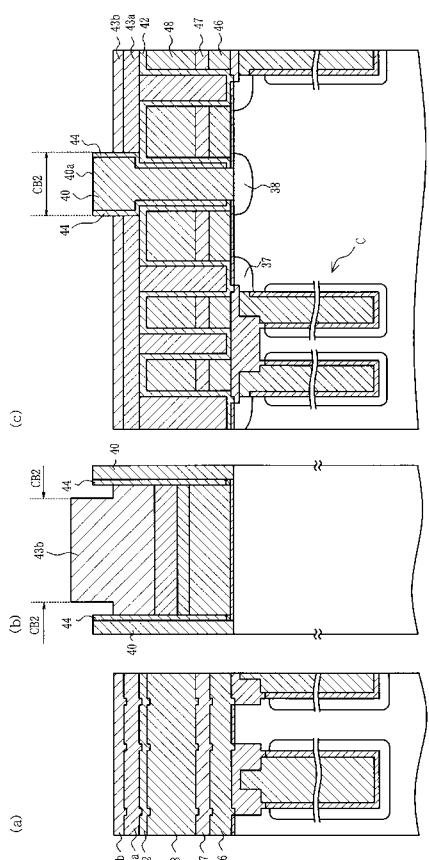

また、図 1 ( a ) は、図 3 における A - A 線に沿う模式的な縦断側面図を示しており、図 1 ( b ) は、図 3 における B - B 線に沿う模式的な縦断側面図を示しており、さらに図 1 ( c ) は、図 3 における C - C 線に沿う模式的な縦断側面図を示している。

#### 【0018】

本実施形態においては、図 1 ( a ) ~ 図 1 ( c ) に示す上部導電層 2 ( ビット線 B L に相当 ) および接続配線層 ( 後述する第 3 の多結晶シリコン層 3 に相当 ) の接続形態に特徴を備えているため、その接続形態の説明について詳細に行う。

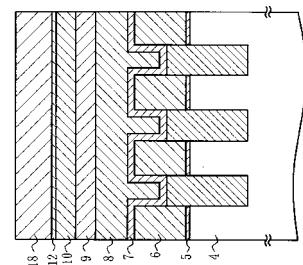

図 1 ( a ) および図 1 ( c ) に示すように、各トランジスタ T r s , T r n におけるゲート電極形成領域 G には、p 型のシリコン半導体基板 4 上にシリコン酸化膜 5 , 第 1 の多結晶シリコン層 6 , O N O ( Oxide Nitride Oxide ) 膜 7 , 第 2 の多結晶シリコン層 8 , タングステンシリサイド ( W S i ) 層 9 , 第 1 のシリコンナイトライド膜 1 0 の順に下から積層形成されている。尚、選択ゲート形成領域 G において、第 1 および第 2 の多結晶シリコン層 6 および 8 はその外部において電気的に接続されているが、この接続形態については図示していない。尚、p 型のシリコン半導体基板 4 上に形成された実施形態を示すが、これは p ウエル領域に形成されていても良いし、必要に応じて逆導電型のシリコン半導体基板に形成されていても良い。

#### 【0019】

シリコン酸化膜 5 は、例えば 8 nm の膜厚により形成されており、各トランジスタ T r s , T r n のゲート絶縁膜として機能する。

第 1 の多結晶シリコン層 6 は、p 型の不純物がドープされた多結晶シリコンにより例えば 160 nm の膜厚で形成されており、トランジスタ T r n のフローティングゲート電極 F G として機能する。

#### 【0020】

O N O 膜 7 は、図 1 ( a ) に示すように、第 1 の多結晶シリコン層 6 の側壁にも形成されている。この O N O 膜 7 は、素子分離領域 ( S T I ) として機能する第 2 のシリコン酸化膜 1 1 と共に第 1 の多結晶シリコン層 6 を覆うように例えば 17 nm ( Oxide5nm : SiN<sub>7</sub>nm : Oxide5nm ) の膜厚により形成され、トランジスタ T r n のゲート電極形成領域 G における第 1 および第 2 の多結晶シリコン層 6 および 8 ( フローティングゲート電極 F G およびコントロールゲート電極 G C ) を電気的に絶縁するために形成されている。

#### 【0021】

第 2 の多結晶シリコン層 8 は、p 型の不純物がドープされた多結晶シリコンにより例えば 100 nm 膜厚で形成されており、トランジスタ T r n のゲート電極形成領域 G においては、タングステンシリサイド層 9 と共にコントロールゲート電極 G C として機能し、トランジスタ T r s のゲート電極形成領域においてはタングステンシリサイド層 9 と共に選択ゲート電極 S G として機能し、所謂ワード線として形成される。タングステンシリサイド層 9 は、例えば 90 nm の膜厚により形成されている。また、第 1 のシリコンナイトライド膜 1 0 は、絶縁膜として機能する。

#### 【0022】

各トランジスタ T r s , T r n のゲート電極形成領域 G に形成された各層 6 ~ 1 0 を覆うように、第 2 のシリコンナイトライド膜 1 2 が形成されている。この第 2 のシリコンナイトライド膜 1 2 は、隣接するトランジスタ T r s , T r n ... のゲート電極形成領域 G 間

10

20

30

40

50

を電気的に絶縁するようになっておりゲート電極分離用絶縁膜として機能する。

また、図1(b)および図1(c)並びに図3に示すように、隣接するトランジスタTrsおよびTrsのゲート電極形成領域G間(隣接する選択ゲートSG間)には、ビット線コンタクト形成領域CBが設けられている。

#### 【0023】

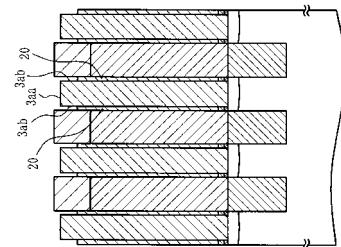

このビット線コンタクト形成領域CBには孔部13が形成されており、この孔部13に接続配線層として第3の多結晶シリコン層3が埋込み形成されている。この第3の多結晶シリコン層3は、図1(c)に示すように、トランジスタTrsおよびTrsを構成する各層6~10を覆う第2のシリコンナイトライド膜12の間に埋込み形成される。第3の多結晶シリコン層3は縦長橋円柱状に縦長片部3b(本発明の下配線部に相当)として形成されると共に、この上部に円板状に上板部3a(本発明の上配線部に相当)として形成されることにより、第3の多結晶シリコン層3は縦断面T字形状に形成される。第3の多結晶シリコン層3はシリコン半導体基板4に形成された拡散層14(本発明の下部導電層に相当)と上部導電層2を構成するチタン層15とを電気的に接続している。

#### 【0024】

この第3の多結晶シリコン層3の上板部3aは、図1(c)に示すように、トランジスタTrsのゲート電極形成領域Gの第2のシリコンナイトライド膜12の上部にまで水平方向に形成されている。また、図1(b)に示すように、隣接するビット線コンタクト形成領域CB間には第2のシリコン酸化膜17、第3のシリコン酸化膜18(本発明の第1の絶縁膜に相当)および第4のシリコン酸化膜19が埋込み形成されている。これらの第2、第3および第4のシリコン酸化膜17~19は、隣接する第3の多結晶シリコン層3を電気的に絶縁するために設けられている。

#### 【0025】

図1(b)および図1(c)に示すように、第3の多結晶シリコン層3の縦長片部3bの外周面には第3のシリコンナイトライド膜20が形成されている。この第3のシリコンナイトライド膜20は、図1(b)に示すように、第3の多結晶シリコン層3と、第2および第3のシリコン酸化膜17および18との間に縦長状に形成されると共に第3の多結晶シリコン層3の側壁に形成されるもので、隣接する第3の多結晶シリコン層3間の電気的絶縁機能を強化するためのスペーサとして機能する。

#### 【0026】

また、第3の多結晶シリコン層3の上板部3aにおける側壁外周面下部には第3のシリコンナイトライド膜20(本発明の第2の絶縁膜に相当)が形成されている。この第3のシリコンナイトライド膜20も前述したシリコンナイトライド膜と同様に、隣接する第3の多結晶シリコン層3間のスペーサとして機能するようになっている。

図1(c)に示すように、1つのメモリセルアレイを構成する各トランジスタTrnおよびTrsのゲート電極形成領域G間には、第2のシリコン酸化膜17が埋込み形成されている。この部位に埋め込まれる第2のシリコン酸化膜17は、各トランジスタTrsおよびTrn...のゲート電極形成領域G間の電気的絶縁機能を向上するために埋込み形成されており、第2のシリコンナイトライド膜12の上面に対して面一になるように埋込み形成されている。

#### 【0027】

第2のシリコンナイトライド膜12および第2のシリコン酸化膜17の上部には、ビット線コンタクト形成領域CB以外の領域に対して第3のシリコン酸化膜18が形成されている。この第3のシリコン酸化膜18は、第3の多結晶シリコン層3の側方に水平方向に薄板状に形成されており、各種ゲート電極(コントロールゲート電極GC、選択ゲート電極SG、フローティングゲート電極FG)やタングステンシリサイド層9とビット線BL(タングステン層16およびチタン層15)との間の絶縁性能を保持するために設けられている。

#### 【0028】

また、図1(b)および図1(c)に示すように、第3の多結晶シリコン層3の上板部

10

20

30

40

50

3 a のうちの上面部 3 a a および上側面部 3 a b に接触するように上部導電層としてタンゲステン (W) 層 1 6 およびチタン (Ti) 層 1 5 が形成されている。

これらのタンゲステン層 1 6 およびチタン層 1 5 は、所謂ビット線 BL として機能する。チタン層 1 5 は例えば 4 5 nm の膜厚により形成され、第 3 の多結晶シリコン層 3 の上板部 3 a のうちの上面部 3 a a および上側面部 3 a b , 並びに第 3 のシリコンナイトライド膜 2 0 の上部に接触するように形成されていると共に、第 3 のシリコン酸化膜 1 8 の上部に例えば 4 5 nm の膜厚により形成されている。このチタン層 1 5 は、第 3 のシリコン酸化膜 1 8 とタンゲステン層 1 6 との間に両層 1 6 および 1 8 が非接触状態を保つように形成されている。タンゲステン層 1 6 は、例えば 4 0 0 nm の膜厚により形成され、その下部がチタン層 1 5 に覆われるようによく形成されている。

10

#### 【 0 0 2 9 】

第 1 の実施形態の構成によれば、第 3 の多結晶シリコン層 3 の上板部 3 a の全側壁が第 3 のシリコンナイトライド膜 2 0 により覆われてはおらず、第 3 の多結晶シリコン層 3 の上板部 3 a の上面部 3 a a および上側面部 3 a b においてチタン層 1 5 が第 3 の多結晶シリコン層 3 に接触するようになっているため、第 3 の多結晶シリコン層 3 およびチタン層 1 5 間の接触面積を増加させることができ（図 1 (b) および図 1 (c) の接触面積 S 2 を参照）。

#### 【 0 0 3 0 】

< 詳細な製造方法について >

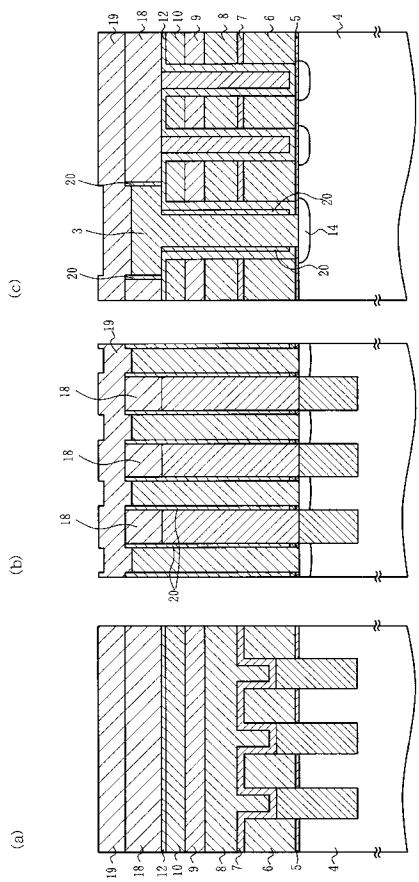

以下、図 4 ないし図 19 をも参照しながら、詳細な製造方法について説明する。尚、図 20

4 ~ 図 16 の図面中、同一の添え字 (a) ~ (c) を付した図面については、それぞれ図 3 の平面図における A - A 線, B - B 線, C - C 線に沿う縦断側面図を示している。尚、前記した構成を形成することができれば、以下に示す工程については必要に応じて省いても良いし付加しても良い。

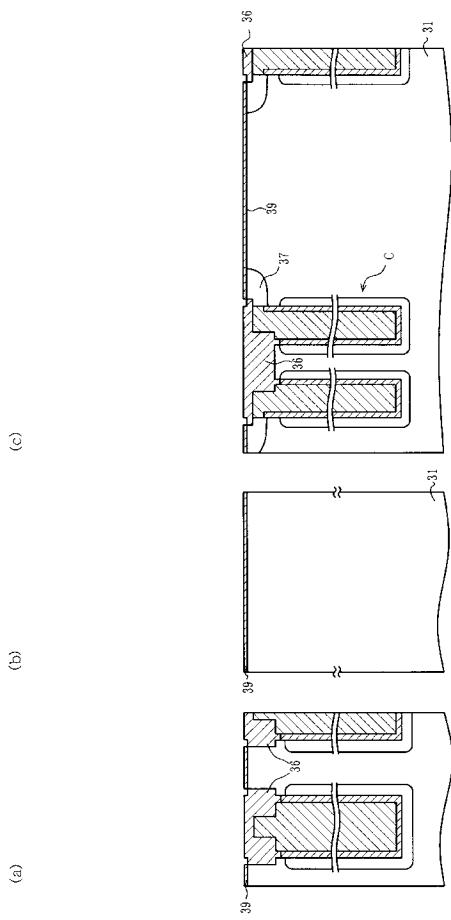

#### 【 0 0 3 1 】

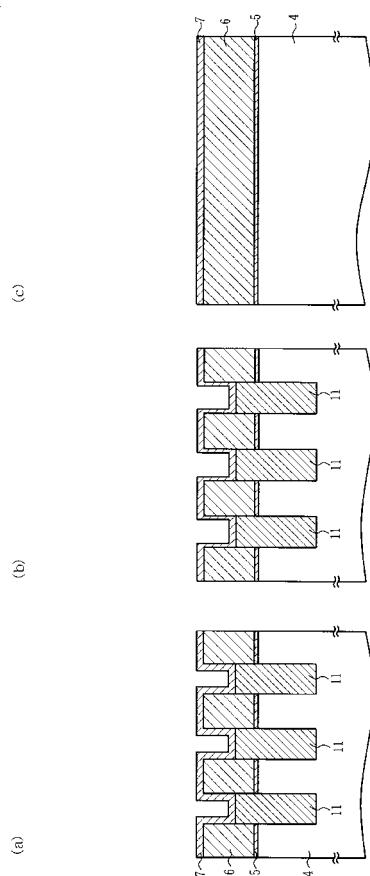

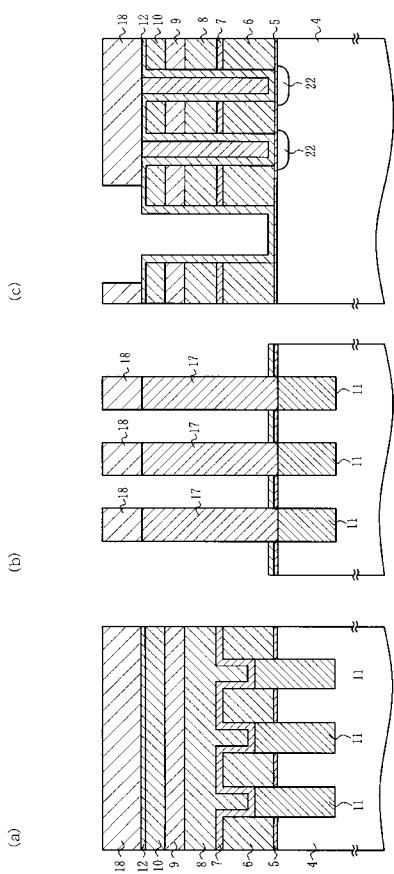

(1) 図 4 に示す構造を形成する工程について

p 型のシリコン半導体基板 4 の上にシリコン酸化膜 5 を例えば 8 nm 形成する。そして、減圧 CVD (Low Pressure Chemical Vapor Deposition) 法により p 型の不純物がドープされた第 1 の多結晶シリコン層 6 を例えば 1 6 0 nm 形成し、さらに第 4 のシリコンナイトライド膜 2 1 を例えば 7 0 nm 形成する。そして、その上にフォトレジスト（図示せず）を塗布しリソグラフィ技術により所定のレジストパターンに加工し、このレジストパターンをマスクとして RIE (Reactive Ion Etching) 法により第 4 のシリコンナイトライド膜 2 1 , 第 1 の多結晶シリコン層 6 , 第 1 のシリコン酸化膜 5 , およびシリコン半導体基板 4 を同時に所定の深さまで加工することにより素子分離領域 STI を形成するための溝部 2 2 を形成し、フォトレジストを除去する。すると図 4 に示すように形成される。

30

#### 【 0 0 3 2 】

(2) 図 5 に示す構造を形成する工程について

(1) の形成工程終了後、HDP (High Density Plasma) - CVD 法により第 2 のシリコン酸化膜 1 1 を溝部 2 2 に埋込むように例えば 5 5 0 nm 堆積する。そして、第 4 のシリコンナイトライド膜 2 1 が露出するように CMP (Chemical Mechanical Polishing) 法により第 2 のシリコン酸化膜 1 1 を平坦化し、窒素雰囲気において例えば 9 0 0 に加熱する。次に、例えば 1 5 0 のリン酸処理により第 4 のシリコンナイトライド膜 2 1 を除去する。そして、フォトレジスト（図示せず）を塗布し、リソグラフィ技術により所定のレジストパターンに加工し、このレジストパターンをマスクとして RIE 法により第 2 のシリコン酸化膜 1 1 を落とし込む。フォトレジストを除去後、減圧 CVD 法により第 2 のゲート絶縁膜としての ONO 膜 7 を 1 7 nm (Oxide:5nm, SiN:7nm, Oxide:5nm) 等方的に形成する。すると図 5 に示すように形成される。

40

#### 【 0 0 3 3 】

(3) 図 6 に示す構造を形成する工程について

(2) の形成工程終了後、酸化性雰囲気において加熱する。そして、ONO 膜 7 の上に

50

減圧 C V D 法により P 型の不純物がドープされた第 2 の多結晶シリコン層 8 を例えば 100 nm 形成する。そして、第 2 の多結晶シリコン層 8 の上にスパッタ法によりタングステンシリサイド層 9 を例えば 90 nm 形成する。そして、減圧 C V D 法により第 1 のシリコンナイトライド膜 10 を 300 nm 形成する。すると、図 6 に示すように形成される。

#### 【 0034 】

( 4 ) 図 7 に示す構造を形成する工程について

( 3 ) の形成工程終了後、フォトレジスト( 図示せず ) を塗布しリソグラフィ技術によりフォトレジストを所定のレジストパターンに加工し、このフォトレジストをマスクとして R I E 法により第 1 のシリコンナイトライド膜 10 をエッチングする。このエッチングは、ゲート電極形成領域 G 以外の領域について行われる。フォトレジストをアッシングにより除去した後、第 1 のシリコンナイトライド膜 10 をマスクとしてタングステンシリサイド層 9 , 第 2 の多結晶シリコン層 8 , O N O 膜 7 , および第 1 の多結晶シリコン層 6 を R I E 法によりエッチングする( 図 7 ( b ) および図 7 ( c ) 参照 ) 。

#### 【 0035 】

このとき、ビット線 B L を接続形成するためのビット線コンタクト形成領域 C B およびその周辺においては、第 1 のシリコンナイトライド膜 10 やタングステンシリサイド層 9 , 第 2 の多結晶シリコン層 8 , O N O 膜 7 , および第 1 の多結晶シリコン層 6 を R I E 法によりエッチングし、図 7 ( b ) に示すように、シリコン酸化膜 5 を除きシリコン半導体基板 4 上に形成された全層を除去する。すると図 7 に示すように形成される。

#### 【 0036 】

( 5 ) 図 8 に示す構造の形成工程について

( 4 ) の形成工程終了後、例えば 1050 程度の R T O (Rapid Thermal Oxidation) 处理を行う。そして、第 2 のシリコンナイトライド膜 12 を例えば 20 nm 等方的に形成する。その後、隣接するトランジスタ T r n および T r s のゲート電極形成領域 G 間に形成された第 2 のシリコン窒化膜 12 および第 2 のシリコン酸化膜 17 を介してシリコン半導体基板 4 に n 型の不純物を打込むことによりトランジスタ T r n および T r s のソース / ドレイン拡散層 22 を形成する。

#### 【 0037 】

その後、トランジスタ T r n および T r s のゲート電極形成領域 G 間に形成された第 2 のシリコンナイトライド膜 12 の上部に第 2 のシリコン酸化膜 17 を埋込み形成すると共に、トランジスタ T r n および T r s のゲート電極形成領域 G 間に形成された第 2 のシリコンナイトライド膜 12 の上部に第 2 のシリコン酸化膜 17 を埋込み形成する。

このとき、図 8 ( b ) に示すように、第 2 のシリコン酸化膜 17 を形成する。この第 2 のシリコン酸化膜 17 は、隣接する第 3 の多結晶シリコン層 3 間の電気的絶縁用として設けられている。

#### 【 0038 】

そして、燃焼酸化雰囲気において 800 程度でリフロー処理し、第 2 および第 1 のシリコンナイトライド膜 12 および 10 をストップとして C M P 法により第 2 のシリコン酸化膜 17 を平坦化する。その後、第 2 および第 1 のシリコンナイトライド膜 12 および 10 や第 2 のシリコン酸化膜 17 の上部に対してプラズマ C V D 法により第 3 のシリコン酸化膜 18 を形成する。フォトレジスト( 図示せず ) を塗布しリソグラフィ技術により所定のレジストパターンに加工し、第 3 のシリコン酸化膜 18 を除去する。すると図 9 に示すように形成される。

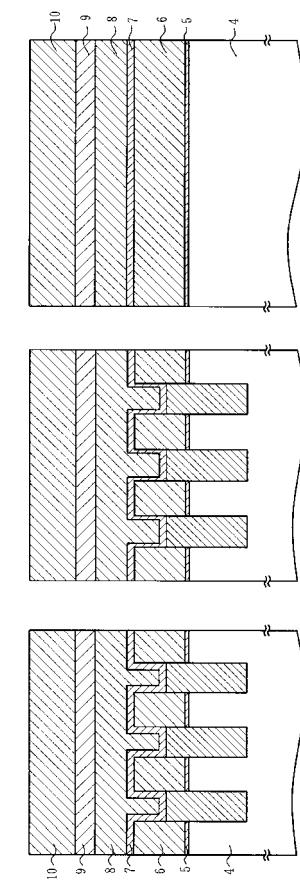

#### 【 0039 】

( 5 ) の形成工程終了後、図 10 に示すように、第 3 のシリコンナイトライド膜 20 を例えば 10 nm 等方的に形成する。さらに、図 11 に示すように、第 3 のシリコンナイトライド膜 20 をドライエッチングすることにより、第 3 のシリコン酸化膜 18 上に形成された第 3 のシリコンナイトライド膜 20 と、トランジスタ T r s のゲート電極形成領域 G 上に形成された第 3 のシリコンナイトライド膜 20 と、シリコン半導体基板 4 の直上部に形成された第 1 のシリコン酸化膜 5 とをゲート電極形成領域 G の側壁絶縁膜として形成さ

10

20

30

40

50

れる部分を除き除去する。すると、図11に示すように、第3のシリコン酸化膜18のピット線コンタクト形成領域CB側の側壁、および2のトランジスタTrsのゲート電極形成領域G間に挟まれたピット線コンタクト形成領域CB側の側壁に第2および第3のシリコンナイトライド膜12および20が残存する。

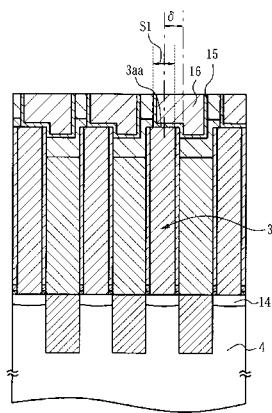

#### 【0040】

さらに、図12に示すように、第3の多結晶シリコン層3をピット線コンタクト形成領域CBに埋込み形成し、CDE(Chemical Dry Etching)法により第3の多結晶シリコン層3の上部をエッチバックし高さを調整する。その後、窒素性雰囲気において970の熱処理を行いドーパントを活性化させる。

さらに、図13に示すように、プラズマCVD法により第3のシリコン酸化膜18、第3のシリコンナイトライド膜20、および第3の多結晶シリコン膜3の上に、さらに第4のシリコン酸化膜19を形成することによりシリコン酸化膜の厚さを増加させる。

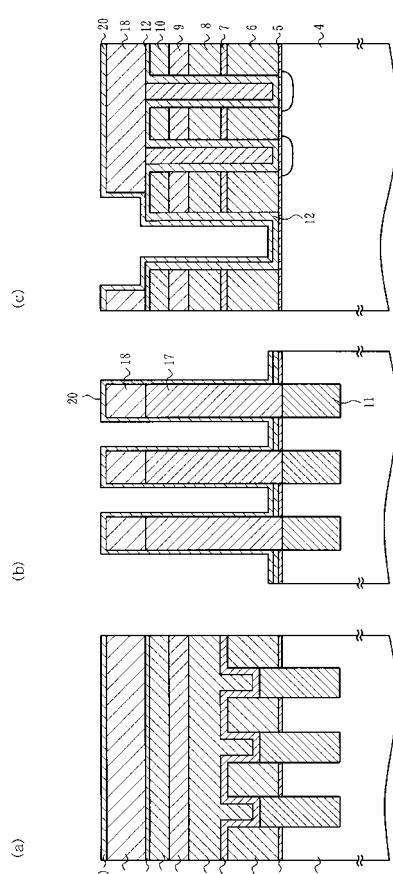

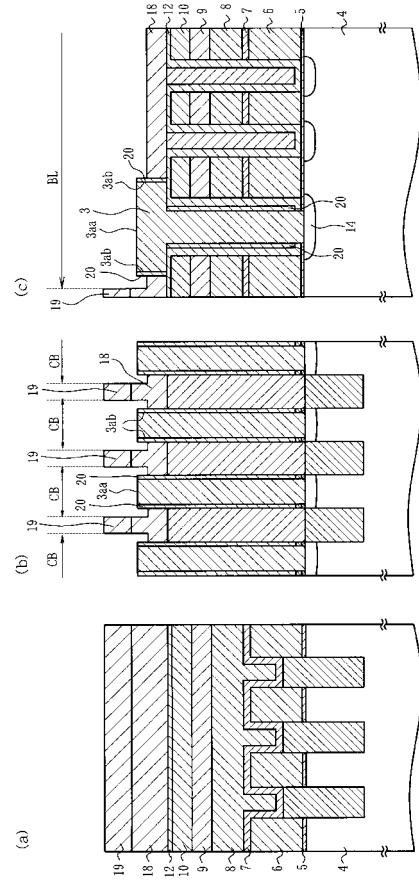

#### 【0041】

その後、フォトレジスト(図示せず)を塗布し当該フォトレジストに所定のレジストパターンを形成しこのレジストパターンをマスクとしてRIE法により第3および第4のシリコン酸化膜18および19を、多結晶シリコンおよびシリコン窒化膜に対して高選択性を有するエッチング条件によりエッチバックしピット線BLの領域を形成する。

このときピット線コンタクト形成領域CB周辺では、第3の多結晶シリコン層3の上板部3aの上面部3aaよりも下方まで第3のシリコン酸化膜18をエッチバックする。第3のシリコン窒化膜20は、第3の多結晶シリコン層3の上板部3aの上方部分については第3および第4のシリコン酸化膜18および19と略同時に除去されるが、第3の多結晶シリコン層3の上板部3aの側壁に第3のシリコン窒化膜20が付着し残存するようになる。

#### 【0042】

その後、図15に示すように、シリコン酸化膜や多結晶シリコンに対して高選択性を有するエッチング条件により(例えば、150のリン酸処理等によるウェットエッチング処理)、第3のシリコン酸化膜18の上面より下方で、且つ、第2のシリコンナイトライド膜12の上面より上方まで第3のシリコンナイトライド膜20を除去する。尚、ドライエッチングにより第3のシリコンナイトライド膜20を除去するようにしても良い。すなわち、第3の多結晶シリコン層3の側壁の上部について第3のシリコンナイトライド膜20を除去する。すると図15に示すように形成される。

#### 【0043】

この後、図16に示すように、PVD法によりTi膜15を例えば45nm等方的に形成する。そして水素を含む窒素性雰囲気において550, 90分加熱する。さらに、図1に示すように、PVD法によりW(タンゲステン)膜16を例えば400nm等方的に形成し、その後、タンゲステン膜16およびTi膜15を第4の多結晶シリコン酸化膜19が露出するまでCMP法により平坦化する。そして、水素を含む窒素性雰囲気において400, 30分熱処理する。さらに後工程を行うことにより、NAND型不揮発性記憶装置1のメモリセル領域を形成することができるようになる。

#### 【0044】

従来、第3の多結晶シリコン層3の上板部3aの外周面の側壁に第3のシリコンナイトライド膜20をスペーサとして形成してしまうと、第3の多結晶シリコン層3は上板部3aの上面部3aaとのみしかチタン層15と接触しないため接触部分の高抵抗化を免れない。

そこで本実施形態の製造方法では、第2のシリコンナイトライド膜12および第2のシリコン酸化膜17の上部にピット線コンタクト形成領域CBを除いて第3のシリコン酸化膜18を形成し、ピット線コンタクト形成領域CBにスペーサとして第2のシリコンナイトライド膜12を等方的に形成し、シリコン半導体基板4の上面に位置する第2および第3のシリコンナイトライド膜12および20を除去し、ピット線コンタクト形成領域CBにソース/ドレイン拡散層14と接触すると共に第2のシリコンナイトライド膜12の上

10

20

30

40

50

方まで上板部 3 a の上面部 3 a a が形成されるように第 3 の多結晶シリコン層 3 を埋込み形成し、第 3 のシリコン酸化膜 1 8 を第 3 の多結晶シリコン層 3 の上面部 3 a a から水平方向下方に上面が位置するように第 3 のシリコン酸化膜 1 8 を除去し、第 3 の多結晶シリコン層 3 の上面部 3 a a から水平方向下方まで第 3 のシリコンナイトライド層 2 0 を除去し、第 3 の多結晶シリコン層 3 の上側面部 3 a b にチタン層 1 5 を形成するため、第 3 の多結晶シリコン層 3 およびチタン層 1 5 間の接触面積を増加させることができ、これにより接触部分の抵抗を低減することができるようになる。

#### 【 0 0 4 5 】

また、ビット線 B L (チタン層 1 5 およびタンゲステン層 1 6) を形成するときに、図 1 7 ( a ) に模式的な平面図を示すように、ビット線コンタクト形成領域 C B に対してビット線 B L の形成領域のリソグラフィ技術によるマスク合わせずれが生じない場合には問題ないものの、図 1 7 ( b ) に示すように、特に隣接するビット線コンタクト形成領域 C B 側にリソグラフィ技術によるマスクの合わせずれが特にワード線方向 (ゲート電極形成方向) に生じると、第 3 の多結晶シリコン層 3 およびチタン層 1 5 の接触形態の基本構成例の模式的な断面図を図 1 9 に示すように、第 3 の多結晶シリコン層 3 およびチタン層 1 5 の接触部分が上面部 3 a a のみに留まってしまうと、第 3 の多結晶シリコン層 3 の上面部 3 a a では接触するが接触面積 S 1 が少なくなってしまう。

#### 【 0 0 4 6 】

本実施形態の製造方法によれば、マスクずれが生じると接触面積の低下に伴う抵抗値の増大が懸念されるものの第 3 の多結晶シリコン層 3 の外周面側壁の上側面部 3 a b について第 3 のシリコンナイトライド膜 2 0 の上部を除去し、その上側面部 3 a b においても第 3 の多結晶シリコン層 3 およびチタン層 1 5 が接触するため、第 3 の多結晶シリコン層 3 の上面部 3 a a およびチタン層 1 5 間の接触面積 (接触面積 S 1 参照) が少なくなったとしても上側面部 3 a b でも接触する (接触面積 S 2 参照) ようになるため、接触面積の低下を抑制できるようになる。

#### 【 0 0 4 7 】

##### ( 第 2 の実施形態 )

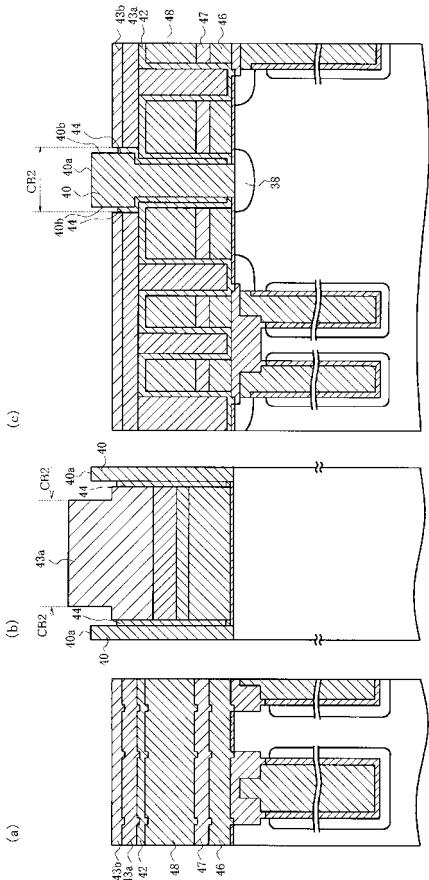

図 2 0 は、本発明の第 2 の実施形態の説明図を示すもので、上記実施形態と異なるところは製造工程にある。以下、上記実施形態と同一部分については同一符号を付して説明を省略し、以下異なる部分について説明する。

本実施形態においては、図 1 2 を使用して説明を行った製造工程終了後、前述実施形態に説明した工程に代えて次に示す製造工程を行う。

#### 【 0 0 4 8 】

すなわち、図 2 0 に示すように、第 3 の多結晶シリコン層 3 および第 3 のシリコン酸化膜 1 8 に対して高選択性を有するエッチング条件により第 3 の多結晶シリコン層 3 の上面部 3 a a から下方にかけて第 3 のシリコンナイトライド膜 2 0 の上部 (第 3 の多結晶シリコン層 3 の上側面部 3 a b) を除去する。そして、図示はしないが、前述実施形態と同様にビット線 B L 領域を除いて第 3 のシリコン酸化膜 1 8 の上部に第 4 のシリコン酸化膜 1 9 を形成した後、第 3 および第 4 のシリコン酸化膜 1 8 および 1 9 を第 3 の多結晶シリコン層 3 および第 3 のシリコンナイトライド膜 2 0 に対して高選択性を有するエッチング条件下において除去する。そして前述実施形態と同様にチタン層 1 5 およびタンゲステン層 1 6 を埋込み形成する。このような第 2 の実施形態においても、前述実施形態と略同様な作用効果を奏する。

#### 【 0 0 4 9 】

##### ( 第 3 の実施形態 )

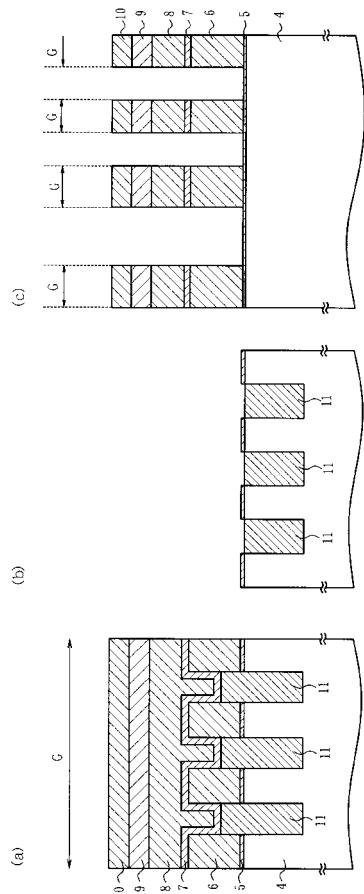

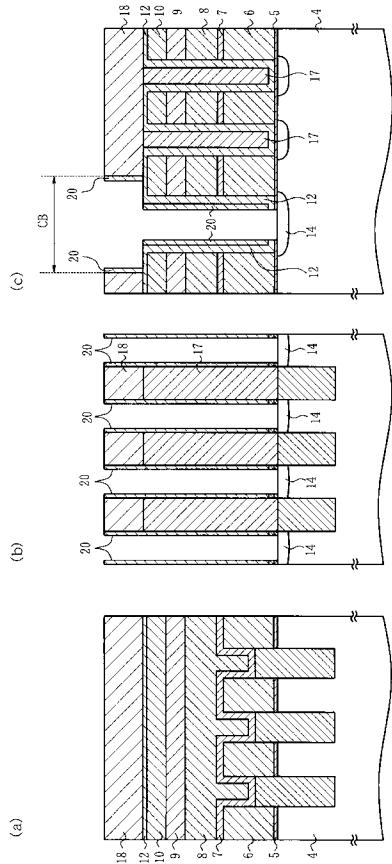

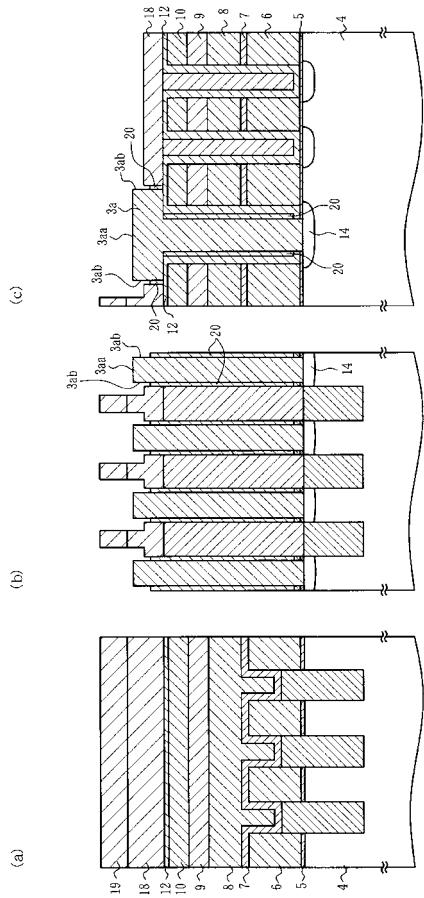

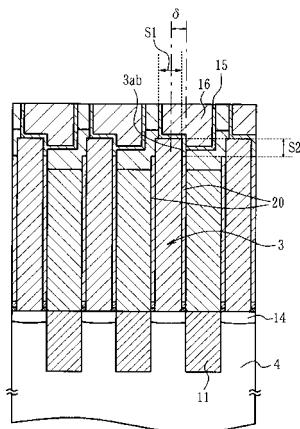

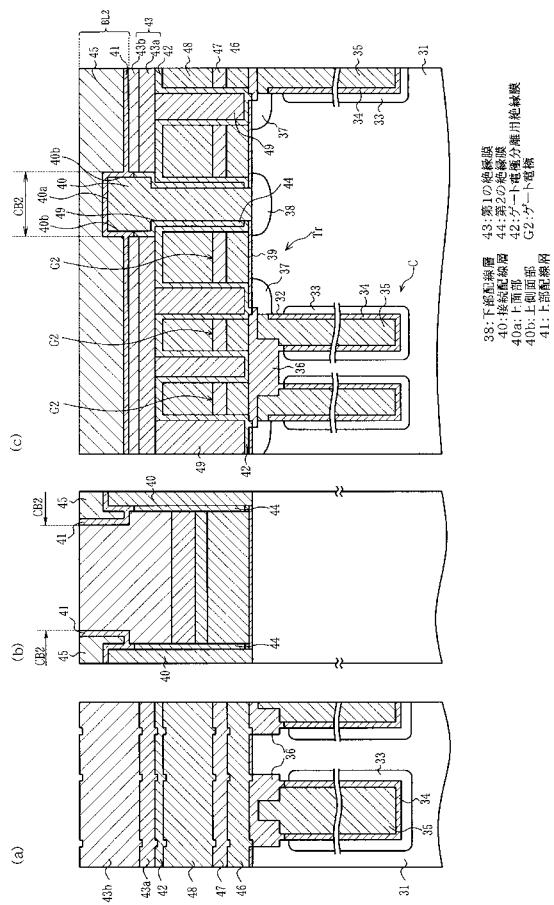

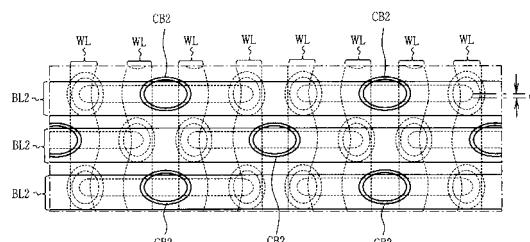

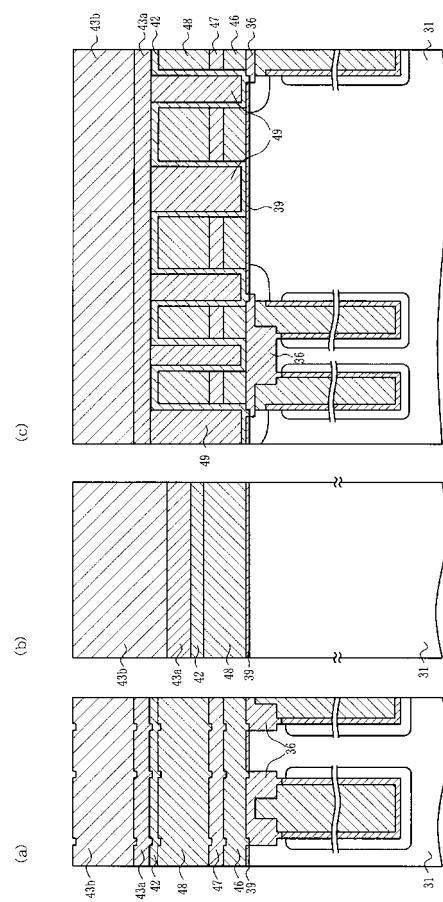

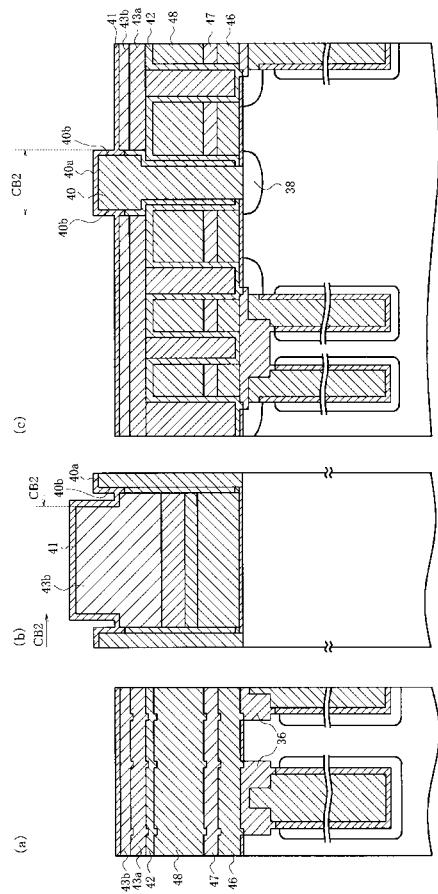

図 2 1 ~ 図 3 1 は、本発明の第 3 の実施形態の説明図を示すもので、上記各実施形態と異なるところは、トレンチ型の D R A M 半導体記憶装置に適用したところにある。

まず、図 2 1 および図 2 2 を参照しながら D R A M 半導体記憶装置 3 1 の機能的な構造について説明する。図 2 2 は、D R A M 半導体記憶装置の模式的な平面図を示しており、図 2 1 ( a ) は、この図 2 2 における D - D 線に沿う断面図を示しており、図 2 1 ( b )

10

20

30

40

50

は、図22におけるE-E線に沿う断面図を示しており、図21(c)は、図22におけるF-F線に沿う断面図を示している。

#### 【0050】

この図21において、半導体装置としてのDRAM半導体記憶装置30は、メモリセル領域においては、1メモリセルとして1のMOS型のセルトランジスタTrおよび1のトレンチキャパシタCが形成されており、これらのメモリセルが複数配列されている。シリコン半導体基板31には、深いトレンチ32(溝部)が形成されており、このトレンチ32の底部側に位置してトレンチキャパシタCが形成されている。尚、トレンチ4は、図22に示すように橿円形状に形成されている。

#### 【0051】

以下、トレンチキャパシタCの構成について概略的に説明する。トレンチ32の外周には、当該トレンチ32の底部側からある所定の高さまでプレート拡散層33が形成されている。このプレート拡散層33はトレンチキャパシタCのプレート電極として機能する。トレンチ32の内面で且つプレート拡散層33の上には、キャパシタ絶縁膜34が形成されている。このキャパシタ絶縁膜34は、SiN-SiO<sub>2</sub>膜またはAl<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub>膜、またはHfO<sub>2</sub>-SiO<sub>2</sub>膜等により形成されており、トレンチキャパシタCの両プレート電極分離用の絶縁膜として機能する。

#### 【0052】

トレンチ32の内面且つキャパシタ絶縁膜34の上には、多結晶シリコン層またはポリサイド材料による第1の導電層35が埋込み形成されている。この第1の導電層35は、トレンチキャパシタCのプレート電極として機能する。このようにしてトレンチキャパシタCは、第1の導電層35、キャパシタ絶縁膜34、プレート拡散層33により構成されている。

#### 【0053】

第1の導電層35の上部には、素子分離領域36(STI(Shallow Trench Isolation))が形成されている。図21に示すように、この素子分離領域36は、セルトランジスタTrが形成される側とは逆側に形成される層であり、トレンチキャパシタCと隣接した他のメモリセルとの間で電気的に絶縁分離するように形成されている。また、この素子分離領域36は、図21(c)に示すように、この素子分離領域36上を通過するように形成されたワード線WL(ゲート電極G2)とトレンチキャパシタCとを電気的に絶縁分離する機能を有しているものである。

#### 【0054】

セルトランジスタTrは、トレンチキャパシタCに対して隣接して配設されると共に電気的に接続するようにトレンチ32の所定方向側に形成されている。セルトランジスタTrは、ワード線WLとしても機能するゲート電極G2、n型の拡散層37および38(ソース/ドレイン拡散層)、並びにゲート絶縁膜として機能する第1のシリコン酸化膜39を備えている。一方の拡散層37には、トレンチキャパシタCを構成する第1の導電層38が接続されている。

#### 【0055】

また、他方の拡散層38(本発明の下部導電層に相当)の上部にはビット線BL2に電気的に接続するための第2の多結晶シリコン層40(ビット線コンタクト:本発明の接続配線層に相当)が埋込み形成されている。他方の拡散層38には、当該第2の多結晶シリコン層40を介して上層側のビット線BL2を構成するチタン層41が接触しており、この第2の多結晶シリコン層40を介して拡散層38とチタン層41とが電気的に接続されている。

#### 【0056】

また、ゲート電極G2を覆うようにゲート電極分離用絶縁膜としてゲート側壁絶縁膜42が形成されている。このゲート側壁絶縁膜42は、第1のシリコンナイトライド膜として形成されており、隣接するゲート電極G2間を絶縁分離するために設けられている膜である。

さらに、ピット線 B L 2 とメモリセルを電気的に絶縁分離するように層間絶縁膜 4 3 (本発明の第1の絶縁膜に相当)が形成されている。第2の導電層 4 0 の側壁外周面にはスペーサとして第2のシリコンナイトライド膜 4 4 (本発明の第2の絶縁膜に相当)が形成されている。この第2のシリコンナイトライド膜 4 4 は、チタン層 4 1 と第2の導電層 4 0 の上面部 4 0 a および上側面部 4 0 b において接触するようになっている。

#### 【0057】

また、チタン層 4 1 の上部にはタングステン層 4 5 が形成されている。これらチタン層 4 1 およびタングステン層 4 5 によりピット線 B L 2 が構成されている。このようにして 1 のメモリセルが構成されており、図 2 2 に示すように複数のメモリセルが密接するよう配設されている。尚、図 2 2 において、アクティブエリア A A は、メモリセルの活性領域を示している。

#### 【0058】

このような場合、図 2 2 ( a ) に示すように、ピット線 B L 2 (チタン層 4 1 およびタングステン層 4 5 ) が図中上下方向にマスク合わせずれが生じることなく形成される場合には、ピット線 B L 2 と隣接する第2の導電層 4 0 間の距離も長いため、その電気的相互作用も無視できるが、近年の設計ルールの縮小化に伴いその距離が短くなっているため、図 2 2 ( b ) に示すようにピット線 B L 2 の形成時にマスクの合わせずれ 2 が生じると、ピット線 B L 2 と隣接する第2の導電層 4 0 間の距離も短くなってしまうと共に、ピット線 B L 2 と第2の導電層 4 0 との接触面積も低下してしまう。本実施形態では、上面部 4 0 a だけでなく上側面部 4 0 b でもピット線 B L 2 と第2の導電層 4 0 とが接触するようになっているため、ピット線 B L 2 と第2の導電層 4 0 との接触面積の低下を抑制することができ、接触部分の抵抗を極力抑えることができるようになる。

#### 【0059】

##### < 製造方法 (プロセス) について >

以下、前述した機能的部分を形成する場合の実質的な層の形成方法について図 2 1 ないし図 3 1 を参照しながら説明する。本実施形態では、特にピット線 B L 2 (後述するチタン層 4 1 ) とコンタクトプラグ (後述する第2の多結晶シリコン層 4 0 ) とを接続する構成部分およびその周辺関連部分に特徴があるため、トレンチキャパシタ C やゲート電極 G 2 の形成方法については省略し、本実施形態の特徴部分に関連するシリコン半導体基板 3 1 の上層部分について、その説明を行う。

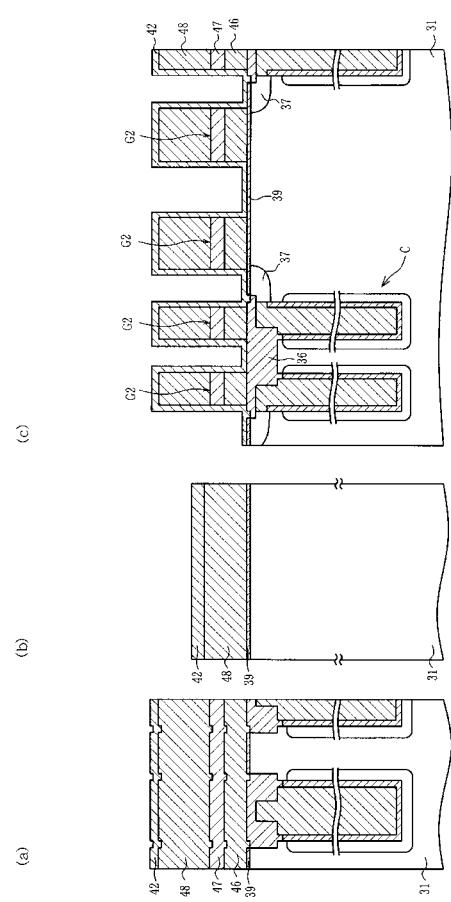

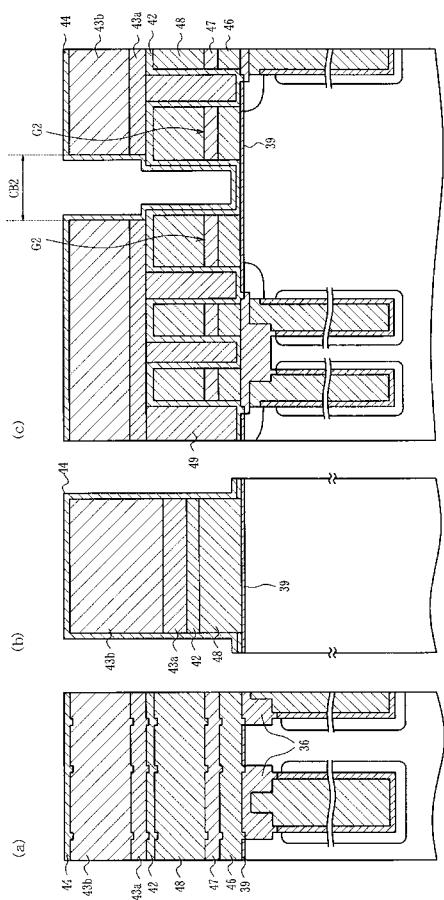

#### 【0060】

##### (1) 図 2 3 ないし図 2 5 に示す構造の形成方法について

図 2 3 に示すように、p 型のシリコン半導体基板 3 1 上に例えば 8 nm 膜厚のシリコン酸化膜をゲート絶縁膜 3 9 として形成すると共に、トレンチキャパシタ C や素子分離領域 3 6 を形成した後ゲート電極 G 2 を形成する。

このゲート電極 G 2 は次のように形成される。

#### 【0061】

図 2 4 に示すように、減圧 C V D 法により p 型の不純物がドープされた第1の多結晶シリコン層 4 6 をゲート絶縁膜 3 9 の上部に 100 nm 形成し、第1の多結晶シリコン層 4 6 の上部に対してタングステンシリサイド層 4 7 を 55 nm 形成する。タングステンシリサイド層 4 7 の上部に第3のシリコンナイトライド膜 4 8 を減圧 C V D 法により 200 nm 形成する。そして、フォトレジスト (図示せず) を塗布し、リソグラフィ技術により所定のレジストパターンに加工し、このレジストパターンをマスクとして第3のシリコンナイトライド膜 4 8 を R I E 法によりエッチングする。

#### 【0062】

すると、第1の多結晶シリコン層 4 6 およびタングステンシリサイド層 4 8 が分断され、これらの第1の多結晶シリコン層 4 6 およびタングステンシリサイド層 4 8 によりゲート電極 G 2 が構成されると共に、各ゲート電極 G 2 間の第3のシリコンナイトライド膜 4 8 が除去される。

その後、フォトレジストをアッティングにより剥離し、残存した第3のシリコンナイトラ

10

20

30

40

50

イド膜 4 8 をマスクとしてタングステンシリサイド層 4 7 , p 型の不純物がドープされた第 1 の多結晶シリコン層 4 6 を R I E 法により加工する。すると、各ゲート電極 G 2 間の第 1 の多結晶シリコン層 4 6 およびタングステンシリサイド層 4 7 が除去される。その後、1050 程度の R T O (Rapid Thermal Oxidation)処理を施した後、第 1 のシリコンナイトライド膜 4 2 を 40 nm 程度等方的に形成する。すると図 25 に示すように、各ゲート電極 G 2 間に第 1 のシリコンナイトライド膜 4 2 がゲート側壁絶縁膜として薄く形成されるようになる。

#### 【 0 0 6 3 】

( 2 ) 図 26 に示す構造の形成方法について

( 1 ) の形成工程後、各ゲート電極 G 2 間に第 4 のシリコン酸化膜 4 9 を埋込み形成する。第 1 のシリコンナイトライド膜 4 2 の上部に形成された第 4 のシリコン酸化膜 4 9 を第 1 および第 3 のシリコンナイトライド膜 4 2 および 4 8 をストップとして C M P (Chemical Mechanical Polish)法により平坦化する。

#### 【 0 0 6 4 】

その後、露出した第 1 もしくは第 3 のシリコンナイトライド膜 4 2 , 4 8 の上部および第 4 のシリコン酸化膜 4 9 の上部に、第 2 のシリコン酸化膜 4 3 a を例えれば 150 nm 形成する。その後、第 2 のシリコン酸化膜 4 3 a の上部に第 3 のシリコン酸化膜 4 3 b を 350 nm 形成する。すると、図 26 に示すように形成される。尚、これらの第 2 および第 3 シリコン酸化膜 4 3 a および 4 3 b が形成工程が終了すると層間絶縁膜 4 3 として機能するようになる。

#### 【 0 0 6 5 】

( 2 ) の形成工程後、第 3 のシリコン酸化膜 4 3 b の上部にフォトレジスト ( 図示せず ) を塗布し、リソグラフィ技術によりフォトレジストを所定のレジストパターンに加工する。その後、フォトレジストをマスクとして R I E 法により第 3 および第 2 のシリコン酸化膜 4 3 b および 4 3 a を加工 ( 除去 ) し、さらに、図 27 に示すように、ピット線コントラクト形成領域 C B 2 として形成される部分に対してセルフアラインコントラクト形成技術により第 4 のシリコン酸化膜 4 9 を除去すると共に、この部分に第 2 のシリコンナイトライド膜 4 4 を等方的に形成する。この第 2 のシリコンナイトライド膜 4 4 がスペーサとして機能するようになる。

#### 【 0 0 6 6 】

そして、ゲート電極 G 2 間の底部に形成された第 2 および第 1 のシリコンナイトライド膜 4 4 および 4 2 をドライエッチングする。すると、各ゲート電極 G 2 の側壁に第 2 のシリコンナイトライド膜 4 4 がスペーサとして残存するようになり孔部が形成される。そして、この孔部を通じて n 型の不純物をシリコン半導体基板 3 1 に拡散させることによりソース / ドレイン拡散層 3 8 を形成する。

#### 【 0 0 6 7 】

その後、第 2 のシリコンナイトライド膜 4 4 の内側に p 型の不純物がドープされた多結晶シリコンを埋込み形成することによりコントラクトプラグとして機能する第 2 の多結晶シリコン層 4 0 を埋込み形成する。そして、図 28 に示すように、C D E (Chemical Dry Etching)法により第 2 の多結晶シリコン層 4 0 の上部を除去することにより高さを調整する。さらに、970 の窒素性雰囲気内で加熱処理を行いドーパントを活性化させる。

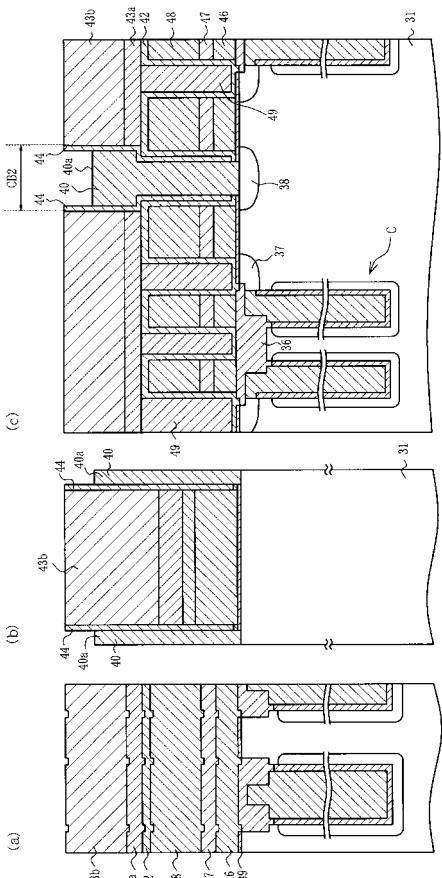

#### 【 0 0 6 8 】

そして、図 29 に示すように、多結晶シリコンおよびシリコン窒化膜に対して選択性の高いエッチング条件において、第 2 の多結晶シリコン層 4 0 の上面部 4 0 a よりも下方まで第 2 のシリコン酸化膜 4 3 b をエッチングにより除去する。すると、図 29 に示すように、第 2 のシリコンナイトライド膜 4 4 も同時に第 2 の多結晶シリコン層 4 0 の上面部 4 0 a まで除去されるようになる。

#### 【 0 0 6 9 】

そして、図 30 に示すように、第 2 の多結晶シリコン層 4 0 の外周面の上部側壁に形成された第 2 のシリコンナイトライド膜 4 4 を 150 のリン酸処理等のウェットエッチ

10

20

30

40

50

グにより除去する。このとき、第2の多結晶シリコン層40の上面部40aよりも下方まで第2のシリコンナイトライド膜44をシリコン酸化膜および多結晶シリコンに対して選択性の高いエッティング条件下におけるウェットエッティングにより除去し、第2の多結晶シリコン層40の側壁外周面の上側面部40bを露出させる。

#### 【0070】

このとき、図30に示すように、第2のシリコンナイトライド膜44の上部が第3のシリコン酸化膜43bの上面より下方に位置するように第2のシリコンナイトライド膜44を除去することが望ましい。尚、このとき、第2のシリコンナイトライド膜44を除去するときにはドライエッティングにより除去しても良い。

さらに、図31に示すように、第2および第3のシリコン酸化膜43aおよび43bの上部並びに第2のシリコンナイトライド膜44の上部にチタン膜41をPVD法により例えば45nm程度等方的に堆積する。すると、第2の多結晶シリコン層40の上面部40aおよび上側面部40bに接触するようにチタン膜41が形成されるようになる。さらに、550, 90分の水素を含む窒素性雰囲気内で加熱する。

#### 【0071】

続いて、図21に示すように、このチタン層41の上部にPVD法によりタングステン層45を例えば400nm程度堆積し、図21(b)に示すように、タングステン膜45およびチタン膜41を平坦化し、水素を含む窒素性雰囲気において400で30分間加熱する。このようにしてビット線コンタクト(コンタクトプラグ)としての第2の多結晶シリコン層40とビット線BL2との接触部分が構成される。

#### 【0072】

このような第3の実施形態においても、ビット線コンタクトとしての第2の多結晶シリコン層40とビット線BL2とが第2の多結晶シリコン層40の上面部40aのみに留まらず第2の多結晶シリコン層40の上側面部40bにおいても接触するため、第1の実施形態と略同様の作用効果を奏すると共に、DRAM半導体記憶装置30にも適用できるようになる。

#### 【0073】

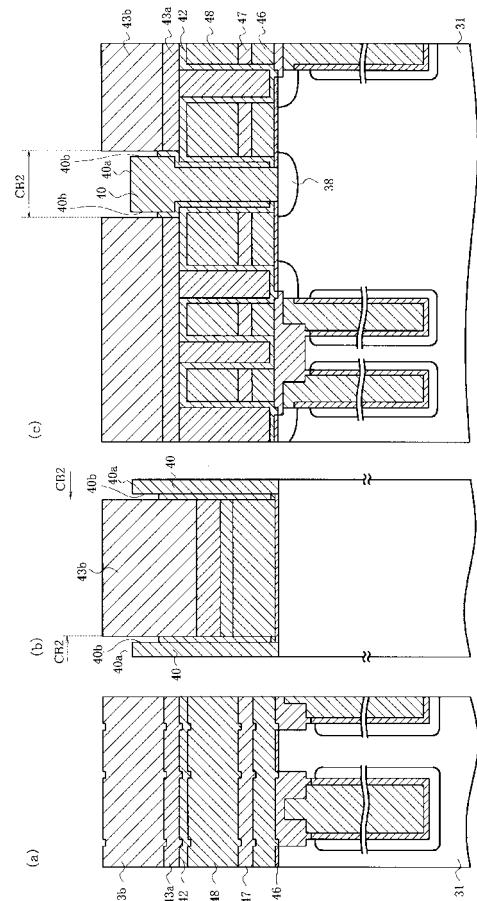

##### (第4の実施形態)

図32は、本発明の第4の実施形態の説明図を示すもので、第3の実施形態と異なるところはその製造方法にある。上記実施形態と同一部分には同一符号を付して説明を省略し、以下異なる製造方法について説明する。

図28に示す構造を形成した後、シリコン半導体基板31の拡散層38の上面に位置する第2および第1のシリコンナイトライド膜44および42およびシリコン酸化膜39を除去し、第2の多結晶シリコン層40を埋込み形成する。そして、この第2の多結晶シリコン層40の上部を高さ調整した後、第2の多結晶シリコン層40の側壁外周面の上側面部40bに形成された第2のシリコンナイトライド膜44を除去する。この場合、シリコン酸化膜および多結晶シリコンに対して選択性の高いエッティング条件下においてエッティングすることにより第2のシリコンナイトライド膜44を除去し、第2の多結晶シリコン層40の上面部40aよりも下方に第2のシリコンナイトライド膜44の上部が位置するように第2のシリコンナイトライド膜44を除去し、第2の多結晶シリコン層40の上側面部40bを露出させる。

#### 【0074】

その後、図21に示すように、多結晶シリコンおよびシリコンナイトライドに対して選択性の高いエッティング条件下において第3のシリコン酸化膜43bをエッティングすることにより、第3のシリコン酸化膜43bの上部を第2の多結晶シリコン層40の上面部40aの下方で、且つ、第2のシリコンナイトライド膜44の上方まで除去する。

そして、前述実施形態と同様に第3のシリコン酸化膜43bの上部および第2の多結晶シリコン層40の上面部40aおよび上側面部40bにチタン層41を形成し、その上部にタングステン層45を形成することにより前述実施形態と同様の構成を形成することができるようになる。このような第4の実施形態においても、第3の実施形態と略同様の作

10

20

30

40

50

用効果を奏する。

【図面の簡単な説明】

【0075】

【図1】本発明の第1の実施形態の構成を模式的に示す要部の断面図((a)図3のA-A線に沿う断面図、(b)図3のB-B線に沿う断面図、(c)図3のC-C線に沿う断面図)

【図2】回路構成を概略的に示す図

【図3】要部の平面図

【図4】一製造工程を模式的に示す図(その1)

10

【図5】一製造工程を模式的に示す図(その2)

【図6】一製造工程を模式的に示す図(その3)

【図7】一製造工程を模式的に示す図(その4)

【図8】一製造工程を模式的に示す図(その5)

【図9】一製造工程を模式的に示す図(その6)

【図10】一製造工程を模式的に示す図(その7)

【図11】一製造工程を模式的に示す図(その8)

【図12】一製造工程を模式的に示す図(その9)

【図13】一製造工程を模式的に示す図(その10)

【図14】一製造工程を模式的に示す図(その11)

20

【図15】一製造工程を模式的に示す図(その12)

【図16】一製造工程を模式的に示す図(その13)

【図17】(a)ビット線とビット線コンタクトとの接続形態を模式的に示す平面図、(b)ビット線の形成時にマスクずれが生じたときの一例を模式的に示す平面図

【図18】ビット線の形成時にマスクずれが生じたときの一例を模式的に示す断面図

【図19】ビット線の形成時にマスクずれが生じたときの基本構成例を模式的に示す断面図

【図20】本発明の第2の実施形態の一製造工程を模式的に示す図

【図21】本発明の第3の実施形態を模式的に示す要部の断面図((a)図22(a)のD-D線に沿う断面図、(b)図22(a)のE-E線に沿う断面図、(c)図22(a)のF-F線に沿う断面図)

30

【図22】要部を模式的に示す平面図((a)はビット線のマスクずれが生じない場合、(b)はビット線のマスクずれが生じた場合)

【図23】一製造工程を模式的に示す図(その1)

【図24】一製造工程を模式的に示す図(その2)

【図25】一製造工程を模式的に示す図(その3)

【図26】一製造工程を模式的に示す図(その4)

【図27】一製造工程を模式的に示す図(その5)

【図28】一製造工程を模式的に示す図(その6)

【図29】一製造工程を模式的に示す図(その7)

【図30】一製造工程を模式的に示す図(その8)

40

【図31】一製造工程を模式的に示す図(その9)

【図32】本発明の第4の実施形態の一製造工程を模式的に示す図

【符号の説明】

【0076】

図面中、2およびBLはビット線(上部導電層)、3は接続配線層、3aaは上面部、3abは上側面部、6は第1の多結晶シリコン層、8は第2の多結晶シリコン層、10は第1のシリコンナイトライド膜、11は第2のシリコン酸化膜(素子分離領域、STI)、12は第2のシリコンナイトライド膜(第2の絶縁膜、ゲート電極分離用絶縁膜)、13は孔部、14は拡散層(下部導電層)、18はシリコン酸化膜(第1の絶縁膜)、20はシリコンナイトライド膜(第2の絶縁膜)、Arはメモリセルアレイ、BLはビット線

50

、 C B および C B 2 はビット線コンタクト形成領域、 G はゲート電極形成領域、 F G はフローティングゲート電極（ゲート電極）、 G C はコントロールゲート電極（ゲート電極）、 S はソース線、 S G は選択ゲート電極（ゲート電極）、 T r s は選択ゲートトランジスタ、 T r n はメモリセルトランジスタを示す。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【 図 1 9 】

【 図 2 0 】

3

(b)

(a)

【 図 2 1 】

【図22】

(b)

【図23】

【図25】

【図24】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

---

フロントページの続き(51)Int.Cl.<sup>7</sup>H 01 L 29/788

H 01 L 29/792

F I

H 01 L 29/78

3 7 1

テーマコード(参考)

(72)発明者 原 徹

愛知県名古屋市中区栄一丁目16番6号 名古屋三蔵東邦生命ビル6階 中部東芝エンジニアリング株式会社内

F ターム(参考) 5F033 HH04 HH18 HH19 HH28 JJ04 KK01 LL04 MM12 MM30 NN15

NN31 NN37 NN40 PP09 PP14 PP15 QQ08 QQ09 QQ10 QQ11

QQ13 QQ16 QQ19 QQ28 QQ31 QQ48 QQ58 QQ73 QQ74 QQ75

QQ76 QQ82 RR03 RR04 RR06 SS11 SS13 SS15 TT02 TT07

TT08 VV06 VV10 VV16 XX01 XX09 XX15

5F083 AD17 AD60 EP02 EP23 EP33 EP34 EP55 EP60 EP76 ER22

GA02 GA27 JA03 JA04 JA35 JA39 KA05 MA03 MA06 MA20

NA01 NA06 PR05 PR13 PR18 PR40

5F101 BA02 BA29 BB05 BB08 BD02 BD22 BD34 BD35 BH03 BH17