(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2008-306037

(P2008-306037A)

(43) 公開日 平成20年12月18日(2008.12.18)

(51) Int.Cl.

H01L 25/00 (2006.01)

F 1

H01L 25/00

テーマコード(参考)

B

審査請求 未請求 請求項の数 9 O L (全 13 頁)

(21) 出願番号

特願2007-152604 (P2007-152604)

(22) 出願日

平成19年6月8日 (2007.6.8)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100107836

弁理士 西 和哉

(74) 代理人 100064908

弁理士 志賀 正武

(74) 代理人 100101465

弁理士 青山 正和

(72) 発明者 西山 佳秀

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(54) 【発明の名称】半導体モジュール及びその製造方法

## (57) 【要約】

【課題】受動部品を有する場合であっても小型化が可能な半導体モジュール及びその製造方法を提供する。

【解決手段】本発明の半導体モジュール1は、第1のインターポーラ2と、能動面3Aと裏面3Bとを有し、裏面3Bが第1のインターポーラ2と対向して配置された半導体チップ3と、半導体チップ3の能動面3Aに対向して半導体チップ3と電気的に接続し、且つ第1のインターポーラと電気的に接続する第2のインターポーラ40と、第2のインターポーラ40の少なくとも上面40Aに実装された受動部品4とを備えている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

第1のインターポーザと、

能動面と裏面とを有し、前記裏面が前記第1のインターポーザと対向して配置された半導体チップと、

前記半導体チップの前記能動面に対向して該半導体チップと電気的に接続し、且つ前記第1のインターポーザと電気的に接続する第2のインターポーザと、

前記第2のインターポーザの、少なくとも前記半導体チップと反対側の第1の面に実装された第1の受動部品と、を備えたことを特徴とする半導体モジュール。

**【請求項 2】**

前記第2のインターポーザは、前記半導体チップの前記能動面と平行な平面内における大きさが前記半導体チップよりも大きく、

前記第2のインターポーザの前記半導体チップと対向する第2の面のうち、前記半導体チップが存在する第1の領域以外の第2の領域にも、前記第1の受動部品が実装されていることを特徴とする請求項1に記載の半導体モジュール。

**【請求項 3】**

前記第2のインターポーザは、前記半導体チップの前記能動面と平行な平面内における大きさが前記半導体チップよりも大きく、

前記第1のインターポーザの前記半導体チップに対向する前記第1の面のうち、前記第2のインターポーザの前記第2の領域に対向する領域に第2の受動部品が実装されていることを特徴とする請求項1または2記載の半導体モジュール。

**【請求項 4】**

前記第2のインターポーザは、

前記第1の受動部品と電気的に接続するための第1の端子と、

前記半導体チップと電気的に接続するための第2の端子と、

前記第1のインターポーザと電気的に接続するための第3の端子と、を備えた多層配線基板からなることを特徴とする請求項1乃至3のいずれか一項に記載の半導体モジュール。

**【請求項 5】**

前記第2のインターポーザの前記第1の端子、前記第2の端子、及び前記第3の端子が、金めっきされていることを特徴とする請求項4記載の半導体モジュール。

**【請求項 6】**

前記半導体チップは、前記第2のインターポーザの前記第2の端子と接続する端子を備え、

当該端子が金バンプまたはハンダバンプからなることを特徴とする請求項4または5記載の半導体モジュール。

**【請求項 7】**

前記第1のインターポーザは、前記第2のインターポーザの前記第3の端子と電気的に接続する端子を備え、

当該端子と前記第3の端子とがワイヤーボンディングによって接続されていることを特徴とする請求項4または5記載の半導体モジュール。

**【請求項 8】**

前記半導体チップは、前記第2のインターポーザにフリップチップ実装されていることを特徴とする請求項1乃至7のいずれか一項に記載の半導体モジュール。

**【請求項 9】**

能動面と裏面とを有する半導体チップを用意し、

第1のインターポーザに、前記半導体チップを、前記裏面が前記第1のインターポーザと対向するようにして実装する工程と、

前記半導体チップの前記能動面側に、前記第2のインターポーザを電気的に接続するようにして実装する工程と、

10

20

30

40

50

前記第2のインターポーザの少なくとも前記半導体チップと反対側の第1の面に、受動部品を接続する工程と、

前記第1のインターポーザと前記第2のインターポーザとを電気的に接続する工程と、

を含むことを特徴とする半導体モジュールの製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体モジュール及びその製造方法に関するものである。

【背景技術】

【0002】

電子機器の小型化及び高性能化等を目的として、複数の半導体チップ及び受動部品等をインターポーザ上に実装することによってモジュールを形成する、MCM (Multi Chip Module)、SiP (System in a Package) 等と呼ばれる半導体モジュールが案出されている。下記特許文献には、半導体モジュールに関する技術の一例が開示されている。

【特許文献1】特開平5-206379号公報

【特許文献2】特開平11-220089号公報

【特許文献3】特開2002-359341号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

受動部品を有する半導体モジュールにおいて、インターポーザ上に半導体チップと受動部品とを並べて配置する場合、受動部品を配置するための領域を確保しなければならず、半導体モジュールの小型化、特に、インターポーザの表面と平行な面内における半導体モジュールの小型化が困難となる。

【0004】

また、インターポーザ上に半導体チップと受動部品とを並べて配置するために、製造工程がインターポーザと半導体チップ及び受動部品のそれぞれとを接続する工程を有する場合、その工程が複雑又は煩雑になる可能性がある。

【0005】

本発明はこのような事情に鑑みてなされたものであって、受動部品を有する場合であっても小型化が可能な半導体モジュール及びその製造方法を提供することを目的としている。

【課題を解決するための手段】

【0006】

本発明の半導体モジュールは、上記課題を解決するために、第1のインターポーザと、能動面と裏面とを有し、裏面が第1のインターポーザと対向して配置された半導体チップと、半導体チップの能動面に対向して該半導体チップと電気的に接続し、且つ第1のインターポーザと電気的に接続する第2のインターポーザと、第2のインターポーザの、少なくとも半導体チップと反対側の第1の面に実装された第1の受動部品と、を備えたことを特徴とする。

【0007】

本発明の半導体モジュールによれば、半導体チップをその裏面を対向させて第1のインターポーザに実装するとともに、半導体チップの能動面と対向させて第2のインターポーザを配置し、少なくともその上面（半導体チップと反対側の第1の面）に受動部品を搭載してなるので、半導体モジュールの小型化、特に第1、第2のインターポーザの表面と平行な面内における半導体モジュールの小型化を実現することができる。また、本発明によれば、半導体モジュールを製造するときの工程の複雑化等を抑制できる。

【0008】

また、第2のインターポーザは、半導体チップの能動面と平行な平面内における大きさが半導体チップよりも大きく、第2のインターポーザの半導体チップと対向する第2の面

10

20

30

40

50

のうち、半導体チップが存在する第1の領域以外の第2の領域にも、第1の受動部品が実装されていることが好ましい。

このような構成によれば、第2のインターポーラの半導体チップと対向する第2の面のうち、半導体チップが接続された第1の領域以外の第2の領域を有効に利用することができる。すなわち、このように第2のインターポーラの、半導体チップから底状に張り出した領域にも第1の受動部品を備えることで、第2のインターポーラの両面を有効に利用することができる。

#### 【0009】

また、第2のインターポーラは、半導体チップの能動面と平行な平面内における大きさが半導体チップよりも大きく、第1のインターポーラの半導体チップに対向する第1の面のうち、第2のインターポーラの第2の領域に対向する領域に第2の受動部品が実装されていることが好ましい。

このような構成によれば、第1のインターポーラの第1の面のうち、半導体チップが接続される領域以外の領域を有効に利用することができる。

#### 【0010】

また、第2のインターポーラは、第1の受動部品と電気的に接続するための第1の端子と、半導体チップと電気的に接続するための第2の端子と、第1のインターポーラと電気的に接続するための第3の端子と、を備えた多層配線基板からなることが好ましい。

このような構成によれば、第2のインターポーラに各端子間の接続配線を設けることにより、モジュール全体の高集積化が可能になる。

#### 【0011】

また、第2のインターポーラの第1の端子、第2の端子、及び第3の端子が、金めっきされていることが好ましい。

このような構成によれば、半導体チップと第2のインターポーラとの電気的接続を良好にできるとともに、第2のインターポーラと受動部品との電気的接続を良好にすることができます。

#### 【0012】

また、半導体チップは、第2のインターポーラの第2の端子と接続する端子を備え、当該端子が金パンプまたはハンダパンプからなることが好ましい。

このような構成によれば、半導体チップを第1のインターポーラ上にフリップチップ実装することができ、これにより、半導体チップの能動面と第1のインターポーラとを良好に接続することができる。

#### 【0013】

また、第1のインターポーラは、第2のインターポーラの第3の端子と電気的に接続する端子を備え、当該端子と第3の端子とがワイヤーボンディングによって接続されていることが好ましい。

このような構成によれば、第1のインターポーラと第2のインターポーラとを、ワイヤーを介して電気的に良好に接続することができる。

#### 【0014】

また、半導体チップは、第2のインターポーラにフリップチップ実装されていることが好ましい。

このような方法によれば、半導体チップの能動面と第2のインターポーラとを良好に接続することができる。

#### 【0015】

本発明の半導体モジュールの製造方法によれば、能動面と裏面とを有する半導体チップを用意し、第1のインターポーラに、半導体チップをその裏面が第1のインターポーラと対向するようにして実装する工程と、半導体チップの能動面側に、第2のインターポーラを電気的に接続するようにして実装する工程と、第2のインターポーラの少なくとも半導体チップと反対側の第1の面に、受動部品を接続する工程と、第1のインターポーラと第2のインターポーラとを電気的に接続する工程と、を含むことを特徴とする。

10

20

30

40

50

本発明の半導体モジュールの製造方法によれば、半導体チップをその裏面を対向させるようにして第1のインターポーラーを実装するとともに、半導体チップの能動面と対向させるようにして第2のインターポーラーを配置し、少なくともその上面（半導体チップと反対側の第1の面）に受動部品を接続するようにしたので、半導体モジュールの小型化、特に第1、第2のインターポーラーの表面と平行な面内における半導体モジュールの小型化を実現することができる。また、本発明によれば工程の複雑化等を抑制できる。なお、半導体チップを第1のインターポーラー及び第2のインターポーラーのどちらに先に実装するかは適宜選択するものとする。

【発明を実施するための最良の形態】

【0016】

<半導体モジュール>

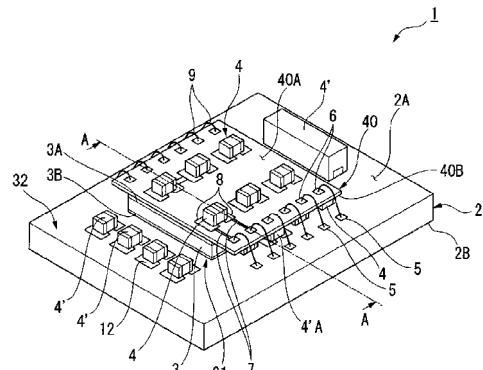

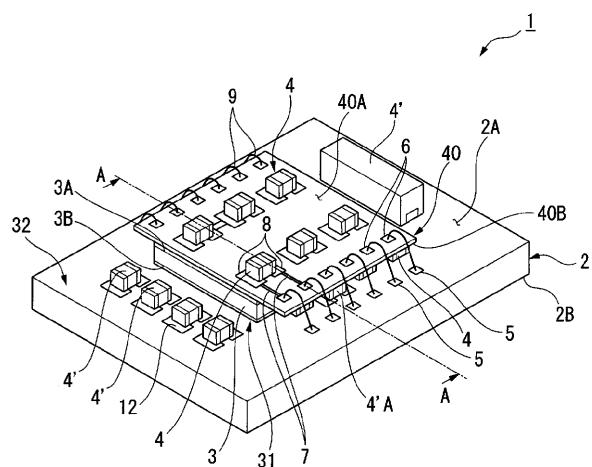

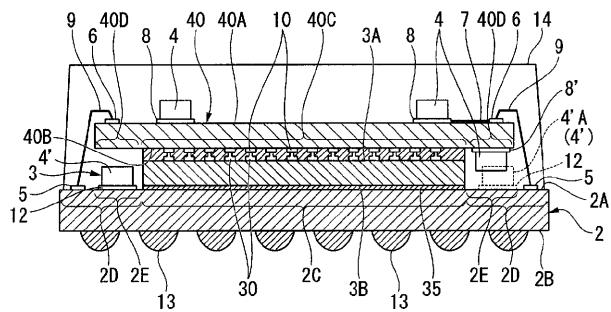

本発明の半導体モジュールの一実施形態について説明する。図1は、本実施形態に係る半導体モジュール1を模式的に示す斜視図、図2は、断面図であって、図1のA-A線断面矢視図に相当する。また、図3は、本実施形態に係る半導体モジュール1の一部を拡大した平面図である。なお、以下の説明に用いる各図面では、各部材を認識可能な大きさとするため、各部材の縮尺を適宜変更している。

【0017】

図1、図2及び図3において、半導体モジュール1は、第1のインターポーラー2と、能動面3Aと裏面3Bとを有し、裏面3Bが第1のインターポーラー2と対向するように配置された半導体チップ3と、半導体チップ3の能動面3Aと対向するように配置された第2のインターポーラー40と、第2のインターポーラー40に接続された受動部品4とを備えている。

【0018】

第1のインターポーラー2は、半導体チップ3の裏面3Bに対向する上面2A（第1の面）と、その上面2Aとは反対側の下面2Bとを有している。

【0019】

第2のインターポーラー40は、半導体チップ3の能動面3Aに対向する下面40B（第2の面）と、その下面40Bとは反対側の上面40A（第1の面）とを有している。

【0020】

半導体チップ3は、第1のインターポーラー2の上面2Aに実装され、半導体チップ3の裏面3Bと第1のインターポーラー2の上面2Aとが、例えば樹脂や無鉛はんだ等で接着されている。また、半導体チップ3の能動面3Aと第2のインターポーラー40の下面40Bとが電気的に接続されている。

【0021】

第1のインターポーラー2は、例えばエポキシ樹脂、ポリイミド樹脂等の合成樹脂（有機材料）、セラミックス、及びガラス等の絶縁性の材料によって形成された基板と、その基板に形成された導電性の配線パターンとを備えている。

【0022】

第2のインターポーラー40も、例えばエポキシ樹脂、ポリイミド樹脂等の合成樹脂（有機材料）、セラミックス、及びガラス等の絶縁性の材料によって形成された基板と、その基板に形成された導電性の配線パターンとを備えている。この第2のインターポーラー40としては、下面40B及び上面40Aのそれぞれに電極（端子）を有し、さらに中間部にも配線パターンを有した多層配線基板が用いられている。

【0023】

半導体チップ3は、シリコン基板を含み、トランジスタ、メモリ素子等を含む電子回路（集積回路）を有する。半導体チップ3の能動面3Aには、少なくとも集積回路が形成されている。

【0024】

受動部品4は、抵抗、コンデンサ、及びインダクタ等を含む。本実施形態においては、半導体モジュール1が複数の受動部品4（4'）を備えている。以下の説明においては、

10

20

30

40

50

便宜上、第1のインターポーザ2に実装される受動部品4（第1の受動部品）と、第2インターポーザ40に実装される受動部品4'（第2の受動部品）とで符号を区別しているが、これら第1のインターポーザ2及び第2のインターポーザ40に実装される受動部品に違いがあるのではない。

【0025】

本実施形態においては、半導体チップ3の能動面3Aと平行な平面内における半導体チップ3の大きさは、第2のインターポーザ40よりも小さく、半導体チップ3の能動面3Aは、第2のインターポーザ40の下面40Bの一部の領域40Cに接続されている。以下の説明において、第2のインターポーザ40の下面40Bのうち、半導体チップ3が接続される領域40Cを適宜、第1領域40C、と称する。

10

【0026】

本実施形態においては、第2のインターポーザ40の一部が、半導体チップ3の外側に庇状に張り出している。すなわち、第2のインターポーザ40の下面40Bのうち、半導体チップ3と接続された第1領域40C以外の第2領域40Dが、半導体チップ3の外側に張り出している。以下の説明においては、第2のインターポーザ40の下面40Bうち、半導体チップ3の外側に張り出した第2領域40Dを適宜、オーバーハング領域40D、と称する。

【0027】

そして、複数の受動部品4の少なくとも一つは、第2のインターポーザ40の下面40Bのうち第1領域40C以外の第2領域（オーバーハング領域）22に接続されている。この第2領域40Dには、図2に示すように、受動部品4と電気的に接続可能な端子8'が所定位置に形成されている。端子8'は、多層配線基板からなる第2のインターポーザ40の下面40Bあるいは内部の中間部に引き廻された配線（不図示）を介して半導体チップ3と電気的に接続されている。また、これにより、端子8'と電気的に接続された受動部品4が半導体チップ3と電気的に接続されている。

20

【0028】

また、複数の受動部品4の少なくとも一つは、第2のインターポーザ40の半導体チップ3が接続される下面40Bと反対側の上面40Aに接続されている。すなわち、本実施形態においては、受動部品4が、第2のインターポーザ40の下面40Bの第2領域（オーバーハング領域）22、及び上面40Aのそれぞれに接続されている。さらに、本実施形態においては、下面40B及び上面40Aのそれぞれに、受動部品4が複数配置されている。

30

【0029】

第1のインターポーザ2の上面2Aには、端子5が形成されている。第2のインターポーザ40の上面40Aには、第1のインターポーザ2に形成された端子5と電気的に接続可能な端子6（第3の端子）が形成されている。また、第2のインターポーザ40の上面40Aには、端子6と受動部品4とを電気的に接続する配線7が形成されている。

【0030】

また、第2のインターポーザ40の上面40Aには、受動部品4と電気的に接続する端子8（第1の端子）が形成されている。そして、配線7は、端子6と端子8とを接続するように形成されている。端子6と端子8とが配線7を介して電気的に接続されることによって、端子8と電気的に接続された受動部品4と端子6とが配線7を介して電気的に接続される。

40

【0031】

端子5、端子6、端子8、及び端子8'のそれぞれは電極パッド（ランド）である。端子5、端子6、端子8、及び端子8'のそれぞれの表面は、例えは金（Au）によってメッキされている。以下の説明においては、端子5を適宜、電極パッド5、と称し、端子6を適宜、電極パッド6、と称し、端子8を適宜、電極パッド8、と称し、端子8'を、電極パッド8'、と称する。

【0032】

50

電極パッド 8 は、複数の受動部品 4 のそれぞれに対応するように、第 2 のインターポーナ 40 の上面 40A において複数形成されている。また、本実施形態においては、電極パッド 8 は、1 つの受動部品 4 に対して少なくとも 2 つ形成されている。図 1 において、受動部品 4 は、第 2 のインターポーナ 40 の上面 40A に 6 つ配置されており、電極パッド 8 は、1 つの受動部品 4 に対して 2 つずつ形成され、全部で 12箇所に形成されている。

なお、電極パッド 8' においても、下面 40B 側に接続される受動部品 4 に対応するように形成されている。

#### 【0033】

電極パッド 6 は、複数の電極パッド 8 のそれぞれに対応するように、第 2 のインターポーナ 40 の上面 40A において複数形成されている。本実施形態においては、電極パッド 6 は、全部で 12箇所に形成されており、上面 40A の対向する二辺に沿って並ぶように形成されている。

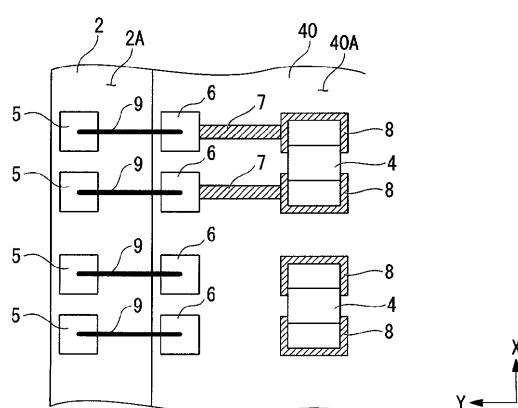

10

#### 【0034】

配線 7 は、所定の電極パッド 6 及び電極パッド 8 に対応して第 2 のインターポーナ 40 の上面 40A において形成されている。配線 7 は、所定の電極パッド 6 と所定の電極パッド 8 とを接続するように形成されている。また、配線 7 は、所定の受動部品 4 同士を接続すべく、所定の電極パッド 8 間を繋ぐように形成されている。

#### 【0035】

本実施形態においては、図 1, 2 において、半導体チップ 3 は、第 1 のインターポーナ 2 の上面 2A に対して裏面 3B 側を対向させた状態でダイボンディング実装されている。半導体チップ 3 の裏面 3B と第 1 のインターポーナ 2 の上面 2A とは、ダイボンディングするための接着剤 35 によって接続されている。ダイボンディングするための接着剤（ダイボンディングペースト）35 としては、例えば樹脂や無鉛はんだ等を用いることができる。

20

#### 【0036】

また、第 2 のインターポーナ 40 には、半導体チップ 3 がフリップチップ実装されている。半導体チップ 3 の能動面 3A には、金及び無鉛はんだの少なくとも一方を含むバンプ 30 が形成されている。また、第 2 のインターポーナ 40 の下面 40B には、半導体チップ 3 のバンプ 30 と電気的に接続可能な接続端子 10（第 2 の端子）が形成されている。そして、半導体チップ 3 が第 2 のインターポーナ 40 に対してフリップチップ実装されることによって、第 2 のインターポーナ 40 の下面 40B と半導体チップ 3 の能動面 3A とが電気的に接続される。本実施形態では、フリップチップ実装において、バンプ 30 と接続端子 10 とを位置合わせし、荷重を加えつつ所定の方向に振動させ、その摩擦熱によってバンプ 30 と接続端子 10 とを機械的、電気的に接続する方法（超音波接合）が用いられる。

30

#### 【0037】

第 2 のインターポーナ 40 を半導体チップ 3 上に実装する際の接合材としては、異方性導電フィルム（A C F : Anisotropic Conductive Film）、異方性導電ペースト（A C P : Anisotropic Conductive Paste）、非導電性フィルム（N C F : Non Conductive Film）、及び非導電性ペースト（N C P : Non Conductive Paste）の少なくとも一つを用いることができる。また、実装する際、加熱しつつ加圧するようにしてもよいし、超音波を作用させながら実装してもよい。なお、接合材を用いない場合には、半導体チップ 3 上に第 2 のインターポーナ 40 を実装した後、半導体チップ 3 と第 2 のインターポーナ 40 との間にアンダーフィル材を充填してもよい。

40

#### 【0038】

また、本実施形態では、第 2 のインターポーナ 40 が多層配線基板であることから、上記電極パッド 6, 8 と半導体チップ 3 とを電気的に接続するための配線（不図示）が、第 2 のインターポーナ 40 の上面 40A や下面 40B、あるいは中間部に引き廻されている。

#### 【0039】

50

そして、第1のインターポーザ2の上面2Aに形成された電極パッド5と、第2のインターポーザ40の上面40Aに形成された電極パッド6とは、ワイヤーボンディングによって接続されている。ワイヤーボンディングするためのワイヤー9は、例えば、金(Au)、アルミニウム(Al)によって形成可能である。

【0040】

また、半導体チップ3は、第1のインターポーザ2の上面2Aの一部の領域2Cに実装されている。以下の説明において、第1のインターポーザ2の上面2Aのうち、半導体チップ3が実装される領域2Cを適宜、第3領域2C、と称する。

【0041】

本実施形態においては、第1のインターポーザ2の上面2Aのうち半導体チップ3が実装された第3領域2C以外の第4領域2Dにも、受動部品4'が実装されている。受動部品4'は、第2のインターポーザ2の上面2Aに形成された第6電極パッド(第6の端子)12と電気的に接続される。本実施形態においては、受動部品4'及びその受動部品4'に接続される電極パッド12の少なくとも一部は、第3領域2Cに実装された半導体チップ3を囲むように複数設けられている。

【0042】

ここで、受動部品4'が接続される第1のインターポーザ2の上面2Aの第4領域2Dは、第2のインターポーザ40の下面40Bのうち第1領域40C以外の第2領域(オーバーハング領域)22と対向する領域2Eを含む。すなわち、第1のインターポーザ2の上面2Aに接続される受動部品4'の一つは、上面2Aにおいて、第2のインターポーザ2のオーバーハング領域40Dと対向する領域2E(オーバーハング領域40Dの下側の領域)に配置される(図1、図2の符号4' A参照)。

【0043】

また、上述のように、受動部品4'の一つは、第2のインターポーザ40のオーバーハング領域40Dにも接続されている。すなわち、本実施形態においては、複数の受動部品4'の少なくとも一部は、第1のインターポーザ2の上面2Aの第4領域2D(オーバーハング領域40Dと対向する領域2E)と、第2のインターポーザ40の下面40Bの第2領域40Dとの間の空間に配置される。

【0044】

また、第1のインターポーザ2のうち、半導体チップ3が実装される上面2Aとは反対側の下面2Bには、例えばマザーボード等の外部機器と電気的に接続可能な端子13が形成されている。本実施形態においては、端子13は、はんだボールによって形成されている。

【0045】

また、第1のインターポーザ2の上面2A側に実装された半導体チップ3、受動部品4'、ワイヤー9等は、樹脂14(図2)によって覆われている。樹脂14は型(モールド)を形成する。

【0046】

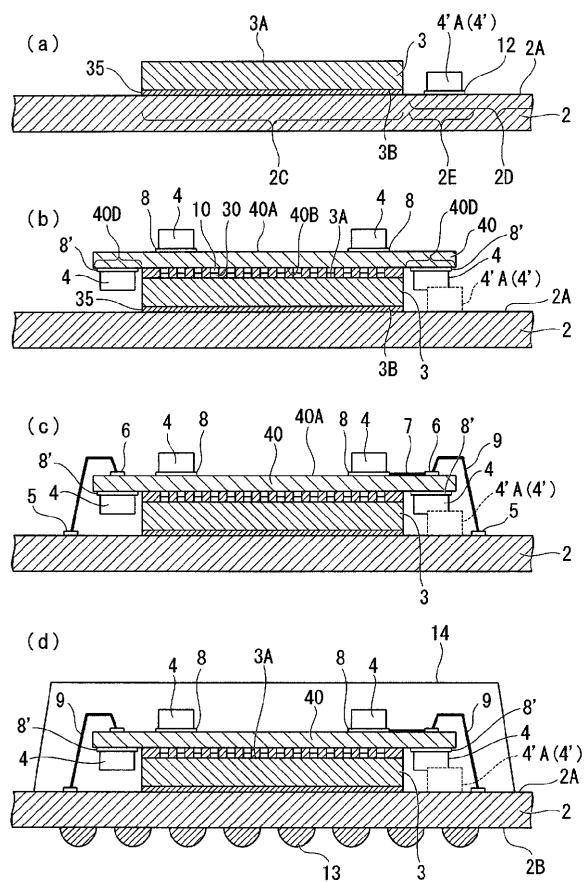

[半導体モジュールの製造方法]

次に、半導体モジュール1を製造する手順の一例について説明する。なお、本実施形態においては、既存の半導体チップ3を用いて半導体モジュール1を構成してもよいし、以下に説明するように半導体チップ3を始めから形成することとしてもよい。

半導体モジュール1の半導体チップ3を形成する際には、図5に示すように、同一のシリコン基板(ウエハ)100上に半導体チップ3を複数一括して形成し、その後ダイシング(切断)して個片化することによって、半導体チップ3が得られることになるが、以下の図4を用いた説明においては、簡略化のため、1つの半導体チップ3を形成する場合について説明する。

【0047】

シリコン基板に、後に半導体チップ3の一部となる集積回路を含む第1面(能動面3A)と第2面(裏面3B)とを形成する。シリコン基板に能動面3Aと裏面3Bとを有する

10

20

30

40

50

半導体チップ3を形成した後、図4(a)に示すように、その半導体チップ3を第1のインターポーザ2にダイボンディングする。このとき、半導体チップ3を、その裏面3Bが第1のインターポーザ2の上面2Aに対向するようにして第1のインターポーザ2に接続する。

【0048】

上述のように、ダイボンディングするためのダイボンディングペースト35としては、例えば導電性樹脂、無鉛はんだ等を用いることができる。なお、ダイボンディングペースト35は、例えばインクジェット法、ディスペ ns法、印刷法等を用いて、半導体チップ3の裏面3B及び第1のインターポーザ2の上面2Aの第3の領域2Cの少なくとも一方に供給可能である。

10

【0049】

また、図4(a)に示すように、第1のインターポーザ2の上面2Aの第4領域2Dに受動部品4'を接続するとともに、第4領域2Dの一部の領域である上記領域2Eに受動部品4'Aを接続する。本実施形態においては、受動部品4' (4'A)と第1のインターポーザ2の上面2Aの電極パッド12とを、導電性材料を含む接着剤を介して電気的に接続(ボンディング)する。

【0050】

受動部品4' (4'A)と電極パッド12とを電気的に接続するための接着剤としては、例えば導電性樹脂、無鉛はんだ等を用いることができる。なお、接着剤は、例えばインクジェット法、ディスペ ns法、印刷法等を用いて、受動部品4' (4'A)及び第1のインターポーザ2の電極パッド12の少なくとも一方に供給可能である。

20

【0051】

また、別の工程において、第2のインターポーザ40の下面40Bの周縁の第2領域40D、及び上面40Aの所定位置に、受動部品4を接続する。受動部品4と第2のインターポーザ2の上面40Aの電極パッド8とは、導電性材料を含む接着剤を介して電気的に接続(ボンディング)する。受動部品4と電極パッド8とを電気的に接続するための接着剤としては、例えば導電性樹脂、無鉛はんだ等を用いることができる。

【0052】

なお、接着剤は、例えばインクジェット法、ディスペ ns法、印刷法等を用いて、受動部品4及び第2のインターポーザ2の電極パッド8の少なくとも一方に供給可能である。同様に、第2のインターポーザ40の下面40B(第2領域40D)にも、受動部品4と電気的に接続可能な電極パッド8'を形成し、受動部品4と、第2のインターポーザ40の下面40Bの電極パッド8'とを、導電性材料を含む接着剤を介して電気的に接続する。

30

【0053】

そして、図4(b)に示すように、第1のインターポーザ2に実装された半導体チップ3の能動面3Aに、受動部品4が接続された第2のインターポーザ40の下面40Bを接続する。本実施形態においては、半導体チップ3を第2のインターポーザ40にフリップチップ実装する。半導体チップ3を、その能動面3Aを第2のインターポーザ40の下面40Bとを対向させて第2のインターポーザ40に実装する。このとき、半導体チップ3のバンプ30と第2のインターポーザ40の接続端子10とを接触させるように実装することによって、半導体チップ3と第2のインターポーザ40とが電気的に接続されることになる。

40

【0054】

このフリップチップ実装には、金属圧着式、ろう材や異方性導電材を用いた加圧加熱式、超音波振動式(超音波加熱方式)などを用いることができる。本実施形態では、上述したように超音波接合(Au-Au接合)することにより、狭ピッチに対応した電気接続を可能としている。これは、半導体チップ3のバンプ30と第2のインターポーザ40の接続端子10との接合に留まらず、能動面3Aと下面40Bとの接着性を向上させる手段としても有効である。

50

## 【0055】

次に、図4(c)に示すように、第1のインターポーザ2の電極パッド5と第2のインターポーザ40の電極パッド6とをワイヤーボンディングによって電気的に接続する。上述のように、ワイヤーボンディングするためのワイヤー9は、例えば、金(Au)、アルミニウム(Al)によって形成可能である。

## 【0056】

そして、図4(d)に示すように、第1のインターポーザ2の上面2A側に実装された半導体チップ3、受動部品4、4'、ワイヤー9等を覆うように、モールドを形成するための樹脂14が供給される。

## 【0057】

また、第1のインターポーザ2のうち、半導体チップ3が実装される上面2Aとは反対側の下面2Bには、例えばマザーボード等の外部機器と電気的に接続可能なはんだボール等の端子13が形成される。

## 【0058】

以上説明したように、本実施形態によれば、第1のインターポーザ2に裏面3Bを対向させて半導体チップ3を実装するとともに、半導体チップ3の能動面3Aと対向するよう受動部品4が接続された第2のインターポーザ40を配置するようにしたので、半導体モジュール1の小型化、特に第1のインターポーザ2の表面(上面2A、下面2B)、及び第2のインターポーザ40の表面(上面40A、下面40B)と平行な面内における半導体モジュール1の小型化を実現することができる。

10

20

## 【0059】

すなわち、受動部品4を有する半導体モジュール1において、全ての受動部品4を例えば第1のインターポーザ2の上面2Aに設け、第1のインターポーザ2上に半導体チップ3と受動部品4とを並べるように配置する場合、受動部品4を配置するための領域を確保しなければならず、半導体モジュール1の小型化、特に、第1のインターポーザ2の上面2Aと平行な面内における半導体モジュール1の小型化が困難となる。

## 【0060】

本実施形態においては、図2に示すように、半導体モジュール1に実装される受動部品の少なくとも一部を、半導体チップ3を介して第2のインターポーザ40に実装するようにしたので、半導体モジュール1の小型化を実現することができる。

30

## 【0061】

また、本実施形態においては、半導体モジュール1を製造する際、第1のインターポーザ2に半導体チップ3を実装する第1の工程と、第2のインターポーザ40に受動部品4を接続する第2の工程とを別々に実行し、それら第1、第2の工程の後、第1のインターポーザ2に実装された半導体チップ3の能動面3Aに、受動部品4が接続された第2のインターポーザ40を接続するようにしたので、半導体モジュール1を製造する際の工程の複雑化等を抑制できる。

## 【0062】

また、本実施形態においては、第2のインターポーザ40の大きさを、半導体チップ3よりも大きくし、第2のインターポーザ40の下面40Bにオーバーハング領域40Dが形成されるようにしたので、そのオーバーハング領域40Dにも受動部品4を接続することができる。所定数の受動部品4を第2のインターポーザ40に接続しようとする場合、上面40Aのみに複数の受動部品4を接続しようとすると第2のインターポーザ40の大きさを大きくしなければならなくなる可能性がある。本実施形態においては、第2のインターポーザ40にオーバーハング領域40Dを設けて下面40Bにも受動部品4を接続するようにしたので、第2のインターポーザ40の下面40Bのうち、半導体チップ3が接続される第1領域40C以外のオーバーハング領域40Dを有効に利用して、第2のインターポーザ40の大型化を抑制しつつ、所定数の受動部品4をその第2のインターポーザ40に接続することができる。

40

## 【0063】

50

また、本実施形態においては、半導体チップ3は、第1のインターポーザ2の上面2Aの第3領域2Cに実装され、半導体モジュール1に実装される受動部品の一部は、第1のインターポーザ2の上面2Aのうち、半導体チップ3が実装される第3領域2C以外の第4領域2Dに接続される。また、第4領域2Dのうち、半導体チップ3から庇状に張り出した第2のインターポーザ40のオーバーハング領域40Dに対向する領域2Eにも受動部品を接続するようにしたので、第1のインターポーザ2の上面2Aの第4領域2Dを有効に利用することができる。

【0064】

また、本実施形態においては、その第1のインターポーザ2に接続される受動部品4' (4'A)を、第2のインターポーザ2のオーバーハング領域40Dと対向する領域に配置するようにしたので、半導体モジュール1の小型化を実現することができる。

10

【0065】

また、本実施形態においては、受動部品4が実装される第2のインターポーザ40の上面40Aには、第1のインターポーザ2の電極パッド5と電気的に接続可能な電極パッド6が形成されるとともに、受動部品4と電極パッド6とを電気的に接続するための電極パッド8及び配線7が形成され、電極パッド5と電極パッド6とはワイヤーボンディングで接続されるので、第2のインターポーザ40に接続された受動部品4と第1のインターポーザ2とを電気的に接続することができる。

【0066】

以上、添付図面を参照しながら本発明に係る好適な実施形態について説明したが、本発明は係る例に限定されることは言うまでもなく、上記各実施形態を組み合わせても良い。当業者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、それらについても当然に本発明の技術的範囲に属するものと了解される。

20

【0067】

なお、上述の実施形態においては、第2のインターポーザ40の下面40Bに、受動部品4を接続可能なオーバーハング領域40Dを設けているが、所定数の受動部品4の全てを第2のインターポーザ40の上面40Aに接続可能であるならば、オーバーハング領域40Dは無くてもよい。すなわち、能動面3Aと平行な面内における第2のインターポーザ40の大きさが、半導体チップ3の大きさとほぼ同じあるいは小さくてもよい。こうすることにより、より一層、半導体モジュール1を小型化することができる。

30

【0068】

また、上述の実施形態においては、第1のインターポーザ2の上面2Aの第4領域2Dにも受動部品4'が接続されているが、受動部品4'を設けないようにしてよい。こうすることにより、第4領域2Dを小さくすることができる。すなわち、半導体チップ3の裏面3Bと平行な面内における第1のインターポーザ2の大きさを小さくすることができて、より一層、半導体モジュール1を小型化することができる。

30

【0069】

また、上述の実施形態においては、受動部品4が接続された第2のインターポーザ40を半導体チップ3に実装したが、第1のインターポーザ2に実装された半導体チップ3の能動面3Aに、第2のインターポーザ40を接続した後、その第2のインターポーザ40に受動部品4を接続するようにしてもよい。

40

【0070】

また、上述の実施形態においては、第1のインターポーザ2に半導体チップ3を先に設け、その後半導体チップ3上に第2のインターポーザ3を実装したが、半導体チップ3を第2のインターポーザ40に対して先に実装し、その後、第2のインターポーザ40を備えた半導体チップ3を第1のインターポーザ2に実装するようにしてもよい。これにより、第2のインターポーザ2に対する半導体チップ3の位置決めが容易となり、フリップチップ実装精度が向上する。

【図面の簡単な説明】

50

【 0 0 7 1 】

【図1】本実施形態に係る半導体モジュールを模式的に示す斜視図である。

【図2】本実施形態に係る半導体モジュールの側断面図であって、図1のA-A線断面矢視図に相当する図である。

【図3】本実施形態に係る半導体モジュールの一部を拡大した平面図である。

【図4】本実施形態に係る半導体モジュールを製造する手順の一例を説明するための図である。

【図5】本実施形態に係る半導体モジュールを製造する手順の一例を説明するための図である。

## 【符号の説明】

0

[ 0 0 7 2 ]

1 … 半導体モジュール、2 … 第 1 のインターポーザ、2 A … 上面（第 1 の面）、3 … 半導体チップ、3 A … 能動面、3 B … 裏面、4, 4', 4'' A … 受動部品、5, 6, 8, 8', 12 … 電極パッド（端子）、7 … 配線、9 … ワイヤー、10 … 接続端子、40 C, 40 D, 2 C, 2 D, 2 E … 領域、40 … 第 2 のインターポーザ、40 A … 上面（第 1 の面）、40 B … 下面（第 2 の面）

〔 図 1 〕

( 义 3 )

〔 2 〕

【 図 4 】

【 図 5 】