(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6678506号

(P6678506)

(45) 発行日 令和2年4月8日(2020.4.8)

(24) 登録日 令和2年3月19日(2020.3.19)

|              |                                 |

|--------------|---------------------------------|

| (51) Int.Cl. | F 1                             |

| H01L 23/00   | (2006.01)                       |

| H01L 23/12   | (2006.01)                       |

| H05K 1/02    | (2006.01)                       |

|              | HO1L 23/00 HO1L 23/12 H05K 1/02 |

|              | A F R                           |

請求項の数 11 (全 22 頁)

(21) 出願番号 特願2016-90189 (P2016-90189)

(22) 出願日 平成28年4月28日 (2016.4.28)

(65) 公開番号 特開2017-199823 (P2017-199823A)

(43) 公開日 平成29年11月2日 (2017.11.2)

審査請求日 平成30年11月13日 (2018.11.13)

(73) 特許権者 507292184

株式会社アムコー・テクノロジー・ジャパン

大分県臼杵市福良1913-2

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

(72) 発明者 竹原 靖之

石川県能美市赤井町は86番地 株式会社

ジェイデバイス 根上センター内

(72) 発明者 北野 一彦

石川県能美市赤井町は86番地 株式会社

ジェイデバイス 根上センター内

審査官 平林 雅行

最終頁に続く

(54) 【発明の名称】半導体パッケージ及び半導体パッケージの製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

少なくとも 1 つの凹部が設けられた基材と、

前記基材の前記少なくとも 1 つの凹部が設けられた面側に配置された半導体装置と、

前記半導体装置を覆う樹脂絶縁層と、

前記基材と前記半導体装置との間に配置された接着層と、

を有し、

前記接着層は、前記少なくとも 1 つの凹部を露出する開口部を有し、

前記開口部の端部は、平面視で前記少なくとも 1 つの凹部に隣接し、

前記樹脂絶縁層は、前記開口部を規定する前記接着層の側壁に接していることを特徴とする半導体パッケージ。

## 【請求項 2】

前記半導体装置に電気的に接続された導電層をさらに有し、

前記樹脂絶縁層は、前記半導体装置の上方に設けられ、

前記導電層は、前記半導体装置及び前記樹脂絶縁層の上方に設けられ、

前記導電層は、前記樹脂絶縁層に設けられた開口を通じて前記半導体装置に接続されていることを特徴とする請求項 1 に記載の半導体パッケージ。

## 【請求項 3】

前記開口部の前記端部は、前記少なくとも 1 つの凹部を連続して囲み、

前記開口部には、導電性材料を含んだ、前記半導体装置に接続された構造体が設けられ

10

20

ていいないことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項4】**

前記凹部は2つ以上設けられ、前記半導体装置のそれぞれ対角に対応する位置に設けられており、

前記開口部には、導電性材料を含んだ、前記半導体装置に接続された構造体が設けられていなことを特徴とする請求項1に記載の半導体パッケージ。

**【請求項5】**

基材に第1凹部を形成し、

前記第1凹部が形成された前記基材の表面に接着層を形成し、

前記接着層は、前記第1凹部を露出する第1開口部を含み、

前記第1開口部の端部は、平面視で前記第1凹部を囲み、

前記第1凹部に基づいて位置合わせして、半導体装置を前記接着層の表面に配置し、

前記半導体装置を覆う樹脂絶縁層を形成し、

前記樹脂絶縁層は、前記第1開口部を規定する前記接着層の側壁に接していることを特徴とする半導体パッケージの製造方法。

**【請求項6】**

前記樹脂絶縁層に、前記半導体装置の外部端子を露出する開口をさらに形成し、

前記外部端子に接続されるように、前記樹脂絶縁層の上及び前記樹脂絶縁層の前記開口の中に導電層をさらに形成することを特徴とする請求項5に記載の半導体パッケージの製造方法。

10

**【請求項7】**

前記樹脂絶縁層は、前記第1凹部の側壁に接するように形成されることを特徴とする請求項5に記載の半導体パッケージの製造方法。

**【請求項8】**

前記基材に第2凹部をさらに形成し、

前記接着層を形成することは、前記第2凹部を露出する第2開口部を前記接着層に形成することを含み、

前記位置合わせは、前記第1凹部及び前記第2凹部に基づいて行われることを特徴とする請求項5に記載の半導体パッケージの製造方法。

20

**【請求項9】**

基材に第1凹部、第2凹部、及び第3凹部を形成し、

前記第1凹部、前記第2凹部、及び前記第3凹部が形成された前記基材の表面に接着層を形成し、

前記接着層は、

前記第1凹部を露出する第1開口部を含み、

前記第2凹部を露出する第2開口部を含み、

前記第3凹部を露出する第3開口部を含み、

前記第1開口部の端部は、平面視で前記第1凹部を囲み、

前記第1凹部は、前記基材の前記表面の一部が前記端部と前記第1凹部との間に位置するように、前記端部の内側に配置され、

30

前記第1凹部及び前記第2凹部に基づいて位置合わせして、第1半導体装置を前記接着層上に配置し、

前記第2凹部及び前記第3凹部に基づいて位置合わせして、第2半導体装置を前記接着層上に配置し、

前記第1半導体装置及び前記第2半導体装置を覆う樹脂絶縁層を形成し、

前記樹脂絶縁層は、前記第1開口部の側壁、前記第2開口部の側壁、及び前記第3開口部の側壁に接していることを特徴とする半導体パッケージの製造方法。

40

**【請求項10】**

前記樹脂絶縁層に、前記第1半導体装置の外部端子を露出する開口をさらに形成し、

前記外部端子に接続されるように、前記樹脂絶縁層の上及び前記樹脂絶縁層の前記開口

50

の中に導電層をさらに形成することを特徴とする請求項9に記載の半導体パッケージの製造方法。

【請求項11】

前記樹脂絶縁層は、前記第1凹部の側壁、前記第2凹部の側壁、及び前記第3凹部の側壁に接するように形成されることを特徴とする請求項9に記載の半導体パッケージの製造方法。

【発明の詳細な説明】

【技術分野】

10

【0001】

本発明は、半導体パッケージ及び半導体パッケージの製造方法に関する。特に、基材上における半導体装置の実装技術に関する。

【背景技術】

【0002】

従来、携帯電話やスマートホン等の電子機器において、支持基板上にICチップ等の半導体装置を搭載する半導体パッケージ構造が知られている（例えば、特許文献1）。このような半導体パッケージは、一般的には、支持基材上に接着層を介してICチップやメモリ等の半導体装置を接着し、その半導体装置を封止体（封止用樹脂材料）で覆って、半導体デバイス保護する構造を採用している。

20

【0003】

半導体装置に用いる支持基材としては、プリント基材、セラミックス基材等の様々な基材が用いられている。特に、近年では、金属基材を用いた半導体パッケージの開発が進められている。金属基材上に半導体装置を搭載し、再配線によりファンアウトする半導体パッケージは、電磁シールド性や熱特性に優れるといった利点を有し、信頼性の高い半導体パッケージとして注目されている。また、このような半導体パッケージは、パッケージデザインの自由度が高いという利点も有する。

【0004】

また、支持基材上に半導体装置を搭載する構造とした場合、大型の支持基材上に複数の半導体装置を搭載することにより、同一プロセスで複数の半導体パッケージを製造することが可能である。この場合、支持基材上に形成された複数の半導体パッケージは、製造プロセスの終了後に個片化され、個々の半導体パッケージが完成する。このように支持基材上に半導体装置を搭載する半導体パッケージ構造は、量産性が高いという利点も有している。

30

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010-278334号公報

【発明の概要】

【発明が解決しようとする課題】

40

【0006】

上記のように、支持基材として大型の金属基材を用いた量産を考慮した場合、当該金属基材へ半導体装置を配置する際の高いアライメント精度、又は半導体装置と配線との良好なコンタクト、又は歩留まりが高い半導体パッケージの個片化などが課題となっている。

【0007】

本発明は、そのような課題に鑑みてなされたものであり、基材へ半導体装置を配置する際の高いアライメント精度を得るために半導体パッケージの製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

50

本発明の一実施形態に係る半導体パッケージは、少なくとも1つの凹部が設けられた基材と、基材の凹部が設けられた面側に配置された半導体装置と、半導体装置を覆う樹脂絶縁層と、を有する。

【0009】

また、基材と半導体装置との間に配置された接着層をさらに有していてもよい。

【0010】

また、接着層は、凹部を露出する開口部を有し、樹脂絶縁層は、開口部の側壁に接して置いてよい。

【0011】

また、凹部は2つ以上設けられ、半導体装置のそれぞれ対角に対応する位置に設けられていってよい。 10

【0012】

本発明の一実施形態に係る半導体パッケージの製造方法は、基材に少なくとも1つの凹部を形成し、凹部に基づいて位置合わせして、半導体装置を基材の凹部が形成された面側に配置し、半導体装置を覆う樹脂絶縁層を形成する。

【0013】

また、凹部が形成された基材上に接着層をさらに形成し、半導体装置は接着層上に配置されてもよい。

【0014】

また、接着層に凹部を露出する開口部をさらに形成し、樹脂絶縁層は、開口部の側壁に接するように形成されてもよい。 20

【0015】

また、凹部は、2つ以上形成され、位置合わせは、2つ以上の凹部に基づいて行われてもよい。

【0016】

本発明の一実施形態に係る半導体パッケージの製造方法は、基材に第1凹部、第2凹部、及び第3凹部を形成し、第1凹部及び第2凹部に基づいて位置合わせして、第1半導体装置を基材の第1凹部及び第2凹部が形成された面側に配置し、第2凹部及び第3凹部に基づいて位置合わせして、第2半導体装置を基材の第2凹部及び第3凹部が形成された面側に配置し、第1半導体装置及び第2半導体装置を覆う樹脂絶縁層を形成する。 30

【0017】

また、第1凹部、第2凹部、及び第3凹部が形成された基材上に接着層をさらに形成し、第1半導体装置及び第2半導体装置は接着層上に配置されてもよい。

【0018】

また、接着層に、第1凹部を露出する第1開口部、第2凹部を露出する第2開口部、及び第3凹部を露出する第3開口部をさらに形成し、樹脂絶縁層は、第1開口部の側壁、第2開口部の側壁、及び第3開口部の側壁に接するように形成されてもよい。

【発明の効果】

【0019】

本発明に係る半導体パッケージの製造方法によると、基材へ半導体装置を配置する際の高いアライメント精度を得るために半導体パッケージの製造方法を提供することができる。

【図面の簡単な説明】

【0020】

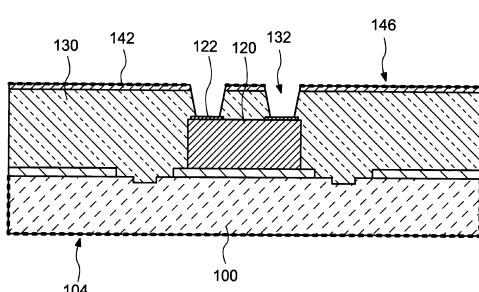

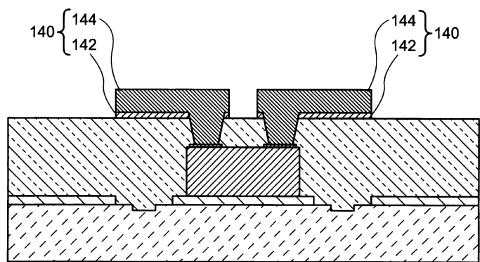

【図1A】本発明の一実施形態に係る半導体パッケージの断面模式図である。

【図1B】本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。

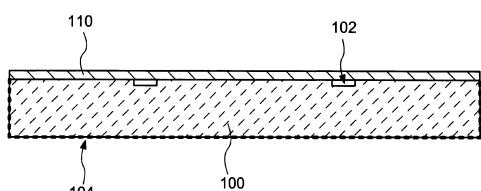

【図2】本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材にアライメントマーカを形成する工程を示す図である。

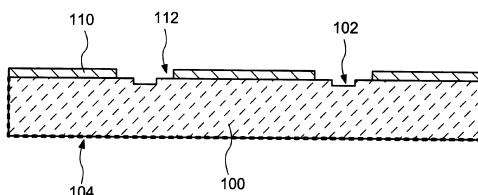

【図3】本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材に接

40

50

着層を形成する工程を示す図である。

【図4】本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材の裏面及び側面を粗化する工程を示す図である。

【図5】本発明の一実施形態に係る半導体パッケージの製造方法において、接着層の一部を除去する工程を示す図である。

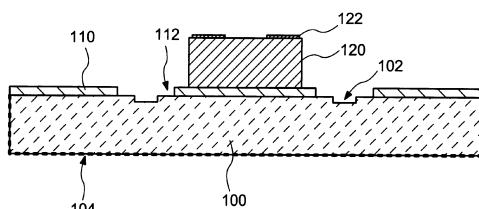

【図6】本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材上に半導体装置を配置する工程を示す図である。

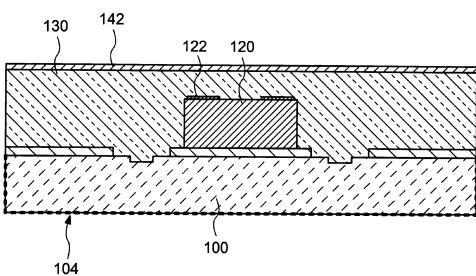

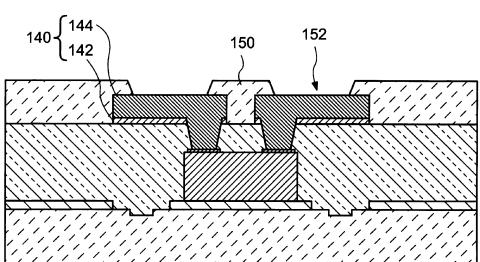

【図7】本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層を形成する工程を示す図である。

【図8】本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層上に導電層を形成する工程を示す図である。 10

【図9】本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の表面を粗化する工程を示す図である。

【図10】本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に開口部を形成する工程を示す図である。

【図11】本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の表面の粗化された領域を除去し、開口底部の残渣を除去する工程を示す図である。

【図12】本発明の一実施形態に係る半導体パッケージの製造方法において、無電解めっき法によって導電層を形成する工程を示す図である。

【図13】本発明の一実施形態に係る半導体パッケージの製造方法において、感光性フォトレジストを形成する工程を示す図である。 20

【図14】本発明の一実施形態に係る半導体パッケージの製造方法において、フォトリソグラフィによって感光性フォトレジストの一部を除去する工程を示す図である。

【図15】本発明の一実施形態に係る半導体パッケージの製造方法において、電解めっき法によって導電層を形成する工程を示す図である。

【図16】本発明の一実施形態に係る半導体パッケージの製造方法において、感光性フォトレジストを除去する工程を示す図である。

【図17】本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の一部を除去して配線を形成する工程を示す図である。

【図18】本発明の一実施形態に係る半導体パッケージの製造方法において、配線を覆う樹脂絶縁層を形成する工程を示す図である。 30

【図19】本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に配線を露出する開口部を形成する工程を示す図である。

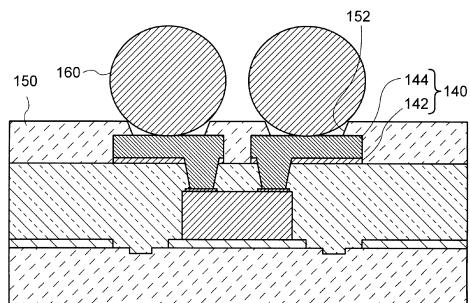

【図20】本発明の一実施形態に係る半導体パッケージの製造方法において、露出された配線に対応する位置にはんだボールを配置する工程を示す図である。

【図21】本発明の一実施形態に係る半導体パッケージの製造方法において、はんだボールをリフローする工程を示す図である。

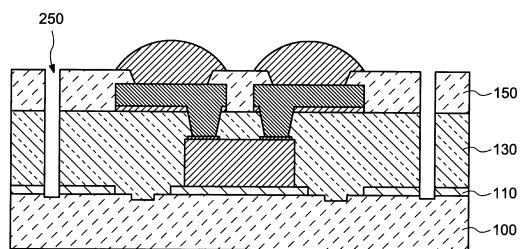

【図22】本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に支持基材に達する溝を形成する工程を示す図である。

【図23】本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材を切断して半導体パッケージを個片化する工程を示す図である。 40

【図24】本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。

【図25】本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。

#### 【発明を実施するための形態】

##### 【0021】

以下、本発明の一実施形態に係る半導体パッケージの構造及びその製造方法について、図面を参照しながら詳細に説明する。なお、以下に示す実施形態は本発明の実施形態の一例であって、本発明はこれらの実施形態に限定して解釈されるものではない。なお、本実 50

施形態で参照する図面において、同一部分または同様な機能を有する部分には同一の符号または類似の符号を付し、その繰り返しの説明は省略する場合がある。また、図面の寸法比率は説明の都合上実際の比率とは異なる場合や、構成の一部が図面から省略される場合がある。また、説明の便宜上、上方又は下方という語句を用いて説明するが、例えば、第1部材と第2部材との上下関係が図示と逆になるように配置されてもよい。また、以下の説明で基板の第1面及び第2面は基板の特定の面を指すものではなく、基板の表面方向又は裏面方向を特定するもので、つまり基板に対する上下方向を特定するための名称である。

#### 【0022】

##### 実施形態1

10

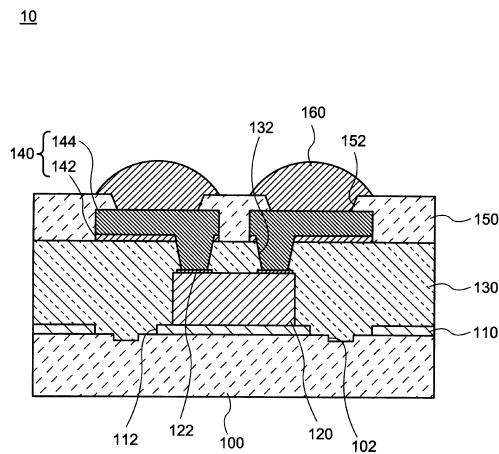

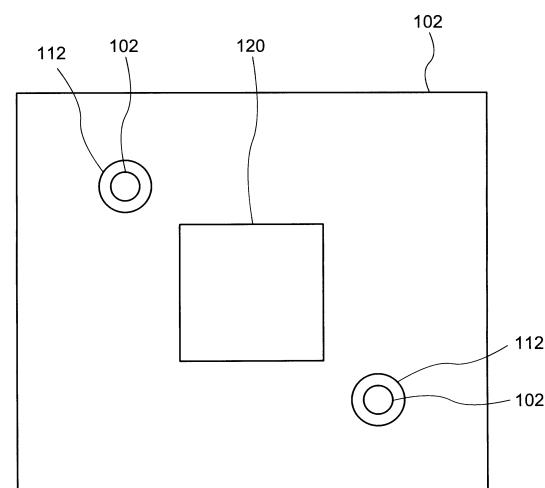

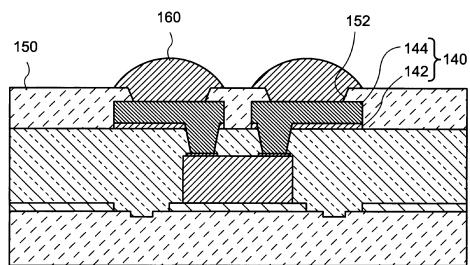

本発明の実施形態1に係る半導体パッケージの概要について、図1A及び図1Bを参照しながら詳細に説明する。図1Aは、本発明の一実施形態に係る半導体パッケージの断面模式図である。図1Bは、本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。なお、図1Bでは、説明の便宜上半導体装置120よりも上層の、例えば配線140及びはんだボール160は省略して図示した。

#### 【0023】

##### [半導体パッケージ10の構造]

図1Aに示すように、半導体パッケージ10は、支持基材100、接着層110、半導体装置120、第1樹脂絶縁層130、配線140、第2樹脂絶縁層150、及びはんだボール160を有する。また、図1Bに示すように、支持基材100上において、半導体装置120の周囲にアライメントマーカ102が設けられている。図1Bでは、アライメントマーカ102は半導体装置120の対角に対応する位置に2つ設けられている。

20

#### 【0024】

支持基材100には、支持基材100の一部が凹んだ形状のアライメントマーカ102(凹部)が設けられている。換言すると、半導体パッケージ10には平坦ではない支持基材100が用いられる。接着層110は支持基材100の表面に配置されており、アライメントマーカ102を露出するように接着層110の一部が開口されている。ここで、支持基材100の表面とは、支持基材100のアライメントマーカ102が設けられた面側を指す。なお、接着層110にはアライメントマーカ102よりも広い領域で開口された開口部112が設けられており、開口部112はアライメントマーカ102及びその周辺の支持基材100の表面を露出している。

30

#### 【0025】

ここで、アライメントマーカ102のサイズ(最も径が大きな箇所におけるサイズ)は0.05mm以上1.0mm以下の範囲で選択することができる。好ましくは、アライメントマーカ102のサイズは0.1mm以上0.3mm以下であるとよい。また、アライメントマーカ102と半導体装置120との距離は0.05mm以上0.5mm以下の範囲で選択することができる。ここで、アライメントマーカ102のサイズは、アライメントマーカの読み取り装置が認識可能なサイズであればよい。また、図1Bでは、アライメントマーカ102の形状が円形状である例を示したが、その他の形状であってもよい。また、アライメントマーカ102は数字や文字であってもよい。なお、アライメントマーカ102のサイズとは、1つのアライメントマーカ102において最も径が大きい箇所のサイズを意味する。また、アライメントマーカ102と半導体装置120との距離とは、両者の間隔のうち最も短い箇所の距離を意味する。

40

#### 【0026】

半導体装置120は、接着層110上に配置されている。半導体装置120の上部には、半導体装置120に含まれる電子回路に接続された外部端子122が設けられている。ここで、図1Aでは接着層110が単層である構造を例示したが、この構造に限定されず、接着層110は複数層であってもよい。また、図1Bでは1つの半導体装置120に対して2つのアライメントマーカ102が設けられた構成を例示したが、この構成に限定されない。例えば、アライメントマーカ102は1つの半導体装置120に対して少なくと

50

も1つ以上設けられていればよい。また、アライメントマーカ102は1つの半導体装置120に対して3つ以上設けられていてもよい。

#### 【0027】

第1樹脂絶縁層130は半導体装置120を覆うように支持基材100上に配置されている。第1樹脂絶縁層130は開口部112及びアライメントマーカ102の凹部を埋めるように配置されている。換言すると、第1樹脂絶縁層130は開口部112の側壁に接している。同様に、第1樹脂絶縁層130はアライメントマーカ102の凹部の側壁に接している。また、第1樹脂絶縁層130には開口部132が設けられている。開口部132は外部端子122に達している。換言すると、開口部132は外部端子122を露出するように設けられている。

10

#### 【0028】

ここで、図1Aでは、開口部112の側壁の形状が垂直であり、当該側壁と接着層110の表面とが直角をなしている構造を例示したが、この構造に限定されない。例えば、開口部112の側壁が接着層110の表面に対する垂線から傾斜したテーパ形状であってもよい。テーパ形状としては、開口部112の下方から上方に向かって開口径が大きくなる順テーパ形状であってもよく、逆に開口部112の下方から上方に向かって開口径が小さくなる逆テーパ形状であってもよい。また、開口部112の側壁と接着層110の表面との間が湾曲していてもよい。つまり、開口部112の側壁と接着層110の表面との角部が丸まった形状であってもよい。

#### 【0029】

配線140は第1導電層142及び第2導電層144を有する。第1導電層142は第1樹脂絶縁層130の上面に配置されている。第2導電層144は第1導電層142上及び開口部132内部に配置されており、外部端子122に接続されている。図1Aでは、第1導電層142は第1樹脂絶縁層130の上面のみに配置されており、開口部132の内部には全く配置されていない構造を例示したが、この構造に限定されない。例えば、第1導電層142の一部が開口部132内部に入り込んでいてもよい。第1導電層142及び第2導電層144の各々は、図1Aに示すように単層であってもよく、第1導電層142及び第2導電層の一方又は両方が複数層であってもよい。

20

#### 【0030】

第2樹脂絶縁層150は配線140を覆うように第1樹脂絶縁層130上に配置されている。また、第2樹脂絶縁層150には開口部152が設けられている。開口部152は配線140に達している。換言すると、開口部152は配線140を露出するように設けられている。

30

#### 【0031】

はんだボール160は開口部152内部及び第2樹脂絶縁層150の上面に配置されており、配線140に接続されている。はんだボール160の上面は第2樹脂絶縁層150の上面から上方に突出している。はんだボール160の突出部は上に凸の湾曲形状を有している。はんだボール160の湾曲形状は断面視において円弧であってもよく、放物線であってもよい。

#### 【0032】

以上のように、実施形態1に係る半導体パッケージによると、第1樹脂絶縁層130がアライメントマーカ102の凹部の側壁に接していることで、接着層110と第1樹脂絶縁層130との密着性を向上させることができる。例えば、支持基材100にアライメントマーカ102を設けると、アライメントマーカ102が設けられた領域における接着層110による接着効果が弱くなってしまう。そのため、局所的に第1樹脂絶縁層130が支持基材100から剥離し、その剥離をきっかけとして第1樹脂絶縁層130が接着層110から剥離してしまうことがある。しかし、上記のように、第1樹脂絶縁層130がアライメントマーカ102の凹部の側壁に接していることで、局所的な第1樹脂絶縁層130の支持基材100からの剥離を抑制することができる。

40

#### 【0033】

50

[半導体パッケージ 10 の各部材の材質 ]

図 1 A 及び図 1 B に示す半導体パッケージ 10 に含まれる各部材（各層）の材料について詳細に説明する。

【 0034 】

支持基材 100 としては、金属基材を用いることができる。金属基材としては、ステンレス (SUS) 基材、アルミニウム (Al) 基材、チタン (Ti) 基材、銅 (Cu) 等の金属材料を用いることができる。また、支持基材 100 として、金属基材の他にシリコン基板、炭化シリコン基板、化合物半導体基板などの半導体基材を用いることができる。なお、SUS 基材は熱膨張率が低く、低価格であるため、支持基材 100 として SUS 基材を用いることが好ましい。

10

【 0035 】

接着層 110 としては、エポキシ系樹脂またはアクリル系樹脂を含む接着剤を用いることができる。

【 0036 】

半導体装置 120 としては、中央演算処理装置 (Central Processing Unit ; CPU)、メモリ、微小電気機械システム (Micro Electro Mechanical Systems ; MEMS)、電力用半導体素子 (パワー・デバイス) などを用いることができる。

【 0037 】

第 1 樹脂絶縁層 130 及び第 2 樹脂絶縁層 150 としては、ポリイミド、エポキシ樹脂、ポリイミド樹脂、ベンゾシクロブテン樹脂、ポリアミド、フェノール樹脂、シリコーン樹脂、フッ素樹脂、液晶ポリマー、ポリアミドイミド、ポリベンゾオキサゾール、シアネット樹脂、アラミド、ポリオレフィン、ポリエステル、BTレジン、FR-4、FR-5、ポリアセタール、ポリブチレンテレフタレート、シンジオタクチック・ポリスチレン、ポリフェニレンサルファイド、ポリエーテルエーテルケトン、ポリエーテルニトリル、ポリカーボネート、ポリフェニレンエーテルポリサルホン、ポリエーテルスルホン、ポリアリレート、ポリエーテルイミドなどを用いることができる。なお、エポキシ系樹脂は電気特性および加工特性に優れているため、第 1 樹脂絶縁層 130 及び第 2 樹脂絶縁層 150 としてエポキシ系樹脂を用いることが好ましい。

20

【 0038 】

ここで、本実施形態で用いられる第 1 樹脂絶縁層 130 にはフィラーが含まれている。フィラーとしては、ガラス、タルク、マイカ、シリカ、アルミナ等の無機フィラーが用いられてもよい。また、フィラーとしてフッ素樹脂フィラーなどの有機フィラーが用いられてもよい。ただし、第 1 樹脂絶縁層 130 が必ずフィラーを含む樹脂であることを限定するものではない。また、本実施形態では、第 2 樹脂絶縁層 150 はフィラーを含んでいないが、第 2 樹脂絶縁層 150 にフィラーが含まれていてもよい。

30

【 0039 】

第 1 導電層 142 及び第 2 導電層 144 としては、銅 (Cu)、金 (Au)、銀 (Ag)、白金 (Pt)、ロジウム (Rh)、スズ (Sn)、アルミニウム (Al)、ニッケル (Ni)、パラジウム (Pd)、クロム (Cr) 等の金属またはこれらを用いた合金などから選択することができる。第 1 導電層 142 と第 2 導電層 144 とは同じ材料を用いてもよく、異なる材料を用いてもよい。

40

【 0040 】

はんだボール 160 としては、例えば Sn に少量の Ag、Cu、Ni、ビスマス (Bi)、又は亜鉛 (Zn) を添加した Sn 合金で形成された球状の物体を用いることができる。また、はんだボール以外にも一般的な導電性粒子を使用することができる。例えば、導電性粒子として、粒子状の樹脂の周囲に導電性の膜が形成されたものを使用することができる。また、はんだボール以外に、はんだペーストを用いることができる。はんだペーストとしては、Sn、Ag、Cu、Ni、Bi、リン (P)、ゲルマニウム (Ge)、インジウム (In)、アンチモン (Sb)、コバルト (Co)、鉛 (Pb) を用いることがで

50

きる。

#### 【0041】

##### [半導体パッケージ10の製造方法]

図2乃至図23を用いて、本発明の実施形態1に係る半導体パッケージ10の製造方法を説明する。図2乃至図23において、図1A及び図1Bに示す要素と同じ要素には同一の符号を付した。ここで、支持基材100としてSUS基材、第1樹脂絶縁層130としてエポキシ系樹脂、第1導電層142及び、第2導電層144としてCu、はんだボール160として上記Sn合金を使用して半導体パッケージを作製する製造方法について説明する。

#### 【0042】

10

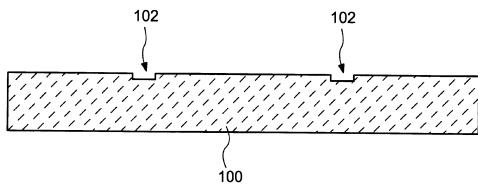

図2は、本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材にアライメントマーカを形成する工程を示す図である。アライメントマーカ102(凹部)は、フォトリソグラフィ及びエッチングによって形成される。アライメントマーカ102の位置及び平面形状は目的に応じて適宜決定することができる。アライメントマーカ102は、光学顕微鏡等で支持基材100を上面側から観察したときに、視認できる程度に段差が設けられていればよい。

#### 【0043】

ここで、図2では、後の工程で半導体装置120が配置される領域に対して2つのアライメントマーカ102を形成する製造方法を例示したが、この製造方法に限定されない。例えば、アライメントマーカ102は1つの半導体装置120が配置される領域に対して少なくとも1つ以上設けられていればよい。また、アライメントマーカ102は1つの半導体装置120が配置される領域に対して3つ以上設けられていてもよい。

20

#### 【0044】

また、アライメントマーカ102の形成方法として、上記のフォトリソグラフィ及びエッチングによる形成以外の方法を用いることができる。例えば、支持基材100の表面からレーザ照射を行うことでアライメントマーカ102を形成してもよい。レーザ照射の一つとして、マスクを使用せずにレーザ光を走査することによって、支持基材100に直接描画を行うレーザ直描装置を用いることができる。または、アライメントマーカ102に対応する形状の金型を用いて支持基材100を形成することもできる。

#### 【0045】

30

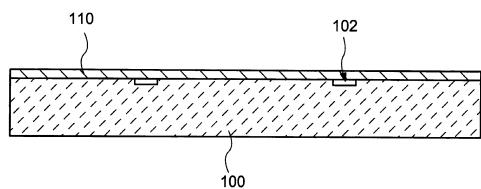

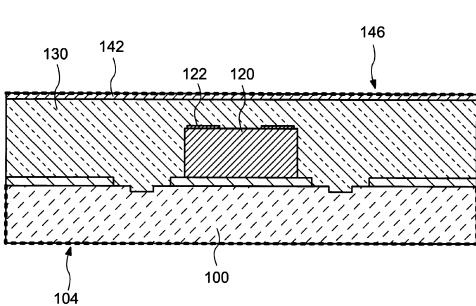

図3は、本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材に接着層を形成する工程を示す図である。アライメントマーカ102が形成された支持基材100の上面に接着層110を形成する。接着層110としてシート状の接着層を貼り付ける。なお、接着層110として接着層材料が溶解された溶媒を塗布法によって形成してもよい。図3では、アライメントマーカ102の凹部が空洞になっているが、アライメントマーカ102が形成された領域の接着層110は後の工程で除去されるので、この工程において接着層110がアライメントマーカ102の凹部に埋め込まれていてもよい。

#### 【0046】

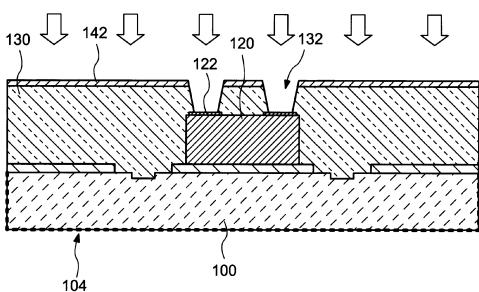

図4は、本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材の裏面及び側面を粗化する工程を示す図である。ここでは、後の工程で無電解めっき法によつて形成されるめっき層が剥離することを抑制する目的で、支持基材100の裏面及び側面を粗化(又は粗面化)する。支持基材100の粗化は、Cuを含む薬液(エッチャント)を用いることで行うことができる。図4において、粗化領域104を点線で示した。

40

#### 【0047】

支持基材100の粗化について、より詳細に説明する。支持基材100にSUS基材を用いる場合、SUS基材の表面は不動態化されている。ここで、上記のエッチャントに含まれるCuイオンはSUS基材中のFe、Cr、Niの少なくとも1つと置換されることでSUSがエッチングされる。しかし、SUSのエッチングは局所的に進行するため不均一にエッチングされ、エッチング後のSUS表面の凹凸が大きくなる。つまり、図4に示す状態でエッチャントに浸漬することで、SUS基材の裏面及び側面を同一処理で粗化す

50

ることができる。

#### 【0048】

なお、ここでは、接着層110を貼り付けた後にSUS基材の粗化を行う製造方法を例示したが、この製造方法に限定されない。例えば、接着層110を貼り付ける前、又はアライメントマーカ102を形成する前に粗化を行ってもよい。

#### 【0049】

図5は、本発明の一実施形態に係る半導体パッケージの製造方法において、接着層の一部を除去する工程を示す図である。アライメントマーカ102をより精度よく読み取るために、アライメントマーカ102の上方の接着層110を除去して開口部112を形成する。接着層110の除去は、例えばCO<sub>2</sub>レーザを用いたレーザ照射による昇華又はアブレーションによって行うことができる。又は、フォトリソグラフィ及びエッチングによって形成することもできる。開口部112はアライメントマーカ102を確実に露出するためにアライメントマーカ102よりも広い領域に形成される。つまり、開口部112は支持基材100の表面を露出する。換言すると、平面視において、開口部112はアライメントマーカ102を囲むように形成される。

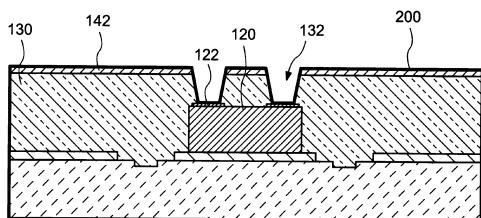

#### 【0050】

図6は、本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材上に半導体装置を配置する工程を示す図である。上記のようにして露出されたアライメントマーカ102に基づいて位置合わせを行い、上面（アライメントマーカ102が形成された面側）に外部端子122を有する半導体装置120を接着層110を介して支持基材100に配置する。アライメントマーカ102の読み取りは、例えば、光学顕微鏡、CCDカメラ、電子顕微鏡等の方法を行うことができる。この方法によって、高いアライメント精度で半導体装置120の実装を実現することができる。

#### 【0051】

図7は、本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層を形成する工程を示す図である。第1樹脂絶縁層130は、絶縁性のシート状フィルムの貼り付けによって形成される。具体的には、当該シート状フィルムを半導体装置120が実装された支持基材100に貼り付けた後に、加熱処理によってシート状フィルムを溶融させ、加圧処理によって溶融したシート状フィルムをアライメントマーカ102の凹部に埋め込む。この加熱処理および加圧処理によって上記シート状フィルムから、図7に示す第1樹脂絶縁層130を得る。第1樹脂絶縁層130は、開口部112及びアライメントマーカ102の凹部を埋めるように形成される。換言すると、第1樹脂絶縁層130は開口部112の側壁に接するように形成される。同様に、第1樹脂絶縁層130はアライメントマーカ102の凹部の側壁に接するように形成される。ここで、第1樹脂絶縁層130の膜厚は、第1樹脂絶縁層130が半導体装置120を覆うように設定される。つまり、第1樹脂絶縁層130の膜厚は半導体装置120の厚さよりも厚い。なお、第1樹脂絶縁層130は、半導体装置120、接着層110などによって形成された段差を緩和（平坦化）するため、平坦化膜と呼ばれることがある。

#### 【0052】

ただし、第1樹脂絶縁層130は、半導体装置120及び外部端子122と配線140とが導通することを防ぐことができればよいため、半導体装置120及び外部端子122と配線140とのギャップが十分に確保できていればよい。つまり、第1樹脂絶縁層130が半導体装置120及び外部端子122の少なくとも上面及び側面に配置されていれば、半導体装置120が配置されていない領域における第1樹脂絶縁層130の膜厚は半導体装置120の厚さよりも薄くてもよい。また、図7の説明では、第1樹脂絶縁層130をスピンドル法で形成する製造方法を例示したが、この方法に限定されない。例えば、ディップ法、インクジェット法、蒸着法などの多様な方法で第1樹脂絶縁層130を形成することができる。

#### 【0053】

図8は、本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層

10

20

30

40

50

上に導電層を形成する工程を示す図である。第1樹脂絶縁層130の上面に導電性を有するシート状のフィルムを貼り付ける。ここで、この導電性フィルムは第1導電層142の一部である。ここでは、第1導電層142をフィルムの貼り付けによって形成する製造方法を例示したが、この方法に限定されない。例えば、第1導電層142は物理蒸着法(Physical Vapor Deposition; PVD法)によって形成されてもよい。PVD法としては、スパッタリング法、真空蒸着法、電子ビーム蒸着法、めっき法、及び分子線エピタキシー法などを用いることができる。また、導電性を有する樹脂材料が溶解された溶媒を塗布することで第1導電層142を形成してもよい。

#### 【0054】

図9は、本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の表面を粗化する工程を示す図である。図9に示すように、第1樹脂絶縁層130上に形成された第1導電層142の表面を粗化する。第1導電層142表面の粗化は、塩化第二鉄薬液を用いたエッチングによって行うことができる。図9において、粗化領域146を点線で示した。

#### 【0055】

図10は、本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に開口部を形成する工程を示す図である。図10に示すように、外部端子122に対応する位置において、第1導電層142表面の粗化領域146に対してレーザを照射することによって外部端子122を露出する開口部132を形成する。開口部132の形成は、第1導電層142及び第1樹脂絶縁層130に対して一括で行うことができる。開口部132を形成するためのレーザとして、CO<sub>2</sub>レーザを用いることができる。CO<sub>2</sub>レーザは、開口部132のサイズに合わせてスポット径およびエネルギー量が調整され、複数回パルス照射される。ここで、第1導電層142の表面に粗化領域146が形成されていることで、照射されたレーザ光のエネルギーを効率よく第1導電層142に吸収させることができる。レーザ光は外部端子122の内側に照射される。つまり、レーザ光は外部端子122のパターンを外れないように照射される。ただし、半導体装置120の一部を加工したい場合は、意図的にレーザ光の一部が外部端子122の外側にはみ出すように照射してもよい。

#### 【0056】

なお、図10では、開口された第1導電層142の側壁と第1樹脂絶縁層130の側壁とが連続している構造を例示したが、この構造に限定されない。例えば、レーザ照射によって開口する場合、第1導電層142に比べて第1樹脂絶縁層130の方が支持基材100の平面方向(開口径が広がる方向)に大きく後退し、第1導電層142の端部が第1樹脂絶縁層130の端部よりも開口部132の内側方向に突出した構造になってもよい。換言すると、開口部132は第1導電層142が突出したひさし形状になってもよい。また換言すると、開口部132が形成された時点において、第1導電層142の一部の下面が開口部132の内部に露出されてもよい。その際に、開口部132の内側方向に突出した第1導電層142が開口部132の内部において外部端子122の方向に屈曲した形状になってもよい。

#### 【0057】

図11は、本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の表面の粗化された領域を除去し、開口底部の残渣を除去する工程を示す図である。まず、開口部132を形成した後に第1導電層142表面の粗化領域146を除去する。粗化領域146の除去は、酸処理によって行うことができる。粗化領域146の除去に続いて、開口部132の底部の残渣(スミア)を除去する。ここで、残渣の除去(デスマニア)は2段階の工程で行われる。

#### 【0058】

ここで、開口部132の底部の残渣を除去する方法について詳細に説明する。まず、開口部132の底部に対してプラズマ処理を行う。プラズマ処理としては、フッ素(CF<sub>4</sub>)ガス及び酸素(O<sub>2</sub>)ガスを含むプラズマ処理を用いることができる。プラズマ処理は

10

20

30

40

50

、主に開口部 132 の形成時に除去しきれなかった第 1 樹脂絶縁層 130 を除去する。このとき、開口部 132 の形成時に発生した第 1 樹脂絶縁層 130 の変質層を除去することもできる。例えば、開口部 132 をレーザ照射で形成した場合、レーザのエネルギーによって変質した第 1 樹脂絶縁層 130 が開口部 132 の底部に残ることがある。ここで、上記のようにプラズマ処理を行うことで、上記の変質層を効率良く除去することができる。

#### 【0059】

上記のプラズマ処理に続いて、薬液処理を行う。薬液処理としては、少なくとも過マンガン酸ナトリウム又は過マンガン酸カリウムを用いることができる。薬液処理は、上記のプラズマ処理によって除去しきれなかった残渣を除去することができる。例えば、第 1 樹脂絶縁層 130 に含まれ、上記のプラズマ処理では除去することができなかったフィラーを除去することができる。なお、過マンガン酸ナトリウム又は過マンガニ酸カリウムは、残渣をエッティングするための役割を有するエッティング液である。ここで、上記のエッティング液による処理の前に第 1 樹脂絶縁層 130 を膨潤させる膨潤液を用いることもできる。また、上記のエッティング液による処理の後にエッティング液を中和する中和液を用いることもできる。

#### 【0060】

膨潤液を用いることで、樹脂環が拡がるため液の濡れ性が高くなる。これによって、エッティングされない領域の発生を抑制することができる。中和液を用いることで、エッティング液を効率よく除去することができるため、意図しないエッティングの進行を抑制することができる。例えば、エッティング液にアルカリ性の薬液を用いた場合、アルカリ性の薬液は水洗では除去しにくいため、意図しないエッティングが進んでしまうことがある。このような場合であっても、エッティング後に中和液を用いれば、意図しないエッティングの進行を抑制することができる。

#### 【0061】

ここで、膨潤液としては、ジエチレングリコール モノブチルエーテル、エチレングリコールなどの有機溶剤を用いることができる。また、中和液としては、硫酸ヒドロキシルアミンなどの硫酸系の薬液を用いることができる。

#### 【0062】

例えば第 1 樹脂絶縁層 130 に無機材料のフィラーを用いた場合、フィラーはプラズマ処理で除去することができず、残渣となる場合がある。このような場合であっても、プラズマ処理の後に薬液処理を行うことで、フィラーに起因する残渣を除去することができる。

#### 【0063】

図 12 は、本発明の一実施形態に係る半導体パッケージの製造方法において、無電解めっき法によって導電層を形成する工程を示す図である。無電解めっき法によって、上記のデスマニア工程後に露出された外部端子 122 に接続されるめっき層 200 (導電体) を形成する。無電解めっき法は、パラジウム (Pd) コロイドを樹脂上に吸着させて Cu を含む薬液中に浸漬させ、Pd と Cu を置換することで Cu を析出させる方法を用いることができる。ここで、粗化領域 146 を除去してから無電解めっき法によってめっき層 200 を形成することで、第 1 導電層 142 に対するめっき層 200 の密着性を向上させることができる。

#### 【0064】

図 13 は、本発明の一実施形態に係る半導体パッケージの製造方法において、感光性フォトレジストを形成する工程を示す図である。図 13 に示すように、めっき層 200 上に感光性のフォトレジスト 210 を形成する。フォトレジストはスピンドルコート法などの塗布法によって形成される。フォトレジスト形成前に、めっき層 200 とフォトレジスト 210 との密着性を向上させる処理 (HMDS 処理などの疎水化表面処理) をおこなってよい。フォトレジスト 210 は、感光された領域が現像液に対してエッティングされにくくなるネガ型を用いることもでき、逆に感光された領域が現像液によってエッティングされるポジ型を用いることもできる。

10

20

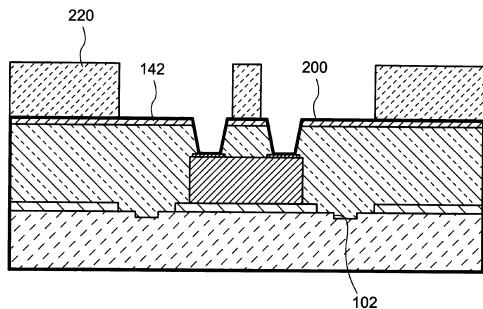

30

40

50

## 【0065】

図14は、本発明の一実施形態に係る半導体パッケージの製造方法において、フォトリソグラフィによって感光性フォトレジストの一部を除去する工程を示す図である。塗布されたフォトレジスト210に対して露光及び現像を行うことで、図1に示す配線140を形成する領域のフォトレジスト210を除去して、図14に示すようなレジストパターン220を形成する。なお、レジストパターン220を形成する露光を行う際に、支持基材100に形成されたアライメントマーカ102を用いて位置合わせを行う。

## 【0066】

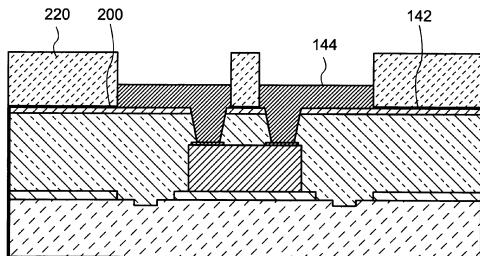

図15は、本発明の一実施形態に係る半導体パッケージの製造方法において、電解めっき法によって導電層を形成する工程を示す図である。レジストパターン220を形成後、無電解めっき法によって形成されためっき層200に通電して電解めっき法を行い、レジストパターン220から露出しているめっき層200をさらに成長させて厚膜化して第2導電層144を形成する。ここで、レジストパターン220下の第1導電層142及びめっき層200は、全面をエッチングすることで除去するため、厚膜化された第2導電層144も膜減りする。したがって、上記の膜減り量を考慮して厚膜化する第2導電層144の量を調整する。

10

## 【0067】

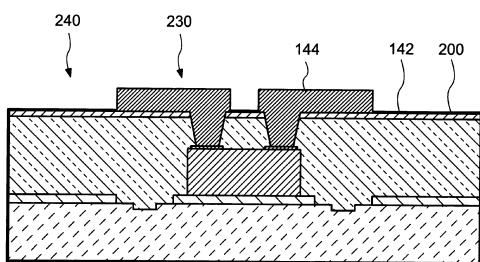

図16は、本発明の一実施形態に係る半導体パッケージの製造方法において、感光性フォトレジストを除去する工程を示す図である。図16に示すように、めっき層200を厚膜化して第2導電層144を形成した後に、レジストパターン220を構成するフォトレジストを有機溶媒により除去する。なお、フォトレジストの除去には、有機溶媒を用いる代わりに、酸素プラズマによるアッシングを用いることもできる。フォトレジストを除去することで、第2導電層144が形成された厚膜領域230及びめっき層200のみが形成された薄膜領域240を得ることができる。なお、厚膜領域230において、第2導電層144はめっき層200上に電解めっき法によって厚膜化されためっき層が形成されているため、厳密には2層で形成されているが、ここではその2層を区別せずに図示した。

20

## 【0068】

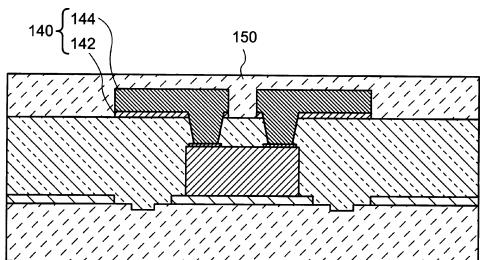

図17は、本発明の一実施形態に係る半導体パッケージの製造方法において、導電層の一部を除去して配線を形成する工程を示す図である。図17に示すように、レジストパターン220によって覆われ、厚膜化されなかった領域のめっき層200及び第1導電層142を除去（エッチング）することで、各々の配線140を電気的に分離する。めっき層200及び第1導電層142のエッチングによって、厚膜領域230の第2導電層144の表面もエッチングされて薄膜化するため、この薄膜化の影響を考慮して第2導電層144の膜厚を設定することが好ましい。この工程におけるエッチングとしては、ウェットエッチングやドライエッチングを使用することができる。なお、図17では、配線140を1層形成する製造方法を例示したが、この方法に限定されず、配線140の上方に絶縁層及び導電層を積層させ、複数の配線層が積層された多層配線を形成してもよい。その際に、配線層を形成する度に新たにアライメントマーカを形成し、上層の配線層形成の際の位置合わせに利用してもよい。

30

## 【0069】

図18は、本発明の一実施形態に係る半導体パッケージの製造方法において、配線を覆う樹脂絶縁層を形成する工程を示す図である。第2樹脂絶縁層150は第1樹脂絶縁層130と同様に、絶縁性のシート状フィルムを貼り付け、加熱・加圧処理を行うことで形成する。ここで、第2樹脂絶縁層150の膜厚は、第2樹脂絶縁層150が配線140を覆うように設定される。つまり、第2樹脂絶縁層150の膜厚は配線140の厚さよりも厚い。なお、第2樹脂絶縁層150は、配線140などによって形成された段差を緩和（平坦化）するため、平坦化膜と呼ばれることがある。

40

## 【0070】

ただし、第2樹脂絶縁層150は、配線140とはんだボール160とが導通することを防ぐことができればよいため、配線140とはんだボール160とのギャップが十分に

50

確保できていればよい。つまり、第2樹脂絶縁層150が配線140の少なくとも上面及び側面に配置されていれば、配線140が配置されていない領域における第2樹脂絶縁層150の膜厚は配線140の厚さよりも薄くてもよい。また、図18の説明では、第2樹脂絶縁層150をスピンドルコート法で形成する製造方法を例示したが、この方法に限定されない。例えば、ディップ法、インクジェット法、蒸着法などの多様な方法で第2樹脂絶縁層150を形成することができる。

#### 【0071】

図19は、本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に配線を露出する開口部を形成する工程を示す図である。図19に示すように、第2樹脂絶縁層150に配線140を露出する開口部152を形成する。開口部152はフォトリソグラフィ及びエッチングによって形成してもよく、第2樹脂絶縁層150として感光性樹脂を用いた場合は露光及び現像によって形成してもよい。ここで、第1樹脂絶縁層130の開口部132に対して行われたデスマニア処理を開口部152に対して行ってもよい。ここで、配線140と同じ工程で形成したアライメントマーカに基づいて位置合わせすることで、開口部152を形成することができる。

#### 【0072】

図20は、本発明の一実施形態に係る半導体パッケージの製造方法において、露出された配線に対応する位置にはんだボールを配置する工程を示す図である。図20に示すように、開口部152に対してはんだボール160を配置する。なお、図20では、1つの開口部152に対して1つのはんだボール160が配置された製造方法を例示したが、この方法に限定されず、1つの開口部152に複数のはんだボール160が配置されてもよい。また、図20では、はんだボール160を開口部152に配置した段階で、はんだボール160が配線140に接触している製造方法を例示したが、この方法に限定されず、図20に示す段階においてははんだボール160が配線140に接触していないなくてもよい。ここで、配線140と同じ工程で形成したアライメントマーカに基づいて位置合わせすることで、はんだボール160を配置することができる。

#### 【0073】

図21は、本発明の一実施形態に係る半導体パッケージの製造方法において、はんだボールをリフローする工程を示す図である。図20に示す状態で熱処理を行うことで、はんだボール160をリフローさせる。リフローとは固体の対象物の少なくとも一部を液化させて流動性を持たせることで、対象物を凹部の内部に流し込むことである。はんだボール160をリフローすることで、開口部152の内部で露出された配線140の上面の全域においてはんだボール160と配線140とを接触させることができる。

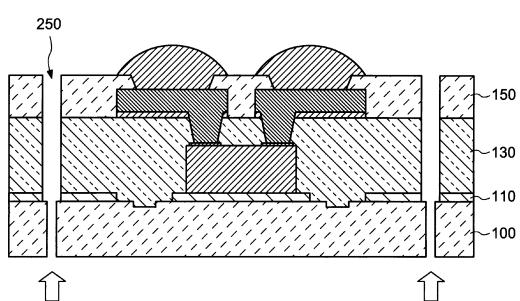

#### 【0074】

図22は、本発明の一実施形態に係る半導体パッケージの製造方法において、樹脂絶縁層に支持基材に達する溝を形成する工程を示す図である。ここでは、ダイシングブレード（例えば、ダイヤモンド製の円形回転刃）を用いて接着層110、第1樹脂絶縁層130、及び第2樹脂絶縁層150に切り込み250を入れる。切り込み250の形成は、ダイシングブレードを高速回転させ、純水で冷却・切削屑の洗い流しを行いながら切断することで行われる。切り込み250は接着層110、第1樹脂絶縁層130、及び第2樹脂絶縁層150に形成されるが、支持基材100に達するようにダイシングし、支持基材100の上面付近に凹部が形成されてもよい。逆に、接着層110の一部、又は接着層110及び第1樹脂絶縁層130の一部を残すようにダイシングしてもよい。

#### 【0075】

図23は、本発明の一実施形態に係る半導体パッケージの製造方法において、支持基材を切断して半導体パッケージを個片化する工程を示す図である。図23に示すように、支持基材100の裏面側（半導体装置120が配置された側とは逆側）からレーザ照射することで半導体パッケージを個片化する。支持基材100に照射するレーザとしては、CO<sub>2</sub>レーザを用いることができる。ここで、支持基材100のアライメントマーカ102に基づいて位置合わせすることで、レーザ照射を行うことができる。レーザは切り込み25

10

20

30

40

50

0よりも狭い領域に対して照射される。

#### 【0076】

なお、ここでは支持基材100の裏面側からレーザ照射をおこなう製造方法を例示したが、この方法に限定されず、切り込み250を通過させて支持基材100の表面側からレーザ照射を行ってもよい。また、レーザを照射する領域が切り込み250が形成された領域よりも狭い製造方法を例示したが、この方法に限定されない。例えば、レーザを切り込み250が形成された領域と同じ領域に照射してもよく、それよりも広い領域に照射してもよい。

#### 【0077】

ここで、支持基材100に金属基材を用いた場合、接着層110、第1樹脂絶縁層130、第2樹脂絶縁層150、及び支持基材100を一括で加工しようとすると、ダイシングブレードの消耗が大きくなり、ダイシングブレードの使用寿命が短くなってしまう。また、金属基材をダイシングブレードで機械的に加工すると、加工端において角の形状が鋭利な「ぱり」が発生してしまい、ハンドリングの際に作業者がけがをする危険性がある。しかし、支持基材100をレーザ加工することで、ダイシングブレードの消耗を避けることができ、支持基材100の加工端の形状を滑らかにすることができます。したがって、特に支持基材100として金属基材を用いた場合、上記のように支持基材100上の構造物をダイシングブレードで加工し、支持基材100をレーザで加工することが好ましい。

#### 【0078】

以上のように、実施形態1に係る半導体パッケージの製造方法によると、半導体装置120を支持基材100に配置する前に、支持基材100にアライメントマーカを形成することで、半導体装置120の配置におけるアライメント精度を向上させることができる。

#### 【0079】

##### 実施形態2

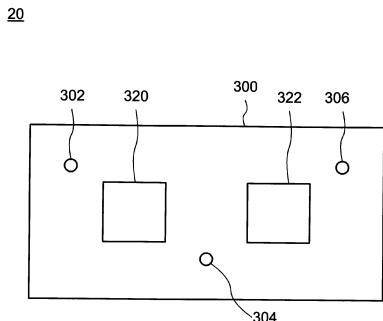

本発明の実施形態2に係る半導体パッケージの製造方法において、半導体装置を配置する際のアライメント方法について、図24を参照しながら詳細に説明する。図24は、本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。図24では、説明の便宜上、支持基材(300)、半導体装置(320、322)、及びアライメントマーカ(302、304、306)のみを表示したが、図1Aと同様の構造とすることができます。

#### 【0080】

##### [半導体パッケージ20の構造]

図24に示すように、半導体パッケージ20は、支持基材300上において、第1半導体装置320及び第2半導体装置322の周囲に第1アライメントマーカ302(第1凹部)、第2アライメントマーカ304(第2凹部)、及び第3アライメントマーカ306(第3凹部)が設けられている。第1アライメントマーカ302及び第2アライメントマーカ304は第1半導体装置320の対角に対応する位置に設けられており、第2アライメントマーカ304及び第3アライメントマーカ306は第2半導体装置322の対角に対応する位置に設けられている。換言すると、第1半導体装置320と第2半導体装置322との間に第2アライメントマーカ304が設けられている。

#### 【0081】

##### [半導体パッケージ20の製造工程におけるアライメント方法]

図24を用いて、第1半導体装置320及び第2半導体装置322のアライメント方法について詳細に説明する。まず、図2に示した方法と同様の方法で支持基材300に第1アライメントマーカ302、第2アライメントマーカ304、及び第3アライメントマーカ306を形成する。次に、図6に示した方法と同様の方法で第1アライメントマーカ302及び第2アライメントマーカ304に基づいて位置合わせを行って第1半導体装置320を配置し、第2アライメントマーカ304及び第3アライメントマーカ306に基づいて位置合わせを行って第2半導体装置322を配置する。そして、第1半導体装置320及び第2半導体装置322を覆う第1樹脂絶縁層130を形成する。上記以外の製造工

10

20

30

40

50

程は、図2～図23と同様の方法で製造することができる。

#### 【0082】

上記のように、半導体パッケージ20の製造工程では、第1半導体装置320のアライメントマーカと第2半導体装置322のアライメントマーカとを共有させる。換言すると、半導体パッケージ20の製造工程における半導体装置(320、322)を配置する際に用いられるアライメントマーカの数は、実施形態1の半導体パッケージ10の製造工程における半導体装置120を配置する際に用いられるアライメントマーカの数よりも少ない。また換言すると、実施形態1の半導体パッケージ10の製造方法では、1つの半導体装置120を配置する際に2つのアライメントマーカ102を用いていたが、半導体パッケージ20の製造方法では、2つの半導体装置(320、322)を配置する際に3つのアライメントマーカ(302、304、306)を用いる。つまり、半導体パッケージ20の製造方法では、1つの半導体装置を配置する際に1.5のアライメントマーカを用いて行うことができる。

10

#### 【0083】

半導体パッケージ20の製造工程において、各々の半導体パッケージ20を個片化する際に、第2アライメントマーカ304が第1半導体装置320側又は第2半導体装置322側のいずれかに含まれるように支持基材300が分断されてもよい。又は、各々の半導体パッケージ20を個片化する際に、第2アライメントマーカ304が2つに分断され、第1半導体装置320側に第2アライメントマーカ304の一部が含まれ、第2半導体装置322側に第2アライメントマーカ304の残りの部分が含まれるように支持基材300が分断されてもよい。又は、各々の半導体パッケージ20の個片化の際に、第2アライメントマーカ304が消失してもよい。つまり、個片化された半導体パッケージ20に含まれるアライメントマーカの数が2つ未満であってもよい。

20

#### 【0084】

以上のように、実施形態2に係る半導体パッケージ20によると、半導体装置を配置するためのアライメントマーカの数を低減することができる。したがって、アライメントマーカを個別に形成する製造方法の場合に、アライメントを形成する工程を短縮することができる。上記の構成は、アライメントマーカを配置する領域が十分に確保することが難しい場合にも有効である。

#### 【0085】

30

##### 実施形態3

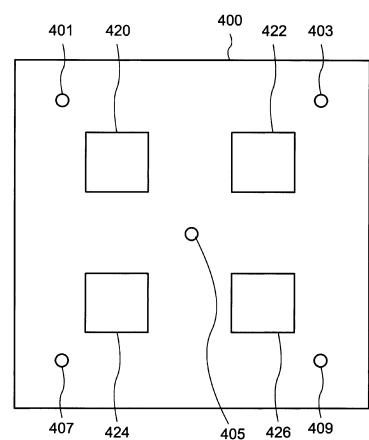

本発明の実施形態3に係る半導体パッケージの製造方法において、半導体装置を配置する際のアライメント方法について、図25を参照しながら詳細に説明する。図25は、本発明の一実施形態に係るアライメントマーカと半導体装置との位置関係を示す平面模式図である。図25では、説明の便宜上、支持基材(400)、半導体装置(420、422、424、426)、及びアライメントマーカ(401、403、405、407、409)のみを表示したが、図1Aと同様の構造とすることができます。

#### 【0086】

##### [半導体パッケージ30の構造]

図25に示すように、半導体パッケージ30は、支持基材400上において、第1半導体装置420、第2半導体装置422、第3半導体装置424、及び第4半導体装置426の周囲に第1アライメントマーカ401、第2アライメントマーカ403、第3アライメントマーカ405、第4アライメントマーカ407、及び第5アライメントマーカ409が設けられている。

40

#### 【0087】

第1アライメントマーカ401及び第3アライメントマーカ405は第1半導体装置420の対角に対応する位置に設けられている。第2アライメントマーカ403及び第3アライメントマーカ405は第2半導体装置422の対角に対応する位置に設けられている。第3アライメントマーカ405及び第4アライメントマーカ407は第3半導体装置424の対角に対応する位置に設けられている。第3アライメントマーカ405及び第5ア

50

ライメントマーカ 409 は第 4 半導体装置 426 の対角に対応する位置に設けられている。換言すると、第 1 半導体装置 420 と、第 2 半導体装置 422 と、第 3 半導体装置 424 と、第 4 半導体装置 426 との間に第 3 アライメントマーカ 405 が設けられている。

#### 【0088】

[半導体パッケージ 30 の製造工程におけるアライメント方法]

図 25 を用いて、第 1 半導体装置 420 、第 2 半導体装置 422 、第 3 半導体装置 424 、及び第 4 半導体装置 426 のアライメント方法について詳細に説明する。まず、図 2 に示した方法と同様の方法で支持基材 400 に第 1 アライメントマーカ 401 、第 2 アライメントマーカ 403 、第 3 アライメントマーカ 405 、第 4 アライメントマーカ 407 、及び第 5 アライメントマーカ 409 を形成する。次に、図 6 に示した方法と同様の方法で第 1 アライメントマーカ 401 及び第 3 アライメントマーカ 405 に基づいて位置合わせを行って第 1 半導体装置 420 を配置し、第 2 アライメントマーカ 403 及び第 3 アライメントマーカ 405 に基づいて位置合わせを行って第 2 半導体装置 422 を配置し、第 3 アライメントマーカ 405 及び第 4 アライメントマーカ 407 に基づいて位置合わせを行って第 3 半導体装置 424 を配置し、第 3 アライメントマーカ 405 及び第 5 アライメントマーカ 409 に基づいて位置合わせを行って第 4 半導体装置 426 を配置する。そして、第 1 半導体装置 420 、第 2 半導体装置 422 、第 3 半導体装置 424 、及び第 4 半導体装置 426 を覆う第 1 樹脂絶縁層 130 を形成する。上記以外の製造工程は、図 2 ~ 図 23 と同様の方法で製造することができる。

#### 【0089】

上記のように、半導体パッケージ 30 の製造工程では、第 1 半導体装置 420 のアライメントマーカ、第 2 半導体装置 422 のアライメントマーカ、第 3 半導体装置 424 のアライメントマーカ、及び第 4 半導体装置 426 のアライメントマーカを共有させる。換言すると、半導体パッケージ 30 の製造工程における半導体装置 (420 、 422 、 424 、 426 ) を配置する際に用いられるアライメントマーカの数は、実施形態 1 の半導体パッケージ 10 の製造工程における半導体装置 120 を配置する際に用いられるアライメントマーカの数よりも少ない。また換言すると、実施形態 1 の半導体パッケージ 10 の製造方法では、1つの半導体装置 120 を配置する際に 2 つのアライメントマーカ 102 を用いていたが、半導体パッケージ 30 の製造方法では、4つの半導体装置 (420 、 422 、 424 、 426 ) を配置する際に 5 つのアライメントマーカ (401 、 403 、 405 、 407 、 409 ) を用いる。つまり、半導体パッケージ 30 の製造方法では、1つの半導体装置を配置する際に 1.25 のアライメントマーカを用いて行うことができる。

#### 【0090】

半導体パッケージ 30 の製造工程において、各々の半導体パッケージ 30 を個片化する際に、第 3 アライメントマーカ 405 が第 1 半導体装置 420 側、第 2 半導体装置 422 側、第 3 半導体装置 424 側、又は第 4 半導体装置 426 側のいずれかに含まれるように支持基材 400 が分断されてもよい。又は、各々の半導体パッケージ 30 を個片化する際に、第 3 アライメントマーカ 405 を 2 ~ 4 つに分断してもよい。又は、各々の半導体パッケージ 30 の個片化の際に、第 3 アライメントマーカ 405 が消失してもよい。つまり、個片化された半導体パッケージ 30 に含まれるアライメントマーカの数が 2 つ未満であつてもよい。

#### 【0091】

以上のように、実施形態 3 に係る半導体パッケージ 30 によると、半導体装置を配置するためのアライメントマーカの数を低減することができる。したがって、アライメントマーカを個別に形成する製造方法の場合に、アライメントを形成する工程を短縮することができる。

#### 【0092】

なお、本発明は上記実施の形態に限られたものではなく、要旨を逸脱しない範囲で適宜変更することが可能である。

#### 【符号の説明】

10

20

30

40

50

## 【0093】

- 10、20、30：半導体パッケージ

100、300、400：支持基材

102、302、304、306、401、403、405、407、409：アライメントマーカ

104：粗化領域

110：接着層

112：開口部

120、320、322、420、422、424、426：半導体装置

122：外部端子

130：第1樹脂絶縁層

132、152：開口部

140：配線

142：第1導電層

144：第2導電層

146：粗化領域

150：第2樹脂絶縁層

160：はんだボール

200：めっき層

210：フォトレジスト

220：レジストパターン

230：厚膜領域

240：薄膜領域

250：切り込み

10

20

【図1A】

【図1B】

【 図 2 】

【図3】

【 义 4 】

【図5】

【図6】

【圖 8】

【図10】

( 9 )

〔 図 1 1 〕

【図12】

【図14】

【図13】

【図15】

【図16】

【図18】

【図17】

【図19】

【図20】

【図22】

【図21】

【図23】

【図24】

【図25】

---

フロントページの続き

(56)参考文献 特開2012-253390(JP,A)

特開2013-069741(JP,A)

特開2003-179193(JP,A)

実開昭62-163962(JP,U)

特開2014-179648(JP,A)

米国特許出願公開第2008/0083994(US,A1)

中国特許出願公開第1501490(CN,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/54

H01L 23/00 - 23/04

H01L 23/06 - 23/26

H01L 23/50

H05K 1/00 - 1/02