**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

(51) Int. Cl.<sup>5</sup>

H01L 27/11

(11) 공개번호 특 1994-0018988

(43) 공개일자 1994년 08월 19일

|            |                                                                                      |

|------------|--------------------------------------------------------------------------------------|

| (21) 출원번호  | 특 1994-0000828                                                                       |

| (22) 출원일자  | 1994년 01월 18일                                                                        |

| (30) 우선권주장 | 007,879 1993년 01월 22일 미국(US)                                                         |

| (71) 출원인   | 모토로라 인코포레이티드(Motorola, Inc.) 빈센트 비. 인그라시아<br>미합중국, 일리노이 60196, 샤움버그, 이스트 앨공퀸 로드 1303 |

| (72) 발명자   | 페리 에이취. 펠리 3세<br>미합중국, 텍사스 78759, 오스틴, 베이럿지 테라스 6815                                 |

| (74) 대리인   | 이병호, 최달용                                                                             |

**심사청구 : 없음**

**(54) 어드레스 변이 검출을 발생시키는 어드레스 버퍼(An address buffer for generating an address transition detection)**

**요약**

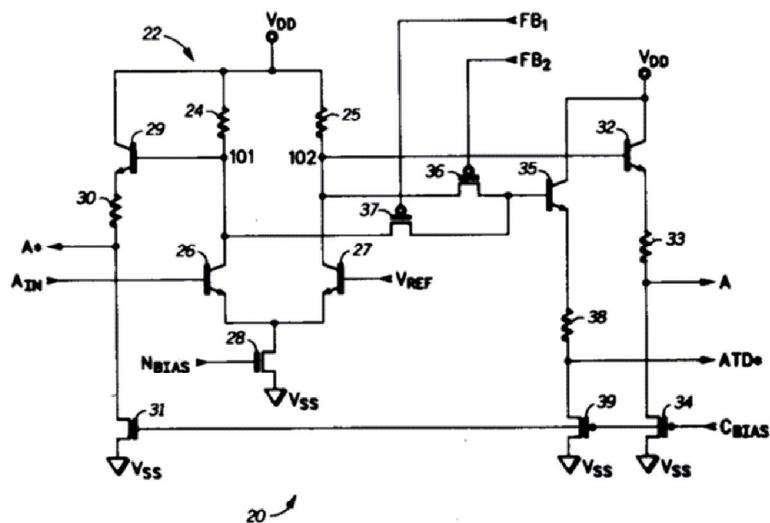

어드레스 버퍼(20)는 하나의 논리 상태로부터 다른 상태로 변이하는 어드레스 신호에 응답해서 ATD펄스를 제공한다. 어드레스 버퍼(20)는 자동 증폭기(22), 에미터-풀로워 트랜지스터(35), 2개의 P채널 트랜지스터(36 및 37)를 포함한다. 각각의 P채널 트랜지스터의 제1전류 전극이 자동 증폭기(22)의 출력 노드(101 및 102)에 연결되고, 각각의 P채널 트랜지스터(36 및 37)의 제2전류 전극은 에미터-풀로워 트랜지스터(35)의 베이스에 연결된다. 지연 제어 신호는 ATD펄스를 에미터-풀로워 트랜지스터(35)의 에미터에서 공급되도록 하기 위해 레벨 변환기 회로(60)의 의해 P채널 트랜지스터(36 및 37)의 게이트에 공급된다. 어드레스 버퍼의 ATD펄스를 발생시키는 것은 ATD펄스를 매우 빨리 발생시킨다.

**대표도**

**도1**

**명세서**

[발명의 명칭]

어드레스 변이 검출을 발생시키는 어드레스 버퍼(An address buffer for generating an address transition detection)

[도면의 간단한 설명]

제1도는 본 발명에 따라 ATD발생을 갖는 어드레스 버퍼의 개략적인 다이어그램 예시도.

본 내용은 요부공개 건이므로 전문내용을 수록하지 않았음

**(57) 청구의 범위**

**청구항 1**

제1및 2논리 상태를 갖는 입력 신호를 수신하는 입력 단자를 가지며 제1및 2출력 노드(101, 102)를 갖는 차동증폭기(22)와, 상기 차동 증폭기(22)의 제1출력 노드(101)에 결합된 제1전류 전극, 제2전류 전극, 및 제1제어 신호를 수신하는 게이트를 갖는 제1MOS트랜지스터(37)와, 상기 차동 증폭기(22)의 상기 제2출력 노드(102)에 결합된 제1전류 전극, 제2전류 전극, 및 제2제어 신호를 수신하는 게이트를 갖는 제2MOS트랜지스터(36)와, 상기 제1및 2MOS트랜지스터(37, 36)의 제2전류 전극에 결합된 베이스, 및 제1논리 상태로부터 제2논리 상태로 변이하는 입력 신호에 응답하여 출력 펄스를 공급하는 에미터를 갖는 에미터-풀로워 트랜지스터(35)를 구비하는 것을 특징으로 하는 입력 버퍼(20).

**청구항 2**

제1전력 공급 전압 단자 및 제1바이폴리 트랜지스터(26)의 콜렉터간에 결합된 제1저항기(24)의 상기 제1전력 공급 전압 단자 및 제2바이폴리 트랜지스터(27)의 콜렉터간에 결합된 제2저항기(25)를 가지며, 제1 및 2논리상태를 갖는 어드레스 신호를 수신하는 상기 차동 증폭기(22)와, 상기 제1바이폴리 트랜지스터(26)의 콜렉터에 결합된 제1전류 전극, 제2전류 전극, 및 제1지연 제어 신호를 수신하는 게이트를 갖는 제1MOS트랜지스터(37)와, 상기 제2바이폴리 트랜지스터(27)의 콜렉터에 결합된 제1전류 전극,

제2전류 전극, 및 제2지연 제어 신호를 수신하는 게이트를 갖는 제2MOS트랜지스터(36)와, 제1전력 공급 전압 단자에 결합된 콜렉터, 상기 제1및 2MOS트랜지스터(37,36)의 제2전류 전극에 결합된 베이스, 및 ATD펄스를 공급하는 에미터를 갖는 제1에미터-풀로워 트랜지스터(35)와, 전력 공급 전압 단자에 결합된 콜렉터, 차동 증폭기(22)의 제1출력 노드(101)에 결합된 베이스, 및 제1버퍼된 논리 신호를 공급하는 에미터를 갖는 제2에미터-풀로워 트랜지스터(29)와, 전력 공급 전압 단자에 결합된 콜렉터, 상기 차동 증폭기(22)의 제2출력 노드(102)에 결합된 베이스, 및 버퍼된 논리 신호를 공급하는 에미터를 갖는 제3에미터-풀로워 트랜지스터(32)와, 제1및 2버퍼된 논리 신호를 수신하고 제1및 2지연 제어 신호를 공급하는 레벨 변환기(60)를 구비하는 것을 특징으로 하며, ATD(address transition detection, 어드레스 변이 검출)펄스를 발생시키는 어드레스 버퍼(20).

### 청구항 3

전력 공급 전압 단자 및 제1바이폴리 트랜지스터(26)의 콜렉터간에 결합된 제1저항기(24)와 상기 전력 공급 전압 단자 및 제2바이폴라 트랜지스터(27)의 콜렉터간에 결합된 제2저항기(25)를 가지며, 제1및 2논리 상태를 갖는 ECL레벨 어드레스 신호를 수신하는 상기 차동 증폭기(22)와, 상기 제1바이폴라 트랜지스터(26)의 콜렉터에 결합된 제1전류 전극, 제2전류 전극, 및 제1지연 제어 신호를 수신하는 게이트를 갖는 제1p채널 트랜지스터(37)와, 상기 제2바이폴라 트랜지스터(27)의 콜렉터에 결합된 제1전류 전극, 제2전류 전극, 및 제2지연 제어 신호를 수신하는 게이트를 갖는 제2p채널 트랜지스터(36)와, 상기 전력 공급 전압 단자에 결합된 콜렉터, 상기 제1및 2MOS트랜지스터(37,36)의 제2전류 전극에 결합된 베이스, 및 ECL레벨 어드레스 신호가 제1논리 상태로부터 제2논리 상태로 변이될 때, ATD펄스를 공급하는 에미터를 갖는 제1에미터-풀로워 트랜지스터(35)와, 전력 공급 전압 단자에 결합된 콜렉터, 상기 제1바이폴라 트랜지스터(26)의 콜렉터에 결합된 베이스, 및 제1버퍼된 논리 신호를 공급하는 에미터를 갖는 제2에미터-풀로워 트랜지스터(35)와, 전력 공급 전압 단자에 결합된 콜렉터, 상기 제1바이폴라 트랜지스터(26)의 콜렉터에 결합된 베이스, 및 제1버퍼된 논리 신호를 공급하는 에미터를 갖는 제2에미터-풀로워 트랜지스터(29)와, 전력 공급 전압 단자에 결합된 콜렉터, 상기 제2바이폴라 트랜지스터(27)의 콜렉터에 결합된 베이스, 및 제2버퍼된 논리 신호를 공급하는 에미터를 갖는 제3에미터-풀로워 트랜지스터(32)를 구비하는 것을 특징으로 하며, ATD(address transition detection, 어드레스 변이 검출) 발생을 갖는 어드레스 버퍼(20).

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

### 도면

#### 도면1