(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6066617号

(P6066617)

(45) 発行日 平成29年1月25日(2017.1.25)

(24) 登録日 平成29年1月6日(2017.1.6)

(51) Int.Cl.

F 1

|                    |                  |      |       |     |

|--------------------|------------------|------|-------|-----|

| <b>H01L 27/146</b> | <b>(2006.01)</b> | H01L | 27/14 | A   |

| <b>H04N 5/369</b>  | <b>(2011.01)</b> | H04N | 5/335 | 690 |

| <b>H04N 5/357</b>  | <b>(2011.01)</b> | H04N | 5/335 | 570 |

| <b>H04N 5/374</b>  | <b>(2011.01)</b> | H04N | 5/335 | 740 |

請求項の数 14 (全 22 頁)

(21) 出願番号

特願2012-178278 (P2012-178278)

(22) 出願日

平成24年8月10日 (2012.8.10)

(65) 公開番号

特開2014-36200 (P2014-36200A)

(43) 公開日

平成26年2月24日 (2014.2.24)

審査請求日

平成27年6月30日 (2015.6.30)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 岩田 旬史

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72) 発明者 乾 文洋

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置および撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

信号電荷を多数キャリアとする第一導電型の第一半導体領域と、前記第一半導体領域と P N 接合を成し、前記信号電荷を少数キャリアとする第二導電型の第二半導体領域と、を半導体基板の表面から裏面へ向かってこの順で有する光電変換素子を有する画素が配列された画素部を備え、

所定方向に沿って隣り合って配された前記画素の各々の前記第一半導体領域が、絶縁分離領域を介することなく第二導電型の第三半導体領域で互いに分離されており、前記画素部の画素の各々の前記第二半導体領域が、前記第三半導体領域と電気的に連続し、前記第三半導体領域を介して前記第二半導体領域に基準電位を付与する基準コンタクトが前記表面に設けられた撮像装置であって、

前記画素部における前記基準コンタクトの数が、前記画素部における画素の数の1/4未満であり、前記画素部は前記基準コンタクトの近傍に位置する第一種画素と第二種画素とを有し、

前記第一種画素の第一半導体領域、前記基準コンタクト、及び前記第二種画素の第一半導体領域とが前記所定方向に沿って、間にトランジスタを挟むことなくこの順に隣り合い、

前記表面と前記第一種画素の前記P N 接合との距離は、前記表面と前記第二種画素の前記P N 接合との距離よりも小さく、

前記基準コンタクトと前記第一種画素の前記第一半導体領域との距離が、前記基準コン

タクトと前記第二種画素の前記第一半導体領域との距離よりも小さいことを特徴とする撮像装置。

【請求項 2】

前記画素部には、前記第一種画素の信号電荷に基づく電気信号を生成する第一増幅トランジスタと、前記第二種画素の信号電荷に基づく電気信号を生成する第二増幅トランジスタと、が設けられている請求項 1 に記載の撮像装置。

【請求項 3】

前記第一増幅トランジスタは前記第一種画素を含む第一画素群の画素の信号電荷に基づく電気信号を生成し、前記第二増幅トランジスタは前記第二種画素を含む第二画素群の画素の信号電荷に基づく電気信号を生成する請求項 2 に記載の撮像装置。 10

【請求項 4】

前記第一画素群の各画素が第一浮遊拡散領域に共通に接続されており、前記第二画素群の各画素が第二浮遊拡散領域に共通に接続されている請求項 3 に記載の撮像装置。

【請求項 5】

前記第一増幅トランジスタから前記電気信号を出力する第一出力コンタクトと前記基準コンタクトとの距離が、前記第二増幅トランジスタから前記電気信号を出力する第二出力コンタクトと前記基準コンタクトとの距離よりも小さい請求項 2 乃至 4 のいずれか 1 項に記載の撮像装置。

【請求項 6】

前記画素部には、前記第一種画素の信号電荷をリセットする第一リセットトランジスタと、前記第一種画素の信号電荷をリセットする第二リセットトランジスタと、が設けられており、前記第一増幅トランジスタと前記第二リセットトランジスタは共通のコンタクトに接続されている請求項 2 乃至 5 のいずれか 1 項に記載の撮像装置。 20

【請求項 7】

前記基準コンタクトは、前記第三半導体領域の、前記第一種画素の前記第一半導体領域と前記第二種画素の前記第一半導体領域との間に位置する部分の上に設けられている請求項 1 乃至 6 のいずれか 1 項に記載の撮像装置。

【請求項 8】

前記画素の各々は信号電荷を転送する転送ゲートを含み、前記第一種画素の前記第一半導体領域と前記第二種画素の前記第一半導体領域とが並ぶ方向において、前記第一種画素の転送ゲートの転送の向きが、前記第二種画素の転送ゲートの転送の向きとは逆である請求項 1 乃至 7 のいずれか 1 項に記載の撮像装置。 30

【請求項 9】

前記画素部は第三種画素を有し、前記第一種画素は第一波長を主透過波長とするカラーフィルタを前記半導体基板に対して前記表面側に含み、前記第二種画素は前記第一波長よりも長い第二波長を主透過波長とするカラーフィルタを前記半導体基板の前記表面側に含み、前記第三種画素は前記第二波長よりも長い第三波長を主透過波長とするカラーフィルタを前記半導体基板の前記表面側に含む請求項 1 乃至 8 のいずれか 1 項に記載の撮像装置。 40

【請求項 10】

前記画素の各々は、ポリシリコンゲート電極を有し信号電荷を転送する転送ゲートを含み、前記画素部の少なくとも一部の区域において、前記画素部の中央から周辺へ向かって、前記第三種画素の前記第一半導体領域と、前記第三種画素の前記転送ゲートと、前記第一種画素の前記第一半導体領域がこの順に並んでいる請求項 9 に記載の撮像装置。

【請求項 11】

前記半導体基板の前記表面側に光導波路が設けられている請求項 1 乃至 10 のいずれか 1 項に記載の撮像装置。

【請求項 12】

前記画素部における前記基準コンタクトの数が、前記画素部における画素数の 1 / 8 以下である請求項 1 乃至 11 のいずれか 1 項に記載の撮像装置。 50

**【請求項 1 3】**

請求項 1 乃至 1 2 のいずれか 1 項に記載の撮像装置と、前記撮像装置で得られた画像を表示する表示装置と、を備える撮像システム。

**【請求項 1 4】**

請求項 1 乃至 1 3 のいずれか 1 項に記載の撮像装置と、非テレセントリック光学系または物体側テレセントリック光学系と、を備える撮像システム。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

基準電位を供給するためのコンタクトを有する撮像装置に関する。 10

**【背景技術】****【0 0 0 2】**

半導体装置である撮像装置の半導体基板内では、信号電荷を多数キャリアとする第一導電型の半導体領域に蓄積する信号電荷を、信号電荷を少数キャリアとする第二導電型の半導体領域で画素毎に区分している。半導体基板上には、第二導電型の半導体領域に基準電位を供給するための基準コンタクトが設けられる。特許文献 1, 2 には、基板コンタクトを、各画素に均等に配置するのではなく、特定の画素に偏って配置することが記載されている。

**【先行技術文献】****【特許文献】**

20

**【0 0 0 3】**

【特許文献 1】特開 2009 - 289872 号公報

【特許文献 2】特開 2011 - 14773 号公報

**【発明の概要】****【発明が解決しようとする課題】****【0 0 0 4】**

基準コンタクトに近い画素は基準コンタクトから遠い画素に比べてノイズが大きくなる傾向にある。そこで本発明は、基準コンタクトによるノイズの影響を低減して、画質の良い画像が得られる撮像装置を提供することを目的とする。

**【課題を解決するための手段】**

30

**【0 0 0 5】**

上記課題を解決するための手段は、信号電荷を多数キャリアとする第一導電型の第一半導体領域と、前記第一半導体領域と P N 接合を成し、前記信号電荷を少数キャリアとする第二導電型の第二半導体領域と、を半導体基板の表面から裏面へ向かってこの順で有する光電変換素子を有する画素が配列された画素部を備え、所定方向に沿って隣り合って配された前記画素の各々の前記第一半導体領域が、絶縁分離領域を介すことなく第二導電型の第三半導体領域で互いに分離されており、前記画素部の画素の各々の前記第二半導体領域が、前記第三半導体領域と電気的に連続し、前記第三半導体領域を介して前記第二半導体領域に基準電位を付与する基準コンタクトが前記表面に設けられた撮像装置であって、前記画素部における前記基準コンタクトの数が、前記画素部における画素の数の 1 / 4 未満であり、前記画素部は前記基準コンタクトの近傍に位置する第一種画素と第二種画素とを有し、前記第一種画素の第一半導体領域、前記基準コンタクト、及び前記第二種画素の第一半導体領域とが前記所定方向に沿って、間にトランジスタを挟むことなくこの順に隣り合い、前記表面と前記第一種画素の前記 P N 接合との距離は、前記表面と前記第二種画素の前記 P N 接合との距離よりも小さく、前記基準コンタクトと前記第一種画素の前記第一半導体領域との距離が、前記基準コンタクトと前記第二種画素の前記第一半導体領域との距離よりも小さいことを特徴とする。 40

**【発明の効果】****【0 0 0 6】**

本発明の撮像装置によれば、画質の良い画像が得られる。 50

## 【図面の簡単な説明】

## 【0007】

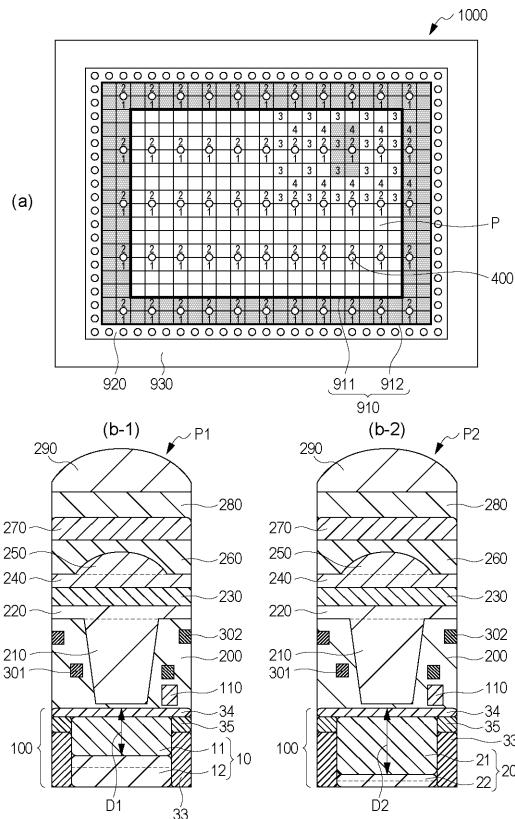

【図1】(a) 撮像装置の一例の平面模式図、(b-1)甲種画素の一例の断面模式図、(b-2)乙種画素の一例の断面模式図。

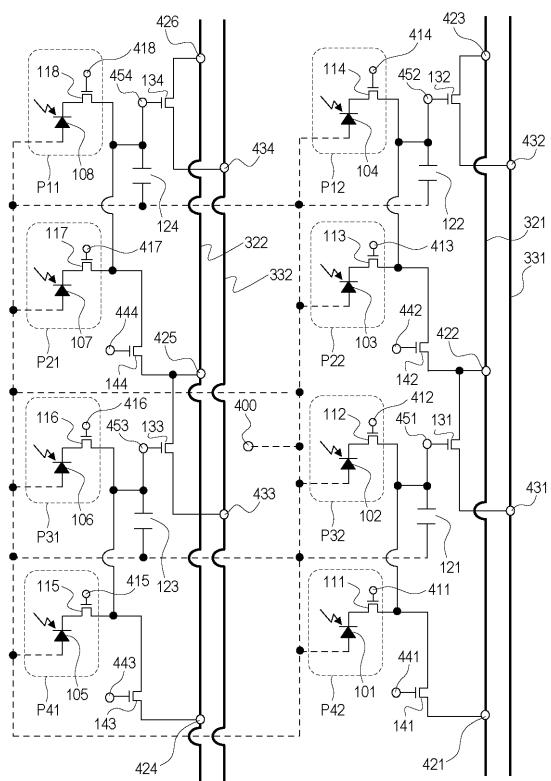

【図2】画素部の一例の等価回路図。

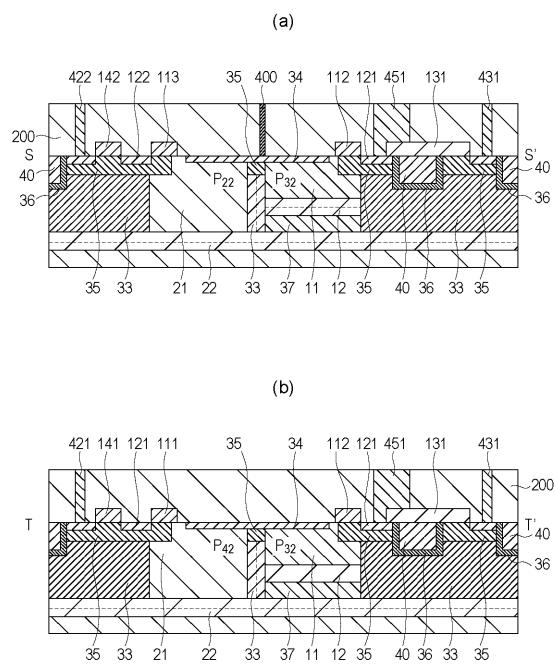

【図3】画素部の一例の平面模式図。

【図4】画素部の一例の断面模式図。

【図5】画素部の一例の断面模式図。

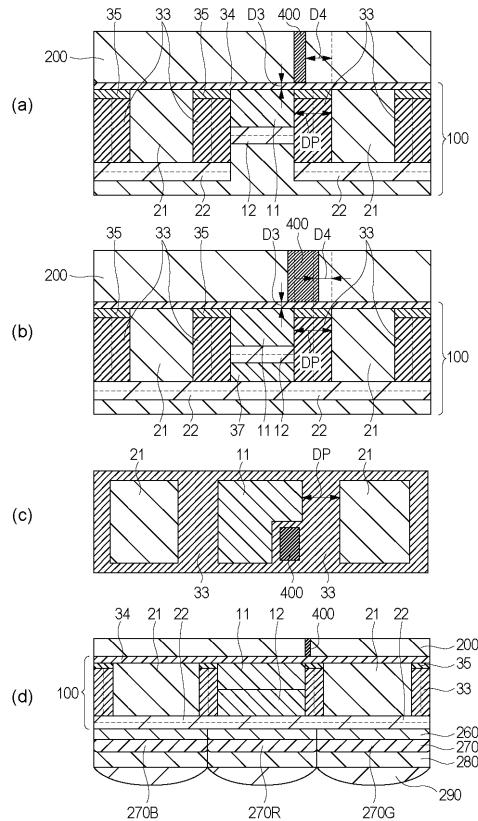

【図6】画素部の一例の断面模式図。

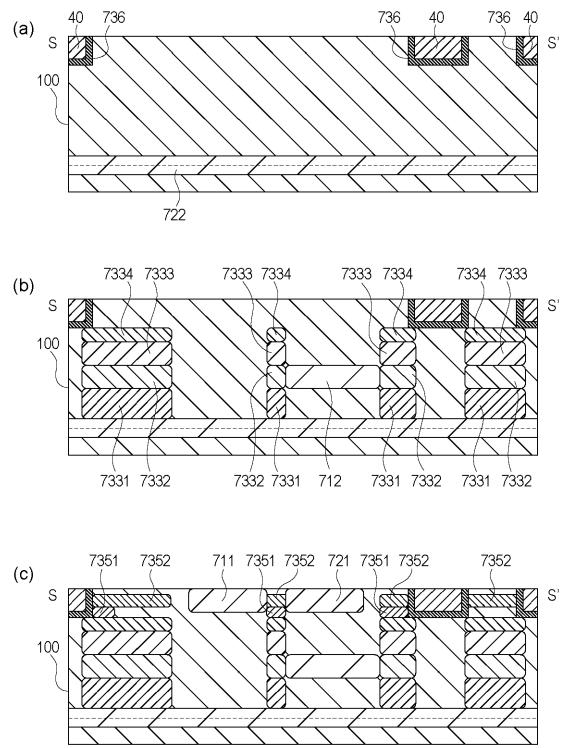

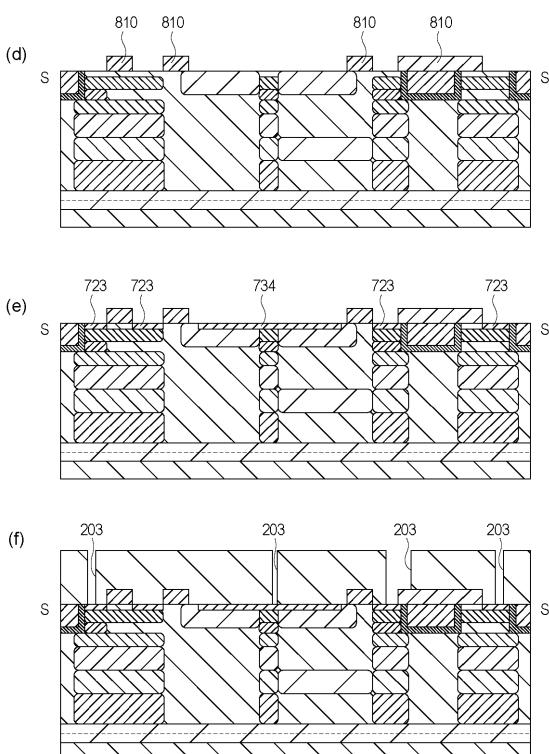

【図7】撮像装置の製造方法の一例の断面模式図。

10

【図8】撮像装置の製造方法の一例の断面模式図。

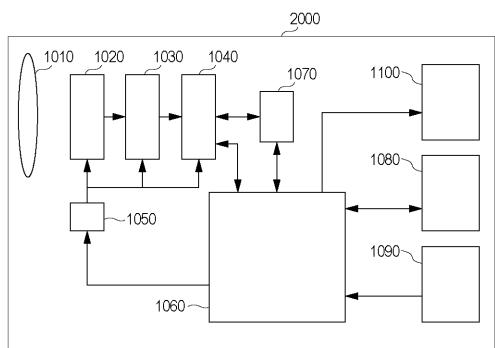

【図9】撮像システムの一例のブロック図。

## 【発明を実施するための形態】

## 【0008】

以下、図面を用いて実施形態の一例としての撮像装置を説明する。

## 【0009】

図1(a)は撮像装置1000の一例の平面模式図である。本例の撮像装置1000は画素部910と中間部920と周辺部930を有する。画素部910には複数の画素Pが二次元状に設けられている。また、画素部910には画素Pで得られた信号電荷から電気信号を生成する画素回路を設けることもできる。画素部910は受光画素部911と遮光画素部912を含むことができる。受光画素部911で得られた電気信号に基づいて画像が形成され、遮光画素部912で得られた電気信号はノイズ低減等の信号処理に利用される。受光画素部911が撮像部として機能する。図1(a)では、受光画素部911には14行×19列の計266画素が、遮光画素部912には計148画素がそれぞれ設けられており、全部で414画素の構成となっている。実際の撮像装置における画素数は例えば数十万～数千万でありうる。本例の遮光画素部912は受光画素部911を囲むように4辺に設けられているが、隣接する2辺のみ、対向する2辺のみ、あるいは1辺のみに設けることもできる。周辺部930には画素回路を駆動する駆動回路や受光画素部911で得られた電気信号を処理する信号処理回路等のいわゆる周辺回路が設けられる。周辺部930には周辺回路に加えて、アライメントマークや外部との通信を行う電極パッドが設けられる。また、周辺部930と画素部910の間には画素部910を囲むように中間部920が設けられているが、中間部920を省略することもできる。

20

## 【0010】

図1(b-1)、(b-2)は受光画素部911における1つの画素Pの断面模式図を示している。1つの画素Pは半導体基板100内に設けられた1つの光電変換素子を有する。半導体基板100は表面と不図示の裏面を有し、本例では表面が受光面となる。本例の画素部910は、光電変換素子の構造が異なる少なくとも2種類の画素を含む。具体的には、図1(b-1)に示した甲種画素P1と、図1(b-2)に示した乙種画素P2である。例えば、図1(a)において、「1」または「4」と記載した画素が甲種画素であり、「2」または「3」と記載した画素が乙種画素である。無印の画素については乙種画素でも甲種画素でもどちらでもよい。

30

## 【0011】

甲種画素P1の光電変換素子10は信号電荷を多数キャリアとする第一導電型の第一半導体領域11を有する。また、光電変換素子10は信号電荷を少数キャリアとする第二導電型の第二半導体領域12を有する。半導体基板100の表面から裏面へ向かって第一半導体領域11と第二半導体領域12とがこの順で配されている。つまり、半導体基板100の表面と第二半導体領域12との間に第一半導体領域11が位置する。第二半導体領域12は第一半導体領域11に連続する。詳細には、第一半導体領域11と第二半導体領域12はPN接合を成して連続する。つまり、第二半導体領域12は、第一半導体領域11とはPN接合を成さないような、半導体基板100のさらに深部にある第二導電型の半導

40

50

体領域とは区別される。

【0012】

乙種画素P2の光電変換素子20は信号電荷を多数キャリアとする第一導電型の第一半導体領域21を有する。また、光電変換素子20は信号電荷を少数キャリアとする第二導電型の第二半導体領域22を有する。半導体基板100の表面から裏面へ向かって第一半導体領域21と第二半導体領域22とがこの順で配されている。つまり、半導体基板100の表面と第二半導体領域22との間に第一半導体領域21が位置する。第二半導体領域22は第一半導体領域21に連続する。詳細には、第一半導体領域21と第二半導体領域22は、第一半導体領域21とはPN接合を成さないような、半導体基板100のさらに深部にある第二導電型の半導体領域とは区別される。10

【0013】

本例では信号電荷は電子であり、第一導電型がN型、第二導電型がP型であるが、信号電荷が正孔である場合には、第一導電型がP型、第二導電型がN型である。なお、信号電荷そのものではなく、信号電荷と正負が同じ電荷を多数キャリアとする半導体領域も第一導電型であり、信号電荷と正負が逆の電荷を少数キャリアとする半導体領域も第二導電型である。

【0014】

甲種画素P1の光電変換素子10と乙種画素P2の光電変換素子20は、第一半導体領域と第二半導体領域の、半導体基板100の表面からの深さが異なる。乙種画素P2の第一半導体領域21は甲種画素P1の第一半導体領域11よりも半導体基板100の表面から深い位置まで存在している。甲種画素P1の第二半導体領域12が乙種画素P2の第二半導体領域22よりも半導体基板100の表面から浅い位置に存在している。半導体基板100の表面から第二半導体領域12までの距離を第一の距離D1、半導体基板100の表面から第二半導体領域22までの距離を第二の距離D2とすると、第一の距離D1は第二の距離D2( $D_1 < D_2$ )よりも小さい。第一の距離D1の取りうる範囲は例えば1~3μmであり、第二の距離D2の取りうる範囲は例えば2~5μmである。第一半導体領域と第二半導体領域の境界であるPN接合面は、甲種画素P1が乙種画素P2よりも半導体基板100の近くに位置しうる。20

【0015】

第二半導体領域12、22は、深さ方向において連続した第二導電型の半導体領域内の第二導電型の不純物濃度のピーク濃度を示す部分を有しうる。図1(b)ではピーク濃度を示す部分を点線で示しており、ここが実質的なポテンシャル障壁として機能する。第二半導体領域12、22がピーク濃度を示す位置も、甲種画素P1が乙種画素P2よりも半導体基板100の近くに位置しうる。30

【0016】

半導体基板100内における光電変換素子10以外の構成が、甲種画素P1と乙種画素P2で異なる必要はない。第一半導体領域11、21の周囲には第二導電型の第三半導体領域33が設けられている。第三半導体領域33は画素間に配されており、各画素の光電変換素子をPN接合によって分離(接合分離)している。本例では、半導体基板100の表面と第一半導体領域11、21との間には、表面シールド領域として第二導電型の第四半導体領域34が設けられている。第四半導体領域34により、光電変換素子10、20はいわゆる埋め込み型フォトダイオードとなっている。本例では第三半導体領域33と第四半導体領域34の間には中間領域として第五半導体領域35が設けられている。40

【0017】

第二半導体領域12、22と第三半導体領域33は第二導電型の半導体領域として電気的に連続しており、これらは実質的に等電位となりうる。また、第三半導体領域33と第四半導体領域34は第五半導体領域35を介して電気的に連続しており、これらは実質的に等電位となりうる。したがって、半導体基板100の表面から第二半導体領域12、22まで、第三半導体領域33、第四半導体領域34および第五半導体領域35を介して電50

気的に連続している。なお、中間領域としての第五半導体領域35は典型的には第二導電型であるが、第三半導体領域33に基準電位を付与できる程度であれば、不純物濃度の低い第一導電型の半導体領域であってもよい。第五半導体領域35を省略して第三半導体領域33と第四半導体領域34とが接する構成としてもよい。

#### 【0018】

本例では、半導体基板100の表面側には表面へ向かって順に、第一レンズ290、カラーフィルタ270、第二レンズ250、低屈折率膜230、光導波路210および絶縁膜200が設けられている。さらに、第一レンズ290とカラーフィルタ270の間には第一中間膜280が、カラーフィルタ270と第二レンズ250の間には第二中間膜260が設けられている。第二レンズ250と低屈折率膜230との間には第一高屈折率膜240が設けられ、低屈折率膜230と光導波路210との間には第二高屈折率膜220が設けられている。10

#### 【0019】

光導波路210と第二高屈折率膜220、第一高屈折率膜240と第二レンズ250は、それぞれ同じ材料で一体的に形成してもよい。低屈折率膜230は第一高屈折率膜240および第二高屈折率膜220より低い屈折率を有する。低屈折率膜230を省略して第二高屈折率膜220と第一高屈折率膜240とが接してもよく、第二高屈折率膜220と第一高屈折率膜240と同じ材料で一体的に形成してもよい。光導波路210の周囲には光導波路210より低屈折率を有する低屈折率層を少なくとも含んで構成された絶縁膜200が設けられている。光導波路210をコア、低屈折率層をクラッドとして、光導波路210内を低損失で光が伝搬することができる。この絶縁膜200内には配線用に複数の導電層301、302が設けられている。20

#### 【0020】

絶縁膜200の低屈折率層は導電層301、302を絶縁するための層間絶縁層としても機能しうる。絶縁膜200は、導電層301、302に含まれる金属の拡散防止層も含むことができ。拡散防止層の屈折率は光導波路の屈折率以上であってもよい。第一レンズ290や第二レンズ250、第一高屈折率膜240、第二高屈折率膜220などの構成部材は層間の光の反射を抑制するための反射防止層を含みうる。絶縁膜200と半導体基板100との間には、MOSゲートやMOSトランジスタの、ポリシリコンゲート電極110が設けられる。30

#### 【0021】

画素部910ではRGBの3原色のカラーフィルタがベイヤー配列に従ってカラーフィルタアレイを構成している。また画素部910では、複数の画素Pによって、光導波路アレイ、第一レンズアレイ、第二レンズアレイを構成している。第一中間膜280および第二中間膜260は画素部910に渡って延在して平坦化層として機能する。遮光画素部912における画素は光電変換素子を遮光する遮光膜(不図示)を有する。画素の構成はこの例に限定されることはなく、これらの少なくともいずれかを省略することもできるし、光学的要素あるいは機械的要素、化学的要素を付加することもできる。本例ではいわゆる表面照射型のCMOSセンサを挙げているが、表面照射型でなくて裏面照射型であってもよいし、CMOSセンサでなくCCDセンサであってもよい。40

#### 【0022】

撮像装置1000はカメラやカメラ機能付き情報端末などの撮像システムに組み込まれる。図9は撮像システム2000の一例のブロック図である。撮像システム2000は、撮像部1020へ光を導く光学系1010を備える。光学系1010はレンズやシャッター、絞りを含み得る。また、撮像システム2000は撮像部1020から得られた電気信号を処理する信号処理部1030と、信号処理部1030で処理された信号に基づいて画像信号を生成する画像処理部1040を含み得る。信号処理部1030はアナログ信号処理部とアナログ/デジタル変換部、デジタル信号処理部とを含み得る。半導体装置としての撮像装置1000は、少なくとも撮像部1020を含むが、さらに信号処理部1030の一部あるいは全部を含んでいてもよい。撮像装置1000から得られる画像信号はアナ50

ログ信号であってもデジタル信号であってもよい。撮像システム 2000 は撮像部 1020 と信号処理部 1030 と画像処理部 1040 の同期をとるためのタイミング発生部 1050 や、各種演算を行って撮像システム 2000 を制御する制御部 1060 、演算のためにデータを記憶する記憶部 1070 を備える。撮像システム 2000 は、画像データを記録する記録部 1080 、撮像システム 2000 を操作するためのインターフェースを有する操作部 1090 、撮影された画像を表示する表示部 1100 を備える。

#### 【0023】

図 2 には図 1 (a) の受光画素部 911においてハッチングをつけて示した単位構造として 4 行 2 列の 8 画素分の等価回路図を示している。以下、1 行目 1 列目の画素を  $P_{1,1}$  、 $i$  行目  $j$  列目の画素を  $P_{i,j}$  と表記する。

10

#### 【0024】

各画素の光電変換素子 101 ~ 108 はここではフォトダイオードであり、図 1 (b - 1) で説明した光電変換素子 10 または図 1 (b - 2) で説明した光電変換素子 20 の構造を有しうる。第一半導体領域 11、21 がフォトダイオードのカソードとして、第二半導体領域 12、22 がフォトダイオードのアノードとして機能しうる。図 2 において点線で示した電気経路が第三半導体領域 33 に相当する。詳細は後述するが、本例においては、画素  $P_{1,2}$ 、 $P_{3,2}$  が甲種画素あり、画素  $P_{1,1}$ 、 $P_{2,1}$ 、 $P_{3,1}$ 、 $P_{4,1}$ 、 $P_{2,2}$ 、 $P_{4,2}$  が乙種画素である。

#### 【0025】

各画素は、光電変換素子 101 ~ 108 に接続された転送ゲート 111 ~ 118 を有しており、各画素の光電変換素子 101 ~ 108 は、転送ゲート 111 ~ 118 を介して適切な浮遊拡散領域 121 ~ 128 に接続されている。転送ゲート 111 ~ 118 は、光電変換素子 101 ~ 108 で収集された信号電荷を、光電変換素子 101 ~ 108 から対応する浮遊拡散領域 121 ~ 124 へ転送する。転送ゲート 111 ~ 118 と光電変換素子 101 ~ 108 と浮遊拡散領域 121 ~ 124 は、光電変換素子 101 ~ 108 をソース、浮遊拡散領域 121 ~ 124 をドレインとするトランジスタを構成している。本例では、画素  $P_{3,2}$  と画素  $P_{4,2}$  が第一浮遊拡散領域 121 に接続されており、画素  $P_{1,2}$  と画素  $P_{2,2}$  が第二浮遊拡散領域 122 に接続されている。画素  $P_{3,1}$  と画素  $P_{4,1}$  が第三浮遊拡散領域 123 に接続されており、画素  $P_{1,1}$  と画素  $P_{2,1}$  が第四浮遊拡散領域 124 に接続されている。このように、複数の転送ゲートに 1 つの浮遊拡散領域を共通に接続することができるが、全ての画素について、転送ゲート毎に別々の浮遊拡散領域を接続することもできる。

20

#### 【0026】

本例の撮像装置 1000 は、画素部 910 の画素回路が増幅トランジスタを含む、いわゆる画素増幅型の撮像装置である。画素部 910 には複数の増幅トランジスタ 131 ~ 134 が設けられている。各増幅トランジスタ 131 ~ 134 は、対応する画素の光電変換素子 101 ~ 108 の信号電荷に基づく電気信号を生成する。画素回路は画素群ごとに設けられている。本例の画素群は、画素  $P_{3,2}$  と画素  $P_{4,2}$  からなる第一画素群、画素  $P_{1,2}$  と画素  $P_{2,2}$  からなる第二画素群、画素  $P_{3,1}$  と画素  $P_{4,1}$  からなる第三画素群、画素  $P_{1,1}$  と画素  $P_{2,1}$  からなる第四画素群が 4 行 2 列の 8 画素を構成している。

30

#### 【0027】

画素  $P_{3,2}$  と画素  $P_{4,2}$  に対応する第一浮遊拡散領域 121 は第一増幅トランジスタ 131 のゲートに接続されている。画素  $P_{1,2}$  と画素  $P_{2,2}$  に対応する第二浮遊拡散領域 122 は第二増幅トランジスタ 132 のゲートに接続されている。画素  $P_{3,1}$  と画素  $P_{4,1}$  に対応する第三浮遊拡散領域 123 は第三増幅トランジスタ 133 のゲートに接続されている。画素  $P_{1,1}$  と画素  $P_{2,1}$  に対応する第四浮遊拡散領域 124 は第四増幅トランジスタ 134 のゲートに接続されている。

40

#### 【0028】

第一浮遊拡散領域 121 は第一リセットトランジスタ 141 のソースに接続されている。第二浮遊拡散領域 122 は第二リセットトランジスタ 142 のソースに接続されている

50

。第三浮遊拡散領域 123 は第三リセットトランジスタ 143 のソースに接続されている。

。第四浮遊拡散領域 124 は第四リセットトランジスタ 144 のソースに接続されている。

。

### 【 0029 】

本例の画素回路は 2 画素からなる画素群が 1 つの増幅トランジスタとリセットトランジスタを共有する画素共有構造である。複数の画素の信号電荷を浮遊拡散領域で加算して、加算された信号電荷に基づく電気信号を生成することができる。あるいは、画素毎に転送のタイミングを制御することにより、1 つの浮遊拡散領域で画素毎の信号電荷に基づく電気信号を生成することもできる。4 画素からなる画素群で 1 つの増幅トランジスタを共有する構造を採用することもできるし、画素共有構造を採用せずに画素毎に増幅トランジスタを設けることもできる。また、転送ゲートを含む 3 トランジスタの構成であるが、増幅トランジスタのソースに接続された選択トランジスタを含む、4 トランジスタの構成としてもよい。画素部 910 における増幅トランジスタの数は画素部 910 における画素数と同じであってもよいが、画素部 910 における画素数よりも小さくてもよく、画素部における画素数の半分以下であってもよい。本例では増幅トランジスタの数は画素部における画素数の半分である。

### 【 0030 】

図 2において白抜き丸で示した電気的接続は、配線と半導体素子の接続領域、いわゆるコンタクトである。典型的に、配線と半導体素子との接続は、アルミニウムや銅を主成分とする配線パターンと半導体基板との間に設けられたタンゲステンなどからなるコンタクトプラグが半導体基板 100 にオーミック接合することで実現される。したがってコンタクトの位置はコンタクトプラグの位置に対応している。なお、黒塗り丸で示した電気的接続は半導体基板内の半導体同士の接続を示している。なお、半導体同士の接続は P N 接合であってもよいし、濃度の異なる同一導電型の領域同士の接合であってもよい。

### 【 0031 】

第三半導体領域 33 には、配線の一部である基準線から基準コンタクト 400 を介して基準電位が付与される。第三半導体領域 33 に接続されたフォトダイオードのアノードである第二半導体領域 12、22 にもまた基準電位が付与される。基準電位は光電変換素子のアノード電位や、画素回路のトランジスタのボディ電位として用いられる。基準電位は典型的には固定電位であるが、基準電位の変調を行ってもよい。固定電位としては、例えば接地電位であるが負電位あるいは正電位としてゲートバイアスを印加することもできる。

### 【 0032 】

第三半導体領域 33 が半導体基板である場合には基準コンタクト 400 を基板コンタクトと呼ぶことができ、第三半導体領域 33 が半導体基板 100 に形成されたウェルである場合には基準コンタクト 400 をウェルコンタクトと呼ぶことができる。

### 【 0033 】

第一リセットトランジスタ 141 のドレインは第一電源コンタクト 421 を介して電源電位を供給する電源線 321 に接続されている。第一増幅トランジスタ 131 のドレインは第二電源コンタクト 422 を介して、電源線 321 に接続されている。第一増幅トランジスタ 131 のソースは第一出力コンタクト 431 を介して出力線 331 に接続されている。第一増幅トランジスタ 131 のドレインは第二浮遊拡散領域 122 をソースとする第二リセットトランジスタ 142 のドレインを兼ねている。第二増幅トランジスタ 132 のドレインは第三電源コンタクト 423 を介して、電源電位を供給する電源線 321 に接続されている。第二増幅トランジスタ 132 のソースは第二出力コンタクト 432 を介して出力線 331 に接続されている。第三増幅トランジスタ 133 と第四増幅トランジスタ 134 については、第一増幅トランジスタ 131 と第二増幅トランジスタ 132 の関係と同様であるので、説明を省略する。第一増幅トランジスタ 131、第二増幅トランジスタ 132、第三増幅トランジスタ 133、第四増幅トランジスタ 134 の各々に対応する電源コンタクトが第一電源コンタクト 421、第二電源コンタクト 422、第三電源コンタク

10

20

30

40

50

ト423、第四電源コンタクト424である。第一増幅トランジスタ131、第二増幅トランジスタ132、第三増幅トランジスタ133、第四増幅トランジスタ134の各々に対応する出力コンタクトが第一出力コンタクト431、第二出力コンタクト432、第三出力コンタクト433、第四出力コンタクト434である。増幅トランジスタ131～134の各々のゲート電極（増幅ゲート電極）と、浮遊拡散領域121～124は、それぞれ、第一接続コンタクト451、第二接続コンタクト452、第三接続コンタクト453、第四接続コンタクト454を介して接続されている。各画素～144のゲート電極（リセットゲート電極）はリセットゲートプラグ441に対応する転送ゲート111～118のゲート電極（転送ゲート電極）は転送ゲートプラグ411～418を介して、転送信号を供給する第一走査線（不図示）に接続されている。各リセットトランジスタ141～144を介して、リセット信号を供給する第二走査線（不図示）に接続されている。

10

#### 【0034】

図3(a)は図2で示した繰り返し単位を2つ並べた16画素を含む区域における半導体基板100の表面から浅い部分（浅部）の平面模式図である。図3(b)は、同じ区域の図3(a)よりも半導体基板100の表面から深い部分（深部）の平面模式図である。ただし、図3(a)および図3(b)に示した部材の全てが同一平面内に位置するわけではない。1列目と3列目、2列目と4列目は等価である。図4(a)は図3(a)のM-M'線における断面模式図であり、図4(b)は図3(a)のN-N'線における断面模式図である。図5(a)は図3(a)のS-S'線における断面模式図であり、図4(b)は図3(a)のT-T'線における断面模式図である。図3～図5において、図2で説明した要素と同じ要素については、同一の符号を付しており、相互に参照することができるため、図毎の詳細な説明を省略する。

20

#### 【0035】

図3(a)には、第一導電型の半導体領域である、第一半導体領域11、21、浮遊拡散領域121～124、各トランジスタのソース領域およびドレイン領域を示している。トランジスタを示す符号は、そのゲート電極に付している。典型的なゲート電極はポリシリコンゲート電極である。

#### 【0036】

図3(a)に示す様に、画素P<sub>12</sub>、P<sub>32</sub>は浅い第一半導体領域11を有する甲種画素である。画素P<sub>11</sub>、P<sub>21</sub>、P<sub>31</sub>、P<sub>41</sub>、P<sub>22</sub>、P<sub>42</sub>は深い第一半導体領域21を有する乙種画素である。

30

#### 【0037】

半導体基板100内では、行方向および列方向に交差する方向（斜め方向）において、第一半導体領域、転送チャネル領域、浮遊拡散領域がこの順で周期的に配置されている。転送チャネル領域は転送ゲート電極の下に位置する。

#### 【0038】

図3(a)において転送ゲート電極に示した矢印は転送チャネル領域における信号電荷の転送方向を示している。図3(a)から理解されるように、各画素の転送方向は図面上で右上向きまたは右下向きである。行方向成分と列方向成分に転送方向を分解すると、行方向に関してはいずれの転送方向も図面で右向きであるが、列方向に関しては奇数行に配された画素の転送方向は下向き、偶数行に配された画素の転送方向は上向きである。つまり、1行目と2行目、3行目と4行目の同じ列同士の画素は、それらの信号電荷が互いに近づく向きに転送され、2行目と3行目の同じ列同士の画素は、それらの信号電荷が互いに遠ざかる向きに転送される。

40

#### 【0039】

図3(a)には、半導体領域を絶縁体によって分離（絶縁分離）してなる絶縁分離領域40を示している。本例の絶縁分離領域40は絶縁体の大部分が半導体基板100に埋め込まれたSTI(Shallow Trench Isolation)構造である。絶縁分離領域40はLOCOS(Local Oxidation Of Silicon)構造でもよい。あるいは特開2005-347325号公報に記載されているように、

50

絶縁体の大部分が半導体基板 100 の表面から突出した構造であってもよい。本例では、絶縁分離領域 40 は列間に設けられており、列方向に沿って絶縁分離領域 40 が延在している。図 5 (a)、(b) に示す様に、絶縁分離領域 40 の絶縁体と接する半導体基板 100 の表面には、界面シールド領域として第二導電型の第六半導体領域 36 が設けられている。

#### 【0040】

図 3 (b) には、第二導電型の半導体領域である、第二半導体領域 12、22 および第三半導体領域 33 を示している。なお、図 3 (b) には、図 3 (a) との位置の対比を簡易にするために半導体基板 100 の表面におけるゲート電極の位置を点線にて示している。

10

#### 【0041】

図 3 (b) に示す様に、画素  $P_{1,2}$ 、 $P_{3,2}$  は浅い第二半導体領域 12 を有する甲種画素である。画素  $P_{1,1}$ 、 $P_{2,1}$ 、 $P_{3,1}$ 、 $P_{4,1}$ 、 $P_{2,2}$ 、 $P_{4,2}$  は深い第二半導体領域 22 を有する乙種画素である。図 3 (b) から理解されるように、第三半導体領域 33 は、行方向および列方向に沿って矩形格子状に設けられている。第三半導体領域 33 の位置は、連続した第二導電型の半導体領域内の平面方向において第二導電型の不純物濃度のピーク濃度を示す位置で代表される。図 4 (a) ではピーク濃度を示す位置を点線で示しており、ここが実質的なポテンシャル障壁として機能する。

#### 【0042】

図 3 (a) と図 3 (b) との相互参照から理解されるように、列間では、半導体基板 100 の浅部には絶縁分離領域 40 が設けられており、半導体基板 100 の深部には接合分離領域が設けられている。本例では、行間には絶縁分離領域は設けられておらず、接合分離領域のみが配されているが、これに限らず、行間に絶縁分離領域を設けることもできるし、列間の絶縁分離領域を省略することもできる。

20

#### 【0043】

図 4 (a) に示す様に、本例では、乙種画素である画素  $P_{1,1}$ 、 $P_{2,1}$ 、 $P_{3,1}$ 、 $P_{4,1}$ 、 $P_{2,2}$ 、 $P_{4,2}$  の第二半導体領域 22 は全て同じ深さに設けられている。しかし、これらの画素の或る一部の画素の第二半導体領域 22 を別の一部の画素の第二半導体領域 22 よりも深い位置に設けることもできる。例えば、画素  $P_{2,1}$ 、 $P_{4,1}$  の第二半導体領域 22 を画素  $P_{1,1}$ 、 $P_{3,1}$ 、 $P_{2,2}$ 、 $P_{4,2}$  の第二半導体領域 22 よりも深い位置に設けることもできる。

30

#### 【0044】

図 4 (a) に示す様に、画素  $P_{1,2}$ 、 $P_{3,2}$  の第二半導体領域 12 より深部には、第一導電型の第七半導体領域 37 が位置している。さらに第七半導体領域 37 の下には、画素  $P_{2,2}$  と  $P_{4,2}$  の第二半導体領域 22 に連続し、画素  $P_{2,2}$  と  $P_{4,2}$  の第二半導体領域 22 と同じ深さで位置する第二導電型の半導体領域が位置している。しかし、この半導体領域は画素  $P_{1,2}$  や画素  $P_{3,2}$  の第一半導体領域 11 とは PN 接合を成していない。そのため、画素  $P_{1,2}$ 、 $P_{3,2}$  の第二半導体領域としては機能しない。図 6 (a) に示す様に、このような第二導電型の半導体領域が画素  $P_{1,2}$ 、 $P_{3,2}$  の下に存在しないようにすることもできる。

40

#### 【0045】

図 5 (a) に示す様に、浮遊拡散領域やソース領域、ドレイン領域は第三半導体領域 33 の上に配されている。浮遊拡散領域やソース領域、ドレイン領域と第三半導体領域の間に中間領域としての第五半導体領域 35 が設けられている。この第五半導体領域 35 は、ポテンシャルバリアやパンチスルーストッパ、閾値設定などを目的として、トランジスタのチャネル領域、ソース領域やドレイン領域の濃度の調整を行うために設けられる。その導電型や濃度分布は適宜設定できるが、典型的には第五半導体領域 35 の大部分は第二導電型であり、第一導電型であっても第一半導体領域 11、12 や浮遊拡散領域、ソース領域、ドレイン領域よりも不純物濃度は低い。少なくとも第五半導体領域 35 の第三半導体領域 33 と第四半導体領域 34 との間に位置する部分は第二導電型であることが望ましい

50

。

#### 【 0 0 4 6 】

図3(a)には図2で説明した各種コンタクトの位置を示している。ゲート電極に接続されたゲートプラグは絶縁分離領域40の上に位置している。また、半導体基板100に接続された各コンタクトは第三半導体領域33上に設けられている。基準コンタクト400は第三半導体領域33を介して第二半導体領域12と電気的に接続している。なお、半導体基板100に接続されたコンタクトのうち、基準コンタクト400以外のコンタクト(接続コンタクト、電源コンタクト、出力コンタクト)は接合分離領域上に設けられている。ただし、第三半導体領域33これらコンタクトの間には、ソース領域やドレイン領域などの第一導電型の半導体領域が設けられている。そのため、基準コンタクト400以外のコンタクトは第三半導体領域33および第二半導体領域12と電気的に分離されている。本例の接続コンタクトはいわゆるシェアードコンタクトプラグによって構成されている。10

#### 【 0 0 4 7 】

基準コンタクト400は少なくとも2つの光電変換素子の近傍に設けられる。詳細には、基準コンタクト400は第三半導体領域33や第四半導体領域34、第五半導体領域35を介在させて、光電変換素子10、20の第一半導体領域11、21の近傍に位置している。光電変換素子10、20が画素の主たる部材であるから、以下、光電変換素子10、20を画素として説明する。

#### 【 0 0 4 8 】

本例では複数の画素を、基準コンタクト400との位置関係に着目して、近傍画素と非近傍画素に分類し、近傍画素をさらに一次近傍画素と二次近傍画素と三次近傍画素に分類する。本例では、一次近傍画素が甲種画素であり、二次近傍画素が乙種画素である。また、三次近傍画素は乙種画素であり、非近傍画素では甲種画素と乙種画素が混在している。20

#### 【 0 0 4 9 】

一次近傍画素は基準コンタクト400に最も近い第一半導体領域11を有する画素である。二次近傍画素は、基準コンタクト400に2番目に近い第一半導体領域21を有する画素である。二次近傍画素は一次近傍画素に隣り合う画素である。基準コンタクト400から一次近傍画素の第一半導体領域11までの距離を第三の距離D3、基準コンタクト400から二次近傍画素の第一半導体領域21までの距離を第四の距離D4とすると、第三の距離D3は第四の距離D4( $D_3 < D_4$ )よりも小さい。なお、図4(a)では第三の距離D3と第四の距離D4とを、その実質的な違いである平面方向での距離で示している。実際には半導体基板100の深さ方向において、第四半導体領域34や第五半導体領域35の厚みもこれらの距離として考慮される。なお、図4(a)で示した平面方向での距離D3はゼロであってもよい。その場合、図6(a)に示す様に、基準コンタクト400と第一半導体領域11との距離D3は、第四半導体領域34の厚みに依存する。三次近傍画素は、一次近傍画素に隣り合う画素の中で二次近傍画素以外の画素であって、二次近傍画素よりも基準コンタクト400からの距離が大きい第一半導体領域21を有する画素である。或る画素が一次～三次近傍画素あるいは非近傍画素のいずれであるかは、その画素に最も近い基準コンタクト400を基準とするべきである。非近傍画素は一次近傍画素に隣り合わない画素である。ここで、画素 $P_{i,j}$ に隣り合う画素を画素 $P_{g,h}$ とすると、 $g = i - 1, i, i + 1$ および $h = j - 1, j, j + 1$ を満たす $P_{i,j}$ 以外の画素であり、本例では画素部の最外周を除いてどの画素にも8つ存在する。3040

#### 【 0 0 5 0 】

図3(a)の例において、基準コンタクト400は、画素 $P_{3,2}$ と画素 $P_{2,2}$ との間に設けられている。このように本例では2行目と3行目の間に基準コンタクト400が設けられている。画素 $P_{3,2}$ が一次近傍画素に該当し、画素 $P_{2,2}$ が二次近傍画素に該当する。画素 $P_{2,1}$ 、 $P_{3,1}$ 、 $P_{4,1}$ 、 $P_{4,2}$ が三次近傍画素に該当する。画素 $P_{1,1}$ 、 $P_{1,2}$ が非近傍画素に該当する。

#### 【 0 0 5 1 】

10

20

30

40

50

本例では、基準コンタクト 400 は第三半導体領域 33 上に設けられる。つまり、第三半導体領域 33 は互いに隣り合う第一半導体領域 11 と第一半導体領域 21 の間に位置するため、平面的に見ると、基準コンタクト 400 は互いに隣り合う第一半導体領域 11 と第一半導体領域 21 の間に位置する。つまり、間に基準コンタクト 400 が位置する互いに隣接する第一半導体領域 11、21 を有する画素に関して、より基準コンタクト 400 に近い方の第一半導体領域 11 を有する画素が一次近傍画素である。より基準コンタクト 400 から遠い方の第一半導体領域 21 を有する画素が二次近傍画素である。

#### 【0052】

本例では基準コンタクト 400 は絶縁分離領域 40 の無い行間に設けられているが、列間に設けることもできる。基準コンタクト 400 を例えば画素  $P_{3,2}$  と画素  $P_{3,1}$  との間に設けることもできる。その場合には、基準コンタクト 400 と画素  $P_{3,2}$  との距離は、基準コンタクト 400 と画素  $P_{3,1}$  との距離よりも小さくするとよい。2 行目と 3 行目の間であっても、画素  $P_{2,1}$  と画素  $P_{3,1}$  との間には基準コンタクト 400 が設けられない。

10

#### 【0053】

図 6 (b) に示す様に、基準コンタクト 400 の一部が第一半導体領域 11 の上に位置してもよい。この場合も、基準コンタクト 400 と第一半導体領域 11 との距離  $D_3$  は、第四半導体領域 34 の厚みに依存する。基準コンタクト 400 を第一半導体領域 11 の上のみに設けることもできるが、受光量の低下やノイズの増加、第二半導体領域 12 までの抵抗の増大などの観点からこれを避けることが望ましい。また、図 6 (b) に示す様に、基準コンタクト 400 の一部が第三半導体領域 33 のポテンシャル障壁よりも第一半導体領域 21 側に位置してもよいが、乙種画素でのノイズの増加が懸念されるため、極力これを避けることが望ましい。一次近傍画素の第一半導体領域 11 と二次近傍画素の第一半導体領域 21 との距離を  $D_P$  とすると、第四の距離  $D_4$  は  $D_P / 2$  よりも大きいことが望ましい。基準コンタクト 400 の径は  $D_P / 2$  よりも小さくすると良い。距離  $D_P$  は 1.0  $\mu m$  以下でありうる。図 6 (c) は変形例の平面模式図であるが、甲種画素の第一半導体領域 11 の面積を小さくして、空いたスペースに基準コンタクトを設けることができる。

20

#### 【0054】

図 1 (a) に示した白抜き丸は画素部 910 における基準コンタクト 400 の大まかな位置を示している。図 1 (a) から理解されるように、画素部 910 における基準コンタクト 400 の数は、画素部 910 における画素数よりも少なくできる。受光画素部 911 におけるにおける基準コンタクト 400 の数が受光画素部 911 における画素数よりも少ないことが画質の向上に効果的である。図 1 (a) では、画素部 910 において 8 画素に 1 つの割合で基準コンタクト 400 を設けており、全 414 画素に対して、基準コンタクト 400 の数は 1/4 未満の 55 個となっている。画素部 910 における基準コンタクト 400 の数は、画素部 910 における画素数の 1/4 未満、1/8 以下、さらには 1/16 以下であってもよい。例えば 100 ~ 10000 画素に 1 つの割合で基準コンタクトを設けることもできる。例えば一つの基準コンタクト 400 で 100 ~ 10000  $\mu m^2$  の区域に存在する画素に基準電位を付与できる。基準コンタクト 400 を増やすほどシェーディングを低減できる。本例では、基準コンタクト 400 は矩形格子状に配置されているが、斜方格子状、六角格子状あるいは正方格子状に配置してもよい。

30

#### 【0055】

遮光画素部 912 の構造は受光画素部 911 の構造に極力近いことが好ましいため、受光画素部 911 と遮光画素部 912 とで基準コンタクト 400 の密度（数 / 面積）を近づけるとよい。つまり遮光画素部 912 における基準コンタクト 400 の数もまた受光画素部 911 における画素数よりも少ないことが好ましい。基準コンタクト 400 の配列が周期的であることが画素の特性均一化にとって好ましい。

40

#### 【0056】

図 1 (a) に示した例では、図示はしないが、第二半導体領域 12 が画素部 910 から中間部 920 に延在しており、中間部 920 にも第二半導体領域 12 と電気的に接続する

50

基準コンタクト 400 が設けられている。中間部 920 の基準コンタクト 400 の数は 86 であり、画素部 910 の基準コンタクト 400 の数よりも多くなっている。

#### 【0057】

中間部 920 に設けられた基準コンタクト 400 の数は画素部 910 の基準コンタクト 400 の数よりも大きくてよい。また、中間部 920 に設けられた基準コンタクト 400 の密度は画素部 910 の基準コンタクト 400 の密度よりも大きくてよい。ここで密度は、画素部 910 あるいは中間部 920 における基準コンタクト 400 の数を画素部 910 あるいは中間部 920 の面積で割った値である。中間部 920 に多くの基準コンタクト 400 を設けることで、画素部 910 の電位分布を安定化あるいは均一化することができる。

10

#### 【0058】

本例では複数の画素を長波長画素と中波長画素と短波長画素に分類する。長波長画素と中波長画素と短波長画素の違いは、カラーフィルタの主透過波長である。長波長画素のカラーフィルタの主透過波長である第一波長は中波長画素のカラーフィルタの主透過波長である第二波長よりも長い。短波長画素のカラーフィルタの主透過波長である第三波長は第二波長よりも短い。図 2、図 3 には、各画素のカラーフィルタの主透過光の一例を波長の長い順から R, G, B で示している。例えば、長波長光 R は赤色光、中波長光 G は緑色光、短波長光 B は青色光である。本例では、画素 P<sub>2,1</sub>、P<sub>4,1</sub> は赤色光フィルタが設けられた長波長画素に該当する。画素 P<sub>1,1</sub>、P<sub>3,1</sub>、P<sub>2,2</sub>、P<sub>4,2</sub> は緑色光フィルタが設けられた中波長画素に該当する。画素 P<sub>1,2</sub>、P<sub>3,2</sub> は青色光フィルタが設けられた短波長画素に該当する。本例ではカラーフィルタアレイはベイヤー配列に従って形成されている。

20

#### 【0059】

画素部 910 に設けられた複数の画素 P は、上述したようにいくつかの観点で分類される。これらの観点を複合して、複数の画素を第一種画素、第二種画素、第三種画素、第四種画素に分類する。具体的には、甲種画素かつ一次近傍画素が第一種画素、乙種画素かつ二次近傍画素が第二種画素、長波長画素が第三種画素、甲種画素かつ非近傍画素が第四種画素である。

#### 【0060】

図 1 (a)において、第一種画素には「1」と、第二種画素には「2」と、第三種画素には「3」と、第四種画素には「4」とそれぞれ記している。なお無印の画素は第一乃至第四種画素のいずれかであってもよいし、これら以外の画素であってもよい。これら以外の画素としては例えば撮像用画素ではなく、専ら焦点検出用に用いられる画素が挙げられる。

30

#### 【0061】

二次近傍画素は、一次近傍画素に比べて基準コンタクト 400 に起因する暗電流が小さいと考えられる。第三半導体領域 33 が形成するポテンシャル障壁が基準コンタクト 400 に起因するノイズ電荷の分水嶺として機能しうる。そのため、基準コンタクト 400 に起因する画素毎のノイズ電荷の多寡は、分水嶺に対する基準コンタクト 400 の位置に応じて異なるであろう。基準コンタクト 400 は分水嶺に対して一次近傍画素側に位置するため、二次近傍画素は一次近傍画素に比べて基準コンタクト 400 に起因するノイズ電荷を蓄積しにくくなると考えられる。

40

#### 【0062】

甲種画素は、乙種画素に比べて半導体基板 100 の深部で生じる暗電流が小さい。第二半導体領域 12、22 が形成するポテンシャル障壁が半導体基板 100 の深部で生じるノイズ電荷の分水嶺として機能しうる。そのため、半導体基板 100 の深部で生じるノイズ電荷の多寡は、半導体基板 100 における分水嶺の深さに応じて異なるであろう。甲種画素は乙種画素に比べて第二半導体領域による分水嶺が浅いため、半導体基板 100 の深部で生じるノイズ電荷を蓄積しにくくなると考えられる。

#### 【0063】

50

なお、甲種画素は、乙種画素に比べてダイナミックレンジが低いという特徴がある。そのため、全ての画素の第二半導体領域を甲種画素の様に浅くすると、撮像装置 1000 全体のダイナミックレンジが低下してしまう。本例では、一部の画素のみを甲種画素とすることで、撮像装置 1000 全体のダイナミックレンジが大きく損なわれることを抑制している。

#### 【0064】

以上のような理由から、本例の撮像装置 1000においては、第一種画素と第二種画素間でのノイズレベルの差を低減することができる。すなわち、本例では、一次近傍画素である画素 P<sub>3,2</sub> を甲種画素とすることで、画素 P<sub>3,2</sub> の暗電流のうち半導体基板 100 の深部で生じる分を少なくしている。そして、ある基準コンタクト 400 の近傍に位置する乙種画素である画素 P<sub>2,2</sub> を二次近傍画素とすることで、画素 P<sub>2,2</sub> の暗電流のうち基準コンタクト 400 に起因する分を少なくしている。これにより、一次近傍画素と二次近傍画素とで一方が他方よりも極端に暗電流が大きいという事態を回避できる。10

#### 【0065】

また、近傍画素同士の転送の向きを基準コンタクト 400 に対して互いに逆向きにすることで、基準コンタクト 400 に起因する暗電流が信号に乗ることを抑制できる。近傍画素を別々の増幅トランジスタに接続することで、特定の増幅トランジスタでのみ暗電流が極端に大きくなることを抑制できる。

#### 【0066】

基準コンタクト 400 が設けられる半導体基板 100 の表面が受光面である場合、甲種画素のカラーフィルタの主透過波長を乙種画素のカラーフィルタの主透過波長よりも短くすると良い。シリコンでは、長波長光にくらべて短波長光で可視光の吸収が大きいため、長波長光によって生成された信号電荷を収集するには甲種画素よりも乙種画素が有利なためである。逆に基準コンタクト 400 が設けられるシリコン基板の表面とは反対の裏面が受光面である場合、乙種画素のカラーフィルタの主透過波長を甲種画素のカラーフィルタの主透過波長よりも短くすると良い。図 6 (d) は、半導体基板の裏面側にカラーフィルタやマイクロレンズを配置した場合の断面模式図を示している。例えば、表面から浅い第二半導体領域 12 を有する画素には赤色のカラーフィルタ 270R を設けている。一方、表面から深い第二半導体領域 22 を有する画素には緑色のカラーフィルタ 270G または青色のカラーフィルタ 270B を設けている。20

#### 【0067】

図 4 (b) は長波長光 R、中波長光 G、短波長光 B の光路を模式的に表している。撮像システム 2000 は、光学系 1010 として、非テレセントリック光学系または物体側テレセントリック光学系を備える。その場合、受光面への入射角は受光画素部 911 の中央から周辺に向けて放射状に大きくなる。つまり、撮像装置 1000 の受光面への入射角は、受光画素部 911 の中央付近では 0 度に近く、受光画素部 911 の中央から離れるほど入射角が大きくなる。例えば、受光画素部 911 を 3 × 3 の 9 つの区域に分割して考えることができる。9 つの区域を中央区域、右上区域、右区域、右下区域、下区域、左下区域、左区域、左上区域と呼ぶことにする。例えば、図 1 (a) において、受光画素部 911 の右上区域では光は画面の右上に向かって広がるように入射し、受光画素部 911 の左下区域では光は左下に向かって広がるように入射する。図 4 (b) は図 1 (a) においてハッティングを付けた右上区域における、中央側 (N - N' 線の N 側) から周辺側 (N - N' 線の N' 側) へ向かう方向での断面図であるから、入射光は図 4 (b) に示したように傾いて入射する。ここで、絶縁膜 200 から半導体基板 100 の上面や転送ゲート 115、113 の転送ゲート電極の上面へ入射した光 (R, G, B) は受光面に対する角度が小さくなる様に屈折する。これに対し、転送ゲート 115、113 の転送ゲート電極の側面への入射光 (R', G', B') は、受光面に対する角度が大きくなるように屈折する。これは、ポリシリコンからなる転送ゲート 115, 113 の転送ゲート電極の屈折率 (例えば 4.0) が絶縁膜 200 の屈折率 (例えば 1.4 ~ 2.3) より高いことに起因する。このような転送ゲート 115、113 の転送ゲート電極の側面への入射光が迷光となつて304050

他の画素で光電変換されると、混色を生じる。半導体基板 100 に吸収されにくい波長の光ほど迷光となりやすく、混色の原因として顕著になる。シリコンにおいては赤色光などの長波長光で顕著になるため、ここでは赤色光フィルタを含む画素の転送ゲート 115 の転送ゲート電極の側面への入射光が迷光となりやすい。これは転送ゲート 117 においても同様である。そして、図 1 (b - 2) に示す様に、光導波路 210 を設けることにより入射光の散逸が少なくなると、このような要因による迷光が目立つことになる。特に、図 1 (b - 2) に示す様に、光導波路 210 がゲート電極 110 の側面と対向する位置まで延在するような場合には、光導波路 210 からの漏れ光がポリシリコンゲート電極 110 の側面に入射し易くなる。本例では、長波長画素の転送ゲート電極は、図面上、その画素の第一半導体領域 11 の右上部に設けられている。そのため、受光画素部 911 の中でも、図面上で右上区域では斜め入射光が転送ゲート電極の光電変換素子側の側面に入射し易くなる。その結果、受光画素部 911 の右上区域において混色が顕著になる。ベイヤー配列の場合、斜め方向においては長波長画素と短波長画素が並んでいるため、長波長画素からの赤色光の迷光が、本来青色光を検出する短波長画素で検出され、画像では受光画素部 911 の右上区域に対応する部分において、青色が強調されて出力され得る。さらに本例では、受光画素部 911 の全体に渡って、図 3 (a)、(b) のレイアウトが並進対称に配されているため、図面上で左上、左下、右下の区域では転送ゲート電極の側面への入射光は生じにくい。そのため、画像において左上、左下、右下区域に対応する部分と比較すると右上区域に対応する部分の青色の強さが際立つのである。なお、図 3 (a)、(b) のレイアウトを、受光画素部 911 の中央を中心として回転対称に配した場合には全体的に青っぽい画像となり得る。

#### 【0068】

ここでは、長波長画素の転送ゲート電極を画素の右上部に配置した例を挙げたが、長波長画素の転送ゲート電極を画素の右部に配置した場合にも類似した問題が生じ得る。カラーフィルタがベイヤー配列に従う場合には、長波長画素の転送ゲート電極の右隣りには中波長画素が存在する。そのため、受光画素部 911 の右区域において、赤色光が中波長画素への混色となり、受光画素部 911 の右区域に対応する部分で緑色の強さが際立つ画像となる。このように、撮影画像において、撮像部である受光画素部 911 の特定の区域に対応した部分の色味が他の区域に対応した部分の色味と異なる現象が生じる。

#### 【0069】

本例では、このように長波長画素の転送ゲート 115 の転送ゲート電極へ入射する長波長光の混色を転送ゲート電極の位置と第二半導体領域 12 の深さによって低減することができる。すなわち、長波長画素の転送ゲート電極の側面の内、長波長光が入射しうる部分が、長波長画素の光電変換素子 20 と甲種画素の光電変換素子 10 との間に位置するよう転送ゲート電極を配置する。これにより、長波長画素の転送ゲート電極に入射した光が、甲種画素の光電変換素子 10 の下方に導かれる。具体的には、上述したように、長波長画素の転送ゲート 115 の転送ゲート電極を長波長画素である画素 P<sub>4,1</sub> の第一半導体領域 21 と甲種画素である画素 P<sub>3,2</sub> の第一半導体領域 11 の間の領域の上方に設ける。受光画素部 911 の少なくとも一部の区域において、画素 P<sub>4,1</sub> の光電変換素子 20 (第一半導体領域 21 ) と、画素 P<sub>3,2</sub> の光電変換素子 10 (第一半導体領域 11 ) が受光画素部 911 の中央から周辺に向かってこの順に並んでいる。そして、画素 P<sub>4,1</sub> の転送ゲート 115 が画素 P<sub>4,1</sub> の光電変換素子 20 と画素 P<sub>3,2</sub> の光電変換素子 10 の間に位置する。本例では、この並び順は、受光画素部 911 の右上の区域で成立する。また、本例では、長波長画素の転送の向きの先に甲種画素が位置している。典型的には、長波長画素の受光面における光学中心と、甲種画素の受光面における光学中心とを結ぶ直線が、長波長画素の転送ゲートを貫くように位置する。

#### 【0070】

甲種画素において第二半導体領域 12 の下方に第一導電型の半導体領域あるいは第二半導体領域 12 よりも薄い第二導電型の半導体領域が存在する場合、これらの領域に対して第二半導体領域 12 がポテンシャル障壁として機能する。そのため第二半導体領域 12 の

10

20

30

40

50

下方の領域で迷光による光電変換が生じても、当該画素での混色は抑制される。ここでは第三種画素である画素 P<sub>4,1</sub>からの迷光による混色を第一種画素である画素 P<sub>3,2</sub>で抑制する例を説明した。このように、基準コンタクト 400 に対して一次近傍画素となる画素 P<sub>3,2</sub> の第二半導体領域 12 の浅さを生かすことができる。しかし、基準コンタクト 400 とは無関係に、第三種画素である画素 P<sub>2,1</sub>からの迷光による混色も、第四種画素である画素 P<sub>1,2</sub> は抑制することができる。このように、非近傍画素であっても甲種画素を設けることは有効である。上述のように長波長画素の転送ゲート電極を画素の右部に配置する場合には、中波長画素を甲種画素とすることで同様に混色の影響を低減することができる。しかし、甲種画素とすることによる光電変換効率の低下は短波長画素よりも、半導体基板 100 の深部により多くの光が届く中波長画素で大きい。そのため、甲種画素を、中波長画素ではなく短波長画素とすることで、中波長画素を甲種画素にする場合に比べて光電変換効率の低下を抑制することができる。半導体基板 100 の表面より深く埋められた絶縁体を含む絶縁分離領域 40 は、半導体と絶縁体との屈折率差により半導体基板 100 内の迷光を反射し得る。そのため、長波長画素と短波長画素との間に絶縁分離領域 40 (STI) を設けることで、半導体基板 100 内での混色の発生を抑制しうる。

10

#### 【0071】

以下、撮像装置 1000 の製造方法の一例を説明する。図 7、図 8 は図 5(a) に対応する断面において、撮像装置の製造方法の一例を示す図である。

#### 【0072】

<工程 A> 図 7(a) を用いて工程 A を説明する。半導体基板 100 としては、第二導電型の半導体基体の上に第一導電型の半導体層をエピタキシャル成膜により形成したものを用いることができる。実質的にこの第一導電型の半導体層(エピタキシャル層)が半導体基板 100 として機能する。半導体基板 100 の浅部にトレンチを形成し、トレンチの内表面に第六半導体領域 36 として機能する第二導電型の不純物層 736 を形成する。この不純物層 736 は例えば 10 ~ 50 KeV の注入エネルギー、 $1 \times 10^{13} \sim 5 \times 10^{13}$  (ions/cm<sup>2</sup>) のドーザ量で形成できる。そして、トレンチに絶縁体を埋め込んで絶縁分離領域 40 を形成する。次いで、半導体基板 100 の深部(エピタキシャル層の深部)に乙種画素 P2 における第二半導体領域 22 として機能する第二導電型の不純物層 722 を形成する。この不純物層 722 は例えば 2 ~ 4 MeV の注入エネルギー、 $1 \times 10^{11} \sim 1 \times 10^{12}$  (ions/cm<sup>2</sup>) のドーザ量で形成できる。

20

30

#### 【0073】

<工程 B> 図 7(b) を用いて工程 B を説明する。半導体基板 100 の深部に第三半導体領域 33 として機能する第二導電型の不純物層 7331 ~ 7334 を形成する。この不純物層 7331 ~ 7334 はいずれも  $1 \times 10^{11} \sim 1 \times 10^{12}$  (ions/cm<sup>2</sup>) のドーザ量で形成できる。不純物層 7331、7332 は例えば 0.75 ~ 2.0 MeV の注入エネルギーで、不純物層 7333、7334 は例えば 0.25 ~ 0.75 MeV の注入エネルギーで形成できる。

#### 【0074】

また、半導体基板 100 の深部に第二半導体領域 12 として機能する第二導電型の不純物層 712 を形成する。この不純物層 712 は例えば 0.75 ~ 2.0 MeV の注入エネルギー、 $1 \times 10^{11} \sim 1 \times 10^{12}$  (ions/cm<sup>2</sup>) のドーザ量で形成できる。不純物層 712 と不純物層 7332 とがほぼ同じ深さに位置している。不純物層 712 と不純物層 7332 とが重なるように形成することもできる。不純物層 712 のドーザ量を不純物層 7332 のドーザ量よりも高くしてもよい。不純物層 7332 のドーザ量を不純物層 7331 と不純物層 7333 の少なくとも一方よりも低くしてもよい。本例では不純物層 7331、7332、7333、7334 を同じマスクで、不純物層 712 を不純物層 7332 とは別のマスクで形成している。不純物層 7331、7333、7334 を同じマスクで形成し、不純物層 712 と不純物層 7332 を 1 つのマスクで形成することもできる。

40

#### 【0075】

<工程C>図7(c)を用いて工程Cを説明する。

**【0076】**

半導体基板100の浅部に第五半導体領域35として機能する第二導電型の不純物層7351、7352を形成する。本例では、不純物層7351は行間に形成され、列間には形成されない。不純物層7352は行間及び列間に形成される。この不純物層7351、7352は例えば50~500KeVの注入エネルギー、 $1 \times 10^{11} \sim 1 \times 10^{13}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。半導体基板100の浅部に第一半導体領域11、21として機能する第一導電型の不純物層711、721を形成する。この不純物層711、721は例えば10~500KeVの注入エネルギー、 $1 \times 10^{11} \sim 1 \times 10^{13}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。なお、上述したように第一半導体領域21は第一半導体領域11よりも深くまで配されうる。しかし、不純物層711、721の形成条件は同じでよく、同時に形成することができる。その場合、第一半導体領域21の第一半導体領域11よりも深い部分は半導体基板100(エピタキシャル層)の濃度が支配的となる。つまり、不純物層711、721の下方の領域の導電型および濃度プロファイルは、エピタキシャル層に対する不純物層712のカウンタードープの有無が支配的となる。10

**【0077】**

<工程D>図7(d)を用いて工程Dを説明する。

**【0078】**

半導体基板100上にゲート絶縁膜を形成したのち、ポリシリコン膜を成膜する。ポリシリコン膜に対して、画素部910および周辺部930のNMOSトランジスタに対応した部分に第一導電型の不純物を注入し、周辺部930のPMOSトランジスタに対応した部分に第二導電型の不純物を注入する。適当なマスクを用いてポリシリコン膜をパターニングしてゲート電極810を形成する。このポリシリコン膜への不純物の導入は例えば1~50KeVの注入エネルギー、 $1 \times 10^{14} \sim 1 \times 10^{16}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。20

**【0079】**

<工程E>図7(e)を用いて工程Eを説明する。

**【0080】**

半導体基板100の浅部に浮遊拡散領域や増幅トランジスタのソース領域、ドレイン領域などとして機能する第一導電型の不純物層723を形成する。この不純物層723は例えば1~50KeVの注入エネルギー、 $1 \times 10^{12} \sim 1 \times 10^{14}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。30

**【0081】**

半導体基板100の浅部に第四半導体領域34として機能する第二導電型の不純物層734を形成する。この不純物層734は例えば1~50KeVの注入エネルギー、 $1 \times 10^{12} \sim 1 \times 10^{14}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。これまでの工程で半導体基板100内に不純物が導入されるが、適切なタイミングで半導体基板100の加熱が行われる。この加熱によって各不純物層の不純物が半導体基板100内に拡散し、適切な半導体領域の不純物濃度分布が得られる。40

**【0082】**

<工程F>図7(f)を用いて工程Fを説明する。

**【0083】**

半導体基板100の上に、適当な表面絶縁層(不図示)や、層間絶縁層201を形成する。層間絶縁層201にコンタクトホール203を形成する。コンタクトホール203を介して半導体基板100に不純物を導入する。これはコンタクト抵抗を下げるためである。基準コンタクト400となる部分には第二導電型の不純物が導入され、電源コンタクトや出力コンタクト、接続コンタクトとなる部分には第一導電型の不純物が少なくとも導入される。第一導電型の不純物と第二導電型の不純物は、例えば1~100KeVの注入エネルギー、 $1 \times 10^{14} \sim 1 \times 10^{16}$ (ions/cm<sup>2</sup>)のドーズ量で形成できる。50

基準コンタクトのための第二導電型の不純物のドーズ量を、電源コンタクトや出力コンタクトのための第一導電型の不純物のドーズ量よりも高くすることもできる。例えば第二導電型の不純物のドーズ量を第一導電型の不純物のドーズ量の5～20倍にすることができる。W-CMP法によりコンタクトプラグを形成する。

#### 【0084】

その後は、例えば図1(b-1)、(b-2)に示した撮像装置1000とする工程を経る。銅配線やアルミ配線による配線工程を経て絶縁膜200を形成したのち、絶縁膜200に開口を形成する。絶縁膜200より屈折率の高い窒化シリコン等の材料を開口に埋め込んで光導波路210を形成する。なお、開口を形成する際に、層間絶縁層を形成する前に形成された窒化シリコン層をエッチングストップとして用いることもできる。この窒化シリコン層は開口に埋め込まれる窒化シリコン等の高屈折率材料と共に光導波路210を構成しうる。エッチングストップとしての窒化シリコン層が転送ゲートのポリシリコングート電極110の側面を覆うことで、光導波路210がポリシリコングート電極110の側面と対向する位置まで延在することになる。光導波路210を形成後、第二レンズ250、カラーフィルタ270、第一レンズ290を順次形成して撮像装置1000を得ることができる。

#### 【符号の説明】

#### 【0085】

- 1 1 第一半導体領域（甲種画素）

- 1 2 第二半導体領域（甲種画素）

- 2 1 第一半導体領域（乙種画素）

- 2 2 第二半導体領域（乙種画素）

- 3 3 第三半導体領域

- 1 0 0 半導体基板

- 4 0 0 基準コンタクト

- 9 1 0 画素部

- 1 0 0 0 撮像装置

10

20

【図1】

【図2】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 渡邊 高典

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 篠原 真人

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

審査官 今井 聖和

(56)参考文献 特開2009-206260(JP,A)

特開2011-003716(JP,A)

特開2011-086888(JP,A)

特開2009-206941(JP,A)

特開2011-181595(JP,A)

特開2006-269546(JP,A)

特開2008-270299(JP,A)

特開2009-289872(JP,A)

米国特許出願公開第2010/0140731(US,A1)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14

H04N 5/335