(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 603 08 148 T2 2007.08.16

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 1 470 588 B1

(51) Int Cl.<sup>8</sup>: H01L 25/07 (2006.01)

(21) Deutsches Aktenzeichen: 603 08 148.7

(86) PCT-Aktenzeichen: PCT/US03/02326

(96) Europäisches Aktenzeichen: 03 705 914.4

(87) PCT-Veröffentlichungs-Nr.: WO 2003/065454

(86) PCT-Anmeldetag: 27.01.2003

(87) Veröffentlichungstag

der PCT-Anmeldung: 07.08.2003

(97) Erstveröffentlichung durch das EPA: 27.10.2004

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 06.09.2006

(47) Veröffentlichungstag im Patentblatt: 16.08.2007

(30) Unionspriorität:

353809 P 29.01.2002 US

(84) Benannte Vertragsstaaten:

AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB,

GR, HU, IE, IT, LI, LU, MC, NL, PT, SE, SI, SK, TR

(73) Patentinhaber:

Advanced Power Technology Inc., Bend, Oreg., US

(72) Erfinder:

FREY, B., Richard, Bend, OR 97702, US

(74) Vertreter:

Fleuchaus & Gallo, 81479 München

(54) Bezeichnung: LEISTUNGSMODUL MIT GETEILTEM GATTER UND METHODE ZUR UNTERDRÜCKUNG VON SCHWINGUNGEN DARIN

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

**Beschreibung****BEREICH DER ERFINDUNG**

**[0001]** Die vorliegende Erfindung betrifft Leistungsmodul mit mehreren Transistorchips (Transistor-Halbleiterplättchen), die ein einzelnes, externes Gate-Terminal zur Verfügung stellen. Insbesondere betrifft sie ein Leistungsmodul, das bei einer ersten Frequenz ohne Oszillation bei einer zweiten, höheren Frequenz betrieben wird, die unter einer Grenzfrequenz der Transistoren liegt.

**HINTERGRUND DER ERFINDUNG**

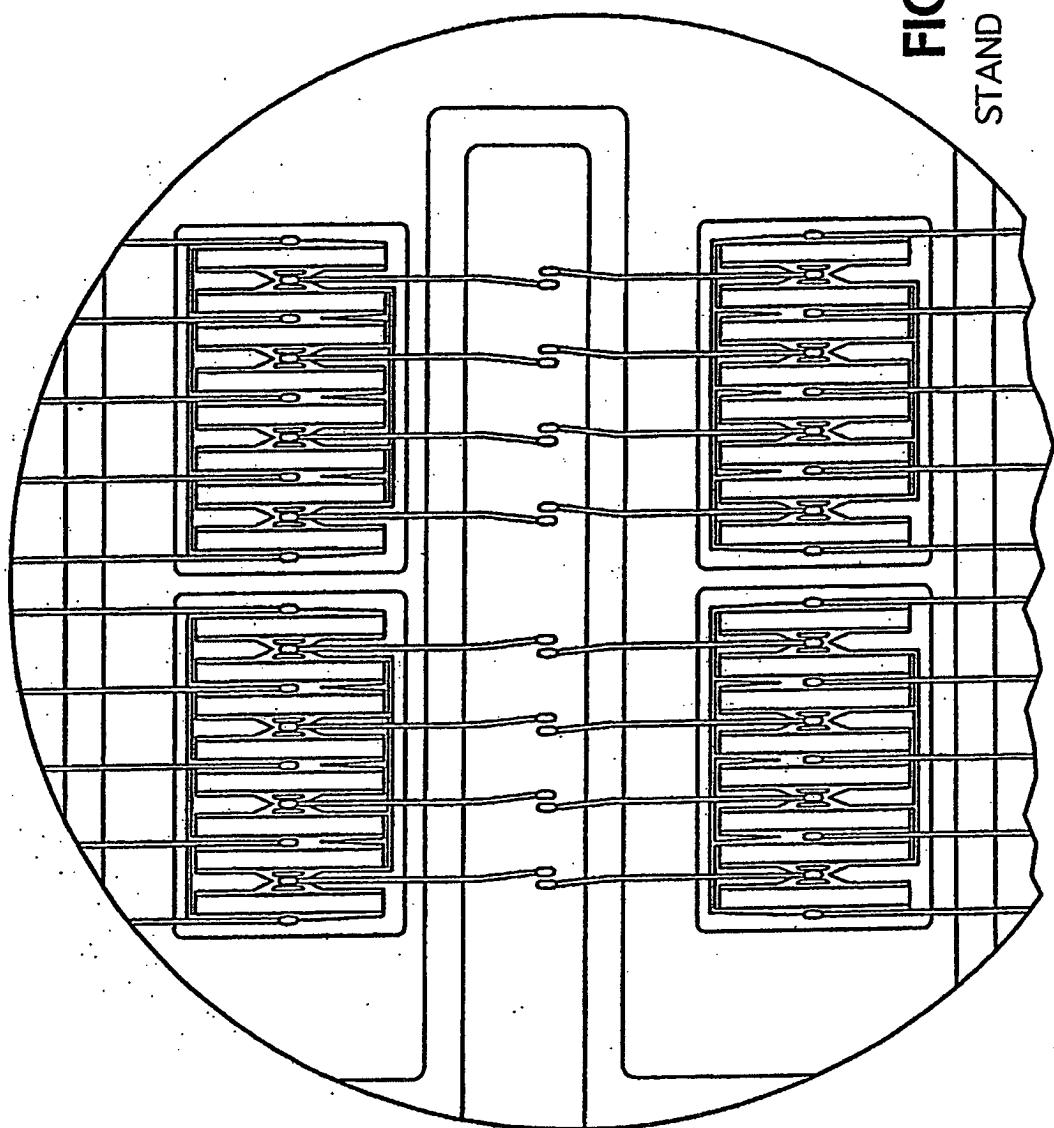

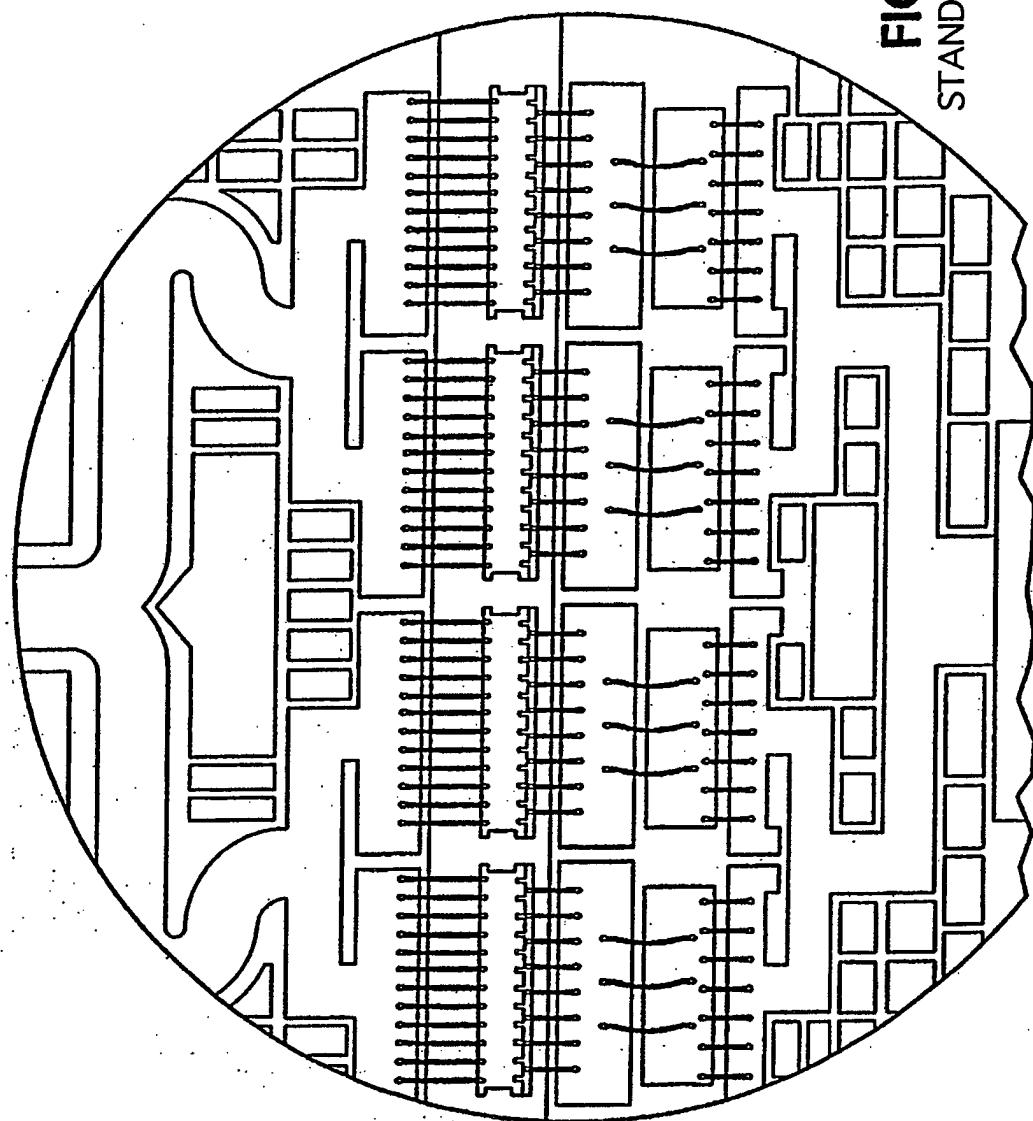

**[0002]** Aus dem Stand der Technik sind Leistungsmoduleinrichtungen bekannt, die mehrere Transistorchips verwenden. [Fig. 1](#) und [Fig. 2](#) stellen zwei solcher Konfigurationen aus dem Stand der Technik dar, wobei [Fig. 1](#) eine Einrichtung darstellt, die als SGS Thompson TH430 bekannt ist, und [Fig. 2](#) eine Einrichtung darstellt, die als Toshiba TPM1919 bekannt ist.

**[0003]** Die in [Fig. 1](#) gezeigte SGS Thompson TH430 ist eine bipolare Einrichtung mit vier Chips, die eine zentrale Basiseinspeisung enthält, wobei die Emitter an der Außenseite der rechteckigen Anordnung angeordnet sind. Gemäß dieser Gestaltung ist keine Einrichtung zum Angleichen der Weglänge von dem Basis-Terminal zu den Basen der einzelnen Chips vorgesehen. Es wird angenommen, dass die obere Frequenz des Chips, die hier als die Grenzfrequenz der Transistoren bezeichnet wird, in der Nähe der oberen Frequenzgrenze, 50 MHz, der Einrichtung mit vier Chips liegt.

**[0004]** Die in [Fig. 2](#) gezeigte Toshiba TPM1919 ist eine 2-GHz-Einrichtung mit vier MESFET-Chips in linearer Anordnung. Sie verwendet eine "Echelon"-Teilerstruktur zum Aufteilen des Gate-Signals auf vier Wege. Zwischen den Gate-Anschlüssen und den Enden der Teilerstruktur befinden sich Anpassungsnetzwerke. Es wird angenommen, dass diese Anpassungsnetzwerke Impedanz-Transformation mit der gewünschten Betriebsfrequenz liefern, was die Umsetzung der Einrichtung vereinfacht. Die Eingabestruktur der Einrichtung stellt bestimmte Abgleich- und Isolationsfunktionen zur Verfügung. Es wird angenommen, dass ihre Betriebsfrequenz in der Nähe der Obergrenze der einzelnen Chips liegt.

**[0005]** Dementsprechend werden die aus dem Stand der Technik bekannten Einrichtungen am oberen Ende der Frequenz-Kapazität der Chips betrieben. Die Gate- bzw. Basisdrähte aus dem Stand der Technik sind aufgrund der damit verbundenen sehr hohen Frequenzen notwendigerweise kurz. Infolgedessen ist ihre Störresonanz-(und mögliche Oszillations-) Frequenz höher als die Frequenz, bei der die

Chips keine Verstärkung mehr liefern können. Somit kommt es zu geringer oder gar keiner Oszillation.

**[0006]** Der in US-Patent Nr. 4,639,760 beschriebene Aufbau der MRF 154 von Motorola ([Fig. 2'](#)) verwendet serielle Gate-Widerstände, um die Verstärkung der einzelnen Gate-Zellen gezielt im Wesentlichen zu verringern, damit eine Oszillation im Wesentlichen verhindert wird. Der Chip hat einen Amplitudengang von >500 MHz, aber der gewünschte Frequenzbereich der gesamten Einrichtung war <100 MHz. Die Gestaltung von Motorola weist also überschüssige Verstärkung auf.

**[0007]** Des Weiteren beschreibt das US-Patent Nr. 5,731,970 eine Einrichtung zur Leistungsumwandlung, einen Umrichter mit drei Ebenen zum Antreiben von Motoren in Fahrzeugen und ein Halbleitermodul zum Verringern der negativen Auswirkungen von hoher Draht-Induktivität (-Induktanz) bei der Verwendung von vielen Einrichtungen.

**[0008]** Das US-Patent 5,731,970 bezieht sich auf das Problem der Oszillation in der Emitter-(Source-)Kollektorbahn in einem Modul mit mehreren Leistungseinrichtungen, und das US-Patent Nr. 5,731,970 lehrt eine Minimierung der Impedanz, insbesondere der Induktivität, indem die Kabellängen möglichst kurz bemessen werden, indem sie hinsichtlich der jeweiligen Einrichtung identisch bemessen werden und indem die Einrichtungen in einem Modul untergebracht werden, bei dem die Drähte durch Elektrodenbereiche ersetzt werden, um Induktivität zu eliminieren und die Uneinheitlichkeit der Stromstärke der Einrichtungen zu verringern.

**ZUSAMMENFASSUNG DER ERFINDUNG**

**[0009]** Die Erfindung wird durch die Ansprüche definiert.

**[0010]** Die Erfindung beinhaltet ein Verfahren zum Einhäusern und Verbinden mehrerer Leistungstransistorchips, um bei einer ersten Frequenz ohne Oszillation bei einer zweiten Frequenz betrieben zu werden, welche höher ist als die erste Frequenz, aber tiefer als eine Grenzfrequenz der Transistoren. Das Verfahren umfasst: Montieren der Chips auf einem Substrat, wobei eine untere Seite (drain, wörtlich "Senke"; hier "Anode") jedes Chips elektrisch und thermisch auf eine erste Fläche einer leitfähigen Schicht auf dem Substrat gebondet ist; elektrisches Verbinden einer Source (dt. wörtlich "Quelle", hier "Kathode") jedes Chips mit einer zweiten Fläche der leitfähigen Schicht auf dem Substrat und elektrisches Verbinden eines Gates jedes Chips mit einer dritten, gemeinsamen, inneren, zentralen Fläche der leitfähigen Schicht auf dem Substrat über separate elektrische Leiter.

**[0011]** Die Leiter sind im Wesentlichen auf dieselbe elektrische Länge bemessen und stellen zur Verfügung: eine erste Impedanz, welche der elektrischen Länge von der gemeinsamen Fläche zu jedem Gate entspricht und die erste Frequenz im Wesentlichen ungedämpft durchlässt, und wobei eine zweite Impedanz von dem Gate eines Chips zu dem Gate eines zweiten Chips zur Verfügung gestellt wird, welche die zweite Frequenz im Wesentlichen dämpft. Gemäß einem ersten Ausführungsbeispiel haben die Leiter die Form eines oder mehrerer Brückendrähte in Serie mit einem Schichtwiderstand. Gemäß einem zweiten Ausführungsbeispiel haben sie die Form einer oder mehrerer mäandrierender Streifenleitungen mit vorgegebener Impedanz-Charakteristik und einer oder mehreren gebondeter Gate-Anschlussanordnungen (gate bonding pads), die über lange Brückendrähte mit ihren jeweiligen Gates verbunden sind.

#### KURZE BESCHREIBUNG DER ZEICHNUNGEN

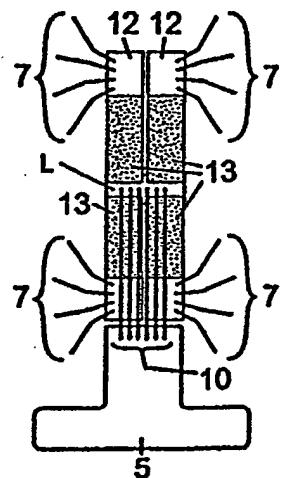

**[0012]** [Fig. 1](#) stellt einen Leistungsverstärker des Standes der Technik dar.

**[0013]** [Fig. 2](#) stellt einen weiteren Leistungsverstärker des Standes der Technik dar.

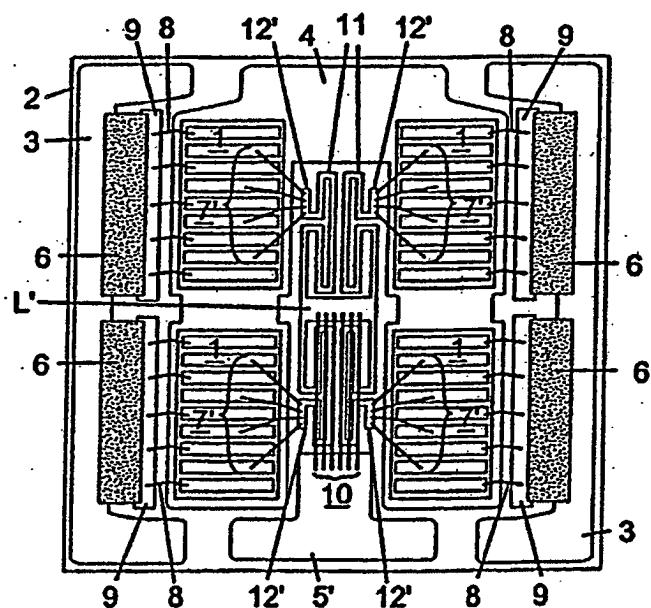

**[0014]** [Fig. 2](#) stellt einen dritten Leistungsverstärker des Standes der Technik dar.

**[0015]** [Fig. 3](#) ist ein schematisches Diagramm eines ersten Ausführungsbeispiels der vorliegenden Erfindung.

**[0016]** [Fig. 4](#) ist ein schematisches Diagramm eines zweiten Ausführungsbeispiels der vorliegenden Erfindung.

**[0017]** [Fig. 5](#) ist ein detaillierteres schematisches Diagramm der Gate-Struktur gemäß dem in [Fig. 3](#) gezeigten Ausführungsbeispiel.

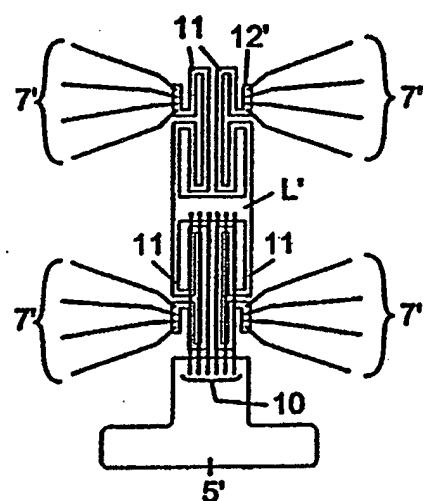

**[0018]** [Fig. 6](#) ist ein detaillierteres schematisches Diagramm der Gate-Struktur gemäß dem in [Fig. 4](#) gezeigten Ausführungsbeispiel.

#### AUSFÜHRLICHE BESCHREIBUNG

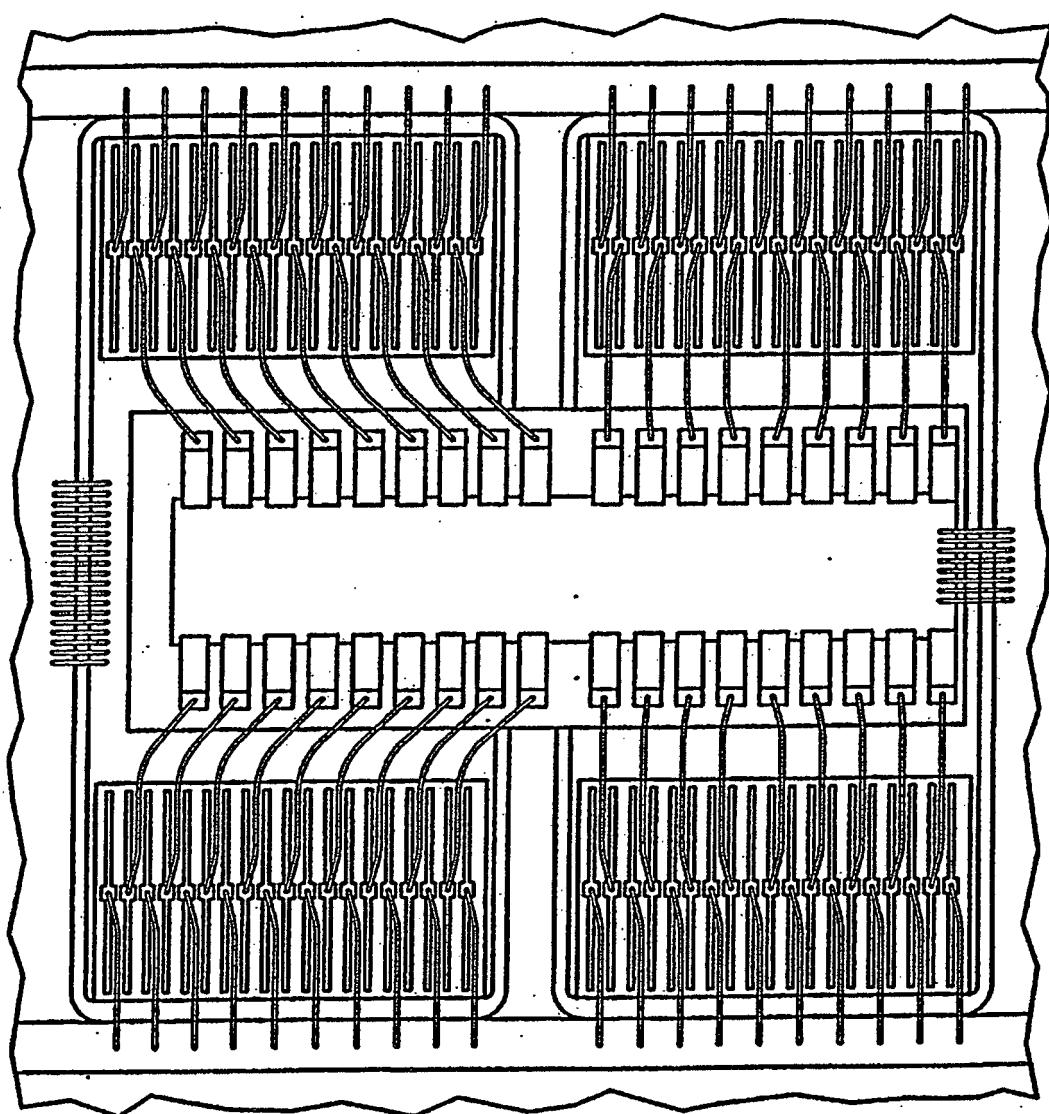

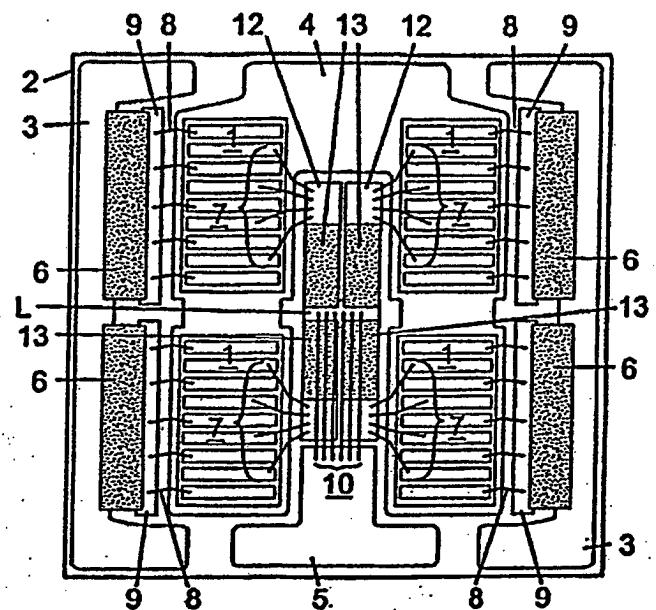

**[0019]** Gemäß der vorliegenden Erfindung sind vier MOSFET-Leistungstransistorchips in einer rechteckigen, z.B. quadratischen, Anordnung wie in [Fig. 3](#) und [Fig. 4](#) angeordnet. Die Chips haben eine Obergrenze von 250 MHz, sind aber zweimal so groß wie die Chips in der Gestaltung von Motorola. Infolgedessen ist die Eingangskapazität der Transistoren erfindungsgemäß hoch. Diese hohe Kapazität senkt die Resonanzfrequenz der störenden Struktur der Transistoren, die zu Oszillation führen kann, wenn die Transistoren in einem Leistungsmodul parallel gekoppelt sind. Aufgrund der höheren Eingangskapazi-

tät und der Verwendung von Source-Widerständen ist gemäß einem ersten Ausführungsbeispiel der Erfindung die Verstärkung bei der gewünschten Betriebsfrequenz von vornherein nicht sehr hoch. Somit gibt es nur wenig überschüssige Verstärkung, und die Gate-Widerstände für sich allein verringern die Gesamtverstärkung des Verstärkers. Wenn der für die Unterdrückung der Oszillation benötigte Widerstand zu hoch ist, können stattdessen Induktionsschleifen verwendet werden. Dementsprechend werden bei einem zweiten Ausführungsbeispiel der Erfindung Gate-Induktivitäten anstelle von Gate-Widerständen verwendet, und es wird höhere Verstärkung ohne Oszillation zur Verfügung gestellt.

**[0020]** Die Erfindung lässt sich so betrachten, dass sie eine modulare Konfiguration aus mehreren MOSFET-Chips für Hochfrequenzleistungs-Anwendungen zur Verfügung stellt, die zuverlässig sowie leicht und wiederholbar herzustellen ist.

**[0021]** [Fig. 3](#) stellt ein erstes Ausführungsbeispiel der Erfindung mit symmetrierten Gate-Eingangsan schlüssen dar, bei denen gedruckte, serielle Widerstände verwendet werden. Dem Fachmann wird bewusst sein, dass gemäß diesem ersten Ausführungsbeispiel ein Verstärker mit vergleichsweise geringerer Verstärkung erzielt wird, der aber ohne unerwünschte Oszillation funktioniert. Ebenso wird dem Fachmann bewusst sein, dass zur Erhöhung der Verstärkung, die durch einen Verstärker gemäß dieser Ausführungsform erzeugt wird, kleinere Chips mit höherer Verstärkung verwendet werden können, damit die seriellen Widerstände bei der gewünschten Betriebsfrequenz nicht den Großteil des Verstärkungsspielraums aufbrauchen.

**[0022]** [Fig. 3](#) zeigt die Anordnung mit vier Chips (jeweils mit 1 bezeichnet), die vorzugsweise auf einem Keramik-(z.B. BeO-)Substrat 2 angebracht ist und folgendes zur Verfügung stellt: eine leitfähige Source-Anschlussfläche 3, eine leitfähige Drain-Anschlussfläche 4 und eine leitfähige Gate-Anschlussfläche 5. Außerhalb des Umfanges der Chip-Anordnung sind auf dem Substrat Dünnschicht-Source-Widerstände 6 (z.B. Palladium-Gold) angeordnet. Gate-Bond-Drähte 7 und Source-Bond-Drähte 8 (z.B. Aluminium) sowie gebondete Source-Anschlussanordnungen 9 (z.B. Silber) sind wie dargestellt vorgesehen. Überbrückungsdrähte 10 (z.B. Aluminium) erstrecken sich von der Gate-Anschlussfläche 5 zu einer zentral angeordneten Gate-Landefläche L, die neben seriellen Gate-Widerständen 13 angeordnet und mit diesen elektrisch verbunden ist. Die anderen Enden der Gate-Widerstände 13 bestehen aus Draht, der mit Gate-Bond-Drähten zu mehreren entsprechenden Gate-Anschlüssen auf jedem der Chips 1 gebondet ist.

**[0023]** [Fig. 4](#) zeigt ein zweites Ausführungsbeispiel

der Erfindung mit symmetrierten Eingangsanschlüssen, bei denen mäandrierende, gedruckte Streifenleitungen bzw. Streifenleitungs-Verbindungsleitungen **11** verwendet werden, die eine relativ hohe Eigeninduktivität aufweisen. Da die Impedanz der induktiven Streifenleitungen frequenzabhängig ist (im Gegensatz zu der frequenzunabhängigen der Widerstände), ist es gemäß diesem zweiten Ausführungsbeispiel der Erfindung möglich, eine höhere Verstärkung ohne Oszillation zu erreichen. Dabei ist einsichtig, dass die topologische Anordnung des zweiten Ausführungsbeispiels der des ersten gleicht: Der erste nicht auf den Chips angeordnete Anschluss der Gates soll sich darin an einer gemeinsamen, inneren, zentralen Stelle befinden. Dem Fachmann wird bewusst sein, dass die Streifenleitungen ebenfalls über einen charakteristischen Eigenwiderstand und eine charakteristische Eigenkapazität verfügen, wenn diese auch gering sind.

**[0024]** Aus [Fig. 4](#) ist ersichtlich, dass die mäandrierenden Streifenleitungen eine im Wesentlichen gleiche elektrische Länge haben, d.h. sie weisen nahezu identische Impedanzen auf (einschließlich Widerstand, Induktivität und Kapazität) und erstrecken sich von einem externen Gate-Terminal **5'** durch Brückendrähte **10** zu einem Bereich einer zentralen, gemeinsamen Landefläche **L'** innerhalb der Chip-Anordnung und zwischen nebeneinander liegenden Chips. Die mäandrierenden Induktionsschleifen enden in gebondeten Gate-Anschlussanordnungen **12'** für die gebondete Verdrahtung mithilfe von Gate-Bonddrähten **7'** zu den mehreren entsprechenden Gate-Anschlussanordnungen auf den jeweiligen Chips **1**. Dabei ist einsichtig, dass das Substrat **2**, die Source-Anschlussfläche **3**, die Drain-Anschlussfläche **4**, die Source-Widerstände **6**, die Source-Bonddrähte **8** und die gebondeten Source-Anschlussanordnungen **9** im Wesentlichen identisch mit denen des ersten Ausführungsbeispiels der Erfindung sind, das oben mit Bezug auf [Fig. 3](#) beschrieben wurde. Dem Fachmann wird bewusst sein, dass die Leiter durch das Mäandrieren der Streifenleitungen effektiv elektrisch verlängert werden, ohne dass die dafür erforderliche Fläche der Anschlussanordnung hierdurch wesentlich vergrößert würde.

**[0025]** [Fig. 5](#) ist ein detailliertes schematisches Diagramm, das nur die Gate-Anschlussfläche der Einrichtung aus [Fig. 3](#) zeigt. [Fig. 5](#) zeigt den oben beschriebenen Gate-Anschluss **5** für die Einrichtung und die Bond-Drähte **7**. Sie zeigt auch zweite (zentrale) Gate-Anschluss-Bonddrähte **10** (sechs gemäß dem ersten gezeigten Ausführungsbeispiel), die einen Weg mit gesteuerter Impedanz (z.B. resistiv/induktiv/kapazitiv) zwischen dem Gate-Anschluss **5** und der zentral angeordneten Gate-Landefläche **L** zur Verfügung stellen. Des Weiteren zeigt sie die gebondeten Gate-Anschlussanordnungen **12** (eine pro Chip). Schließlich zeigt sie vorzugsweise gedruckte

Schaltungs-Widerstände **13** (ebenfalls einen pro Chip). Die Anzahl der Brückendrähte **10** und deren Längen können angepasst werden, damit die gewünschte Induktivität, der gewünschte Widerstand und die gewünschte Stromkapazität für eine bestimmte Anwendung erreicht wird.

**[0026]** Gemäß einem bevorzugten ersten Ausführungsbeispiel haben die seriellen Gate-Widerstände ca.  $3 \Omega$  oder weniger. Dem Fachmann wird bewusst sein, dass der Wert der seriellen Widerstände so gewählt wird, dass die Oszillation bei einer bestimmten Betriebsfrequenz der Einrichtung effektiv unterdrückt wird, ohne dass dabei die Gesamtverstärkung der Einrichtung mehr als nötig verringert würde. Außerdem sind die sechs dünnen Brückendrähte **10**, wie in dem bevorzugten ersten Ausführungsbeispiel dargestellt, parallel angeordnet.

**[0027]** [Fig. 6](#) ist ein detailliertes schematisches Diagramm, das nur die Gate-Anschlussfläche der Einrichtung aus [Fig. 4](#) zeigt. Wie oben mit Bezug auf [Fig. 4](#) beschrieben, gibt es in dem zweiten Ausführungsbeispiel der Erfindung keine seriellen Gate-Widerstände **13**; die gebondeten Gate-Anschlussanordnungen **12'** sind darin auf eine kleinere Fläche umkonfiguriert, und es enthält vier Streifenleitungs-Verbindungsleitungen **11** mit gesteuerter Impedanz, die sich, wie dargestellt, zwischen einer gemeinsamen, zentralen Landefläche **L'** und gebondeten Anschlussanordnungen **12'** erstrecken. Man sieht, dass die Landefläche **L'** wie in [Fig. 3](#) und [Fig. 5](#) über sechs parallele Brückendrähte **10** mit der Gate-Verbindung **5'** verbunden ist.

**[0028]** Die typische charakteristische Impedanz der Streifenleitungen mit gesteuerter Impedanz – kompatibel mit den ausgewählten Chips – beträgt ca.  $90 \Omega$ , bestimmt durch die Breite der Streifenleitungen sowie die Dicke und die dielektrischen Eigenschaften des Substrates **2**. Gemäß dem zweiten Ausführungsbeispiel der Erfindung, das oben unter Bezugnahme auf [Fig. 4](#) und [Fig. 6](#) beschrieben wurde, sind die Streifenleitungen ca. 0,65 Zoll (1,651 cm) lang und 0,013 Zoll (0,033 cm) breit, während das Substrat ca. 40 mil dick ist. Die Eingangsimpedanz der Chips **1** selbst liegt unter ca.  $0,2 \Omega$ .

**[0029]** Dem Fachmann wird bewusst sein, dass das Verhältnis zwischen der Leiterbreite und der Dicke der dielektrischen Schicht die charakteristische Impedanz bestimmt und dass die Länge des Leiters die serielle Impedanz bestimmt, welche die mäandrierende Streifenleitung zwischen dem Gate und dem gemeinsamen Anschlusspunkt **L'** vermittelt. Ebenso wird dem Fachmann bewusst sein, dass die dargestellten Streifenleitungen innerhalb des Gedankens und Geltungsbereiches der Erfindung durch unterschiedliche Merkmale gekennzeichnet sein, unterschiedlich ausgebildet sein und/oder unterschiedlich

geleitet werden können.

**[0030]** Zum Zweck der Beschreibung wird eine rechteckige Anordnung von vier Chips dargestellt. Andere geometrische Anordnungen wie z.B. kreisrund, dreieckig usw., mit mehr oder weniger Chips könnten mit dem beschriebenen Verfahren ebenfalls verwendet werden und liegen innerhalb des Gedankens und Geltungsbereiches der Erfindung.

**[0031]** Dementsprechend dürfte dem Fachmann nach dieser Darstellung und Beschreibung der Prinzipien unserer Erfindung in einer bevorzugten Ausführungsform ohne Weiteres ersichtlich sein, dass die Erfindung in Anordnung und Details abgewandelt werden kann, ohne dass dadurch von diesen Prinzipien abgewichen würde. Wir beanspruchen alle Abwandlungen, die in den Geltungsbereich der beiliegenden Ansprüche fallen.

### Patentansprüche

1. Verfahren zum Einhäusen und zur Verbindung mehrerer Leistungstransistor-Halbleiterplättchen, um bei einer ersten Frequenz ohne Oszillation bei einer zweiten Frequenz betrieben zu werden, welche höher ist als die erste Frequenz, aber tiefer als eine Grenzfrequenz der Transistoren, wobei das Verfahren umfasst:

Montieren der Halbleiterplättchen (1) auf einem Substrat (2), wobei eine untere Seite (drain, dt. wörtlich Senke, hier Anode) jedes Halbleiterplättchens elektrisch und thermisch auf eine erste Fläche (4) einer leitfähigen Schicht auf dem Substrat gebondet ist; elektrisches Verbinden der Source (dt. wörtlich Quelle, hier Kathode) jedes Halbleiterplättchens mit einer zweiten Fläche (3) der leitfähigen Schicht auf dem Substrat; und elektrisches Verbinden eines Gates jedes Halbleiterplättchens mit einer dritten gemeinsamen, inneren zentralen Landefläche (L, L') der leitfähigen Schicht auf dem Substrat über separate elektrische Leiter, **dadurch gekennzeichnet**, dass

sich die Leiter von der dritten gemeinsamen, inneren zentralen Landefläche (L, L') zu jedem der Gates der Halbleiterplättchen erstrecken und auf die im Wesentlichen gleiche elektrische Länge bemessen sind und eine erste Impedanz zur Verfügung stellen, die der elektrischen Länge von der gemeinsamen Fläche (L, L') zu jedem Gate entspricht, welche die erste Frequenz im Wesentlichen ungedämpft passieren lässt, und eine zweite Impedanz von dem Gate eines ersten Halbleiterplättchens zu dem Gate eines zweiten Halbleiterplättchens zur Verfügung stellen, welche die zweite Frequenz im Wesentlichen abdämpft.

2. Verfahren gemäß Anspruch 1, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, und wobei das Substrat (2) so angeordnet ist, dass die zweite Fläche (3), die mit den

Sources verbunden ist, außerhalb der Anordnung positioniert ist, und wobei die dritte Fläche (L, L') innen und zentral bezüglich der Anordnung und zwischen den Halbleiterplättchen liegt.

3. Verfahren gemäß Anspruch 1, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, welche ferner einen Satz von leitfähigen ersten Brückendrähten (10) umfasst, welche die dritte Fläche (L, L') mit einer vierten Fläche (5, 5') verbinden, und wobei das Substrat (2) so angeordnet ist, dass die zweite Fläche (3), die mit den Sources verbunden ist, außerhalb der Anordnung auf gegenüberliegenden ersten und zweiten Seiten positioniert ist, wobei die dritte Fläche (L, L') ungefähr in der Mitte innerhalb der Anordnung positioniert ist und die vierte Fläche (5, 5') im Wesentlichen außerhalb der Anordnung liegt.

4. Verfahren gemäß Anspruch 1, wobei die Anschlüsse jeweils einen ersten Bereich (11, 13) beinhalten, der sich von der dritten Fläche (L, L') zu einer Gate-Anschlussanordnung (12, 12') erstreckt, welches dem Gate eines entsprechenden Halbleiterplättchens entspricht, wobei der erste Bereich eine oder mehrere Schichten mit Impedanzen in bestimmten Rahmen beinhaltet, einen zweiten Bereich, der in Serie mit dem ersten Bereich verbunden ist, wobei der zweite Bereich die Gate-Anschlussanordnung (12, 12') beinhaltet, und einen dritten Bereich, der in Serie mit dem zweiten Bereich verbunden ist, wobei der dritte Bereich einen oder mehrere leitende Brücken (7, 7') beinhaltet, die sich zu dem Gate des entsprechenden Halbleiterplättchens erstrecken.

5. Verfahren gemäß Anspruch 4, wobei wenigstens der erste und der zweite Bereich (11, 13; 12, 12') der Leiter integral in der leitfähigen Schicht ausgebildet sind, um so Leitungen von im Wesentlichen gleicher, definierter Impedanz auf dem Substrat zu abzgrenzen, die im Wesentlichen gleiche Resistanz, Induktanz und Kapazitanz aufweisen, und wobei die leitfähigen Brücken (7, 7') konfiguriert sind, um eine im Wesentlichen gleiche, definierte Impedanz aufzuweisen, die jede Gate-Anschlussanordnung mit dem entsprechenden Gate verbindet.

6. Verfahren gemäß Anspruch 1, wobei die Leiter jeweils wenigstens einen ersten Bereich (11) beinhalten, der integral in der leitfähigen Schicht ausgebildet ist, und der sich zwischen der dritten Fläche (L') und der Gate-Anschlussanordnung (12') erstreckt, welche einem der Halbleiterplättchen (1) entspricht, wobei der erste Bereich die Form einer mäandrierenden Streifenleitung (11) annimmt, und wobei die Leiter jeweils einen zweiten Bereich beinhalten, welcher einen ersten Satz von mehreren leitfähigen Brücken (7') beinhaltet, die konfiguriert sind, um eine im Wesentlichen gleiche, definierte Impedanz aufzuweisen, die jede Gate-Anschlussanordnung mit dem entspre-

chenden Gate verbindet.

7. Verfahren gemäß Anspruch 6, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, welche ferner einen Satz von leitfähigen ersten Brückendrähten (10) umfasst, welche die dritte Fläche (L') mit einer vierten Fläche (5') verbinden, und wobei das Substrat so angeordnet ist, dass die zweite Fläche (3), die mit den Sources verbunden ist, außerhalb der Anordnung auf gegenüberliegenden ersten und zweiten Seiten positioniert ist, wobei die dritte Fläche (L') ungefähr in der Mitte innerhalb der Anordnung positioniert ist, und die vierte Fläche (5') im Wesentlichen außerhalb der Anordnung liegt.

8. Verfahren nach Anspruch 2, 3 oder 7, wobei die Anordnung rechteckig ist.

9. Leistungsmodul, welches mehrere Leistungstransistor-Halbleiterplättchen einhäust und verbindet, um bei einer ersten Frequenz ohne Oszillation bei einer zweiten Frequenz betrieben zu werden, welche höher ist als die erste Frequenz, aber tiefer als eine Grenzfrequenz der Transistoren, wobei das Modul umfasst:

ein Substrat (2), welches eine leitfähige Schicht aufweist, welche strukturiert ist, um eine erste Fläche (4) auszubilden, eine zweite Fläche (3), und eine dritte gemeinsame, innere zentrale Landefläche (L, L'); mehrere Leistungstransistor-Halbleiterplättchen, die auf dem Substrat montiert sind, wobei eine untere Seite (drain) jedes Halbleiterplättchens elektrisch und thermisch auf die erste Fläche (4) der leitfähigen Schicht auf dem Substrat gebondet ist;

eine Source jedes Halbleiterplättchens elektrisch mit der zweiten Fläche (3) der leitfähigen Schicht auf dem Substrat verbunden ist; und

ein Gate jedes Halbleiterplättchens elektrisch mit der dritten gemeinsamen, inneren zentralen Landefläche (L, L') der leitfähigen Schicht auf dem Substrat über separate elektrische Leiter verbunden ist, dadurch gekennzeichnet, dass sich die Leiter von der dritten gemeinsamen, inneren zentralen Landefläche (L, L') zu jedem der Gates der Halbleiterplättchen erstrecken und auf die im Wesentlichen gleiche elektrische Länge bemessen sind, und eine erste Impedanz zur Verfügung stellen, die der elektrischen Länge von der gemeinsamen Fläche (L, L') zu jedem Gate entspricht, welche die erste Frequenz im Wesentlichen ungedämpft passieren lässt und eine zweite Impedanz von dem Gate eines ersten Halbleiterplättchens zu dem Gate eines zweiten Halbleiterplättchens zur Verfügung stellen, welche die zweite Frequenz im Wesentlichen abdämpft.

10. Leistungsmodul gemäß Anspruch 9, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, und wobei das Substrat (2) so angeordnet ist, dass die zweite Fläche (3), die mit den Sources verbunden ist, außerhalb der Anord-

nung positioniert ist, und wobei die dritte Fläche (L, L') innen und zentral bezüglich der Anordnung und zwischen den Halbleiterplättchen liegt.

11. Leistungsmodul gemäß Anspruch 9, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, welche ferner einen Satz von leitfähigen ersten Brückendrähten (10) umfasst, welche die dritte Fläche (L, L') mit einer vierten Fläche (5, 5') verbinden, und wobei das Substrat (2) so angeordnet ist, dass die zweite Fläche (3), die mit den Sources verbunden ist, außerhalb der Anordnung auf gegenüberliegenden ersten und zweiten Seiten positioniert ist, wobei die dritte Fläche (L, L') ungefähr in der Mitte innerhalb der Anordnung positioniert ist und die vierte Fläche (5, 5') im Wesentlichen außerhalb der Anordnung liegt.

12. Leistungsmodul gemäß Anspruch 9, wobei die Anschlüsse jeweils einen ersten Bereich (11, 13) beinhalten, der sich von der dritten Fläche (L, L') zu einer Gate-Anschlussanordnung (12, 12') erstreckt, welche dem Gate eines entsprechenden Halbleiterplättchens entspricht, wobei der erste Bereich eine oder mehrere Schichten mit Impedanzen in bestimmten Rahmen beinhaltet, einen zweiten Bereich, der in Serie mit dem ersten Bereich verbunden ist, wobei der zweite Bereich die Gate-Anschlussanordnung (12, 12') beinhaltet, und einen dritten Bereich, der in Serie mit dem zweiten Bereich verbunden ist, wobei der dritte Bereich einen oder mehrere leitende Brücken (7, 7') beinhaltet, die sich zu dem Gate des entsprechenden Halbleiterplättchens erstrecken.

13. Leistungsmodul gemäß Anspruch 12, wobei wenigstens der erste und der zweite Bereich (11, 13; 12, 12') der Leiter integral in der leitfähigen Schicht ausgebildet sind, um so Leitungen von im Wesentlichen gleicher, definierter Impedanz auf dem Substrat zu abzugrenzen, die im Wesentlichen gleiche Resistanz, in Induktanz und Kapazitanz aufweisen, und wobei die leitfähigen Brücken (7, 7') konfiguriert sind, um eine im Wesentlichen gleiche, definierte Impedanz aufzuweisen, die jede Gate-Anschlussanordnung mit dem entsprechenden Gate verbindet.

14. Leistungsmodul gemäß Anspruch 9, wobei die Leiter jeweils wenigstens einen ersten Bereich (11) beinhalten, der integral in der leitfähigen Schicht ausgebildet ist, und der sich zwischen der dritten Fläche (L') und der Gate-Anschlussanordnung (12') erstreckt, welche einem der Halbleiterplättchen (1) entspricht, wobei der erste Bereich die Form einer mäandrierenden Streifenleitung (11) annimmt, und wobei die Leiter jeweils einen zweiten Bereich beinhalten, welcher einen ersten Satz von mehreren leitfähigen Brücken (7') beinhaltet, die konfiguriert sind, um eine im Wesentlichen gleiche, definierte Impedanz aufzuweisen, die jede Gate-Anschlussanordnung mit dem entsprechenden Gate verbindet.

15. Leistungsmodul nach Anspruch 14, wobei die mehreren Halbleiterplättchen (1) in einer Anordnung angeordnet sind, welche ferner einen Satz von leitfähigen ersten Brückendrähten (10) umfasst, welche die dritte Fläche (L') mit einer vierten Fläche (5') verbinden, und wobei das Substrat so angeordnet ist, dass die zweite Fläche (3), die mit den Sources verbunden ist, außerhalb der Anordnung auf gegenüberliegenden ersten und zweiten Seiten positioniert ist, wobei die dritte Fläche (L') ungefähr in der Mitte innerhalb der Anordnung positioniert ist, und die vierte Fläche (5') im Wesentlichen außerhalb der Anordnung liegt.

16. Leistungsmodul nach Anspruch 10, 11 oder 15, wobei die Anordnung rechteckig ist.

Es folgen 5 Blatt Zeichnungen

**FIG.1**

STAND DER TECHNIK

**FIG.2**

STAND DER TECHNIK

FIG.2'

STAND DER TECHNIK

FIG. 3

FIG. 4

Fig. 5

Fig. 6