(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-221501

(P2004-221501A)

(43) 公開日 平成16年8月5日(2004.8.5)

(51) Int.Cl.<sup>7</sup>

H01L 29/205

H01L 21/331

H01L 29/737

F 1

H01L 29/205

H01L 29/72

テーマコード(参考)

5FO03

H

審査請求 未請求 請求項の数 9 O L (全 10 頁)

(21) 出願番号

特願2003-10189 (P2003-10189)

(22) 出願日

平成15年1月17日 (2003.1.17)

(71) 出願人 000002093

住友化学工業株式会社

大阪府大阪市中央区北浜4丁目5番33号

100077540

弁理士 高野 昌俊

井上 智

茨城県つくば市北原6番 住友化学工業株式会社内

F ターム(参考) 5F003 BB01 BC01 BE01 BF06 BG06

BM03 BP31 BP32

(54) 【発明の名称】半導体材料及びそれを用いた半導体素子

## (57) 【要約】

【課題】コンタクト層の低抵抗化を図った半導体材料及びこれを用いた半導体素子を提供すること。

【解決手段】コレクタ層4の上にInGaAs層からなるコンタクト層5を設けた半導体ウエハ10において、コンタクト層5内の界面K側にInn組成傾斜層を設けることなく、コンタクト層5のInn組成を0.5以上することにより、コンタクト層5の成長条件を格子緩和がより早めに生じる条件とし、コンタクト層5とn<sup>+</sup>-GaAs層4との界面Kに接してコンタクト層5内に形成される空乏化領域の空乏化幅をより小さなものとし、コンタクト層5のオーミックコンタクト特性をより改善した。

【選択図】 図3

**【特許請求の範囲】****【請求項 1】**

半導体層と、該半導体層上に直接接するように形成されたコンタクト層とを備えて成る半導体材料において、前記コンタクト層が前記半導体層の材料と格子不整合の条件の材料で構成されており、前記コンタクト層での格子緩和が前記コンタクト層と前記半導体層との界面から 500 以内で生じていることを特徴とする半導体材料。

**【請求項 2】**

半導体層と、金属電極とオーミックコンタクトを形成するためのコンタクト層とを備えて成り、該コンタクト層が前記半導体層上に直接接するように形成されている半導体材料において、前記コンタクト層と前記半導体との界面における空乏化相当幅が 500 以下であることを特徴とする半導体材料。 10

**【請求項 3】**

前記半導体層が GaAs 基板上に形成されている請求項 1 又は 2 記載の半導体材料。

**【請求項 4】**

前記コンタクト層の材料が、In 組成が 0.5 以上の InGaAs である請求項 3 記載の半導体材料。

**【請求項 5】**

前記コンタクト層内であって前記界面に接して層厚 300 以下の In 組成傾斜層が形成されている請求項 4 記載の半導体材料。

**【請求項 6】**

前記 In 組成傾斜層における In 組成が、前記界面では 0 であり、前記界面から最も遠いところで少なくとも 0.5 となるように変化する請求項 5 記載の半導体材料。 20

**【請求項 7】**

前記コンタクト層のうち前記界面に接する下部層の In 組成を該下部層に連なる上部層の In 組成よりも大きくした請求項 4 記載の半導体材料。

**【請求項 8】**

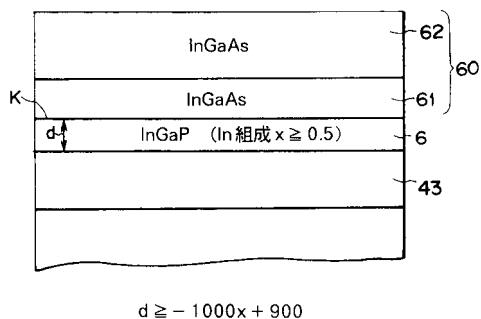

前記コンタクト層と前記半導体層との間に In 組成 x が 0.5 以上である InGaP 層が設けられており、該 InGaP 層の層厚 d ( ) が  $d = -1000x + 900$  となっている請求項 7 記載の半導体材料。 30

**【請求項 9】**

請求項 1 ~ 8 のうちいずれかに記載された半導体材料を用いて製作した半導体素子。

**【発明の詳細な説明】****【0001】****【特許文献 1】**

特開平 6-267867 号公報

**【0002】****【発明の属する技術分野】**

本発明は改善された電気抵抗特性を有するコンタクト層を備えた半導体材料及びそれを用いた半導体素子に関する。

**【0003】****【従来の技術】**

各種半導体素子にあっては、外部回路との接続を金属電極を介して行なっているが、外部回路に接続すべき半導体層と金属電極との間のオーミック接続をアニール処理なしで行なうようにするために、該半導体層と金属電極との間にコンタクト層が設けられている。このように、コンタクト層は半導体層と金属電極とのオーミック接続を良好ならしめるためのものであるから、コンタクト層の材料としては、バンドギャップが小さくて高キャリア濃度のものであるのが望ましい。

**【0004】**

例えば、ヘテロバイポーラトランジスタ (HTB) の場合であると、GaAs 基板上にコレクタ層、ベース層、エミッタ層がこの順序で順次薄膜結晶層として形成されており、エ 40 50

ミッタ層の最上層にコンタクト層が設けられ、これにより金属電極との接触抵抗の低減が図られるようになっている。このコンタクト層におけるオーミックコンタクト特性を向上させる目的で、コンタクト層の材料として、電子キャリア濃度が  $10^{19} \text{ cm}^{-2}$  程度で In 組成が 0.5 程度の InGaAs がバンドギャップが小さいとの理由で広く用いられている。しかし、エミッタ層が GaAs 層として形成されるので、このような In 組成の大きい InGaAs 層をエミッタ層上にコンタクト層として形成すると両層間で格子不整合を生じることとなり、コンタクト層の成長過程で格子緩和を起こすこととなる。この結果、出来上がった基板表面の平坦度が損なわれ、基板表面上における良好なパターニングを期待できなくなるなどの不具合を生じるばかりか、 InGaAs / GaAs 界面の InGaAs 側においてキャリアの失活による空乏化領域を誘発すると考えられている。

10

### 【0005】

このように、良好なオーミックコンタクトを実現しようとして InGaAs 層をコンタクト層として用いる場合には、格子不整合に由来する空乏化領域を生じさせ、これにより当該部分の電気抵抗が高くなってしまうという問題が生じることとなる。そこで、従来においては、格子不整合による応力の分散緩和を目的として、コンタクト層の In 組成を、エミッタ層との境界においては 0 とし、エミッタ層から離れるに従って In の組成が大きくなるように厚み方向に沿って In 組成値を変化させる、所謂 In 組成傾斜層をエミッタ層とコンタクト層との形に形成するようにした構成が採用されている（特許文献 1）。

### 【0006】

#### 【発明が解決しようとする課題】

上述の如く、従来においては、 InGaAs / GaAs 界面において格子緩和が生じることにより InGaAs 側に誘発される空乏化領域を減少させるため、 In 組成傾斜層をその界面に設ける構造が採用してきた。しかしながら、本発明者等が In 組成傾斜層と空乏化領域との関係につき種々の実験を行い、その実験結果を検討したところ、 In 組成傾斜層を用いても空乏化領域が効果的に減少、抑制されていないことが判った。このため、例えば HBT 等においてはエミッタ抵抗のより一層の低抵抗化が求められているが、従来の技術によってはこの要求を実現するのが困難であり、さらなる空乏化領域の抑制を何等かの別の手段で実現する必要がある。

20

### 【0007】

本発明の目的は、従来技術における上述の問題点を解決することができる、半導体材料及びこれを用いた半導体素子を提供することにある。

30

### 【0008】

本発明の別の目的は、エミッタ抵抗の小さい半導体素子を提供することにある。

### 【0009】

本発明の別の目的は、コンタクト層における空乏化領域を減少させ、コンタクト層における電気抵抗特性を改善した半導体材料及びこれを用いた半導体素子を提供することにある。

### 【0010】

#### 【課題を解決するための手段】

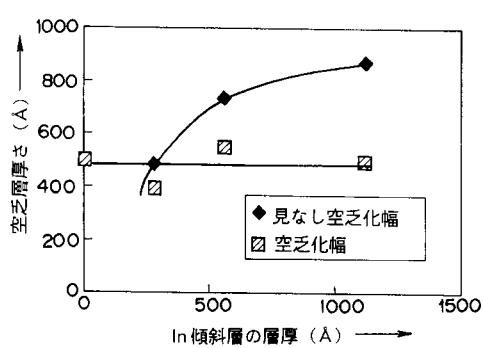

本発明者等は、従来のコンタクト層において用いられている In 組成傾斜層について検討した結果、 In 組成傾斜層を用いることにより格子緩和の影響がエミッタ、ベースに及ぼされるのを避けたとしても、図 1 に示すように空乏化幅は In 傾斜層の膜厚に依らず一定であり、 In 組成傾斜層導入に依るコンタクト層下部における界面の空乏化幅の抑制は充分でないということを見出した。

40

### 【0011】

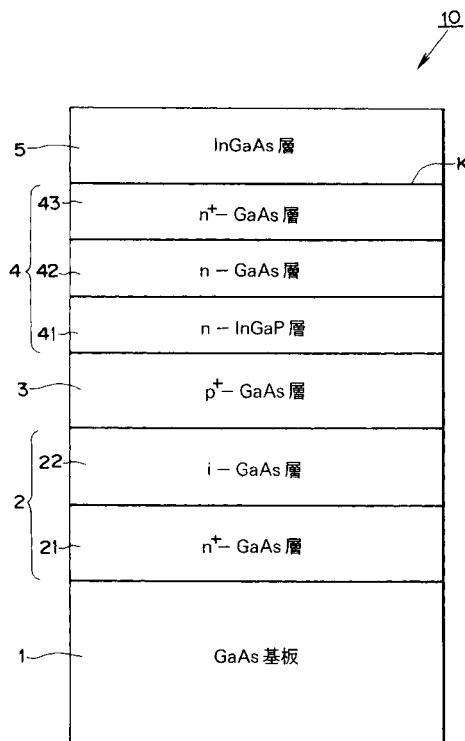

本明細書においては、空乏化幅とは、 InGaAs の膜厚を測定されたキャリア濃度と膜厚の積に対してプロットしたときの膜厚軸の切片として定義する。これは、 n 型の InGaAs 等を半絶縁性の GaAs 基板上に図 2 に示す構造の様に作製し、 InGaAs の膜厚を薄くすると Hall 測定においてキャリア濃度の減少が確認されることに基づくものである。 InGaAs と GaAs との界面の空乏化は HBT などのデバイス素子では測定

50

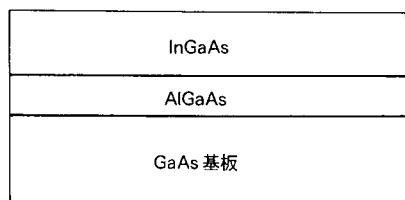

が不可能である。したがって、図2に示す構造のエピタキシャル基板を作成して検討を行った。基板はMOCVD法を用い、5族原料としてAsH<sub>3</sub>を3族原料として有機金属化合物を用い、InGaAs層のn型ドーパントとしてSi原料を供給して作成した。空乏化検討用の基板では、エッチングストップ層としてAlGaAs層をInGaAs層の下に成長した。AlGaAsはGaAsと格子整合するのでAlGaAs層を入れることによる特別な影響は殆どなく、AlGaAs層の膜厚による影響も殆どないとみなせる。

#### 【0012】

図2で示すエピタキシャルウェハにおいて、InGaAsの膜厚をエッチングなどによって薄くしながらホール測定を行うと、膜厚の減少に伴いホール測定で求められるキャリア濃度の減少が確認される。これはInGaAsの下界面における空乏化領域の全体のInGaAsに対して占める割合が、InGaAs層の膜厚が薄いほど大きくなることによる。このような測定を行って得られるInGaAs層の膜厚とキャリア濃度のデータを用いて、InGaAsの膜厚を縦軸に、測定されたキャリア濃度と膜厚の積を横軸にしてプロットして得られる1次関数のグラフの縦軸の切片が空乏化幅となる。

#### 【0013】

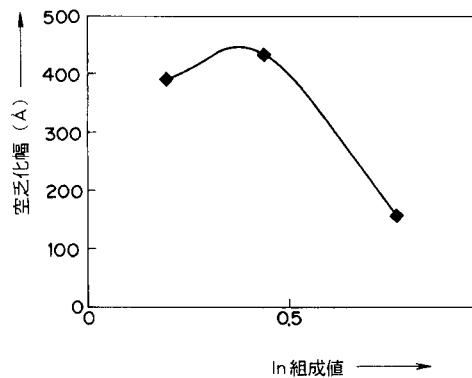

本発明にあたって発明者らは先ず、図4に示すIn組成に対する空乏化幅の関係を、図2の構造を用い、In組成を変えたInGaAsを用いたエピタキシャル基板を作成し求めた。

#### 【0014】

次に、本発明にあたり、図1に示す、In組成傾斜層と空乏化幅との関係を以下の手法によって調べた。図2に於けるInGaAs層を上下2層に分割し、上部InGaAs層にはIn組成0.5のInGaAs層を作成した。下部InGaAs層には、下側から上部InGaAs層にかけてIn組成が0から0.5になるようにしたIn組成傾斜のInGaAs層(In組成傾斜層)を作成した。そして、下部のIn組成傾斜層の膜厚に対する空乏化幅の影響を調べた。

#### 【0015】

一般に、MOCVD法によるn型InGaAsの成長では、In組成が減少するとn型キャリアのドーパント取り込みが減少する。本検討ではIn組成傾斜層を作成する際に、上部のIn=0.5のInGaAs層と同じ量のSi原料を供給している。したがって、下部の組成傾斜層ではInの減少に伴ってドーパントの取り込みが減少し、キャリア濃度が減少する。そのために、上記の空乏化幅算出の手法を用いると、下部層におけるキャリアの減少の影響が取り込まれ、空乏化幅が大きめに見積もられる。図1では、大きめに見積もられた空乏化幅をみなし空乏化幅と定義した。空乏化幅は、In組成に伴うキャリアの減少の測定結果から、みなし空乏化幅にIn組成傾斜層のキャリア減少が与える影響を計算して、見なし空乏化幅を補正することによって求めた。

#### 【0016】

図1において、横軸にIn組成傾斜層の層厚をとり、縦軸にこのIn組成傾斜層内に形成される空乏層厚さをとってある。上述のように、空乏化幅はIn傾斜層の膜厚に依らず一定であるところ、In組成傾斜層を採用すると、In組成傾斜層に於けるIn組成の少ない部分においてキャリアの取り込みが悪くなり、空乏化と同じ効果を界面にもたらしている。その結果、見なし空乏化幅は、図1に示されるように、In組成傾斜層の増加と共に増加しIn組成傾斜層の存在がかえってコンタクト層の抵抗を高めていることが判明した。図1に示した例では、組成傾斜層の層厚が約250において、空乏化幅と見なし空乏化幅とが略同じ値となっている。種々実験を重ねた結果、従来の技術を適用すると空乏化幅を500以下にすることは困難であることが判った。現在使用されているHBTではIn組成傾斜層の層厚は約500である場合が多く、したがって、In組成傾斜層を用いると見なし空乏化幅により、かえって電気抵抗特性を悪くしていることが判った。

#### 【0017】

本発明は、以上の知見に基づいてなされたもので、半導体層と、該半導体層上に直接接するように形成されたコンタクト層とを備えて成る半導体材料において、コンタクト層が半

導体層の材料と格子不整合の条件の材料で構成されており、コンタクト層での格子緩和がコンタクト層と半導体層との界面から 500 以内で生じるようにすることで、上記界面の空乏化領域を減少させ、従来に比べて低抵抗のコンタクト層を実現できるようにしたものである。

**【0018】**

このように、本発明は、コンタクト層における臨界膜厚を 500 以下とすることにより空乏化領域の空乏化幅を 500 以下とし、コンタクト層の低抵抗化を図るようとしたものである。

**【0019】**

請求項 1 の発明によれば、半導体層と、該半導体層上に直接接するように形成されたコンタクト層とを備えて成る半導体材料において、前記コンタクト層が前記半導体層の材料と格子不整合の条件の材料で構成されており、前記コンタクト層での格子緩和が前記コンタクト層と前記半導体層との界面から 500 以内で生じていることを特徴とする半導体材料が提案される。 10

**【0020】**

請求項 2 の発明によれば、半導体層と、金属電極とオーミックコンタクトを形成するためのコンタクト層とを備えて成り、該コンタクト層が前記半導体層上に直接接するように形成されている半導体材料において、前記コンタクト層と前記半導体との界面における空乏化相当幅が 500 以下であることを特徴とする半導体材料が提案される。

**【0021】**

請求項 3 の発明によれば、請求項 1 又は 2 の発明において、前記半導体層が GaAs 基板上に形成されている半導体材料が提案される。 20

**【0022】**

請求項 4 の発明によれば、請求項 3 の発明において、前記コンタクト層の材料が、In 組成が 0.5 以上の InGaAs である半導体材料が提案される。

**【0023】**

請求項 5 の発明によれば、請求項 4 の発明において、前記コンタクト層内であって前記界面に接して層厚 300 以下の In 組成傾斜層が形成されている、半導体材料が提案される。 30

**【0024】**

請求項 6 の発明によれば、請求項 5 の発明において、前記 In 組成傾斜層における In 組成が、前記界面では 0 であり、前記界面から最も遠いところで少なくとも 0.5 となるように変化する半導体材料が提案される。

**【0025】**

請求項 7 の発明によれば、請求項 4 の発明において、前記コンタクト層のうち前記界面に接する下部層の In 組成を該下部層に連なる下部層の In 組成よりも大きくした半導体材料が提案される。 40

**【0026】**

請求項 8 の発明によれば、請求項 7 の発明において、前記コンタクト層と前記半導体層との間に In 組成 x が 0.5 以上である InGaP 層が設けられており、該 InGaP 層の層厚 d が  $1d - 1000x + 900$  となっている半導体材料が提案される。

**【0027】**

請求項 9 の発明によれば、請求項 1 ~ 8 のうちいずれかに記載された半導体材料を用いて製作した半導体素子が提案される。

**【0028】**

**【発明の実施の形態】**

以下、図面を参照して本発明の実施の形態の一例につき詳細に説明する。

**【0029】**

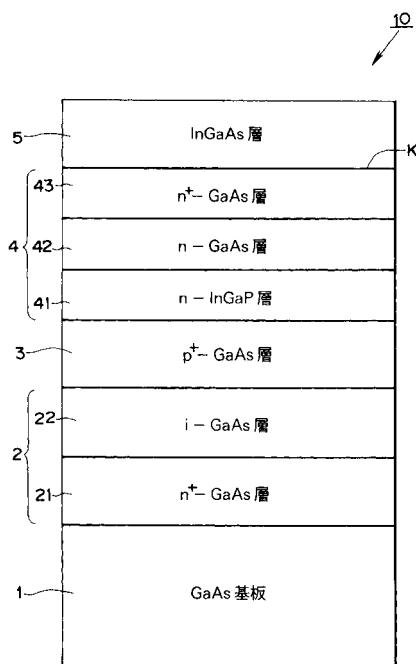

図 3 は、本発明による実施の形態の一例を構成的に示す層構造図であり、ここでは、GaAs 系 HBT の製造に用いる、HBT 用薄膜結晶ウエハの一例が示されている。 50

## 【0030】

図3に示した半導体ウエハ10は、半絶縁性のGaAs化合物半導体結晶であるGaAs基板1上有機金属熱分解法(MOCVD法)を用いて複数の半導体薄膜結晶成長層を次々と成層させて構成されたもので、GaAs基板1上有 $n^+$ -GaAs層21及びi-GaAs層22からなるコレクタ層2が形成されている。コレクタ層2の上には、p<sup>+</sup>-GaAs層からなるベース層3が形成され、該ベース層3上には、n-InGaP層41、n-GaAs層42及びn<sup>+</sup>-GaAs層43がこの順序で積層されて成るエミッタ層4が形成されている。これらの各層の作製はMOCVD装置を用いて行なうことができるが、MBE等他の手法で作成しても構わない。そしてエミッタ層4上にはコンタクト層5が形成されている。

10

## 【0031】

コンタクト層5は、エミッタ層4の最上層であるn<sup>+</sup>-GaAs層43を、半導体素子の作製工程で半導体ウエハ10の表面上に設けられる金属電極に良好にオーミック接続させることができるようするために設けられた層であり、In組成が約0.5であり、膜厚が400でキャリア濃度が約 $3 \times 10^{19} \text{ cm}^{-2}$ のInGaAs層として形成されている。InGaAs層はバンドギャップが小さく高キャリア濃度のものが得られるので、アニール処理を行うことなしに、図示しない金属電極と良好なオーミックコンタクトをとることができる。

20

## 【0032】

一方、コンタクト層5の材料であるInGaAsは、コンタクト層5に接してその下に設けられている半導体層であるn<sup>+</sup>-GaAs層43の材料であるGaAsと格子不整合条件となっているため、n<sup>+</sup>-GaAs層43上にコンタクト層5をMOCVD成長させる場合、コンタクト層5においてはInGaAsがその臨界膜厚まで成長された後、格子緩和を生じることになる。

30

## 【0033】

図3に示した実施の形態では、コンタクト層5のIn組成は0.5以上と比較的大きな値になっており、したがって、このようなIn組成の大きなInGaAs層をn<sup>+</sup>-GaAs層43上に形成すると、この大きな格子不整合状態のために格子緩和が早めに生じ、コンタクト層5における臨界膜厚は小さなものとなる。

30

## 【0034】

ところで、コンタクト層5内に形成される空乏化領域は格子緩和を生じていない臨界膜厚内に限定されるので、コンタクト層5の成層時に格子緩和が早めに生じてそこでの臨界膜厚が小さくなれば、n<sup>+</sup>-GaAs層43とコンタクト層5との界面Kに接するようにしてコンタクト層5内に形成される空乏化領域の空乏化幅はこれに従って小さくなる。この結果、コンタクト層5内の空乏化領域の空乏化幅を従来不可能であった500以下とすることが可能となる。

40

## 【0035】

本実施の形態では、コンタクト層5内の界面K側にIn組成傾斜層を設けることなく、コンタクト層5のIn組成を0.5以上と大きくすることにより、InGaAsの成長条件を格子緩和がより早めに生じる条件とし、コンタクト層5とn<sup>+</sup>-GaAs層43との界面Kに接してコンタクト層5内に形成される空乏化領域の空乏化幅をより小さなものとした。この結果、HBTに於けるエミッタシート抵抗が従来の手法によると58/であったものが、本実施の形態の場合54/となり、充分なエミッタ抵抗の低下を実現した。

40

## 【0036】

このように、GaAs層であるn<sup>+</sup>-GaAs層43の上に、GaAsとは格子不整合条件の材料であるInGaAsを用いたコンタクト層5をコンタクト層として用いるのが一般的であるが、InGaAsのIn組成を0.5以上と比較的大きな値として格子緩和が早めに生じるようにすることにより、コンタクト層5内に生じる空乏化領域の空乏化幅を従来に比べて小さくすることができるので、コンタクト層5とn<sup>+</sup>-GaAs層43

50

との界面 K における空乏化相当幅を 500 以下にするため、コンタクト層 5 において生じる格子緩和が、界面 K から 500 以内の厚み領域内で生じるようにすればよい。

#### 【0037】

In 組成の値と空乏化幅との関係を(0012)に示す方法によって検討した。In 組成のみを 0.2、0.5、0.75 と変えてそのときのコンタクト層 5 の空乏化幅を測定したところ、それぞれ、390、433、156 であった。これらの測定結果を図 4 に示した。図 4 から、In 組成 0.5 未満では空乏化幅は、約 400 程度で一定となり、0.5 以上で急激に低下することが判った。したがって、従来の In = 0.5 よりも In 組成を多くした方がより空乏化幅が小さくなる。また、In 組成が 0.5 以上であれば、実施の形態と同じ効果が得られる。

#### 【0038】

上記説明からわかるように、コンタクト層 5 内の空乏化領域の空乏化幅はコンタクト層 5 の In 組成に大きく依存しているので、コンタクト層 5 の膜厚は、上記一例に限定されることなく、適宜に定めることができる。

#### 【0039】

上記実施の形態では、コンタクト層 5 の In 組成をコンタクト層 5 全体に亘って 0.5 以上の所要の値とすることにより、コンタクト層 5 の形成時に格子緩和が早めに生じるようにした構成について説明した。しかし、本発明はこの一実施形態に限定されるものではなく、以下に説明するようにしてもコンタクト層 5 内の空乏化領域の空乏化幅を小さくすることができるものである。

#### 【0040】

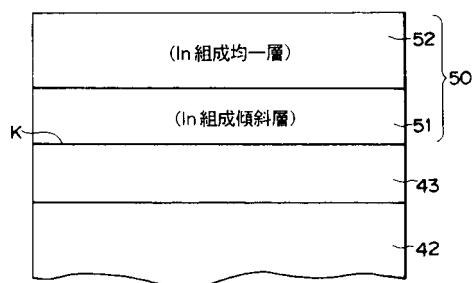

図 5 は、本発明の別の実施の形態の層構造の要部を示す図で、ここでは、コンタクト層 5 0 が下部層 5 1 と上部層 5 2 との積層構造になっており、n<sup>+</sup>-GaAs 層 4 3 と直接接する下部層 5 1 は In 組成がその層厚方向に変化する In 組成傾斜層となっており、下部層 5 1 の上に形成される上部層 5 2 は In 組成が 0.5 以上の所要の一定値になっている In 組成均一層となっている点で、図 3 に示したコンタクト層 5 と異なっている。しかし、その他の構成は図 3 に示した構成と同一である。

#### 【0041】

図 5 の実施の形態では、上部層 5 2 の In 組成は約 0.5 で、その層厚は約 500 である。下部層 5 1 の In 組成は、界面 K において零で、上部層 5 2 との界面において 0.5 であり、これらの間においては層厚方向に直線的に変化するようになっている。そして、下部層 5 1 の層厚は 300 となっている。

#### 【0042】

このように、コンタクト層 5 0 において、界面 K に接する側に 300 より小さい層厚の In 組成傾斜層である下部層 5 1 を設け、コンタクト層 5 0 のその他の部分(上部層 5 2)の In 組成を 0.5 以上とする構成を採用することによってもコンタクト層 5 0 内に界面 K に接するように形成される空乏化領域の空乏化幅を 500 以下とすることができます。したがって、In 組成傾斜層があっても本発明の範囲内となる。

#### 【0043】

図 1 から判る様に、空乏化幅は In 組成傾斜層の厚さに依らず一定である。また、In 組成傾斜層の厚さが 300 となった時、みなし空乏化幅と空乏化幅がほぼ等しくなる。したがって、In 組成傾斜層が 300 以下であればこの部分が組成傾斜であろうと In 一定の層であろうと何ら効果に違いをもたらさない。

#### 【0044】

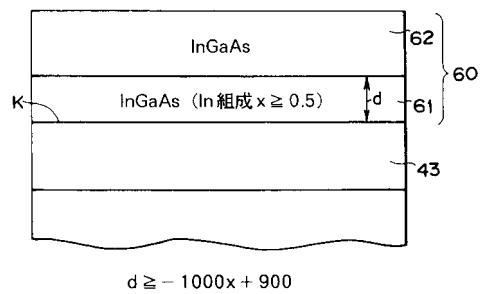

図 6 は、本発明の他の実施の形態の層構造の要部を示すもので、ここでは、コンタクト層 6 0 が下部層 6 1 と上部層 6 2 との積層構造になっており、下部層 6 1 及び上部層 6 2 は何れも In GaAs 層であって、それらの In 組成は 0.5 より大きいが、n<sup>+</sup>-GaAs 層 4 3 と直接接する下部層 6 1 の In 組成が上部層 6 2 の In 組成よりも大きくなっている点で図 2 に示したコンタクト層 5 と異なっている。しかし、その他の構成は図 2 に示した構成と同一である。

10

20

30

40

50

## 【0045】

このように、下部層61のIn組成が大きいと、コンタクト層5の形成時に先ず形成される下部層61において格子緩和が早めに生じ、これにより界面Kに生じる空乏化領域の空乏化幅を小さくすることができる。一方、上部層62におけるIn組成を下部層61より小さくしておくことにより、この領域内での格子欠陥が不要に増えるのを抑え、コンタクト層5の表面の平坦度が大きく悪化するのを防ぐことができる。

## 【0046】

下部層61の層厚は、図4に示すグラフに基づいて定めることができる。すなわち、下部層61の層厚は、図4に示される空乏化幅よりも厚ければ空乏化幅を下部層61内で押え込むことができるるのであるから、例えば、In組成が0.5のときは、その層厚は400

10

以上、In組成が0.75のときは、その層厚は150以上に設定すればよい。図4に示すグラフより、一般に、In組成がxの場合の適切な下部層61の層厚d( )は、

$d = 1000x + 900$

で与えられる。

## 【0047】

本実施の形態では下部層として上部層と同じInGaAsを用いたが、この層は格子緩和を引き起こすことが目的である。したがって格子緩和が300以内で生じるのでれば下部層として用いる材料はInGaAsに限らない。

## 【0048】

以上、本発明の実施の形態について種々説明したが、いずれも、コンタクト層におけるキャリア空乏化幅を大幅におさえることが出来、抵抗特性が改善される。したがって、上述した各構成の半導体機材を用いて従来の適宜の手段を用いてバイポーラトランジスタを製作すれば、エミッターシート抵抗を低減させることができ、高性能のバイポーラトランジスタを製作することができる。また、上記で説明した半導体材料は、HBT等のバイポーラトランジスタの製作の使用に限定されるものではなく、他の適宜の半導体機材の製作に用いることができる。

20

## 【0049】

## (実施例)

実施例として本発明によるコンタクト層を用いて、MOCVD法によって、AsH<sub>3</sub>、PH<sub>3</sub>、ガスを5族元素の原料として、有機金属を3族元素の原料として、n型のドーパント原料としてSi原料を、p型のドーパント原料としてC原料を供給し、ヘテロバイポーラトランジスタを作成した。ヘテロバイポーラトランジスタは以下の順に形成した。

30

## 【0050】

GaAs基板1の上にn<sup>+</sup>-GaAs層21をキャリア濃度が約3×10<sup>18</sup>cm<sup>-3</sup>で膜厚が約5000として形成し、i-GaAs層22を膜厚が約8000として形成した。ベース層3であるp<sup>+</sup>-GaAs層はキャリア濃度が約4×10<sup>19</sup>cm<sup>-3</sup>で、膜厚が約800として形成し、n-InGaP層41はキャリア濃度が約3×10<sup>17</sup>cm<sup>-3</sup>で膜厚が約300とし、n-GaAs層42はキャリア濃度が約3×10<sup>17</sup>cm<sup>-3</sup>で膜厚が約1000とし、n-GaAs層43はキャリア濃度が約3×10<sup>18</sup>cm<sup>-3</sup>で膜厚が約1000として形成した。コンタクト層5はIn組成約0.6からなるInGaAs層で、膜厚を約400、キャリア濃度を約3×10<sup>19</sup>cm<sup>-2</sup>として形成した。ここでいうi-GaAsとはドーパント原料を用いずに作成した半導体のことである。

40

## 【0051】

以上によって作成されたバイポーラトランジスタにおいて、従来の手法で58%であったエミッターシート抵抗が54%となり、コンタクト層の改善のみで約7%のエミッターシート抵抗の低減を実現した。

## 【0052】

## 【発明の効果】

本発明によれば、上記の如く、金属電極とオームックコンタクトをとるためのコンタクト

50

層をその下部層と格子不整合の条件で形成する場合、その界面に形成される空乏化領域の空乏化幅を従来に比べて小さくした半導体材料を実現することができ、コンタクト層の低抵抗化を図ることができる。したがって、本発明によれば、エミッタシート抵抗の小さなHBT等の製作が可能であり、より高性能の半導体素子を製作することができる。

【図面の簡単な説明】

【図1】コンタクト層におけるIn組成傾斜層と空乏化幅の関係を示すグラフ。

【図2】空乏化幅の検討のために用いられたエピタキシャル基板の層構造図。

【図3】本発明による半導体材料の実施の形態の一例を示す構成的な層構造図。

【図4】コンタクト層におけるIn組成と空乏化幅の関係を示したグラフ。

【図5】本発明の他の実施例の要部の構成的層構造図。

10

【図6】本発明の他の実施例の要部の構成的層構造図。

【図7】本発明の他の実施例の要部の構成的層構造図。

【符号の説明】

- 1 GaAs基板

- 2 コレクタ層

- 3 ベース層

- 4 エミッタ層

- 5、50、60 コンタクト層

- 6 InGaP層

- 10 半導体ウエハ

- 43 n<sup>+</sup>-GaAs層

- 51、61 下部層

- 52、62 上部層

20

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】