등록특허 10-2391869

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2022년04월27일

(11) 등록번호 10-2391869

(24) 등록일자 2022년04월25일

- (51) 국제특허분류(Int. Cl.)

*G06T 1/20* (2018.01) *G06F 1/32* (2019.01)

- (52) CPC특허분류

*G06T 1/20* (2013.01)

*G06F 1/32* (2013.01)

- (21) 출원번호 10-2019-0090836

(22) 출원일자 2019년07월26일

심사청구일자 2021년09월28일

- (65) 공개번호 10-2020-0019084

(43) 공개일자 2020년02월21일

- (30) 우선권주장

18188672.2 2018년08월13일

유럽특허청(EPO)(EP)

- (56) 선행기술조사문헌

WO2013105913 A2

(뒷면에 계속)

- 전체 청구항 수 : 총 17 항

- 발명의 명칭 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시키기 위한 제어기 및 방법

- 심사관 : 이후락

**(57) 요 약**

비디오 이미지 처리 파이프라인 제어기(50)가 개시된다. 상기 제어기(50)는 비디오 이미지 처리 파이프라인(20)의 처리 기능(25)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭을 제어하도록 구성된다. 상기 제어기(50)는 상기 비디오 이미지 처리 파이프라인(20)이 비디오 스트림 및 상기 비디오 이미지 처리 파이프라인(20)의 목표 프레임 속도를 생성하는 현재 프레임 속도에 기초하여, 대역폭을 감소시키면서 상기 현재 프레임 속도가 상기 목표 프레임 속도 이하로 떨어지지 않도록 구성되어, 상기 비디오 이미지 처리 파이프라인(20)의 피크 전력 소비를 감소시킨다. 또한 상기 비디오 이미지 처리 파이프라인(20)에서 피크 전력 소비를 감소시키는 방법뿐만 아니라 상기 제어기(50)를 포함하는 비디오 이미지 처리 시스템(1)이 개시된다.

**대 표 도** - 도2

(52) CPC특허분류

G06T 2200/28 (2013.01)

(56) 선행기술조사문헌

BHOJWANI P ET AL."A Heuristic for Peak Power Constrained Design of Network-on-Chip (NoC) Based Multimode Systems".18TH INTERNATIONAL CONFERENCE ON KOLKATA,2005.01.03.,DOI: 10.1109/ICVD.2005.12,(제124면

YUHO JIN ET AL."Peak Power Control for a QoS Capable On- Chip Network"ICPP 2005,2005.06.14.ISBN: 978-0-7695-2380-4,(제58 5면 내지 제592면)

US20180137668 A1

US20170244984 A1

US20170244894 A1

KR1020180015038 A

---

## 명세서

### 청구범위

#### 청구항 1

비디오 이미지 처리 파이프라인의 처리 기능 및 시스템 메모리 간의 하나 이상의 액세스 채널을 통한 통신을 위해 이용 가능한 대역폭을 제어하고;

상기 비디오 이미지 처리 파이프라인이 비디오 스트림을 생성하는 현재 프레임 레이트 및 상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트에 기초하여, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않도록 상기 대역폭을 감소시켜 상기 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시키며, - 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어질 때까지 상기 대역폭을 단계적으로 감소시킴 -; 및

상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지면, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가; 시키도록 구성되는 회로를 포함하는 비디오 이미지 처리 파이프라인 제어기.

#### 청구항 2

제1항에 있어서, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 상기 현재 프레임 레이트가 상기 목표 프레임 아래로 떨어지지 않은 가장 작은 이전의 대역폭으로 상기 대역폭을 증가 시키도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 파이프라인 제어기.

#### 청구항 3

제1항에 있어서, 상기 목표 프레임 레이트는 원래 프레임 레이트인 것을 특징으로 하는 비디오 이미지 처리 파이프라인 제어기.

#### 청구항 4

제1항에 있어서, 상기 회로는 복수의 메모리 액세스 채널의 상기 대역폭을 전체적으로 제어하도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 파이프라인 제어기.

#### 청구항 5

제1항에 있어서, 상기 회로는 복수의 메모리 액세스 채널 각각에서 상기 대역폭을 개별적으로 제어하도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 파이프라인 제어기.

#### 청구항 6

비디오 이미지 데이터를 제공하도록 구성된 비디오 소스;

복수의 처리 기능을 포함하는 비디오 이미지 처리 파이프라인 - 각각의 처리 기능은 상기 비디오 이미지 데이터를 처리하도록 구성됨 -;

시스템 메모리 - 상기 이미지 처리 파이프라인의 처리 기능은 하나 이상의 메모리 액세스 채널을 통해 상기 시스템 메모리를 액세스하도록 구성됨 -; 및

비디오 이미지 처리 파이프라인의 처리 기능 및 시스템 메모리 간의 하나 이상의 메모리 액세스 채널을 사용하는 통신을 위해 이용 가능한 대역폭을 제어하도록 구성된 비디오 이미지 처리 파이프라인 제어기를 포함하고,

상기 비디오 이미지 처리 파이프라인 제어기는 상기 비디오 이미지 처리 파이프라인이 비디오 스트림을 생성하는 현재 프레임 레이트 및 상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트에 기초하여, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않도록 상기 대역폭을 감소시켜 상기 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시키며, - 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어질 때까지 상기 대역폭을 단계적으로 감소시킴 -; 및

상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지면, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가시키는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 7

제6항에 있어서, 상기 비디오 이미지 처리 파이프라인의 처리 기능은 범용 프로세서 또는 그래픽 처리 장치에서 필드-프로그램 가능한 게이트 어레이, 고정-기능 주문형 집적 회로 또는 아날로그 회로가 실행되는 컴퓨터 소프트웨어 부분으로서 구현되는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 8

제6항에 있어서, 상기 비디오 소스는 이미지 센서 또는 이미지 렌더링 엔진인 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 9

제6항에 있어서, 상기 비디오 이미지 처리 시스템은:

전력 소비 유닛; 및

상기 이미지 처리 파이프라인이 상기 시스템 메모리와 통신하는 대역폭의 제어에 의해 절약된 전력을 모니터링하고, 절약된 전력의 적어도 일부를 상기 전력 소비 유닛에 분배하도록 구성되는 전력 관리 유닛;을 더 포함하는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 10

제6항에 있어서, 상기 이미지 처리 시스템은 카메라로 구현되는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 11

제6항에 있어서, 상기 비디오 이미지 처리 파이프라인 제어기는 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 가장 작은 이전의 대역폭으로 상기 대역폭을 증가시키도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 12

제6항에 있어서, 상기 목표 프레임 레이트는 원래 프레임 레이트인 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 13

제6항에 있어서, 상기 비디오 이미지 처리 파이프라인 제어기는 복수의 메모리 액세스 채널의 대역폭을 전체적으로 제어하도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 14

제6항에 있어서, 상기 비디오 이미지 처리 파이프라인 제어기는 복수의 메모리 액세스 채널의 각각에서 상기 대역폭을 개별적으로 제어하도록 추가로 구성되는 것을 특징으로 하는 비디오 이미지 처리 시스템.

#### 청구항 15

비디오 이미지 데이터를 비디오 스트림으로 처리하도록 구성된 비디오 이미지 처리 파이프라인에서 피크 전력 소비를 감소시키는 방법으로서, 상기 비디오 이미지 처리 파이프라인은 복수의 처리 기능을 포함하고, 각각의 처리 기능은 비디오 이미지 데이터를 처리하도록 구성되며, 비디오 이미지 데이터를 처리하는 동안, 상기 처리 기능은 하나 이상의 메모리 액세스 채널을 통해 시스템 메모리를 액세스하도록 구성되고, 상기 방법은:

상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트를 메모리에 저장하는 단계;

상기 비디오 이미지 처리 파이프라인이 상기 비디오 스트림을 생성하는 현재 프레임 레이트 및 상기 목표 프레임 레이트에 기초하여, 비디오 이미지 처리 파이프라인 제어기에 의해, 상기 비디오 이미지 처리 파이프라인의 처리 기능 및 상기 시스템 메모리 간의 통신을 위해 이용 가능한 대역폭을 감소시키는 단계 - 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않도록 상기 통신은 하나 이상의 메모리 액세스 채널을 사용하고, 상기 감소된 대역폭은 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어질 때까지 상기 대역폭을 단계적으로 감소시키는 단계를 포함함 -; 및

상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지면, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가시키는 단계를 포함하는 방법.

#### 청구항 16

제15항에 있어서, 상기 대역폭을 감소시키는 단계는 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 가장 작은 이전의 대역폭으로 상기 대역폭을 증가시키는 단계를 더 포함하는 것을 특징으로 하는 방법.

#### 청구항 17

처리 능력을 갖는 장치에서 실행될 때 상기 장치가 비디오 이미지를 비디오 스트림으로 처리하도록 구성된 비디오 이미지 처리 파이프라인에서 퍼크 전력 소비를 감소시키기 위한 작동을 수행하게 하도록 구성되는 프로그램 코드가 기록되며, 상기 비디오 이미지 처리 파이프라인은 복수의 처리 기능을 포함하고, 각각의 처리 기능은 비디오 이미지 데이터를 처리하도록 구성되며, 비디오 이미지 데이터를 처리하는 동안, 상기 처리 기능은 하나 이상의 메모리 액세스 채널을 통해 시스템 메모리를 액세스하도록 구성되고, 상기 작동은:

상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트를 메모리에 저장하는 단계;

상기 비디오 이미지 처리 파이프라인이 상기 비디오 스트림을 생성하는 현재 프레임 레이트 및 상기 목표 프레임 레이트에 기초하여, 비디오 이미지 처리 파이프라인 제어기에 의해, 상기 비디오 이미지 처리 파이프라인의 처리 기능 및 상기 시스템 메모리 간의 통신을 위해 이용 가능한 대역폭을 감소시키는 단계 - 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않도록 상기 통신은 하나 이상의 메모리 액세스 채널을 사용하고, 상기 감소된 대역폭은 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어질 때까지 상기 대역폭을 단계적으로 감소시키는 단계를 포함함 -; 및

상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지면, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가시키는 단계를 포함하는 것을 특징으로 하는 비-일시적 컴퓨터 판독 가능 기록 매체.

#### 청구항 18

삭제

#### 청구항 19

삭제

#### 청구항 20

삭제

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 비디오 이미지 처리 파이프라인에서의 퍼크 전력 소비의 감소에 관한 것이다. 본 발명은 또한 비디오 이미지 처리 파이프라인 제어기 및 이러한 제어기를 포함하는 비디오 이미지 처리 시스템에 관한 것이다. 본 발명은 또한 비디오 이미지 처리 파이프라인에서 퍼크 전력 소비를 감소시키는 방법에 관한 것이다.

## 배경 기술

- [0002] 일반적으로, 비디오 스트림은 이미지 센서를 사용하여 일련의 이미지를 캡처하여 생성된다. 대안으로, 일련의 이미지들은 이미지 렌더링 엔진(image rendering engine)에 의해 렌더링될 수 있다.

- [0003] 일련의 이미지로부터의 이미지가 비디오 이미지 처리 파이프라인으로 전송될 때 복수의 프로세스가 비디오 프레임을 생성하기 위해 이와 함께 작업을 시작할 것이다. 일반적으로, 일련의 이미지에서 후속 이미지가 비디오 이미지 처리 파이프라인으로 전송되기 전에 프로세스가 완료된다. 이렇게 생성된 비디오 프레임은 비디오 스트림을 형성한다.

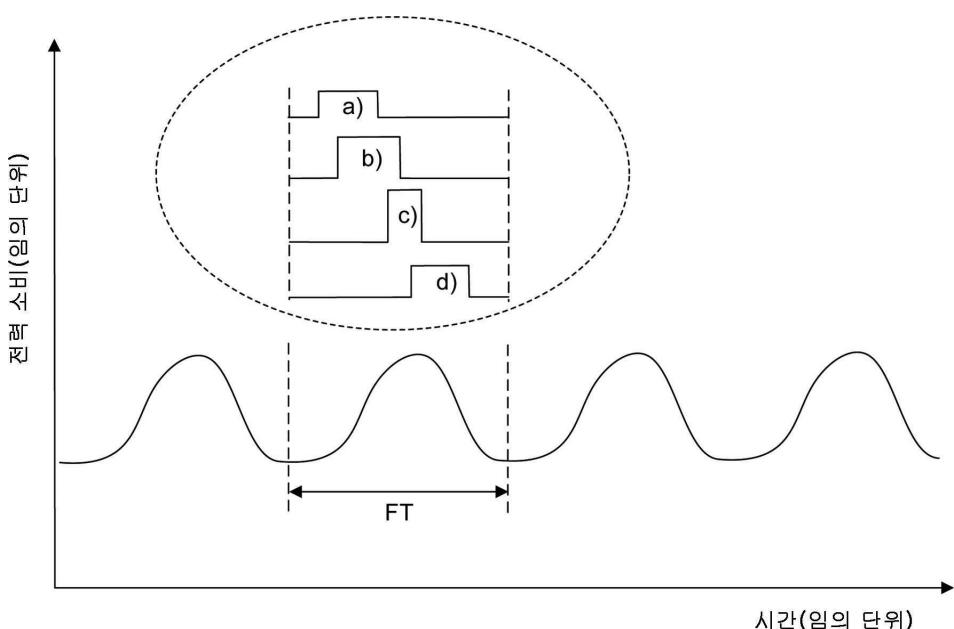

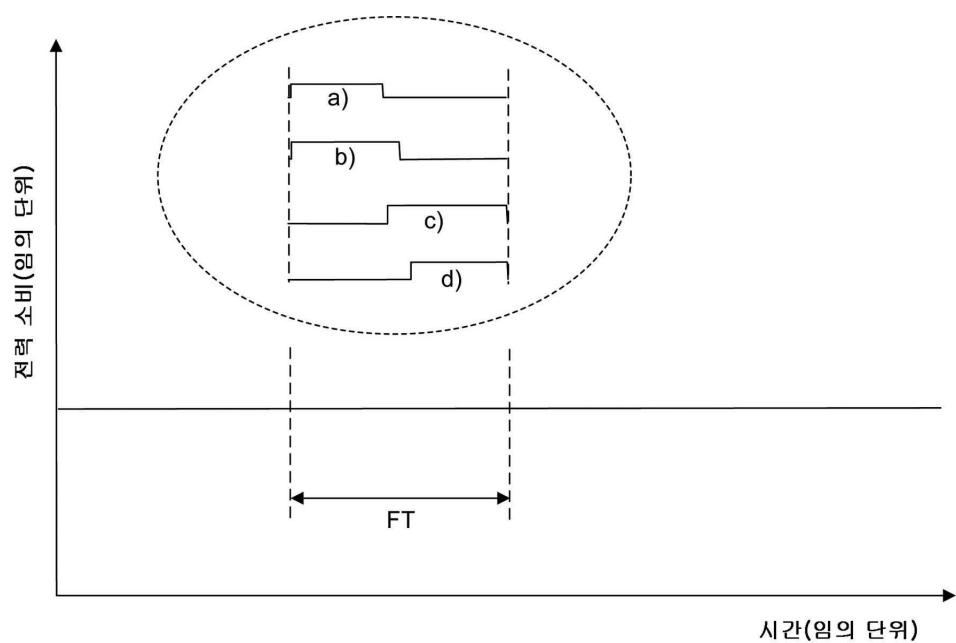

- [0004] 이로 인해 비디오 이미지 처리 파이프라인이 유휴 상태가 되고 뒤이어 비디오 이미지 처리 파이프라인이 최대 용량으로 실행된다. 이로 인해 전력 소비가 고르지 않게 된다. 따라서, 비디오 이미지 처리 파이프라인의 전력 소비는 하나의 비디오 프레임을 생성하는 동안 변한다. 비디오 이미지 처리 파이프라인의 전력 소비의 변화의 일례가 도 1에 도시된다. 도시된 바와 같이, 비디오 이미지 처리 파이프라인의 전력 소비의 특성은 프레임 레이트(frame rate)와 동일한 주파수를 갖는 사인파와 유사하다. 도 1에서, 비디오 프레임의 시간 범위는 FT, 즉 프레임 시간(frame time)으로 표시된다. 비디오 이미지 처리 파이프라인의 전력 소비에서의 변화는 비디오 이미지 처리 파이프라인의 개별 프로세스의 상이한 전력 소비에 기인한다. 도 1에 도시된 전력 소비를 형성하는 비디오 이미지 처리 파이프라인의 4개의 상이한 개별 프로세스의 전력 소비는 도면의 상단에 있는 타원 삽입 내에서 소비 도면 a)-d)로서 도 1에 도시된다.

- [0005] 비디오 이미지 처리 파이프라인의 변하는 전력 소비는 다른 결점을 가질 수 있다. 예를 들어, 비디오 이미지 처리 파이프라인에 전력을 공급하는 전력 유닛은 피크 전력 소비에 따라 크기가 정해져야 한다.

## 발명의 내용

### 해결하려는 과제

- [0006] 따라서, 비디오 이미지 처리 파이프라인의 전력 소비를 고르게(evening out) 할 필요가 있다.

### 과제의 해결 수단

- [0007] 제1 양태에 따르면, 비디오 이미지 처리 파이프라인 제어기가 제공된다. 상기 비디오 이미지 처리 파이프라인 제어기는 비디오 이미지 처리 파이프라인의 처리 기능이 하나 이상의 메모리 액세스 채널을 통해 시스템 메모리와 통신하는 대역폭(bandwidth)을 제어하도록 구성된다. 상기 비디오 이미지 처리 파이프라인 제어기는 상기 비디오 이미지 처리 파이프라인이 비디오 스트림을 생성하는 현재 프레임 레이트(current frame rate) 및 상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트(target frame rate)에 기초하여, 상기 현재 프레임 레이트가 상기 목표 프레임 레이트 아래로 떨어지지 않는 것을 보장하면서 상기 대역폭을 감소시키도록 구성되어, 상기 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시킨다.

- [0008] 따라서, 상기 시스템 메모리와의 통신에 이용 가능한 대역폭이 조정(tune)된다. 상기 시스템 메모리와 통신하는 상기 비디오 이미지 처리 파이프라인의 일부 또는 전부의 처리 기능이 제한(choke)될 것이다. 이는 이를 처리 기능의 타이밍(timing)이 이동(shift)되거나 연장될 수 있게 한다. 상기 비디오 이미지 처리 파이프라인의 일부 또는 모든 처리 기능의 활성 시간을 시간 내에 이동 및/또는 연장시킴으로써, 전력 소비는 안정한 수준으로 유지될 수 있다. 따라서, 상기 피크 전력 소비가 낮아질 수 있다. 상기 대역폭이 너무 감소되면, 상기 비디오 처리 파이프라인은 목표 프레임 레이트로 상기 비디오 스트림을 생성할 수 없다. 따라서, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않도록 대역폭의 감소가 제어될 필요가 있다. 다시 말해서, 상기 제어기는 일정한 프레임 레이트를 유지하면서 가능한 한 대역폭을 감소하도록 구성된다. 바로 하나 이상의 메모리 액세스 채널의 대역폭을 제어함으로써, 상기를 달성할 수 있다. 상기 제어 알고리즘은 상기 비디오 처리 파이프라인이 상기 비디오 스트림을 생성하는 현재 프레임 레이트와 목표 프레임 레이트의 두가지 변수를 사용한다. 상기 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시키기 위해 상기 대역폭을 제어하는 것은 백그라운드(background)에서 연속적으로 실행될 수 있다.

- [0009] 상기 비디오 이미지 처리 파이프라인의 피크 전력 소비를 감소시킴으로써, 상기 비디오 이미지 처리 파이프라인에 전력을 공급하는 전력 공급 유닛(powering unit)은 더 적은 전력을 전달하도록 크기가 정해질 수 있다. 상기 비디오 이미지 처리 파이프라인을 포함하는 카메라에 전력을 공급하기 위한 이더넷 전원 장치(PoE)를 사용하는 예에서, PoE 서비스는 현재 피크 전력의 감소없이 보다 적은 전력을 전달하도록 크기가 정해질 수 있다. 따라서,

피크 전력이 감소하면, PoE 집합체(aggregate)에 의해 전달되는데 필요한 전력도 감소할 수 있다. 대안으로, PoE 집합체는 더 많은 카메라에 전력을 공급하기 위해 사용될 수 있다.

[0010] 상기 전력 공급 유닛의 크기를 감소시키는 대신, 초과 전력은 상기 비디오 이미지 처리 파이프라인을 포함하는 장치에서 다른 프로세스에 의해 사용될 수 있다.

[0011] 상기 비디오 이미지 처리 파이프라인 제어기는 상기 대역폭을 단계적으로 감소시키도록 추가로 구성될 수 있다. 단계적인 대역폭의 감소는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어질 때까지 이루어질 수 있다. 상기 비디오 이미지 처리 파이프라인 제어기는 또한 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가시키도록 추가로 구성될 수 있다.

[0012] 상기 비디오 이미지 처리 파이프라인 제어기는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않은 가장 작은 이전의 대역폭으로 상기 대역폭을 증가시키도록 추가로 구성될 수 있다.

[0013] 목표 프레임 레이트는 원래 프레임 레이트(original frame rate)일 수 있다. 상기 비디오 이미지 파이프라인가 상기 비디오 이미지 데이터를 생성하는 상기 비디오 소스로부터 원래 프레임 레이트가 관독될 수 있다. 상기 대역폭의 조절 전에 원래 프레임 레이트가 관독될 수 있다.

[0014] 상기 비디오 이미지 처리 파이프라인 제어기는 복수의 메모리 액세스 채널의 대역폭을 전체적으로 제어하도록 추가로 구성될 수 있다.

[0015] 상기 비디오 이미지 처리 파이프라인 제어기는 복수의 메모리 액세스 채널 각각에서 상기 대역폭을 개별적으로 제어하도록 추가로 구성될 수 있다. 상기 비디오 이미지 파이프라인의 전력 소비를 가능한 한 양호하고 균일하게 제어하기 위해, 상이한 메모리 액세스 채널을 다르게 제어하는 것이 유리할 수 있다. 이는 실제 측정 또는 추정된 전력 소비를 피드백으로 사용하여 이루어질 수 있다.

[0016] 제2 양태에 따르면, 비디오 이미지 처리 시스템이 제공된다. 상기 비디오 이미지 처리 시스템은: 비디오 이미지 데이터를 제공하도록 구성된 비디오 소스(video source); 복수의 처리 기능을 포함하는 비디오 이미지 처리 파이프라인 - 각각의 처리 기능은 상기 비디오 이미지 데이터를 처리하도록 구성됨 -; 시스템 메모리 - 상기 이미지 처리 파이프라인의 처리 기능은 하나 이상의 메모리 액세스 채널을 통해 상기 시스템 메모리를 액세스하도록 구성됨 -; 및 제1 양태에 따른 비디오 이미지 처리 파이프라인 제어기를 포함한다.

[0017] 적용 가능한 경우, 상기 비디오 이미지 처리 파이프라인 제어기의 상기 언급된 특징은 이러한 제2 양태에도 적용된다. 과도한 반복을 피하기 위해, 상기를 참조한다.

[0018] 상기 비디오 이미지 처리 파이프라인은 하기 처리 기능 중 둘 이상을 포함할 수 있다: 이미지 센서 보정 기능 (correction function), 노이즈 감소 기능, 이미지 스케일링 기능, 감마 보정 기능(gamma correction function), 이미지 향상 기능, 색 공간 변환 기능, 크로마 서브샘플링 기능(chroma subsampling function), 암축 기능, 데이터 저장 기능 및 데이터 전송 기능.

[0019] 상기 비디오 이미지 처리 파이프라인의 처리 기능은 범용 프로세서 또는 그래픽 처리 유닛에서 필드-프로그램 가능한 게이트 어레이, 고정-기능 주문형 집적 회로, 또는 아날로그 회로가 실행되는 컴퓨터 소프트웨어 부분으로서 구현될 수 있다.

[0020] 상기 이미지 소스는 이미지 센서일 수 있다. 상기 이미지 소스는 이미지 렌더링 엔진(image rendering engine)일 수 있다.

[0021] 상기 비디오 이미지 처리 시스템은: 전력 소비 유닛(electrical power consuming unit); 및 상기 이미지 처리 파이프라인이 상기 시스템 메모리와 통신하는 대역폭의 제어에 의해 절약된 전력을 모니터링하고, 절약된 전력의 적어도 일부를 상기 전력 소비 유닛에 분배하도록 구성된 전력 관리 유닛(electrical power managing unit)을 포함한다.

[0022] 상기 이미지 처리 시스템은 카메라로 구현될 수 있다. 상기 카메라는 모니터링 카메라(monitoring camera)일 수 있다.

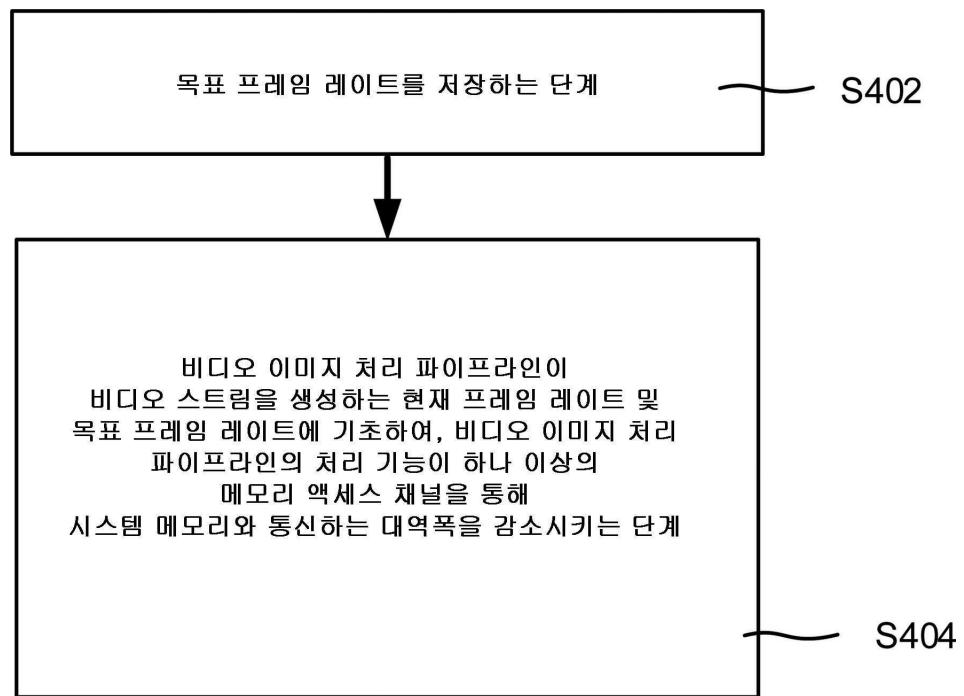

[0023] 제3 양태에 따르면, 비디오 이미지 처리 파이프라인에서 피크 전력 소비를 감소시키는 방법이 제공된다. 상기 비디오 이미지 처리 파이프라인은 비디오 이미지 데이터를 비디오 스트림으로 처리하도록 구성되고, 상기 비디

오 이미지 처리 파이프라인은 복수의 처리 기능을 포함하며, 각각의 처리 기능은 비디오 이미지 데이터를 처리하도록 구성되고, 비디오 이미지 데이터를 처리하는 동안, 상기 처리 기능은 하나 이상의 메모리 액세스 채널을 통해 시스템 메모리를 액세스하도록 구성된다. 상기 방법은: 상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트를 저장하는 단계; 및 상기 비디오 이미지 처리 파이프라인이 상기 비디오 스트림을 생성하는 현재 프레임 레이트 및 상기 목표 프레임 레이트에 기초하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 것을 보장하면서, 처리 기능이 하나 이상의 메모리 액세스 채널을 통해 상기 시스템 메모리와 통신하는 대역폭을 상기 비디오 이미지 처리 파이프라인 제어기에 의해 감소시키는 단계를 포함한다. 상기 비디오 이미지 처리 파이프라인의 목표 프레임 레이트는 메모리에 저장될 수 있다.

[0024] 대역폭을 감소시키는 단계는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어질 때까지 단계적으로 대역폭을 감소시키는 단계 및 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 상기 대역폭을 증가시키는 단계를 포함할 수 있다.

[0025] 대역폭을 감소시키는 단계는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어진다는 것에 응답하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 가장 작은 이전의 대역폭으로 대역폭을 증가시키는 단계를 더 포함할 수 있다.

[0026] 전술한 특징의 제어기 및 시스템은 적용 가능한 경우 이러한 제3 양태에도 적용된다. 과도한 반복을 피하기 위해, 상기를 참조한다.

[0027] 제4 양태에 따르면, 처리 능력을 갖는 장치에서 실행될 때 제3 양태에 따른 방법을 수행하도록 구성된 프로그램 코드가 기록된 비-일시적 컴퓨터 판독 가능 기록 매체가 제공된다.

[0028] 본 발명의 다른 적용 범위는 하기의 상세한 설명으로부터 명백해질 것이다. 그러나, 본 발명의 범위 내에서 다양한 변경 및 수정이 이러한 상세한 설명으로부터 당업자에게 명백해질 것이기 때문에, 본 발명의 바람직한 실시 형태들을 나타내는 상세한 설명 및 특정 예는 단지 예시의 방식으로 제공되는 것을 이해할 것이다.

[0029] 따라서, 본 발명은 상기 장치 및 방법이 다양할 수 있기 때문에 설명된 장치의 특정 구성 요소 부분 또는 설명된 방법의 단계에 제한되지 않음을 이해할 것이다. 또한, 본 발명에서 사용된 용어는 특정 실시 형태만을 설명하기 위한 것이며, 제한하려는 것이 아님을 이해할 것이다. 명세서 및 첨부된 청구 범위에 사용된 바와 같이, "하나", "하나의", "그" 및 "상기"라는 용어는 문맥이 다른 것을 명확하게 지칭하지 않는 한 하나 이상의 요소가 존재하는 것을 의미하는 것으로 의도된다는 점에 유의해야 한다. 따라서, 예를 들어, "장치" 또는 "상기 장치"에 대한 참조는 여러 장치 등을 포함할 수 있다. 또한, "구성하는", "포함하는", "함유하는" 및 유사한 문구는 다른 요소 또는 단계를 배제하지 않는다.

### 도면의 간단한 설명

[0030] 본 발명의 상기 및 다른 측면은 본 발명의 실시 형태를 나타내는 첨부된 도면을 참조하여 보다 상세하게 설명될 것이다. 도면은 본 발명을 특정 실시 형태로 제한하는 것으로 간주되어서는 안되며; 대신 이들은 본 발명을 설명하고 이해하는데 사용된다.

도면에 도시된 바와 같이, 층 및 영역의 크기는 설명을 위해 과장될 수 있으며, 따라서 본 발명의 실시 형태들의 일반적인 구조를 설명하기 위해 제공된다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

도 1은 종래 기술의 비디오 이미지 처리 파이프라인의 4개의 상이한 개별 프로세스의 전력 소비뿐만 아니라 복수의 프레임 시간에 걸친 종래 비디오 이미지 처리 파이프라인의 소비 전력을 개략적으로 도시한다.

도 2는 비디오 이미지 처리 시스템을 개략적으로 도시한다.

도 3은 복수의 프레임 시간에 걸친 비디오 이미지 처리 파이프라인의 전력 소비 및 비디오 이미지 처리 파이프라인의 4개의 상이한 개별 프로세스의 전력 소비를 개략적으로 도시한다.

도 4는 비디오 이미지 처리 파이프라인에서 피크 전력 소비를 감소시키는 방법의 블록도이다.

도 5는 도 2의 비디오 이미지 처리 시스템을 포함하는 카메라를 개략적으로 도시한다.

## 발명을 실시하기 위한 구체적인 내용

[0031]

이하, 첨부된 도면을 참조하여 본 발명의 실시 형태에 대하여 본 발명이 속하는 기술 분야에서 통상의 지식을 가진자가 용이하게 실시할 수 있도록 상세히 설명한다. 그러나, 본 발명은 여러 가지 상이한 형태로 구현될 수 있으며 본 발명에서 설명하는 실시 형태에 한정되지 않는 것으로 이해되어야 하며; 오히려, 이들 실시 형태는 철저함과 완전함을 위해 제공되고, 본 발명의 범위를 당업자에게 완전히 전달한다.

[0032]

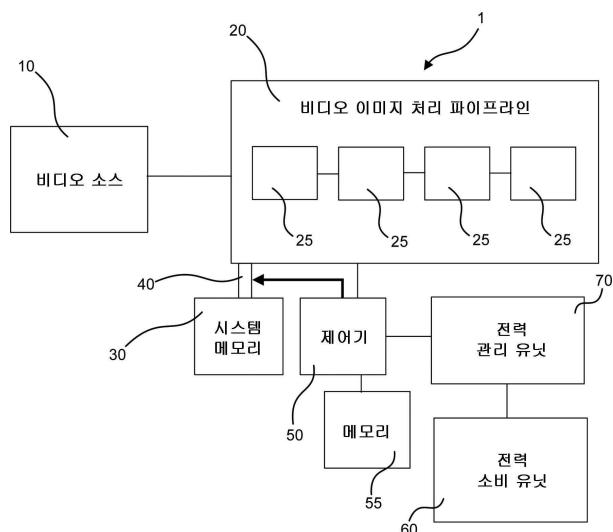

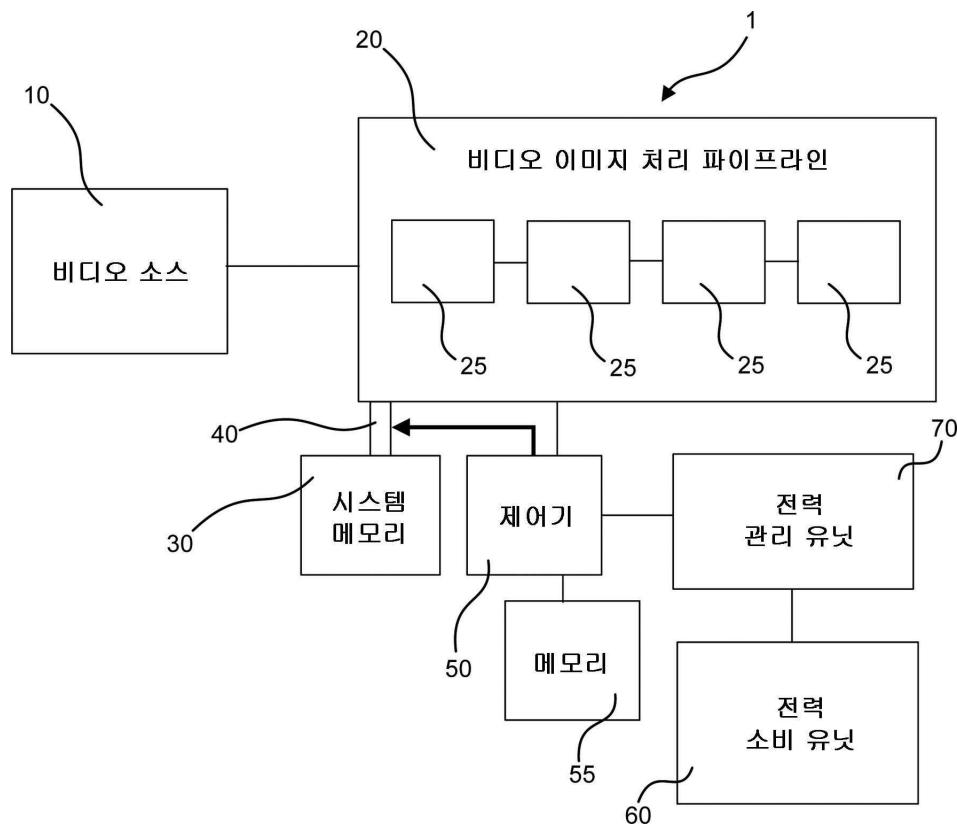

도 2는 비디오 이미지 처리 시스템(1)을 도시한다. 비디오 이미지 처리 시스템(1)은 비디오 소스(10), 비디오 이미지 처리 파이프라인(20), 시스템 메모리(30), 하나 이상의 메모리 액세스 채널(40), 및 비디오 이미지 처리 파이프라인 제어기(50)를 포함한다.

[0033]

비디오 소스(10)는 비디오 이미지 데이터를 제공하도록 구성된다. 비디오 이미지 데이터는 일련의 이미지일 수 있다. 비디오 소스(10)는 이미지 센서일 수 있다. 이미지 센서는 비디오 이미지 데이터를 캡처하도록 구성된다. 이미지 센서는 비디오 카메라의 일부를 형성할 수 있다. 대안으로 또는 조합하여, 비디오 소스(10)는 이미지 렌더링 엔진일 수 있다. 이미지 렌더링 엔진은 비디오 이미지 데이터를 렌더링하도록 구성된다. 이미지 렌더링 엔진은 컴퓨터 프로그램에 의해 2D 또는 3D 모델로부터 사실적(photorealistic) 또는 비-사실적 이미지를 렌더링 하도록 구성될 수 있다. 비디오 소스(10)는 비디오 이미지 데이터를 비디오 이미지 처리 파이프라인(20)으로 전송하도록 구성된다.

[0034]

비디오 이미지 처리 파이프라인(20)은 비디오 이미지 데이터를 비디오 프레임으로 처리하도록 구성된다. 비디오 이미지 처리 파이프라인(20)은 복수의 처리 기능(25)을 포함한다. 각각의 처리 기능(25)은 비디오 이미지 데이터를 처리하도록 구성된다. 복수의 처리 기능(25) 중 일부는 서로 의존적일 수 있다. 그러므로, 이들은 차례로 실행될 필요가 있다. 복수의 처리 기능(25) 중 일부는 서로 독립적일 수 있다. 따라서, 이들은 별별로 실행될 수 있다. 복수의 처리 기능(25)의 프로세스는 일반적으로 일련의 이미지에서 후속 이미지가 비디오 이미지 처리 파이프라인(20)으로 전송되기 전에 잘 완료된다.

[0035]

비디오 이미지 처리 파이프라인(20)은 하기 처리 기능(25) 중 둘 이상을 포함한다: 이미지 센서 보정 기능, 노이즈 감소 기능, 이미지 스케일링 기능, 감마 보정 기능, 이미지 향상 기능, 색 공간 변환 기능, 크로마 서브샘플링 기능, 압축 기능, 데이터 저장 기능 및 데이터 전송 기능. 이미지 센서 보정 기능은 베이어 필터(Bayer filter)를 포함할 수 있다. 색 공간 변환 기능은 RGB, YUV 및 YCbCr과 같은 다른 포맷 간의 변환을 포함할 수 있다.

[0036]

비디오 이미지 처리 파이프라인(20)의 특정 처리 기능(25)은 범용 프로세서 또는 그래픽 처리 유닛에서 필드 프로그램 가능한 케이트 어레이, 고정-기능 주문형 직접 회로, 또는 아날로그 회로가 실행되는 컴퓨터 소프트웨어 부분으로서 구현될 수 있다. 복수의 처리 기능(25) 중 하나는 모두 동일한 유형의 구현을 사용하여 구현될 수 있다. 복수의 처리 기능(25) 중 상이한 것은 처리 기능(25)의 상이한 구현을 사용하여 구현될 수 있다. 복수의 처리 기능(25)의 서브세트는 동일한 유형의 구현을 사용하여 구현될 수 있다. 따라서, 비디오 이미지 처리 파이프라인(20)의 처리 기능(25)은 소프트웨어, 전용 하드웨어 또는 펌웨어, 또는 전용 하드웨어, 펌웨어 및/또는 소프트웨어의 일부 조합으로 구현될 수 있다.

[0037]

시스템 메모리(30)는 비디오 이미지 데이터를 비디오 프레임으로 처리하는 동안 처리 기능(25)에 의해 사용되는 메모리이다. 시스템 메모리(30)는 랜덤-액세스 메모리(RAM)와 같은 휘발성 메모리일 수 있다.

[0038]

이미지 처리 파이프라인(20)의 처리 기능(25)은 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)를 액세스하도록 구성된다. 하나 이상의 메모리 액세스 채널은 직접 메모리 액세스, DMA, 채널일 수 있다. 이미지 처리 파이프라인(20)의 처리 기능(25)은 단일 메모리 액세스 채널(40)을 통해 시스템 메모리(30)를 액세스하도록 구성될 수 있다. 이미지 처리 파이프라인(20)의 처리 기능(25)은 복수의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)를 액세스하도록 구성될 수 있다.

[0039]

비디오 이미지 처리 파이프라인 제어기(50)는 하나 이상의 메모리 액세스 채널(40)의 대역폭을 제어하도록 구성된다. 복수의 메모리 액세스 채널(40)의 경우, 비디오 이미지 처리 파이프라인 제어기(50)는 각각 메모리 액세스 채널(40)의 대역폭을 개별적으로 제어하도록 구성될 수 있다. 따라서, 각각의 메모리 액세스 채널(40)의 대역폭은 다른 메모리 액세스 채널(40)의 대역폭과 독립적으로 제어될 수 있다. 비디오 이미지 파이프라인(20)의 전력 소비를 가능한 한 양호하고 균등하게 제어하기 위해, 상이한 메모리 액세스 채널을 다르게 제어하는 것이 유리할 수 있다. 이는 실제 측정 또는 추정된 전력 소비를 피드백으로 사용하여 이루어질 수 있다. 실제 전력 소비는 전력 관리 유닛(70)에 의해 제공될 수 있다. 대안으로, 복수의 메모리 액세스 채널(40)의 경우, 비디오

이미지 처리 파이프라인 제어기(50)는 메모리 액세스 채널(40)의 대역폭을 전체적으로 제어하도록 구성될 수 있다. 따라서, 복수의 메모리 액세스 채널의 대역폭은 하나 이상의 메모리 액세스 채널(40)의 총 대역폭을 제어하여 함께 제어될 수 있다. 따라서, 비디오 이미지 처리 파이프라인 제어기(50)는 비디오 이미지 처리 파이프라인(20)의 처리 기능(25)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭을 제어하도록 구성된다. 비디오 이미지 처리 파이프라인 제어기(50)는 대역폭이 감소되도록 대역폭을 제어하도록 구성된다. 대역폭의 제어는 비디오 이미지 처리 파이프라인(20)이 비디오 스트림을 생성하는 현재 프레임 레이트 및 비디오 이미지 처리 파이프라인(20)의 목표 프레임 레이트에 기초하여 이루어진다. 목표 프레임 레이트는 비디오 이미지 처리 시스템(1)의 메모리(55)에 저장될 수 있다. 목표 프레임 레이트는 비디오 스트림의 원래 프레임 레이트일 수 있다. 원래 프레임 레이트는 비디오 소스가 일련의 이미지를 생성하는 프레임 레이트일 수 있다. 대역폭의 감소는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 것을 보장하도록 제어된다. 따라서, 대역폭은 현재 프레임 레이트에 기초하여 목표로서 원래 프레임 레이트와 함께 제어될 수 있다.

[0040] 이러한 방식에 따라 하나 이상의 메모리 액세스 채널(40)의 대역폭을 제어함으로써, 비디오 이미지 처리 파이프라인(20)의 피크 전력 소비의 감소가 달성될 수 있다. 이는 대역폭에서의 감소가 프레임 시간 내에서 처리 기능(25)의 활성 시간의 이동을 유발 및/또는 연장시키기 때문에 야기된다. 활성 시간을 이동 및/또는 연장함으로써 전력 소비는 안정된 레벨로 유지될 수 있다. 따라서, 피크 전력 소비가 낮아질 수 있다. 이는 도 3과 관련하여 개략적으로 도시된다. 도 3의 상단의 타원 삽입 내에서, 도 1에 도시된 바와 같이 전력 소비를 형성하는 비디오 이미지 처리 파이프라인(20)의 4개의 상이한 개별 프로세스의 전력 소비가 상기 방식에 따라 대역폭의 감소 후에 개략적으로 도시된다. 대역폭의 감소는 특정 처리 기능(25)의 실행이 시간 내에 확산되는 것을 초래할 수 있다. 이는 그 특정 처리 기능(25)을 위한 전력 소비가 또한 시가 내에 확산됨을 의미할 수 있다. 이는 도 3의 상단의 타원 삽입에 도시되며, 상이한 처리 기능(25)과 관련된 상이한 프로세스들 a)-d)의 전력 소비는 대역폭을 감소시키지 않고 실행되는 비디오 이미지 처리 시스템과 비교하여 시간 내에 확산되며, 후자는 도 1에 개략적으로 도시된다. 대안으로 또는 조합하여, 대역폭의 감소는 특정 처리 기능(25)의 실행이 시간 내에 이동되는 것을 초래할 수 있다. 이는 또한 도 3의 상단의 타원 삽입에 도시되며, 여기서 프로세스 a) 및 b)의 전력 소비는 대역폭을 감소시키지 않고 실행되는 비디오 이미지 처리 시스템과 비교하여 시간 내에 이동되고, 후자는 개략적으로 도 1에 도시된다.

[0041] 전술한 바와 같이, 복수의 처리 기능(25) 중 일부는 서로 의존적일 수 있다. 도 1 및 도 3에 도시된 예에서, 프로세스 a) 및 c)는 서로에 대해 의존적이고 프로세스 b) 및 d)는 서로에 대해 의존적이다. 따라서, 이들은 차례로 실행된다. 또한, 전술한 바와 같이, 복수의 처리 기능(25) 중 일부는 서로 독립적일 수 있다. 예를 들어, 도 1 및 도 3에 도시된 예에서, 프로세스 a)는 프로세스 b) 및 d)에 독립적이다. 따라서, 프로세스 a)는 프로세스 b) 및/또는 d)와 병렬로 실행될 수 있다.

[0042] 비디오 이미지 처리 파이프라인 제어기(50)는 이미지 처리 파이프라인(20)의 처리 기능(25)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭을 피크 전력이 최소화될 때까지 조정하도록 구성될 수 있다.

[0043] 비디오 이미지 처리 파이프라인 제어기(50)는 이미지 처리 파이프라인(20)의 처리 기능(25)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭을 단계적으로 감소시키도록 추가로 구성될 수 있다. 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어질 때까지 대역폭은 단계적으로 감소될 수 있다. 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 비디오 이미지 처리 파이프라인 제어기(50)는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 대역폭을 증가시키도록 구성될 수 있다. 이는 예를 들어, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 가장 작은 이전의 대역폭으로 대역폭을 증가시킴으로써 이루어질 수 있다.

[0044] 비디오 이미지 처리 시스템(1)은 전력 소비 유닛(60) 및 전력 관리 유닛(70)을 더 포함할 수 있다.

[0045] 전력 소비 유닛(60)은 비디오 소스(10)에 의해 보여지는 장면을 조명하도록 구성된 조명 장치, 비디오 소스(10)를 팬(pan)/틸트(tilt)하도록 구성된 팬/틸트 모터, 및 시스템(1)의 하나 이상의 구성 요소를 냉각하도록 구성된 냉각 장치 중 하나 이상일 수 있다.

[0046] 전력 관리 유닛(70)은 이미지 처리 파이프라인(20)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭의 제어에 의해 절약된 전력을 모니터링하도록 구성된다. 전력 관리 유닛(70)은 절약된 전력의 적어도 일부를 전력 소비 유닛(60)에 분배하도록 추가로 구성될 수 있다.

[0047]

도 4와 관련하여, 비디오 이미지 처리 파이프라인(20)에서 페크 전력 소비를 감소시키는 방법이 설명될 것이다. 상기 방법은 하기 단계를 포함한다: 비디오 이미지 처리 파이프라인(20)의 목표 프레임 레이트를 저장하는 단계(S402), 목표 프레임 레이트는 비디오 이미지 처리 시스템(1)의 메모리(55)에 저장될 수 있고, 비디오 이미지 처리 파이프라인(20)이 비디오 스트림을 생성하는 현재 프레임 레이트 및 목표 프레임 레이트에 기초하여, 처리 기능(25)이 하나 이상의 메모리 액세스 채널(40)을 통해 시스템 메모리(30)와 통신하는 대역폭을 감소시키는 단계(S404). 감소시키는 단계(S404)는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 것을 보장하도록 수행된다. 감소시키는 단계(S404)는 비디오 이미지 처리 파이프라인 제어기(50)에 의해 수행될 수 있다. 대역폭을 감소시키는 단계(S404)는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어질 때까지 단계적으로 대역폭을 감소시키는 단계, 및 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않는 대역폭으로 대역폭을 증가시키는 단계를 포함할 수 있다. 대역폭을 감소시키는 단계(S404)는 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지는 것에 반응하여, 현재 프레임 레이트가 목표 프레임 레이트 아래로 떨어지지 않은 가장 작은 이전의 대역폭으로 대역폭을 증가시키는 단계를 추가로 포함할 수 있다.

[0048]

당업자는 본 발명이 결코 전술된 바람직한 실시 형태로 제한되지 않음을 인지한다. 반대로, 첨부된 청구 범위의 범위 내에서 많은 수정 및 변형이 가능하다.

[0049]

예를 들어, 비디오 이미지 처리 시스템은 카메라(100)에서 구현될 수 있다. 이는 도 5와 관련하여 도시된다. 카메라(100)는 모니터링 카메라일 수 있다. 시스템이 카메라(100)에서 구현되는 경우, 전력 소비 유닛(60)은 카메라(100)에 의해 보여지는 장면을 조명하도록 구성된 조명 장치, 카메라(100)를 팬/틸트하도록 구성된 팬/틸트 모터, 및 카메라(100)를 냉각하도록 구성된 냉각 장치 중 하나 이상일 수 있다.

[0050]

또한, 개시된 실시 형태에 대한 변형물은 도면, 개시물 및 첨부된 청구 범위의 연구로부터 청구된 발명을 실시 할 때 당업자에 의해 이해되고 영향을 받을 수 있다.

## 도면

### 도면1

## 도면2

## 도면3

도면4

도면5