(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4965971号

(P4965971)

(45) 発行日 平成24年7月4日(2012.7.4)

(24) 登録日 平成24年4月6日(2012.4.6)

(51) Int.Cl.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>G06F</b> | <b>12/02</b> | <b>(2006.01)</b> | G06F | 12/02 | 580E |

| <b>G06F</b> | <b>12/00</b> | <b>(2006.01)</b> | G06F | 12/00 | 571A |

| <b>G06T</b> | <b>1/20</b>  | <b>(2006.01)</b> | G06T | 1/20  | A    |

| <b>H04N</b> | <b>5/232</b> | <b>(2006.01)</b> | H04N | 5/232 | Z    |

| <b>H04N</b> | <b>5/76</b>  | <b>(2006.01)</b> | H04N | 5/76  | Z    |

請求項の数 13 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2006-299182 (P2006-299182)

(22) 出願日

平成18年11月2日 (2006.11.2)

(65) 公開番号

特開2008-117135 (P2008-117135A)

(43) 公開日

平成20年5月22日 (2008.5.22)

審査請求日

平成21年10月15日 (2009.10.15)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100125254

弁理士 別役 重尚

(72) 発明者 法田 紗央里

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 原 秀人

(56) 参考文献 特開2005-100418 (JP, A

)特開2001-166767 (JP, A

)

最終頁に続く

(54) 【発明の名称】メモリ制御装置、撮像装置およびメモリ制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

データを記憶するメモリ手段を備え、前記メモリ手段に対して行われるアクセスを制御するメモリ制御装置であって、

前記メモリ手段の2次元的な領域に連続的に書き込みを行う第1アクセス手段と、

前記第1アクセス手段によって書き込まれた、前記メモリ手段の2次元的な領域を分割した分割領域から読み出しを行う第2アクセス手段と、

前記第1および第2アクセス手段を制御するメモリ制御手段とを備え、

前記メモリ制御手段は、前記第1アクセス手段によって最後に書き込みが行われた前記メモリ手段のアドレスと、前記第2アクセス手段によって次に読み出しが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセス手段による読み出しを行わせず、

前記間隔が一定間隔より大きいときには、前記第2アクセス手段による読み出しを行わせることを特徴とするメモリ制御装置。

## 【請求項 2】

前記第1アクセス手段は、前記2次元的な領域に対し、水平方向のライン毎に連続的に書き込みを行う場合、前記一定間隔は、前記第1アクセス手段が垂直方向に1ライン進むために要するアドレス数であることを特徴とする請求項1に記載のメモリ制御装置。

## 【請求項 3】

データを記憶するメモリ手段を備え、前記メモリ手段に対して行われるアクセスを制御

するメモリ制御装置であって、

前記メモリ手段の2次元的な領域から連続的に読み出しを行う第1アクセス手段と、

前記第1アクセス手段によって読み出された、前記メモリ手段の2次元的な領域を分割した分割領域に書き込みを行う第2アクセス手段と、

前記第1および第2アクセス手段を制御するメモリ制御手段とを備え、

前記メモリ制御手段は、前記第1アクセス手段によって最後に読み出しが行われた前記メモリ手段のアドレスと、前記第2アクセス手段によって次に書き込みが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセス手段による書き込みを行わせず、

前記間隔が一定間隔より大きいときには、前記第2アクセス手段による書き込みを行わせることを特徴とするメモリ制御装置。

10

**【請求項4】**

前記第1アクセス手段は、前記2次元的な領域に対し、水平方向のライン毎に連続的に読み出しを行う場合、前記一定間隔は、前記第1アクセス手段が垂直方向に1ライン進むために要するアドレス数であることを特徴とする請求項3に記載のメモリ制御装置。

**【請求項5】**

データを記憶するメモリ手段を備え、前記メモリ手段に対して行われるアクセスを制御するメモリ制御装置であって、

前記メモリ手段の2次元的な領域を分割した第1分割領域に書き込みを行う第1アクセス手段と、

20

前記第1アクセス手段によって書き込まれた領域に、前記第1分割領域とは異なる分割をした第2分割領域から読み出しを行う第2アクセス手段と、

前記第1および第2アクセス手段を制御するメモリ制御手段とを備え、

前記メモリ制御手段は、前記第1アクセス手段によって次に書き込みが行われる前記メモリ手段のアドレスと、前記第2アクセス手段によって次に読み出しが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセス手段による読み出しを行わず、

前記間隔が一定間隔より大きいときには、前記第2アクセス手段による読み出しを行うことを特徴とするメモリ制御装置。

**【請求項6】**

30

前記一定間隔は、前記第1分割領域および前記第2分割領域のうち、前記垂直方向の長さが大きい方の領域を前記垂直方向に2つ進むために要するアドレス数であることを特徴とする請求項5に記載のメモリ制御装置。

**【請求項7】**

前記メモリ制御手段は、前記第1アクセス手段の処理が終了した後、前記間隔の大小による前記第2アクセス手段の制御を無効にするラッチ回路をさらに有することを特徴とする請求項1乃至5のいずれか1項に記載のメモリ制御装置。

**【請求項8】**

請求項1に記載のメモリ制御装置と、

入射された被写体光を画像データとして出力する撮像手段と、を有し、

40

前記第1アクセス手段は、前記撮像手段によって得られた画像データを前記メモリ手段に書き込み、前記第2アクセス手段は、前記書き込まれた画像データを信号処理するために前記メモリ手段から読み出すことを特徴とする撮像装置。

**【請求項9】**

請求項3に記載のメモリ制御装置と、

入射された被写体光を画像データとして出力する撮像手段と、

前記画像データを変倍する変倍手段と、

前記画像データを変調する変調手段と、を有し、

前記第1アクセス手段は、前記メモリ手段に書き込まれた前記画像データを、前記変調手段によって変調するために前記メモリ手段から読み出し、

50

前記第2アクセス手段は、前記変倍手段によって変倍処理が行われた画像データを前記メモリ手段に書き込むことを特徴とする撮像装置。

【請求項10】

請求項5に記載のメモリ制御装置と、

入射された被写体光を画像データとして出力する撮像手段と、

前記画像データに信号処理を施す処理手段と、

前記画像データを変倍する変倍手段と、を有し、

前記第1アクセス手段は、前記処理手段によって信号処理が行われた画像データを前記メモリ手段に書き込み、

前記第2アクセス手段は、前記書き込まれた画像データを前記変倍手段によって変倍処理するために前記メモリ手段から読み出すことを特徴とする撮像装置。

10

【請求項11】

データを記憶するメモリ手段に対して行われるアクセスを制御するメモリ制御方法であつて、

前記メモリ手段の2次元的な領域に連続的に書き込みを行う第1アクセスステップと、

前記第1アクセスステップで書き込まれた、前記メモリ手段の2次元的な領域を分割した分割領域から読み出しを行う第2アクセスステップと、

前記第1アクセスステップで最後に書き込みが行われた前記メモリ手段のアドレスと、前記第2アクセスステップで次に読み出しが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセスステップでの読み出しを一時停止させ、

20

前記間隔が一定間隔より大きいときには、前記第2アクセスステップでの読み出しを繰り返すことを特徴とするメモリ制御方法。

【請求項12】

データを記憶するメモリ手段に対して行われるアクセスを制御するメモリ制御方法であつて、

前記メモリ手段の2次元的な領域に連続的に読み出しを行う第1アクセスステップと、

前記第1アクセスステップで読み出された、前記メモリ手段の2次元的な領域を分割した分割領域に書き込みを行う第2アクセスステップと、

前記メモリ制御ステップでは、前記第1アクセスステップで最後に読み出しが行われた前記メモリ手段のアドレスと、前記第2アクセスステップで次に書き込みが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセスステップでの書き込みを一時停止させ、

30

前記間隔が一定間隔より大きいときには、前記第2アクセスステップでの書き込みを繰り返すことを特徴とするメモリ制御方法。

【請求項13】

データを記憶するメモリ手段に対して行われるアクセスを制御するメモリ制御方法であつて、

前記メモリ手段の2次元的な領域を分割した第1分割領域に書き込みを行う第1アクセスステップと、

40

前記第1アクセスステップで書き込まれた領域に、前記第1分割領域とは異なる分割をした第2分割領域から読み出しを行う第2アクセスステップと、

前記第1アクセスステップで次に書き込みが行われる前記メモリ手段のアドレスと、前記第2アクセスステップで次に読み出しが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセスステップでの読み出しを一時停止させ、

前記間隔が一定間隔より大きいときには、前記第2アクセスステップでの読み出しを繰り返すことを特徴とするメモリ制御方法。

【発明の詳細な説明】

【技術分野】

50

**【0001】**

本発明は、データを記憶するメモリに対して行われるアクセスを制御するメモリ制御装置、撮像装置およびメモリ制御方法に関する。

**【背景技術】****【0002】**

近年、デジタルカメラなどの電子カメラに使用される撮像素子の画素数は、数百万画素から1000万画素を越えるサイズのものになっている。そのような撮像素子により得られた画像データを処理する際、メモリに対してデータの読み出しや書き込みを行うと、画像サイズが大きくなるに伴って処理時間が長くなってしまう。

**【0003】**

10

メモリへの書き込み時間および読み出し時間を短縮させるために、例えば、撮像素子から得られた画像データをメモリに書き込み、直後にメモリからその画像データを読み出して画像処理を行うことが行われる。この場合、読み出しアドレスが書き込み中のアドレスを追い越さないように、書き込み処理と読み出し処理を並行して実行する追い越し制御方法が用いられる。

**【0004】**

20

従来、このような追い越し制御方法において、読み出し処理が書き込み処理を追い越さないようにメモリアクセスを行う技術が提案されている（特許文献1参照）。この技術では、メモリに書き込んだデータを読み出す処理の過程で、読み出し回数をカウントするリードカウンタ、および書き込み回数をカウントするライトカウンタが用いられる。読み出し回数と書き込み回数との差分値が上限閾値を越えると、その差分値を小さくするために、追われる側の書き込み処理を停止する。一方、その差分値が下限閾値を満たさないと、その差分値を大きくするために、追う側の読み出し処理を停止する。

**【0005】**

また一方、撮像素子から得られた画像データの信号処理を行う際、垂直フィルタが用いられる。また、ラインメモリは垂直フィルタのタップ数分必要とされる。水平方向および垂直方向の画素から構成される画像データを連続して処理する場合、撮像素子のサイズが大きくなればなるほど、水平方向1ラインの画素数も増加し、より容量の大きなラインメモリが必要とされる。このラインメモリを削減するために、画像データを水平方向および垂直方向に分割したブロック毎に画像処理を行う分割処理方法が採用された。

30

**【特許文献1】特開2003-323333号公報****【発明の開示】****【発明が解決しようとする課題】****【0006】**

しかしながら、上記従来のメモリ制御装置では、以下に掲げる問題があった。撮像装置で画像データの分割処理を行う場合、前述したメモリに対し、リードカウンタおよびライトカウンタが用いられていたので、読み出しアドレスと書き込みアドレスの位置関係が不明であった。このため、読み出しアドレスが分割ブロックを移動した際、読み出し処理が書き込み処理を追い越したか否かを判定することが難しかった。

**【0007】**

40

そこで、本発明は、データの分割処理を行う場合であっても、追い越し制御を適正に実行することができるメモリ制御装置、撮像装置およびメモリ制御方法を提供することを目的とする。

**【課題を解決するための手段】****【0008】**

上記目的を達成するために、本発明のメモリ制御装置は、データを記憶するメモリ手段を備え、前記メモリ手段に対して行われるアクセスを制御するメモリ制御装置であって、前記メモリ手段の2次元的な領域に連続的に書き込みを行う第1アクセス手段と、前記第1アクセス手段によって書き込まれた、前記メモリ手段の2次元的な領域を分割した分割領域から読み出しを行う第2アクセス手段と、前記第1および第2アクセス手段を制御す

50

るメモリ制御手段とを備え、前記メモリ制御手段は、前記第1アクセス手段によって最後に書き込みが行われた前記メモリ手段のアドレスと、前記第2アクセス手段によって次に読み出しが行われる前記メモリ手段のアドレスとの間隔が、一定間隔より小さいときには、前記第2アクセス手段による読み出しを行わせず、前記間隔が一定間隔より大きいときには、前記第2アクセス手段による読み出しを行わせることを特徴とする。

【発明の効果】

【0010】

本発明の請求項1に係るメモリ制御装置によれば、データの分割処理を行う場合であっても、追い越し制御を適正に実行することができる。

【0012】

請求項7に係るメモリ制御装置によれば、前記第1アクセス手段の処理が終了すると、前記第2アクセス手段のアドレスが前記一定間隔以上進めなくなってしまい、処理が完了できなくなるのを防止することができる。

【0016】

請求項3に係るメモリ制御装置によれば、データを分割してメモリ手段に書き込みながら、書き込まれたデータを一括してメモリ手段から読み出して変調を行う際に有効である。

【0017】

請求項5に係るメモリ制御装置によれば、データを分割してメモリ手段に書き込みながら、書き込まれたデータを分割してメモリ手段から読み出す際に有効である。

【発明を実施するための最良の形態】

【0018】

本発明のメモリ制御装置、撮像装置およびメモリ制御方法の実施の形態について図面を参照しながら説明する。本実施形態のメモリ制御装置は、撮影した画像データをメモリに記憶する撮像装置に適用される。

【0019】

[第1の実施形態]

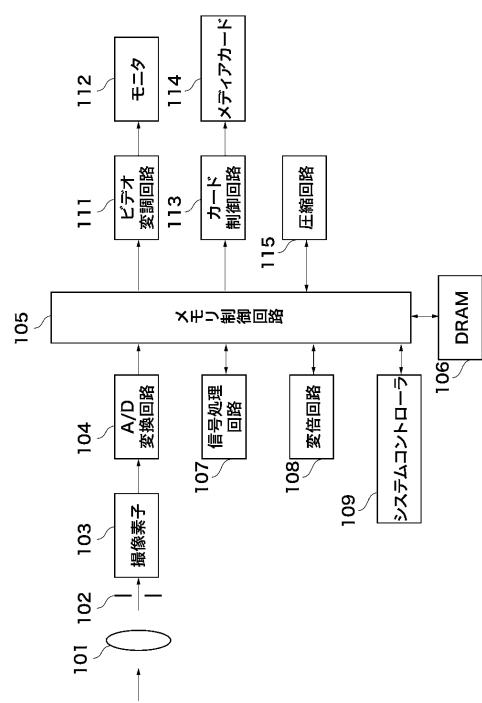

図1は第1の実施形態のメモリ制御装置が適用された撮像装置の構成を示すブロック図である。撮像装置は、撮像レンズ101、絞り102、光信号を電気信号に光電変換する撮像素子103、電気信号であるアナログ画像信号をデジタル画像データに変換するA/D変換回路104、およびこの画像データを一時記憶するDRAM106を有する。

【0020】

また、撮像装置は、DRAM106と各回路のバスアービトレーションを行うメモリ制御回路105、補間処理や色変換処理などの画像処理を行う信号処理回路107、および画像データの縮小や拡大を行う変倍回路108を有する。

【0021】

また、撮像装置は、各回路のモードやパラメータを決定するシステムコントローラ109、画像データを表示するモニタ112、およびモニタ112で画像データを再生するためのビデオ変調回路111を有する。

【0022】

また、撮像装置は、画像データをJPEG圧縮方式などで圧縮及び伸長する圧縮回路115、この圧縮された画像データを記録する脱着可能なメディアカード114、およびこのメディアカード114とのインターフェースを行うカード制御回路113を有する。

【0023】

上記構成を有する撮像装置の動作を示す。始めに、撮影が行われていない状態では、レンズ101に入射した被写体光は、絞り102を通して、適正に露出された状態で撮像素子103によって電気信号に変換される。撮像素子103から得られた被写体光の電気信号は、A/D変換回路104でアナログ画像信号からデジタル画像データに変換される。

【0024】

A/D変換回路104で得られた画像データは、メモリ制御回路105によってDRAM

10

20

30

40

50

M106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によって信号処理回路107に読み出される。

#### 【0025】

信号処理回路107では、補間処理や色変換処理などの処理が施され、輝度色差信号である画像データに変換される。信号処理回路107で処理された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。

#### 【0026】

DRAM106に書き込まれた画像データは、メモリ制御回路105によって変倍回路108に転送されるべく読み出される。変倍回路108は、画像データをモニタ112で再生するために、例えば $720 \times 240$ のサイズに変倍する。変倍回路108で変倍された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によってビデオ変調回路111に転送されるべく読み出される。

#### 【0027】

ビデオ変調回路111で画像データのエンコードが行われると、モニタ112には、画像データが表示される。

#### 【0028】

そして、撮影が開始されると、レンズ101に入射した被写体光は、絞り102を通過し、適正に露出された状態で撮像素子103によって電気信号に変換され、A/D変換回路104によってデジタル画像データに変換される。

#### 【0029】

A/D変換回路104で得られた画像データは、メモリ制御回路105によってDRAM106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によって信号処理回路107に転送されるべく読み出される。

#### 【0030】

信号処理回路107では、適切な処理が施される。信号処理回路107で処理された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によって変倍回路108に転送されるべく読み出される。

#### 【0031】

変倍回路108は、画像データを所定のサイズに変倍する。変倍回路108で変倍された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によって圧縮回路115に転送されるべく読み出される。

#### 【0032】

圧縮回路115は、画像データをJPEG等の圧縮方式で圧縮する。圧縮回路115で圧縮された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。DRAM106に書き込まれた画像データは、メモリ制御回路105によってカード制御回路113に読み出される。カード制御回路113は、圧縮された画像データをメディアカード114に書き込む。

#### 【0033】

前述したように、撮像素子103から、被写体光が二次元的に連続して変換された電気信号が出力されると、A/D変換回路104でデジタル値に変換された画像データは、メモリ制御回路105によってDRAM106に書き込まれる。このとき、DRAM106上のアドレスをジャンプすることなく、一括して画像データの書き込みが行われる。

#### 【0034】

また、メモリ制御回路105によってDRAM106から書き込まれた画像データが読み出されると、信号処理回路107は、読み出された画像データに対して画像処理を行う。このとき、信号処理回路107は、画像データを水平方向および垂直方向に複数分割して画像処理を行うので、メモリ制御回路105は、画像データを分割してDRAM106

10

20

30

40

50

から読み出す。

**【0035】**

つぎに、メモリ制御回路105によってDRAM106に一括して書き込まれた画像データを、メモリ制御回路105が水平方向および垂直方向に分割して二次元的に不連続で読み出し、信号処理回路107で画像処理を行う際の動作を示す。

**【0036】**

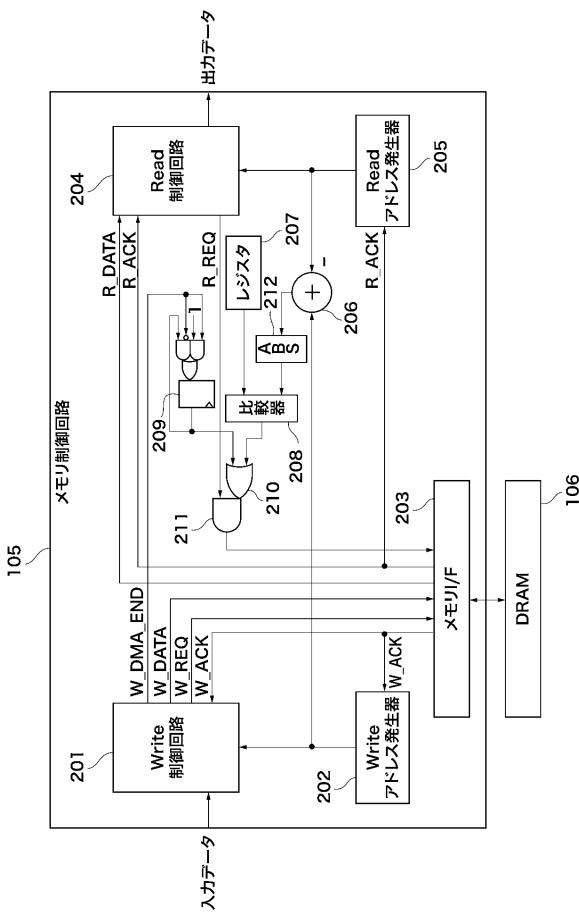

図2はメモリ制御回路105の構成を示す回路図である。ライト(Write)制御回路201は、DRAM106への書き込み処理を制御する。ライト(Write)アドレス発生器202は、画像データをDRAM106に書き込む際のアドレスを生成する。リード(Read)制御回路204は、DRAM106からの読み出し処理を制御する。リード(Read)アドレス発生器205は、画像データをDRAM106から読み出す際のアドレスを生成する。

10

**【0037】**

メモリI/F203は、Write制御回路201およびRead制御回路204から入力する制御信号に従って、DRAM106とのインターフェースを行う。減算器206は、Writeアドレス発生器202が出力するWriteアドレスからReadアドレス発生器205が出力するReadアドレスを減算する。

**【0038】**

絶対値回路(ABS回路)212は、減算器206の出力値から絶対値を算出する。レジスタ207には、WriteアドレスとReadアドレスが最も近づける距離(一定のアドレス間隔)が設定される。比較器208は、ABS回路212の出力値とレジスタ207の設定値を比較する。

20

**【0039】**

フリップフロップ209は、Write制御回路201から信号W\_DMA-ENDが出力されるタイミングで値1をホールドする。OR回路210は、フリップフロップ209が値1をホールドしている期間、Read制御回路204から出力される信号R\_REQのマスクを解除する。AND回路211は、OR回路210からの出力値が値0である場合、信号R\_REQをマスクする。

**【0040】**

また、データW\_DATAは、Write制御回路201からメモリI/F203に出力され、DRAM106に書き込まれる。リクエスト信号W\_REQは、Write制御回路201からメモリI/F203に出力され、DRAM106への書き込みを行うようにメモリI/F203に命令する信号である。

30

**【0041】**

アクノレッジ信号W\_ACKは、メモリI/F203がリクエスト信号W\_REQを受け付けてデータW\_DATAをDRAM106に書き込むと、メモリI/F203からWrite制御回路201に出力される。信号W\_DMA-ENDは、Write処理が完了した時、Write制御回路201から出力されるHighレベルのパルス信号である。

40

**【0042】**

データR\_DATAは、DRAM106から読み出され、メモリI/F203からRead制御回路204に出力されるデータである。リクエスト信号R\_REQは、Read制御回路204から出力され、DRAM106から読み出しを行うようにメモリI/F203に命令する信号である。

**【0043】**

アクノレッジ信号R\_ACKは、メモリI/F203がリクエスト信号R\_REQを受け付けてデータR\_DATAをDRAM106から読み出すと、メモリI/F203からRead制御回路204に出力される。

**【0044】**

A/D変換回路104から出力される画像データは、入力データとしてメモリ制御回路

50

105内のWrite制御回路201に入力される。

**【0045】**

また、Writeアドレス発生器202は、DRAM106に書き込む際のWriteアドレスを生成し、Write制御回路201に出力する。Write制御回路201は、リクエスト信号W\_REQをメモリI/F203に送信すると同時に、入力データをデータW\_DATAとしてメモリI/F203に送信する。

**【0046】**

メモリI/F203は、リクエスト信号W\_REQを受け付けると、データW\_DATAをDRAM106に書き込み、Write制御回路201およびWriteアドレス発生器202にアクノレッジ信号W\_ACKを送信する。

10

**【0047】**

Writeアドレス発生器202は、アクノレッジ信号W\_ACKを受信すると、次に書き込むWriteアドレスをWrite制御回路201に出力する。

**【0048】**

一方、Readアドレス発生器205は、DRAM106から画像データを読み出すためのReadアドレスをRead制御回路204に出力する。Read制御回路204は、リクエスト信号R\_REQをAND回路211に出力する。

**【0049】**

減算器206は、前述したように、Writeアドレス発生器202から出力されたWriteアドレスから、Readアドレス発生器205から出力されたReadアドレスを減算し、WriteアドレスおよびReadアドレス間の距離を求める。

20

**【0050】**

ABS回路212は、前述したように、WriteアドレスとReadアドレスの差分の絶対値をとる。レジスタ207には、前述したように、WriteアドレスとReadアドレスが最も近づける距離が設定される。比較器208は、前述したように、ABS回路212の出力値とレジスタ207に設定された値を比較し、ABS回路212の出力値がレジスタ207の設定値より大きい場合、Highレベルの信号をOR回路210に出力する。

**【0051】**

フリップフロップ209は、Write処理が終了しない期間、すなわちWrite制御回路201から信号W\_DMA-ENDとしてHighレベルのパルス信号が出力される前、Lowレベルを保持した状態である。

30

**【0052】**

Write処理が終了すると、Write制御回路201から信号W\_DMA-ENDとしてHighレベルのパルス信号が出力され、フリップフロップ209は、Highレベルを保持した状態になる。フリップフロップ209に保持された信号は、OR回路210に出力される。すなわち、Write処理が終了しない期間、Read処理がWrite処理に近づき、その差がレジスタ207の設定値未満になると、比較器208の出力信号は、Lowレベルとなり、リクエスト信号R\_REQをマスクしてRead処理を一時停止させる。そして、Write処理の終了後、比較器208の出力信号が無効化されると、リクエスト信号R\_REQはマスクされることなく、残りのRead処理が行われる。

40

**【0053】**

メモリI/F203でリクエスト信号R\_REQが受け付けられると、DRAM106から読み出された画像データは、データR\_DATAとしてRead制御回路204に出力される。同時に、メモリI/F203からRead制御回路204およびReadアドレス発生器205にアクノレッジ信号R\_ACKが出力される。Read制御回路204は、アクノレッジ信号R\_ACKを受信すると、データR\_DATAを出力データとして信号処理回路107に出力する。

**【0054】**

50

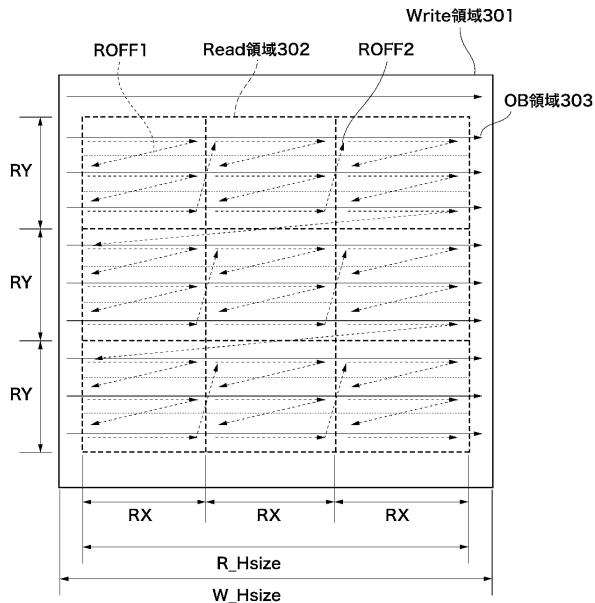

図3はA/D変換回路104からDRAM106への画像データの書き込み順序およびDRAM106から信号処理回路107への画像データの読み出し順序を示す図である。

#### 【0055】

Write領域301は、撮像素子103によって被写体光が二次元的に連続して光電変換された画像データの範囲を表す。このWrite領域301には、OB(Optical Black)領域303が含まれている。

#### 【0056】

Write領域301では、Writeアドレス発生器202によって生成されるWriteアドレスは、DRAM106に書き込まれる画像データの左上から右下に向かってライン毎に順次移動する。ここで、OB領域303は、Read領域302の上下それぞれに1ラインずつ存在するものとする。

10

#### 【0057】

Read領域302は、Write領域301からOB領域303を除いた有効画素領域である。また、図3に示すように、Read領域302では、水平に3分割された1ブロック分の3ラインをRYとし、垂直に3分割された1ブロック分の水平方向の画素数をRXとする。

#### 【0058】

ここでは、Write領域301とRead領域302の開始アドレスが異なっており、WriteアドレスがRead領域302の開始アドレスの通過後にRead処理が開始されることを前提としている。

20

#### 【0059】

メモリ制御回路105は、DRAM106にWrite領域301の画像データを書き込みながら、Read領域302の画像データをDRAM106から読み出す際、Read処理がWrite処理を追い越さないようにRead処理を制御する。このため、Write処理とRead処理の間隔には、追いかけられるWrite処理が行う1ライン分の画像データの長さW\_Hsize以上、距離を設けておく必要がある。

#### 【0060】

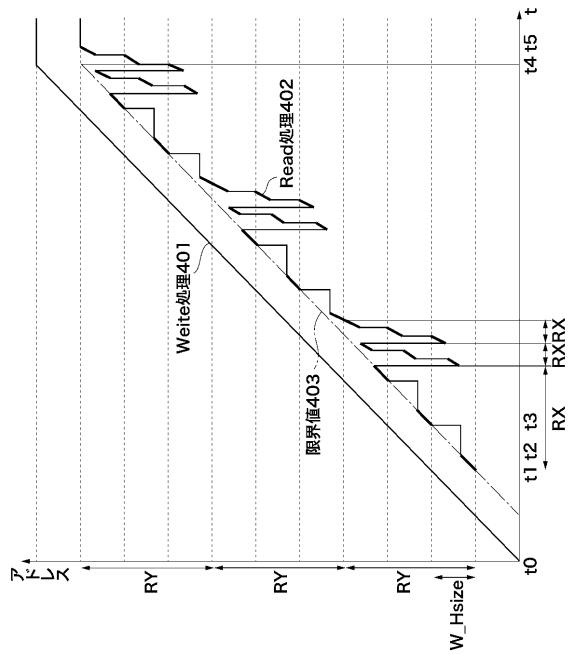

図4はRead処理がWrite処理を追いかける様子を示すタイミングチャートである。図中、横軸は時間t、縦軸はアドレスを表す。Write処理401では、二次元的に連続して書き込みが行われる。

30

#### 【0061】

Read処理402は、Write処理401の2倍の速さで行われ、Write処理401の2ライン目から開始する。なお、Write処理401とRead処理402の処理速度の関係は、これに限られるものではない。また、図中、Write処理401から、1ライン分の画像データの長さW\_Hsizeに相当する距離を、限界値403として示す。Read処理402は、Write処理401から限界値403以上に離れたアドレスのデータの読み出しを行う。

#### 【0062】

具体的に、時刻t0において、Write処理401が開始する。時刻t1において、Read処理402の開始アドレスがWrite処理401から長さW\_Hsizeだけ離れたので、Read処理402は、Write処理401との距離を長さW\_Hsize以上保ちながら読み出しを行う。

40

#### 【0063】

時刻t2において、Read処理402の次のアドレスは、Write処理401との距離が長さW\_Hsize未満になるので、次のラインにジャンプできず、Write処理401との距離が長さW\_Hsize以上離れるまで読み出しを行わずに待つ。

#### 【0064】

時刻t3において、Read処理402の次のアドレスとWrite処理401との距離が長さW\_Hsizeだけ離れたので、Read処理402は、Write処理401との距離を長さW\_Hsize以上保ちながら読み出しを行う。

50

**【0065】**

そして、時刻t4において、Write処理401が終了すると、限界値403は解除され、Read処理402は残りのデータの読み出しを行い、時刻t5においてRead処理402が終了する。

**【0066】**

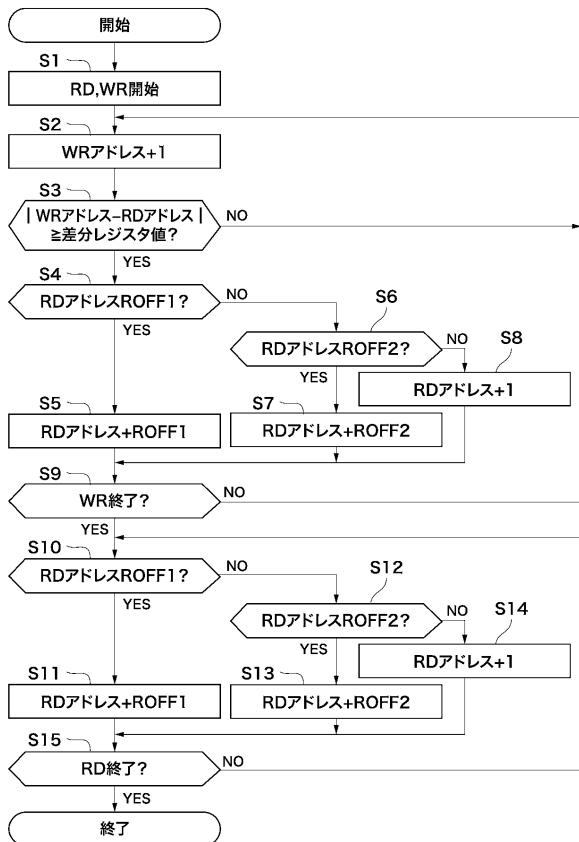

図5は追い越し処理手順を示すフローチャートである。この処理はメモリ制御回路105によって実行される。まず、メモリ制御回路105は、Write処理およびRead処理を開始させる(ステップS1)。Write処理のアドレスを値1進める(ステップS2)。このアドレスでWrite処理が行われる。

**【0067】**

Write処理のアドレスとRead処理のアドレスの距離(絶対値)がレジスタ207の設定値以上であるか否かを判別する(ステップS3)。Write処理のアドレスとRead処理のアドレスの距離がレジスタ207の設定値未満である場合、ステップS2の処理に戻り、Write処理のアドレスを値1進める。

10

**【0068】**

一方、ステップS3でWrite処理のアドレスとRead処理のアドレスの距離がレジスタ207の設定値以上である場合、Read処理の次のアドレスが、図3に示す値R0FF1だけジャンプするか否かを判別する(ステップS4)。Read処理の次のアドレスが値R0FF1だけジャンプする場合、Read処理のアドレスを値R0FF1だけ移動させる(ステップS5)。このアドレスでRead処理が行われる。

20

**【0069】**

一方、ステップS4でRead処理の次のアドレスが値R0FF1だけジャンプしない場合、Read処理の次のアドレスが、図3に示す値R0FF2だけジャンプするか否かを判別する(ステップS6)。Read処理の次のアドレスが値R0FF2だけジャンプする場合、Read処理のアドレスを値R0FF2だけ移動させる(ステップS7)。このアドレスでRead処理が行われる。一方、ステップS6でRead処理の次のアドレスが値R0FF2だけジャンプしない場合、Read処理のアドレスを値1進める(ステップS8)。このアドレスでRead処理が行われる。

**【0070】**

ステップS5、S7あるいはS8の処理後、Write処理の終了判定を行う(ステップS9)。Write処理が終了していない場合、ステップS2に戻って、Write処理のアドレスを値1進める。一方、Write処理が終了している場合、Read処理の次のアドレスが値R0FF1だけジャンプするか否かを判別する(ステップS10)。

30

**【0071】**

Read処理の次のアドレスが値R0FF1だけジャンプする場合、Read処理のアドレスを値R0FF1だけ移動させる(ステップS11)。このアドレスでRead処理が行われる。一方、ステップS10でRead処理の次のアドレスが値R0FF1だけジャンプしない場合、Read処理の次のアドレスが値R0FF2だけジャンプするか否かを判別する(ステップS12)。Read処理の次のアドレスが値R0FF2だけジャンプする場合、Read処理のアドレスを値R0FF2だけ移動させる(ステップS13)。このアドレスでRead処理が行われる。

40

**【0072】**

一方、ステップS12でRead処理の次のアドレスが値R0FF2だけジャンプしない場合、Read処理のアドレスを値1進める(ステップS14)。このアドレスでRead処理が行われる。

**【0073】**

ステップS11、S13あるいはS14の処理後、Read処理の終了判定を行う(ステップS15)。Read処理が終了していない場合、ステップS10に戻って、Read処理のアドレスを値1進める。一方、Read処理が終了すると、本追い越し制御処理を終了させる。

50

**【0074】**

上記追い越し制御を行うことによって、D R A M 1 0 6 から読み出された画像データは、信号処理回路 1 0 7 で画像処理された後、再びメモリ制御回路 1 0 5 によって D R A M 1 0 6 に書き込まれる。

**【0075】**

第 1 の実施形態のメモリ制御装置によれば、画像データの読み出し処理および書き込み処理を並行して実行する際、先行するアドレスと後続するアドレスとの間隔を設定するので、画像データの分割処理を行う場合でも、追い越し制御を適正に実行することができる。

**【0076】**

なお、上記実施形態では、W r i t e 処理およびR e a d 処理を、画像データの左上から右下へ向かう方向で行う場合を示したが、画像データの左下から右上へ向かう方向でW r i t e 処理およびR e a d 処理を行う場合についても対応可能である。

**【0077】**

この場合も、上記追い越し処理を行うためのメモリ制御回路 1 0 5 は、図 2 と同様の構成を有するので、その説明を省略する。ここで、A B S 回路 2 1 2 は、W r i t e アドレスとR e a d アドレスの位置関係を示す符号を消去するので、両者の前後関係は無視される。また、上記追い越し処理を行う手順は、図 5 に示したフローチャートと同様であるので、その説明を省略する。

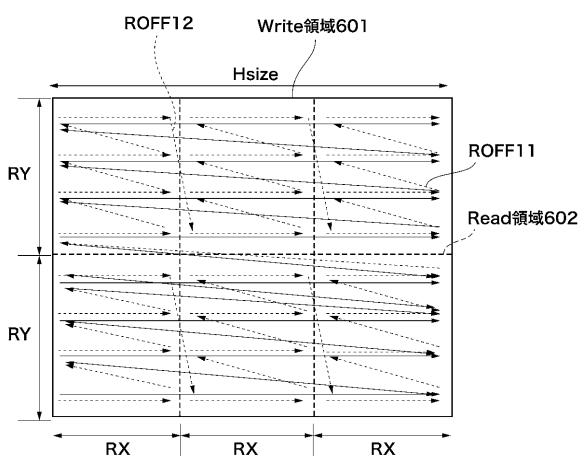

**【0078】**

図 6 は画像データの左下から右上へ向かう方向でW r i t e 処理およびR e a d 処理を行う場合のA / D 変換回路 1 0 4 からD R A M 1 0 6 への画像データの書き込み順序およびD R A M 1 0 6 から信号処理回路 1 0 7 への画像データの読み出し順序を示す図である。

**【0079】**

このW r i t e 処理およびR e a d 処理では、O B 領域がなく同じサイズの画像データが処理されるものとする。また、W r i t e 処理では、W r i t e 領域 6 0 1 を左下から右上に向かって二次元的に連続して書き込みが行われる。一方、R e a d 処理では、R e a d 領域 6 0 2 を水平に 2 分割、垂直に 3 分割して二次元的に不連続な読み出しが行われる。

**【0080】**

R e a d 領域 6 0 2 において、水平に 2 分割された 1 ブロック分の 4 ラインをR Y とし、垂直に 3 分割された 1 ブロック分の水平方向の画素数をR X とする。また、W r i t e 処理とR e a d 処理の間隔は、長さH s i z e 以上離れるものとする。

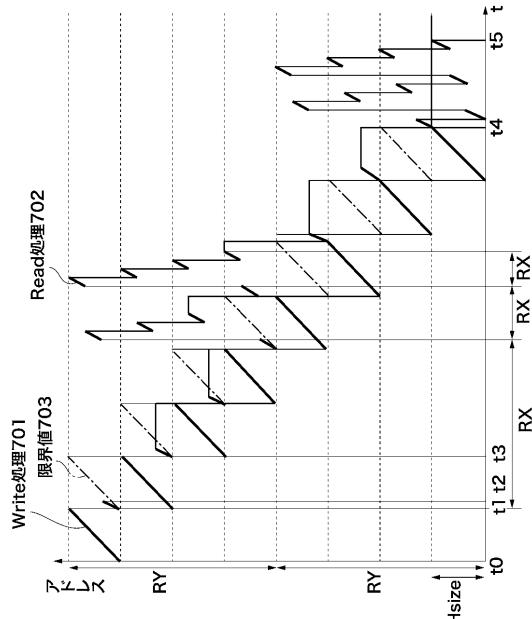

**【0081】**

図 7 はR e a d 処理がW r i t e 処理を追いかける様子を示すタイミングチャートである。図中、横軸は時間t、縦軸はアドレスである。また、W r i t e 処理 7 0 1 から長さH s i z e の距離を限界値 7 0 3 として示す。

**【0082】**

R e a d 処理 7 0 2 では、W r i t e 処理 7 0 1 から限界値 7 0 3 以上に離れたアドレスのデータを読み出す。また、R e a d 処理 7 0 2 は、W r i t e 処理 7 0 1 の 2 倍の速さで行われるものとする。

**【0083】**

具体的に、時刻t 0において、W r i t e 処理 7 0 1 では、画像データの最終ラインの左端から書き込みが行われる。時刻t 1において、1 ラインの処理が終わると、W r i t e アドレスは1 ライン上の左端のアドレスにジャンプする。このとき、W r i t e アドレスおよびR e a d アドレス間の距離が長さH s i z e になるので、R e a d 処理 7 0 2 が開始する。

**【0084】**

時刻t 2において、R e a d 処理 7 0 2 の次のアドレスは、W r i t e 処理 7 0 1 との

10

20

30

40

50

距離が長さ H size 未満となるので、次のラインにジャンプできず、Write 处理 701 との距離が長さ H size 以上離れるまで読み出しを行わずに待つ。

#### 【0085】

時刻 t3において、Read 处理 702 の次のアドレスおよび Write 处理 701 間の距離が長さ H size だけ離れたので、Read 处理 702 は、Write 处理 701 との距離を長さ H size 以上保ちながら読み出しを行う。

#### 【0086】

そして、時刻 t4において、Write 处理 701 が終了すると、限界値 703 は解除され、Read 处理 702 は残りのデータの読み出しを行う。時刻 t5において、Read 处理 702 が終了する。

10

#### 【0087】

##### [第2の実施形態]

撮像装置(図1参照)では、変倍回路 108 で変倍処理された画像データは、メモリ制御回路 105 によってDRAM 106 に書き込まれる。このとき、画像データは、水平方向および垂直方向に複数分割された状態でメモリ制御回路 105 に出力されるので、DRAM 106 のアドレスをジャンプしながら書き込まれる。

#### 【0088】

また、書き込まれた画像データは、メモリ制御回路 105 によってDRAM 106 から読み出され、ビデオ変調回路 111 でビデオ信号に変調される。このとき、ビデオ変調回路 111 における変調は、二次元の画像データを連続的に処理するので、メモリ制御回路 105 によってDRAM 106 のアドレスをジャンプすることなく一括して画像データが読み出される。

20

#### 【0089】

さらに、ビデオ変調回路 111 によって読み出された画像データが記憶されていたDRAM 106 のアドレスに、変倍回路 108 から出力された新たなフレームとなる画像データが上書きされる。

#### 【0090】

第2の実施形態では、DRAM 106 の画像データを一括してビデオ変調回路 111 に読み出し、ビデオ変調回路 111 への読み出しが完了したアドレス領域に変倍回路 108 で変倍された次のフレームの画像データを分割して書き込む。

30

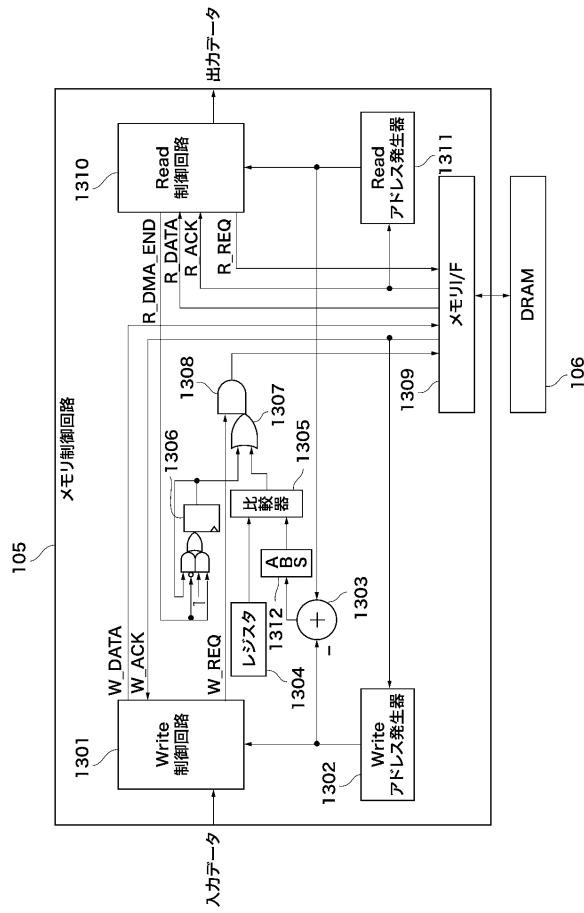

#### 【0091】

図8は第2の実施形態におけるメモリ制御回路 105 の構成を示す回路図である。Read アドレス発生器 1311 は、DRAM 106 から読み出す際の Read アドレスを Read 制御回路 1310 に出力する。Read 制御回路 1310 は、リクエスト信号 RREQ をメモリ I/F 1309 に出力する。

#### 【0092】

メモリ I/F 1309 は、リクエスト信号 RREQ を受け付けると、DRAM 106 から読み出した画像データをデータ RDATA として Read 制御回路 1310 に出力する。同時に、メモリ I/F 1309 から Read 制御回路 1310 および Read アドレス発生器 1311 にアクリエット信号 ACK が出力される。

40

#### 【0093】

Read 制御回路 1310 は、アクリエット信号 ACK を受信すると、データ RDATA を出力データとしてビデオ変調回路 111 に出力する。

#### 【0094】

一方、変倍回路 108 から出力される画像データは、入力データとしてメモリ制御回路 105 内の Write 制御回路 1301 に入力される。Write アドレス発生器 1302 では、DRAM 106 に書き込む際の Write アドレスが生成される。この Write アドレスは、Write 制御回路 1301 に出力される。Write 制御回路 1301 は、リクエスト信号 WREQ を AND 回路 1308 に出力する。

#### 【0095】

50

減算器 1303 は、Write アドレス発生器 1302 から出力された Write アドレスから、Read アドレス発生器 1311 から出力された Read アドレスを減算し、Write アドレスと Read アドレスの差分を求める。ABS 回路 1312 は、Read アドレスと Write アドレスの差分の絶対値を算出する。レジスタ 1304 には、Write 处理と Read 处理が最も近づける距離（一定のアドレス間隔）が設定される。

#### 【0096】

比較器 1305 は、ABS 回路 1312 の出力値とレジスタ 1304 に設定された値を比較し、ABS 回路 1312 の出力値がレジスタ 1304 の設定値より大きい場合、High レベルの信号を OR 回路 1307 に出力する。

#### 【0097】

フリップフロップ 1306 は、Read 处理が終了しない期間、すなわち Read 制御回路 1310 から信号 R\_DMA\_END として High パルスが出力される前、Low レベルを保持した状態である。そして、Read 处理が終了すると、Read 制御回路 1310 から信号 R\_DMA\_END として High パルスが出力され、フリップフロップ 1306 は、High レベルを保持した状態になる。

#### 【0098】

フリップフロップ 1306 に保持された信号は、OR 回路 1307 に出力される。すなわち、Read 处理が終了しない期間、Write 处理が Read 处理に近づき、その差がレジスタ 1304 の設定値未満になると、比較器 1305 の出力信号はリクエスト信号 W\_REQ をマスクして Write 处理を一時停止させる。

#### 【0099】

Read 处理の終了後、比較器 1305 の出力信号は無効化され、リクエスト信号 W\_REQ はマスクされることなく、残りの Write 处理が行われる。

#### 【0100】

メモリ I/F 1309 では、リクエスト信号 W\_REQ が受け付けられると、Write 制御回路 1301 からデータ W\_DATA として出力される画像データが DRAM 106 に書き込まれる。同時に、メモリ I/F 1309 から Write 制御回路 1301 および Write アドレス発生器 1302 へアクノレッジ信号 W\_ACK が出力される。Write アドレス発生器 1302 は、アクノレッジ信号 W\_ACK を受信すると、Write 处理の次のアドレスを Write 制御回路 1301 に出力する。

#### 【0101】

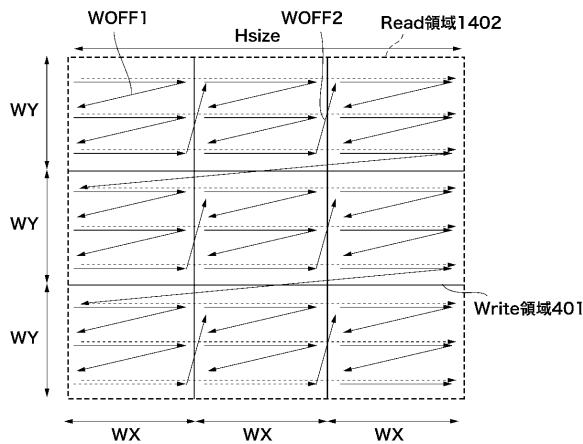

図 9 は変倍回路 108 から DRAM 106 への画像データの書き込み順序および DRAM 106 からビデオ変調回路 111 への画像データの読み出し順序を示す図である。ここで、Write 处理および Read 处理では、同じサイズの画像データが処理されるものとする。

#### 【0102】

Read 領域 1402 では、Read アドレス発生器 1311 によって生成される Read アドレスは、DRAM 106 から読み出される画像データの左上から右下に向かって順次移動する。

#### 【0103】

また、変倍回路 108 の処理は、画像データを水平方向および垂直方向に複数に分割して行われるものとする。このため、メモリ制御回路 105 は、DRAM 106 に画像データを分割して書き込む。図 9 に示すように、Write 領域 1401 では、水平に 3 分割された 1 ブロック分の 3 ラインを WY とし、垂直に 3 分割された 1 ブロック分の水平方向の画素数を WX とする。

#### 【0104】

メモリ制御回路 105 は、DRAM 106 から Read 領域 1402 のデータを読み出しながら、Write 領域 1401 にデータを書き込む際、Write 处理が Read 处理を追い越さないように、Write 处理を制御する。本実施形態では、Write 处理と Read 处理の間隔に長さ H\_size 以上の距離をおく必要がある。

10

20

30

40

50

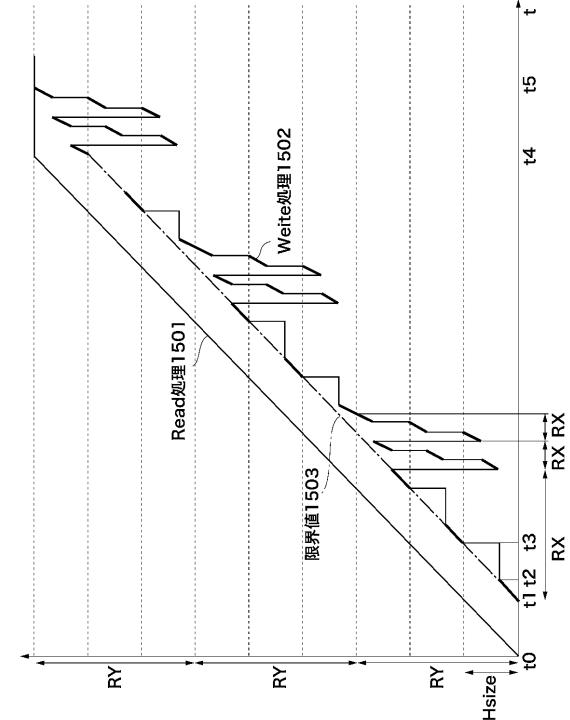

**【0105】**

図10はWrite処理がRead処理を追いかける様子を示すタイミングチャートである。図中、横軸は時間t、縦軸はアドレスである。また、Write処理1502は、Read処理1501の2倍の速さで行われるものとする。

**【0106】**

Read処理1501から長さHsize離れた位置を限界値1503として示す。Write処理1502では、Read処理1501から限界値1503以上に離れたアドレスのデータを書き込む。

**【0107】**

具体的に、時刻t0において、Read処理1501が開始する。時刻t1において、Write処理1502の開始アドレスがRead処理1501から長さHsizeだけ離れたので、Write処理1502では、Read処理1501との距離を長さHsize以上保ちながら書き込みが行われる。10

**【0108】**

時刻t2において、Write処理1502の次のアドレスは、Read処理1501との距離が長さHsize未満になるので、次のラインにジャンプできず、Read処理1501との距離が長さHsize以上離れるまで書き込みを行わずに待つ。

**【0109】**

時刻t3において、Write処理1502の次のアドレスとRead処理1501との距離が長さHsizeだけ離れたので、Write処理1502では、Read処理1501との距離を長さHsize以上保ちながら書き込みが行われる。20

**【0110】**

そして、時刻t4において、Read処理1501が終了すると、限界値1103は解除され、Write処理1502では、残りのデータの書き込みが行われる。さらに、時刻t5において、Write処理1502が終了する。

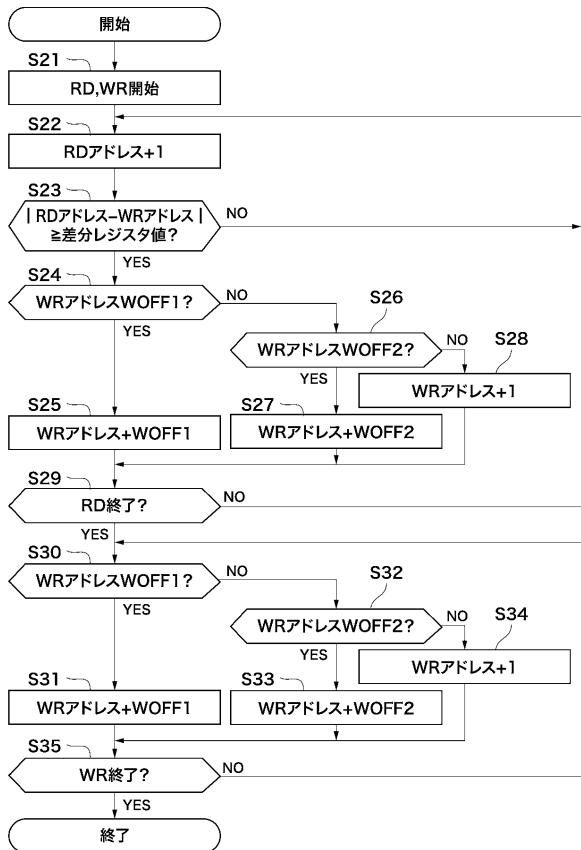

**【0111】**

図11は追い越し処理手順を示すフローチャートである。この処理はメモリ制御回路105によって実行される。まず、メモリ制御回路105は、Read処理およびWrite処理を開始させる(ステップS21)。このアドレスでRead処理が行われる。

**【0112】**

Read処理のアドレスを値1進める(ステップS22)。Write処理のアドレスとRead処理のアドレスの距離がレジスタ1304の設定値以上であるか否かを判別する(ステップS23)。設定値未満である場合、ステップS22に戻ってRead処理のアドレスを値1進める。30

**【0113】**

一方、レジスタ1304の設定値以上である場合、Write処理の次のアドレスが図9に示す値WOFF1だけジャンプするか否かを判別する(ステップS24)。Write処理の次のアドレスが値WOFF1だけジャンプする場合、Write処理のアドレスを値WOFF1だけ移動させる(ステップS25)。このアドレスでWrite処理が行われる。40

**【0114】**

一方、ステップS24でWrite処理の次のアドレスが値WOFF1だけジャンプしない場合、Write処理の次のアドレスが値WOFF2だけジャンプするか否かを判別する(ステップS26)。Write処理の次のアドレスが値WOFF2だけジャンプする場合、Write処理のアドレスを値WOFF2だけ移動させる(ステップS27)。このアドレスでWrite処理が行われる。

**【0115】**

一方、ステップS26でWrite処理の次のアドレスがジャンプしない場合、Write処理のアドレスを値1進める(ステップS28)。このアドレスでWrite処理が行われる。50

**【0116】**

ステップS25、S27あるいはS28の処理後、Read処理の終了判定を行う（ステップS29）。Read処理が終了していない場合、ステップS22に戻ってRead処理のアドレスを値1進める。

**【0117】**

一方、Read処理が終了すると、Write処理の次のアドレスが値WOFF1だけジャンプするか否かを判別する（ステップS30）。Write処理の次のアドレスが値WOFF1だけジャンプする場合、Write処理のアドレスを値WOFF1だけ移動させる（ステップS31）。このアドレスでWrite処理が行われる。

**【0118】**

一方、ステップS30でWrite処理の次のアドレスが値WOFF1だけジャンプしない場合、Write処理の次のアドレスが値WOFF2だけジャンプするか否かを判別する（ステップS32）。Write処理の次のアドレスが値WOFF2だけジャンプする場合、Write処理のアドレスをWOFF2だけ移動させる（ステップS33）。このアドレスでWrite処理が行われる。

**【0119】**

一方、ステップS32でWrite処理の次のアドレスがジャンプしない場合、Write処理のアドレスを値1進める（ステップS34）。このアドレスでWrite処理が行われる。

**【0120】**

ステップS31、S33あるいはS34の処理後、Write処理の終了判定を行う（ステップS35）。Write処理が終了していない場合、ステップS30に戻る。一方、Write処理が終了すると、本追い越し制御処理が終了する。

**【0121】**

上記追い越し制御を行うことで、DRAM106から読み出された画像データは、ビデオ変調回路111でビデオ信号に変調された後、モニタ112に表示される。

**【0122】**

このように、第2の実施形態のメモリ制御装置によれば、画像データの読み出し処理および書き込み処理を並行して実行する際、先行するアドレスと後続するアドレスとの間隔を設定する。これにより、画像データの分割処理を行う場合でも、撮像装置における追い越し制御を適正に実行することができる。

**【0123】****[第3の実施形態]**

撮像装置（図1参照）では、信号処理回路107で画像処理された画像データは、メモリ制御回路105によってDRAM106に書き込まれる際、画像データは水平方向及び垂直方向に複数に分割された状態でメモリ制御回路105に出力される。従って、DRAM106のアドレスをジャンプさせながら画像データが書き込まれる。

**【0124】**

また、書き込まれた画像データは、メモリ制御回路105によってDRAM106から読み出され、変倍回路108で変倍処理が行われる。変倍回路108における変倍処理は、画像データを水平方向および垂直方向に複数に分割して行われるので、メモリ制御回路105はDRAM106から画像データを分割して読み出す。

**【0125】**

第3の実施形態では、メモリ制御回路105が信号処理回路107で処理された画像データを水平方向および垂直方向に分割してDRAM106に書き込み、その画像データを水平方向および垂直方向に分割して読み出して変倍回路108に出力する場合を示す。

**【0126】**

ここで、第3の実施形態におけるメモリ制御回路105の構成は、前記第1の実施形態に示した回路図（図2参照）と同様である。また、図2の入力データとして、信号処理回路107から出力される画像データが入力される。また、図2の出力データは変倍回路1

10

20

30

40

50

08に出力される。

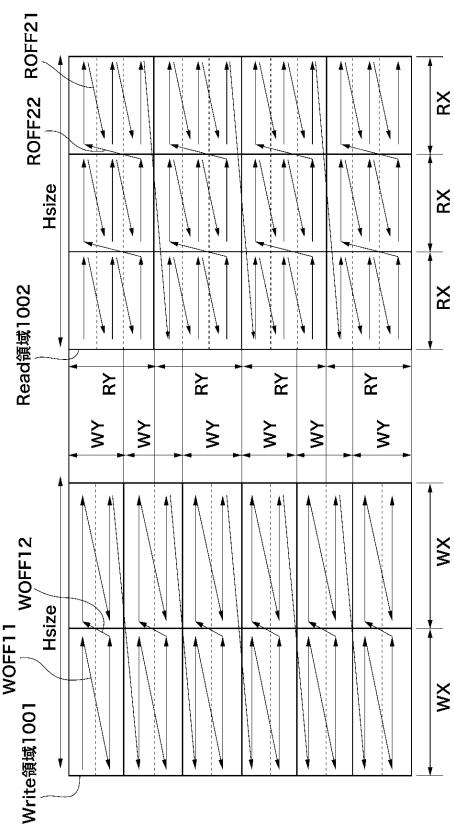

**【0127】**

図12は第3の実施形態における信号処理回路107からDRAM106への画像データの書き込み順序およびDRAM106から変倍回路108への画像データの読み出し順序を示す図である。なお、Write処理およびRead処理は同じサイズの画像データを処理するものとする。

**【0128】**

Write領域1001において、水平に6分割された1ブロック分の2ラインをWYとし、垂直に2分割された1ブロック分の水平方向の画素数をWXとする。また、Read領域1002において、水平に4分割された1ブロック分の3ラインをRYとし、垂直に3分割された1ブロック分の水平方向の画素数をRXとする。

10

**【0129】**

メモリ制御回路105は、DRAM106にWrite領域1001の画像データを書き込みながら、Read領域1002の画像データを読み出す際、Read処理がWrite処理を追い越さないようにRead処理を制御する。

**【0130】**

このように、分割処理が分割処理を追いかける場合、水平に分割された1ブロック当たりのライン数が大きい方のライン数をLargeYとすると、両者の間隔は、数式(1)に示す値以上である。

**【0131】**

$$2 \times \text{LargeY} \times \text{Hsize} \dots (1)$$

常に、両者の間隔の最短距離を、数式(1)で示される値に定めておくことで、どのような大きさに分割されたとしても、追い越しは発生しない。図12では、ライン数WYよりライン数RYの方が多いので、ライン数LargeYはライン数RYとなる。

**【0132】**

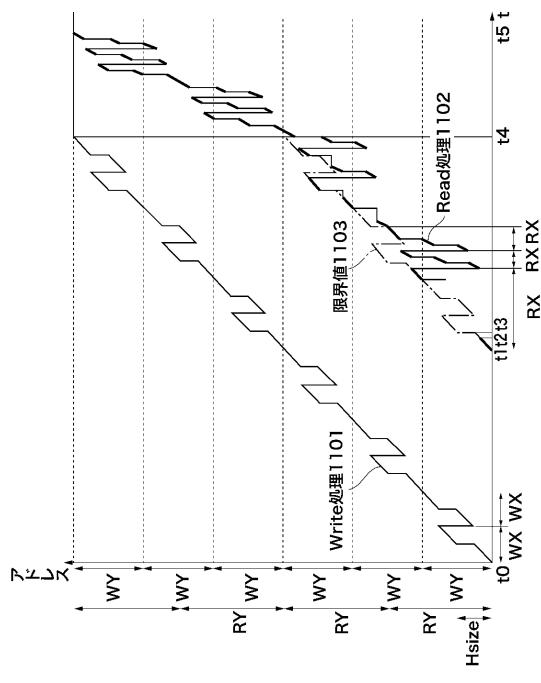

図13はRead処理がWrite処理を追いかける様子を示すタイミングチャートである。図中、横軸は時間t、縦軸はアドレスである。また、Read処理1102は、Write処理1101の2倍の速さで行われるものとする。また、Write処理1101から数式(1)で示される距離を、限界値1103として示す。Read処理1102は、Write処理1101から限界値1103以上に離れたアドレスのデータを読み出す。

30

**【0133】**

時刻t0において、Write処理1101が開始する。時刻t1において、Read処理1102の開始アドレスがWrite処理1101から数式(1)で示される距離だけ離れたので、Read処理1102は、Write処理1101との距離を数式(1)で示される距離以上保ちながら読み出しを行う。

**【0134】**

時刻t2において、Read処理1102の次のアドレスは、Write処理1101との距離が数式(1)の距離以下になるので、次のラインにジャンプできず、Write処理1101との距離が数式(1)の距離以上離れるまで読み出しを行わずに待つ。

40

**【0135】**

時刻t3において、Read処理1102の次のアドレスとWrite処理1101との距離が数式(1)の距離だけ離れたので、Read処理1102は、Write処理1101との距離を数式(1)の距離以上保ちながら読み出しを行う。

**【0136】**

時刻t4において、Write処理1101が終了すると、限界値1103は解除され、Read処理1102は残りのデータの読み出しを行い、時刻t5においてRead処理1102が終了する。

**【0137】**

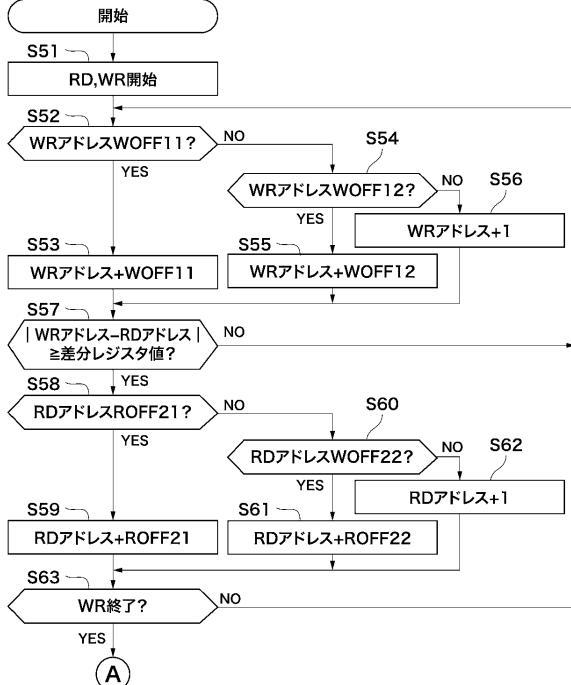

図14および図15は追い越し処理手順を示すフローチャートである。この処理はメモ

50

リ制御回路105によって実行される。まず、メモリ制御回路105は、W<sub>rite</sub>処理およびR<sub>ead</sub>処理を開始させる(ステップS51)。W<sub>rite</sub>処理の次のアドレスが図12に示す値WFFF11だけジャンプするか否かを判別する(ステップS52)。

#### 【0138】

W<sub>rite</sub>処理の次のアドレスが値WFFF11だけジャンプする場合、W<sub>rite</sub>処理のアドレスを値WFFF11だけ移動させる(ステップS53)。このアドレスでW<sub>rite</sub>処理が行われる。

#### 【0139】

一方、W<sub>rite</sub>処理の次のアドレスが値WFFF11だけジャンプしない場合、W<sub>rite</sub>処理の次のアドレスが図12に示す値WFFF12だけジャンプするか否かを判別する(ステップS54)。W<sub>rite</sub>処理の次のアドレスが値WFFF12だけジャンプする場合、W<sub>rite</sub>処理のアドレスを値WFFF12だけ移動させる(ステップS55)。このアドレスでW<sub>rite</sub>処理が行われる。

10

#### 【0140】

一方、W<sub>rite</sub>処理の次のアドレスがジャンプしない場合、W<sub>rite</sub>処理のアドレスを1進める(ステップS56)。このアドレスでW<sub>rite</sub>処理が行われる。

#### 【0141】

ステップS53、S55あるいはS56の処理後、W<sub>rite</sub>処理のアドレスおよびR<sub>ead</sub>処理のアドレス間の距離がレジスタ207の設定値以上であるか否かを判別する(ステップS57)。レジスタ207の設定値未満である場合、ステップS52の処理に戻り、W<sub>rite</sub>処理のアドレスを進める。

20

#### 【0142】

一方、ステップS57でW<sub>rite</sub>処理のアドレスとR<sub>ead</sub>処理のアドレスの距離がレジスタ207の設定値以上である場合、R<sub>ead</sub>処理のアドレスを進める。

#### 【0143】

即ち、R<sub>ead</sub>処理の次のアドレスが図12に示す値ROFF21だけジャンプするか否かを判別する(ステップS58)。R<sub>ead</sub>処理の次のアドレスが値ROFF21だけジャンプする場合、R<sub>ead</sub>処理のアドレスを値ROFF21だけ移動させる(ステップS59)。このアドレスでR<sub>ead</sub>処理が行われる。

#### 【0144】

一方、ステップS58でR<sub>ead</sub>処理の次のアドレスが値ROFF21だけジャンプしない場合、R<sub>ead</sub>処理の次のアドレスが図12に示す値ROFF22だけジャンプするか否かを判別する(ステップS60)。R<sub>ead</sub>処理の次のアドレスが値ROFF22だけジャンプする場合、R<sub>ead</sub>処理のアドレスを値ROFF22だけ移動させる(ステップS61)。このアドレスでR<sub>ead</sub>処理が行われる。

30

#### 【0145】

一方、R<sub>ead</sub>処理の次のアドレスがジャンプしない場合、R<sub>ead</sub>処理のアドレスを1進める(ステップS62)。このアドレスでR<sub>ead</sub>処理が行われる。

#### 【0146】

ステップS59、S61あるいはS62の処理後、W<sub>rite</sub>処理の終了判定を行う(ステップS63)。W<sub>rite</sub>処理が終了していない場合、ステップS52に戻り、W<sub>rite</sub>処理のアドレスを進める。

40

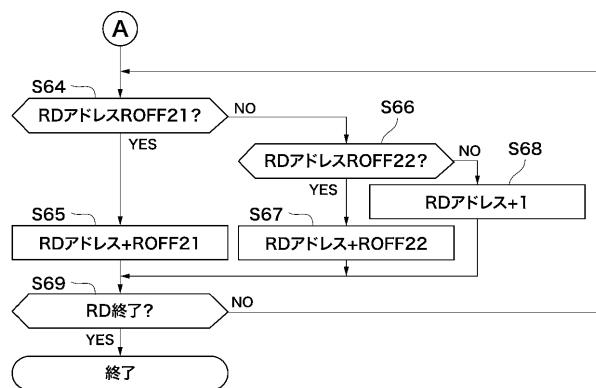

#### 【0147】

一方、ステップS63でW<sub>rite</sub>処理が終了すると、R<sub>ead</sub>処理の次のアドレスが値ROFF21だけジャンプするか否かを判別する(ステップS64)。R<sub>ead</sub>処理の次のアドレスが値ROFF21だけジャンプする場合、R<sub>ead</sub>処理のアドレスを値ROFF21だけ移動させる(ステップS65)。このアドレスでR<sub>ead</sub>処理が行われる。

#### 【0148】

一方、ステップS64でR<sub>ead</sub>処理の次のアドレスが値ROFF21だけジャンプしない場合、R<sub>ead</sub>処理の次のアドレスが値ROFF22だけジャンプするか否かを判別

50

する（ステップS66）。Read処理の次のアドレスが値RFFF22だけジャンプする場合、Read処理のアドレスを値RFFF22だけ移動させる（ステップS67）。このアドレスでRead処理が行われる。

#### 【0149】

一方、Read処理の次のアドレスがジャンプしない場合、Read処理のアドレスを値1進める（ステップS68）。このアドレスでRead処理が行われる。

#### 【0150】

ステップS65、S67あるいはS68の処理後、Read処理の終了判定を行う（ステップS69）。Read処理が終了していない場合、ステップS64に戻り、Read処理のアドレスを進める。一方、ステップS69でRead処理が終了している場合、本追い越し制御処理を終了する。10

#### 【0151】

上記追い越し制御を行うことで、DRAM106から読み出された画像データは、変倍回路108で変倍処理が行われた後、メモリ制御回路105によってDRAM106に書き込まれる。

#### 【0152】

このように、第3の実施形態のメモリ制御装置によれば、信号処理回路107で処理された画像データを分割してDRAM106に書き込み、その画像データを分割して読み出して変倍回路108に出力する場合でも、追い越し制御を適正に実行することができる。20

#### 【0153】

なお、本発明は、上記実施形態の構成に限られるものではなく、特許請求の範囲で示した機能、または本実施形態の構成が持つ機能が達成できる構成であればどのようなものであっても適用可能である。

#### 【0154】

例えば、上記実施形態では、ラインを変えながら水平方向に連続したデータの読み出しおよび書き込みを行う場合を示したが、垂直方向に連続したデータの読み出しおよび書き込みを行う場合であっても同様に、本発明は適用可能である。

#### 【図面の簡単な説明】

#### 【0155】

【図1】第1の実施形態のメモリ制御装置が適用された撮像装置の構成を示すブロック図である。30

【図2】メモリ制御回路105の構成を示す回路図である。

【図3】A/D変換回路104からDRAM106への画像データの書き込み順序およびDRAM106から信号処理回路107への画像データの読み出し順序を示す図である。

【図4】Read処理がWrite処理を追いかける様子を示すタイミングチャートである。

【図5】追い越し処理手順を示すフローチャートである。

【図6】画像データの左下から右上へ向かう方向でWrite処理およびRead処理を行う場合のA/D変換回路104からDRAM106への画像データの書き込み順序およびDRAM106から信号処理回路107への画像データの読み出し順序を示す図である40。

【図7】Read処理がWrite処理を追いかける様子を示すタイミングチャートである。

【図8】第2の実施形態におけるメモリ制御回路105の構成を示す回路図である。

【図9】変倍回路108からDRAM106への画像データの書き込み順序およびDRAM106からビデオ変調回路111への画像データの読み出し順序を示す図である。

【図10】Write処理がRead処理を追いかける様子を示すタイミングチャートである。

【図11】追い越し処理手順を示すフローチャートである。

【図12】第3の実施形態における信号処理回路107からDRAM106への画像データ

10

20

30

40

50

タの書き込み順序およびDRAM 106から変倍回路108への画像データの読み出し順序を示す図である。

【図13】Read処理がWrite処理を追いかける様子を示すタイミングチャートである。

【図14】追い越し処理手順を示すフローチャートである。

【図15】図14につづく追い越し処理手順を示すフローチャートである。

【符号の説明】

【0156】

105 メモリ制御回路

106 DRAM

201、1301 Write制御回路

202、1302 Writeアドレス発生器

203、1309 メモリI/F

204、1310 Read制御回路

205、1311 Readアドレス発生器

206、1303 減算器

207、1304 レジスタ

208、1305 比較器

209、1306 フリップフロップ

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51)Int.Cl. F I

H 04N 101/00 (2006.01) G 06F 12/00 570C

H 04N 101:00

(58)調査した分野(Int.Cl., DB名)

G 06F 12 / 00 - 12 / 06

G 06T 1 / 20

H 04N 5 / 232

H 04N 5 / 76

H 04N 101 / 00