(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4965835号

(P4965835)

(45) 発行日 平成24年7月4日(2012.7.4)

(24) 登録日 平成24年4月6日(2012.4.6)

(51) Int.Cl.

F 1

|               |              |                  |        |       |

|---------------|--------------|------------------|--------|-------|

| <b>B82B</b>   | <b>1/00</b>  | <b>(2006.01)</b> | B 82 B | 1/00  |

| <b>B82Y</b>   | <b>30/00</b> | <b>(2011.01)</b> | B 82 Y | 30/00 |

| <b>H01L</b>   | <b>29/06</b> | <b>(2006.01)</b> | H 01 L | 29/06 |

| <b>H01J</b>   | <b>1/304</b> | <b>(2006.01)</b> | H 01 J | 1/30  |

| <b>G 11 B</b> | <b>5/65</b>  | <b>(2006.01)</b> | H 01 L | 29/06 |

請求項の数 4 (全 31 頁) 最終頁に続く

(21) 出願番号 特願2005-258274 (P2005-258274)

(22) 出願日 平成17年9月6日 (2005.9.6)

(65) 公開番号 特開2006-297581 (P2006-297581A)

(43) 公開日 平成18年11月2日 (2006.11.2)

審査請求日 平成20年9月3日 (2008.9.3)

(31) 優先権主張番号 特願2005-88981 (P2005-88981)

(32) 優先日 平成17年3月25日 (2005.3.25)

(33) 優先権主張国 日本国 (JP)

前置審査

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 安居 伸浩

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

(72) 発明者 堀江 亮子

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

最終頁に続く

(54) 【発明の名称】構造体、その製造方法、及び該構造体を用いたデバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

元素 A と  $Si_n Ge_{1-n}$  (ここで  $0 < n < 1$ ) との化合物を含む第一の部材と、 $Si_n Ge_{1-n}$  (ここで  $0 < n < 1$ ) からなる第二の部材とで構成される構造体であって、前記第一及び第二の部材のいずれか一方の部材は、他方の部材に側面を取り囲まれている柱状部材であり、

前記柱状部材は、複数あり、前記柱状部材の横断面形状の長軸方向の平均直径  $D_1$  と短軸方向の平均直径  $D_s$  との比  $D_1 / D_s$  が 5 未満であり、

前記元素 A は、Co、Ni、Cu、Pd、Pt のいずれかであり、かつ

複数の前記柱状部材における短軸方向の平均直径が  $0.5 \text{ nm}$  以上  $20 \text{ nm}$  以下であることを特徴とする構造体。

## 【請求項 2】

複数の前記柱状部材のそれぞれにつき最も近接する柱状部材との横断面形状における重心間の平均距離が  $30 \text{ nm}$  以下であることを特徴とする、請求項 1 記載の構造体。

## 【請求項 3】

前記第一の部材と第二の部材との間の組成範囲において共晶型合金平衡状態図を有し、前記化合物における前記元素 A と前記  $Si_n Ge_{1-n}$  の比率が  $A : Si_n Ge_{1-n} = 1 : y$  であり、

前記元素 A と前記  $Si_n Ge_{1-n}$  の全量に対して前記元素 A の組成範囲 [atom %] が  $10y / (y + 1)$  以上  $90y / (y + 1)$  以下であることを特徴とする、請求

項1又は2記載の構造体。

【請求項4】

請求項1から3のいずれか1項に記載の構造体からなる下地層と該下地層上に配置され磁性粒子が分散している記録層とを有する磁気記録媒体であって、

前記記録層を構成する磁性粒子は前記下地層の柱状部材に対応して該柱状部材と接続されて位置していることを特徴とする磁気記録媒体。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、相分離構造をもつナノメートルサイズの構造体或いはそれから得られる構造体に関するものである。更には、本発明は、これら構造体の製造方法、及びこれら構造体を用いて構成される電子デバイス、電極、磁気記録媒体、触媒能を有する機能性膜または電子放出素子などのデバイスに関するものである。 10

【背景技術】

【0002】

近年、機能性材料としての微細構造体への関心が高まっている。こうした微細構造体の作製手法としては、フォトリソグラフィーなどの微細パターン形成技術に代表される半導体加工技術によって直接的に微細構造体を作製する手法が挙げられる。

【0003】

また、微細構造体の作製手法としては、上述の半導体加工技術とは別に、材料の自己組織化 (self-organization) 現象あるいは自己形成化現象を利用する手法がある。これは、即ち、自然に形成される規則的な構造をベースに、新規な微細構造体を実現しようというものである。その中でも特許文献1に示すものは、第一の材料と第二の材料との間での相分離の構造を形成するものであり、無機材料にて自己組織化構造を得ることを可能にしている。 20

【特許文献1】特開2004-223695号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上述の特許文献1に示すような構造体の作製においては、第一の材料と第二の材料との間（例えばアルミニウムとシリコンとの間）で化合物を作らないことが必要な条件であると考えられていた。その場合、選択可能な材料の組み合わせというのは、いくつかに限られている。そのため、そのような限定された材料の組み合わせ以外に、化合物を形成し得る材料同士の組み合わせにおいても、自己組織的な相分離構造を形成可能にすることが望まれている。 30

【0005】

そこで、本発明の1つの目的は、2種の材料間で化合物を形成し得る場合において有効な相分離構造をもつナノメートルサイズの構造体を提供することにあり、更に該構造体の製造方法を提供することにある。

【0006】

特に、本発明の目的は、 $Si_nGe_{1-n}$  (ここで0 < n < 1) がSi及びGeの双方を除く元素Aとの間で化合物を形成し得る場合において、元素Aと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物と、元素Aまたは $Si_nGe_{1-n}$  (ここで0 < n < 1)との有効な相分離構造をもつナノメートルサイズの構造体を提供することにあり、更に該構造体の製造方法を提供することにある。 40

【0007】

また、本発明の他の目的は、以上のような相分離構造をもつ構造体から一方の相を構成する材料を除去して得られる構造体を提供することにある。

【0008】

本発明の更に別の目的は、以上のような構造体を用いて構成される各種デバイスを提供することにある。 50

## 【課題を解決するための手段】

## 【0009】

本発明は、上記目的のいずれかを達成するものとして、 $Si$ 及び $Ge$ の双方を除く元素Aと $Si_nGe_{1-n}$ (ここで $0 < n < 1$ )との間の化合物を含む第一の部材と、前記元素Aと $Si_nGe_{1-n}$ (ここで $0 < n < 1$ )のいずれか一方を含む第二の部材とで構成される構造体であって、前記第一及び第二の部材のいずれか一方の部材は他方の部材に側面を取り囲まれている柱状部材であり、前記柱状部材の横断面形状の長軸方向の平均直径DIと短軸方向の平均直径Dsとの比DI/Dsが5未満であることを特徴とする構造体、を提供する。

## 【0010】

本発明の一態様においては、前記元素Aは、 $Li$ 、 $Na$ 、 $Mg$ 、 $K$ 、 $Ca$ 、 $Sc$ 、 $Ti$ 、 $V$ 、 $Cr$ 、 $Mn$ 、 $Fe$ 、 $Co$ 、 $Ni$ 、 $Cu$ 、 $Rb$ 、 $Sr$ 、 $Y$ 、 $Zr$ 、 $Nb$ 、 $Mo$ 、 $Ru$ 、 $Rh$ 、 $Pd$ 、 $Cs$ 、 $Ba$ 、 $La$ 、 $Hf$ 、 $Ta$ 、 $W$ 、 $Re$ 、 $Os$ 、 $Ir$ 、 $Pt$ 、 $Ce$ 、 $Pr$ 、 $Nd$ 、 $Sm$ 、 $Gd$ 、 $Tb$ 、 $Dy$ 、 $Ho$ 、 $Er$ 、 $Tm$ 、 $Yb$ 、 $Lu$ 、 $B$ のいずれかである。本発明の一態様においては、複数の前記柱状部材における短軸方向の平均直径が0.5nm以上20nm以下である。本発明の一態様においては、複数の前記柱状部材のそれぞれにつき最も近接する柱状部材との横断面形状における重心間の平均距離が30nm以下である。本発明の一態様においては、前記構造体は膜の形態をしており、前記柱状部材における横断面形状は前記膜の一方の主面を形成する前記柱状部材の端面の形状と実質上同等である。本発明の一態様においては、前記膜は基体の表面上に形成されている。本発明の一態様においては、前記第一の部材と第二の部材との間の組成範囲において共晶型合金平衡状態図を有する。

## 【0011】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体を製造する方法であって、基体を用意する工程、 $Si_nGe_{1-n}$ (ここで $0 < n < 1$ )と前記元素Aとを個別にまたは一体的に含んでなる材料を用いて前記基体上に非平衡状態で膜を形成する工程を含み、該膜を形成する工程において、前記比DI/Dsが5未満となるように、前記材料における $Si_nGe_{1-n}$ (ここで $0 < n < 1$ )と前記元素Aとの比率と、前記膜の形成の際の条件との組み合わせを用いることを特徴とする、構造体の製造方法、を提供する。

## 【0012】

本発明の一態様においては、前記膜を形成する工程はスパッタリング法による。本発明の一態様においては、前記膜の形成の際の条件として、前記基体の温度、前記基体へ印加されるバイアス電圧、スパッタリングターゲットと前記基体との間の距離、投入電力及びプロセスガスの圧力を選択する。

## 【0013】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体から前記柱状部材の部分を除去したような形態をなすことを特徴とするポーラス構造体、を提供する。

## 【0014】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体から前記柱状部材の部分を除去することを特徴とする、ポーラス構造体の製造方法、を提供する。本発明の一態様においては、前記柱状部材の部分をエッティングにより除去する。

## 【0015】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体から前記柱状部材以外の部分を除去したような形態をなすことを特徴とする針状構造体、を提供する。

## 【0016】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体から前記柱状部材以外の部分を除去することを特徴とする、針状構造体の製造方法、を提供する。本発明の一態様においては、前記柱状部材以外の部分をエッティングにより除去する。

10

20

30

40

50

## 【0017】

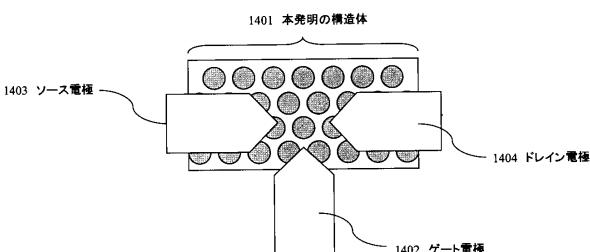

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体を用いた電子デバイス、を提供する。本発明の一態様においては、前記電子デバイスは前記構造体の表面上に形成されたソース電極、ドレイン電極及びゲート電極を有するトランジスタである。

## 【0018】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体を用いた電極、を提供する。

## 【0019】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体からなる下地層と該下地層上に配置され磁性粒子が分散している記録層とを有する磁気記録媒体であって、前記記録層を構成する磁性粒子は前記下地層の柱状部材に対応して該柱状部材と接続されて位置していることを特徴とする磁気記録媒体、を提供する。 10

## 【0020】

また、本発明は、上記目的のいずれかを達成するものとして、上記のポーラス構造体の空隙部分に硬磁性材料を充填してなる記録層を有する磁気記録媒体、を提供する。

## 【0021】

また、本発明は、上記目的のいずれかを達成するものとして、記録層と上記のポーラス構造体の空隙部分に軟磁性材料を充填してなる軟磁性層とを有する磁気記録媒体、を提供する。 20

## 【0022】

また、本発明は、上記目的のいずれかを達成するものとして、上記の磁気記録媒体を用いた磁気記録再生装置、を提供する。

## 【0023】

また、本発明は、上記目的のいずれかを達成するものとして、上記の磁気記録再生装置を用いた情報処理装置、を提供する。

## 【0024】

また、本発明は、上記目的のいずれかを達成するものとして、上記のポーラス構造体を利用した触媒能を有する機能性膜、を提供する。

## 【0025】

また、本発明は、上記目的のいずれかを達成するものとして、上記の針状構造体を利用した触媒能を有する機能性膜、を提供する。 30

## 【0026】

また、本発明は、上記目的のいずれかを達成するものとして、上記の構造体を用い、該構造体の柱状部材を電子放出部として利用した電子放出素子、を提供する。

## 【0027】

また、本発明は、上記目的のいずれかを達成するものとして、上記の針状構造体を用い、該針状構造体の柱状部材を電子放出部として利用した電子放出素子、を提供する。

## 【発明の効果】

## 【0028】

本発明によれば、2種の材料間で化合物を形成し得る場合においても相分離構造をもつナノメートルサイズの構造体が提供される。特に、本発明によれば、 $Si_nGe_{1-n}$ (ここで0  $n$  1)がSi及びGeの双方を除く元素Aとの間で化合物を形成し得る場合において、元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物と、元素Aまたは $Si_nGe_{1-n}$ (ここで0  $n$  1)との相分離構造をもつナノメートルサイズの構造体が提供される。該相分離構造をもつ構造体から一方の相を構成する材料を除去することでポーラス構造体または針状構造体が提供され、これらの構造体を用いた各種デバイスが提供される。 40

## 【発明を実施するための最良の形態】

## 【0029】

本発明の構造体、及び構造体の製造方法、構造体の形成の概念等に関して図面を参照し 50

ながら詳細に説明する。さらに、本発明による電子デバイス、半導体集積回路用ゲート電極、磁気記録媒体、触媒能を有する機能性膜、電子放出素子について説明する。

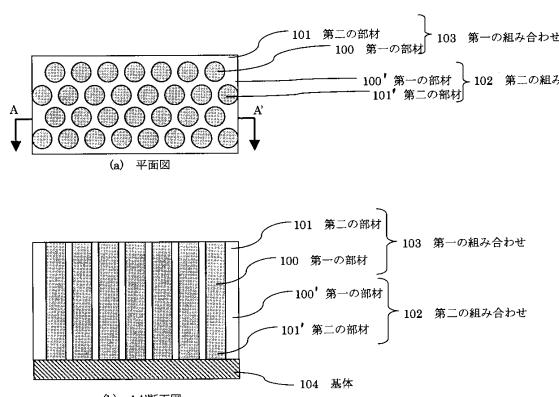

### 【0030】

#### [構造体について]

図1に本発明の構造体の模式図を示す。構造体は、基体104の表面上に形成された膜の形態をなしている。即ち、 $Si_nGe_{1-n}$ （ここで0  $n$  1）との間で化合物を形成し得る元素Aの $Si_nGe_{1-n}$ （ここで0  $n$  1）との間の化合物を含んでなる第一の部材と、 $Si_nGe_{1-n}$ （ここで0  $n$  1）及び元素Aのうちのいずれか一方を含んでなる第二の部材とを含み構成されている。 $Si_nGe_{1-n}$ （ここで0  $n$  1）は、 $n=1$ の場合にはSiであり、 $n=0$ の場合にはGeであり、 $0 < n < 1$ の場合にはSi及びGeを含んでなる物質（以後、この物質をSiGeと略記することがある）である。第一及び第二の部材のいずれか一方の部材は柱状部材であり、該柱状部材は基体104の表面（あるいは基体上に形成された前記第一及び第二の部材で構成される膜と基体との界面）に対してほぼ垂直に形成されている。元素Aとしては、Li、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bが例示される。

### 【0031】

第一の組み合わせ103においては、例えばPdSi、PdGe、PdSiGe等の「元素Aと $Si_nGe_{1-n}$ （ここで0  $n$  1）との間の化合物」を主として含んでなる第一の部材100が柱状部材である。該第一の部材100は例えばSi、Ge、SiGe等の $Si_nGe_{1-n}$ （ここで0  $n$  1）を主として含んでなる第二の部材101に側面を取り囲まれて複数が分散して配置されている。第二の組み合わせ102においては、例えばSi、Ge、SiGe等の $Si_nGe_{1-n}$ （ここで0  $n$  1）を主として含んでなる第二の部材101'が柱状部材である。該第二の部材101'は例えばPdSi、PdGe、PdSiGe等の「元素Aと $Si_nGe_{1-n}$ （ここで0  $n$  1）との間の化合物」を主として含んでなる第一の部材100'に側面を取り囲まれて複数が分散して配置されている。尚、実際の構造体では、第一の組み合わせ103及び第二の組み合わせ102のうちの一方が実現される。

### 【0032】

柱状部材100、101'は、膜厚方向即ち基体104の表面に対してほぼ垂直に延びており、その横断面形状は膜厚方向の位置によらずほぼ一定である。従って、膜状構造体の横断面形状は、基板側とは反対側の正面を形成する柱状部材100、101'の上端面の形状と実質上同等である。図1では、柱状部材100、101'の上端面の形状が円形に描かれているが、これに限定されるものではなく、細長く伸びた橢円形、さらに細長く伸び屈曲した構造であってもよい。しかしながら、柱状部材100、101'の上端面の形状は好ましくは円形であり、各々の柱状部材間においてサイズの揺らぎ（ばらつき）が少ないことが好ましい。この場合、特に、柱状部材間の直径の標準偏差は、3 nm以下であることが好ましく、更に好ましくは2 nm以下である。なお、横断面形状とは、基体上に形成された前記第一及び第二の部材で構成される膜と基体との界面に対して垂直な方向から当該膜を見た場合の形状である。即ち基体上に前記膜を形成した場合の、当該膜の平面形状である。

### 【0033】

図1では、柱状部材100、101'がハニカム状に規則正しく並んでいるが、これに限定されるものではない。但し、後述のようなスパッタリング法により基体104上に非平衡状態で膜状の構造体を形成する場合には、形成される膜の厚みが十分厚い領域においては自己組織的にハニカム配列を形成する傾向がある。また、柱状部材100、101'の規則的な配列は、ある領域内で保たれており、異なる領域同士の境界では規則性に乱れが生じることもある。

### 【0034】

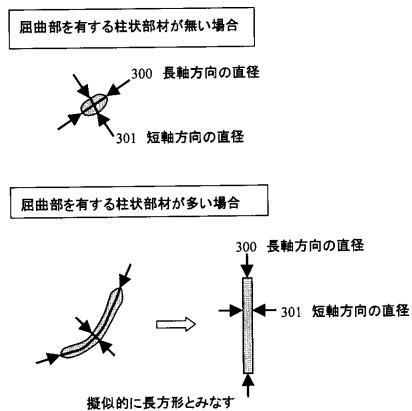

本発明においては、複数の柱状部材100、101'における横断面形状（または端面形状）の長軸方向の平均直径Dlと短軸方向の平均直径Dsとの比Dl/Dsが5未満である。図

3に示すように、横断面形状（または端面形状）において屈曲部を有する柱状部材が無い場合には、柱状部材の横断面形状（または端面形状）における長軸方向及び短軸方向は明らかであり、長軸方向の直径300と短軸方向の直径301とが容易に定義される。ただし、屈曲部を有する柱状部材の場合は複雑である。短軸方向の直径301は複数の柱状部材について比較的幅が一定であることから柱状部材の横断面形状（または端面形状）における短い部分を幅として任意の場所で定義できるが、長軸方向の直径は直線を引くことでは算出できない。この場合、柱状部材の横断面形状（または端面形状）における屈曲部を引き伸ばし擬似的に細長い長方形としてみなしてから長軸方向の直径300を算出することが有効である。

## 【0035】

10

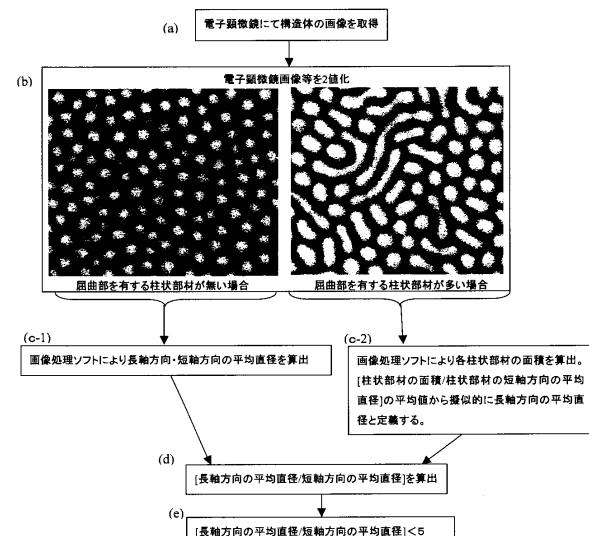

ここで、図2のフローチャートを用いて、[長軸方向の平均直径DI]/[短軸方向の平均直径Ds] < 5を満たす構造体かどうかの判別法を説明する。

## 【0036】

(a)先ず、本発明の構造体の表面を電子顕微鏡により観察し、柱状部材の上端面の形状が判別可能な画像を取得する。このとき、元素構成によっては走査型電子顕微鏡では構造が不明瞭にしか観察されない場合があるため、透過型電子顕微鏡により上端面からの2次電子からの結像だけでなく透過電子の結像をも用いて画像を取得しても良い。

## 【0037】

20

(b)前記(a)にて取得した画像を適宜のソフトウェアにて画像処理し、2値化する。例えば、本発明に属する構造体の画像を2値化したものが図2(b)に2種示されている。ここで、構造体の特徴として柱状部材の上端面の形状が細長いものに関しては直径の概念の形成が困難であるため解析に際して、以下のように場合分けを行った。

## 【0038】

## [屈曲部を有する柱状部材が無い場合]

(c-1)画像処理ソフトウェアにより2値化した画像の柱状部材を認識させ、その長軸方向・短軸方向のそれぞれの直径を算出する。

## 【0039】

## [屈曲部を有する柱状部材が多い場合]

(c-2)画像処理ソフトウェアにより2値化した画像の柱状部材を認識させ、個々の柱状部材の面積を算出する。さらに、短軸方向と思われる方向の直径はほぼ一定であることが画像から認識できるため、複数の柱状部材についての短軸方向の直径の平均値（短軸方向の平均直径）を算出する。そして、それぞれの柱状部材につき[柱状部材の面積]/[短軸方向の平均直径]の式により算出された数値の複数の柱状部材についての平均値を擬似的に長軸方向の平均直径とする。このことは、屈曲したものを長さの等しい長方形とみなして計算したことに相当する。

30

## 【0040】

(d)次に、算出したそれぞれの平均直径を[長軸方向の平均直径DI]/[短軸方向の平均直径Ds]の式に従って算出する。

## 【0041】

40

(e)最後に、(d)で得られた値が5未満である場合には本発明の構造体であるという判断にいたるものである。

## 【0042】

本発明においては、複数の柱状部材における短軸方向の平均直径は、例えば0.5nm以上20nm以下である。また、複数の柱状部材において、それぞれにつき最も近接する柱状部材との横断面形状における重心間距離の平均は、例えば30nm以下である。

## 【0043】

## [構造体の製造方法]

膜状の構造体を形成するための基体を準備する。基体104としては、特に限定されるものではないが、例えばガラス、石英ガラスなどの酸化物やプラスチックなどからなる絶縁性基板、シリコン、ゲルマニウムやガリウム砒素やインジウム燐などからなる半導体基

50

板、またはアルミニウム等からなる金属基板を目的に応じて用いることができる。さらに、レジスト等によりパターニングされたものも使用可能である。また、基体104は上記材料に限定されるものではない。

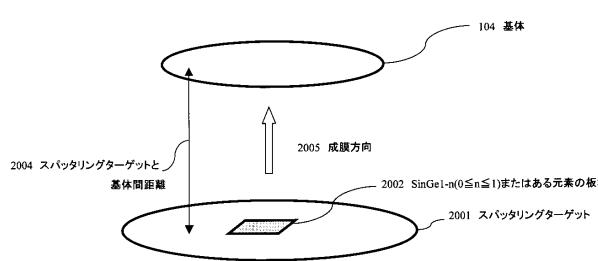

【0044】

更に、構造体を構成する材料であるところの元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)とを個別にまたは一体的に含んでなる材料を準備する。 $SiGe$ については、 $Si$ と $Ge$ とを個別に含んでなる材料を用いてもよい。即ち、構造体は必ず $Si$ 及び $Ge$ の双方を除く元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物を含むのであるから、 $Si_nGe_{1-n}$ (ここで0  $n$  1)と元素Aとを原料として準備する必要がある。ただし、 $Si_nGe_{1-n}$ (ここで0  $n$  1)と元素Aとは単離している必要はない。元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物と元素A、元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物と $Si_nGe_{1-n}$ (ここで0  $n$  1)、元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との混合物などの形態でもかまわない。これらの材料を用いて、基体104に対して非平衡状態において原料となる元素の堆積を行い目的の構造体を得ることが可能である。このとき、上記のように、柱状部材の短軸方向の平均直径Dsが0.5nm以上20nm以下であり、最近接の柱状部材との重心間の平均距離が30nm以下である構造体を形成するためには、基体104上で原料となる元素が急速に冷却されるのが好ましい。すなわち、原料となる元素のエネルギーが急速に失われるような状態が好ましい。ただし、原料となる元素の相分離が起こるような時間のスケールで表面拡散を起こすような状況にする。これにより、従来バルクで試みられてきた手法(全体を溶解して、一方向急冷凝固する手法)では容易には達成不可能であったような微細な組織を原料となる元素の堆積方向に一様に形成することが可能になる。さらに、好ましくはこの非平衡状態における成膜手法としては、スパッタリング法、電子線蒸着法など気相中・真空中で行うものが好ましく、特にスパッタリング法で行うことが好ましい。スパッタリング法については、図20に示されるように主に原料を含むスパッタリングターゲット2001に対して基体104が対向するように配置される。また、スパッタリングターゲット2001の状態は、所要の原料を含むものであれば、合金でもかまわないし、焼結したものでもかまわない。また、図20に示されているように、一方の材料をターゲットとして配置し、他方の材料を任意の大きさの板としてターゲットの上に配置して使用しても良い。例えば、スパッタリングターゲット2001が $Si_nGe_{1-n}$ (ここで0  $n$  1)からなり、その中心部分に配置された $Si_nGe_{1-n}$ (ここで0  $n$  1)またはある元素(元素A)の板2002がPdからなるという具合である。さらに、スパッタリングとはアルゴンなどのプロセスガスによりスパッタリングターゲット2001から弾き飛ばされた原料が逐次基体104に堆積するものであり、対向するように配置される基体104に対して成膜方向2005が堆積方向である。さらに、弾き飛ばされた原料は高いエネルギーを有しており、基体104上で急速にエネルギーを失い、さらに基体の表面をある程度拡散するので本発明の構造体を得るために有効な手法である。従って、スパッタリング法におけるスパッタリングターゲットと基体との間の距離2004、投入電力、プロセスガスの種類・圧力、基体104の温度、基体104に印加するバイアス電圧等により高度に構造体の形成を制御することが可能である。

【0045】

本発明の構造体は、原料となる元素等の基体104上での相互拡散による自己組織的な構造形成を基本としており、成膜速度が速くなりすぎる状況では相分離が完了する前に逐次原料となる元素等が堆積してくるため相分離の程度が弱くなる傾向がある。従って、成膜速度が遅いほうが分離には有効である。スパッタリングターゲットと基体との間の距離2004を大きくすることによっても成膜速度を十分遅くすることが可能ではある。しかし、基体104までの距離が長くなりすぎると堆積する原料となる元素等のエネルギーが基体104に飛来する前に低くなり基体104上で拡散する時間は有していても拡散するエネルギーが足りなくなることがある。そこで、そのような状況下において基体104へバイアス電圧を印加する、または基体温度を上げることにより、基体104上に飛来した原料の拡散に要するエネルギーを与えてやるということも可能である。従って、上記のことを勘案して、成膜条件を適切に保つことが本発明の構造体の形成には好ましい。

10

20

30

40

50

## 【0046】

最後に、本発明の構造体は、上記例示のものその他のような基体104の表面上へも適用できるものであり、各々の形成条件において基体104の損傷を伴わない状況があり得るものである。また、構造体の膜としての厚さは、形成時間を長くすることでいくらでも厚くすることが可能である。しかし、形成される膜に発生する応力等を適切に維持することを勘案して、基体104の種類及び所望により該基体の表面層として形成される下地層の種類などは適宜選択するのが好ましい。

## 【0047】

## [構造体の形成の概念等]

本発明の構造体の形成に関して、更に述べることにする。

10

## 【0048】

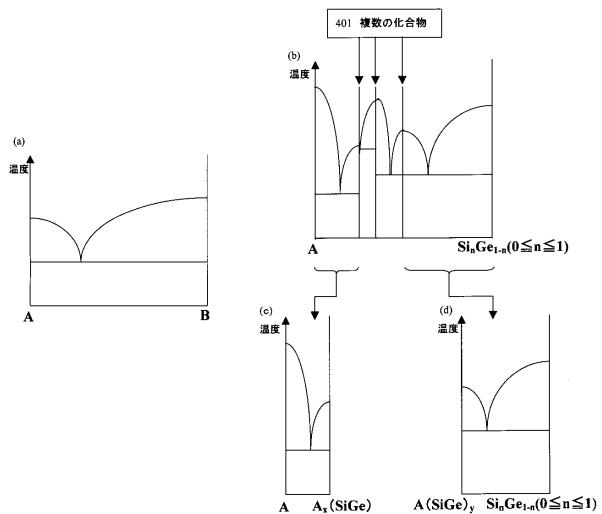

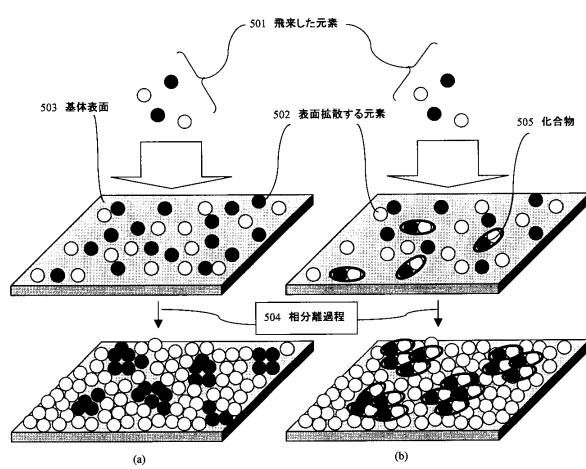

まず、無機材料をもとに自己組織化を利用したナノスケールの構造体の形成に関する提案は、従来まれである。ただ、上述のように、主にアルミニウムとシリコンとを用いた相分離構造が提案されている。しかし、その提案においては、図4(a)に示すような2元系の全率共晶型の状態図を有していることが必要であることから、このような状態図を有する元素の組み合わせというものは、意外と少ないことが判る。かくして、このような構造体をその他の元素の組み合わせで達成させることは非常に困難であると考えられていた。すなわち、図5(a)に示す概念図のように、2元系において全率共晶型である場合には、これらの化合物を作らないため、飛来した元素(原子などの形態)501の基体表面503での相分離過程504がスムーズに進むことが考えられる。しかし、2元系の状態図において図4(b)のような場合においては、形成可能な複数の化合物401が存在し、基体104上において化合物の形成と相分離とが同時に進行するのは複雑であることが予想される。即ち、図4(c)や(d)のように原料元素等と化合物との間ににおいて共晶型の状態図である場合においても、図5(b)の概念図のような表面拡散する元素502が化合物505を形成してさらに凝集するような相分離過程504を逐次生ぜしめるであろうことが自明でないことは容易に想像できるものである。

20

## 【0049】

しかしながら、本発明者らは、鋭意検討の結果、非平衡状態の成膜条件を巧く制御してやることで、図4(c)や(d)のような原料元素等とその化合物と間ににおいても相分離が可能であることを見出した。従って、本発明により、従来適用不可能であると思われていた材料の多くを用いてナノスケールの相分離構造をもつ構造体を形成することが可能になった。

30

## 【0050】

本発明の主要な特徴は $Si_nGe_{1-n}$ (ここで0  $n$  1)あるいはSi及びGeの双方を除く元素Aと、該元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物との間ににおける相分離構造である。それらは構成元素等同士の間ににおいては全率共晶型でなくともよいのである。従って、選択可能な材料としては原料となる元素Aを、Li、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bのうちから選択することが好ましい。ただし、本発明の構造体を形成できるものであれば、元素Aとして上記以外の元素を用いてもよい。また、上記原料以外の元素が30 atomic%以下で添加されていることも好ましい。更に好ましくは、上記原料以外の元素の添加量は15 atomic%以下である。特に、 $Si_nGe_{1-n}$ (ここで0  $n$  1)と全率において共晶型の状態図を有する材料の一部添加を行うことも好ましい。そのような材料としては、例えばAl、Zn、Ag、Au、Sb、Sn、Inが例示される。添加とは、上記元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物よりも組成割合が低いということを指すものであり、組成はatomic%にて比較され得るものである。

40

## 【0051】

また、本発明の構造体は、その部材のうちの一方を元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物が占めている。しかし、この化合物とは $Si_nGe_{1-n}$ (ここで0  $n$  1)と元素

50

Aとの間に複数の結合が存在していることであり、必ずしも結晶化している必要はないものである。特に、非晶質の状態であることも応用上好ましい。例えば、パラジウムと $Si_nGe_{1-n}$  (ここで0 < n < 1)とからなる系においては、Pdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物（即ち、AがPdであるA(SiGe) y : 尚、yについては後述）と $Si_nGe_{1-n}$  (ここで0 < n < 1)との間で図4(d)のような共晶型の状態図を有している。この場合、本発明の構造体を形成することが可能であるが、Pdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物として存在する場合には、この化合物の結晶としてのみでなく、非晶質として分離構造を形成してもかまわない。従って、 $Si_nGe_{1-n}$  (ここで0 < n < 1)のみをエッチングする場合においても、Pdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物の結晶はエッチングされなくとも、非晶質状態のPdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物ではSiまたはGeのダングリングボンドが複数存在するためエッチングされうる場合がある。この場合、結合の甘いSiまたはGeはエッチングされ、Pd組成の高いものが残されるということもありうるのである。このように、本発明においては、構造体を構成する部材のうちのいずれか一方を除去する場合において、他方が少し侵されることをも許容するものである。

#### 【0052】

また、本発明で選択可能な元素Aにおいて、 $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物を形成する組成に関しては材料ごとに色々な状態を取るため一律に表現することが出来ない。しかし、図4(b)のような状態図において図4(c)や(d)の状態図として取り出せるものが有効である。そのときの図4(c)が示す元素Aが多数を占めるAx(SiGe)または図4(d)が示す $Si_nGe_{1-n}$  (ここで0 < n < 1)が多数を占めるA(SiGe) yのx,yの値は材料固有である。しかしながら、一旦x,yの値が決まると組成の範囲も決まる。例えば、Ax(SiGe)の場合には、Aと $Si_nGe_{1-n}$  (ここで0 < n < 1)との全量に対するAの組成範囲 [atomic%] は、 $(100x+10)/(x+1)$ 以上 $(100x+90)/(x+1)$ 以下において選択することが好ましい。また、この組成範囲においても本発明の構造体を形成するかどうかは作製条件によるため、最低限満たす必要がある組成範囲を示している。したがって、この組成範囲内かつ前述の柱状部材の長軸方向の平均直径DIと短軸方向の平均直径Dsとの比が5未満であることから本発明の構造体であるか判断されるものである。さらに、A(SiGe) yの場合には、Aと $Si_nGe_{1-n}$  (ここで0 < n < 1)との全量に対するAの組成範囲は、 $10y/(y+1)$ 以上 $90y/(y+1)$ 以下において選択することが好ましい。このAx(SiGe)は $Si_nGe_{1-n}$  (ここで0 < n < 1)一個あたりX個のAが存在する組成の比を表している。A(SiGe) yにおいても同様である。たとえば、前述のPdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物と、 $Si_nGe_{1-n}$  (ここで0 < n < 1)における系を考えれば、Pdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物はA(SiGe) y型であり、y=1である。つまり、Aと $Si_nGe_{1-n}$  (ここで0 < n < 1)は1:1の同量のときに形成される化合物であるということである。このときの、Aの組成範囲は、 $10y/(y+1)$ 以上 $90y/(y+1)$ 以下から選択することが好ましいということ、即ちこれにy=1を代入して得られる5 atomic%以上45 atomic%以下ということになる。これは、Pdと $Si_nGe_{1-n}$  (ここで0 < n < 1)との間の化合物の系のy=1の場合に成り立つものであり、もしもy=2などの場合には6.667 atomic%以上60 atomic%以下となる。

#### 【0053】

上記の $Si_nGe_{1-n}$  (ここで0 < n < 1)は、SiとGeとの組成を表現しており、Si組成が $100n$  [atomic%]、Ge組成が $100(1-n)$  [atomic%]である。一方、Ax(SiGe)は、Aと $Si_nGe_{1-n}$  (ここで0 < n < 1)との比率のみを表現しており、組成に換算すると、A組成が $100x/(x+1)$  [atomic%]、 $Si_nGe_{1-n}$  (ここで0 < n < 1)組成が $100/(x+1)$  [atomic%]である。

#### 【0054】

また、本発明の構造体の形成される条件というのも一律ではなく、選択される材料固有のものとなるが、本発明者らは鋭意検討の結果、ある相関を見出したので、これを以下の表1及び表2に記載する。

#### 【0055】

【表1】

| 材料                    | 共晶温度 [°C] | 柱状部材の平均直径 [nm] |

|-----------------------|-----------|----------------|

| Cu <sub>3</sub> Si-Si | 800       | 7              |

| PdSi-Si               | 860       | 5              |

| NiSi-Si               | 980       | 2.5            |

| CoSi <sub>2</sub> -Si | 1258      | 2              |

| TiSi <sub>2</sub> -Si | 1330      | 0              |

| WSi <sub>2</sub> -Si  | 1400      | 0              |

10

【0056】

【表2】

| 材料                    | 共晶温度 [°C] | 柱状部材の平均直径 [nm] |

|-----------------------|-----------|----------------|

| Cu <sub>3</sub> Ge-Ge | 642       | 7              |

| PdGe-Ge               | 728       | 4.5            |

| NiGe-Ge               | 762       | 3.5            |

| TiGe <sub>2</sub> -Ge | 900       | 0              |

20

【0057】

上記の表1及び表2には、いくつかの主だった材料を選択した場合の状態図における共晶温度[°C]を示した。また、基体104の温度を室温とし、基体104へのバイアス電圧印加等も無い条件にてスパッタリング法で作製した構造体の柱状部材の平均直径[nm]とを示した。その他の条件としては、ターゲットと基体との間の距離は約80mm、プロセスガスはアルゴンを0.1Pa、投入電力は4インチサイズのターゲットに対してSi系の場合には120WとしGe系の場合には60Wとした。注意としては、組成は柱状部材の上端面の形状がほぼ円形になるような状況とした。そのため長軸方向、短軸方向の区別なく、平均直径として示している。また、共晶温度は一般的なバルクの平衡状態図を参照したものであるが、この場合にはある程度の誤差を含んでいても、本発明者らの見出した相関関係には実質上影響はない。

30

【0058】

表1及び表2から見て取れるように、柱状部材の平均直径は、共晶温度が高くなるほど小さくなり、あるところで本発明の構造体を形成しなくなることがわかる。これらのうち、本発明の構造体を形成する4つのデータに基づき大まかに(一次近似にて)相関を定式化すると、以下のようになる。材料の選択にかかわらず、所望の柱状部材の平均直径に対してどのような共晶温度の材料を選択することが可能であるかの判断ができるのである。

Si系の場合には

$$[\text{共晶温度}] = 1280 - 75 \times [\text{柱状部材の平均直径nm}] \quad [1]$$

Ge系の場合には

$$[\text{共晶温度}] = 897 - 37 \times [\text{柱状部材の平均直径nm}] \quad [2]$$

また、式[1], [2]において注目すべきは、柱状部材の平均直径が0となる場合、つまりSi系の場合にはおよそ1280以上、Ge系の場合にはおよそ897以上の共晶温度を有するものに関しては構造体が形成されないことが示唆されるのである。しかしながら、これは構造体の形成条件が前述の様に固定されているためである。基体104の温度をさらに上昇させたり、基体104へのバイアス電圧の印加等により基体表面503における元素の拡散を促進させてやれば、上記の相関におけるSi系の場合の1280やGe系の場合の897はさらに上昇するものである。ここで示した例は、Si系及びGe系のものであるが、SiGe系においても同様の傾向がある。

40

【0059】

50

ここで、Si系及びGe系における相関を示す式[1], [2]が大きく異なる。これはGeのスパッタリング率（プロセスガス [この場合はArガス] 1つに対してはじき飛ばされる確率）がSiに対して大幅に高いことから、Ge系の成膜レートが高いことに起因している。双方の成膜レートを等しくした場合には、Si系、Ge系及びSiGe系の区別なく1つの相関式で表現することができる。尚、前述のスパッタリングでの投入電力（RFパワー）がSi系の場合には120WとしGe系の場合には60Wとして双方での成膜レートの値が近づくようになっているが、これでもまだGe系の場合にはSi系の場合に比べて成膜レートが高い。

## 【0060】

参考として、PdSi系に関して述べれば、基体温度に対して、形成される構造体の柱状部材の平均直径を以下の表3のように変化させることができる。

## 【0061】

## 【表3】

| 材料      | 基体温度 [°C] | 柱状部材の平均直径 [nm] |

|---------|-----------|----------------|

| PdSi-Si | 25        | 5              |

|         | 200       | 6              |

|         | 300       | 7.2            |

## 【0062】

この場合には、

$$[\text{基体温度}] = -575 + 124 \times [\text{柱状部材の平均直径nm}]$$

[3]

というような相関が式[3]として得られるのである。

## 【0063】

以上のように、特定の材料のみにかかわるものでなく、統一的な相関を見出すことにより、ナノスケールの領域において所望のサイズの柱状部材を有する構造体を形成することが可能である。

## 【0064】

従って、本発明においては、化合物の形成を含みながらも相分離構造を形成した構造体を形成することが可能であることを見出し、さらには材料にほとんどかかわらない相関関係を見出した。それに基づき、非常に有効な相分離構造をもつナノスケールの構造体、及びその製造方法を提供するものである。

## 【0065】

また、本発明の構造体は、適当な組成を選択することにより、上記平均直径の比率を限りなく1に近くし、さらに複数の柱状部材における直径の揺らぎも小さくすることが可能である。これは平衡状態図において図4に示すように広い温度域にわたり共晶型の相図であるからであり、言い換えれば、相分離構造の形成過程においてただ一つ有する共晶温度において分離が生じるからである。従って、相分離が複数存在する状態図においては、何度も渡り相分離が繰り返され、複雑な構造に至ることが容易に推測できる。

## 【0066】

## [ポーラス構造体、針状構造体、及びその作製方法]

本発明のポーラス構造体、針状構造体、及びその作製方法について述べることにする。

## 【0067】

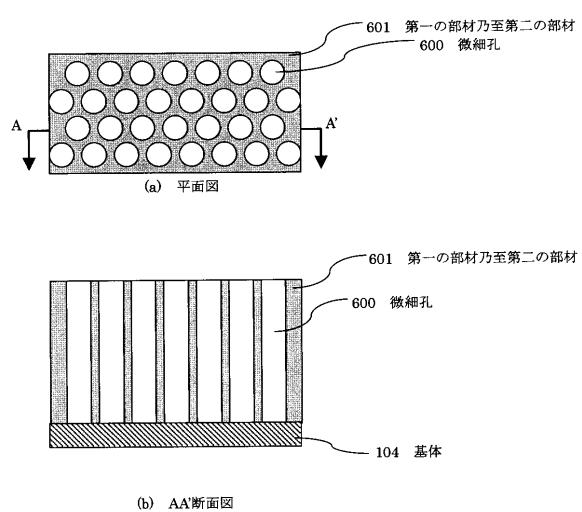

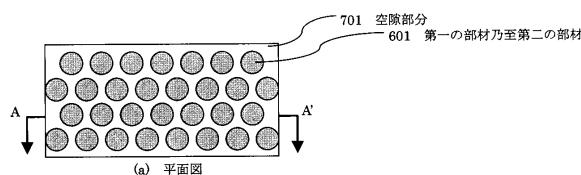

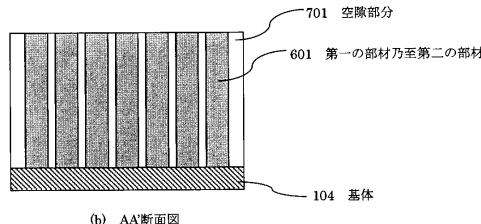

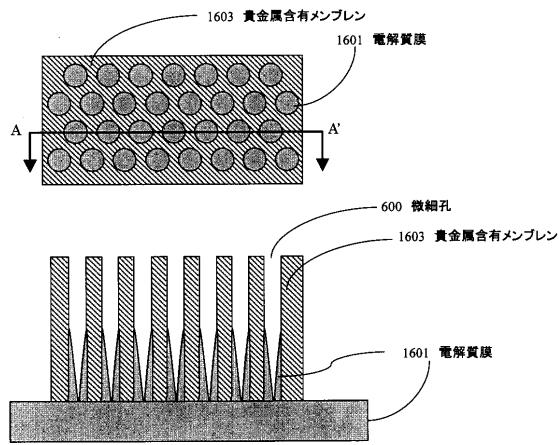

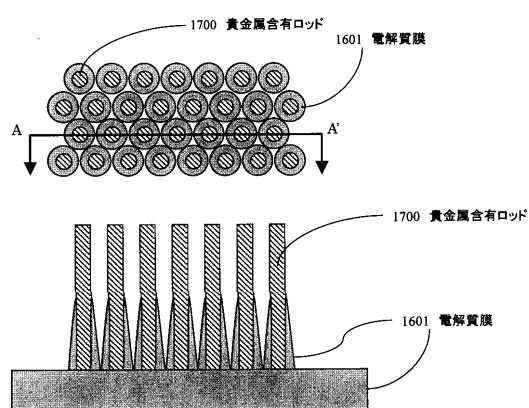

本発明の上記相分離構造をもつ構造体から柱状部材部分のみを取り除くことにより形成可能であるポーラス構造体は、図6に示すように、複数の微細孔600と第一の部材乃至第二の部材601からなるマトリックス部分からなることを特徴とする。微細孔600は基体104に対してほぼ垂直に伸びており直線性に優れるのが特徴である。また、本発明の上記相分離構造をもつ構造体から柱状部材以外の部分を取り除くことにより形成可能な針状構造体は、図7に示すように、第一の部材乃至第二の部材601からなる複数の針状部分と該針状部分間の空隙部分701からなることを特徴とする。針状部分は基体104

10

20

30

40

50

に対してほぼ垂直に伸びており直線性に優れるのが特徴である。

【0068】

以上のポーラス構造体または針状構造体の作製に際しては、柱状部材部分または柱状部材以外の部分のみを除去する方法としては、ケミカルウェットエッティング、気相エッティング、プラズマアシストエッティングなど選択性のあるエッティング法が使用可能である。出発点となる本発明の上記相分離構造をもつ構造体が元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物からなる部分と $Si_nGe_{1-n}$ (ここで0  $n$  1)からなる部分とから構成される場合、ケミカルウェットエッティングにおいては、KOH水溶液などのエッティング液を用いて加熱状態において $Si_nGe_{1-n}$ (ここで0  $n$  1)のみをエッティングすることが可能である。また、 $Si_nGe_{1-n}$ (ここで0  $n$  1)がGe組成の低いまたはGeを含まないものである場合の気相エッティングでは、 $XeF_2$ などのSiのみのエッティングが可能なエッティングガスを利用することが有効である。特に、 $XeF_2$ によるエッティングは、本発明の構造体の柱状部材の直径または柱状部材間の間隔がナノメートルサイズであるにもかかわらず、高い選択性を活かしてアスペクト比の高いエッティングを可能にする。さらに、プラズマ等のアシストも不要であり被エッティング部分以外へのダメージが少ないとことやレジスト等へのダメージも無いことから自己組織化膜とフォトリソグラフィーとの組み合わせによるプロセスがスムーズに行えるのである。また、 $Si_nGe_{1-n}$ (ここで0  $n$  1)がGe組成の高いものである場合には、GeまたはSiGeを過酸化水素水にてエッティングすることも好ましい。また、出発点となる本発明の上記相分離構造をもつ構造体が元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物からなる部分と元素Aからなる部分とから構成される場合には、特に元素Aが金属である場合には元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物の高い耐薬品性を考え、ケミカルエッティングが非常に有効である。特に、元素Aが容易に酸やアルカリに溶解する場合には速やかに本発明のポーラス構造体や針状構造体を得ることが可能である。また、構造体に電気を流せる場合には酸水溶液中にて陽極側に構造体を配置して電圧を印加することによって構造体の一部を加速的に溶解させることも可能である。最後に、これらポーラス構造体や針状構造体を得る過程において被エッティング部分以外の場所は表面への酸素吸着等による酸化を伴うこともあってもよい。特に、電圧印加した場合には酸化も促進するために、積極的に酸化したい場合にはこの手段が好ましい。

【0069】

本発明のポーラス構造体または針状構造体を形成する構成元素には、Li、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bが含まれていることが好ましい。更に、ポーラス構造体または針状構造体を形成する構成元素には、前述の添加元素として適用可能なAl、Zn、Ag、Au、Sb、Sn、In等が含まれていてもよい。但し、これらの添加元素は上記構成元素のいずれかと固溶する範囲にて添加が実施されることが好ましい。

【0070】

[本発明を利用した電子デバイスについて]

本発明における電子デバイスとは、量子ドット、量子細線、量子細線トランジスタ、単電子トランジスタ、あるいは単電子メモリなどである。さらに、それらデバイスを用いた情報処理装置をも含むものである。特に、本発明は元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物と $Si_nGe_{1-n}$ (ここで0  $n$  1)あるいは元素Aとからなる構造体であることが特徴である。従って、たとえばFe、Ca、Sr、Mg、Baなどと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物などの環境半導体と呼ばれる材料からなる柱状部材の形成が可能であり、それらに微量元素を添加することにより伝導性の制御を行えば細線状の電子デバイスが可能となる。これらの場合には、それぞれのバンドギャップに応じて発光する場合も含む。また、量子ドット、量子細線と呼ばれるものに対して、図14に示されるような本発明の構造体1401に対してソース電極1403、ドレイン電極1404を有し、ゲート電極1402にて電子の移動を制御するようなトランジスタを構成すること等が実現可能である。また、以下に説明するように、本発明の構造体に対して図15のように電極部分を形成し

10

20

30

40

50

た電子デバイスを作製することも好ましい。

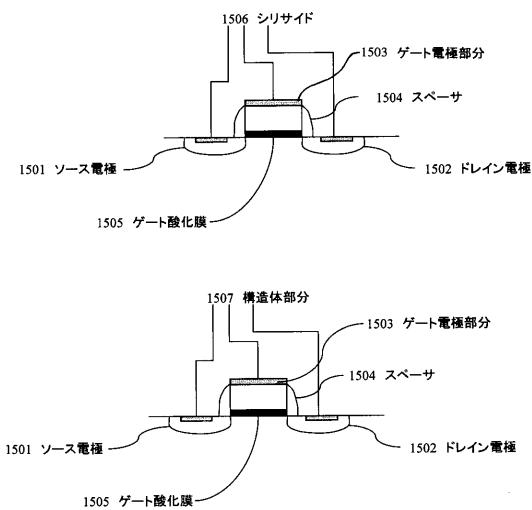

【0071】

[本発明を利用したゲート電極について]

従来のトランジスタの構成は、図15において上側に示すように、ソース電極1501、ドレイン電極1502、ゲート酸化膜1505、スペーサ1504、ゲート電極部分1503、シリサイド1506となっている。それに対して、図15において下側に示すように、本発明におけるゲート電極部分1503とは、従来シリサイド1506だった部分を本発明の構造体部分1507にすることにより、構造体の柱状構造による材料の異方性がリーク電流の減少をもたらす。これにより、電力消費の少ないトランジスタ、ひいては集積回路を可能にするものである。柱状部材の構成材料としては、Ti、Co、Mo、Vと $Si_nGe_{1-n}$ (ここで0 < n < 1)との間の化合物等が電気伝導性に優れるため用いられている。また、本発明にはこのゲート電極を用いた集積回路、その集積回路を搭載した情報処理装置をも含むものである。

【0072】

[本発明を利用した磁気記録媒体、磁気記録再生装置、及び情報処理装置について]

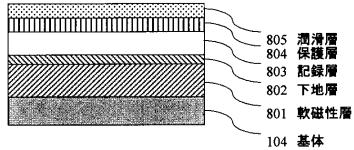

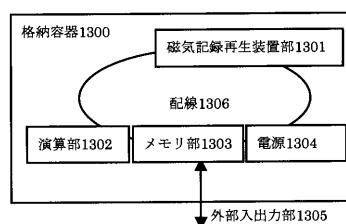

本発明の磁気記録媒体を説明するための磁気記録媒体の層構成について図8を用いて説明する。磁気記録媒体は、まず基体104上に磁気ヘッドからの磁束が記録層803へ集中するように軟磁性層801が形成され、さらに記録層の構造や結晶の配向などを制御する目的の下地層802が続き、それを介して記録層803が形成されている。媒体の劣化やヘッドの浮上安定性と耐衝突性とを兼ね備えるために保護層804と潤滑層805とが順に形成されていることが好ましい。ただし、これは最低限の層構成であって、各層間に更に1つ又は複数の層を適宜挿入してもよい。

【0073】

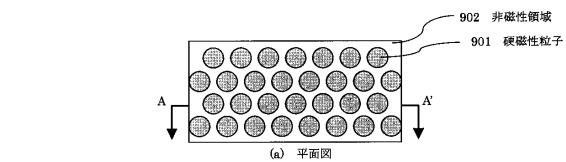

さて、本発明の磁気記録媒体における第一の発明とは、自己組織的に柱状部材が分散した本発明の構造体を下地層802として、各々の柱状部材に記録層803の磁性粒子が接続した構造を有することを特徴とするものである。図9を用いてこれを説明する。下地層802として本発明の構造体からなる層(膜)900を適用し、その構造体の柱状部材の各々に対して記録層803に含まれる硬磁性粒子901が連続的に接続していることが特徴である。また、本発明の構造体からなる層900の柱状部材部分以外の領域が記録層803に含まれる非磁性領域902と連続的に接続していることを特徴とする磁気記録媒体である。本発明においては、硬磁性粒子901を含む記録層803を形成する初期に硬磁性粒子901の核形成を下地層の柱状部材によりすみやかに発生させることができるのが特徴である。この下地層を形成する本発明の構造体の構成元素Aには、Li、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bが含まれていることが好ましい。さらに、記録層803の形成手段は化学気相成長法(Chemical Vapor deposition)、スパッタリング法、蒸着法、メッキ法などが好ましく、特にスパッタリング法等の気相中成膜法が好ましい。記録層803の材料としては、適当な組成を有するCoCr、CoCrPt、CoCrPtB、CoCrPtTa、CoPt-MgO、FePt-MgO、CoPt-SiO<sub>2</sub>、FePt-SiO<sub>2</sub>、CoCrPt-SiO<sub>2</sub>、Co/Pt系、Fe/Pt系、Co/Pd系、Fe/Pd系多層膜等を選択することが好ましい。その他スパッタリング法のような気相中成膜法が適用できる材料であればどのような材料でも適用可能である。そして、下地層802の表面において、本発明の構造体の柱状部材が自己組織的にハニカム状に配列していることが好ましく、それにより20nm以下の平均直径を有する硬磁性粒子901の粒径分散も低減され、非常に低ノイズの磁気記録媒体の提供が可能である。これは、本発明の構造体における柱状部材の平均直径の分散が非常に小さいという特徴が有効に働いている。尚、ここでいうハニカム状配列は、ある領域内での配列を意味し、異なる領域の間で配列が乱雑であることを許容するものとする。

【0074】

次に、本発明の磁気記録媒体における第二の発明は、本発明の構造体の柱状部材部分の

10

20

30

40

50

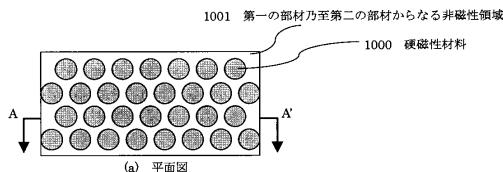

みを除去した後にそこに硬磁性材料を充填した記録層を有する磁気記録媒体である。つまり、本発明のポーラス構造体の微細孔に硬磁性材料を充填した場合と同様である。図10に示すのが磁気記録媒体における第二の発明であり、記録層803の模式図である。本磁気記録媒体は硬磁性材料が本発明の構造体の柱状部材と同様の形状を有していることが特徴であり、それは構造体から柱状部材のみを除去することにより得られるポーラス構造体の微細孔600に対して、硬磁性体を充填したものだからである。従って、柱状部材が硬磁性材料1000からなり、それ以外の部分が第一の部材乃至第二の部材からなる非磁性領域1001であることが好ましい。この第一の部材乃至第二の部材は、前述の本発明の構造体における部材を指すものであり、それぞれ元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物を含む部材、及び $Si_nGe_{1-n}$ (ここで0  $n$  1)または元素Aを含む部材である。元素AはLi、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bから選択することが好ましい。これらの元素は、組成によって磁性を持つことになるものもあるが、 $Si_nGe_{1-n}$ (ここで0  $n$  1)との間での化合物においては硬磁性とはなり得ない。従って、少なくとも $Si_nGe_{1-n}$ (ここで0  $n$  1)との間での化合物が柱状部材でない方の部材を形成する形態での使用が可能である。

## 【0075】

また、硬磁性材料1000としては、Co、Fe、 $L1_0$ 規則合金であるMPt(M=Co、Fe、Niのうち一つ以上からなる)、 $L1_2$ 規則合金である $M_3Pt$ (M=Co、Fe、Niのうち一つ以上からなる)を主成分とする材料、さらにCoまたはFeとPtまたはPdを主成分とする多層膜等から選択することが好ましい。また、充填方法としては、ポーラス構造体の微細孔600へ硬磁性材料が導入されれば、手段を問わないが、化学気相成長法(Chemical Vapor deposition)、スパッタリング法、蒸着法、メッキ法などが好ましい。また、メッキ法が電解メッキの場合には記録層803の下部の下地層802には低抵抗金属が含まれることが好ましい。

## 【0076】

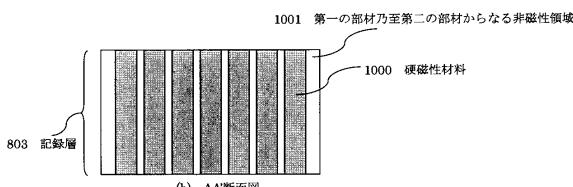

さらに、本発明の磁気記録媒体における第三の発明は、本発明の構造体の柱状部材部分のみを除去した後にそこに軟磁性材料を充填した軟磁性層を有する磁気記録媒体である。つまり、本発明のポーラス構造体の微細孔に軟磁性材料を充填した場合と同様である。図11に示すのが磁気記録媒体における第三の発明であり、軟磁性層801の模式図である。本磁気記録媒体の軟磁性層は、本発明の構造体の柱状部材と同様の形状を有していることが特徴であり、それは構造体から柱状部材のみを除去することにより得られるポーラス構造体の微細孔600に対して、軟磁性体を充填したものだからである。従って、柱状部材が軟磁性材料1100からなり、それ以外の部分が第一の部材乃至第二の部材からなる非磁性領域1001であることが好ましい。この第一の部材乃至第二の部材は、前述の本発明の構造体における部材を指すものであり、それぞれ元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物を含む部材、及び $Si_nGe_{1-n}$ (ここで0  $n$  1)または元素Aを含む部材である。元素AはLi、Na、Mg、K、Ca、Sc、Ti、V、Cr、Mn、Fe、Co、Ni、Cu、Rb、Sr、Y、Zr、Nb、Mo、Ru、Rh、Pd、Cs、Ba、La、Hf、Ta、W、Re、Os、Ir、Pt、Ce、Pr、Nd、Sm、Gd、Tb、Dy、Ho、Er、Tm、Yb、Lu、Bから選択することが好ましい。軟磁性材料1100としては、Co、Fe、Niのうち2つ以上からなる合金、 $L1_2$ 規則合金である $MPt_3$ (M=Co、Fe、Niのうち一つ以上からなる)等を主成分とした高透磁率な材料を選択することが好ましい。また、充填方法としては、ポーラス構造体の微細孔600へ軟磁性材料が導入されれば、手段を問わないが、化学気相成長法(Chemical Vapor deposition)、スパッタリング法、蒸着法、メッキ法などが好ましい。また、メッキ法が電解メッキの場合には軟磁性層801の下部の基体104には低抵抗金属が含まれることが好ましい。

## 【0077】

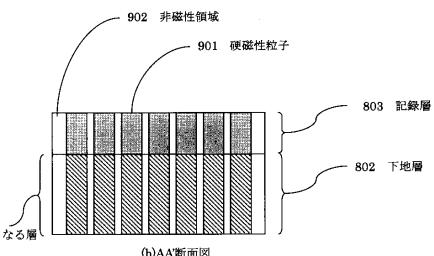

さらに、本発明の磁気記録再生装置は、上記の本発明の磁気記録媒体における第一、第二、第三の発明を用いることが特徴である。この磁気記録再生装置は、図12に示す模式図のように、筐体の中に本発明の磁気記録媒体1200のいずれかと媒体を駆動する磁気記録媒体駆動部1201と磁気ヘッド1202と磁気ヘッド駆動部1203と信号処理部

10

20

30

40

50

1204から構成されることを特徴とする。また、本発明の磁気記録再生装置においては、記録再生方式は、図12に示されるような媒体の回転駆動及びヘッドの円弧上の駆動のみに限定されるものではない。

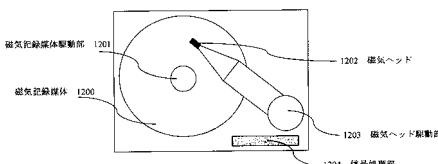

【0078】

また、本発明の磁気記録再生装置を用いた情報処理装置について説明する。図13に示すように、本発明の情報処理装置は、格納容器1300内に磁気記録再生装置1301と演算部1302とメモリ部1303と電源1304とを格納している。各々を配線1306で接続し、各種情報が外部入出力部1305を介してやり取りされることを特徴とする。また、配線1306や外部入出力部1305は、有線を指すだけでなく、情報の受け渡しが可能であれば無線で行うことも好ましい。

10

【0079】

[本発明のポーラス構造体及び針状構造体を利用した触媒能を有する機能性膜について]

前記の本発明のポーラス構造体と針状構造体は、通常の膜の状態に比べて格段に表面積が増大しており、なおかつナノスケールにて構造が繰り返されている。このため、同様の構造物においてもミクロンサイズとは異なりナノスケールという点において多大なメリットを有することが特徴である。本発明のポーラス構造体と同様の形状を柱状部材の平均直径が $1\text{ }\mu\text{m}$ 、柱状部材の重心同士の平均間隔が $1\text{. }3\text{ }\mu\text{m}$ にて実現している場合と、本発明のポーラス構造体の一例として柱状部材の平均直径が $6\text{ nm}$ 、柱状部材の重心同士の平均間隔が $8\text{ nm}$ のものとを比較する。表面積を比較すると、柱状部材の側面の面積比がその違いにあたり、柱状部材を円形と近似すれば個々の柱状部材の側面面積が $Rh$ （ $R$ は直径、 $h$ は高さ）となり単位面積あたりの個数を $n$ とすれば $Rhn$ で表現可能である。したがって、この場合に同じ膜厚で比較するので異なるのは $R$ と $n$ となる、そうすると結果として $R$ の比が $6[\text{nm}]/1000[\text{nm}]$ であり、 $n$ の比がおよそ $3.0\times 10^{10}[\text{個}]/1.2\times 10^6[\text{個}]$ （ $1.3\text{m m}$ 四方で計算）である。したがって、 $R$ と $n$ の比をそれぞれ掛け合わせると $150$ となり、本発明の構造体の方が $150$ 倍も表面積を大きくとることが可能なのである。そこで、表面積を有効に利用するような手法すなわち触媒能を有する機能性膜においては非常に有効であることがわかる。また、本発明の機能性膜では、ポーラス構造体における第一の部材乃至第二の部材601や針状構造体における第一の部材乃至第二の部材601として、触媒能を有する貴金属材料を含有することが好ましい。特に、Pd、Ptが含有されることが好ましく、さらに貴金属の使用量を少なくするために他の材料との合金系で含まれることも好ましい。貴金属としては、所望の触媒能を発揮するものを適宜選択して使用することができる。従って、本発明においては、Pd、Ptからなるポーラス構造体や針状構造体を形成可能であるが、さらにPdSi、PtSi、PdGe、PtGe等を主成分とすることも好ましい。この場合には、Pd、ないしPtの膜全体（ポーラス構造体または針状構造体）に対する組成範囲は、 $50\%$ 前後となり、ナノスケールにて表面積を稼いだ上に貴金属の使用量を半分に抑えることを可能にする。このような触媒は、燃料電池等における水素を効率良く発生させることに利用できるものであり、特にこれらのポーラス構造体や針状構造体をプロトン伝導性を担う高分子電解質膜と一体化させることが好ましい。つまり、模式図としては、図16及び図17に図示されるような構成であり、ポーラス構造体にあっては貴金属含有メンブレン1603の微細孔600の壁に沿って電解質膜1601の一部が侵入して一体化していることが好ましい。また、針状構造体にあっては貴金属含有ロッド1700に沿って電解質膜1601の一部が包囲して一体化していることが好ましい。これらの作製は、前記ポーラス構造体や針状構造体を作製し、電解質膜を塗布・圧着し、構造体部分が支持されていた基体104から引き剥がすことで作製可能である。尚、微細孔600や貴金属含有ロッド1700は、図示するように完全なハニカム状配列である必要はなく、一様に配列されればよい。

20

【0080】

[本発明の構造体及び針状構造体を利用した電子放出素子について]

本発明の電子放出素子は、本発明の構造体に対して引き出し電極を設けたものであり、本発明の構造体がナノスケールでの相分離構造をもつことから低抵抗な各々の柱状部材へ

30

40

50

電界が集中し、より閾値の低い電子放出素子の形成が可能である。好ましくは、さらに本発明の構造体における柱状部材以外の部分を取り除くことで、最表面以外の側面も関与した電子放出素子の形成が可能である。

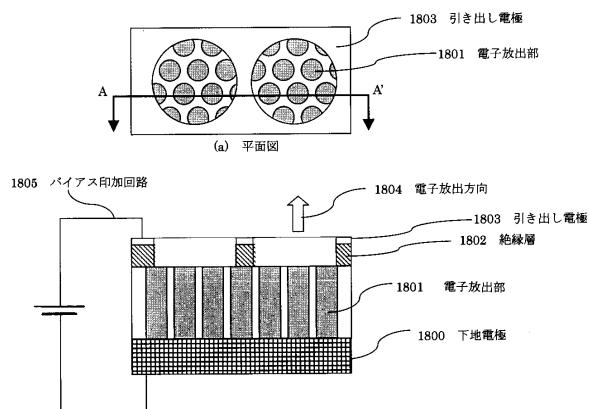

【0081】

まず、図18の模式図に示すように、電子放出部1801となる柱状部材を複数含む開口を有する引き出し電極1803が絶縁層1802で電子放出部1801と隔たれて形成されている。電子放出部1801の下に位置する下地電極1800と引き出し電極1803との間にバイアス印加回路1805にて電圧が印加され、それにより電子放出部1801から引き出された電子が電子放出方向1804に放出されることを特徴とする電子放出素子である。

10

【0082】

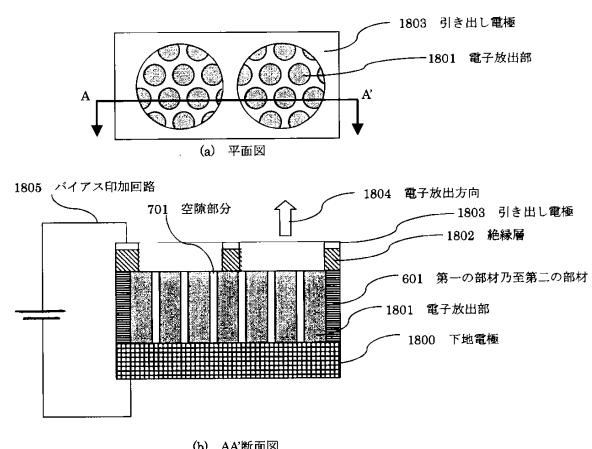

さらに、本発明における柱状部材間の材料の絶縁性によっては、図19の模式図に示すように、柱状部材部分以外の第一の部材乃至第二の部材601を引き出し電極1803に設けられた開口部に対応する部分のみ除去することにより空隙部分701を形成することが好ましい。そうすることで、電子放出部1801と引き出し電極1803との間に下地電極1800を介してバイアス印加回路1805で電圧を印加することにより電子が電子放出方向1804に放出され、電子放出効率の高い電子放出素子の形成が可能となる。

【0083】

また、電子放出素子の形態は、図18、19に図示されているものに限るものではない。特に、本発明の構造体の一方の相である柱状部材間にバイアスを印加することで電子を放出させるような構造も好ましい。これと類似の電子放出素子は、空隙部分701を有する上記の本発明の針状構造体を使用することでも得られる。さらに、上記の電子放出素子において電子放出部1801の表面に薄くカーボンをコーティングすることも好ましい。

20

【0084】

なお、上記の電子放出素子の発明は、これらを多数配置した画像表示装置を含むものである。

【0085】

【実施例1】

本実施例は、本発明の構造体の形成に関するものである。

【0086】

30

本発明の範囲に属する構造体は、 $Si_nGe_{1-n}$ (ここで0  $n$  1)と元素Aとを主成分とする2元系以上からなるが、本実施例ではPdSi - Si系、PdGe - Ge系及びPdSiGe - SiGe系を取り上げてその構造について述べることにする。

【0087】

まず、図20のようにSiのスパッタリングターゲット上の中心にPdの12mm角の金属片を一つ配置し、基体104としてGe基板を選択する。ターゲットと基板との間の距離は約80mmであり、基板はターゲットに対して直上に配置する。成膜条件は、基板温度室温、基板へのDCバイアスなし、RF120Wの投入電力で、アルゴンガス圧0.1Paとし、5分間成膜を行う。

【0088】

40

また、同様にして、Geのスパッタリングターゲット上の中心にPdの12mm角の金属片を二つ配置し、基体104としてSi基板を選択する。ターゲットと基板との間の距離は約80mmであり、基板はターゲットに対して直上に配置する。成膜条件は、基板温度室温、基板へのDCバイアスなし、RF60Wの投入電力で、アルゴンガス圧0.1Paとし、5分間成膜を行う。

【0089】

そして、これら基板上に得られた膜の構造観察のために走査型電子顕微鏡にてその表面と断面の構造観察を行う。

【0090】

そうすると、PdSi - Si系では、Ge基板上に、表面構造として形状は円形で、平均直径が

50

約3nmの柱状のPdSi部分とその周りのSi部分からなる構造の確認ができる。さらに、断面観察においてPdSi部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。SiとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約12atomic%である。また、膜厚は約40nmである。

#### 【0091】

PdGe - Ge系では、Si基板上に、表面構造として形状は円形で、平均直径が約4.5nmの柱状のPdGe部分とその周りのGe部分からなる構造の確認ができる。さらに、断面観察においてPdGe部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。GeとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約15atomic%である。また、膜厚は約50nmである。

10

#### 【0092】

また、PdSi - Si系について、同様の成膜条件において、Siのスパッタリングターゲット上にPdの12mm角の金属片を3個配置して実施する。そうして得られる膜においては、表面構造として形状は円形で、平均直径が約3nmの柱状のSi部分とその周りのPdSi部分からなる構造ができる。さらに、断面観察においてSi部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。SiとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約37atomic%である。また、膜厚は約45nmである。

#### 【0093】

また、PdGe - Ge系について、同様の成膜条件において、Geのスパッタリングターゲット上にPdの12mm角の金属片を4個配置して実施する。そうして得られる膜においては、表面構造として形状は円形で、平均直径が約4.5nmの柱状のGe部分とその周りのPdGe部分からなる構造ができる。さらに、断面観察においてGe部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。GeとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約35atomic%である。また、膜厚は約50nmである。

20

#### 【0094】

更に、Siのスパッタリングターゲット上に、Pdの12mm角の金属片を1個配置し、且つGeの10mm角の金属片を1個配置し、RF100Wの投入電力で、成膜を実施する。基板としては、MgO基板を用いる。そうして得られる膜においては、表面構造として形状は円形で、平均直径が約3nm弱の柱状のPdSiGe部分とその周りのSiGe部分からなる構造ができる。さらに、断面観察においてPdSiGe部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。SiGeとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約10atomic%である。また、膜厚は約45nmである。このように、PdSiGe - SiGe系においても、PdSi - Si系やPdGe - Ge系と同様に、本発明の構造体の形成が確認される。

30

#### 【0095】

また、Siのスパッタリングターゲット上に、Pdの12mm角の金属片を3個配置し、且つGeの10mm角の金属片を1個配置し、RF100Wの投入電力で、成膜を実施する。基板としては、MgO基板を用いる。そうして得られる膜においては、表面構造として形状は円形で、平均直径が約3nm弱の柱状のSiGe部分とその周りのPdSiGe部分からなる構造ができる。さらに、断面観察においてSiGe部分が基板面から垂直に膜が堆積する方向に伸びた柱状構造を有していることも確認できる。SiGeとPdの組成を蛍光X線による分析から算出するとこの場合においてはPdが約39atomic%である。また、膜厚は約50nmである。このように、PdSiGe - SiGe系においても、PdSi - Si系やPdGe - Ge系と同様に、本発明の構造体の形成が確認される。

40

#### 【0096】

以上のことから、本発明の構造体の模式図である図1が示すように元素Aと $Si_nGe_{1-n}$ (ここで0 < n < 1)との間の化合物(本実施例ではPdSi、PdGe、PdSiGe)が柱状部材を担い、 $Si_nGe_{1-n}$ (ここで0 < n < 1)(本実施例ではSi、Ge、SiGe)または元素A(本実施例ではPd

50

) がその周りの部材を担う第一の組み合わせ 103 と、その担い手が反転した状態である第二の組み合わせ 102 とのいずれもが、組成の変化により達成可能であることがわかる。

**【0097】**

**[実施例 2]**

本実施例は、得られる構造体が本発明の範囲内のものであるかどうかを判断する手段に関する。

**【0098】**

実施例 1 に記載の柱状部材が PdSi であり平均直径が約 3 nm の構造体を 1 つの例として、その走査型電子顕微鏡像を利用して図 2 に示すフローチャートに従い判定を行うこととする。

10

**【0099】**

ちなみに、この画像を 2 値化したものが図 2 (b) に示される左側の画像に対応するものである。そして、2 値化した画像から (c-1) に従い長軸方向の平均直径 DI と短軸方向の平均直径 Ds を算出し、どちらも約 3 nm という値を得る。従って、DI/Ds を計算すると 1 となり、本発明で規定する 5 未満に適合するため、この構造体は本発明の構造体であると判明する。

**【0100】**

さらに、実施例 1 の場合とは異なり、Si スパッタリングターゲットの中心付近に 12 mm 角の Pd 板を 1 枚と 6 mm 角の Pd 板を 2 枚配置した場合に得られる構造を用いて、再度図 2 のフローチャートに従った判定を行うこととする。この場合は、図 2 (b) の右側に示されるものが対応する画像である。まず、画像を 2 値化した後、明らかに柱状部材の上面の形状が屈曲部を有する細長い形状を有しているものもあり、直ちに長軸方向の平均直径 DI を算出することが容易ではないことがわかる。従って、チャート中の (c-2) の処理に従い個々の柱状部材の上端面の面積を短軸方向の平均直径の算出値 Ds = 約 4 nm で割ることとする。それで得られる値の平均値を算出すると長軸方向の平均直径 DI として約 9 nm を得る。最終的に、DI/Ds を計算すると 9/4 となり 2.25 が導かれ、5 未満であることから本発明の構造体に属することが示せるのである。

20

**【0101】**

**[実施例 3]**

30

本実施例は、本発明の構造体が複数の材料から選択可能であることを示すと同時にそれらにおいて材料にかかわらず存在する相関関係に関する。

**【0102】**

実施例 1 のように相分離構造の柱状部材における上端面の形状が円形であるような組成に対して、成膜を Cu<sub>3</sub>Si-Si 系、PdSi-Si 系、NiSi-Si 系、CoSi<sub>2</sub>-Si 系、TiSi<sub>2</sub>-Si 系、WSi<sub>2</sub>-Si 系、更に Cu<sub>3</sub>Ge-Ge 系、PdGe-Ge 系、NiGe-Ge 系、TiGe<sub>2</sub>-Ge 系において試みる。それらの構造の平均直径を走査型電子顕微鏡にて観察すると上記の表 1 及び表 2 を得る。但し、ここでは、PdSi-Si 系の組成は実施例 1 のものと異なる。

**【0103】**

表 1 及び表 2 にはバルクの平衡状態図から読み取れる共晶温度 [ ] と本実施例にて観察される柱状部材の平均直径 [nm] とを列記している。ここから上記式 [1], [2] に示される相関関係が見出せる。

40

**【0104】**

このように、同じような構造体が得られる成膜条件や組成においては、異種材料やそれらの組成差に大きく依存しないという意味深い関係を導き出せる。これは、今までにない新たな発見であり、本発明において最も重要な事項の 1 つである。

**【0105】**

**[実施例 4]**

本実施例は、本発明の構造体が同一の材料と組成においても構造のサイズ等が変化することについての相関関係に関する。

50

## 【0106】

本実施例では、代表例としてPdSi-Si系を用いて説明する。実施例3と同様の条件で但し基板温度のみを室温の25、200、300と変化させて成膜を実施し、柱状部材を形成するPdSiの上端面の平均直径を計測すると上記の表3を得る。即ち、基板(基体)の温度に応じて、形成される構造体の柱状部材の平均直径が表3のように変化する。これから上記式[3]に示される相関関係が見出せる。

## 【0107】

この相関もまた本発明において最も重要な事項の1つであり、実施例3とあわせると所望の柱状部材の直径を得るためにどのような材料をどのような条件で実施することが好ましいかという指針を与えるものである。

10

## 【0108】

## [実施例5]

本実施例では、原料の種類や組成による構造の変化ではなく、スパッタリング法において制御可能なパラメータに依存して構造体が変化することに関する。

## 【0109】

まず、スパッタリング法におけるパラメータとしては、スパッタリングターゲットと基板との間の距離、投入電力、プロセスガスの種類・圧力、基板温度、基板バイアスの印加等があげられる。

## 【0110】

まず、4インチターゲットに対して投入電力を120Wとし、アルゴンガス圧を0.1Pa、基板温度室温に固定する。スパッタリングターゲットと基板との間の距離(以下、基板間距離といふことがある)の60mm、90mm、120mmに対して代表例としてPdSi-Si系を用いて構造の違いを見ることにする。基板にはGe基板を用いることとする。基板間距離が増加するに従ってPdSiの柱状構造の境界がやや不明瞭かつサイズ分布が大きくなることが観察され、基板間距離が増加するに従いスパッタリングされた原料粒子が基板まで飛来する間にエネルギーが失われることが確認される。

20

## 【0111】

次に、スパッタリングターゲットと基板との間の距離を90mmに固定し、投入電力を200Wとして、投入電力120Wとの比較を行う。PdSiの柱状構造が不明瞭かつ平均直径が小さくなることが観察され、投入電力の上昇による成膜速度の上昇にともない、基板上の元素の拡散による相分離が早い堆積速度により阻害されることが確認される。

30

## 【0112】

さらに、スパッタリングターゲットと基板との間の距離を90mm、投入電力を120Wに固定し、アルゴンガス圧を0.25Paとして、アルゴンガス圧0.1Paの場合との構造の違いを見ることとする。アルゴンガス圧の上昇に伴い、柱状構造のPdSiの平均直径が小さくなり、さらに境界も不明瞭になることが確認される。即ち、ガス圧の上昇に伴い飛来中に原料粒子のエネルギーが失われることと基板上においても拡散が阻害されることによることが確認される。

## 【0113】

基板温度に関しては、実施例4に示すとおりである。ただし、バルクの平衡状態図における共晶温度に近い基板温度となると二次元表面での拡散ではなく、バルクと同様の三次元的な拡散が支配的となるため好ましくないが、一定の温度まではおおむね実施例4に示すことが成り立つことがわかる。

40

## 【0114】

最後に、基板バイアスの印加である。スパッタリングターゲットと基板との間の距離を90mm、投入電力を120W、アルゴンガス圧を0.1Pa、基板温度を室温として、基板バイアスをDCで0V、-20V、-40V印加した場合を行った。ただ、基板の抵抗が大きい場合にはDCバイアスを印加することが不可能であるため低抵抗な基板を使用する。絶縁基板の場合には、RFバイアスを印加することで対応可能である。この場合には、バイアスの印加なしの小さな平均直径を有するPdSiの柱状構造が、バイアスの印加を増大させて

50

いくにつれ、平均直径が顕著に大きくなることがわかる。基板バイアスの効果としては、イオン化した粒子を基板上に引き込み、基板上の粒子と衝突させることにより、エネルギーの受け渡しの結果として表面拡散のエネルギーを増加させ、平均直径を大きくすることが挙げられる。また、この効果が行過ぎた場合には、スパッタリングと同様の現象となり、基板表面の粒子が離脱して膜が形成されないこともわかる。

【0115】

以上のように、スパッタリング法における様々なパラメータの変化によっても構造体の制御が可能であることが示される。

【0116】

[実施例6]

10

本実施例は、本発明の相分離構造をもつ構造体から柱状部材部分のみを除去することにより得られるポーラス構造体に関する。

【0117】

実施例1に示したPdSi-Si系を代表例として取り上げる。先ず、12mm角のPd板をスパッタリングターゲットの中心付近に3個配置した場合に得られる膜状構造体と、その状況にて基板温度を300に変更した場合に得られる膜状構造体とを準備する。前者の膜状構造体は柱状部材がSiであり平均直径が約3nmであり、後者の膜状構造体も柱状部材がSiであり但し平均直径が約5nmである。

【0118】

それぞれの膜状構造体のSi部分を除去することにより本発明のポーラス構造体の形成が可能である。Si部分の除去にはSiのみをエッチング可能とする選択性を持った手法が好ましく、60程度のKOH水溶液中に浸漬することで、Siの選択エッチングが可能であることがわかる。しかし、本実施例の前者の場合は、柱状部材のSiを取り囲むPdSi部分が十分結晶化しておらずアモルファス状であるためSiのダンギングボンドの存在によりSiのエッチングと同時にPdSi部分もゆっくりエッチングされることがわかる。ただ、後者の場合にはPdSi部分の結晶化が進んでおり、エッチングにおいても犯されることなく目的のSiの柱状部材のみが除去され、ポーラス構造体を得ることが可能になる。以上は液中のエッチングであるが、気相中のエッチングを行うことも好ましい。そこで、上記の2種類の膜状構造体に対して、XeF<sub>2</sub>というガスの雰囲気下でのSiの選択エッチングという特徴を利用する方法を試みることが可能である。上記の前者の膜に適用すると柱状部材をなすSi部分のみならず、PdSi部分のSiをも除去しており、本発明のポーラス構造体の形成には好ましくないことが確認できる。しかし、後者の膜ではやはりPdSiが十分結晶化しているためにSiの柱状部材部分のみ選択的にエッチングされていることが確認できる。

20

30

30

【0119】

以上から、本発明の相分離構造をもつ構造体は、元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物の部分が十分結晶化している場合のみに限定するものではないが、本発明のポーラス構造体を形成するにあたっては、ある程度元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物の部分の結晶化が進んだ構造体を用いることが、選択性エッチングに対して好ましいことが示される。

【0120】

40

また、本実施例は元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物とSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)とからなる構造体を出発点として示している。しかし、元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物と元素Aとからなる構造体においても同様に結晶化が進んでいる元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物の高い耐薬品性や耐熱性等を利用して選択的にエッチングすることが可能である。さらに、元素Aが金属である場合には金属固有の酸またはアルカリのエッチング溶液などを用いることで選択的なエッチングが容易に可能である。この場合には、金属の種別にもよるが酸に容易に溶解するために元素AとSi<sub>n</sub>Ge<sub>1-n</sub>(ここで0≤n≤1)との間の化合物の部分が十分結晶化していない場合にも本発明のポーラス構造体を得ることが可能である。

【0121】

50

## [実施例 7]

本実施例は、本発明の相分離構造をもつ構造体から柱状部材以外の部分のみを除去することにより得られる針状構造体に関する。

## 【0122】

実施例 6 の手段に順ずるが、実施例 1 に示した PdSi-Si 系を代表例として取り上げる。先ず、12mm 角の Pd 板をスパッタリングターゲットの中心付近に 1 個配置した場合に得られる膜状構造体と、その状況にて基板温度を 300 にした場合に得られる膜状構造体とを準備する。前者の膜状構造体は柱状部材の部分が PdSi であり平均直径が約 3nm であり、後者の膜状構造体も柱状部材が PdSi であり但し平均直径が約 5nm である。もちろん、柱状部材以外の部分を Si が形成している。

10

## 【0123】

それぞれの膜状構造体の Si 部分を除去することにより本発明の針状構造体の形成が可能である。Si 部分の除去には Si のみをエッチング可能とする選択性を持った手法が好ましく、60 程度の KOH 水溶液中に浸漬することで、Si の選択性エッチングが可能であることがわかる。しかし、本実施例の前者の場合は、柱状部材の PdSi 部分が十分結晶化しておらずアモルファス状であるため Si のダングリングボンドの存在により Si のエッチングと同時に PdSi 部分もゆっくりエッチングされることがわかる。ただ、後者の場合には PdSi 部分の結晶化が進んでおり、エッチングにおいても犯されることなく目的の柱状部材以外の部分を形成する Si のみが除去されている針状構造体を得ることが可能である。以上は液中のエッティングであるが、気相中のエッティングを行うことも好ましい。そこで、上記の 2 種類の膜状構造体に対して、XeF<sub>2</sub> というガスの雰囲気下での Si の選択性エッティングという特徴を利用する方法を試みることが可能である。上記の前者の膜状構造体に適用すると柱状部材以外の部分をなす Si 部分のみならず、柱状部材をなす PdSi 部分の Si をも除去しており、本発明の針状構造体の形成には好ましくないことが確認できる。しかし、後者の膜状構造体ではやはり PdSi が十分結晶化しているために柱状部材以外の部分をなす Si のみが選択的にエッティングされていることが確認できる。

20

## 【0124】

以上から、本発明の相分離構造をもつ構造体は、元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物の部分が十分結晶化している場合のみに限定するものではないが、本発明の針状構造体を形成するにあたっては、ある程度元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物の部分の結晶化が進んだ構造体を用いることが、選択性エッティングに対して好ましいことが示される。

30

## 【0125】

また、本実施例は元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) とからなる構造体を出発点として示している。しかし、元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物と元素 A とからなる構造体においても同様に結晶化が進んでいる元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物の高い耐薬品性や耐熱性等を利用して選択性にエッティングすることが可能である。さらに、元素 A が金属である場合には金属固有の酸またはアルカリのエッティング溶液などを用いることで選択性エッティングが容易に可能である。この場合には、金属の種別にもよるが酸に容易に溶解するために元素 A と Si<sub>n</sub>Ge<sub>1-n</sub> (ここで 0 < n < 1) との間の化合物の部分が十分結晶化していない場合にも本発明の針状構造体を得ることが可能である。

40

## 【0126】

## [実施例 8]

本実施例は、本発明の相分離構造をもつ構造体を用いた電子デバイスに関する。

## 【0127】

本発明の構造体の上部に 3 つの電極を配置する。ちょうど図 14 のように配置すると電極間にはほぼ柱状部材が一つ配置されている格好となる。この状況を本発明の NiSi-Si 系にて構成される NiSi の柱状部材とその周りの Si とからなる構造体を代表例として利用して実現させることができ。これらの図 14 中の左右の電極 (ソース電極 1403 及び

50

ドレイン電極 1404) 間で計測を行うと図 14 中の下部の電極 (ゲート電極 1402) にてバイアスを印加している場合にはトンネル電流が観測されない。しかし、バイアスを解除するとトンネル電流が観測され、NiSi の柱状部材間の Si 領域をトンネルして、電極間を電子が通過したことが確認できる。従って、本発明の構造体を利用すると量子ドット、量子細線などの電子デバイス、単電子デバイスに有効であることがわかる。

【0128】

[実施例 9]

本実施例は、本発明の相分離構造をもつ構造体を用いたゲート電極に関する。

【0129】

柱状部材が  $TiSi_2$ 、 $CoSi_2$  等からなりその周りに Si からなる本発明の膜状構造体を代表例として取り上げる。図 15 にて下側に示すゲート電極部分 1503 (ソース電極部分、ドレイン電極部分にも適用可) に成膜する。比較例として、Ti、Co 等からなる金属膜を同様に成膜し、急速加熱で拡散させて界面に、図 15 にて上側に示すように、 $TiSi_2$ 、 $CoSi_2$  等のシリサイドからなるゲート電極部分 1503 (ソース電極部分、ドレイン電極部分にも適用可) を形成させる。これらの電極を用いるトランジスタのリーク電流値を比較すると、本発明の構造体を利用する場合においては、柱状部材部分が電流を垂直方向のみに誘導し、面内方向へのリークが抑制されていることが確認できる。従って、本発明のゲート電極によれば、電流を流す向きに異方性を持たせることができることがわかる。

10

【0130】

[実施例 10]

20

本実施例は、本発明の相分離構造をもつ構造体を記録層制御に用いた磁気記録媒体に関する。

【0131】

まず、本発明の構造体の相分離構造における特徴は幅広い温度領域に渡って共晶関係にある材料を出発点としている。つまり、図 4 (c) または (d) のように簡潔な共晶系状態図を有していることであり、現行の CoCr 系磁気記録媒体における相分離構造と比較した場合、柱状部材の平均直径などの分散や柱状部材の形状において、本発明の構造体の方が優れている。さらに、図 8 の磁気記録媒体における記録層 803 の初期層と呼ばれる初期の結晶配列などが乱れた層領域が磁記録性などに悪影響を及ぼすことがわかっている。これを克服するために、本発明の構造体を下地層 802 として用いることで、記録層形成初期の層領域から、構造体の柱状部材部分に記録層 803 の磁性粒子がエピタキシャルに成長を開始する核の役割を果たさせる。これにより、非常に磁性粒子の形状制御と結晶性制御にすぐれた記録層 803 の形成が可能である。

30

【0132】

まず、本発明の構造体である PdSi-Si 系を代表例として取り上げ、これを下地層として準備し、引き続き CoCrPt-SiO<sub>2</sub> 系の材料をスパッタリング成膜する。この試料の断面方向からの透過型電子顕微鏡による観察を実施すると、本発明の構造体からなる下地層の柱状部材をなす PdSi と記録層を形成する CoCrPt とがエピタキシャルに接続して結晶成長していることが確認できる。さらに、PdSi の周りの Si 部分に対応して SiO<sub>2</sub> 部分が成長しており、下地層における PdSi の直径の低分散な状態を保ったまま CoCrPt が記録層を形成できることが確認できる。この状況は、低ノイズな磁気記録媒体の提供において重要である。

40

【0133】

以上のように、本発明の構造体は結晶成長における非常に優れた下地層としての役割を果たすことが可能であることがわかる。

【0134】

[実施例 11]

本実施例は、本発明のポーラス構造体を用いた磁気記録媒体に関する。

【0135】

実施例 6 により得られた本発明のポーラス構造体を準備する。ただし、このポーラス構造体の層の下には Pt からなる金属層を形成しておく。このポーラス構造体をスルファミン

50

酸コバルトを主成分とするメッキ液に浸漬し、Pt層を介して電圧を印加する。参照極のAg/AgClに対して-1.0Vの電位にて実施するとポーラス構造体の微細孔の底部からコバルトが析出し、すべての微細孔がコバルトで充填された膜を得ることが可能である。このようにして、メッキ液の調製が可能であれば所望の硬磁性材料をポーラス構造体の微細孔にメッキ技術により充填することが可能であり、その際ポーラス構造体の下には低抵抗金属からなる金属層を配置してメッキすることが可能である。また、電解メッキのみならず、無電解メッキも適用可能であることがわかる。

【0136】

以上のようにして磁性材料が充填されている膜からなる記録層が形成されたのち、保護層としてダイヤモンドライクカーボンを成膜し、パーフルオロポリエーテルからなる潤滑剤を塗布して潤滑層を形成し、記録再生可能な媒体とすることが可能である。

10

【0137】

こうして得られる磁気記録媒体は、記録層の硬磁性粒子部分以外の部分が強度にすぐれた元素Aと $Si_nGe_{1-n}$ (ここで0 < n < 1)との間の化合物でできているので、使用環境において変質・衝撃に対する耐久性が強い。

【0138】

また、十分磁性粒子が分離されており、低ノイズな磁気記録媒体としても非常に有効である。特に、磁性粒子の直径を8nm以下とする場合には、CoPt、FePt等の規則合金を主成分とする材料を利用することも可能である。

【0139】

20

[実施例12]

本実施例は、本発明のポーラス構造体を用いた磁気記録媒体に関する。

【0140】

実施例6により得られた本発明のポーラス構造体を準備する。ただし、このポーラス構造体の層の下にはPtからなる金属層を形成しておく。このポーラス構造体をスルファミン酸ニッケルと塩化鉄とを主成分とする軟磁性用メッキ液に浸漬し、Pt層を介して電圧を印加する。参照極のAg/AgClに対して-1.2Vの電位にて実施するとポーラス構造体の微細孔の底部からニッケル鉄合金が析出し、すべての微細孔がニッケル鉄合金で充填された膜を得ることが可能である。このようにして、メッキ液の調製が可能であれば所望の軟磁性材料をポーラス構造体の微細孔にメッキ技術により充填することが可能であり、その際ポーラス構造体の下には低抵抗金属からなる金属層を配置してメッキすることが可能である。また、電解メッキのみならず、無電解メッキも適用可能であることがわかる。

30

【0141】

以上のようにして軟磁性材料が充填されている膜からなる軟磁性層が形成されたのち、記録層(CoCrPt-SiO<sub>2</sub>系材料からなるもの)を形成する。更には保護層としてダイヤモンドライクカーボンを成膜し、パーフルオロポリエーテルからなる潤滑剤を塗布して潤滑層を形成し、記録再生可能である媒体とすることが可能である。尚、軟磁性層と記録層との間に下地層を介在させてよい。

【0142】

こうして得られる磁気記録媒体は、軟磁性層の軟磁性粒子部分以外の部分が強度にすぐれた珪化物でできているので、使用環境において変質・衝撃に対する耐久性が強い。

40

【0143】

また、十分磁性粒子が分離されており、軟磁性層を起源とするスパイクノイズなどが発生しない磁気記録媒体としても非常に有効である。

【0144】

[実施例13]

本実施例は、本発明の磁気記録媒体を用いた磁気記録再生装置に関する。

【0145】

実施例10、11、12に示すような本発明の磁気記録媒体を用いて、図12のような磁気記録媒体1200と磁気記録媒体駆動部1201と磁気ヘッド1202と磁気ヘッド

50

駆動部 1203 と信号処理部 1204 とからなる装置に組み立てる。これにより、磁気記録再生装置を形成することが可能である。尚、本実施例により本発明の磁気記録媒体 1200 の駆動が回転のみ、磁気ヘッド 1202 の駆動が円周上のスライドのみに限定されるものではない。

【0146】

[実施例 14]

本実施例は、本発明の磁気記録再生装置を用いた情報処理装置に関する。

【0147】

実施例 13 に記載の磁気記録再生装置部 1301 は、情報の出し入れが可能である。このため、図 13 に示すように、この磁気記録再生装置部とメモリ部 1303 と演算部 1302 と外部入出力部 1305 と電源 1304 とこれらをつなぐ配線 1306 とを格納容器 1300 に収めた情報処理装置を形成することが可能である。また、配線 1306 は有線、無線の関係なく、情報のやり取りが可能であればその役割を果たすものである。

【0148】

[実施例 15]

本実施例は、本発明のポーラス構造体を用いた触媒能を有する機能性膜に関する。ここでは、本発明の構造体として PtSi-Si 系構造体を代表例として取り上げる。

【0149】

スパッタリング法により基板温度 300 にて、RF電力 120W、アルゴンガス圧 0.1 Pa にて 15mm 角の Pt 板を Si のスパッタリングターゲットの中心に 4 枚配置し、PtSi-Si 系構造体を 1 μm 厚さで、W 下地層を有する基体 104 上に作製した。そして、XeF<sub>2</sub> のガスにより Si 部分を選択エッチングすると PtSi のメンブレンが形成されていることが確認できる。さらに、燃料電池用の電解質膜を塗布・圧着し、引き剥がすことにより基体 104 から PtSi メンブレンを剥離し、電解質膜 1601 と貴金属含有メンブレン 1603 とが図 16 のように一体化した燃料電池用触媒にも利用できる機能性膜を形成することが可能である。比較例としての一般的な貴金属粒子をカーボンブラックに担持させた触媒（貴金属担持させるものの厚さを 1 μm とする）との電流密度と燃料電池セル電圧特性の違いを比較する。同一の電圧出力に対して、本発明の触媒能を有する機能性膜の方が比較例の担持触媒よりも電流密度が約 2.5 倍高い値を示すことが確認できる。これは、単位容積当たりの貴金属使用量が少ないにもかかわらず高い電流密度の値を得ることを可能にするものであることがわかる。

【0150】

[実施例 16]

本実施例は、本発明の針構造体を用いた触媒能を有する機能性膜に関する。ここでは、本発明の構造体として PtSi-Si 系構造体を代表例として取り上げる。

【0151】

スパッタリング法により基板温度 300 にて、RF電力 120W、アルゴンガス圧 0.1 Pa にて 15mm 角の Pt 板を Si のスパッタリングターゲットの中心に 2 枚配置し、PtSi-Si 系構造体を 1 μm 厚さで、W 下地層を有する基体 104 上に作製した。そして、XeF<sub>2</sub> のガスにより Si 部分を選択エッチングすると PtSi のロッドが形成されていることが確認できる。さらに、燃料電池用の電解質膜を塗布・圧着し、引き剥がすことにより基体 104 から PtSi ロッドが剥離し、電解質膜 1601 と貴金属含有ロッド 1700 とが図 17 のように一体化した燃料電池用触媒にも利用できる機能性膜を形成することが可能である。比較例としての一般的な貴金属粒子をカーボンブラックに担持させた触媒（貴金属担持させる厚さを 1 μm とする）との電流密度と燃料電池セル電圧特性の違いを比較する。同一の電圧出力に対して、本発明の触媒能を有する機能性膜の方が比較例の担持触媒よりも電流密度が約 3 倍高い値を示すことが確認できる。これは、単位容積当たりの貴金属使用量が少ないにもかかわらず高い電流密度の値を得ることを可能にするものであることがわかる。

【0152】

[実施例 17]

10

20

30

40

50

本実施例は、本発明の相分離構造をもつ構造体を用いた電子放出素子に関する。

【0153】

図18にあるように、本発明のNb、Mo、W、Ti等の元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物の柱状部材を有する構造体上に開口を有する絶縁層1802と引き出し電極1803とを形成し、引き出し電極1803と本発明の構造体との間に電圧を印加する。これにより、構造体の柱状部材から効率良く電子放出を行うことが可能であることが確認できる。さらに、効果としては柱状部材が元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物から形成されていることを反映して、非常に高い耐熱性を有していることが確認でき、長寿命で電子放出の電流値が安定した電子放出素子を得られることが確認できる。

【0154】

10

[実施例18]

本実施例は、本発明の針状構造体を用いた電子放出素子に関する。

【0155】

図19にあるように、本発明のNb、Mo、W、Ti等の元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物の柱状部材を有する構造体上に開口を有する絶縁層1802と引き出し電極1803とを形成する。さらに $XeF_2$ による選択エッティングにより電子放出部1801に対応する領域の柱状部材の周りの $Si_nGe_{1-n}$ (ここで0  $n$  1)の部分のみの除去を行って、空隙部分701を形成する。そして、引き出し電極1803と本発明の構造体との間に電圧を印加することで構造体の柱状部材から効率良く電子放出を行うことが可能であることが確認できる。さらに、効果としては元素Aと $Si_nGe_{1-n}$ (ここで0  $n$  1)との間の化合物から形成されていることを反映して、非常に高い耐熱性を有していることが確認でき、長寿命で電子放出の電流値が安定した電子放出素子を得られることが確認できる。

20

【図面の簡単な説明】

【0156】

【図1】本発明の構造体の模式図である。

【図2】本発明の構造体を長軸方向の平均直径と短軸方向の平均直径との比から規定する方法に関するフローチャートである。

【図3】本発明の構造体における長軸方向の直径と短軸方向の直径を示す模式図である。

【図4】従来の構造体及び本発明の構造体をそれぞれ構成する原料が有する平衡状態図の一例である。

30

【図5】相分離構造を形成する過程を示す概念図である。

【図6】本発明のポーラス構造体の模式図である。

【図7】本発明の針状構造体の模式図である。

【図8】磁気記録媒体の層構成を示す模式図である。

【図9】本発明の構造体を用いた磁気記録媒体の一例を示す模式図である。

【図10】本発明のポーラス構造体を用いた記録層の一例を示す模式図である。

【図11】本発明のポーラス構造体を用いた軟磁性層の一例を示す模式図である。

【図12】本発明の磁気記録媒体を用いた磁気記録再生装置を示す模式図である。

【図13】本発明の磁気記録再生装置を用いた情報処理装置の概念図である。

【図14】本発明の構造体を用いた電子デバイスの一例を示す概念図である。

40

【図15】トランジスタの電極部分を示す模式図である。

【図16】本発明のポーラス構造体を用いた触媒能を有する機能性膜の模式図である。

【図17】本発明の針状構造体を用いた触媒能を有する機能性膜の模式図である。

【図18】本発明の構造体を用いた電子放出素子の概念図である。

【図19】本発明の針状構造体を用いた電子放出素子の概念図である。

【図20】スパッタリング法を説明する概念図である。

【符号の説明】

【0157】

100, 100' 第一の部材

101, 101' 第二の部材

50

|         |                       |    |

|---------|-----------------------|----|

| 1 0 2   | 第二の組み合わせ              |    |

| 1 0 3   | 第一の組み合わせ              |    |

| 1 0 4   | 基体                    |    |

| 3 0 0   | 長軸方向の直径               |    |

| 3 0 1   | 短軸方向の直径               |    |

| 4 0 1   | 複数の化合物                |    |

| 5 0 1   | 飛来した元素                |    |

| 5 0 2   | 表面拡散する元素              |    |

| 5 0 3   | 基体表面                  |    |

| 5 0 4   | 相分離過程                 | 10 |

| 5 0 5   | 化合物                   |    |

| 6 0 0   | 微細孔                   |    |

| 6 0 1   | 第一の部材乃至第二の部材          |    |

| 7 0 1   | 空隙部分                  |    |

| 8 0 1   | 軟磁性層                  |    |

| 8 0 2   | 下地層                   |    |

| 8 0 3   | 記録層                   |    |

| 8 0 4   | 保護層                   |    |

| 8 0 5   | 潤滑層                   |    |

| 9 0 0   | 本発明の構造体からなる層          | 20 |

| 9 0 1   | 硬磁性粒子                 |    |

| 9 0 2   | 非磁性領域                 |    |

| 1 0 0 0 | 硬磁性材料                 |    |

| 1 0 0 1 | 第一の部材乃至第二の部材からなる非磁性領域 |    |

| 1 1 0 0 | 軟磁性材料                 |    |

| 1 2 0 0 | 磁気記録媒体                |    |

| 1 2 0 1 | 磁気記録媒体駆動部             |    |

| 1 2 0 2 | 磁気ヘッド                 |    |

| 1 2 0 3 | 磁気ヘッド駆動部              |    |

| 1 2 0 4 | 信号処理部                 | 30 |

| 1 3 0 0 | 格納容器                  |    |

| 1 3 0 1 | 磁気記録再生装置部             |    |

| 1 3 0 2 | 演算部                   |    |

| 1 3 0 3 | メモリ部                  |    |

| 1 3 0 4 | 電源                    |    |

| 1 3 0 5 | 外部入出力部                |    |

| 1 3 0 6 | 配線                    |    |

| 1 4 0 1 | 本発明の構造体               |    |

| 1 4 0 2 | ゲート電極                 |    |

| 1 4 0 3 | ソース電極                 | 40 |

| 1 4 0 4 | ドレイン電極                |    |

| 1 5 0 1 | ソース電極                 |    |

| 1 5 0 2 | ドレイン電極                |    |

| 1 5 0 3 | ゲート電極部分               |    |

| 1 5 0 4 | スペーサ                  |    |

| 1 5 0 5 | ゲート酸化膜                |    |

| 1 5 0 6 | シリサイド                 |    |

| 1 5 0 7 | 構造体部分                 |    |

| 1 6 0 1 | 電解質膜                  |    |

| 1 6 0 3 | 貴金属含有メンブレン            | 50 |

|      |                                        |    |

|------|----------------------------------------|----|

| 1700 | 貴金属含有ロッド                               |    |

| 1800 | 下地電極                                   |    |

| 1801 | 電子放出部                                  |    |

| 1802 | 絶縁層                                    |    |

| 1803 | 引き出し電極                                 |    |

| 1804 | 電子放出方向                                 |    |

| 1805 | バイアス印加回路                               |    |

| 2001 | スパッタリングターゲット                           |    |

| 2002 | $Si_nGe_{1-n}$ (ここで0 < n < 1) または元素Aの板 |    |

| 2004 | スパッタリングターゲットと基体との間の距離                  | 10 |

| 2005 | 成膜方向                                   |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

(a) 平面図

(b) AA'断面図

【図8】

【図10】

(a) 平面図

(b) AA'断面図

【図11】

(a) 平面図

(b) AA'断面図

【図9】

(a) 平面図

(b) AA'断面図

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

| (51) Int.CI. |                 | F I     |               |

|--------------|-----------------|---------|---------------|

| G 1 1 B      | 5/667 (2006.01) | H 0 1 L | 29/06 6 0 1 L |

| G 1 1 B      | 5/738 (2006.01) | G 1 1 B | 5/65          |

| H 0 1 L      | 29/66 (2006.01) | G 1 1 B | 5/667         |

|              |                 | G 1 1 B | 5/738         |

|              |                 | H 0 1 L | 29/66 E       |

(72) 発明者 田 透

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 渡邊 吉喜

(56) 参考文献 米国特許第05211707(US, A)

特開2005-059125(JP, A)

特開2004-223695(JP, A)

特開2004-237429(JP, A)

特開2005-060755(JP, A)

(58) 調査した分野(Int.CI., DB名)

B 8 2 B 1 / 0 0 - 3 / 0 0,

B 8 2 Y 5 / 0 0 - 9 9 / 0 0