(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6261720号

(P6261720)

(45) 発行日 平成30年1月17日(2018.1.17)

(24) 登録日 平成29年12月22日(2017.12.22)

(51) Int.Cl.

F 1

H01L 33/54 (2010.01)

H01L 33/50 (2010.01)H01L 33/54

H01L 33/50

請求項の数 15 (全 24 頁)

(21) 出願番号 特願2016-513237 (P2016-513237)

(86) (22) 出願日 平成25年5月17日 (2013.5.17)

(65) 公表番号 特表2016-518725 (P2016-518725A)

(43) 公表日 平成28年6月23日 (2016.6.23)

(86) 國際出願番号 PCT/EP2013/060279

(87) 國際公開番号 WO2014/183800

(87) 國際公開日 平成26年11月20日 (2014.11.20)

審査請求日 平成28年1月15日 (2016.1.15)

(73) 特許権者 599133716

オスラム オプト セミコンダクターズ

ゲゼルシャフト ミット ベシュレンクテ

ル ハフツング

Osram Opto Semiconduc

tors GmbH

ドイツ連邦共和国、93055 レーゲン

スブルグ、ライプニッツシュトラーゼ 4

Leibnizstrasse 4, D

-93055 Regensburg,

Germany

(74) 代理人 100114890

弁理士 アインゼル・フェリックス=ライ

ンハルト

最終頁に続く

(54) 【発明の名称】オプトエレクトロニクス素子およびオプトエレクトロニクス素子の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

オプトエレクトロニクス素子であって、

ケーシング(100)を有しており、

当該ケーシング(100)は、当該ケーシング(100)の上面(101)に向かって開放されている第1のキャビティ(200)と、当該ケーシング(100)の前記上面(101)に向かって開放されている第2のキャビティ(300)とを有しており、

前記第1のキャビティ(200)と前記第2のキャビティ(300)とは、接続チャネル(400)によって接続されており、

前記第1のキャビティ(200)の中には、オプトエレクトロニクス半導体チップ(700)が配置されており、

前記第1のキャビティ(200)の、前記オプトエレクトロニクス半導体チップ(700)を包囲している領域内には、注封材料(800、810)が配置されており、

前記オプトエレクトロニクス半導体チップ(700)の電気的なコンタクト面と、前記ケーシング(100)のボンディング面(610)との間にボンディングワイヤー(630)が配置されており、

前記ボンディング面(610)は前記接続チャネル(400)に配置されており、

前記第2のキャビティ(300)内に、注封材料(800、820)が配置されており、

前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において

10

20

、前記第1のキャビティ(200)における、前記第1のキャビティ(200)の底面(210)からの前記注封材料の高さのうちの最も小さい高さ(811)と、前記第2のキャビティ(300)における、前記第2のキャビティ(300)の底面からの前記注封材料の高さのうちの最も小さい高さ(821)とは異なっている、

ことを特徴とするオプトエレクトロニクス素子。

【請求項2】

前記接続チャネル(400)は、前記第1のキャビティ(200)と前記第2のキャビティ(300)との間の接続方向に対して垂直に、前記第1のキャビティ(200)および前記第2のキャビティ(300)よりも狭い幅(401)を有している、請求項1記載のオプトエレクトロニクス素子。

10

【請求項3】

前記第1のキャビティ(200)は第1の容積(202)を有しており、

前記第2のキャビティ(300)は第2の容積(302)を有しており、

前記第2の容積(302)は少なくとも、前記第1の容積(202)と同じ大きさである、請求項1または2記載のオプトエレクトロニクス素子。

【請求項4】

前記第1のキャビティ(20)は、周囲を包囲している壁部(230)によって画定されており、

前記壁部(230)は段階部(260)を有しており、

前記第1のキャビティ(200)は当該段階部(260)で、前記ケーシング(100)の前記上面(101)に向かって幅が広くなっている、請求項1から3までのいずれか1項記載のオプトエレクトロニクス素子。

20

【請求項5】

前記第1のキャビティ(200)と前記第2のキャビティ(300)は、前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、異なる深さを有している、請求項1から4までのいずれか1項記載のオプトエレクトロニクス素子。

【請求項6】

前記オプトエレクトロニクス半導体チップ(700)は、ビームを放射する上面(701)を有しており、

ビームを放射する前記上面(701)上には、波長変換素子(730)が配置されている、請求項1から5までのいずれか1項記載のオプトエレクトロニクス素子。

30

【請求項7】

前記波長変換素子(730)の上面(731)と、前記第1のキャビティ(200)の、前記ケーシング(100)に形成されている、周囲を囲んでいる縁部(240)との間に、前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、60μmを下回る、高さの相違が生じている、請求項6記載のオプトエレクトロニクス素子。

【請求項8】

前記オプトエレクトロニクス半導体チップ(700)の上面(701)と、前記第1のキャビティ(200)の、前記ケーシング(100)に形成されている、周囲を取り囲んでいる縁部(240)との間に、前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、60μmを下回る、高さの相違が生じている、請求項1から5までのいずれか1項記載のオプトエレクトロニクス素子。

40

【請求項9】

前記ケーシング(100)は、前記ケーシング(100)の前記上面(101)に向かって開放されている、別のキャビティ(1300)を有しており、

当該別のキャビティ(1300)は、別の接続チャネル(1400)によって、前記第1のキャビティ(200)または前記第2のキャビティ(300)と接続されている、請求項1から8までのいずれか1項記載のオプトエレクトロニクス素子。

【請求項10】

50

前記別のキャビティの中には、別のオプトエレクトロニクス半導体チップ(1700)が配置されている、請求項9記載のオプトエレクトロニクス素子。

【請求項11】

オプトエレクトロニクス素子であって、

ケーシング(100)を有しており、

当該ケーシング(100)は、当該ケーシング(100)の上面(101)に向かって開放されている第1のキャビティ(200)と、当該ケーシング(100)の前記上面(101)に向かって開放されている第2のキャビティ(300)とを有しており、

前記第1のキャビティ(200)と前記第2のキャビティ(300)とは、接続チャネル(400)によって接続されており、

前記第1のキャビティ(200)の中には、オプトエレクトロニクス半導体チップ(700)が配置されており、

前記第1のキャビティ(200)の、前記オプトエレクトロニクス半導体チップ(700)を包囲している領域内には、注封材料(800、810)が配置されており、

前記オプトエレクトロニクス半導体チップ(700)の電気的なコンタクト面と、前記ケーシング(100)のボンディング面(610)との間にボンディングワイヤー(630)が配置されており、

前記オプトエレクトロニクス半導体チップ(700)は、第1の幾何学的形状を備えた上面(701)を有しており、

前記第1のキャビティ(200)は、幾何学的な基本形状を有している底面(210)を有しており、当該幾何学的な基本形状は、前記第1の幾何学的形状と相似関係にあり、かつ、当該第1の幾何学的形状を拡大することにより形成され、

前記第1のキャビティ(200)の前記底面(210)は、前記幾何学的な基本形状に対して付加的に張り出し部(250)を有しており、

前記ボンディング面(610)は、前記底面(210)に接している前記張り出し部(250)内に配置されており、

前記第2のキャビティ(300)内に、注封材料(800、820)が配置されており、

前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、前記第1のキャビティ(200)における、前記第1のキャビティ(200)の底面(210)からの前記注封材料の高さのうちの最も小さい高さ(811)と、前記第2のキャビティ(300)における、前記第2のキャビティ(300)の底面からの前記注封材料の高さのうちの最も小さい高さ(821)とは異なっている、

ことを特徴とするオプトエレクトロニクス素子。

【請求項12】

前記第1のキャビティ(200)と前記第2のキャビティ(300)は、前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、異なる深さを有している、請求項11記載のオプトエレクトロニクス素子。

【請求項13】

前記ケーシング(100)は、前記ケーシング(100)の前記上面(101)に向かって開放されている、別のキャビティ(1300)を有しており、

当該別のキャビティ(1300)は、別の接続チャネル(1400)によって、前記第1のキャビティ(200)または前記第2のキャビティ(300)と接続されている、請求項11または12記載のオプトエレクトロニクス素子。

【請求項14】

オプトエレクトロニクス素子の製造方法であって、

・ケーシング(100)を提供するステップを有しており、当該ケーシング(100)は、当該ケーシング(100)の上面(101)に向かって開放されている第1のキャビティ(200)と、当該ケーシング(100)の前記上面(101)に向かって開放されている第2のキャビティ(300)とを有しており、前記第1のキャビティ(200)と

10

20

30

40

50

前記第2のキャビティ(300)とは、接続チャネル(400)によって接続されており、

・オプトエレクトロニクス半導体チップ(700)を前記第1のキャビティ(200)内に配置するステップを有しており、

・注封材料(800)を、前記第1のキャビティ(200)の、前記オプトエレクトロニクス半導体チップ(700)を包囲している領域に入れるステップを有しており、

前記注封材料(800)を前記第2のキャビティ(300)内に入れ、

前記注封材料(800)は前記第2のキャビティ(300)から前記接続チャネル(400)を通じて、前記第1のキャビティ(200)に達し、

前記ケーシング(100)の前記上面(101)に対して垂直な方向(11)において、前記第1のキャビティ(200)における、前記第1のキャビティ(200)の底面(210)からの前記注封材料の高さのうちの最も小さい高さ(811)と、前記第2のキャビティ(300)における、前記第2のキャビティ(300)の底面からの前記注封材料の高さのうちの最も小さい高さ(821)とは異なっている、

ことを特徴とする、オプトエレクトロニクス素子の製造方法。

#### 【請求項15】

前記製造方法は、

・前記ケーシング(100)の、前記第2のキャビティ(300)を含んでいる部分を切り離すステップを含んでいる、請求項14記載の方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、請求項1記載のオプトエレクトロニクス素子、請求項13記載のオプトエレクトロニクス素子、並びに請求項18記載のオプトエレクトロニクス素子の製造方法に関する。

##### 【0002】

従来技術から、オプトエレクトロニクス素子が既知である。ここでは、オプトエレクトロニクス半導体チップは、オプトエレクトロニクス素子のケーシングの、オプトエレクトロニクス素子の放射面の方に向かって開放されているキャビティ内に配置されている。オプトエレクトロニクス半導体チップおよび場合によって設けられているボンディングワイヤーおよび変換素子は、ここで、しばしば、透明な、または、着色された注封材料によって注封されている。ここでこの注封材料は、キャビティを少なくとも部分的に満たしている。この注封材料は、ここで、光学的な反射体を形成し、チップ、ボンディングワイヤーおよび変換素子を機械的に保護する。

##### 【0003】

注封材料を、従来のオプトエレクトロニクス素子のキャビティに入れる際の問題は、注封材料によるボンディングワイヤーの確実な被覆を保証し、同時に、注封材料による、オプトエレクトロニクス半導体チップまたは変換素子の上面または他のビーム放射表面の汚染を阻止することである。

##### 【0004】

本発明の課題は、オプトエレクトロニクス素子を提供することである。この課題は、請求項1の特徴部分に記載されている構成を有するオプトエレクトロニクス素子および請求項13の特徴部分に記載されている構成を有するオプトエレクトロニクス素子によって解決される。本発明の別の課題は、オプトエレクトロニクス素子の製造方法を提供することである。この課題は、請求項18の特徴部分に記載された構成を有する方法によって解決される。従属請求項には、種々の発展構成が記載されている。

##### 【0005】

オプトエレクトロニクス素子は、ケーシングを含んでいる。このケーシングは、ケーシングの上面に向かって開放されている第1のキャビティと、ケーシングの上面に向かって開放されている第2のキャビティとを有している。ここで、この第1のキャビティと第2

10

20

30

40

50

のキャビティとは、接続チャネルによって接続されている。第1のキャビティ内には、オプトエレクトロニクス半導体チップが配置されている。第1のキャビティの、このオプトエレクトロニクス半導体チップを包囲している領域には、注封材料が配置されている。

【0006】

有利には、このオプトエレクトロニクス素子のケーシングの第2のキャビティは、注封材料のための貯蔵所を形成する。第1のキャビティ内の注封材料の充填レベルは、注封材料の量に依存して生じる。オプトエレクトロニクス素子のこのケーシングでは、第1のキャビティの容積と第2のキャビティの容積とは、接続チャネルを介して相互に接続されているので、第1のキャビティ内の注封材料の充填レベルは、第1のキャビティと第2のキャビティとによって形成される総容積における注封材料の量に依存する。ケーシングの、第1のキャビティと、第2のキャビティと、第1のキャビティと第2のキャビティとを接続している接続チャネルとの総容積は第1のキャビティ単独の容積よりも大きいので、総容積が第1のキャビティ容積だけのことである場合に比べて、総容積内に入れられる注封材料の量の変化によって生じる第1のキャビティ内の注封材料の充填レベルの変化がより小さくなる。これによって有利には、第1のキャビティ内に入れられている注封材料の量の測定時の誤差が避けられないのにもかかわらず、オプトエレクトロニクス素子のケーシングの第1のキャビティ内の注封材料の充填レベルを、高い精度および再現可能性で設定することができる。

【0007】

オプトエレクトロニクス素子の、第1のキャビティと第2のキャビティとを有するこのケーシングのさらなる利点は、注封材料が第2のキャビティ内に充填され、第2のキャビティから第1のキャビティ内に達することが可能である、ということである。これによって、注封材料の充填の間、オプトエレクトロニクス半導体チップのビーム放射上面、または、オプトエレクトロニクス半導体チップ上に配置されている素子の上面の意図しない、かつ、不所望の汚染を回避することができる。

【0008】

オプトエレクトロニクス素子の実施形態では、接続チャネルは、接続方向に対して垂直に、第1のキャビティと第2のキャビティとの間に、第1のキャビティよりも、かつ、第2のキャビティよりも狭い幅を有している。有利には、第1のキャビティと第2のキャビティはこれとによって、明確に相互に分けられた容積として形成されている。これによって、オプトエレクトロニクス素子のケーシングの第1のキャビティの輪郭を次のように設計することが可能になる。すなわち、第1のキャビティ内に配置されたオプトエレクトロニクス半導体チップが、全面で、幅狭く、かつ、第1のキャビティの壁部からほぼ一定の間隔で画定されるように設計することが可能になる。これによって、有利には、次のこと 30 が保証される。すなわち、全面で、オプトエレクトロニクス半導体チップの隣で、注封材料の表面に形成されるメニスカスが小さくなるということが保証される。これによって有利には、オプトエレクトロニクス半導体チップの確実な組み込みおよび注封材料によるボンディングワイヤーの確実な被覆がサポートされる。第1のキャビティを第2のキャビティと明確に区分することのさらなる利点は、後続の処理ステップにおいて、第2のキャビティを切り離すことができる、ということである。これによって、ケーシングの大きさを 40 低減することができる。

【0009】

オプトエレクトロニクス素子のある実施形態では、第1のキャビティは第1の容積を有し、第2のキャビティは第2の容積を有する。ここで、第2の容積は少なくとも、第1の容積と同じ容積を有する。有利には、この第2のキャビティによって、第1の容積に比べて、第1のキャビティの容積と第2のキャビティの容積とによって形成される総容積を格段に増大させることができる。これによって、オプトエレクトロニクス素子のケーシングの第2のキャビティは、注封材料のための効果の大きい貯蔵所を形成し、注封材料の充填量変動を効果的に補償することができる。

【0010】

10

20

30

40

50

オプトエレクトロニクス素子のある実施形態では、ボンディングワイヤーは、オプトエレクトロニクス半導体チップの電気的なコンタクト面と、ケーシングのボンディング面との間に配置されている。有利には、ボンディングワイヤーはこの場合には、注封材料によって覆われ、これによって、外部の機械的な作用による損傷から保護される。有利には、これは、オプトエレクトロニクス素子の頑強性を高める。

#### 【0011】

オプトエレクトロニクス素子のある実施形態では、ボンディング面は、接続チャネル内に配置されている。有利にはこれによって、オプトエレクトロニクス素子のケーシングの第1のキャビティに、ボンディング面用の空間を取って置く必要がなくなる。これによって、オプトエレクトロニクス素子のケーシングの第1のキャビティの輪郭を次のように形成することが可能になる。すなわち、第1のキャビティ内に配置されているオプトエレクトロニクス半導体チップが、全ての面で、幅狭く、かつ、第1のキャビティの壁部からほぼ均一の間隔で、画定されるように形成することが可能になる。これによって有利には、第1のキャビティ内に配置されている注封材料のメニスカスが、オプトエレクトロニクス半導体チップの全面で、ほぼ同じ大きさで形成される。これは、オプトエレクトロニクス半導体チップの確実な組み込みをサポートし、注封材料によるボンディングワイヤーの確実かつ完全な被覆をサポートする。

#### 【0012】

オプトエレクトロニクス素子のある実施形態では、オプトエレクトロニクス半導体チップは、第1の幾何学的な形状を備えた上面を有する。ここで第1のキャビティは、幾何学的な基本形状を備えた底面を有する。これは、第1の幾何学的な形状から延ばすことによって形成される。さらに、第1のキャビティの底面は、この幾何学的な基本形状に対して付加的に張り出し部を有している。ここで、ボンディング面は、底面に接している張り出し部内に配置されている。有利には、オプトエレクトロニクス半導体チップの上面の第1の幾何学的な形状と、第1のキャビティの底面の幾何学的な基本形状とが相似していることによって、第1のキャビティの壁部は、第1のキャビティ内に配置されているオプトエレクトロニクス半導体チップを、オプトエレクトロニクス半導体チップの全面で、ほぼ同じ間隔で包囲することができる。張り出し部の領域においてのみ、第1のキャビティの形状は、オプトエレクトロニクス半導体チップの形状と相違する。しかし、この張り出し部は、ボンディングワイヤーを収容するためだけに設けられているので、この張り出し部を小さく形成することができる。オプトエレクトロニクス半導体チップ全面で、オプトエレクトロニクス半導体チップの外縁と、第1のキャビティの壁部との間の間隔がほぼ同じであることによって、第1のキャビティ内に配置された注封材料は、オプトエレクトロニクス半導体チップの全面で、ほぼ同じ大きさのメニスカスを形成する。これによって、オプトエレクトロニクス半導体チップの確実な組み込みと、注封材料によるボンディングワイヤーの確実な被覆が保証される。底面に、第1のキャビティの張り出し部内に、ボンディング面を配置することによって、有利には、次のことが可能になる。すなわち、第2のキャビティ、および、要望に応じては、オプトエレクトロニクス素子のケーシングの、第1のキャビティと第2のキャビティとの間の接続チャネルを包囲する部分も切り離すことが可能になる。これによって、オプトエレクトロニクス素子のケーシングの全体的な大きさを低減することができる。

#### 【0013】

オプトエレクトロニクス素子のある実施形態では、第2のキャビティ内に注封材料が配置されている。有利には、ここで、このオプトエレクトロニクス素子のケーシングのこの第2のキャビティは注封材料のための貯蔵所を形成し、これによって、注封材料の充填量変動を補償する。

#### 【0014】

オプトエレクトロニクス素子のある実施形態では、注封材料は、ケーシングの上面に対して垂直な方向で、第1のキャビティと第2のキャビティとにおいて異なる高さを有している。有利にはこれによって次のことが可能になる。すなわち、オプトエレクトロニクス

10

20

30

40

50

素子のケーシングの第2のキャビティによって形成された貯蔵所が、注封材料の充填量変動を補償することが可能になる。ここで、第1のキャビティにおける注封材料の高さは、ほぼ、注封材料の量の変動に依存しない。これによって有利には、オプトエレクトロニクス半導体チップの確実な組み込みと、ボンディングワイヤーの確実な被覆とが保証される。同時に、オプトエレクトロニクス半導体チップの上面の、または、オプトエレクトロニクス半導体チップ上に配置されている素子の上面の、注封材料による汚染も確実に阻止される。

#### 【0015】

オプトエレクトロニクス素子のある実施形態では、第1のキャビティは、周囲を包囲している壁部によって画定されている。この壁部は段階部(Absatz)を有している。ここで、第1のキャビティはこの段階部でケーシングの上面へ向かって幅が広がっている。有利には、段階部を設けることによって、第1のキャビティ内の注封材料の所望の充填レベルを設定することができる。第1のキャビティの壁部と第1のキャビティ内に配置されているオプトエレクトロニクス半導体チップとの間の間隔が十分に小さい場合には、第1のキャビティの壁部は、毛細管現象によって、段階部まで、注封材料によって濡れている。これによって、第1のキャビティ内に配置される注封材料は、場合によって存在する、注封材料の充填量変動に依存せずに、確実に所定の目標値を有することができる。

#### 【0016】

オプトエレクトロニクス素子のある実施形態では、第1のキャビティと第2のキャビティとは、ケーシングの上面に対して垂直な方向において、異なる深さを有している。有利にはこれによって、第2のキャビティの容積は、第1のキャビティの容積と比べて格段される。

#### 【0017】

オプトエレクトロニクス素子のある実施形態では、オプトエレクトロニクス半導体チップは、ビーム放射上面を有している。ここで、このビーム放射上面には、波長変換素子が配置されている。波長変換素子は、次のように構成可能である。すなわち、オプトエレクトロニクス半導体チップによって放射された電磁ビームの波長を変換するように構成可能である。このために、波長変換素子には例えば、発光材料が組み込まれている。

#### 【0018】

オプトエレクトロニクス素子のある実施形態では、波長変換素子の上面と、第1のキャビティの、ケーシングに構成された、第1のキャビティの周囲を包囲する縁部との間に、ケーシングの上面に対して垂直な方向において、 $60\mu\text{m}$ を下回る高さの差が発生する。有利には、これによって、オプトエレクトロニクス半導体チップおよび波長変換素子の、第1のキャビティ内に配置されている注封材料内への確実な組み込みが保証される。ここでは、波長変換素子の上面が、注封材料によって汚染されることはない。

#### 【0019】

オプトエレクトロニクス素子のある実施形態では、オプトエレクトロニクス半導体チップの上面と、ケーシングに構成されている、第1のキャビティの周囲を包囲する縁部との間に、ケーシングの上面に対して垂直な方向において、 $60\mu\text{m}$ を下回る、高さの差が生じる。有利には、これによって、オプトエレクトロニクス素子のケーシングの第1のキャビティへ内に配置されている注封材料内への、オプトエレクトロニクス半導体チップの確実な組み込みが保証される。ここでは、オプトエレクトロニクス半導体チップの上面は、封入材料によって汚染されない。

#### 【0020】

オプトエレクトロニクス素子のある実施形態では、ケーシングは、さらなる、ケーシングの上面に向かって開放されているキャビティを有している。ここで、このさらなるキャビティは、さらなる接続チャネルによって、第1のキャビティまたは第2のキャビティと接続されている。有利には、このさらなるキャビティは、第1のキャビティ内に配置されている注封材料のための、さらなる貯蔵所として用いられ、これによって、第1のキャビティと、第2のキャビティと、さらなるキャビティと、接続チャネルとの総容積をさらに

10

20

30

40

50

増大させることができる。このさらなるキャビティ内には、さらなるオプトエレクトロニクス半導体チップも配置可能である。

#### 【0021】

オプトエレクトロニクス素子のある実施形態では、さらなるキャビティ内に、さらなるオプトエレクトロニクス半導体チップが配置されている。有利には、第1のキャビティとさらなるキャビティに、このオプトエレクトロニクス素子では同時に、注封材料を充填することができる。注封材料は、ここで有利には、オプトエレクトロニクス素子のケーシングの第2のキャビティ内に充填され、接続チャネルおよびさらなる接続チャネルによって、第1のキャビティおよびさらなるキャビティ内に達する。これによって、注封材料の充填の間、オプトエレクトロニクス半導体チップの上面またはオプトエレクトロニクス半導体チップ上に配置されている素子の上面の、注封材料による汚染、および、さらなるオプトエレクトロニクス半導体チップの上面またはこのさらなるオプトエレクトロニクス半導体チップ上に配置されている素子の上面の、注封材料による汚染を阻止することができる。

10

#### 【0022】

オプトエレクトロニクス素子の製造方法は、ケーシングの上面に向かって開放されている第1のキャビティと、ケーシングの上面に向かって開放されている第2のキャビティとを備えたケーシングを提供するステップを有している。ここで、第1のキャビティと第2のキャビティは、接続チャネルによって接続されている。さらにこの方法は、第1のキャビティ内に、オプトエレクトロニクス半導体チップを配置するステップと、第1のキャビティの、オプトエレクトロニクス半導体チップを包囲している領域に注封材料を入れるステップとを有している。有利には、この方法は、第1のキャビティへの、注封材料の充填レベルの確実かつ制限可能な調整を可能にする。第1のキャビティにおける、この方法において実現される、第1のキャビティ内の注封材料の充填レベルは、ここで、有利には、充填材料の充填量の変動に対して許容性を有している。これは次のことによって実現される。すなわち、第2のキャビティと接続チャネルとが、注封材料のための貯蔵所として用いられることによって実現される。第2のキャビティと接続チャネルとによって得られる容積拡大は、注封材料の充填量への、第1のキャビティ内の注封材料の得られる充填レベルの依存性を低減する。これによって、この方法は、有利には、オプトエレクトロニクス半導体チップの確実な組み込みを可能にする。同時に、この方法では、有利には、オプトエレクトロニクス半導体チップの上面またはオプトエレクトロニクス半導体チップの上面に配置された素子の上面の汚染の危険が僅かになる。

20

#### 【0023】

この方法のある実施形態では、注封材料は、第2のキャビティ内に入れられる。ここで、注封材料は、第2のキャビティから、接続チャネルを通って、第1のキャビティに達する。有利には、これによって、注封材料の組み込みの間、オプトエレクトロニクス半導体チップの上面またはオプトエレクトロニクス半導体チップの上面に配置された素子の上面の、注封材料による汚染、例えば、はねによる汚染が阻止される。

30

#### 【0024】

この方法の実施形態では、この方法は、第2のキャビティを含んでいる、ケーシングの部分を切り離すさらなるステップを含んでいる。第2のキャビティを含んでいる、このケーシング部分の分離は、ここで例えば、注封材料の硬化後に行われる。有利には、第2のキャビティを含んでいるケーシング部分を分離することによって、オプトエレクトロニクス素子のケーシングの残りの部分の大きさが低減される。これによって、この方法によって得られるオプトエレクトロニクス素子は、有利なコンパクトな外側寸法を有する。

40

#### 【0025】

本発明の上述した特性、特徴および利点並びに様式は、これが実現されるように、実施例の後続の説明に関連して、より明瞭、かつ、より理解しやすくなる。実施例は、図面に関連してより詳細に説明される。

#### 【図面の簡単な説明】

50

## 【0026】

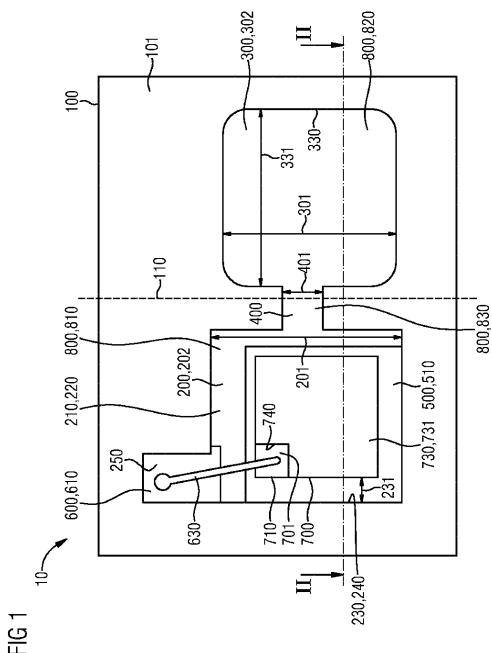

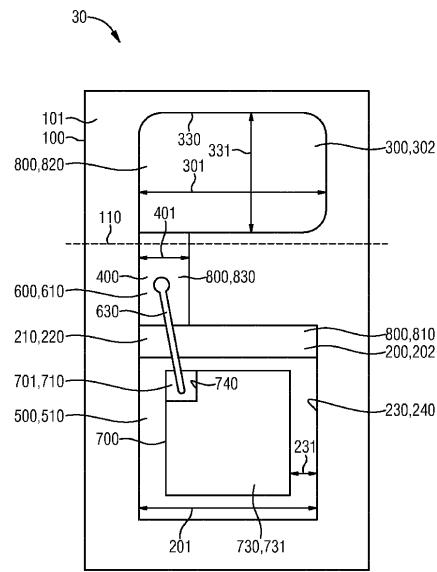

【図1】第1のオプトエレクトロニクス素子の平面図

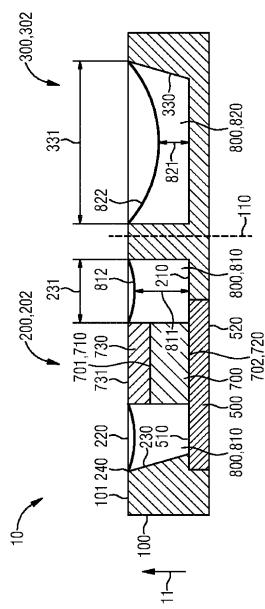

【図2】第1のオプトエレクトロニクス素子の断面図

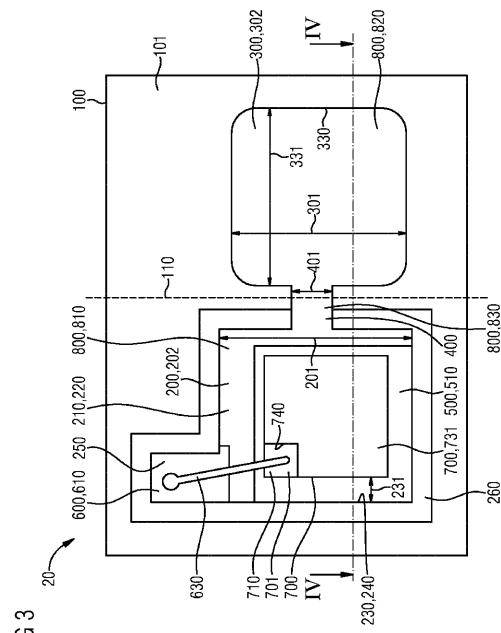

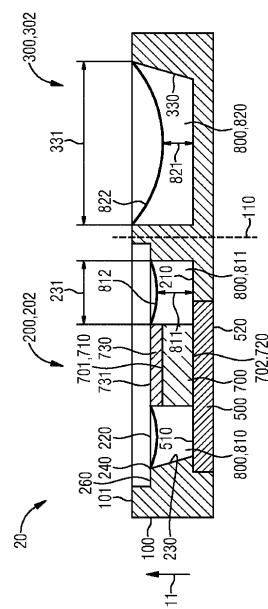

【図3】第2のオプトエレクトロニクス素子の平面図

【図4】第2のオプトエレクトロニクス素子の断面図

【図5】第3のオプトエレクトロニクス素子の平面図

【図6】第4のオプトエレクトロニクス素子の平面図

【図7】第5のオプトエレクトロニクス素子の平面図

【図8】第6のオプトエレクトロニクス素子の平面図

【図9】第7のオプトエレクトロニクス素子の平面図

10

【図10】複数個の第8のオプトエレクトロニクス素子を備えた素子結合体の平面図

【発明を実施するための形態】

## 【0027】

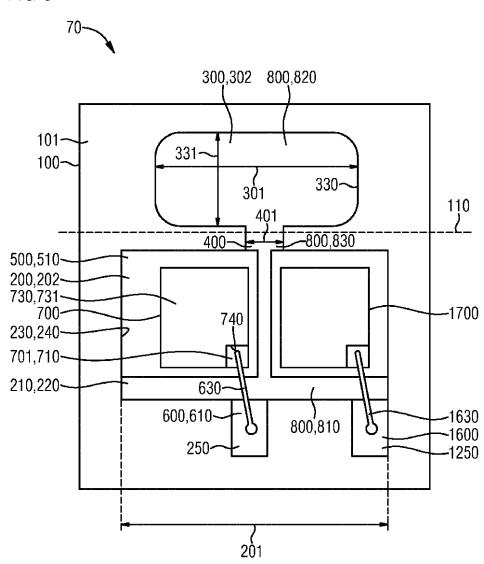

図1は、第1のオプトエレクトロニクス素子10のケーシング100の上面101の平面図を概略的に示している。図2は、第1のオプトエレクトロニクス素子10のケーシング100の、図1に示された切断線I-Iに沿って切断された断面図を示している。第1のオプトエレクトロニクス素子10は例えば、発光ダイオード素子であり得る。

## 【0028】

ケーシング100は、電気的に絶縁性の材料、例えばプラスチック材料を有している。ケーシング100は、例えば射出成形、トランスファ成形または他の成形プロセスによって製造可能である。

20

## 【0029】

第1のオプトエレクトロニクス素子10のケーシング100は、第1のキャビティ200を有している。この第1のキャビティ200は、ケーシング100の上面101に向かって開放されている。従って、第1のキャビティ200は、ケーシング100の上面101から、ケーシング100内へと延在している。ケーシング100の上面101で、第1のキャビティ200は、開放面220を有している。第1のキャビティ200の、ケーシング100内に配置されている底面は、底面210によって形成される。第1のキャビティ200の、底面210と、開放面220との間には、周囲を包囲する壁部230が延在している。この壁部230は、ケーシング100の材料によって形成され、第1のキャビティ200を側方で制限する。開放面220では、周囲を包囲する壁部230は、縁部240を形成する。従ってこの縁部240は、第1のキャビティ200の開放面220を包囲する。

30

## 【0030】

ケーシング100は第1のキャビティ200の隣に、第2のキャビティ300を有している。第2のキャビティ300は、同様に、ケーシング100の上面101に向かって開放されている。従って、第2のキャビティ300も、ケーシング100の上面101からケーシング100内に延在している。第2のキャビティ300は同様に、ケーシング100内に配置された底面を有している。ケーシング100の上面101で、第2のキャビティ300は開放面を有している。第2のキャビティ300の底面と開放面との間には、第2のキャビティ300の周囲を包囲する壁部330が延在している。これは、ケーシング100の材料によって形成されており、第2のキャビティ300を側方で制限する。

40

## 【0031】

第1のオプトエレクトロニクス素子10のケーシング100の第1のキャビティ200と第2のキャビティ300とは、接続チャネル400によって相互に接続されている。接続チャネル400は、同様に、ケーシング100の上面101に向かって開放されている。すなわちこれは、ケーシング100の上面101からケーシング100内へと延在している。

## 【0032】

第1のキャビティ200と第2のキャビティ300との間には、接続チャネル400が

50

、接続方向に沿って延在している。接続方向に対して垂直に、および、ケーシング 100 の上面 101 に対して平行に、接続チャネルは幅 401 を有している。第 1 のキャビティ 200 は、この方向において、幅 201 を有している。第 2 のキャビティ 300 は、同じ方向において、幅 301 を有している。接続チャネル 400 の幅 401 は、第 1 のキャビティ 200 の幅 201 よりも狭く、かつ、第 2 のキャビティ 300 の幅 301 よりも狭い。これは次のことを意味する。すなわち、第 1 のキャビティ 200 と接続チャネル 400 と第 2 のキャビティ 300 のつながっている容積が、接続チャネル 400 から第 1 のキャビティ 200 の方へ、および、第 2 のキャビティ 300 の方へそれぞれ拡張していることを意味している。接続チャネル 400 は、第 1 のキャビティ 200 と第 2 のキャビティ 300 との間に、縮小箇所を形成する。

10

#### 【0033】

第 1 のオプトエレクトロニスク 素子 10 のケーシング 100 の第 1 のキャビティ 200 内には、オプトエレクトロニクス半導体チップ 700 が配置されている。このオプトエレクトロニクス半導体チップ 700 は例えば、発光ダイオードチップ (LEDチップ) であり得る。オプトエレクトロニクス半導体チップ 700 は、電磁ビーム、例えば可視光を放射するように構成されている。オプトエレクトロニクス半導体チップ 700 は、例えば面発光型発光ダイオードチップとして、または、ボリュームエミッタ (volumenemittierender) 型発光ダイオードチップとして形成可能である。

#### 【0034】

オプトエレクトロニクス半導体チップ 700 は、上面 701 と、この上面 701 に対向している下面 702 とを有している。オプトエレクトロニクス半導体チップ 700 は、次のように第 1 のキャビティ 200 内に配置されている。すなわち、オプトエレクトロニクス半導体チップ 700 の下面 702 が、第 1 のキャビティ 200 の底面 210 の方を向いているように配置されている。オプトエレクトロニクス半導体チップ 700 の上面 701 は、ケーシング 100 の上面 101 の第 1 のキャビティ 200 の開放部へ向かって配向されている。

20

#### 【0035】

図 1 および 2 に図示されている例では、オプトエレクトロニクス半導体チップ 700 の上面 701 に波長変換素子 730 が配置されている。この波長変換素子 730 は、オプトエレクトロニクス半導体チップ 700 によって放射された電磁ビームの波長を、変換するために配置されている。このために、波長変換素子 730 は、第 1 の波長を有する電磁ビームを吸収し、第 2 の、典型的により長い波長を有する電磁ビームを放射することができる。波長変換素子 730 は、例えば、埋め込まれた発光材料を含んでいる。埋め込まれた発光材料は、ここで、有機発光材料であっても、無機発光材料であってもよい。埋め込まれた発光材料は量子ドットを有し得る。

30

#### 【0036】

波長変換素子 730 は、上面 731 を有している。この上面は、オプトエレクトロニクス半導体チップ 700 の上面 701 から離反している。これによって、波長変換素子 730 の上面 731 は、オプトエレクトロニクス半導体チップ 700 と波長変換素子 730 によって形成されているオプトエレクトロニクス半導体チップ装置の上面を形成する。しかしこの波長変換素子 730 を省くこともできる。この場合には、オプトエレクトロニクス半導体チップ 700 の上面 701 が、オプトエレクトロニクス半導体チップ装置の上面を形成する。オプトエレクトロニクス半導体チップ 700 の上面 701 または波長変換素子 730 の上面 731 に、他の素子、例えば透明なセラミック (Klar-Keramik)、ガラス、または、透明なキャスティングコンパウンドも配置することができる。この場合には、さらなる素子の上面が、オプトエレクトロニクス半導体チップ装置の上面を形成する。以降では、波長変換素子 730 の上面 731 は、オプトエレクトロニクス半導体チップ装置の上面を表す。

40

#### 【0037】

オプトエレクトロニクス半導体チップ 700 の上面 701 は、幾何学的形状を有する。

50

図示の例では、オプトエレクトロニクス半導体チップ700の上面701は、長方形を有している。しかしオプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的形状を、長方形と異なった形状に形成することができる。ケーシング100の第1のキャビティ200の底面210は、幾何学的な基本形状を有している。これは、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的形状を延ばすことによって形成される。すなわち、底面210の幾何学的な基本形状は、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的な形状に相似している。しかし、底面210の幾何学的な基本形状は、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的な形状よりも大きい。図示の例では、第1のキャビティ200の底面210は、長方形の、幾何学的な基本形状を有している。

10

#### 【0038】

しかし第1のオプトエレクトロニクス素子10ケーシング100の第1のキャビティ200の底面210の形状は、第1のキャビティ200が付加的な張り出し部250を有している、という点において、幾何学的な基本形状とは異なる。張り出し部250の領域において、底面210は、幾何学的な基本形状を超えて延在する。図示の例では、張り出し部250は長方形に形成されており、第1のキャビティ200の底面210の長方形の幾何学的な基本形状の外縁に配置されている。ここで、張り出し部250は、図示の例では、第1のキャビティ200の底面210の長方形の幾何学的な基本形状の角領域に接している。しかし、張り出し部250が、第1のキャビティ200の他の位置に配置されてもよい。張り出し部250は、第1のキャビティ200の残りの寸法と比べて小さい。例えば、張り出し部250の容積は、第1のキャビティ200の総容積の10%よりも小さい。

20

#### 【0039】

有利には、第1のキャビティ200の開放面220も、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的な形状に相似している、幾何学的な基本形状を有している。ここで、第1のキャビティ200の開放領域220も、張り出し部250の領域においてのみ、この幾何学的な基本形状と相違している。

#### 【0040】

第1のオプトエレクトロニクス半導体素子10のケーシング100内には、第1のリードフレーム部分500と、第2のリードフレーム部分600とが埋設されている。第1のリードフレーム部分500と、第2のリードフレーム部分600とは、それぞれ、導電性の材料を有している。これは例えば金属である。第1のリードフレーム部分500と第2のリードフレーム部分600とは、例えば、打ち抜きおよび/またはエッチングによって、共通のワークピースから製造される。第1のリードフレーム500と第2のリードフレーム600とは、相互に間隔が空けられている、かつ、相互に電気的に絶縁されている。

30

#### 【0041】

第1のリードフレーム部分500は、チップ受容面510と、このチップ受容面510に対して対向している第1のはんだ付けコンタクト面520とを有している。第2のリードフレーム部分600は、ボンディング面610と、このボンディング面610に対向している第2のはんだ付けコンタクト面620とを有している。第1のリードフレーム部分500と、第2のリードフレーム部分600とは、次のように、ケーシング100の材料内に埋設されている。すなわち、第1のリードフレーム部分500のチップ受容面510と第1のはんだ付けコンタクト面520、並びに、第2のリードフレーム部分600のボンディング面610と第2のはんだ付けコンタクト面620とが、それぞれ少なくとも部分的に、ケーシング100の材料によって被覆されていないように、埋設されている。第1のリードフレーム部分500の第1のはんだ付けコンタクト面520と、第2のリードフレーム部分600の第2のはんだ付けコンタクト面620とは、ケーシングの上面101に対向している、ケーシング100の背面でアクセス可能である。第1のリードフレーム部分500のチップ受容面510と、第2のリードフレーム部分のボンディング面610は、第1のキャビティ200の底面210でアクセス可能であり、第1のキャビティ2

40

50

00の底面210の一部を形成する。第1のリードフレーム部分500のチップ受容面510は、第1のキャビティ200の底面領域210の、幾何学的な基本形状を形成している部分に配置されている。第2のリードフレーム部分600のボンディング面610は、第1のキャビティ200の底面210の、張り出し部250を形成している部分内に、配置されている。

【0042】

オプトエレクトロニクス半導体チップ700は、自身の上面701で、上方の電気的なコンタクト面710を有している。その下面702で、オプトエレクトロニクス半導体チップ700は、下方の、電気的なコンタクト面720を有している。上方の電気的なコンタクト面710と、下方の電気的なコンタクト面720との間で、電圧が、オプトエレクトロニクス半導体チップ700に印加される。これによって、オプトエレクトロニクス半導体チップ700は、電磁ビームを放射するように促される。

10

【0043】

上方の電気的なコンタクト面710は、オプトエレクトロニクス半導体チップ700の上面701の角領域に配置されている。オプトエレクトロニクス半導体チップ700の上面701上に配置されている波長変換素子730は、オプトエレクトロニクス半導体チップ700の上方の電気的なコンタクト面710の領域において、空白部740を有している。これによって、オプトエレクトロニクス半導体チップ700の、上方の電気的なコンタクト面710は、オプトエレクトロニクス半導体チップ700の上面701に波長変換素子730が配置されているのにもかかわらず、露出されている。

20

【0044】

オプトエレクトロニクス半導体チップ700は、次のように、第1のキャビティ200の底面210に配置されている。すなわち、オプトエレクトロニクス半導体チップ700の下方の電気的なコンタクト面720が、第1のリードフレーム部分500のチップ受容面510に対して導電性接続されているように配置されている。オプトエレクトロニクス半導体チップ700の下面702は、例えば、はんだ付けによって、または、導電性接着剤によって、第1のリードフレーム部分500のチップ受容面510と接続可能である。

【0045】

オプトエレクトロニクス半導体チップ700の上面701での上方の電気的なコンタクト面710と、第2のリードフレーム部分600のボンディング面610との間に、ボンディングワイヤー630が配置されている。ボンディングワイヤー630は、オプトエレクトロニクス半導体チップ700の上方の電気的なコンタクト面710と、第2のリードフレーム部分600のボンディング面610との間に、導電性接続を形成する。ボンディングワイヤー630はここで、第1のキャビティ200内に配置されており、少なくとも部分的に、第1のキャビティ200の張り出し部250内へ延在する。

30

【0046】

第1のリードフレーム部分500の第1のはんだ付けコンタクト面520は、チップ受容面510を介して、オプトエレクトロニクス半導体チップ700の下方の電気的なコンタクト面720と導電性接続されている。第2のリードフレーム部分600の第2のはんだ付けコンタクト面620は、ボンディング面610と、ボンディングワイヤー630とを介して、電気的に、オプトエレクトロニクス半導体チップ700の上方の電気的なコンタクト面710と導電性に接続されている。第1のはんだ付けコンタクト面520と、第2のはんだ付けコンタクト面620とは、外部からアクセス可能な、第1のオプトエレクトロニクス素子10の電気的な接続面を形成する。第1はんだ付けコンタクト面520と、第2のはんだ付けコンタクト面620とは、例えば、表面実装方法に従って、電気的に接觸接続される。第1のオプトエレクトロニクス素子10は、この場合、SMD素子を形成する。例えば、第1のはんだ付けコンタクト面520と、第2のはんだ付けコンタクト面620とは、リフローはんだによって、電気的に接觸接続される。

40

【0047】

オプトエレクトロニクス半導体チップ700を包囲している、第1のオプトエレクトロ

50

ニクス素子 10 のケーシング 100 の第 1 のキャビティ 200 の領域内には、注封材料 800 が入れられている。この注封材料 800 は、ケーシング 100 の第 2 のキャビティ 300 内にも、ケーシング 100 の接続チャネル 400 内にも入れられている。注封材料 800 の第 1 の部分 810 は、第 1 のキャビティ 200 の、オプトエレクトロニクス半導体チップ 700 を包囲している領域に入れられている。注封材料 800 の第 2 の部分 820 は、第 2 のキャビティ 300 内に入れられている。注封材料 800 の第 3 の部分 830 は、接続チャネル 400 内に配置されている。

#### 【 0048 】

注封材料 800 は、例えばシリコーンまたはエポキシ樹脂またはシリコーンとエポキシ樹脂とのハイブリッド材料を含み得る。注封材料 800 は、実質的に、電磁ビームに対して透過性であり、特に、オプトエレクトロニクス半導体チップ 700 および / または波長変換素子 730 を通して放射された電磁ビームに対して透過性である。しかし、注封材料 800 が着色されていてもよい。例えば、注封材料 800 に散乱粒子が埋設されていてもよい。この散乱粒子は例えば、 $TiO_2$  を含み得る。注封材料 800 は、埋設された波長変換発光材料も含み得る。

#### 【 0049 】

注封材料 800 の、オプトエレクトロニクス半導体チップ 700 を包囲する、第 1 のキャビティ 200 の領域内に配置された第 1 の部分 810 は、オプトエレクトロニクス半導体チップ 700 の側面および波長変換素子 730 の側面を、有利にはできるだけ完全に包囲するが、オプトエレクトロニクス半導体チップ 700 を有しているオプトエレクトロニクス半導体チップ装置の上面は覆わない。すなわち、図 1 および 2 に示された例では、注封材料 800 の第 1 の部分 810 は、波長変換素子 730 の上面 731 を覆わない。オプトエレクトロニクス半導体チップ 700 が波長変換素子 730 を有していない場合には、オプトエレクトロニクス半導体チップ 700 の上面 701 は、注封材料 800 によって覆われない。

#### 【 0050 】

ボンディングワイヤー 630 は有利には完全に、注封材料 800 の第 1 の部分 810 内に埋設されており、これによって、外部の機械的な作用による損傷から保護される。

#### 【 0051 】

波長変換素子 730 の上面 731 と、開放面 220 の、ケーシング 100 の上面 101 に形成されている縁部 240 との間で、ケーシング 100 の上面 101 に対して垂直な方向 11 において、有利には、高さの違いは、 $60 \mu m$  よりも低い。これに相応して、波長変換素子 730 が存在しない場合には、オプトエレクトロニクス半導体チップ 700 の上面 701 またはオプトエレクトロニクス半導体チップ 700 の上面 701 の上に配置された、別の素子の上面と、第 1 のキャビティ 200 の縁部 240 との間で、ケーシング 100 の上面 101 に対して垂直な方向において、有利には  $60 \mu m$  を下回る高さの相違が生じるだろう。これによって、次のことが可能になる。すなわち、注封材料 800 の第 1 の部分 810 が、第 1 のキャビティ 200 の、周囲を包囲している壁部 230 、および、オプトエレクトロニクス半導体チップ 700 および波長変換素子 730 の側壁も、実質的に完全に覆うことが可能になる。ここでは、注封材料 800 の第 1 の部分 810 は、波長変換素子 730 の上面 731 に達する。

#### 【 0052 】

オプトエレクトロニクス半導体チップ 700 は有利には、第 1 のキャビティ 200 の、幾何学的な基本形状を有する部分のほぼ中央に配置されている。これによって、波長変換素子 730 の上面の外縁は、ほぼ全ての箇所で、実質的に一定の間隔 231 を、第 1 のキャビティ 200 の、周囲を包囲している壁部 230 の縁部 240 に対して有している。この間隔 231 は、ここで、波長変換素子 730 の上面 731 の外縁と、第 1 のキャビティ 200 の、周囲を囲んでいる壁部 230 の縁部 240 との間のより短い間隔として定められる。接続チャネル 400 の領域と、張り出し部 500 の領域のみにおいては、波長変換素子 730 の上面 731 の外縁と、第 1 のキャビティ 200 の開放面 220 の縁部 240

10

20

30

40

50

とは、ケーシング 100 の上面 101 に対して平行な方向において、さらに、相互に離れている。

【0053】

ケーシング 100 の上面 101 の近傍に配置されている、自身の自由表面で、注封材料 800 は、メニスカスを形成する。このメニスカスの形状は実質的に、注封材料 800 の表面張力によって決まる。引力作用は、ここで、下位の役割のみを果たす。波長変換素子 730 の上面 731 の縁部と、第 1 のキャビティ 200 の周囲を囲んでいる壁部 230 との間には、第 1 のメニスカス 812 が形成される。第 2 のキャビティ 300 内には、対向し合っている、第 2 のキャビティ 300 の周囲を包囲している壁部 330 の部分同士の間に、第 2 のメニスカス 822 が形成される。

10

【0054】

形成されたメニスカス 812、822 の半径は、注封材料 800 のほぼ一定の静水圧によって、ほぼ等しい。しかし、相互に対向する、第 2 のキャビティ 300 の周囲を包囲する壁部 330 の部分は、壁間隔 331 を有している。この壁間隔は、波長変換素子 730 の上面 731 の外縁と、第 1 のキャビティ 200 の周囲を包囲する壁部 230 との間の間隔 231 よりも格段に大きい。ここから、次のことが結果として生じる。すなわち、注封材料 800 の、第 1 のキャビティ 200 内に配置されている第 1 の部分 810 が、第 1 のキャビティ 200 の底面 210 から、注封材料 800 の第 1 の部分 810 の第 1 のメニスカス 812 の最も深い点まで見込まれる第 1 の高さ 811 を有している、ということである。この第 1 の高さは、第 2 のキャビティ 300 の底面から、注封材料 800 の第 2 の部分 820 の第 2 のメニスカス 822 まで見込まれる第 2 の高さ 821 よりも大きい。

20

【0055】

波長変換素子 730 の上面 731 と、第 1 のキャビティ 200 の、周囲を取り囲んでいる壁部 230 との間の間隔は、ケーシング 100 の上面 101 に対して平行な方向において、波長変換素子 730 の周りほぼ全体にわたって短く、第 1 のキャビティ 200 の開放面 220 の縁部 240 の輪郭が、波長変換素子 730 の上面 731 の第 1 の幾何学的な形状に配向されているので、注封材料 800 の、第 1 のキャビティ 200 内に配置されている第 1 の部分 810 は、第 1 の高さ 811 を有している。この第 1 の高さは、オプトエレクトロニクス半導体チップ装置の高さ、および、第 1 のキャビティ 200 の高さと、僅かに異なっている。これによって、次のことが保証される。すなわち、ボンディングワイヤー 630 の、第 1 のキャビティ 200 の、幾何学的な基本形状を有する部分内に延在している部分が完全に、注封材料 800 の、第 1 のキャビティ 200 内に配置されている第 1 の部分 810 によって覆われていることが保証される。

30

【0056】

第 1 のキャビティ 200 の、周囲を取り囲んでいる壁部 230 の、相互に対向している部分同士も、第 1 のキャビティ 200 の張り出し部 250 の領域において、相互に僅かな間隔を有しており、有利には、波長変換素子 730 の上面 731 と、第 1 のキャビティ 200 の、周囲を取り囲んでいる壁部 230 との間の間隔 231 に相当する間隔を有しているので、注封材料 800 の第 1 の部分 810 は、第 1 のキャビティ 200 の張り出し部 250 の領域においても、第 1 の高さ 811 にほぼ同等する高さを有している。これによって、有利には、次のことが保証される。すなわち、ボンディングワイヤー 630 の、張り出し部 250 の領域内に延在する部分も、注封材料 800 によって完全に覆われることが保証される。

40

【0057】

波長変換素子 730 の上面 731 の外縁と、第 1 のキャビティ 200 の、周囲を取り囲んでいる壁部 230 との間の、ケーシング 100 の上面 101 に対して平行な方向における間隔 231、並びに、第 1 のキャビティ 200 の張り出し部 250 の領域における、周囲を取り囲んでいる壁部 230 の相互に対向する部分間の間隔は、有利には  $600 \mu m$  を下回る。ここで、より短い間隔 231 が有利である。特に有利には、間隔 231 は、 $100 \mu m$  から  $300 \mu m$  の間である。

50

## 【0058】

注封材料800は、第1のオプトエレクトロニクス素子10の製造時に、有利には、流体の形で、オプトエレクトロニクス素子10のケーシング100の第2のキャビティ300内に充填され、第2のキャビティから、接続チャネル400を介して、第1のキャビティ200に達する。次に、注封材料800が硬化する。注封材料800を第2のキャビティ300内に充填することによって、有利には、波長変換素子730の上面731が、注封材料800を充填する間、注封材料800の飛沫によって汚染されてしまうリスクが低減される。

## 【0059】

第2のキャビティ300と、僅かな程度ではあるが接続チャネル400も、注封材料800のための貯蔵所として用いられる。これによって、注封材料800の充填量変動が補償される。第1のキャビティ200は、第1の容積202を有している。第2のキャビティ300は、第2の容積302を有している。有利には、第2の容積302は、第1の容積202と類似の大きさを有している、または、第1の容積202よりも大きい。第1のキャビティ200の第1の容積202と、第2のキャビティ300の第2の容積302並びに接続チャネル400の容積とから成る容積全体は大きいので、キャビティ200、300内に充填される注封材料800の充填量の変化は、第1のキャビティ200内の注封材料800の第1の部分810の第1の高さ811を僅かにしか変えない。

## 【0060】

オプトエレクトロニクス半導体チップ700ないしは波長変換素子730と、第1のキャビティ200の、周囲を囲んでいる壁部230との間の間隔231が短いので、接続チャネル400を介して、第2のキャビティ300から第1のキャビティ200に達する注封材料800に毛管力が作用する。この毛管力の結果、第1のキャビティ200に達する、注封材料800の第1の部分810は、オプトエレクトロニクス半導体チップ700および波長変換素子730の側面並びに第1のキャビティ200の、周囲を囲んでいる壁部230を実質的に完全に濡らす。この完全な濡れは、波長変換素子730の上面731と、ケーシング100の上面101との間の僅かな高さの差によってもサポートされる。

## 【0061】

オプトエレクトロニクス半導体チップ700および波長変換素子730並びに、第1のキャビティ200の、周囲を囲んでいる壁部230の側面を完全に被覆することは、許容誤差範囲において、キャビティ200、300および接続チャネル400内に入れられる、注封材料800の充填量に依存しない。注封材料800の充填量の変化は、結果的に、許容誤差範囲において、第2のキャビティ300内に、注封材料800の第2の部分820の第2の高さ821の変化だけを生じさせる。しかしこれは、極めて僅かな程度にしか、第1のキャビティ200内の注封材料800の第1の部分810の第1の高さ811の変化を生じさせない。

## 【0062】

第1のキャビティ200の、周囲を囲んでいる壁部230は、ケーシング100の上面101に対して垂直に配向可能である。この場合には、第1のキャビティ200は、円筒状の形状を有している。しかし、周囲を囲んでいる壁部230が、ケーシング100の上面101と、直角とは異なる角度を成していてもよい。この場合には、第1のキャビティ200は、底面210から開放面220の方へ拡張している、または、底面210から開放面の方へ先細りしている。第1のキャビティ200はこの場合には、円錐台の形状に形成されている。ケーシング100の上面101に対して垂直な、周囲を囲んでいる壁部230の個々の部分と、周囲を囲んでいる壁部230の他の部分とが、ケーシング100の上面101に関して、異なる角度で配置されていてもよい。第2のキャビティ300が、円筒状に、円錐台の形状に、またはその他の形状に形成されていてもよい。

## 【0063】

キャビティ200、300および接続チャネル400内に入れられている注封材料800を硬化した後、ケーシング100の、第2のキャビティ300を含んでいる部分を切り

10

20

30

40

50

離すことができる。これによって、第1のオプトエレクトロニクス素子10のケーシング100の大きさを低減することができる。例えば、ケーシング100は、図1および2に概略的に示された分断面110に沿って切り分けられる。ここでこの分断面110は、第1のキャビティ200と第2のキャビティ300との間の接続チャネル400を通って延在する。ケーシング100の、第2のキャビティ300を含んでいる部分は、注封材料800の硬化後、もはや不必要である。

#### 【0064】

次に図3から10に基づいて、別のオプトエレクトロニクス素子を説明する。これらの別のオプトエレクトロニクス素子は、それぞれ、図1および2の第1のオプトエレクトロニクス素子10とほぼ一致している。第1のオプトエレクトロニクス素子10では存在しているコンポーネントに対応している、別のオプトエレクトロニクス素子のコンポーネントには、図3から10において、図1および2においても使用されている参照符号が付けられており、以下で、新たに説明されない。以下では、第1のオプトエレクトロニクス素子10と、これらの別のオプトエレクトロニクス素子との間の違いだけを示す。

10

#### 【0065】

図3は、第2のオプトエレクトロニクス素子20の概略的な平面図を示す。図4は、第2のオプトエレクトロニクス素子20の、図3に示された切断線I-V - I-Vで切断された、概略的な断面図を示している。

#### 【0066】

第2のオプトエレクトロニクス素子20は、第1のオプトエレクトロニクス素子10とは、次の点において異なっている。すなわち、第2のオプトエレクトロニクス素子20のケーシング100の第1のキャビティ200の、周囲を包囲している壁部230が、段階部260を有している、という点において異なっている。この段階部で、第1のキャビティ200は、ケーシング100の上面101に向かって広がっている。ここで、第1のキャビティ200の高さは、ケーシング100の上面101に対して垂直な方向11において、底面210と段階部260との間で、オプトエレクトロニクス半導体チップの高さに合うように調整されている。すなわち、波長変換素子730の上面731と、段階部260との間には、垂直方向11で、有利には、60 μmを下回る高さの差が生じる。

20

#### 【0067】

第1のキャビティ200内に配置されている、注封材料800の第1の部分810は、第1のキャビティ200の底面210から、第1のキャビティ200の、周囲を囲んでいる壁部230における段階部260の高さまで延在しており、ここで、オプトエレクトロニクス半導体チップ700および波長変換素子730の外面を覆っている。周囲を囲んでいる壁部230も、段階部260の高さまで有利には実質的に覆っている。

30

#### 【0068】

第2のオプトエレクトロニクス素子20のケーシング100の第2のキャビティ300の、周囲を囲んでいる壁部330は、段階部を有していない。これによって、第1のオプトエレクトロニクス素子10と比べて、第2のオプトエレクトロニクス素子20では、第2のキャビティ300の第2の容積302は、第1のキャビティ200の第1の容積202に対してさらに増大される。すなわち第2のオプトエレクトロニクス素子20の場合には、第2のキャビティ300は、第1のキャビティ200と比べて、より多くの量の注封材料800を受容することができ、これによって、注封材料800のための、より効果的な貯蔵所を形成することができる。これによって、第2のオプトエレクトロニクス素子の場合には、第1のオプトエレクトロニクス素子10の場合よりも多くの注封材料800の充填量変動を補償することができる。

40

#### 【0069】

第1のオプトエレクトロニクス素子10の図示されていない、さらなる変形では、次のことによって、第2のキャビティ300の容積は、第1のキャビティ200の容積に比べて増大される。すなわち、第2のキャビティ300が、第1のキャビティ200よりも深く形成されることによってである。ケーシング100の上面101に対して垂直な方向1

50

1では、第2のキャビティ300の底面は、第1のキャビティの底面210よりも、低く配置可能である。

【0070】

図5は、第3のオプトエレクトロニクス素子30の概略的な平面図を示している。第3のオプトエレクトロニクス素子30では、ケーシング100の第1のキャビティ200は、張り出し部250を有していない。これによって、第1のキャビティ200の底面210の形状は、第3のオプトエレクトロニクス素子30の場合には、完全に、幾何学的な基本形状に相当する。これは、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的な形状を延ばすことによって形成される。これによって、第1のキャビティ200の開放面220の縁部240の輪郭は、第3のオプトエレクトロニクス素子30の場合には、波長変換素子730の上面731の縁部に、有利には、特に高い精度で追従する。

【0071】

第2のリードフレーム部分600のボンディング面610は、第3のオプトエレクトロニクス素子30の場合には、接続チャネル400の領域に配置されている。ボンディングワイヤー630は、オプトエレクトロニクス半導体チップ700の上方の電気的なコンタクト面710から、第2のリードフレーム部分600のボンディング面610に向かって延在しており、ここで、部分的には第1のキャビティ200内に延在しており、部分的には接続チャネル400内に延在している。

【0072】

オプトエレクトロニクス半導体チップ装置の輪郭が、第1のキャビティ200の、周囲を囲んでいる壁部230およびここから生じる、注封材料800の、第1のキャビティ200内に配置されている第1の部分810の、高い第1の高さ811によって、狭く囲まれていることによって、ボンディングワイヤー630の、第1のキャビティ200内に延在する部分は、完全に、注封材料800によって覆われている。有利には、波長変換素子730の縁部と、第1のキャビティ200の周囲を囲んでいる壁部230との間の間隔231にほぼ相当する接続チャネル400の幅401が狭いことによって、接続チャネル400の領域においても、注封材料800の高い充填レベルが得られる。これによって、ボンディングワイヤー630の、接続チャネル400内に延在する部分も、完全に、注封材料800によって覆われ、これによって、外部の機械的な作用による損傷から保護される。

【0073】

第3のオプトエレクトロニクス素子30の場合にも、注封材料800の硬化の後に、ケーシング100の、第2のキャビティ300を包囲している部分を切り離すことができる。これは例えば、図5に概略的に示された分断面100に沿って行われる。

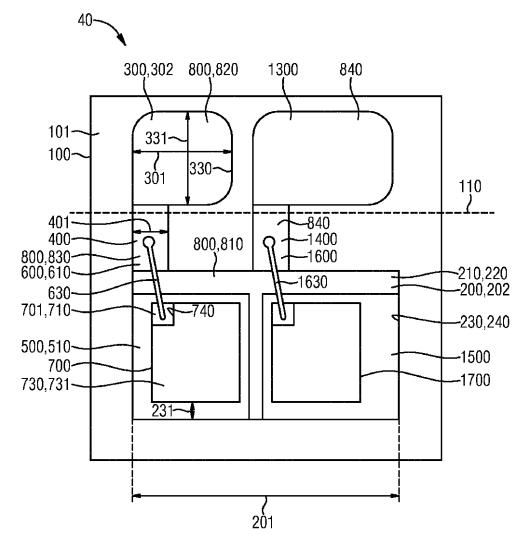

【0074】

図6は、第4のオプトエレクトロニクス素子40の概略的な平面図を示している。第4のオプトエレクトロニクス素子40の場合には、ケーシング100は、第1のキャビティ200と第2キャビティ300との他に、さらに別の第2のキャビティ1300を有している。この別の第2のキャビティ1300は、第2の接続チャネル1400を介して、第1のキャビティ200と接続されている。

【0075】

第4のオプトエレクトロニクス素子40の場合には、第1のキャビティ200内に、オプトエレクトロニクス半導体チップ700の他に、別のオプトエレクトロニクス半導体チップ1700が配置されている。この別のオプトエレクトロニクス半導体チップ1700は、オプトエレクトロニクス半導体チップ700のように構成可能であり、その上面に、波長変換素子または他の素子も有し得る。その波長が、オプトエレクトロニクス半導体チップ700によって放射された電磁ビームの波長に相当する電磁ビームを放射するように、この別のオプトエレクトロニクス半導体チップ1700を構成することができる。しかし、別のオプトエレクトロニクス半導体チップ1700を、異なる波長を有する電磁ビーム

ムを放射するように設けることもできる。

【0076】

第4のオプトエレクトロニクス素子40のケーシング100の第1のキャビティ200は、張り出し部250を有していない。

【0077】

第4のオプトエレクトロニクス素子40のケーシング100内には、第1のリードフレーム部分500と、第2のリードフレーム部分600の他に、別の第1のリードフレーム部分1500と、別の第2のリードフレーム部分1600が埋設されている。この別の第1のリードフレーム部分1500は、別のチップ受容面と、別の第1のはんだ付けコンタクト面とを有している。この別の第2のリードフレーム部分1600は、別のボンディング面と、別の第2のはんだ付けコンタクト面とを有している。第1のリードフレーム部分500のチップ受容面510と、別の第1のリードフレーム部分1500の別のチップ受容面は、第1のキャビティ200の底面210の領域に配置されている。第2のリードフレーム部分600のボンディング面610は、接続チャネル400の領域内に配置されている。別の第2のリードフレーム部分1600の別のボンディング面は、別の接続チャネル1400の領域内に配置されている。10

【0078】

第1のオプトエレクトロニクス半導体チップ700は、第1のリードフレーム部分500のチップ受容面510上に配置されており、ボンディングワイヤー630によって、第2のリードフレーム部分600のボンディング面610と接続されている。ボンディングワイヤー630はここで、部分的に第1のキャビティ200を通って、かつ、部分的に接続チャネル400を通って延在している。別のオプトエレクトロニクス半導体チップ1700は、別の第1のリードフレーム部分1500の別のチップ受容面に配置されており、別のボンディングワイヤー1630を用いて、別の第2のリードフレーム部分1600の別のボンディング面と接続されている。別のボンディングワイヤー1630は、ここで、部分的に第1のキャビティ200を通って延在し、かつ、部分的に別の接続チャネル1400を通って延在していり。20

【0079】

第1のリードフレーム部分500と、別の第1のリードフレーム部分1500とを一体で、共通の第1のリードフレーム部分として形成することも可能である。択一的に、または、付加的に、第2のリードフレーム部分600と別の第2のリードフレーム部分1600とを、これに相応して、一体的に、共通の第2のリードフレーム部分として形成することができる。この場合には、オプトエレクトロニクス半導体チップ700と別のオプトエレクトロニクス半導体チップ1700とは、共通の第1のリードフレーム部分と、共通の第2のリードフレームとの間で、電気的に並列接続されている。これに対して、第1のリードフレーム部分500、1500、および/または、第2のリードフレーム部分600、1600が別個に形成されている場合には、オプトエレクトロニクス半導体チップ700および別のオプトエレクトロニクス半導体チップ1700は、第1のはんだ付けコンタクト面、別の第1のはんだ付けコンタクト面、第2のはんだ付けコンタクト面および別の第2のはんだ付けコンタクト面を介して、別個に駆動制御される。30

【0080】

第4のオプトエレクトロニクス素子40のケーシング100では、注封材料800は、第2のキャビティおよび/または別の第2のキャビティ1300を介して充填され、接続チャネルおよび別の接続チャネル1400を介して、第1のキャビティ200内に、および、場合によっては、第2のキャビティ300または別の第2のキャビティ1300内に達する。ここで、注封材料800の別の部分840は、この別の第2のキャビティ1300内に残る。

【0081】

注封材料800を硬化した後、ケーシング100の、第2のキャビティ300と、別の第2のキャビティ1300とを含んでいる部分が分断される。これは例えば、図6に示さ4050

れた分断面 110 に沿って行われる。

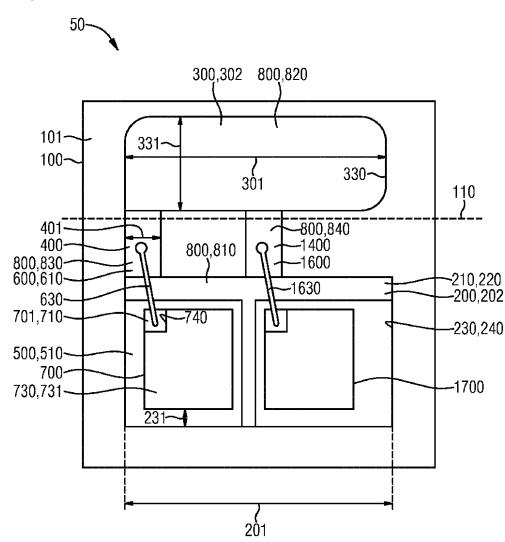

【0082】

図7は、第5のオプトエレクトロニクス素子50の概略的な平面図を示している。この第5のオプトエレクトロニクス素子50は、図6の第4のオプトエレクトロニクス素子40とほぼ一致している。しかし、第5のオプトエレクトロニクス素子50では、別の第2のキャビティ1300は存在していない。このため、第1のキャビティ200は、第5のオプトエレクトロニクス素子50では、接続チャネル400を介してのみ、第2のキャビティ300と接続されているのではなく、付加的に、別の接続チャネル1400も介して接続される。

【0083】

接続チャネル400は、第5のオプトエレクトロニクス素子50の場合には、ボンディングワイヤー630の一部を収容するために用いられる。別の接続チャネル1400は、第5のオプトエレクトロニクス素子50の場合には、別のボンディングワイヤー1630の一部を収容するために用いられる。

【0084】

注封材料800は、第5のオプトエレクトロニクス素子50のケーシング100の場合には、第2のキャビティ300内に充填され、そこから、接続チャネル400と別の接続チャネル1400とを介して、第1のキャビティ200に達する。接続チャネル400内では、接続チャネル400内に残っている注封材料800が、ボンディングワイヤー630の、接続チャネル400内に配置されている部分を覆う。別の接続チャネル1400においては、別の接続チャネル1400内に残っている注封材料800は、別のボンディングワイヤー1630の、別の接続チャネル1400内に配置されている部分を覆う。

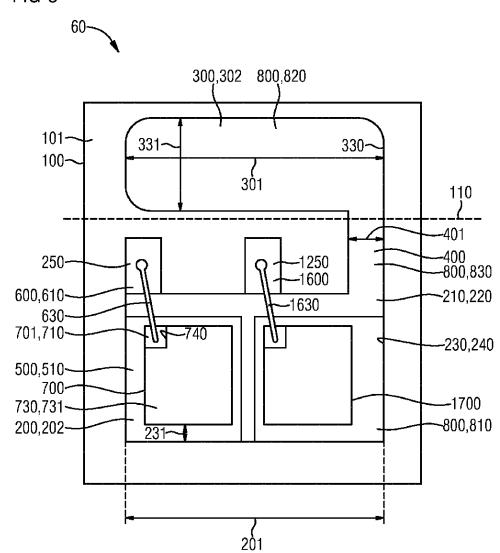

【0085】

図8は、第6のオプトエレクトロニクス素子60の概略的な平面図を示している。第6のオプトエレクトロニクス素子60のケーシング100では、第1のキャビティ200は、接続チャネル400を介して、第2のキャビティ300と接続されている。第1のキャビティ200は、張り出し部250に加えて、別の張り出し部1250を有している。従って、第6のオプトエレクトロニクス素子60では、底面210の形状は、オプトエレクトロニクス半導体チップ700の上面701の第1の幾何学的な形状を延ばすことによって得られる幾何学的な基本形状と、張り出し部250の領域においても、別の張り出し部1250の領域においても、異なっている。

【0086】

第6のオプトエレクトロニクス素子60は、同様に、第1のリードフレーム部分500と第2のリードフレーム部分600の他に、別の第1のリードフレーム部分1500と別の第2のリードフレーム部分1600とを有している。この別の第1のリードフレーム部分1500は、第1のリードフレーム部分500と同様に、第1のキャビティ200の幾何学的な基本形状の領域内に配置されている。第2のリードフレーム部分600は、第1のキャビティ200の張り出し部250の領域内に配置されている。別の第2のリードフレーム部分1600は、別の張り出し部1250の領域内に配置されている。オプトエレクトロニクス半導体チップ700は、第1のリードフレーム部分500のチップ受容面510上に配置されており、ボンディングワイヤー630を用いて、第2のリードフレーム部分600のボンディング面610と接続されている。別のオプトエレクトロニクス半導体チップ1700は、別の第1のリードフレーム部分1500のチップ受容面上に配置されており、別のボンディングワイヤー1630を用いて、別の第2のリードフレーム部分1600のボンディング面と接続されている。

【0087】

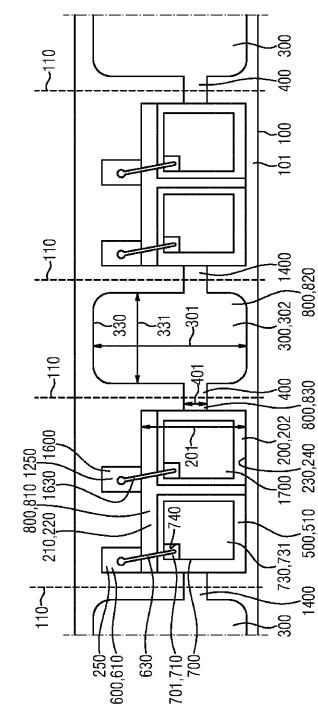

図9は、第7のオプトエレクトロニクス素子70の概略的な平面図を示している。第7のオプトエレクトロニクス素子70は実質的に、第6のオプトエレクトロニクス素子60に相当する。しかし、張り出し部250と別の張り出し部1250は、第7のオプトエレクトロニクス素子70では、第1のキャビティ200の、第2のキャビティ300とは反

10

20

30

40

50

対側の面に配置されている。また、張り出し部 250 と、別の張り出し部 1250 は、図 8 の第 6 のオプトエレクトロニクス素子 60 では、第 1 のキャビティ 200 の、第 2 のキャビティ 300 とは反対側の面に配置されている。図 9 に示された装置は、次のことをする。すなわち、第 1 のキャビティ 200 と第 2 のキャビティ 300 との間の接続チャネル 400 を、図 9 の第 7 のオプトエレクトロニクス素子 70 の場合に、図 8 の第 6 のオプトエレクトロニクス素子 60 の場合よりも短く形成することを可能にする。

#### 【0088】

図 10 は、第 8 オプトエレクトロニクス素子 80 を有している素子結合体 85 の概略的な平面図を示している。素子結合体 85 の第 8 のオプトエレクトロニクス素子 80 は、共通の作業ステップにおいて製造され、図 10 に示された、時間的に続く作業ステップにおいて、分断面 110 に沿って切り分けられる。

10

#### 【0089】

複数の第 8 のオプトエレクトロニクス素子 80 の各々では、第 1 のキャビティ 200 は、張り出し部 250 と、別の張り出し部 1250 を有している。ここで第 1 のキャビティ 200 は、接続チャネル 400 を介して、第 2 のキャビティ 300 と接続されている。第 1 のキャビティ 200 には、オプトエレクトロニクス半導体チップ 700 の他に、さらに、別のオプトエレクトロニクス半導体チップ 1700 が配置されている。この点では、第 8 のオプトエレクトロニクス素子 80 は、図 8 の第 6 のオプトエレクトロニクス素子 60 および図 9 の第 7 のオプトエレクトロニクス素子 70 に相当する。

#### 【0090】

20

しかし、付加的に、素子結合体 85 では、各第 8 のオプトエレクトロニクス素子 80 の第 2 のキャビティ 300 は、別の接続チャネル 1400 を介して、各隣接する第 8 のオプトエレクトロニクス素子 80 の第 1 のキャビティ 200 と接続されている。素子結合体 85 の第 8 のオプトエレクトロニクス素子 80 の製造の間、注封材料 800 は、第 8 のオプトエレクトロニクス素子 80 の第 2 のキャビティ 300 内に充填され、接続チャネル 400 を介して、同じ、第 8 のオプトエレクトロニクス素子 80 それぞれの第 1 のキャビティ 200 内に達し、別の接続チャネル 1400 を介して、各隣接する第 8 のオプトエレクトロニクス素子 80 の第 1 のキャビティ 200 内に達する。素子結合体 85 の全ての第 8 のオプトエレクトロニクス素子 80 の第 1 のキャビティ 200 と第 2 のキャビティ 300 の大きい、つながっている容積によって、入れられる注封材料 800 の充填量変動に対する、さらに格段に大きいトレランスが得られる。

30

#### 【0091】

注封材料 800 を硬化した後、素子結合体 85 の第 8 のオプトエレクトロニクス素子 80 が相互に分けられる。さらに、第 8 のオプトエレクトロニクス素子 80 のケーシング 100 の、第 2 のキャビティ 300 を含んでいる部分それが分断される。

#### 【0092】

40

図 1 ~ 9 の、オプトエレクトロニクス素子 10、20、30、40、50、60、70 も、図 10 に相応して、素子結合体として製造可能である。オプトエレクトロニクス素子 10、20、30、40、50、60、70、80 の残りの特徴も、任意に相互に組み合わせ可能である。

#### 【0093】

本発明を、有利な実施例に基づいて詳細に記載および説明したが、本発明は、開示された例に制限されない。むしろ、本発明の保護範囲を逸脱することなく、ここから、別の形態が当業者によって導出可能である。

#### 【符号の説明】

#### 【0094】

10 第 1 のオプトエレクトロニクス素子、 11 垂直方向、 20 第 2 のオプトエレクトロニクス素子、 30 第 3 のオプトエレクトロニクス素子、 40 第 4 のオプトエレクトロニクス素子、 50 第 5 のオプトエレクトロニクス素子、 60 第 6 のオプトエレクトロニクス素子、 70 第 7 のオプトエレクトロニクス素子、 80

50

第8のオプトエレクトロニクス素子、85 素子結合体、100 ケーシング、101 上面、110 分断面、200 第1のキャビティ、201 幅、202 第1の容積、210 底面、220 開放面、230 周囲を包囲している壁部、231 間隔、240 縁部、250 張り出し部、260 段階部、300 第2のキャビティ、301 幅、302 第2の容積、330 周囲を包囲している壁部、331 壁間隔、400 接続チャネル、401 幅、500 第1のリードフレーム部分、510 チップ受容面、520 第1のはんだ付けコンタクト面、600 第2のリードフレーム部分、610 ボンディング面、620 第2のはんだ付けコンタクト面、630 ボンディングワイヤー、700 オプトエレクトロニクス半導体チップ、701 上面、702 下面、710 上方の電気的なコンタクト面、720 下方の電気的なコンタクト面、730 波長変換素子、731 上面、740 空白部、800 注封材料、810 第1の部分、811 第1の高さ、812 第1のメニスカス、820 第2の部分、821 第2の高さ、822 第2のメニスカス、830 第3の部分、840 別の部分、1250 別の張り出し部、1300 別の第2のキャビティ、1400 別の接続チャネル、1500 別の第1のリードフレーム部分、1600 別の第2のリードフレーム部分、1630 別のボンディングワイヤー、1700 別のオプトエレクトロニクス半導体チップ

【図1】

FIG 1

【図2】

FIG 2

【 义 3 】

FIG 3

【 図 4 】

FIG 4

【 図 5 】

FIG 5

【図6】

FIG 6

【図7】

FIG 7

【 四 8 】

FIG 8

【 図 9 】

FIG 9

【 図 1 0 】

FIG 10

---

フロントページの続き

(74)代理人 100099483

弁理士 久野 琢也

(72)発明者 ユルゲン ホルツ

ドイツ連邦共和国 ヴェンツェンバッハ ブーヘンヴェーク 9

(72)発明者 ミヒヤエル ツィツルスペルガー

ドイツ連邦共和国 レーゲンスブルク シャッテンホーファーガッセ 4

審査官 村井 友和

(56)参考文献 特開平07-038154 (JP, A)

国際公開第2013/001687 (WO, A1)

特表2011-511445 (JP, A)

特開2011-040762 (JP, A)

欧州特許出願公開第2234165 (EP, A2)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64