(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5481477号

(P5481477)

(45) 発行日 平成26年4月23日(2014.4.23)

(24) 登録日 平成26年2月21日(2014.2.21)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 16/02 | (2006.01) | G 11 C 17/00 | 6 1 2 F |

| G 11 C 16/04 | (2006.01) | G 11 C 17/00 | 6 2 2 E |

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 6 4 1   |

G 11 C 17/00 6 3 3 E

請求項の数 13 (全 33 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2011-516811 (P2011-516811)  |

| (86) (22) 出願日 | 平成21年6月30日 (2009.6.30)        |

| (65) 公表番号     | 特表2011-527069 (P2011-527069A) |

| (43) 公表日      | 平成23年10月20日 (2011.10.20)      |

| (86) 国際出願番号   | PCT/US2009/049238             |

| (87) 国際公開番号   | W02010/002879                 |

| (87) 国際公開日    | 平成22年1月7日 (2010.1.7)          |

| 審査請求日         | 平成24年4月3日 (2012.4.3)          |

| (31) 優先権主張番号  | 12/167,128                    |

| (32) 優先日      | 平成20年7月2日 (2008.7.2)          |

| (33) 優先権主張国   | 米国(US)                        |

(73) 特許権者 511242535

サンディスク テクノロジーズ インコーポレイテッド

Sandisk Technologies, Inc.

アメリカ合衆国 75024、テキサス州

、ブラー、ノース ダラス パークウェイ 6900 ツー レガシー タウン

センター

Two Legacy Town Center, 6900 North Dallas Parkway, Plano,

Texas 75024 United States of America

最終頁に続く

(54) 【発明の名称】不揮発性記憶装置のオーバープログラムの訂正

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の不揮発性記憶素子をプログラムするステップと、

オーバープログラムされた前記複数の不揮発性記憶素子の部分集合を特定するステップと、

オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された部分集合に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧するステップと、消去許可電圧を前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に印加するステップとによって、前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に対して、1つまたは複数の消去処理を選択的に実行するステップと、

を備え、

前記チャネル領域の第1の集合および前記チャネル領域の第2の集合は共通基板領域の一部であり、

前記昇圧するステップは、

昇圧許可電圧を前記複数の不揮発性記憶素子の特定された部分集合に関するビットラインに印加するステップ、および、昇圧無効電圧を前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に関するビットラインに印加するステップと、

10

20

前記複数の不揮発性記憶素子の特定された部分集合に関する前記ビットラインおよび前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に関する前記ビットラインが前記非選択ワードラインに結合するように、前記共通基板領域を充電するとともに電圧信号を前記複数の非選択ワードラインに印加するステップと、

電圧信号を前記非選択ワードラインに印加する前記ステップの後に、前記チャネル領域の第1の集合を昇圧するために、前記電圧信号を超えるオーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、を備える、不揮発性記憶装置の動作方法。

#### 【請求項2】

前記チャネル領域の第1の集合および前記チャネル領域の第2の集合の前記チャネル領域は、異なるNANDストリングに関連しており、10

前記昇圧するステップは、前記NANDストリングに接続されているワードラインに印加されている電圧信号に少なくとも部分的に基づいている、

請求項1に記載の方法。

#### 【請求項3】

前記複数の不揮発性記憶素子の特定された部分集合は、NANDストリングの第1の集合に含まれる異なるNANDストリングに属しており、

前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子は、NANDストリングの第2の集合に含まれる異なるNANDストリングに属しており、20

前記NANDストリングの第1の集合および前記NANDストリングの第2の集合は、ワードラインの共通の集合に接続されており、

前記ワードラインの共通の集合は、1本の選択ワードラインと複数の非選択ワードラインを含んでおり、

前記複数の不揮発性記憶素子の特定された部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子は、前記選択ワードラインに接続されており、

前記NANDストリングの第1の集合および前記NANDストリングの第2の集合は、別個のビットラインに接続されている、

請求項1または2に記載の方法。

#### 【請求項4】

前記昇圧するステップは、30

昇圧許可電圧を前記NANDストリングの第1の集合に関するビットラインに印加するステップと、

昇圧無効電圧を前記NANDストリングの第2の集合に関するビットラインに印加するステップと、

オーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、を備え、

前記消去許可電圧を印加するステップは、前記選択ワードラインに負電圧を印加するステップを備え、

前記昇圧するステップは、前記NANDストリングの第1の集合の選択ゲートを遮断するステップをさらに備える、40

請求項3に記載の方法。

#### 【請求項5】

前記昇圧するステップは、

昇圧許可電圧を前記NANDストリングの第1の集合に関するビットラインに印加するステップ、および、昇圧無効電圧を前記NANDストリングの第2の集合に関するビットラインに印加するステップと、

前記NANDストリングの第1の集合に関する前記ビットラインおよび前記NANDストリングの第2の集合に関する前記ビットラインが前記非選択ワードラインに結合して電圧が上昇するように、前記共通基板領域を充電するとともに電圧信号を前記複数の非選択

ワードラインに印加するステップと、

電圧信号を前記非選択ワードラインに印加する前記ステップの後に、前記チャネル領域の第1の集合を昇圧するために、前記電圧信号を超えるオーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、

を備える請求項3に記載の方法。

#### 【請求項6】

前記複数の不揮発性記憶素子は、共通ワードラインに接続されている、請求項1ないし5の何れか1項に記載の方法。

#### 【請求項7】

前記複数の不揮発性記憶素子は、第1型の複数のコントロールラインの共通コントロールラインに接続されており、10

オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された一部に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧する前記ステップは、前記昇圧するステップを確立するために、前記第1型の複数のコントロールラインのうちの他の複数のコントロールラインに複数の信号を印加するステップを含んでおり、

前記1つまたは複数の消去処理を実行するステップは、

前記他の複数のコントロールラインに対してより高い大きさの前記複数の信号を用いて、前記昇圧するステップを繰り返すステップを備える、20

請求項1ないし5の何れか1項に記載の方法。

#### 【請求項8】

前記1つまたは複数の消去処理を実行するステップは、

前記昇圧するステップを前記繰り返すステップに先立って、前記チャネル領域の第1の集合に含まれる一部のチャネル領域をさらなる昇圧から除外するステップを備える、請求項7に記載の方法。25

#### 【請求項9】

前記複数の不揮発性記憶素子は、NANDフラッシュメモリデバイスである、請求項1に記載の方法。30

#### 【請求項10】

共通基板領域上の複数の不揮発性記憶素子と、

前記複数の不揮発性記憶素子と通信する1つまたは複数の管理回路と、を備え、

前記1つまたは複数の管理回路は、前記複数の不揮発性メモリ素子をプログラムするとともに、前記複数の不揮発性記憶素子からオーバープログラムされた部分集合を特定し、35

前記1つまたは複数の管理回路は、前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に、1つまたは複数の消去処理を選択的に実行し、

前記1つまたは複数の消去処理は、

オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された部分集合に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧するステップと、40

消去許可電圧を前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に印加するステップと、を備え、

前記チャネル領域の第1の集合および前記チャネル領域の第2の集合は、前記共通基板領域の一部であり、

前記1つまたは複数の管理回路は、

昇圧許可電圧を前記複数の不揮発性記憶素子の特定された部分集合に関するビットラインに印加するステップ、および、昇圧無効電圧を前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に関するビットラインに印加するステップと、50

前記複数の不揮発性記憶素子の特定された部分集合に関する前記ビットラインおよび前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に関する前記ビットラインが前記非選択ワードラインに結合するように、前記共通基板領域を充電するとともに電圧信号を前記複数の非選択ワードラインに印加するステップと、

電圧信号を前記非選択ワードラインに印加する前記ステップの後に、前記チャネル領域の第1の集合を昇圧するために、前記電圧信号を超えるオーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、によって、前記昇圧するステップを行う、不揮発性記憶装置。

#### 【請求項 1 1】

前記複数の不揮発性記憶素子の特定された部分集合は、NANDストリングの第1の集合に含まれる異なるNANDストリングに属しており、10

前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子は、NANDストリングの第2の集合に含まれる異なるNANDストリングに属しており、

前記NANDストリングの第1の集合および前記NANDストリングの第2の集合は、ワードラインの共通の集合に接続されており、

前記ワードラインの共通の集合は、1本の選択ワードラインと複数の非選択ワードラインを含んでおり、

前記複数の不揮発性記憶素子の特定された部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子は、前記選択ワードラインに接続されており、20

前記NANDストリングの第1の集合および前記NANDストリングの第2の集合は、別個のビットラインに接続されている、

請求項1 0に記載の不揮発性記憶装置。

#### 【請求項 1 2】

前記昇圧するステップは、

昇圧許可電圧を前記NANDストリングの第1の集合に関するビットラインに印加するステップと、

昇圧無効電圧を前記NANDストリングの第2の集合に関するビットラインに印加するステップと、

オーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、を備え30

、

前記消去許可電圧を印加するステップは、前記選択ワードラインに負電圧を印加するステップを備え、

前記昇圧するステップは、前記NANDストリングの第1の集合の選択ゲートを遮断するステップをさらに備える、

請求項1 1に記載の不揮発性記憶装置。

#### 【請求項 1 3】

前記1つまたは複数の管理回路は、

昇圧許可電圧を前記NANDストリングの第1の集合に関するビットラインに印加するステップ、および、昇圧無効電圧を前記NANDストリングの第2の集合に関するビットラインに印加するステップと、40

前記NANDストリングの第1の集合に関する前記ビットラインおよび前記NANDストリングの第2の集合に関する前記ビットラインが前記非選択ワードラインに結合して電圧が上昇するように、前記共通基板領域を充電するとともに電圧信号を前記複数の非選択ワードラインに印加するステップと、

電圧信号を前記非選択ワードラインに印加する前記ステップの後に、前記チャネル領域の第1の集合を昇圧するために、前記電圧信号を超えるオーバードライブ信号を前記複数の非選択ワードラインに印加するステップと、

によって、前記昇圧するステップを行う、請求項1 1に記載の不揮発性記憶装置。

#### 【発明の詳細な説明】

**【技術分野】****【0001】**

本発明は、不揮発性記憶装置のための技術に関する。

**【背景技術】****【0002】**

半導体メモリは、様々な電子デバイスで使われることが一般的になってきている。例えば、不揮発性半導体メモリは、携帯電話、デジタルカメラ、パーソナルデジタルアシスタント、モバイルコンピュータ、非モバイルコンピュータ、及び他の装置に使用されている。電気的消去・再プログラム可能型読取専用メモリ(EEPROM)とフラッシュメモリは、最も普及している不揮発性半導体メモリである。

10

**【0003】**

EEPROMとフラッシュメモリは、半導体基板内のチャネル領域上に配置され、そのチャネル領域から絶縁されているフローティングゲートを採用している。フローティングゲートとチャネル領域は、ソース領域とドレイン領域の間に配置されている。フローティングゲートの上に、そのフローティングゲートから絶縁されている制御ゲートが設けられている。トランジスタの閾値電圧は、フローティングゲート上(または他の電荷蓄積領域)に保持されている電荷量によって制御される。即ち、そのソースとドレインの間の導通を可能にすべくトランジスタをオンするために制御ゲートに印加すべき電圧の最小量は、そのフローティングゲート上(または他の電荷蓄積領域)の電荷量レベルにより制御される。

20

**【0004】**

EEPROMやNAND型フラッシュメモリデバイスなどのフラッシュメモリデバイスにプログラムを行う場合、典型的には、ビットラインが接地されるとともに、制御ゲートにプログラム電圧が加えられる。チャネルからの電子がフローティングゲートへ注入される。フローティングゲートに電子が蓄積されると、フローティングゲートが負値に帶電し、メモリセルの閾値電圧が上昇し、メモリセルがプログラムされた状態となる。典型的なプログラム処理は、プログラム電圧を、時間とともに大きさが増加する一連のパルスとして、制御ゲートに印加する。これらの複数のプログラムパルスの間には、メモリセルが目標閾値電圧に到達したか否かを判断するための検証処理が存在する。プログラムに関するさらなる情報は、「Source Side Self Boosting Technique for Non-Volatile Memory」と題した米国特許第6,859,397号、および、「Detecting Over Programmed Memory」と題した米国特許第6,917,545号に開示されている。これらの両方の文献の内容は、その全体を参照することにより本明細書に組み込まれる。

30

**【0005】**

幾つかのEEPROMおよびフラッシュメモリデバイスは、電荷の2つの範囲を記憶するために用いられる、フローティングゲート(または他の電荷蓄積領域)を備えている。従って、メモリセルは、2つの状態(消去状態およびプログラム状態)の間で、プログラムまたは消去することができる。このようなフラッシュメモリデバイスは、バイナリメモリデバイスと呼ばれる場合がある。

**【0006】**

40

マルチステート記憶装置は、禁止範囲によって分離された複数の明確な許可/有効プログラム閾値電圧範囲を識別することによって、実現される。各々の明確な閾値電圧範囲は、記憶装置で符号化された一組のデータビットに対する所定の値に関連するデータ状態に対応する。

**【0007】**

例えば、妥当な時間でプログラム可能な市販のメモリシステムを製造するために、多くの場合、多数のメモリセルを並列にプログラムする必要がある。しかしながら、大きな数のメモリセルが同時にプログラムされる場合には、問題が発生することがある。この問題は、複数のメモリセルに備えられている半導体デバイスの構造や動作のわずかなバラツキによって、各々のメモリセルの特性が異なることによるものである。この問題は、他のメ

50

モリセルよりも早くプログラムされてしまうメモリセルを発生させたり、一部のメモリセルが目的の状態と異なる状態にプログラムされてしまう可能性を生じさせることがある。多数のメモリセルのより速いプログラムによって、結果として、目的とする閾値電圧範囲を行き過ぎてしまい、記憶されるデータにエラーが発生してしまうことがある。

#### 【0008】

一般的には、データがプログラムされると、メモリセルの閾値電圧が最低レベルよりも高いことを保証するために、メモリデバイスのための検証処理が試行される。しかしながら多くのメモリ装置は、標準のプログラム処理中では、閾値電圧の上限値を一般的には保証しない。従って、オーバープログラム（目的状態の閾値電圧を超えて閾値電圧が上昇することを含む）が起こりうる。オーバープログラムによって、メモリセルに誤ったデータが記憶されうる。従って、続く読み出し処理中に、エラーが発生しうる。10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0009】

オーバープログラムを訂正することが可能なシステムが提供される。

#### 【0010】

一実施形態は、複数の不揮発性記憶素子をプログラムするステップと、オーバープログラムされた前記複数の不揮発性記憶素子の部分集合を特定するステップと、前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に対して、1つまたは複数の消去処理を選択的に実行するステップと、を備える。1つまたは複数の消去処理は、オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された部分集合に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧するステップと、消去許可電圧を前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に印加するステップと、を備える。前記チャネル領域の第1の集合および前記チャネル領域の第2の集合は、共通基板領域の一部である。20

#### 【0011】

一実施形態は、共通ワードラインに接続されるとともに複数のNANDストリングの集合のうちの異なるNANDストリングに配置される複数の不揮発性記憶素子に、プログラムするステップを備える。オーバープログラムされた複数の不揮発性記憶素子の部分集合を特定するステップを備える。前記複数のNANDストリングの部分集合内の複数の不揮発性記憶素子の閾値電圧を低下させるために、前記NANDストリングの集合に許可電圧を印加するとともに複数のNANDストリングの部分集合を選択的に昇圧することによって、オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に対して、1つまたは複数の消去処理を選択的に実行するステップを備える。前記複数のNANDストリングの部分集合は、オーバープログラムされた複数の不揮発性記憶素子の部分集合を備えている。30

#### 【0012】

一実施形態は、第1型の複数のコントロールラインの共通コントロールラインに接続された複数の不揮発性記憶素子をプログラムするステップを備える。オーバープログラムされた複数の不揮発性記憶素子の部分集合を特定するステップを備える。オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に対して、複数の消去処理を選択的に実行するステップを備える。複数の消去処理を選択的に実行するステップは、前記複数の不揮発性記憶素子のオーバープログラムされたと特定された部分集合に対して消去条件を印加するステップを備える。消去条件を印加するステップは、前記第1型の複数のコントロールラインのうちの他の複数のコントロールラインに複数の信号を印加するステップと、前記他の複数のコントロールラインに対してより高い大きさの前記複数の信号を用いて前記消去条件を印加するステップを繰り返すステップと、を備える。前記他の複数のコントロールラインは、前記消去処理の対象として選択されなかった複数の不揮発4050

性記憶素子に接続されている。

**【0013】**

一実施態様は、共通基板領域上の複数の不揮発性記憶素子と、前記複数の不揮発性記憶素子と通信する1つまたは複数の管理回路と、を備える。前記1つまたは複数の管理回路は、複数の不揮発性記憶素子をプログラムし、オーバープログラムされた前記不揮発性記憶素子の部分集合を特定し、前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合に対して1つまたは複数の消去処理を選択的に実行する。前記1つまたは複数の消去処理は、オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された部分集合に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧するステップと、消去許可電圧を前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に印加するステップと、を備える。前記チャネル領域の第1の集合および前記チャネル領域の第2の集合は、前記共通基板領域の一部である。

10

**【0014】**

一実施形態は、共通基板領域内の複数の不揮発性記憶素子と、前記複数の不揮発性記憶素子をプログラムする手段と、前記複数の不揮発性記憶素子からオーバープログラムされた部分集合を特定する手段と、前記オーバープログラムされたと特定された部分集合に対して1つまたは複数の消去処理を選択的に実行する手段と、を備える。前記1つまたは複数の消去処理は、オーバープログラムされたと特定されていない複数の不揮発性記憶素子に対してチャネル領域の第2の集合を第1の電圧範囲に昇圧することなく、前記複数の不揮発性記憶素子の特定された部分集合に対してチャネル領域の第1の集合を前記第1の電圧範囲に昇圧するステップと、消去許可電圧を前記オーバープログラムされたと特定された前記複数の不揮発性記憶素子の部分集合および前記オーバープログラムされたと特定されていない複数の不揮発性記憶素子に印加するステップと、を備える。前記チャネル領域の第1の集合および前記チャネル領域の第2の集合は、共通基板領域の一部である。

20

**【図面の簡単な説明】**

**【0015】**

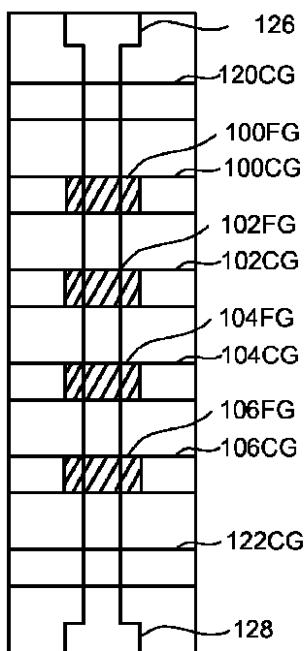

【図1】NANDストリングの平面図である。

30

【図2】NANDストリングの等価回路図である。

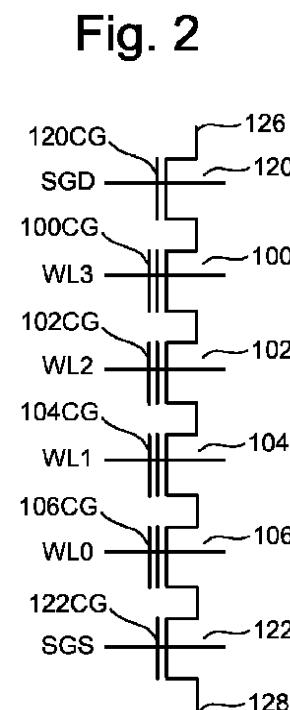

【図3】不揮発性メモリシステムのブロック図である。

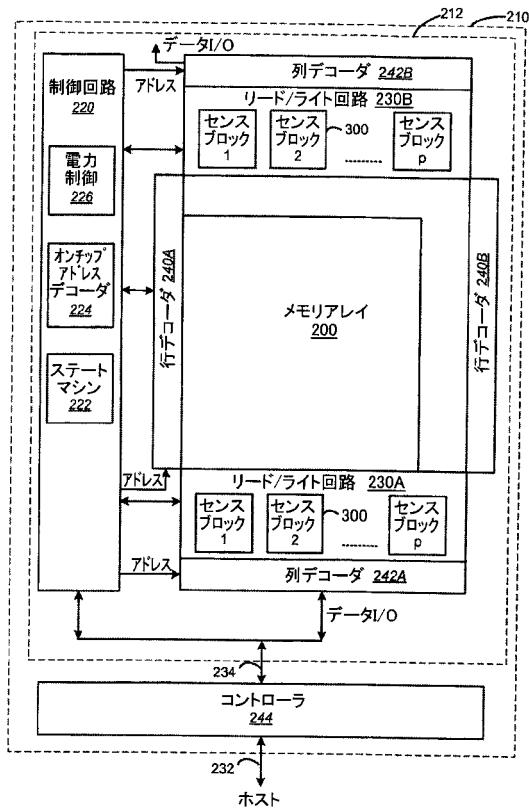

【図4】メモリアレイの一実施例を示すブロック図である。

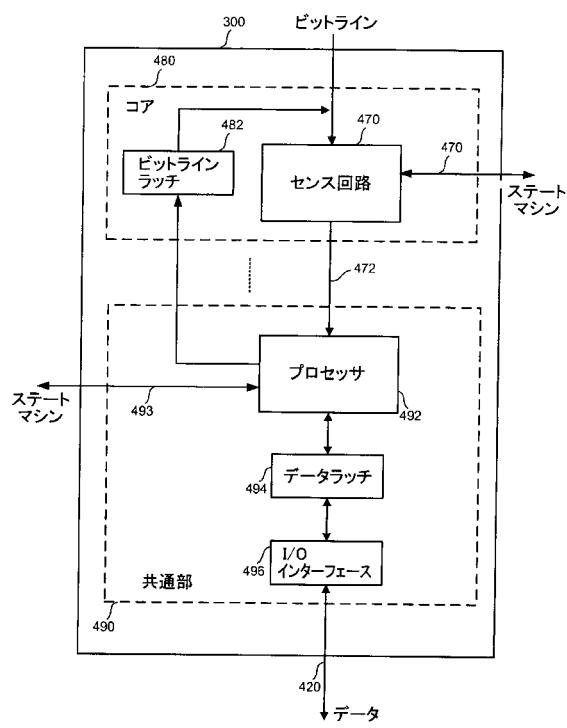

【図5】センスブロックの一実施例を示すブロック図である。

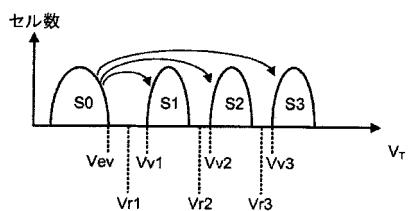

【図6A】閾値電圧区分を示す図である。

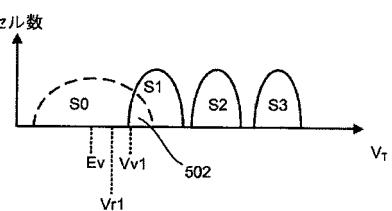

【図6B】閾値電圧区分を示す図である。

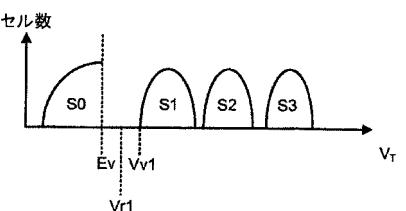

【図6C】閾値電圧区分を示す図である。

【図7】不揮発性記憶メモリ動作の処理の一実施形態を示すフローチャートである。

【図8】不揮発性記憶メモリ動作の処理の一実施形態を示すフローチャートである。

【図9】選択的消去処理の実行処理の一実施形態を示すフローチャートである。

40

【図10】選択的消去処理のタイミング図である。

【図11】選択的消去処理中のNANDストリングを示す図である。

【図12A】選択的消去処理中のNANDストリングの断面図である。

【図12B】選択的消去処理中のNANDストリングの断面図である。

【図13】選択的消去処理の実行処理の一実施形態を示すフローチャートである。

【図14】選択的消去処理のタイミング図である。

【図15】選択的消去処理中のNANDストリングの図である。

【図16A】選択的消去処理中のNANDストリングの断面図である。

【図16B】選択的消去処理中のNANDストリングの断面図である。

【図17】検証処理に干渉することなく多数の消去パルスを用いて選択的に不揮発性記憶

50

装置を消去するステップの処理の一実施形態を示すフローチャートである。

【図18】検証処理に干渉することなく多数の消去パルスを用いて選択的に不揮発性記憶装置を消去するステップのタイミング図である。

【図19】2バスプログラム処理の一実施形態を示すフローチャートである。

【図20】閾値電圧区分を示す図である。

【図21】不揮発性記憶装置をプログラムおよび選択的消去する処理の一実施形態を示すフローチャートである。

【図22】不揮発性記憶装置をプログラムおよび選択的消去する順番を示すテーブルである。

【図23】閾値電圧区分を示す図である。

10

【図24】閾値電圧区分を示す図である。

【図25】閾値電圧区分を示す図である。

【図26A】選択的消去処理を用いてオーバープログラムを訂正するステップを備えるプログラム処理の一実施形態を示すフローチャートである。

【図26B】選択的消去処理を用いてオーバープログラムを訂正するステップを備えるプログラム処理の一実施形態を示すフローチャートである。

【図27】選択的消去処理を用いてオーバープログラムを訂正する処理の一実施形態を示すフローチャートである。

【図28】プログラム処理中にオーバープログラムを訂正する処理の一実施形態を示すフローチャートである。

20

【発明を実施するための形態】

【0016】

フラッシュメモリシステムの一例は、NAND構造を用いており、2つの選択ゲートの間に複数のトランジスタの直列接続を含んでいる。直列に接続されたトランジスタと選択ゲートは、NANDストリングと呼ばれる。図1は、1つのNANDストリングを示す平面図である。図2は、その等価回路である。図1と図2に示すNANDストリングは、第1(又はドレイン側)選択ゲート120と第2(又はソース側)選択ゲート122の間に挟まれている、直列に接続されている4つのトランジスタ100、102、104及び106を有する。選択ゲート120は、ビットコンタクト126を介してNANDストリングをビットラインに接続している。選択ゲート122は、NANDストリングをソースライン128に接続している。選択ゲート120は、選択ラインSGDに適切な電圧を加えることによって制御される。選択ゲート122は、選択ラインSGSに適切な電圧を加えることによって制御される。トランジスタ100、102、104、及び106の夫々は、制御ゲートとフローティングゲートを有している。例えば、トランジスタ100は、制御ゲート100CGとフローティングゲート100FGを備えている。トランジスタ102は、制御ゲート102CGとフローティングゲート102FGを備えている。トランジスタ104は、制御ゲート104CGとフローティングゲート104FGを備えている。トランジスタ106は、制御ゲート106CGとフローティングゲート106FGを備えている。制御ゲート100CGはワードラインWL3に接続されており、制御ゲート102CGはワードラインWL2に接続されており、制御ゲート104CGはワードラインWL1に接続されており、制御ゲート106CGはワードラインWL0に接続されている。

30

【0017】

図1と図2は、NANDストリング内の4個のメモリセルを示しているが、4個のトランジスタの使用は単に一例として提示されている点に留意されたい。NANDストリングは、4個よりも少ない、或いは、4個よりも多いメモリセルを有していてよい。例えば、NANDストリングによっては8個、16個、32個、64個、128個などの数のメモリセルを有していてよい。本明細書の説明は、いかなる特定個数のメモリセルを有するNANDストリングにも限定されない。

【0018】

NAND構造を用いたフラッシュメモリシステムの一般的なアーキテクチャは、いくつ

40

50

かのNANDストリングを含んでいる。各NANDストリングは、選択ラインSGSによって制御されるソース選択ゲートによってソースラインに接続されるとともに、選択ラインSGDによって制御されるドレイン選択ゲートによって関連するビットラインに接続されている。各ビットラインとそのビットラインにビットラインコントラクトを介して接続されている夫々のNANDストリングは、メモリセルアレイの列を構成する。ビットラインは、複数のNANDストリングによって共有されている。典型的には、ビットラインは、ワードラインと直交する方向でNANDストリング上を通り、1以上のセンスアンプと接続されている。

#### 【0019】

NANDタイプのフラッシュメモリおよびそれらの動作に関連する例は、以下の米国特許／特許出願に記載されており、それらの引用文献は、その全体が参照により本明細書に組み込まれる。米国特許第5,570,315号、米国特許第5,774,397号、米国特許第6,046,935号、米国特許第6,456,528号、及び、米国公開公報第US2003/0002348号。

10

#### 【0020】

NANDフラッシュメモリに加えて、不揮発性記憶装置の他のタイプもまた用いることができる。例えば、不揮発性装置は、強誘電体層を用いたメモリセルによって製造されてもよい。前述した導電性のフローティングゲート素子の代わりに、誘電体層が用いられる。誘電体記憶素子を用いたメモリ装置が、「NROM: A Novel Localized Trapping, 2-Bit Nonvolatile Memory Cell」、IEEE Electron Device Letters、21巻、11号、2000年11月、543から545ページに、Eitanらによって開示されている。ONO誘電層は、ソース拡散領域とドレイン拡散領域の間のチャンネルを横切って伸びている。あるデータビットの電荷がドレインに近接した誘電層内に局在し、他のデータビットの電荷がドレインに近接した誘電層内に局在する。例えば、米国特許第5,768,192号および6,011,725号では、2つの酸化シリコン層に挟まれたトラップ用の誘電層を有する不揮発性メモリセルが開示されている。マルチステートのデータ記憶は、誘電層内の空間的に離れた電荷蓄積領域の2値の状態を、別々に読み出すことで行われる。他のタイプのメモリ素子も使用できる。

20

#### 【0021】

図3は、複数のメモリセル（例えば、NANDマルチステートフラッシュメモリなど）のページ（または他のユニット）に平行して読み出しおよびプログラムを行うリード／ライト回路を有する記憶デバイス210を示している。記憶デバイス210は1以上のメモリダイまたはチップ212を備えていてもよい。メモリダイ212は、メモリセルの（2次元又は3次元の）アレイ200、制御回路220、及び、リード／ライト回路230Aと230Bを有する。一実施形態では、様々な周辺回路によるメモリアレイ200へのアクセスはアレイの両側で対称的に実装されており、これにより、各側のアクセスライン及び回路の密度が半分に低減される。リード／ライト回路230A及び230Bは、複数のセンスブロック300を有しており、これらのセンスブロック300によって1ページのメモリセルを並列に読み出し又はプログラムすることができる。メモリアレイ200は、行デコーダ240Aと240Bを介したワードラインと、列デコーダ242Aと242Bを介したビットラインによってアドレス指定される。ワードラインおよびビットラインは、コントロールラインの一例である。典型的な実施形態では、コントローラ244は、1つ以上のメモリダイ212のような同じメモリデバイス210（例えば、取り外し可能なストレージカード又はパッケージ）内に含まれる。命令、及びデータは、ライン232を介してホストとコントローラ244の間で転送され、また、ライン234を介してコントローラと1つ以上のメモリダイ212の間で転送される。

30

#### 【0022】

制御回路220は、リード／ライト回路230Aと230Bと協調して、メモリアレイ200に対してメモリ動作を実行する。制御回路220は、ステートマシン222、オンチップアドレスデコーダ224、及び電力制御モジュール226を有している。ステート

40

50

マシン 222 は、メモリ動作のチップレベルの制御を提供する。オンチップアドレスデコーダ 224 は、ホスト又はメモリコントローラによって用いられるアドレスと、デコーダ 240A、240B、242A 及び 242B によって用いられるハードウェアアドレスの間のアドレスインタフェースを提供する。電力制御モジュール 226 は、メモリ動作中のワードライン及びビットラインに供給される電力及び電圧を制御する。一実施形態では、電力制御モジュール 226 は、供給電力より大きな電圧を作り出すことができる一つ以上のチャージポンプを有する。

#### 【0023】

一実施形態では、制御回路 220、電力制御回路 226、デコーダ回路 224、ステートマシン回路 222、デコーダ回路 242A、デコーダ回路 242B、デコーダ回路 240A、デコーダ回路 240B、リード/ライト回路 230A、リード/ライト回路 230B、及び / 又はコントローラ 244 の一つ又は幾つかの組合せは、1つの管理回路または制御回路、或いは複数の管理回路群または制御回路群と称されることがある。1以上の管理回路または制御回路は、本明細書で記述する処理を実行する。

#### 【0024】

図 4 は、メモリセルアレイ 200 の例示的な構造を示す。一実施形態においては、メモリセルのアレイは、数多くのブロックに分割される（例えば、ブロック 0 - 1023 や、その他の量など）。一実施形態では、ブロックは従来の消去の単位である。その他の消去の単位を用いた装置も使用可能である。

#### 【0025】

1 のブロックは、ビットライン（例えばビットライン BL0 - BLX）およびワードライン（WL0、WL1、WL2、WL3）を介してアクセスされる複数の NANDストリングを備えている。図 4 は、直列接続されることで NANDストリングを形成している、4 つのメモリセルを示している。各々の NANDストリングに 4 つのセルが含まれているが、4 個よりも少ない、或いは、4 個よりも多いメモリセルを有していてよい（例えば、NANDストリングによっては、16 個、32 個、64 個、128 個やその他の数のメモリセルを有していてよい。）各 NANDストリングの一端は、（選択ライン SGD に接続されている）ドレイン選択ゲートを介して対応するビットラインに接続されており、他端は、（選択ライン SG S に接続されている）ソース選択ゲートを介してソースラインに接続されている。一実施形態では、NANDストリングの各々は、NANDストリングのそれぞれの端部に、計 2 つのダミーメモリセルを含んでいる。ダミーメモリセルは、データ記憶には用いられない。

#### 【0026】

各ブロックは、通常、複数のページに分割される。一実施形態においては、ページはプログラムの単位である。プログラムの他の装置も使用可能である。通常、1つ又は複数ページのデータが1列のメモリセルに記憶される。例えば、データの1以上のページが、共通ワードラインに接続されたメモリセルに記憶されてもよい。1つのページは、1つ又は複数のセクタを記憶できる。1つのセクタは、ユーザデータとオーバヘッドデータ（システムデータとも呼ばれる）を含む。オーバヘッドデータは、通常、セクタのユーザデータから算出される誤り訂正符号（Error Correction Code : ECC）とヘッダ情報を含む。コントローラ（またはステートマシン、または他の構成要素）の一部が、データがアレイにプログラムされているときに ECC を計算し、データがアレイから読み出されているときに ECC のチェックも行う。代わりに、ECC 及び / 又は他のオーバヘッドデータはそれらが関係するユーザデータとは異なるページに記憶され、または異なるブロックに記憶されることがある。ユーザデータのセクタは通常、磁気ディスクドライブ内のセクタサイズに相当する 512 バイトである。例えば 8 ページから 32、64、128、或いはそれ以上のページまでの多数のページが 1 ブロックを形成する。異なるサイズのブロックと配置も採用することができる。

#### 【0027】

幾つかの実施形態では、メモリセルは、p 基板、p 基板の内部の n ウェル、n ウェルの

10

20

30

40

50

内部の p ウェルを備えた、トリプルウェルを含んでいる。チャネル領域、ソース領域およびドレイン領域は、典型的には、p ウェル内に配置されている。p ウェルおよびn ウェルは、基板の一部とみなされる。一実施形態では、N A N Dストリングとの間の電気的遮蔽を得るための p ウェル内のトレンチと共に、メモリセルの全体のアレイが、1つの p ウェル内に存在している。一実装様では、同一のビットライン群を共有している p ウェル内の全ブロックは、プレーンと呼ばれる。他の実施形態では、異なるブロックは、異なる p ウェル内に存在するとすることができる。

#### 【 0 0 2 8 】

加えて、デバイスは、n 基板、n 基板の内部の p ウェル、p ウェルの内部の n ウェルから成るトリプルウェルなど、逆極性を有することができる。この構造では、典型的には、チャネル領域、ソース領域およびドレイン領域がn ウェル内に配置される。10

#### 【 0 0 2 9 】

図 5 は、センスモジュール 4 8 0 と呼ばれるコア部と共通部 4 9 0 に分割された個々のセンスブロック 3 0 0 のブロック図である。一実施形態では、各ビットラインに対して個別のセンスモジュール 4 8 0 を用意し、一組の複数センスモジュール 4 8 0 に対して一つの共通部 4 9 0 を用意してもよい。一例として、1 個のセンスブロックは、1 個の共通部 4 9 0 と 8 個のセンスモジュール 4 8 0 を有している。グループ内の各センスモジュールは、データバス 4 7 2 を介して協働する共通部と通信する。一例としては、その全体を参照することにより本明細書に組み込まれる米国特許出願公開公報 2 0 0 6 / 0 1 4 0 0 0 7 号を参照されたい。20

#### 【 0 0 3 0 】

センスモジュール 4 8 0 は、接続されたビットライン内の伝導電流が予め決められたレベルより高いか低いかを判定するセンス回路 4 7 0 を備えている。幾つかの実施形態では、センスモジュール 4 8 0 は、センスアンプと一般に呼ばれる回路を有する。センスモジュール 4 8 0 は、さらに、接続されたビットラインに電圧状態を設定するために用いられるビットラインラッチ 4 8 2 を有している。例えば、ビットラインラッチ 4 8 2 内で予め決められた状態がラッチされることによって、接続されたビットラインを、プログラム禁止を指定する状態（例えば、V d d）に引き上げる（プル）する。

#### 【 0 0 3 1 】

共通部 4 9 0 は、プロセッサ 4 9 2、1 組のデータラッチ 4 9 4、及び、1 組のデータラッチ 4 9 4 とデータバス 4 2 0 の間を接続する I / O インタフェース 4 9 6 を備えている。プロセッサ 4 9 2 は計算を実行する。例えば、その機能の 1 つは、センスされたメモリセル内に記憶されているデータを特定し、特定されたデータを一組のデータラッチ内に記憶することである。1 組のデータラッチ 4 9 4 は、読み出し動作において、プロセッサ 4 9 2 によって特定されたデータビット群を記憶するために用いられる。一組のデータラッチ 4 9 4 は、プログラム動作において、データバス 4 2 0 から取り込んだデータビット群を記憶するためにも用いられる。取り込まれるデータビット群は、メモリ内にプログラムする予定のライトデータ（プログラムデータ）を表す。I / O インタフェース 4 9 6 は、データラッチ 4 9 4 とデータバス 4 2 0 の間のインターフェースを提供する。30

#### 【 0 0 3 2 】

読み出し又はセンス中には、システムの動作はステートマシン 2 2 2 の制御下にあり、ステートマシン 2 2 2 は（電力制御モジュール 2 2 6 を用いて）アドレス指定されたセルへの種々の制御ゲート電圧の供給を制御する。メモリに用意された様々なメモリ状態に対応する様々な既定制御ゲート電圧のステップを進む毎に、センスモジュール 4 8 0 はこれらの電圧の 1 つに遷移し、バス 4 7 2 を介してセンスモジュール 4 8 0 からプロセッサ 4 9 2 に出力が提供される。その時点で、プロセッサ 4 9 2 は、センスモジュールの遷移イベントと、ステートマシンから入力ライン 4 9 3 を介して加えられた制御ゲート電圧についての情報によって、結果としてのメモリ状態を特定する。それから、プロセッサは、メモリ状態に対するバイナリ符号化を計算し、得られたデータビット群をデータラッチ 4 9 4 に格納する。コア部の別の実施形態では、ビットラインラッチ 4 8 2 は、センスモジュ4050

ール 480 の出力をラッチするラッチ、及び、上記のようなビットラインラッチの二つの役割を持つ。

#### 【 0033】

当然のことながら、いくつかの実装形態では複数のプロセッサ 492 を有することができる。一実施形態では、各プロセッサ 492 は出力ライン（図 5 には示されていない）を有し、各出力ラインは共にワイヤード OR（配線論理和）接続される。いくつかの実施形態では、出力ラインは、ワイヤード OR ラインに接続される前段階で反転される。この構成は、ワイヤード OR の結果を受け取るステートマシンが、プログラムされる全てのビットがいつ所望のレベルに到達したかを判断できるので、プログラム処理の完了時点を判定するプログラム検証処理における素早い判定を可能にする。例えば、各ビットがその所望のレベルに到達すると、そのビット用の論理「0」がワイヤード OR ラインに送られる（又はデータ「1」が反転される）。全てのビットがデータ「0」を出力すると（又はデータ「1」が反転されると）、ステートマシンはプログラム処理の完了を知る。各プロセッサが 8 個のセンスモジュールと通信する実施形態では、（いくつかの実施形態において）ステートマシンはワイヤード OR ラインを 8 回読み出す必要があつてもよいし、あるいは、協働するビットラインの結果を蓄積するための論理をプロセッサ 492 に追加し、ステートマシンがワイヤード OR ラインを一度だけ読み出せば良いようにしてもよい。10

#### 【 0034】

データラッチャック 494 は、センスモジュールに対応するデータラッチのスタックを有する。一実施形態では、センスモジュール 480 毎に 3 個（或いは 4 個或いは他の数の）データラッチが存在する。一実施形態では、ラッチは夫々 1 ビットである。20

#### 【 0035】

プログラム又は検証処理の間、プログラムされるべきデータはデータバス 420 から 1 組のデータラッチ 494 内に記憶される。検証処理の間、プロセッサ 492 は、所望のメモリ状態に対する検証メモリ状態を監視する。その 2 つが一致したとき、プロセッサ 492 は、プログラム禁止を指定する状態にビットラインを引き上げる（プルする）ようにビットラインラッチ 482 を設定する。これにより、たとえプログラムパルスがその制御ゲートに影響しても、ビットラインに接続したメモリセルがさらにプログラムされないようにすることができる。他の実施形態では、プロセッサが最初にビットラインラッチ 482 をロードし、センス回路が検証処理中にそれに禁止値を設定する。30

#### 【 0036】

いくつかの実装形態では、（必須ではないが）データラッチはシフトレジスタとして実装され、内部に記憶されたパラレルデータをデータバス 420 用にシリアルデータに変換したり、その逆を行ったりする。好適な一実施形態では、m 個のメモリセルのリード / ライトブロックに対応する全てのデータラッチを相互にリンクしてブロックシフトレジスタを構成し、シリアル転送によってデータのブロックを入力または出力できるようにする。特に、リード / ライトモジュールの一群のデータラッチのそれぞれが、データバスへ或いはデータバスからデータを順に転送するようにリード / ライトモジュールのバンクを構成し、一群のデータラッチがあたかもリード / ライトブロック全体のシフトレジスタの一部であるかのようにしてもよい。40

#### 【 0037】

読み出し動作やセンスアンプについてのさらなる情報は次の文献に記載されている。（1）米国特許出願公開 2004 / 0057287 号、「Non-Volatile Memory And Method With Reduced Source Line Bias Errors」、2004 年 3 月 25 日公開、（2）米国特許出願公開 2004 / 0109357 号、「Non-Volatile Memory And Method with Improved Sensing」、2004 年 6 月 10 日公開、（3）米国特許出願公開 20050169082 号、（4）米国特許出願公開 2006 / 0221692 号、「Compensating for Coupling During Read Operations of Non-Volatile Memory」、発明者 Jian Chen、2005 年 4 月 5 日出願、及び、（5）米国特許出願公開第 2006 / 0158947 号、「Reference Sense Amplifier For Non-Volatile Memory」、発明者 Siu Lu50

ng Chan及びRaúl - Adrian Cernea、2005年12月28日出願。これら5個の特許文献の全ては、その全体を参照することにより本明細書に組み込まれる。

### 【0038】

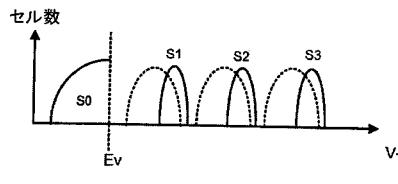

プログラム処理が良好に終了した時点で、メモリセルの閾値電圧は、必要に応じて、プログラムされたメモリセルの閾値電圧の1つまたは複数の区分内、あるいは、消去されたメモリセルの閾値電圧区分内にあるべきである。図6Aに、各メモリセルが2ビットのデータを記憶する場合における、メモリセルアレイに対する（各々がデータ状態に対応する）閾値電圧区分の例を示す。しかしながら、他の実施形態では、メモリセル当たり2ビットよりも多いデータあるいは2ビットよりも少ないデータを使用してもよい。たとえば、メモリセル当たり3ビットのデータ、メモリセル当たり4ビットのデータ、あるいは、他のビット数が使用されうる。図6Aは、消去されたメモリセルに対する第1の閾値電圧区分／データ状態S0を示す。また、プログラムされたメモリセルに対して、3つの閾値電圧区分／データ状態S1、S2、およびS3もまた示されている。一実施形態では、S0における閾値電圧は負であり、S1、S2、およびS3における閾値電圧は正である。いくつかの実施形態では、複数の閾値電圧区分が、負の閾値電圧に対応する。10

### 【0039】

図6Aの明確な各閾値電圧区分は、一組のデータビットに対して、所定の値を有するデータ状態に対応する。メモリセルにプログラムされたデータとメモリセルの閾値電圧レベルとの具体的な関係は、セルに採用されるデータ符号化方式に依存する。たとえば、米国特許第6,222,762号および2003年6月13日に出願された「Tracking Cells For A Memory System」と題する米国特許出願公開第2004/0255090号は、いずれも、その全体を参照することにより本明細書に組み込まれており、マルチステートフラッシュメモリセルに関する様々なデータ符号化方式を掲載している。一実施形態では、フローティングゲートの閾値電圧が誤ってその隣接する物理状態にシフトした場合であっても1ビットしか影響を受けないように、データ値はグレーコード割当を用いて閾値電圧範囲／データ状態に割り当てられる。一例では、「11」を閾値電圧区分／データ状態S0に割り当て、「10」を閾値電圧区分／データ状態S1に割り当て、「00」を閾値電圧区分／データ状態S2に割り当て、「01」を閾値電圧区分／データ状態S3に割り当てる。この例では、メモリセルが消去され、かつプログラムされるデータが11である場合、閾値電圧は11に関連するS0に既に存在しているので、その閾値電圧を変える必要がない。メモリセルが消去され、かつプログラムされるデータが00である場合、メモリセルの閾値電圧はS2に移動される必要がある。2030

### 【0040】

また、図6Aは、メモリセルからデータを読み出すための、3つの読み出し基準電圧Vr1、Vr2、およびVr3も示している。所与のメモリセルの閾値電圧がVr1、Vr2、およびVr3以上であるか以下であるかを試験することによって、システムはメモリセルがどんな閾値電圧区分／データ状態にあるかを判定することができる。

### 【0041】

また、図6Aは、3つの検証基準電圧Vv1、Vv2、およびVv3も示している。メモリセルをデータ状態S1にプログラムする場合、システムは、これらのメモリセルがVv1よりも大きいまたはVv1に等しい閾値電圧を有するか否かを試験する。メモリセルをデータ状態S2にプログラムする場合、システムは、メモリセルがVv2よりも大きいまたはVv2に等しい閾値電圧を有するか否かを試験する。メモリセルをデータ状態S3にプログラムする場合、システムは、メモリセルがVv3よりも大きいまたはVv3に等しい閾値電圧を有するか否かを判定する。40

### 【0042】

フルシーケンスプログラミングとして知られる一実施形態では、メモリセルは、消去された閾値電圧区分／データ状態S0から、プログラムされた閾値電圧区分／データ状態S1、S2、またはS3のいずれかに、直接にプログラムされうる。たとえば、プログラム50

されるメモリセルの母集団は、母集団内にあるすべてのメモリセルが消去された閾値電圧区分 / データ状態 S 0 にあるように、まず消去されてもよい。いくつかのメモリセルは、閾値電圧区分 / データ状態 S 0 から閾値電圧区分 / データ状態 S 1 にプログラマされる。一方、他のメモリセルは、閾値電圧区分 / データ状態 S 0 から閾値電圧区分 / データ状態 S 2 に、および / または、閾値電圧区分 / データ状態 S 0 から閾値電圧区分 / データ状態 S 3 に、プログラマされる。フルシーケンスプログラミングは、図 6 A の 3 つの曲線矢印によって図示される。

#### 【 0 0 4 3 】

メモリセルは、同じワードライン上、同じビットライン上、あるいは近接したワードライン上および近接したビットライン上の隣接メモリセルから、容量結合を受けやすい。隣接メモリセルはプログラマされているので、容量結合はメモリセルの見かけ上の閾値電圧を上昇させる働きをするが、フローティングゲートには、電荷量の追加も損失も生じないこともある。多くのメモリセルの見かけ上の閾値電圧の上昇は、図 6 B に示されるように、閾値電圧区分を広げてしまう。重度の容量結合のいくつかの例では、消去状態の閾値電圧は、第 1 のプログラム状態と重なる点まで広げられる。たとえば、図 6 B では、閾値電圧区分 / データ状態 S 0 が隣接メモリセルからの容量結合によって広げられることで、閾値電圧区分 / データ状態 S 0 が閾値電圧区分 / データ状態 S 1 と重なっている。いくつかの事例では、システムはセルが状態 0 にあるか状態 1 にあるかを判定できないので、閾値電圧が重なっているメモリセルを備えるページまたはセクタは、正しくリードバックされ得ない。

#### 【 0 0 4 4 】

本明細書で提案される技術は、消去状態 0 にあるべきであるものの、容量結合（またはその他の理由）によって見かけ上は消去されたデータ状態 S 0 の閾値電圧区分外に存在する閾値電圧を有するメモリセルを再消去するために、消去処理を選択的に実施する。選択的消去は、プログラマされているべきメモリセルのいずれにおいても、プログラマされたデータを意図的に消去することなく、実施される。それゆえ、一実施形態では、図 6 B の閾値電圧区分 / データ状態 S 0 は、閾値電圧区分 / データ状態 S 0 におけるメモリセルのすべてが消去検証レベル  $E_v$  未満の閾値電圧を有する図 6 C の閾値電圧区分 / データ状態 S 0 のようになるように、狭められる。一実施形態では、 $E_v = 0$  ボルトである。状態 S 1、S 2、および S 3 にあるメモリセルは、選択的消去の間ににおいて、消去処理を施されない。

#### 【 0 0 4 5 】

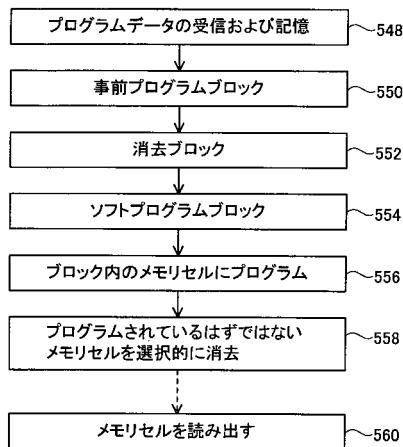

図 7 は、不揮発性記憶装置を動作させる処理を説明するフローチャートである。ステップ 548において、プログラム要求およびプログラムするデータが受信される。データが記憶される。データは、コントローラ、ステートマシン、バッファ、またはその他の場所に記憶させることができる。図 7 の処理の一の実装形態では、メモリセルの劣化を均一に維持するために、メモリセルには事前プログラムが行われる（ステップ 550）。一実施形態では、メモリセルは、状態 S 3（最も高い状態）や、ランダムパターンや、その他のパターンに事前プログラムされる。いくつかの実装形態では、事前プログラムを行う必要がない。

#### 【 0 0 4 6 】

ステップ 552 では、プログラムに先立って、メモリセルが（ブロック単位又は他の単位で）消去される。一実施形態では、ソースとビットラインをフローティング状態にしておきながら、選択されたブロックのワードラインを接地し、十分な期間  $p$  ウェルを消去電圧（例えば 20 ボルト）にまで上昇させることによってメモリセルが消去される。消去対象に選択されていないブロックでは、ワードラインがフロートされる。容量結合のため、非選択ワードライン、ビットライン、選択ライン、及び、共通ソースラインもまた、消去電圧のかなりの割合の電圧まで上昇する。従って、消去されることが選択されていないブロックの消去が妨げられる。消去されることが選択されているブロックでは、選択されたメモリセルのトンネル酸化物層に強力な電場が加わり、主としてファウラ - ノルドハイム

10

20

30

40

50

トンネル効果によってフローティングゲートの電子が基板側に放出されて、選択されたメモリセルのデータが消去される。電子がフローティングゲートから p - ウェル領域に移動するにつれて、選択されたセルの閾値電圧が低下する。消去は、メモリアレイ全体、別々のブロック、又はセルの他の単位で行うことができる。一実施形態では、メモリセルが消去された後、全ての消去済みのメモリセルが状態 S 0 となる（図 6 A 参照）。消去処理の一実装態様では、幾つかの消去パルスを p ウェルに印加するステップ、および、メモリセルが V e v を下回る閾値電圧を有しているか否かを消去パルスの合間に検証するステップを含んでいる。

#### 【 0 0 4 7 】

ステップ 5 5 4 では、消去されたメモリセルの消去閾値電圧の区分を狭めるために、（随意に）ソフトプログラムが実行される。いくつかのメモリセルは、消去処理の結果として必要以上に低い消去状態にあってよい。ソフトプログラムでは、より深く消去されたメモリセルの閾値電圧ほど、消去検証レベル E v に近づくように移動させるように、プログラムパルスを制御ゲートに印加することができる。例えば図 6 A に示すように、ステップ 5 5 4 は、状態 S 0 と関連する閾値電圧区分を狭めるステップを含むことがあり得る。ステップ 5 5 6 では、ブロックのメモリセルにプログラムが行われる。図 7 の処理は、上述した多様な回路を用いたステートマシンの指示によって実行されうる。ステップ 5 5 8 では、（コントローラおよび／またはステートマシンの指示で）メモリシステムは、（例えば再消去する）メモリセルに対して、消去処理を選択的に実行する。消去処理が実行されるメモリセルは、消去状態にされるべきだが、消去データ状態の電圧閾値区分から外れていると考えられる閾値電圧を有しているメモリセルである。選択的消去ステップは、プログラムされていると考えられている何れのメモリセルからもプログラムされたデータを意図的に消去することなく、行われる。メモリセルがプログラムされ、（場合によっては）選択的に消去された後では、メモリセルは読み出されることが可能となり（ステップ 5 6 0 ）、コントローラおよび／またはそのコントローラと通信するホストにデータ読み出しが報知可能とされる。

#### 【 0 0 4 8 】

図 8 は共通ワードラインに接続されているメモリセルにプログラムを実行する際のプロセスの一実施形態を表すフローチャートである。図 8 のプロセスは、図 7 のステップ 5 5 6 において 1 回または複数回実施されうる。例えば、図 8 の処理は、図 6 A のフルシーケンスプログラミングを実行するために使用することができ、その場合には図 8 の処理は各々のワードラインについて 1 回実行されうる。一実施形態では、プログラムプロセスは、ソースラインの最も近くに位置するワードラインから開始して、ビットライン側へ向かって順番に実施される。図 8 の処理は、1 つのワードラインに対して 1 ページ（または一部ページ、または他の単位）のデータのプログラムを行うため、または、マルチバスプログラム処理の 1 つのバスのプログラムを行うためにも使用しうる。他の変更形態もまた使用可能である。図 8 の処理はステートマシン 2 2 2 の指示によって実行される。ここで述べた消去のための技術は、多くの異なるプログラミング方式に適用することができる。

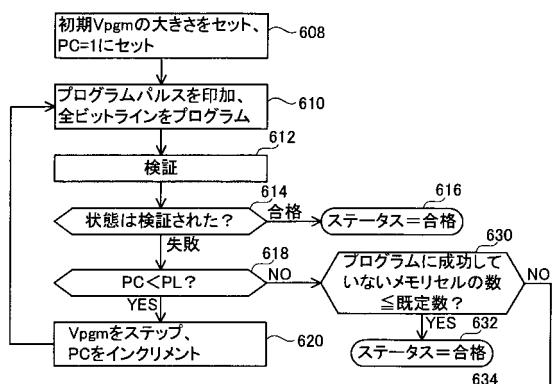

#### 【 0 0 4 9 】

通常、プログラム処理において制御ゲートに印加されるプログラム電圧は、連続するパルスとして印加される。プログラムパルスの合間には、検証処理を可能とするための複数の検証パルスが存在する。多くの実装形態では、連続するパルスの各々の大きさが、所定のステップサイズで増加する。図 8 のステップ 6 0 8 では、プログラム電圧（V p g m ）が初期値（例えば、1 2 ボルトまでの電圧など、その他の適切な値）に初期化されると共に、ステートマシン 2 2 2 によって維持されるプログラムカウンタ P C が 1 に初期化される。ステップ 6 1 0 において、プログラム電圧 V p g m のプログラムパルスが、選択ワードライン（プログラム用に選択されたワードライン）に印加される。非選択ワードラインは、従来知られる昇圧方法を実行することで、1 以上の昇圧電圧（例えば、8 ボルトまでの電圧）を受ける。メモリセルがプログラムされる場合には、対応するビットラインが接地される。一方、メモリセルが現在の閾値電圧を維持する場合には、プログラムを禁止す

10

20

30

40

50

るために、対応するビットラインが $V_{DD}$ に接続される。昇圧方式に関するさらなる情報は、米国特許第6,859,397号、および、米国特許出願公開第20080123425号に記載されている。これらの両方の文献の内容は、その全体を参照することにより本明細書に組み込まれる。

#### 【0050】

ステップ610では、プログラミング対象に選択された選択ワードラインに接続されている全てのメモリセルが一緒にプログラムされるように、選択ワードラインに接続されている全てのメモリセルにプログラムパルスが一斉に印加される。このようにして、選択ワードラインに接続されている全てのメモリセルは、プログラム対象から除外されない限り、一斉に閾値電圧を変更することができる。10

#### 【0051】

ステップ612では、適切な一組の目標レベルを使用して、選択されたメモリセルのデータ状態が検証される。図8のステップ612は、1つ以上の検証処理を有している。一般的に、検証処理および読み出し処理の期間では、関連するメモリセルの閾値電圧がそれらのレベルに到達しているか否かを判断するために、選択されたワードラインが電圧に接続され、その電圧レベルが各々の読み出しおよび検証処理において特定される（例えば、図6Aの検証のための $V_{V1}$ 、 $V_{V2}$ 、 $V_{V3}$ 、および、読み出しのための $V_{R1}$ 、 $V_{R2}$ 、 $V_{R3}$ を参照）。ワードライン電圧を印加した後に、ワードラインに印加された電圧に応じてメモリセルがターンオンしたか否かを判定するために、メモリセルの伝導電流が測定される。所定値よりも大きい伝導電流が測定される場合には、メモリセルがターンオンしており、ワードラインに印加された電圧がメモリセルの閾値電圧よりも大きいと推定される。所定値よりも大きい伝導電流が測定されない場合には、メモリセルがターンオンしておらず、ワードラインに印加された電圧がメモリセルの閾値電圧よりも大きくないと推定される。20

#### 【0052】

読み出しありは検証処理において、メモリセルの伝導電流を測定するためには多くの方法がある。一例としては、センスアンプの専用キャパシタへの伝導電流の放電速度または充電速度によって、メモリセルの伝導電流を測定してもよい。別の例としては、選択したメモリセルの伝導電流が、メモリセルを備えるNANDストリングの対応する、既知の電圧にプレチャージされたビットラインを放電させる（または放電させない）よう構成してもよい。ビットラインが放電されたか否かを調べるために、一定期間後に、ビットラインの電圧が測定される。ここで述べる技術は、検証および読み出しについての他の周知技術についても適用しうることに留意されたい。検証／読み出しについてのさらなる情報は、その全体を参照することにより本明細書に組み込まれる下記の特許文献に記載されている。

(1) 米国特許出願公開2004/0057287号、「Non-Volatile Memory And Method With Reduced Source Line Bias Errors」、(2) 米国特許出願公開2004/0109357号、「Non-Volatile Memory And Method with Improved Sensing」、(3) 米国特許出願公開20050169082号、及び、(4) 米国特許出願公開2006/0221692号、「Compensating for Coupling During Read Operations of Non-Volatile Memory」。3040

#### 【0053】

選択されたメモリセルの閾値電圧が適切な目標レベルに達していることが検知された場合には、例えばそのメモリセルのビットライン電圧がその後のプログラムパルスの間 $V_{dd}$ まで高められることにより、そのメモリセルは以後のプログラムから除外される。

#### 【0054】

図8へ戻り、ステップ614において、全てのメモリセルが目標閾値電圧に到達したか否かが確認される。到達している場合には、全ての選択されたメモリセルがプログラムされていると共に目標状態が検証されているため、プログラム処理が完了し成功している。ステップ616において「合格」ステータスが通知される。ステップ614の幾つかの実装形態では、少なくとも予め決められた数のメモリセルが適切にプログラムされたことが50

検証されたか否かがチェックされることに留意されたい。この予め決められた数は、全メモリセル数よりも少なくともよく、従って、全メモリセルが適切な検証レベルに到達する前にプログラム処理が終了し得る。プログラムに成功しなかったメモリセルは、読み出し処理におけるエラー訂正によって訂正され得る。

#### 【0055】

ステップ614において、全てのメモリセルが目標閾値電圧に到達しているのではないと判断された場合、プログラム処理は継続する。ステップ618では、プログラムカウンタPCがプログラム限度値(PL)に対してチェックされる。プログラム限度値PLの一例は20である。しかしながら、これ以外の値の使用も可能である。プログラムカウンタPCがプログラム限度値未満でない場合には、ステップ630にて、プログラムに成功していないメモリセルの数が既定数以下か否かが判定される。プログラムに失敗したメモリセルの数が既定数以下の場合には、ステップ632にて、プログラム処理が合格したとみなされ、合格のステータスが通知される。多くの場合、プログラムに失敗したメモリセルは、読み出し処理においてエラー訂正を使って訂正され得る。しかし、プログラムに失敗したメモリセルの数が既定数よりも多い場合には、ステップ634にて、プログラム処理に失敗したこと示すフラグが立てられ、失敗ステータスが通知される。10

#### 【0056】

ステップ618において、プログラムカウンタPCがプログラム制限値PL未満であると判断された場合には、ステップ620に進む。ステップ620では、プログラムカウンタPCが1増加され、プログラム電圧Vpgmが次の大きさに段階的に増加される。例えば、次のパルスが前のパルスに対して1ステップサイズ分(例えば、0.1~0.4ボルトのステップサイズ)大きくされる構成としてもよい。ステップ620の後、処理はステップ610へ戻り、別のプログラムパルスが選択ワードラインに印加され、処理が続行される。20

#### 【0057】

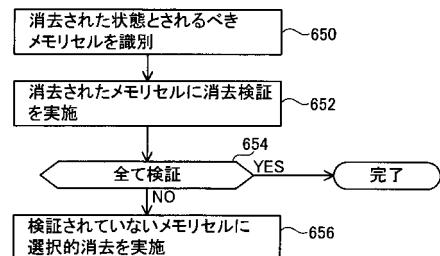

図9は、消去された状態にあるべきであるものの、見かけ上は消去されたデータ状態の閾値電圧区分外に存在する閾値電圧を有するメモリセルの消去処理を、選択的に実施するプロセスを表わすフローチャートである。一実施形態では、図9のプロセスは、選択的消去が1本の選択ワードラインに接続されたメモリセルに対して実施されるように、1本の選択ワードラインに対して実施される。他の変形形態では、種々のワードラインに接続されたメモリセルは、選択的消去処理を同時に施されうる。30

#### 【0058】

ステップ650では、消去された状態を維持すべきメモリセルが識別される。たとえば、状態S0がデータ11に対応し、状態S1がデータ10に対応し、状態S2がデータ00に対応し、状態S3がデータ01に対応する場合、データ11を記憶しているはずのメモリセルが消去されたまま(たとえば、状態S0のまま)であるべきである。消去された状態であるべきメモリセルを識別するのに適した方法は数多くある。一例では、現在プログラムされているデータあるいは最近プログラムされたデータは、バッファ(RAMまたはフラッシュメモリ)に記憶されうる。このデータは、ステップ650においてバッファからの読み出しが可能であり、システムは、コントローラ(図3参照)、ステートマシン(図3参照)、またはプロセッサ492(図4参照)を用いてデータ11を記憶しているはずのメモリセルを識別する。別の実施形態では、データ11を記憶しているはずのメモリセルを判定するために、データが、コントローラからステートマシンまたはプロセッサ492に再発行されうる。別の実施形態では、現在プログラムされているまたは最近プログラムされたデータはデータラッチ494に記憶され得るとともに、またデータ11を記録するべきであるメモリセルを判断するためにプロセッサ492によって使用されうる。40

#### 【0059】

ステップ652では、消去検証処理は、選択ワードラインに接続されたメモリセルに対して実施される。消去検証処理は、メモリセルが正しく消去されているか否かを判定する。一例では、消去検証処理は、メモリセルの閾値電圧が消去検証比較電圧VeVよりも大50

きいか否かを判定する(図6A参照)。選択ワードラインは、消去検証比較電圧 $V_{eV}$ を受ける。非選択ワードラインは、 $V_{read}$ とも呼ばれるオーバードライブ電圧(およそ8~10ボルト)を受ける。図8のステップ612に関して先に説明したように、適切なワードライン電圧(電圧を制御ゲートに印加する)を印加した後、メモリセルが導通しているか否かを判定するために、選択されたメモリセルの伝導電流が観察/測定される。消去検証電圧 $V_{eV}$ に応じて導通するメモリセルは、状態S0内の閾値電圧を有するものと仮定され、したがって、適切に消去されている。消去検証電圧 $V_{eV}$ を受けることに対応して導通せず、かつ消去状態S0にあるはずのメモリセルは、見かけ上は消去データ状態S0の閾値電圧区分外(たとえば、閾値電圧区分よりも高い)にある閾値電圧を有するものと結論付けられる。ステップ654では、すべてのメモリセルが検証される(すなわち、すべてのメモリセルが $V_{eV}$ に応じて導通する)場合、図9のプロセスが終了される。

10

一実施形態では、少なくとも所定数のメモリセルがステップ652における消去検証処理に合格する場合、図9のプロセスは終了される。適切に検証されないメモリセルがある場合(すなわち、検証されるメモリセルが所定数よりも少ない場合)、プロセスはステップ656に引き継がれる。そして、消去状態S0にあると考えられるがステップ652の検証処理に合格しなかったメモリセルに対して、選択的消去処理が実施される。ステップ652において検証処理に合格したメモリセルは、後述のように、ステップ656の選択的消去処理から除外される。ステップ656の選択的消去処理を実施した後、プロセスはステップ652にループバックし、別の消去検証処理が実施される。ステップ652、654、および656のループは、すべてのメモリセルが検証されるまで、あるいは所定数のメモリセルが正しく検証されるまで実施される。他の実施形態では、ループは最大反復回数によって制限される。

20

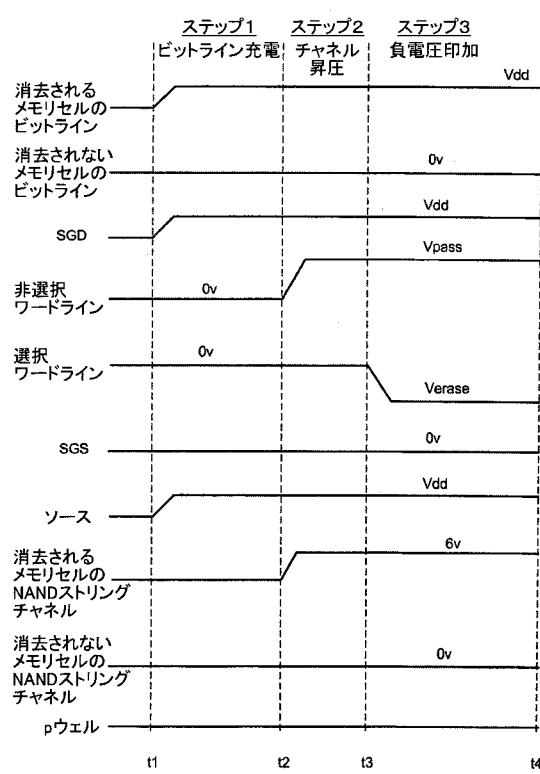

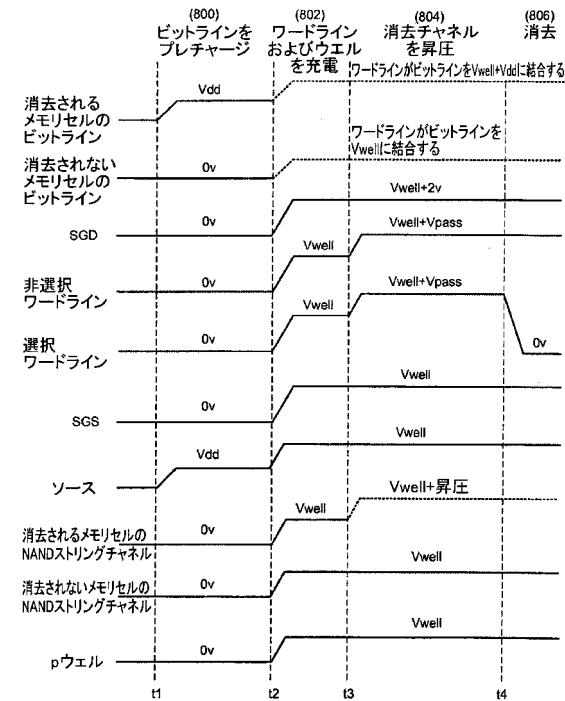

#### 【0060】

図10は、図9のステップ656の選択的消去処理を表わすタイミング図である。図10は、選択的に消去されるメモリセルに接続されたビットライン、消去されないメモリセルに接続されたビットライン、SGD、非選択ワードライン、選択ワードライン、SGS、ソースライン、選択的に消去されているメモリセルを有するNANDストリングのチャネル、選択的に消去されていないメモリセルを有するNANDストリングのチャネル、およびpウェルに対する電圧信号を示す。図10のプロセスは、3つのステップを有する。ステップ1の間、消去されるメモリセルに接続されたビットラインは、t1において $V_{dd}$ (およそ2~2.5ボルト)に充電される。消去されないメモリセルに接続されるビットラインは、(これらのメモリセルはプログラムされているか、あるいは消去されていると考えられて消去検証処理に合格しているので)、0ボルトに保たれる。また、ソースラインおよびSGDは、t1において $V_{dd}$ まで上昇される。ワードライン、SGS、およびpウェルはすべて0ボルトに保たれる。ステップ2はNANDストリングのチャネルを昇圧することを含む。時間t2において、昇圧電圧 $V_{pass}$ が非選択ワードラインに印加される。一実施形態では、 $V_{pass}$ はおよそ10ボルトである。非選択ワードラインを(少なくとも部分的に) $V_{pass}$ まで上昇させると、消去のために選択されたメモリセルを有するNANDストリングに対して、チャネル領域が昇圧される。チャネル領域は、およそ6ボルト(または、6ボルトに近い電圧範囲)まで昇圧される。これらのNANDストリングのビットラインは $V_{dd}$ があるので、ドレイン側の選択ゲートはカットオフ状態になり、これによってチャネルを昇圧することができる。消去するために選択されるメモリセルを有しないNANDストリングは、それらのチャネルを0ボルト(または、0ボルトに近い電圧範囲)に保つことになる。ステップ3は、消去を可能にするために、負電圧を選択ワードラインに印加することを含む。たとえば、Verase(およそ-10ボルト)が、t3において選択ワードラインに印加される。選択ワードラインの負電圧および昇圧されたチャネルにおける正電圧は、選択ワードラインに接続されたメモリセルを選択的に消去する強力な電場を、昇圧されたチャネルを有するNANDストリングを作り出す。一実施形態では、消去するステップは、閾値電圧を低下させるためにフローティングゲートから電子を除去することを含む。一例では、電子がソース/ドレイン領域に移動

30

40

50

される。別の実施形態では、フローティングゲートから電子を移動するのではなく、選択ワードライン／制御ゲートの下のジャンクションでホールをフローティングゲートに注入させる、ゲート誘導ドレインリーク（GIDL）がありうる。

#### 【0061】

なお、図10のプロセスは、ステップ656が実施されるたびに実施される。一実施形態では、Vpassの値は、ステップ656を反復するたびに増分されうる。

#### 【0062】

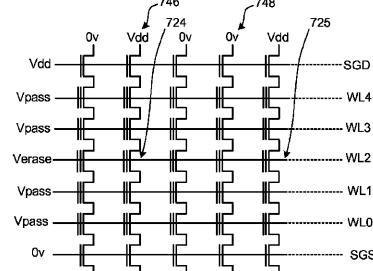

図11は、図10のステップ3の間の1組のNANDストリングを示す。図から分かるように、選択ワードライン（WL2）はVeraseを受け、非選択ワードラインはVpassを受ける。この例では、メモリセル724および725は、消去のために選択される。メモリセル724および725は、いずれも共通ワードラインWL2に接続される。図示のように、選択されないメモリセルも共通ワードラインに接続される。消去されるメモリセルを含むNANDストリングのビットラインは、Vddを受ける。たとえば、メモリセル724を含むNANDストリング746のビットラインは、Vddを受けている。消去されているメモリセルを有しないNANDストリング（たとえば、NANDストリング748）のビットラインは、0ボルトを受ける。Vddを受けるビットラインを有するこれらのNANDストリングのみが、昇圧されたチャネルを有する。0ボルトを受けるビットラインを有するNANDストリングは、昇圧されたチャネルを有しない。なお、図11に示されるNANDストリングは、すべて同じ基板領域（たとえば、同じpウェル）内にある。

10

20

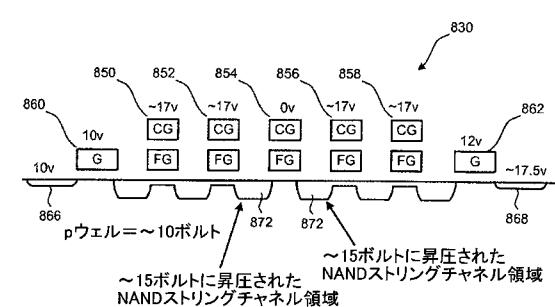

#### 【0063】

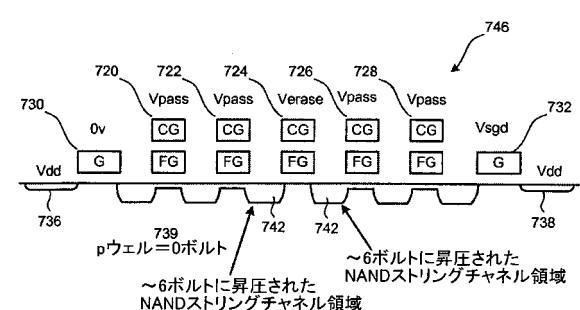

図12Aに、図10に示される消去処理のステップ3の間のNANDストリング746（消去されるメモリセルを有するNANDストリング）の断面を示す。図12Bに、図10に示される消去処理のステップ3の間のNANDストリング748（消去されるメモリセルを有しないNANDストリング）の断面を示す。図12AのNANDストリング746は、5つのメモリセル720、722、724、726、および728を含んでいる。また、NANDストリング746は、ソース側選択ゲート730、ドレイン側選択ゲート732、ソースライン736、およびビットライン738を含んでいる。図から分かるように、メモリセル720、722、726、および728は、それぞれのワードラインを介して、それらの制御ゲートでVpassを受ける。消去のために選択されるメモリセル724は、Veraseを受ける。ソース側選択ゲート730は0ボルトを受ける。ソースライン736はVddを受け、ビットライン738はVddを受ける。NANDストリング746の様々なメモリセルのソース／ドレイン領域とフローティングゲートの下（メモリセル724のフローティングゲートの下を除く）の反転層とは、NANDストリング746のチャネル領域742と呼ばれる等電位領域を形成する。図12Aに示されるこのチャネル領域742は、6ボルトに昇圧される。昇圧されたチャネル領域742は、pウェル領域739の最上部に図示される。メモリセル724のフローティングゲート下方のチャネル領域の昇圧領域には、ギャップがある。

30

#### 【0064】

図12Bは、消去のために選択されたメモリセルを含まないNANDストリング748（図11参照）を示す。NANDストリング748は、メモリセル750、752、754、756、および758を含む。また、NANDストリング748は、ソース側選択ゲート760、ドレイン側選択ゲート762、ソースライン736、ビットライン764、およびソース／ドレイン領域770を含む。図から分かるように、ビットライン764はドレイン側選択ゲート762のカットオフを阻止する0ボルトを受ける。したがって、NANDストリングのチャネル領域は、図12Aに示されるように昇圧しない。図11、12A、および12Bは、共通ワードラインに接続された他のメモリセルが消去されない一方で、同じワードラインに接続されたいくつかのメモリセルが、消去のためにどのように選択されうるかを示している。

40

#### 【0065】

50

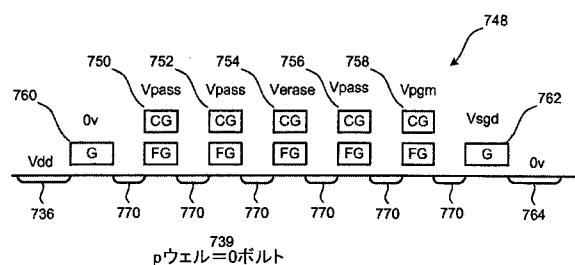

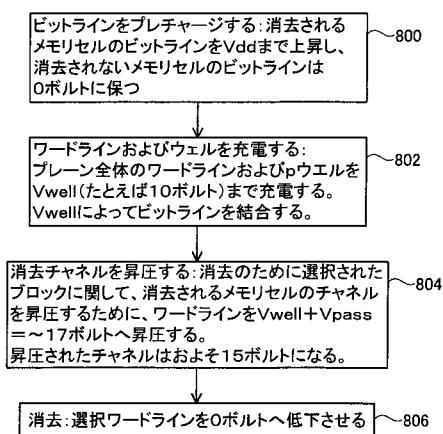

いくつかの実施形態では、負のワードライン電圧を使用するために、行デコーダのためのトリプルウェル構造と、電圧を供給するための負のポンプを必要とする。場合によっては、このような配置はコストが高くなる可能性がある。図13は、ワードラインに接続されたメモリセルの部分集合に対して選択的消去処理を実施するプロセスの、別の実施形態を表わすフローチャートである。図9のステップ656の間に実施されうる図13のプロセスは、4つのステップを含む。ステップ800において、消去されるメモリセルのビットラインはVddまで充電され、消去されないメモリセルのビットラインは0ボルトに保たれる。ステップ802において、pウェルおよびプレーン全体のすべてのワードラインが、電圧Vwell（たとえば、およそ10ボルト）まで充電される。これは、電圧Vwe11によって、ビットラインを結合する。Vddまで充電されたビットラインは、0ボルトのビットラインに比べたときの電圧差を維持する。pウェル充電は、ビットラインジャンクションの順方向バイアスを阻止するために、ダイオードドロップ（またはダイオードドロップよりも大きい電圧降下）によって、（ワードラインに比べて）相殺されうる。ステップ804において、消去のために選択されたメモリセルのロックのワードラインは、消去されるメモリセルを有するNANDストリングのチャネルを昇圧するために、Vwell+Vpass（およそ17ボルト）まで充電される。昇圧されたチャネルは、およそ15ボルトにある。ステップ806において、選択されたメモリセルは、選択ワードラインを0ボルトに低下させることによって消去される。

10

#### 【0066】

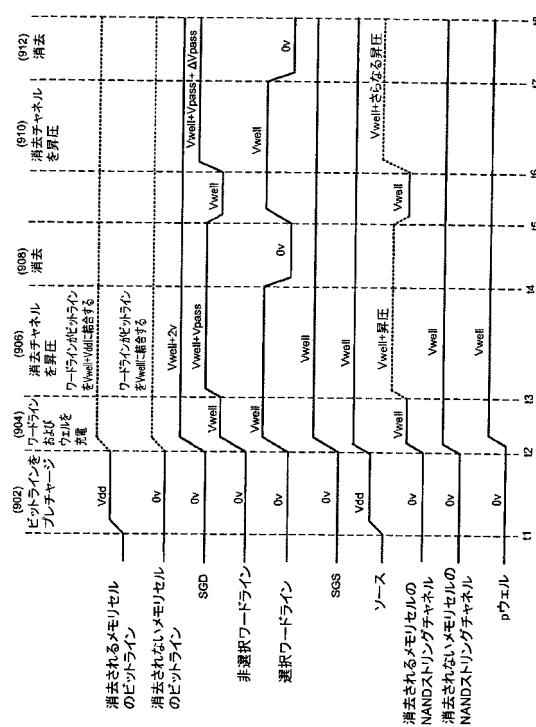

図14は、図13のプロセスのさらなる詳細を示すタイミング図である。図14は図13と同じ4つのステップを示す。第1のステップ（ビットラインをプレチャージする - ステップ800）において、消去されるメモリセルのビットラインはVddまで上昇され、共通ソースラインはVddまで上昇され、消去されるメモリセルを有するNANDストリングに接続されないビットラインは0ボルトに保たれ、図14に示される他のすべての信号も0ボルトに保たれる。

20

#### 【0067】

第2のステップ（ワードラインおよびウェルを充電する - ステップ802）において、非選択および選択ワードラインが、時間t2において0ボルトからVwell1まで充電される。さらに、t2において、SGDが0ボルトからVwell1+2ボルトまで上昇され、SGSが0ボルトからVwell1まで上昇される。ワードラインをVwell1まで上昇させることによって、ビットラインが、消去されるメモリセルと関連するビットラインについてはVwell1+Vdd（およそ10ボルト）に結合する。消去されるメモリセルに関係しない残りのビットラインは、Vwell1のままである。t2において、pウェルはVwell1まで上昇され、これによってNANDストリングのチャネルがVwell1まで上昇される。

30

#### 【0068】

第3のステップ（消去チャネルを昇圧する - ステップ804）において、ロック全体の非選択および選択ワードラインが、時間t3においてVwell1+Vpass（およそ17ボルト）まで上昇される。これによって、消去されるメモリセルのNANDストリングのチャネル領域が（少なくとも部分的に）Vwell1+昇圧電圧（たとえば、およそ15ボルト）、またはそのレベルに近い電圧範囲まで昇圧される。この昇圧は、選択されたメモリセルのビットラインがVwell1+Vddにあることに起因して、ドレイン側選択ゲートがカットオフであるために生じる。選択されないメモリセルのビットラインはわずかVwell1にあるので、これらのドレイン側選択ゲートはカットオフされない。そして、消去されないメモリセルのNANDストリングチャネルは、Vwell1+昇圧電圧まで昇圧されずに、Vwell1またはそのレベルに近い電圧範囲に留まる。

40

#### 【0069】

第4のステップにおいて、時間t4において、選択ワードラインの電圧が、消去が可能な0ボルトに低下される。消去のために選択されるメモリセルは、制御ゲートおよびチャネルの全域で15ボルトを有しており、消去に適した条件を備える。同じNANDストリ

50

ング内の選択されないメモリセルは、ワードラインで17ボルト、チャネルで15ボルトを有しており、消去に適した条件を備えていない。同じ選択ワードラインで選択されないメモリセルは、制御ゲートで0ボルト、チャネルで10ボルトを有しており、消去に適した条件を備えていない。一実施形態では、消去は、フローティングゲートから電子を除去して閾値電圧を低下させることを含む。一例では、電子はチャネル領域に移動される。

#### 【0070】

別の実施形態では、フローティングゲートから電子を移動させるのではなく、フローティングゲートにホールを注入させるために、選択ワードライン／制御ゲートの下のジャンクションでのゲート誘導ドレインリーク（GIDL）がありうる。

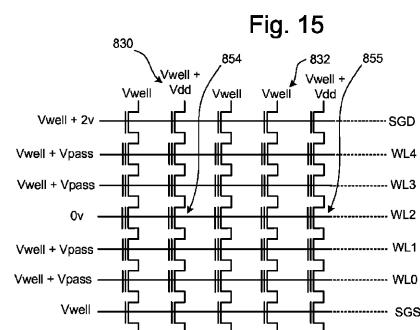

#### 【0071】

図15は、図13のステップ806の間の1組のNANDストリング例を示す。ここでは、（NANDストリング830の）メモリセル854およびメモリセル855が、消去のために選択される。図15は選択的に消去されている2つのメモリセルを示しているだけであるが、他の例では、同じ共通の選択ワードライン（WL2）に接続されているメモリセルの大部分が、消去のために選択されることがある。選択的消去では、選択ワードラインに接続された全メモリの一部が、消去のために選択されうる。図から分かるように、消去されるメモリセルを有するNANDストリング（たとえば、NANDストリング830）のビットラインはV<sub>w</sub>e11+V<sub>d</sub>dにあるが、消去されるメモリセルを有しない他のNANDストリング（たとえば、NANDストリング832）は、ビットラインがV<sub>w</sub>e11にある。選択ワードラインは0ボルトを受けるが、非選択ワードラインはV<sub>w</sub>e11+V<sub>p</sub>a<sub>s</sub>sを受ける。なお、図15に示されたNANDストリングは、すべて同じ基板領域（それゆえ、同じpウェル）内にある。

10

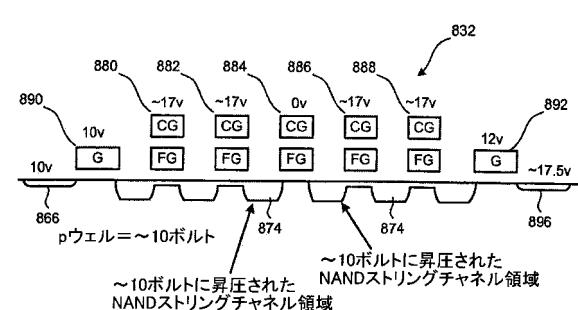

#### 【0072】

図16Aは、図13のステップ806の間のNANDストリング830（消去されるメモリセルを有するNANDストリング）の断面を示す。NANDストリング830は、メモリセル850、852、854、856、および858を含む。また、NANDストリング830は、ソース側選択ゲート860、ドレイン側選択ゲート862、ソースライン866、およびビットライン868を含む。図16Aには昇圧されるチャネル領域872が示されており、このチャネル領域はほぼ15ボルトに昇圧される。

20

#### 【0073】

図16Bは、図13のステップ806の間のNANDストリング832（消去されるメモリセルを有しないNANDストリング）の断面を示す。NANDストリング832は、メモリセル880、882、884、886、および888を含む。また、NANDストリング832は、ソース側選択ゲート890、ドレイン側選択ゲート892、共通ソース側ライン866、およびビットライン896を含む。NANDストリング832は、昇圧されたチャネル領域874を含む。しかしながら、この昇圧されたチャネル領域は、前述のように、およそ10ボルトまで昇圧されるだけであり、したがって、消去が意図的に行われない。

30

#### 【0074】

図9に戻ると、ステップ656は、消去のために選択されるメモリセルに対する、1つまたは複数の消去処理を実施するステップを含んでいる。図10および14の実施形態では、1つの消去処理が、ステップ656の各反復の間に選択されたメモリセルに対して実施される。他の実施形態では、複数の消去処理が、（介入検証処理を実施するか否かにかかわらず、）ステップ656の各反復において実施されうる。さらに、図13および14に示される第4のステップ処理の一変形形態では、ビットライン（800）をプレチャージすることと、ワードライン（802）を一度だけ充電することと、さらにチャネルの昇圧（804）と消去（806）を複数回反復することとを含みうる。

40

#### 【0075】

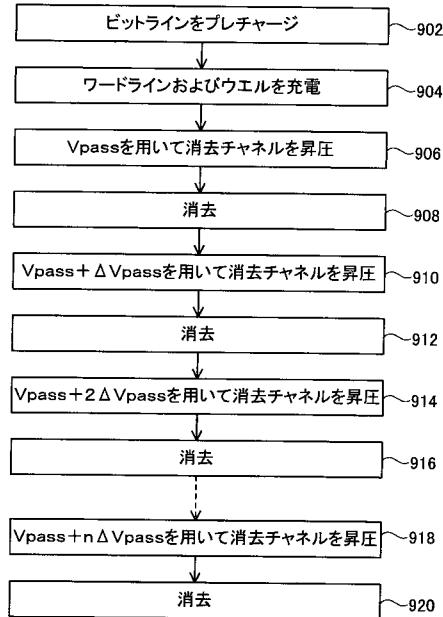

図17は、複数の消去処理を実施する一方で、ビットラインをプレチャージしワードラインを一度だけ充電するプロセスの一実施形態を表わすフローチャートである。図17の

50

ステップ902において、ビットラインは、図13のステップ800で実施されるように充電される。ステップ904において、ワードラインおよびウェルが、図13のステップ802で実施されるように充電される。図17のステップ906において、上昇されたチャネルが図13のステップ804で実施されるように昇圧される。なお、非選択ワードラインは、ステップ906でVpassを受ける。ステップ908において、選択ワードラインは0ボルトまで低下され、電子がフローティングゲートから除去される。ステップ910において、消去チャネルは再び昇圧される。ステップ910は図13のステップ804に似ている。しかしながら、非選択ワードラインおよび選択ワードラインは、Vwell+Vpass+Vpassを受ける。一例では、Vpassは0.2~0.5ボルトのいずれでもありうる。ステップ912において、選択ワードラインは0ボルトに低下される。そして、電子がフローティングゲートから排出されるにつれて、メモリセルが消去される。ステップ912は、ステップ806と同様である。ステップ914において、(ステップ804と同様にして)消去チャネルは昇圧される。しかしながら、ワードラインはVwell+Vpass+2Vpassを受ける。以後の反復では、3Vpass、4Vpassなどが使用される。ステップ916において、選択ワードラインは0ボルトに低下される。そして、ステップ806と同様に、電子がフローティングゲートから排出されるにつれて、選択されたメモリセルが消去される。昇圧および消去は、それぞれステップ918および920まで反復される。図17のプロセスは、ビットラインをプレチャージして(ステップ902)ワードラインを一度充電した(904)後、ビットラインのプレチャージとワードラインの充電とを再びしなくとも、消去チャネルの昇圧および消去処理が複数回反復されることを示す。消去チャネルの昇圧および消去処理の反復は、2度またはそれ以上行われうる。必要とされる具体的な反復回数はない。

【 0 0 7 6 】

図18は、図17のステップ902～912を図示するタイミング図である。当業者は、図17の他のステップを外挿して実施するための、図18の教示の利用法が分かるであろう。図18から分かるように、消去されるメモリセルのビットラインは、最初にt1において、Vddでプレチャージされる(902)。消去されるメモリセルのビットラインは、t2においてVwell+Vddに結合して(904)、t8までそのレベルに留まる。消去されないメモリセルのビットラインは、t2においてVwellに結合して、t8までそこに留まる。SGDは、t2において0ボルトからVwell+2V(またはVdd)に上昇されて、t8までそこに留まる。非選択ワードラインは、t2において0ボルトからVwellに上昇され、さらにt3においてVwell+Vpassに上昇される(906)。ステップ908の後、非選択ワードラインは、回復段階の一部としてt5においてVwellに低下される。ステップ910において、チャネルの昇圧が再び実施されると、非選択ワードラインは、前述のように、Vwell+Vpass+Vpassまで上昇される。図17のプロセスの以後の反復では、非選択ワードラインが、Vwell+Vpass+nVpassまで上昇する。選択ワードラインは、t2においてVwellまで上昇され(904)、この後、t4において消去電圧0ボルトまで低下される(908)。t5における回復段階中の、消去と次の昇圧の間に、選択ワードラインは再びVwellまで上昇される。選択ワードラインは、t7において0ボルトに低下されて、選択的消去が可能となる(912)。このプロセスは、消去チャネル昇圧段階で選択ワードラインをVwellまで上昇し続けて、その後、消去処理を終了させるために、選択ワードラインを0ボルトまで低下させる。SGSは、時間t2において0ボルトからVwellに上昇され、t8までそこに留まる。共通ソースラインは、t1においてVddまで上昇され、この後、t2においてVwellまで上昇され、t8までそこに留まる。pウェルは、t2においてVwellまで上昇され、t8までそこに留まる。pウェルをt2においてVwellまで上昇させた結果として、すべてのNANDストリングのチャネルも、t2においてVwellまで上昇される(904)。消去されていると考えられるNANDストリングのチャネルは、t3においてVwell+昇圧電圧まで昇圧され(906)、t5においてVwellまで低下され、この後、t6においてVwell+

さらなる昇圧レベルまで上昇される(910)。このチャネルは、図17のプロセスの間、Vw e l lとVw e l l + 昇圧を切り換え続ける。

#### 【0077】

一実施形態では、選択的消去は、雑段階とファイン段階を含む2つの(またはそれ以上の)段階的な消去処理の一部として実施されうる。雑段階の間、図17のプロセスは、消去処理間に検証を行うことなく、2回またはそれ以上の消去処理の実施に付随して実施される。消去処理の所定回数の後、雑段階が終了される。その後、ファイン段階が図9のプロセスを実施することによって開始される。そして、ステップ656を実施するために、図14のプロセスが使用される。雑段階は、高速で消去するが精度が低い。ファイン段階は、低速で消去するが精度が高い。

10

#### 【0078】

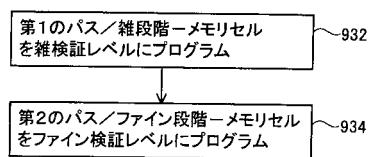

プログラミング中において、プログラム処理の速度を不当に落とすことなく、狭い閾値電圧区分を実現するための1つのソリューションは、2つの(またはそれ以上の)パスプログラム処理を採用することである。第1のパス、雑プログラミング段階は、狭い閾値電圧区分を実現することにさほど注意を払わずに、高速で閾値電圧を上昇させる試行を含んでいる。第2のパス、ファインプログラミング段階は、より狭い閾値電圧区分を実現しながら目標閾値電圧に達するために、閾値電圧を低速で上昇させようとする。

#### 【0079】

図19は、2パスプログラム処理の一実施形態を表わすフローチャートである。ステップ932において、第1のパスが実施される。一実施形態では、第1のパスは雑プログラミング段階である。選択されたメモリセルは、1つまたは複数の雑検証レベルにプログラムされる。選択されたメモリセルのすべてが、それぞれの雑検証レベルに達した時点で、雑プログラミング段階が終了する。ステップ934において、第2のパスが実施される。一実施形態では、第2のパスは、雑プログラミング段階が終了した後に実施されるファインプログラミング段階である。選択されたメモリセルは、1つまたは複数のファイン検証レベルにプログラムされる。選択されたメモリセルのすべてが、それぞれのファイン検証レベルに達した時点で、ファインプログラミング段階が終了する。いくつかの実施形態では、ワードラインに印加されるプログラムパルスが、ファイン段階に比べて、雑段階では大きさが長いあるいは高い。他の実施形態では、雑段階のビットライン電圧が0ボルトであり、ファイン段階のビットライン電圧が0ボルトとVddの間のレベル(たとえば、約1ボルト)にある。また、雑/ファインプログラミング方法の様々な代替形態および実施形態が採用されうる。いくつかの実施形態では、複数の雑段階および/または複数のファイン段階がありうる。雑/ファインとは異なるプロセスを含み、かつ、2パスよりも多くのパスを有するプロセスを含む、他の種類のマルチパスプログラム処理も採用されうる。

20

#### 【0080】

図20は、データ状態S0、S1、S2、およびS3と関連している、1組の閾値電圧区分を示す。各データ状態に対して、雑検証レベル(Vvc)が示されるとともに、ファインレベル(Vvf)が示されている。たとえば、データ状態S1にプログラムされているメモリセルの雑段階の間では、検証レベルはVvc1とされる。そしてファイン段階の間では、メモリセルはVvf1と対照して検証される。データ状態S2にプログラムされるメモリセルは、雑段階の間ではVvc2と対照して検証され、ファイン段階の間ではVvf2と対照して検証される。状態S3にプログラムされるメモリセルは、雑段階の間ではVvc3と対照して検証され、ファイン段階の間ではVvf3と対照して検証される。

30

#### 【0081】

前述の図7に示された処理の方法では、メモリセルがプログラムされ、プログラミングの終了後に選択的消去処理が実施される実施形態を予期している。別の実施形態では、プログラム処理および選択的消去処理が混在した状況で実施されうる。たとえば、選択的消去は、プログラミングの雑段階の後、プログラミングのファイン段階の前に実施されうる。別の実施形態では、選択的消去はいくつかのデータのプログラミングの後、他のデータ

40

50

のプログラミングの前に実施されうる。

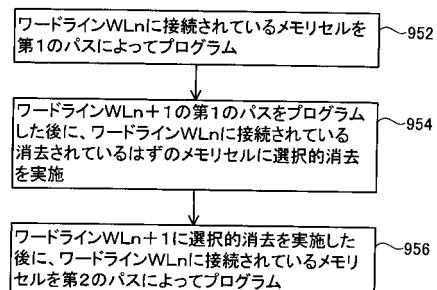

#### 【0082】

図21は、2バスプログラム処理および選択的消去処理が混在する一実施形態を表わすフローチャートである。一実施形態では、2バスプログラム処理は、第1のバスが雑段階であり、第2のバスがファイン段階である雑／ファインプログラム処理である。他の2バスプログラム処理も採用されうる。図21の実施形態では、選択的消去処理は、閾値電圧が間違って移動してしまったメモリセルを再消去するために、第1のバスと第2のバスの間に実施される。この実施形態では、選択的消去処理は、隣接するワードラインが2バスプログラム処理の第1のバスに従ってプログラムされた後にも、実施される。処理のこの順番は、隣接するメモリセルからの結合の影響を減らすことになる。

10

#### 【0083】

図21は、ワードラインWL<sub>n</sub>のメモリセルの視点から、プロセスを説明している。図21のステップ952において、ワードラインWL<sub>n</sub>に接続されたメモリセルは、2バスプログラム処理の第1のバス（たとえば、雑段階）に従ってプログラムされる。ステップ954において、メモリラインWL<sub>n</sub>に接続されたメモリセルは、消去されているはずであるが、消去閾値区分よりも高く上昇された閾値電圧を有しているメモリセルを再消去するために、前述の選択的消去処理を施される。ステップ954は、図9の処理を実施するステップを含んでいる。しかしながら、ステップ954のプロセスは、隣接するワードラインWL<sub>n+1</sub>に接続されたメモリセルに対して2バスプログラム処理の第1のバスをプログラムした後に、実施される。それゆえ、ステップ952がワードラインWL<sub>1</sub>のメモリセルをプログラムするステップを含む場合、ステップ954の選択的消去は、ワードラインWL<sub>2</sub>のメモリセルに対して雑段階を行なった後に実施される。ステップ956において、2バスプログラム処理の第2のバスは、ワードラインWL<sub>n+1</sub>に対して選択的消去処理を実施した後に、WL<sub>n</sub>に接続されたメモリセルに対して実施される。一実施形態では、図21のプロセスは、ブロック内のすべてのワードラインに対して実施される。他の実施形態では、プロセスはワードラインの部分集合のみに対して実施されうる。

20

#### 【0084】

図22は、2バスプログラム処理の第1のバス、2バスプログラム処理の第2のバス、および5本のワードラインのメモリセルに対する選択的消去処理のプログラミングの順序を示す表である。最初に、WL<sub>0</sub>に対して第1のプログラミングバスが実施される。その後に、WL<sub>1</sub>に対して第1のプログラミングバスが実施される。これに、ワードラインWL<sub>0</sub>に対する選択的消去処理が続く。これに、ワードラインWL<sub>2</sub>に対する第1のプログラミングバスが続く。これに、ワードラインWL<sub>1</sub>に対する選択的消去処理が続く。これに、WL<sub>0</sub>に対する第2のプログラミングバスが続く。これに、WL<sub>3</sub>に対する第1のプログラミングバスが続く。これに、ワードラインWL<sub>2</sub>に対する選択的消去処理が続く。これに、WL<sub>1</sub>に対する第2のプログラミングバスが続く。これに、WL<sub>4</sub>に対する第1のプログラミングバスが続く。これに、ワードラインWL<sub>3</sub>に対する選択的消去処理が続く。これに、WL<sub>2</sub>に対する第2のプログラミングバスが続く、といった具合である。図22に示された処理の順序は、5本を超えるワードラインに対しても拡張して適用しうる。

30

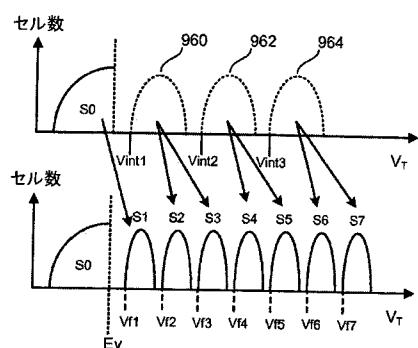

#### 【0085】

図23は、図21および22に従ったプログラム処理に由来する、1組の閾値電圧区分を示す。状態S0、S1、S2、およびS3（ファイン段階後の最終閾値電圧区分を表わす）が示される。状態S1、S2、およびS3の各々の後ろには、雑段階後の対応する閾値電圧区分を表わす点線の閾値電圧区分がある。図から分かるように、最終区分（ファイン段階に由来する）は、雑段階後の閾値電圧区分に比して、非常に狭く、わずかに高い。

#### 【0086】

別の実施形態では、図21および22の2バスプログラミング技術が、データを8つのデータ状態S0～S7にプログラムするために使用されうる。第1のバスの間ににおいて、メモリセルは、検証点Vint1、Vint2、およびVint3の各々を用いて、閾値

40

50

電圧区分 960、962、および 964 にプログラムされる。プログラム処理の第 2 のパスの間ににおいて、メモリセルは、2 つの可能なデータ状態の 1 つに移動されうる。データ状態 S0 にあるメモリセルは、S0 に留まるか、あるいは検証点 Vf1 を用いてデータ状態 S1 にプログラムされるか、のいずれの可能性もある。閾値電圧区分 960 内のメモリセルは、検証点 Vf2 および Vf3 の各々を用いて、データ状態 S2 またはデータ状態 S3 のいずれかにプログラムされうる。閾値電圧区分 962 内のメモリセルは、検証点 Vf4 および Vf5 の各々を用いて、データ状態 S4 またはデータ状態 S5 のいずれかにプログラムされうる。閾値電圧区分 964 内のメモリセルは、検証点 Vf6 および Vf7 の各々を用いて、データ状態 S6 またはデータ状態 S7 のいずれかにプログラムされうる。第 1 のパスの後、第 2 のパスの前ににおいて、選択的消去処理が、図 21 および / または 22 に關して前述したように実施される。10

#### 【0087】

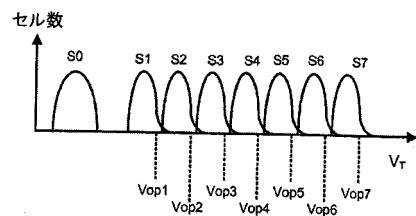

メモリセルがプログラムされるとき、これらのセルが单一パス、複数パスのプログラム処理のいずれを使用するかにかかわらず、いくつかのメモリセルがオーバープログラムされた状態になりうる。たとえば、データ状態 S2 にプログラムするよう意図されているメモリセルは、状態 S2 に対する閾値電圧区分よりも大きいレベルに、その閾値電圧が上昇されることがありうる。図 25 は、いくつかのオーバープログラムされたメモリセルを有する、1 組の閾値電圧区分を示す。図から分かるように、データ状態 S1 ~ S7 は、これらの閾値電圧の右側にテール (tail) を有する。これらのテールは、オーバープログラムされたメモリセルを表わす。さらに、図 25 のグラフに示されるのは、オーバープログラムされた検証点 (Vop1、Vop2、Vop3、Vop4、Vop5、Vop6、および Vop7) である。関連するオーバープログラミング検証点よりも大きい閾値電圧を有する特定閾値電圧区分内にあるこれらのメモリセルは、オーバープログラムされていると考えられる。20

#### 【0088】

いくつかのデバイスでは、比較的低いデータ状態（たとえば、S1、S2、S3）で、高位の状態よりも多くのオーバープログラミングが起きる。いくつかのデバイスでは、高位の状態でオーバープログラミングが起きない。

#### 【0089】

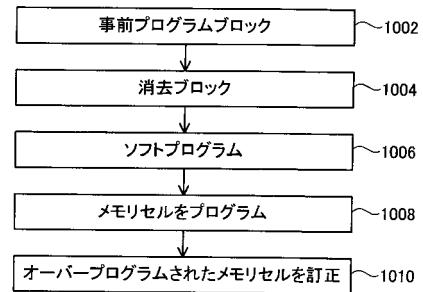

一実施形態では、図 10 ~ 18 に關して前述した選択的消去処理は、オーバープログラムされたメモリセルを訂正するために使用されうる。図 26A および 26B は、オーバープログラムされたメモリセルを訂正するために前述の選択的消去方法を用いる、2 つのプロセスの例を示す。30

#### 【0090】

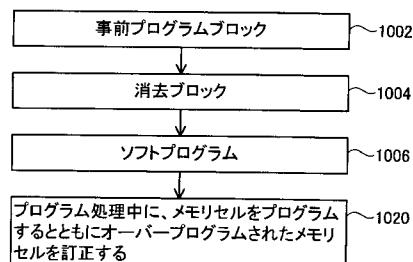

図 26A のステップ 1002 において、メモリセルが事前プログラムされる（図 7 のステップ 550 と同様に）。ステップ 1004 において、メモリセルのブロック（または他の単位）が消去される（図 7 のステップ 552 と同様に）。ステップ 1006 において、メモリセルは、オプションとしてソフトプログラムされてもよい（図 7 のステップ 554 と同様に）。ステップ 1008 において、メモリセルは、当技術分野で周知の種々の適切なプログラム処理のいずれかを用いてプログラムされる。ステップ 1010 において、オーバープログラムされたメモリセルが訂正される。それゆえ、26A のプロセスは、ステップ 1008 のプログラミングを終了した後で、オーバープログラムされたメモリセルを訂正する。40

#### 【0091】

図 26B のプロセスは、プログラム処理の間に、メモリセルのプログラミングとオーバープログラムされたメモリセルの訂正が混在する。ステップ 1002 において、メモリセルのブロックは事前プログラムされる。ステップ 1004 において、メモリセルのブロック（または他の単位）は消去される。ステップ 1006 において、メモリセルは、オプションとしてソフトプログラムされる。ステップ 1020 において、メモリセルがプログラムされる。そして、プログラミングと選択的消去が混在した状況で実施され、オーバープ50

ログラムされたメモリセルは、選択的消去処理を用いて訂正される。さらなる詳細を以下で説明する。

#### 【0092】

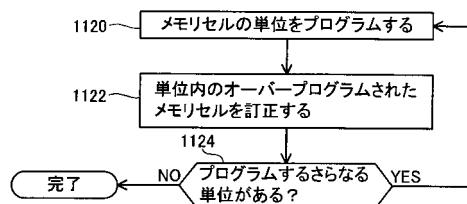

図27は、オーバープログラムされたメモリセルを訂正する一実装形態を表わすフローチャートである。一実施形態では、図27の方法がデータ状態ずつ実施される。たとえば、図27の方法は、S1に対して実施されうる。その後、図27の方法は、S2に対して実施され、以下同様である。ステップ1100において、システムは、意図したデータ状態にプログラムされているはずのメモリセルを識別する。前述のように、この情報は、コントローラからの情報を得ること、バッファ（RAMまたは不揮発性メモリ）から情報を得ること、あるいはデータラッチ494から情報を得ることによって取得することができる。ステップ1102において、検討中のデータ状態に関連する適切なオーバープログラムされた検証レベル（たとえば、Vop1、Vop2、Vop3、Vop4、Vop5、Vop6、およびVop7）を用いて、検証処理が実施される。たとえば、図12のプロセスがデータ状態S1に対して実施されている場合、ステップ1102の検証処理は、Vop1を用いて実施される。Vop1の電圧は、メモリセルの制御ゲートに（ワードラインを介して）印加され、これらのメモリセルがデータ状態1に対してオーバープログラムされているか否かが判定される。すべてのメモリセルがオーバープログラムされておらず、かつすべてが正しく検証されると（ステップ1104）、図27のプロセスが終了する。あるいは、十分な数のメモリセルが正しく検証されると、プロセスは終了しているとみなされうる。すべてのメモリセルが正しく検証されなければ（ステップ1104）、ステップ1102において検証されなかったこれらのメモリセルに、選択的消去処理が実施される。この選択的消去処理は、1つまたは複数の消去処理が施されてメモリセルの閾値電圧が下げられ、閾値電圧が適切なオーバープログラムされた検証レベルよりも低くなるように、実施される。図10～18のプロセスは、ステップ1106を実施するために採用されうる。ステップ1108において、昇圧電圧（Vpass）は、ステップ1102～1108の次の反復に対して増分され、プロセスはステップ1102にループバックして検証処理が実施される。ループ1102～1108は、すべてのメモリセルまたは所定数のメモリセルが良好に検証されるまで反復される。メモリセルは、ステップ1102において検証されると、以後の消去から除外される。

#### 【0093】

一実装形態において、図27のプロセスは、図26Aのステップ1010の間に実施される。一実施形態では、図27のプロセスは、各プログラム状態に対して別々に実施される。7つのプログラム状態（S1～S7）がある場合には、図27のプロセスが、図26Aのステップ1010の間に7回実施される。そして、3つのプログラム状態（S1～S3）がある場合には、図27のプロセスが、図26Aのステップ1010の間に3回実施される。別の実施形態では、図27のプロセスは、以下のように、すべてのデータ状態に対して同時に実施されうる：ステップ1100が各メモリセルのあるべきデータ状態を識別し、ステップ1102が各データ状態に対して検証処理を実施するステップを備え、オーカルプロセッサ482が検証処理を追跡して結果を記憶する。このように、図27のプロセスは一度だけ実施されうる。

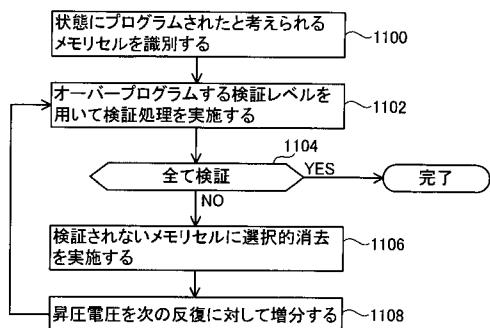

#### 【0094】

図28は、図26Bのステップ1020の実装形態の一例を示す。ステップ1120において、1単位のメモリセルがプログラムされる。プログラミングは、メモリセル当たり1ビットのデータ、メモリセル当たり2ビットのデータ、メモリセル当たり3ビットのデータなどをプログラムすることを含みうる。一実施形態では、1単位のメモリセルは、共通ワードラインに接続されたすべてのメモリセル、ページ内のすべてのメモリセル、セクタ内のすべてのメモリセル、または他の単位でありうる。ステップ1122において、システムは、ステップ1120の最新の反復においてプログラムされたメモリセルの単位の、オーバープログラムされたメモリセルを訂正する。ステップ1122は、図27のプロセスを用いて実施されうる。たとえば、ステップ1122は、各データ状態に対して図2

7のプロセスを一度実施することを含みうる。あるいは、ステップ1122は、前述のように、すべてのデータ状態に対して図27のプロセスを同時に一度実施することを含みうる。ステップ1124において、プログラムすべき単位が他にあるか否かが判定される。なければ、プロセスは終了する。プログラムすべき単位が他にあれば、図28の方法がステップ1120にループバックして、次の単位のメモリセルをプログラムし、この後、ステップ1122において、その単位のメモリセルに対してオーバープログラムされたメモリセルを訂正する。ステップ1120および1122の反復は、プログラムされる必要のあるすべての単位のメモリセルに対して行なわれる。

#### 【0095】

いくつかの実施形態では、オーバープログラミングは低位状態に対して比較的大きい問題であり、したがって、システムは低位状態に対するオーバープログラミングのみを訂正する。

#### 【0096】

いくつかの実施形態では、選択的消去処理は、選択的消去の各反復の間に消去・検証を実施することなくオーバープログラミングを訂正するために採用されうる。たとえば、図27のステップ1106は、ステップ1102を実施することなく複数回実施されうる。1つのこのような実装形態では、図17および18のプロセスが採用される。

#### 【0097】

本発明の前記の詳細な説明は図解及び説明のために提示されたものである。本発明は、網羅的となる、あるいは本発明を開示されている正確な形式に制限することを意図していない。前記教示を鑑みて多くの変型及び変更が可能である。説明された実施形態は、本発明及びその実際的な応用を最もよく説明し、それにより当業者が多様な実施形態において、及び意図されている特定の使用に適するように多様な変型を用いて本発明を最もよく活用できるようにするために選択された。本発明の範囲がここに添付される請求項により定められることが意図される。

【図1】

Fig. 1

【図2】

10

20

【図3】

【図4】

【図5】

【図6 A】

【図6 B】

【図6 C】

【図7】

【図8】

【図9】

【図10】

【図11】

Fig. 11

【図12A】

【図12B】

【図13】

【図14】

【図15】

Fig. 15

【図16B】

【図16A】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

| ワードライン | 第1のバスのプログラム | 選択的消去 | 第2のバスのプログラム |

|--------|-------------|-------|-------------|

| 4      | 10          | 13    | 15          |

| 3      | 7           | 11    | 14          |

| 2      | 4           | 8     | 12          |

| 1      | 2           | 5     | 9           |

| 0      | 1           | 3     | 6           |

【図23】

【図24】

【図25】

【図26A】

【図26B】

【図28】

【図27】

---

フロントページの続き

(74)代理人 110000110

特許業務法人快友国際特許事務所

(72)発明者 ルツツエ ジェフリー ダブリュー.

アメリカ合衆国 95035、カリフォルニア州、ミルピタス、マッカーシー ブールバード 6

01

(72)発明者 リ ヤン

アメリカ合衆国 95035、カリフォルニア州、ミルピタス、マッカーシー ブールバード 6

01

審査官 滝谷 亮一

(56)参考文献 特開平11-176177(JP,A)

国際公開第2007/109883(WO,A1)

特開2006-190820(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 02

G 11 C 16 / 04

G 11 C 16 / 06