## AMT FÜR ERFINDUNGS- UND PATENTWESEN

In der vom Anmelder eingereichten Fassung veröffentlicht

(21) WP G 06 F / 290 513 6

(22) 23.05.86

(44) 02.09.87

(71) VEB Robotron-Elektronik Dresden, 9010 Karl-Marx-Stadt, Postfach 240, DD

(72) Matthes, Wolfgang, Dipl.-Ing., DD

(54) Speicher- und Verarbeitungseinrichtung für Ternärvektorlisten

(55) Spezialprozessor, Ternärvektoren, Boolesche Gleichungen, Umordnung von Listen.

(57) Die Erfindung ist in Spezialprozessoranordnungen anwendbar, die zur Beschleunigung von Operationen mit Booleschen Gleichungen bzw. Differentialgleichungen eingesetzt werden. Ihr Ziel ist es, Zeitverlust und Speicherplatzbedarf für die Umordnung von Ternärvektorlisten mit eingeschränkter, aber praktisch bedeutsamer Variablenzahl zu vermeiden, und es liegt die Aufgabe zugrunde, Beschleunigungs- bzw. Spezialprozessoranordnungen so auszubilden, daß das Umordnen der Listen entfallen kann. Zwischen den Datenausgängen der TVL-Speicher und den Eingängen der nachgeordneten Such- und Verknüpfungsschaltungen sind Datenaustauschschaltungen eingefügt, die aus einer Auswahlschaltung und einer Insertionsschaltung bestehen. Den Auswahlschaltungen sind Wandlungslistenspeicher vorgeschaltet, denen Sperrlemente nachgeschaltet sind, die an eine gemeinsame Erlaubnisleitung angeschlossen sind. Fig. 3

**Patentansprüche:**

1. Speicher- und Verarbeitungseinrichtung für Ternärvektorlisten, die Speichermittel für die Ternärvektorlisten selbst (TVL-Speicher) sowie für weitere Operanden, den besagten Speichermitteln nachgeordnete Such- und Verknüpfungsschaltungen sowie Adressierungs-, Steuer- und Anschlußschaltungen umfaßt, **dadurch gekennzeichnet**, daß in die Verbindungen zwischen den Datenausgängen der TVL-Speicher (1) und den Eingängen der nachgeordneten Such- und Verknüpfungsschaltungen (8) Datenaustauschschaltungen (9) eingefügt sind, die so ausgebildet sind, daß jeder Variablenposition der Such- und Verknüpfungsschaltungen (8) eine Auswahleinrichtung (10) vorgeschaltet ist, die ihrerseits an alle Variablenpositionen der Datenausgänge der TVL-Speicher (1) angeschlossen ist, daß jede Auswahleinrichtung (10) aus Auswahlschaltungen (11) sowie aus einer Insertionsschaltung (12) besteht, daß jeder Auswahleinrichtung (10) ein Wandlungslistenspeicher (13) zugeordnet ist, daß an die Datenausgänge jedes Wandlungslistenspeichers (13) die Auswahleingänge der Auswahlschaltungen (11) sowie der Erlaubniseingang der Insertionsschaltung (12) der jeweiligen Auswahleinrichtung (10) angeschlossen sind, wobei in alle besagten Verbindungen Sperrelemente (14) eingefügt sind und daß alle Sperrelemente (14) aller Wandlungslistenspeicher (13) an eine gemeinsame Erlaubnisleitung angeschlossen sind.

2. Anordnung nach Anspruch 1, **dadurch gekennzeichnet**, daß die Sperrelemente (14) als UND-Verknüpfungen ausgebildet sind.

3. Anordnung nach Anspruch 1, **dadurch gekennzeichnet**, daß jene der Sperrelemente (14), die den Auswahleingängen der Auswahlschaltungen (11) vorgeordnet sind, ihrerseits als Auswahlschaltungen ausgebildet sind, deren erste Eingänge mit einem Festwert beschaltet sind, der der jeweiligen Variablenposition entspricht, an deren zweite Eingänge die betreffenden Ausgänge des jeweiligen Wandlungslistenspeichers (13) angeschlossen sind und deren Auswahleingang mit der gemeinsamen Erlaubnisleitung beschaltet ist.

4. Anordnung nach Anspruch 1, **dadurch gekennzeichnet**, daß die TVL-Speicher (1) aus mehreren Speichermodulen (15) aufgebaut sind und daß diesen die Datenaustauschschaltungen (9) über Auswahlmittel (16) nachgeordnet sind.

5. Anordnung nach Anspruch 1, **dadurch gekennzeichnet**, daß die TVL-Speicher (1) aus mehreren Speichermodulen (15) aufgebaut sind, daß den Datenausgängen der einzelnen Speichermodulen (15) jeweils Auswahleinrichtungen (10) nachgeschaltet sind und daß alle Auswahleinrichtungen (10) in identischen Variablenpositionen über jeweils gemeinsame Sperrelemente (14) an gemeinsame Wandlungslistenspeicher (13) angeschlossen sind.

6. Anordnung nach Ansprüchen 1–5, **dadurch gekennzeichnet**, daß den Datenaustauschschaltungen (9) Deserialisierungsmittel (17) nachgeordnet sind, an die die Such- und Verknüpfungsschaltungen (8) angeschlossen sind.

Hierzu 9 Seiten Zeichnungen

**Anwendungsgebiet der technischen Lösung**

Die Erfindung betrifft eine Speicher- und Verarbeitungseinrichtung für Ternärvektorlisten, die Speichermittel für die Ternärvektorlisten selbst, für weitere Operanden, nachgeordnete Such- und Verknüpfungsschaltungen sowie Adressierungs-, Steuer- und Anschlußschaltungen umfaßt.

Sie wird im Rahmen von Spezialprozessoranordnungen eingesetzt, die zur Beschleunigung von Operationen mit Booleschen Gleichungen bzw. Differentialgleichungen und dgl. dienen.

Anwendungsgebiete sind z. B. der Entwurf digitaler Schaltungen, die Berechnung von Testbelegungen für solche Schaltungen usw.

### Charakteristik des Standes der Technik

Ternärvektorlisten haben sich als Mittel zur numerischen Behandlung von Problemen bewährt, die auf Boolesche Gleichungen zurückführbar sind. Dies ist z.B. in dem Buch von Bochmann/Zarkrevskij/Posthoff (Herausg.): Boolesche Gleichungen, Verlag Technik Berlin 1984 dargestellt. Die einschlägigen Algorithmen sind dabei als Programme für übliche Universalrechner realisiert. Da viele der zu lösenden Anwendungsaufgaben im Sinne der Komplexitätstheorie zu den besonders komplizierten gehören und somit ein starkes Bedürfnis zur Ablaufbeschleunigung besteht, wurden bereits entsprechende Schaltungsanordnungen vorgeschlagen, so z.B. in der WP-Anmeldung G06F/274367.3 „Anordnung zur Verarbeitung von Ternärvektorlisten“ oder in der WP-Anmeldung G06F/282506.4 „Spezialprozessoranordnung zur Verarbeitung von Ternärvektorlisten“. Dabei werden die typischen Such- und Verarbeitungsabläufe wesentlich beschleunigt. Zeitaufwendig bleibt jedoch weiterhin die Umordnung der Ternärvektorlisten vor Ausführung der jeweiligen Operation (die zu verknüpfenden Listen müssen die jeweils gleiche Variablenzuordnung haben). In der Anordnung gemäß der erstgenannten WP-Anmeldung muß dies auf konventionelle Weise durch Software geschehen. In der zweiten WP-Anmeldung wurden Mittel zur Beschleunigung sowohl des Umordnungsablaufs selbst (durch Organisation des Arbeitsspeichers als „aktives Memory Array“ mit horizontalen und vertikalen Zugriffsmöglichkeiten) als auch der Gewinnung der Adressenwerte für die Umordnung vorgeschlagen. Die Nachteile des Zeitverlustes für die Umordnung selbst und des Speicherplatzes für den Aufbau der umgeordneten Listen bestehen dabei weiterhin.

### Ziel der technischen Lösung

Das Ziel der Erfindung besteht darin, den Zeitverlust und Speicherplatzbedarf für die Umordnung von Ternärvektorlisten im Rahmen von Beschleunigungs- bzw. Spezialprozessoranordnungen zu vermeiden, und zwar für Listen mit eingeschränkter, aber praktisch bedeutsamer Variablenzahl.

### Darlegung des Wesens der technischen Lösung

Die Aufgabe der Erfindung besteht darin, an sich bereits vorgeschlagene Beschleunigungs- bzw. Spezialprozessoranordnungen für die Verarbeitung von Ternärvektorlisten so auszubilden, daß das Umordnen der Listen für praktisch bedeutsame Variablenzahlen entfallen kann.

Die Mängel der bekannten Lösungen haben ihre Ursache darin, daß spezifische Schaltmittel fehlen, so daß stets Zeit und Speicherplatz für das Umordnen benötigt wird.

Erfindungsgemäß wird die Aufgabe durch die in den Patentansprüchen angeführten Schaltungen gelöst.

Die Erfindung wirkt folgendermaßen:

Durch die Datenaustauschschaltungen kann jede aus dem TVL-Speichern gelesene Variable zu jeder Eingangsposition der nachgeordneten Such- und Verknüpfungsschaltungen durchgesteuert werden. Für Variablenpositionen, die in der aktuellen Quell-TVL nicht vorhanden sind, werden über die jeweiligen Insertionsschaltungen konstant Belegungen für N-Elemente abgegeben. Jede Datenaustauschschaltung hat einen ladbaren Wandlungslistenspeicher, so daß die gewünschte Umordnung für alle Variablen eines parallel verarbeitenden Abschnittes gemäß der Aufrufbreite der TVL-Speicher gleichzeitig erfolgt. Im Gegensatz zum an sich bekannten „barrel shifter“ ist dabei für jede Variablenposition eine wahlfreie Zuordnung möglich. Über die Sperrelemente in den Datenaustauschschaltungen kann die Umordnungswirkung jederzeit durch Ansteuern einer Erlaubnisleitung ein- und ausgeschaltet werden. Im letztgenannten Fall wird die Information ohne Umordnung durchgesteuert.

### Ausführungsbeispiel

Im folgenden Ausführungsbeispiel zeigen:

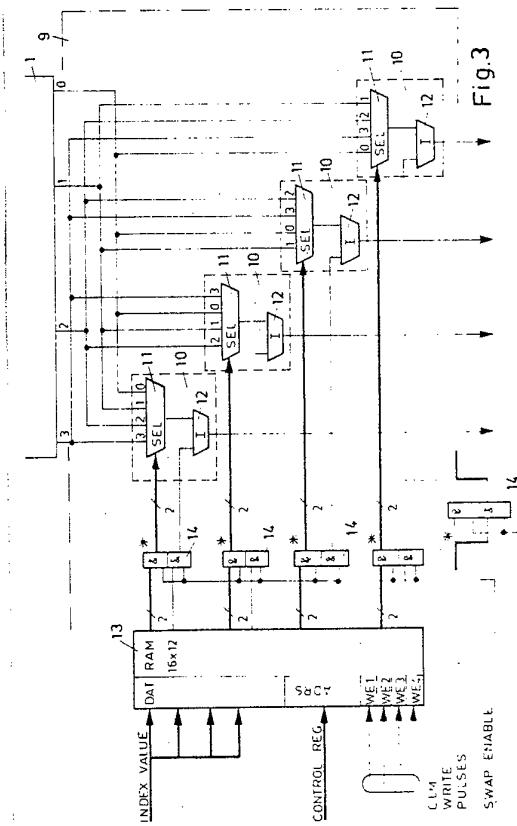

- Fig. 1 ein Blockschatzbild,

- Fig. 2 ein Beispiel für die Umordnung von Ternärvektorlisten,

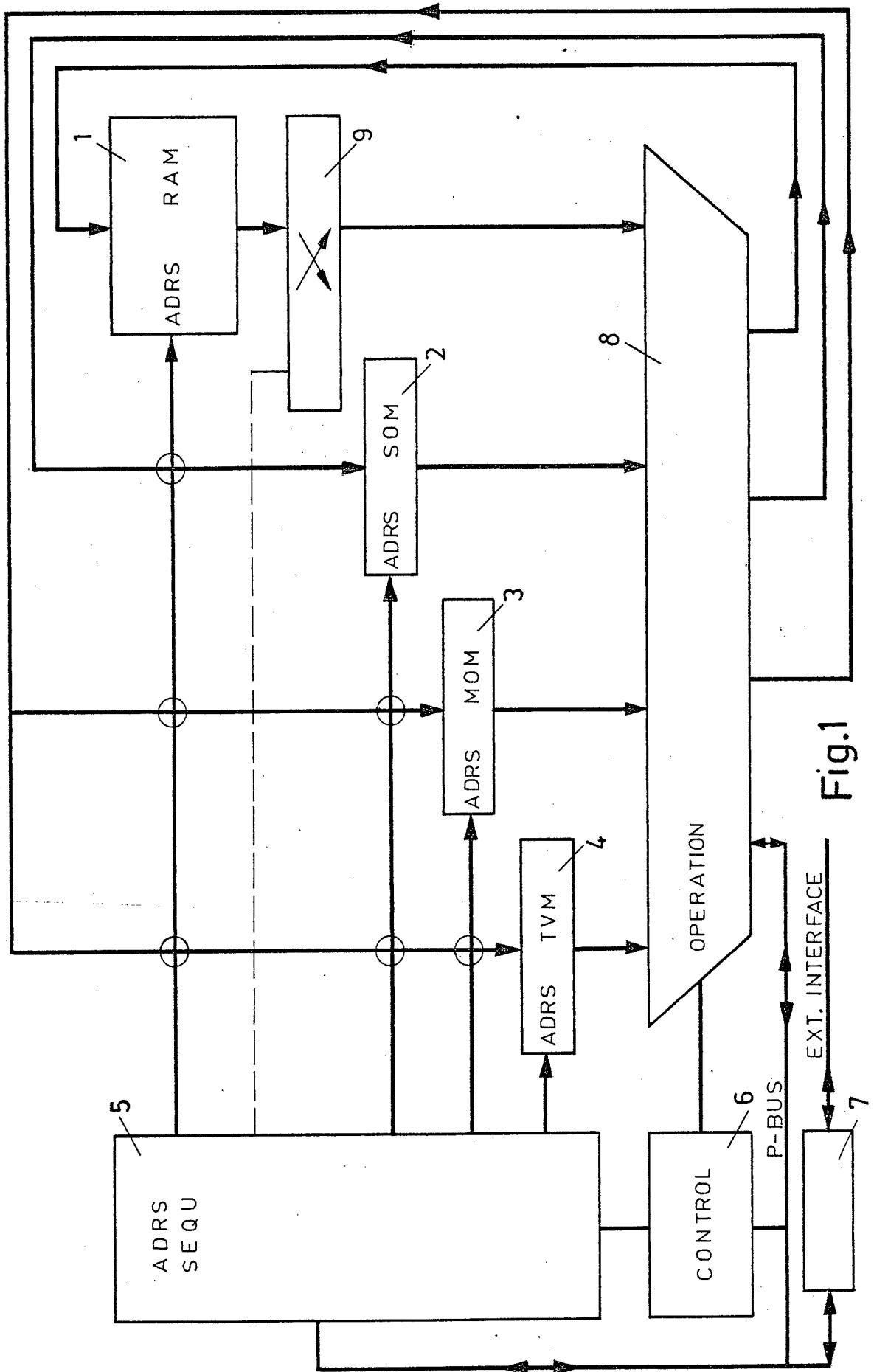

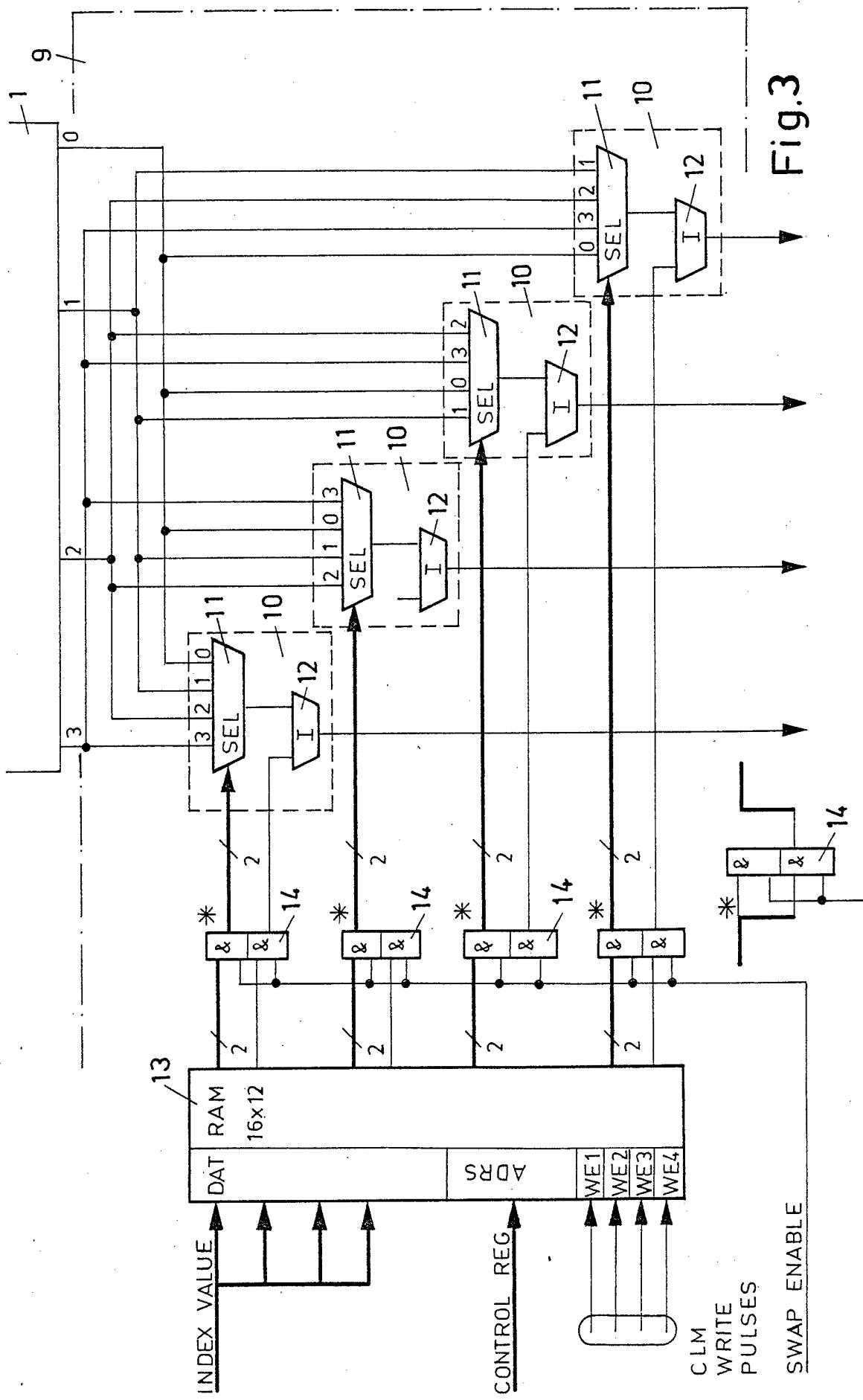

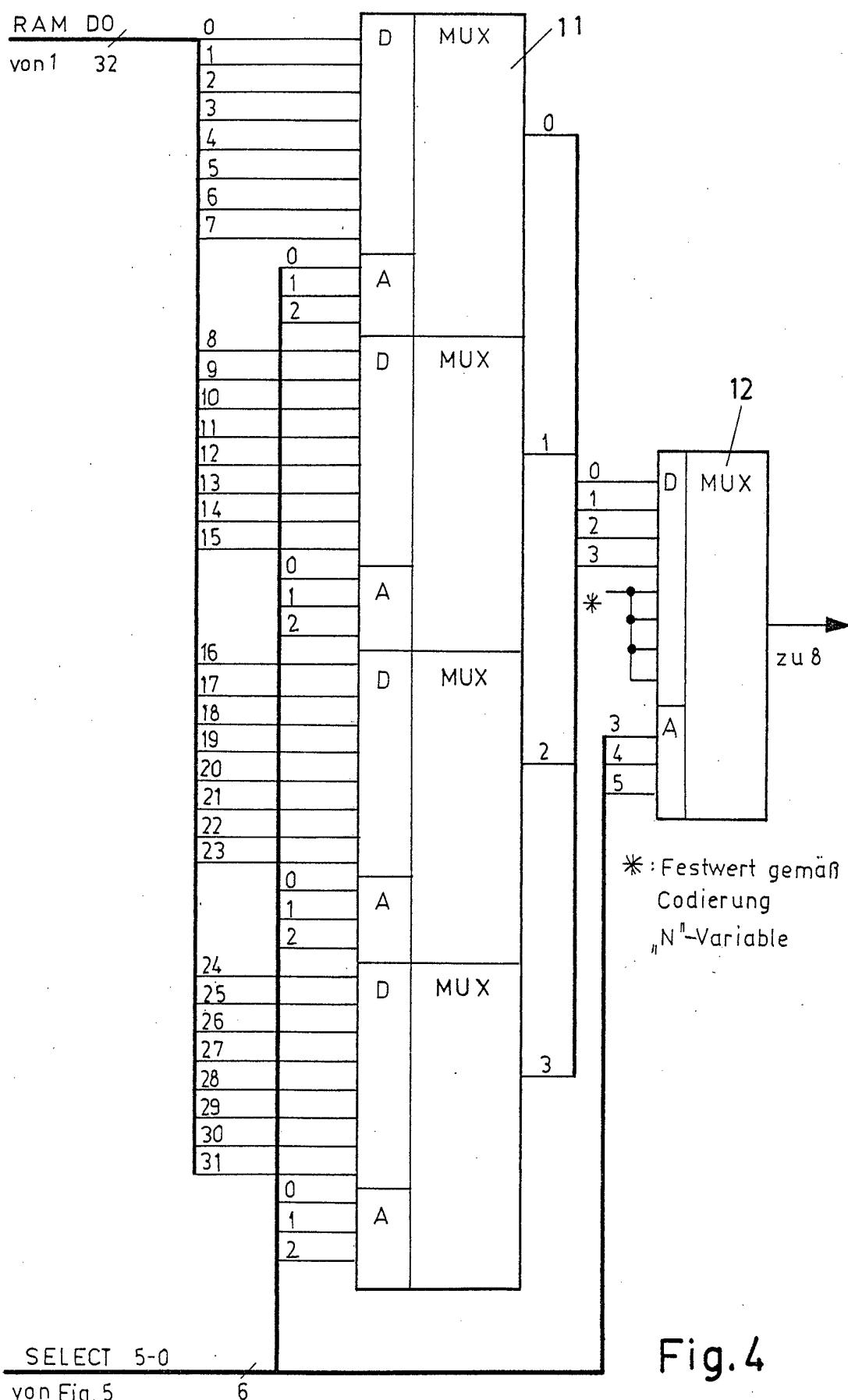

- Fig. 3-5 Details der Datenaustauschschaltungen,

- Fig. 6, 7 spezifische Einsatzfälle der Datenaustauschschaltungen,

- Fig. 8 typische Aufwendungen für die Datenaustauschschaltungen,

- Fig. 9 ein Beispiel für die Belegung der Wandlungslistenspeicher.

Es wird auf folgende Quellen aus der Literatur Bezug genommen:

- /1/: WP-Anmeldung G06F/274367.3 „Anordnung zur Verarbeitung von Ternärvektorlisten“,

- /2/: WP-Anmeldung G06F/282506.4 „Spezialprozessoranordnung zur Verarbeitung von Ternärvektorlisten“

- /3/: Posthoff, Steinbach: Binäre Gleichungen — Algorithmen und Programme. Wissenschaftliche Schriftenreihe der TH Karl-Marx-Stadt, Heft 1, 1979.

Das Blockschaltbild einer Speicher- und Verarbeitungseinrichtung für Ternärvektorlisten, die auf erfindungsgemäße Weise erweitert ist, ist in Fig. 1 dargestellt. Die an sich gegebene Anordnung umfaßt

- Speichermittel 1 für die Ternärvektorlisten (im folgenden als TVL-Speicher 1 bezeichnet),

- Speichermittel für weitere Operanden, und zwar einen Zweitoperandenspeicher SOM (SECOND OPERAND MEMORY) 2, einen Maskenoperandenspeicher MOM (MASK OPERAND MEMORY) 3 und einen Markierungsvektorspeicher TVM (TAG VECTOR MEMORY) 4,

- Adressierungsschaltungen 5, denen die Adresseneingänge aller besagten Speichermittel 2–4 nachgeordnet sind,

- Steuerschaltungen 6,

- Anschlußschaltungen 7, mit denen die Anordnung über Interfaceleitungen mit an sich beliebigen Rechnersystemen verbunden ist,

- Such- und Verknüpfungsschaltungen 8, die den Datenausgängen der Speichermittel 1–4 nachgeordnet und ihrerseits ausgangsseitig an deren Dateneingänge angeschlossen sind.

Die Schaltmittel 5–8 sind über Busleitungen, die zur Übermittlung von Parameterinformation dienen (P-BUS), untereinander verbunden.

Ternärvektorlisten (im folgenden mit TVL abgekürzt) bestehen aus Ternärvektoren, die ihrerseits aus Ternärvariablen gebildet werden. Jede Ternärvariable wird mit zwei Bits codiert. Die möglichen Belegungen sind:

- N („don't care“, „Strichelement“)

- 0

- 1

Typische Operationen sind z.B.:

- das Suchen nach Ternärvektoren der TVL, die zu einem Ternärvektor orthogonal sind (der zweite Ternärvektor ist dabei im SOM2 gespeichert)

- die Blockbildung zwischen zwei Ternärvektoren,

- die Durchschnittsbildung zwischen zwei Ternärvektoren usw.

Durch entsprechende sequentielle Adressierung der Speichermittel 1–4 können elementare Algorithmen, die für TVL definiert sind, mit hoher Geschwindigkeit ausgeführt werden. Details der Algorithmen sind in /3/ beschrieben, die spezifische Ausgestaltung der beschriebenen Schaltmittel ist für verschiedene Leistungsbereiche in /1/, /2/ ausführlich dargestellt, so daß sich eine weitere Beschreibung erübrigts. Wesentlich ist, daß TVL, die miteinander verknüpft werden sollen, zunächst so umgeordnet werden müssen, daß sie genau die gleiche Variablenzuordnung haben. Dies ist in Fig. 2 illustriert. Von zwei Ternärvektorlisten TVL I, II sind die Variablenanordnungen sowie die Belegungen der ersten Zeilen dargestellt. Manche Variablen kommen in beiden TVL vor und manche nicht. Aus den unterschiedlichen primären Variablenzuordnungen (in Fig. 2 oben) muß nun vor der Verarbeitung eine einheitliche Zuordnung (in Fig. 2 unten) aufbereitet werden, wobei die resultierende Reihenfolge der Variablen an sich gleichgültig ist. In Variablenpositionen, die primär in einer TVL nicht vorkommen (z.B. X, Y in TVL I) sind dabei konstant N-Belegungen (in /3/: „Strichelemente“) einzufügen. Die Umordnungsoperationen sind sehr zeitaufwendig (es müssen alle Variablenpositionen beider TVL umgeordnet, d.h. transportiert werden, die konstanten N-Belegungen sind einzutragen usw.). Um diese Transportoperationen zu vermeiden, sind zwischen den Datenausgängen der TVL-Speicher 1 und den Eingängen der nachgeordneten Such- und Verknüpfungsschaltungen 8 Datenaustauschschaftungen 9 eingefügt. Diese sind so ausgebildet, daß jeder Variablenposition der Such- und Verknüpfungsschaltungen 8 eine Auswahlseinrichtung vorgeschaltet ist, die ihrerseits an alle Variablenpositionen der Datenausgänge der TVL-Speicher 1 angeschlossen ist. Jede Auswahlseinrichtung 10 besteht dabei aus Auswahlsschaltungen 11 zur Auswahl jeweils einer der Variablenpositionen und aus einer Insertionsschaltung 12, die eine feste Belegung liefert, die der Codierung des N-Elementes entspricht. Jeder Auswahlseinrichtung 10 ist ein Wandlungslistenspeicher 13 zugeordnet, der die Auswahl- und Steuerinformation enthält. Eine erste Ausgestaltung ist in Fig. 3 dargestellt.

Für vier Variablenpositionen sind vier Auswahlseinrichtungen 10 vorgesehen, die jeweils eine Auswahlsschaltung 11 mit nachgeordneter Insertionsschaltung 12 enthalten. Die vorgeordneten Wandlungslistenspeicher 13 sind zu einer Speicheranordnung zusammengefaßt dargestellt, der die Auswahleingänge der Auswahlsschaltungen 11 und die Steuereingänge der Insertionsschaltungen 12 nachgeschaltet sind. In diese Verbindungen sind Sperrelemente 14 eingefügt, wobei alle Sperrelemente 14 an eine gemeinsame Erlaubnisleitung (SWAP ENABLE) angeschlossen sind.

Im Beispiel sind die Sperrelemente 14 als UND-Verknüpfungen ausgebildet. Mit den Auswahlsschaltungen 11 ist es möglich, die Belegung jeder Variablenposition der TVL-Speicher 1 zu jeder Variablenposition der Such- und Verknüpfungsschaltungen 8 durchzusteuren. Mit den Insertionsschaltungen 12 kann eine konstante N-Belegung an die Such- und Verknüpfungsschaltungen 8 geliefert werden. Somit ist durch entsprechendes Laden der Wandlungslistenspeicher 13 die in Fig. 2 illustrierte Umordnung ausführbar, ohne daß besondere Transportoperationen erforderlich sind.

Weiterhin muß gewährleistet sein, daß auf die Information in den TVL-Speichern 1 zugegriffen werden kann, ohne daß ein Umordnen stattfindet. Dies ist z.B. erforderlich, wenn die TVL-Speicher 1 auch zur Speicherung anderer Informationen (wie Programme, Datenbereiche usw.) verwendet werden sollen bzw. wenn TVL verarbeitet werden sollen, die bereits als Resultat einer Umordnung entstanden sind. Im besonderen trifft dies zu, wenn es sich bei den TVL-Speichern 1 um Speichermittel eines zugeordneten Universalrechners handelt (vgl. /1/).

In der Anordnung nach Fig. 3 sind die Auswahlsschaltungen 11 eingangsseitig jeweils so beschaltet, daß bei der Belegung ihrer Auswahlleitungen mit Null die jeweilige Variablenposition direkt durchgesteuert wird (Eingang 0 zu Ausgang 0, Eingang 1 zu Ausgang 1 usw.). Damit können die Sperrelemente 14 als einfache UND-Gatter ausgeführt sein. Bei Belegung der Erlaubnisleitung (SWAP ENABLE) mit Null unterbleibt somit das Umordnen.

Die einfache Gestaltung der Sperrelemente 14 hat den Nachteil, daß das Bestimmen der Umordnungssteuerinformation für die Wandlungslistenspeicher 13 erschwert wird, da es nicht möglich ist, Variablenpositionen direkt zu laden (es muß stets auf die Beschriftung der jeweiligen Auswahlsschaltung 11 Rücksicht genommen werden).

Der Nachteil wird bei der Ausbildung gem. Fig. 4, 5 vermieden. Fig. 4 zeigt eine Auswahlseinrichtung 10, bei der die Auswahlsschaltung 11 und die Insertionsschaltung 12 durch Multiplexerschaltkreise realisiert sind. Es ist eine Bitposition dargestellt, und zwar für eine Verarbeitungsbreite von 32 Variablenpositionen. Jede der Auswahlseinrichtungen 10 ist völlig gleichartig aufgebaut.

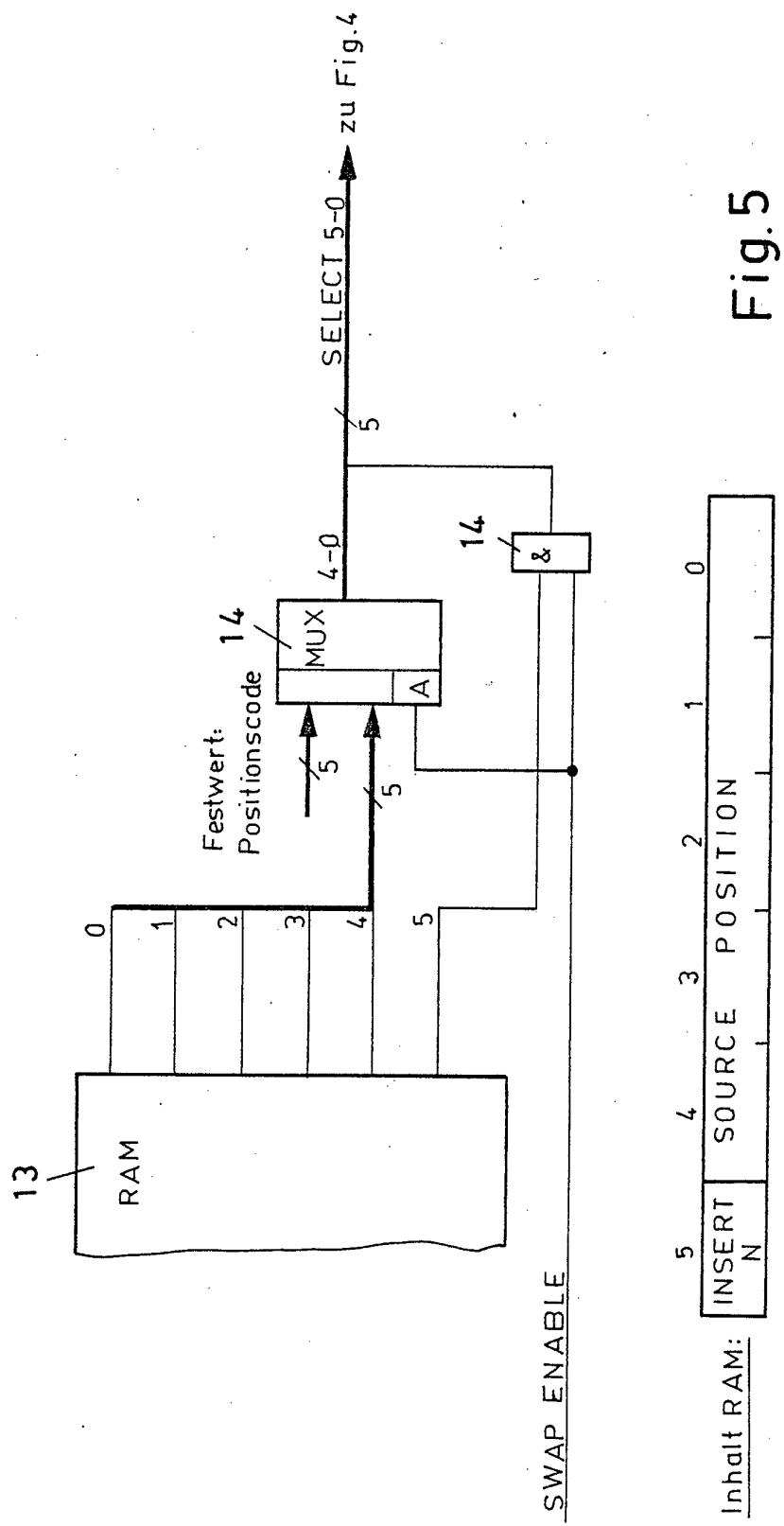

Fig. 5 zeigt einen Wandlungslistenspeicher 13 mit nachgeordneten Sperrelementen 14 für eine Variablenposition gem. Fig. 4. Das Sperrelement 14, das den Auswahleingängen der Auswahlshaltung 10 vorgeordnet ist, ist seinerseits als Auswahlshaltung 10 ausgebildet. Deren erste Eingänge sind mit einem Festwert beschaltet, der der jeweiligen Variablenposition entspricht (Positionscode).

An die zweiten Eingänge sind die Ausgänge des Wandlungslistenspeichers 13 angeschlossen. Der Auswahleingang ist mit der gemeinsamen Erlaubnisleitung (SWAP ENABLE) beschaltet.

Das Sperrelement 14 für die Insertionsschaltung 12 (in Fig. 4 mit der zweiten Stufe der Auswahlshaltung 11 in einem Multiplexerschaltkreis zusammengefaßt und durch die Steuerleitung SELECT 5 gesteuert) ist weiterhin als UND-Verknüpfung ausgebildet.

Der genannte Positionscode entspricht der Position des jeweils nachgeschalteten Einganges der Such- und Verknüpfungsschaltungen 8. Ist die Erlaubnisleitung (SWAP ENABLE) inaktiv, so wird zu jedem der genannten Eingänge der Ausgang der TVL-Speicher 1 mit der jeweils identischen Position durchgesteuert (an den Sperrelementen 14 wird der jeweilige feste Positionscode ausgewählt).

Bei aktiver Erlaubnisleitung ist das Umordnen möglich, wobei jeder Wandlungslistenspeicher 13 direkt mit der gewünschten Quell-Position (im Beispiel von 0 bis 31) geladen werden kann. Da die Durchlaufzeit durch die Datenaustauschschaltungen 9 sehr gering ist (die Auswahl über die Wandlungslistenspeicher 13 bleibt für die Verarbeitung einer TVL konstant, so daß die Information aus den TVL-Speichern 1 nur die Schaltmittel 11, 12 zu durchlaufen hat), kann sie vorteilhaft im Rahmen von Anordnungen gem. Fig. 6, 7 eingesetzt werden. Dabei sind die TVL-Speicher 1 aus mehreren Speichermodulen 15 aufgebaut.

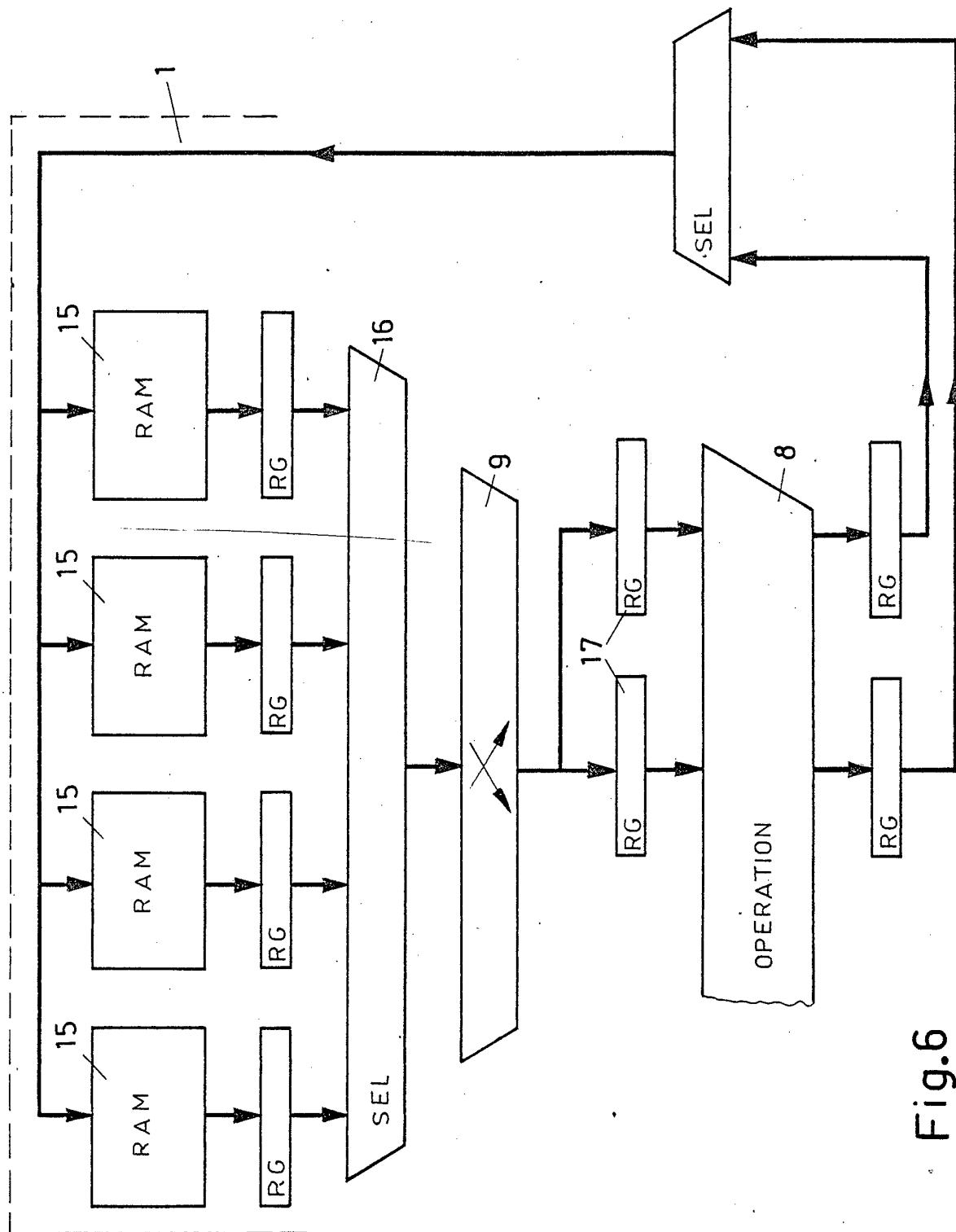

In Fig. 6 sind diese den Datenaustauschschaltungen 9 über Auswahlmittel 16 vorgeschaltet. Bei den Auswahlmitteln 16 kann es sich um konventionelle Auswahlshaltungen handeln oder auch um ein Bussystem, das z.B. mit „tri state“-Schaltkreisen realisiert ist.

Die Speichermodulen 15 werden dabei zeitversetzt betrieben („interleaved mode“), wie dies von größeren Rechnern her bekannt ist. Zum Beispiel hat jedes der Speichermodulen 15 eine Zykluszeit von 800 ns. Es wird zunächst zum ersten Speichermodul zugegriffen. Mit einem Zeitversatz von 200 ns wird das zweite adressiert, wiederum 200 ns später das dritte usw. Somit steht die Information aus den einzelnen Speichermodulen 15 im Intervall von 200 ns nacheinander zur Verfügung und kann über die Auswahlmittel 16 (die sinngemäß alle 200 ns umgeschaltet werden müssen) den Datenaustauschschaltungen 9 und weiter den Such- und Verarbeitungseinrichtungen 8 zugeführt werden.

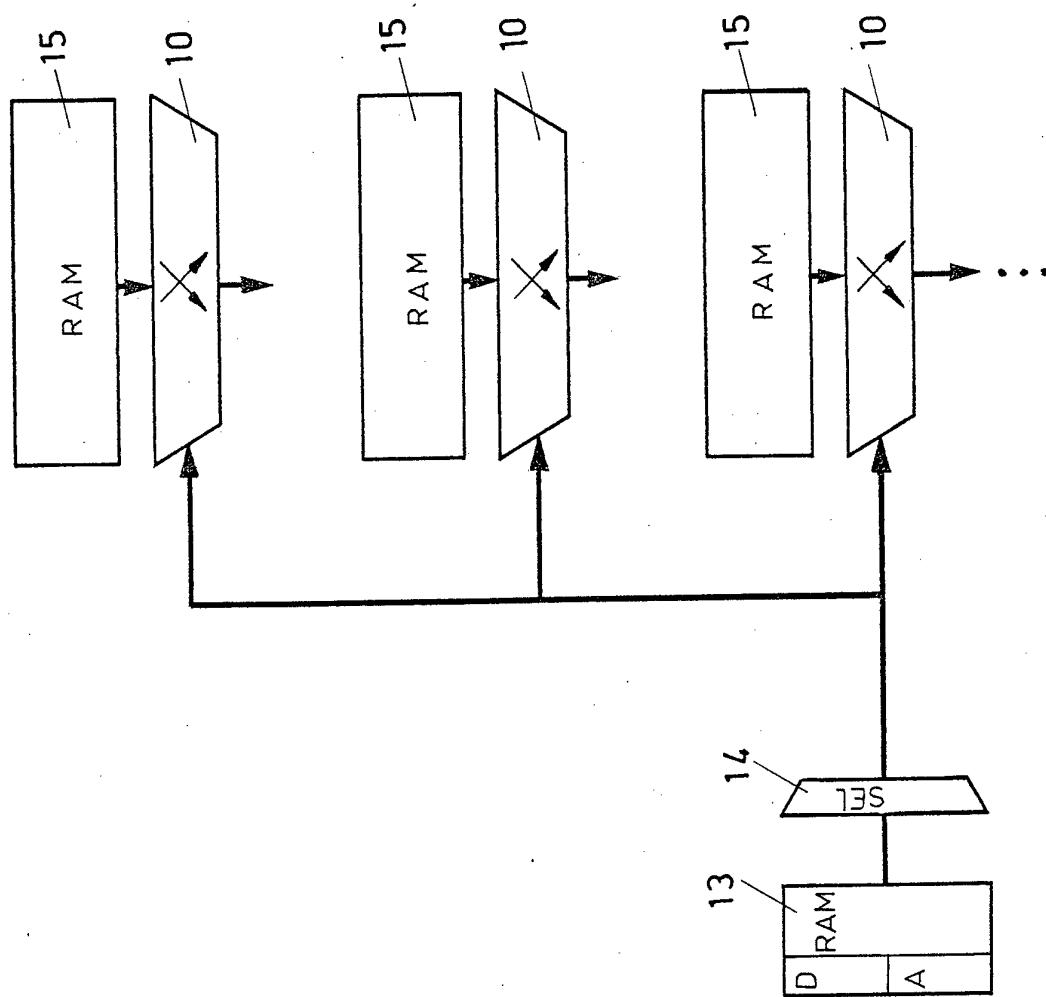

Fig. 7 zeigt eine Ausführung, in der die TVL-Speicher 1 ebenfalls aus mehreren Speichermodulen 15 aufgebaut sind, die aber nicht zeitversetzt, sondern parallel betrieben werden. Dabei sind den Datenausgängen der Speichermodulen 15 jeweils separate Auswahleinrichtungen 10 nachgeschaltet (die ihrerseits mit nicht dargestellten separaten Such- und Verknüpfungsschaltungen verbunden sind). Alle Auswahleinrichtungen 10 in identischen Variablenpositionen sind über jeweils gemeinsame Sperrelemente 14 an gemeinsame Wandlungslistenspeicher 13 angeschlossen.

Damit kann die erfindungsgemäße Anordnung in die Horizontalpositionen eines aktiven Memory-Array (AMA) eingefügt werden, das in /2/ ausführlich beschrieben ist. Dadurch, daß Sperrelemente 14 und Wandlungslistenspeicher 13 nur einmal vorhanden sind, bleibt die Aufwandsverhöhung in Grenzen.

Wesentlich ist, daß die erfindungsgemäße Anordnung nur dann wirksam werden kann, wenn die Zeilen der zu verarbeitenden TVL im Rahmen der Aufrufbreite der TVL-Speicher 1 unterzubringen sind. Bei der üblichen Codierung einer Ternärvariablen mit zwei Bit (s. /3/) und einer Aufrufbreite der TVL-Speicher 1 von n Bit darf somit jede TVL-Zeile maximal  $\frac{n}{2}$  Variable umfassen. Eine Erweiterung ist möglich, wenn die beiden Bitpositionen der VariablenCodierung nicht zusammen in einem Speicherwort untergebracht werden, sondern wenn je TVL-Zeile ein erstes Speicherwort alle ersten Bitpositionen aufnimmt und ein zweites Speicherwort alle zweiten Bitpositionen der Codierung der Ternärvariablen. Somit können n Variable parallel unter Nutzung der erfindungsgemäßen Anordnung verarbeitet werden, wobei jede TVL-Zeile zwei Speicherzugriffe erfordert.

Die entsprechende Ausgestaltung ist in Fig. 6 bereits mit dargestellt. Dabei sind den Datenaustauschschaltungen 9 Deserialisierungsmittel 17 nachgeordnet, und an diese sind die Such- und Verknüpfungsschaltungen 8 angeschlossen.

Im Beispiel sind die Deserialisierungsmittel 17 zwei Register. Bei der Verarbeitung einer TVL-Zeile wird beim ersten Speicherzugriff das erste Register geladen. Beim folgenden Speicherzugriff wird das zweite Register geladen. Dabei durchläuft die Information jeweils die Datenaustauschschaltungen 9. Im folgenden Zyklus können die Such- und Verknüpfungsschaltungen 8 die TVL-Zeile verarbeiten. Dabei kann parallel bereits die folgende TVL-Zeile adressiert werden (vgl. /1/). Der Wechsel zwischen mehr serieller und mehr paralleler Verarbeitung ist in der Informationstechnik üblich, um jeweils gewünschte Aufwands-Leistungs-Kompromisse zu erzielen, und bedarf somit keiner näheren Erläuterung.

Wesentlich für die beschriebene Verarbeitungsweise ist:

1. Je Bitposition ist eine Anordnung aus Wandlungslistenspeicher 13 und Sperrelementen 14 erforderlich.

2. Die Insertionsschaltungen 12 müssen so ausgebildet werden, daß sie während des ersten Zugriffs die erste Bitposition der N-Codierung aufschalten und während des zweiten Zugriffs die zweite (bei der üblichen Codierung mit 0 0 sind gegenüber Fig. 4 keine Änderungen erforderlich).

Fig. 8 veranschaulicht typische Aufwendungen für die Datenaustauschschaltungen 9 bei verschiedenen Aufrufbreiten und Verarbeitungsweisen. Basis ist ein übliches TTL-Schaltkreisortiment und die Realisierung gem. Fig. 4, 5.

Bedeutsam ist, daß bei einer Verarbeitungsbreite von 32 Bit noch TVL mit 32 Variablenpositionen pro Zeile bei erträglichem Zusatzaufwand ohne Umordnungstransporte verarbeitet werden können (bei vielen Problemen des Logikentwurfs, der Schaltungsoptimierung usw. treffen die einzelnen Booleschen Gleichungen kaum mehr als 32 Variable, sondern oftmals erheblich weniger).

Die Wandlungslistenspeicher 13 müssen die Auswahl- und Steuerinformation für wenigstens eine (die aktuell zu verarbeitende) TVL aufnehmen können. Dazu reicht eine Realisierung mit Registerschaltkreisen aus. Bei Einsatz von RAMs hat man jedoch den Vorteil, die Wandlungsinformation von mehreren TVL speichern zu können, so daß vor der jeweiligen Verarbeitungsoperation nur die betreffende RAM-Adresse umgestellt werden muß. Das Gewinnen der Wandlungsinformation durch Vergleich der Variablenbelegungen der TVL ist ein üblicherweise programmtechnisch ausgeführter Prozeß, zu dessen Beschleunigung in /2/ entsprechende Schaltmittel vorgeschlagen wurden. Auch ist der Ablauf selbst in /2/ ausführlich beschrieben, so daß eine genauere Erläuterung entfallen kann. Für das Beispiel von Fig. 2 zeigt Fig. 9 die Belegungen der Wandlungslistenspeicher 13 (ausgebildet gem. Fig. 5). Die Angabe „Variablenposition“ bezieht sich dabei auf die Variablen- (bzw. Bit-)position der

nachgeschalteten Such- und Verknüpfungsschaltungen 8. So ist z. B. der Wandlungslistenspeicher 13 in Variablenposition 4 für die Verarbeitung der TVL I mit dem Wert 2 zu laden, und für die Verarbeitung der TVL II ist INSERT N zu aktivieren (gem. Fig. 5 Belegung 20H).

Dazu ist es erforderlich, daß die Wandlungslistenspeicher 13 programmseitig oder seitens der für das Vergleichen der Variablenbelegungen vorgesehenen Schaltmittel selektiv geladen werden können.

Die Vorteile der erfindungsgemäßen Anordnung können wie folgt zusammengefaßt werden:

Für das Umordnen von TVL wird keine Verarbeitungszeit benötigt. Dies gilt für TVL, deren Spaltenzahl (Variablenpositionen pro Zeile) der Aufrufbreite der Speichermittel entspricht.

Diese Spaltenzahl kann maximal der Anzahl der Bits entsprechen, die in einem Zugriff von den Speichermitteln geliefert werden.

Somit ist die Anordnung für praktisch brauchbare Spaltenzahlen (32–64) mit angemessenem Aufwand ausführbar.

Da sie von der TVL-Information sehr schnell durchlaufen wird, ist eine zeitgeteilte Ausnutzung durch mehrere zeitversetzt arbeitende Speichermodulen möglich.

Es ist weiterhin gewährleistet, daß Zugriffe zu gespeicherter Information, bei denen keine Wandlung stattfinden darf, stets möglich sind, ohne daß dazu Steuerinformation (z. B. in den Wandlungslistenspeichern) umgeladen bzw. eingestellt werden muß.

Für TVL mit größerer Spaltenzahl sind nach wie vor Umwandlungstransporte notwendig. Die erfindungsgemäße Anordnung kann dazu in entsprechenden Programmabläufen vorteilhaft genutzt werden. Sie ist als „barrel shifter“ benutzbar, darüber hinaus ist es aber möglich, in einem Verarbeitungsschritt alle Variablenpositionen eines Zeilenabschnittes (gemäß Aufrufbreite) der Ziel-TVL zu transportieren, die von jeweils einem Zeilenabschnitt der Quell-TVL abhängen, und auch gleichzeitig alle N-Belegungen zu erzeugen.

Fig.1

249 342

7

TVL I

|   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| A | B | C | D | E | F | G | H |

| 1 | 0 | - | - | 1 | 1 | 0 | 0 |

|   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|

| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| A | B | C | D | E | F | G | H | X | Y |

| 1 | 0 | - | - | 1 | 1 | 0 | 0 | * | * |

|   |   |   |   |   |   |

|---|---|---|---|---|---|

| 5 | 4 | 3 | 2 | 1 | 0 |

| E | H | A | B | X | Y |

| - | 0 | - | 1 | 1 | 1 |

|   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|

| 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| A | B | C | D | E | F | G | H | X | Y |

| - | - | - | - | - | - | - | - | - | - |

|   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|

| - | - | - | - | - | - | - | - | - | - |

| A | B | C | D | E | F | G | H | X | Y |

| - | - | - | - | - | - | - | - | - | - |

\*: mit "Strichelementen" (N-Belegungen) aufgefüllt

Fig.2

249342 9

23.MAI.1986 \* 248352

Fig.6

Fig.7

| Aufrufbreite (Bit) | maximale Variablenzahl | Aufwand pro Auswahl | Variable Adressierung | Gesamtaufwand | Verarbeitungsweise |

|--------------------|------------------------|---------------------|-----------------------|---------------|--------------------|

| 16                 | 16                     | 3                   | 4                     | 112           |                    |

| 32                 | 32                     | 5                   | 4                     | 288           | Bitparallel        |

| 64                 | 64                     | 9                   | 5                     | 896           |                    |

| 32                 | 16                     | 10                  | 4                     | 224           |                    |

| 64                 | 32                     | 18                  | 4                     | 704           | Variantenparallel  |

Fig.8

| Variablen-<br>position | TVL I    |      | TVL II   |      |

|------------------------|----------|------|----------|------|

|                        | INSERT N | Code | INSERT N | Code |

| 0                      | 1        | -    |          | 0    |

| 1                      | 1        | -    |          | 1    |

| 2                      |          | 0    |          | 4    |

| 3                      |          | 1    | 1        | -    |

| 4                      |          | 2    | 1        | -    |

| 5                      |          | 3    |          | 5    |

| 6                      |          | 4    | 1        | -    |

| 7                      |          | 5    | 1        | -    |

| 8                      |          | 6    |          | 2    |

| 9                      |          | 7    |          | 3    |

Fig.9