(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5987275号

(P5987275)

(45) 発行日 平成28年9月7日(2016.9.7)

(24) 登録日 平成28年8月19日(2016.8.19)

|                |           |        |       |     |

|----------------|-----------|--------|-------|-----|

| (51) Int.Cl.   | F 1       |        |       |     |

| HO 1 L 27/14   | (2006.01) | HO 1 L | 27/14 | D   |

| HO 1 L 27/146  | (2006.01) | HO 1 L | 27/14 | A   |

| HO 1 L 21/3205 | (2006.01) | HO 1 L | 21/88 | J   |

| HO 1 L 21/768  | (2006.01) | HO 1 L | 21/90 | A   |

| HO 1 L 23/522  | (2006.01) | HO 4 N | 5/335 | 740 |

請求項の数 15 (全 29 頁) 最終頁に続く

|           |                              |           |                                        |

|-----------|------------------------------|-----------|----------------------------------------|

| (21) 出願番号 | 特願2011-162228 (P2011-162228) | (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号 |

| (22) 出願日  | 平成23年7月25日(2011.7.25)        | (74) 代理人  | 110000925<br>特許業務法人信友国際特許事務所           |

| (65) 公開番号 | 特開2013-26565 (P2013-26565A)  | (72) 発明者  | 秋山 健太郎<br>東京都港区港南1丁目7番1号 ソニー株式会社内      |

| (43) 公開日  | 平成25年2月4日(2013.2.4)          |           |                                        |

| 審査請求日     | 平成26年7月18日(2014.7.18)        | 審査官       | 安田 雅彦                                  |

最終頁に続く

(54) 【発明の名称】 固体撮像装置、固体撮像装置の製造方法、および電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換部が配列形成された画素領域を有するセンサ基板と、

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、

前記受光面上に設けられ、前記画素領域の膜厚が当該画素領域の外側に設けられた周辺領域の膜厚よりも薄い段差構造を有する絶縁層と、

前記受光面側における前記周辺領域に設けられた配線と、

前記絶縁層上において前記光電変換部に対応する各位置に設けられたオンチップレンズを備え、

前記配線は、少なくとも一部が前記受光面側から前記センサ基板に埋め込まれた埋込配線として設けられ、

前記絶縁層は、前記周辺領域において前記配線の上部を覆う膜を備えた

固体撮像装置。

## 【請求項 2】

前記配線の上部は、前記センサ基板から前記受光面側に突出している

請求項1記載の固体撮像装置。

## 【請求項 3】

前記配線の上部は、前記絶縁層に埋め込まれている

請求項1または2に記載の固体撮像装置。

**【請求項 4】**

前記画素領域における前記絶縁層と前記オンチップレンズとの間には、前記光電変換部に対応した受光開口を有する遮光膜が設けられている

請求項 1 ~ 3 の何れかに記載の固体撮像装置。

**【請求項 5】**

前記絶縁層は、異なる材料を用いて構成された積層構造であり、

前記画素領域においては、前記絶縁層において積層構造の上層部分を構成する膜が除去されている

請求項 1 ~ 4 の何れかに記載の固体撮像装置。

**【請求項 6】**

前記絶縁層は、前記周辺領域にパターン形成された絶縁パターンと、当該絶縁パターンを覆う状態で前記センサ基板上に設けられた絶縁膜とを含み、

前記画素領域には、前記絶縁膜が設けられている

請求項 1 ~ 5 の何れかに記載の固体撮像装置。

**【請求項 7】**

前記センサ基板には、前記受光面側の前記配線と前記表面側に配置された前記駆動回路とを接続する貫通ビアが設けられている

請求項 1 ~ 6 の何れかに記載の固体撮像装置。

**【請求項 8】**

前記センサ基板側の駆動回路を第 1 の駆動回路とし、当該センサ基板の表面側には、第 2 の駆動回路を有する回路基板が貼り合わせられた

請求項 1 ~ 7 の何れかに記載の固体撮像装置。

**【請求項 9】**

前記センサ基板には、前記受光面側から前記センサ基板を貫通し、前記センサ基板側の第 1 の駆動回路と前記回路基板側の第 2 の駆動回路とに達する異なる高さの底面を有する貫通ビアが、前記配線として設けられている

請求項 8 記載の固体撮像装置。

**【請求項 10】**

前記センサ基板には、前記受光面側の前記配線と前記センサ基板側の第 1 の駆動回路とを接続する貫通ビアと、前記受光面側の前記配線と前記回路基板側の第 2 の駆動回路とを接続する貫通ビアとが設けられている

請求項 8 記載の固体撮像装置。

**【請求項 11】**

前記遮光膜は、前記絶縁層の薄膜部分に形成された開口を介して前記センサ基板に接地されている

請求項 4 記載の固体撮像装置。

**【請求項 12】**

センサ基板に設定された画素領域に光電変換部を配列形成することと、

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に駆動回路を形成することと、

前記センサ基板における前記受光面上に絶縁層を成膜することと、

前記受光面側において、前記画素領域の外側に設けられた周辺領域に配線を形成することと、

前記絶縁層および前記配線を形成した後、当該絶縁層において前記画素領域に対応する部分を前記周辺領域に対して選択的に薄膜化することにより当該絶縁層に段差構造を形成することと、

前記段差構造が形成された前記絶縁層上において前記光電変換部に対応する各位置にオンチップレンズを形成することを含み、

前記絶縁層を成膜する際には、前記周辺領域において前記配線の上部を覆う膜を備えて当該絶縁層を形成し、

10

20

30

40

50

前記配線を形成する際には、少なくとも一部が前記受光面側から前記センサ基板に埋め込まれた埋込配線として当該配線を形成する

固体撮像装置の製造方法。

【請求項 1 3】

前記配線を形成する際には、前記絶縁層に埋め込まれた埋込配線として当該配線を形成する

請求項 1 2 記載の固体撮像装置の製造方法。

【請求項 1 4】

前記絶縁層を成膜する際には、異なる材料を用いて構成された積層構造として当該絶縁層を成膜し、

10

前記絶縁層に段差構造を形成する際には、当該絶縁層において積層構造の上層部分を構成する膜を、下層部分を構成する膜に対して選択的に除去する

請求項 1 2 または 1 3 記載の固体撮像装置の製造方法。

【請求項 1 5】

光電変換部が配列形成された画素領域を有するセンサ基板と、

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、

前記受光面上に設けられ、前記画素領域の膜厚が当該画素領域の外側に設けられた周辺領域の膜厚よりも薄い段差構造を有する絶縁層と、

前記受光面側における前記周辺領域に設けられた配線と、

20

前記絶縁層上において前記光電変換部に対応する各位置に設けられたオンチップレンズと、

前記光電変換部に入射光を導く光学系を備え、

前記配線は、少なくとも一部が前記受光面側から前記センサ基板に埋め込まれた埋込配線として設けられ、

前記絶縁層は、前記周辺領域において前記配線の上部を覆う膜を備えた電子機器。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

30

本技術は、固体撮像装置、固体撮像装置の製造方法、および電子機器に関し、特に半導体基板の受光面とは逆の表面側に駆動回路が設けられた固体撮像装置と、この固体撮像装置の製造方法と、この固体撮像装置を用いた電子機器に関する。

【背景技術】

【0 0 0 2】

固体撮像装置においては、入射光に対する光電変換効率や感度の向上を図ることを目的とし、半導体基板の表面側に駆動回路を形成し裏面側を受光面とする、いわゆる裏面照射型の構造が提案されている。またさらに、光電変換部が形成された半導体基板とは別に、駆動回路を形成した回路基板を用意し、半導体基板における受光面と反対側の面に、回路基板を貼り合わせた 3 次元構造も提案されている。

40

【0 0 0 3】

以上のような裏面照射型の固体撮像装置における受光面側の構成は、次のようなである。光電変換部が形成された半導体基板の受光面側には、絶縁膜を介して遮光膜が設けられている。この遮光膜は、光電変換部に対応する複数の受光開口を有し、光電変換部が配列された画素領域に配置されている。また遮光膜を覆う絶縁膜上には、配線および電極パッドが設けられている。これらの配線および電極パッドは、画素領域の外側の周辺領域に配置され、半導体基板の表面側に形成された駆動回路に接続されている。さらに受光面側において配線および電極パッドを覆う絶縁膜上には、各光電変換部に対応してカラーフィルタおよびオンチップレンズが設けられている（以上、下記特許文献 1 参照）。

【先行技術文献】

50

**【特許文献】****【0004】**

【特許文献1】特開2010-245506号公報(例えば図3および関連記載部参照)

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながらこのような構成の裏面照射型の固体撮像装置においては、受光面の上方に複数層の絶縁膜が設けられ、これらの絶縁膜を介してカラーフィルタやオンチップレンズが配置される。したがって、半導体基板の受光面からオンチップレンズまでの距離が大きく、光電変換部においての受光特性を劣化させる要因となる。

10

**【0006】**

そこで本技術は、画素領域の外側の周辺領域に配線を設けた裏面照射型の固体撮像装置において、画素領域における絶縁膜の薄膜化を図ることにより光電変換部での受光特性の向上を図ることが可能な裏面照射型の固体撮像装置を提供することを目的とする。また本技術は、このような構成の固体撮像装置の製造方法およびこの固体撮像装置を用いた電子機器を提供することを目的とする。

**【課題を解決するための手段】****【0007】**

このような目的を達成するための本技術の固体撮像装置は、光電変換部が配列形成された画素領域を有するセンサ基板と、このセンサ基板において光電変換部に対する受光面とは逆の表面側に設けられた駆動回路とを備えている。さらにセンサ基板における受光面上には、画素領域の膜厚が画素領域の外側に設けられた周辺領域の膜厚よりも薄い段差構造を有する絶縁層が設けられている。またセンサ基板の受光面側における周辺領域には配線が設けられており、絶縁層上において光電変換部に対応した各位置にオンチップレンズが設けられている。

20

**【0008】**

このような構成の固体撮像装置は、光電変換部を設けたセンサ基板において、駆動回路が形成された表面側と反対側の面を受光面とした裏面照射型であり、受光面上には画素領域で膜厚が薄い段差構造の絶縁層が設けられている。これにより、周辺領域においては配線の構成に影響を与えることなく絶縁層の膜厚を確保しつつ、画素領域における絶縁層部分のみを薄膜化してオンチップレンズと受光面との距離を小さくすることができる。

30

**【0009】**

また本技術はこのような固体撮像装置の製造方法でもあり、次の手順が行われる。先ず、センサ基板に設定された画素領域に光電変換部を配列形成する。またセンサ基板において光電変換部に対する受光面とは逆の表面側に駆動回路を形成する。さらに、センサ基板における受光面上に絶縁層を成膜すると共に、この受光面側において、画素領域の外側に設けられた周辺領域に配線を形成する。以上の後、絶縁層において画素領域に対応する部分を周辺領域に対して選択的に薄膜化することにより、当該絶縁層に段差構造を形成する。その後、段差構造が形成された絶縁層上において光電変換部に対応する各位置にオンチップレンズを形成する。

40

**【0010】**

また本技術は、上述した固体撮像装置を備えた電子機器でもあり、光電変換部に入射光を導く光学系をさらに備えている。

**【発明の効果】****【0011】**

以上のような本技術によれば、画素領域の外側の周辺領域に配線を設けた裏面照射型の固体撮像装置において、画素領域の絶縁層部分を選択的に薄膜化することによりオンチップレンズと受光面との距離を小さくできる。この結果、光電変換部においての受光特性の向上を図ることが可能になる。

**【図面の簡単な説明】**

50

## 【0012】

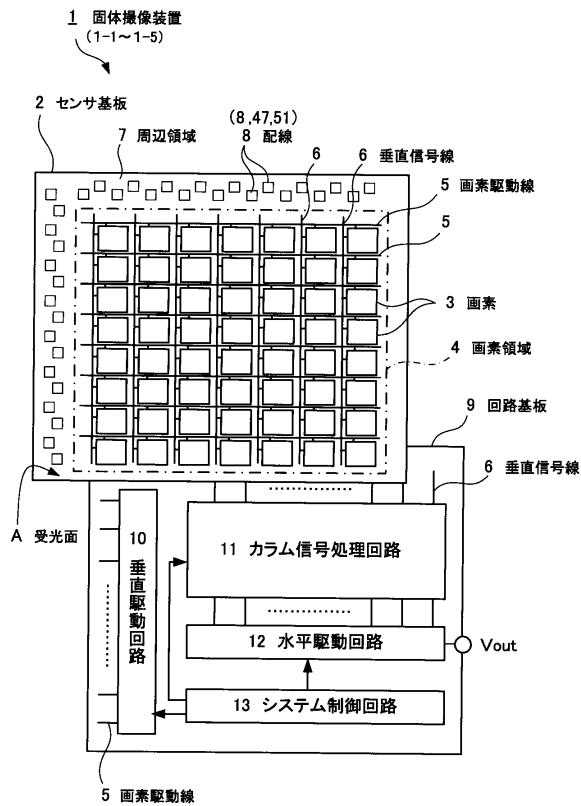

【図1】本技術が適用される固体撮像装置の一例を示す概略構成図である。

【図2】第1実施形態の固体撮像装置の構成を示す要部断面図である。

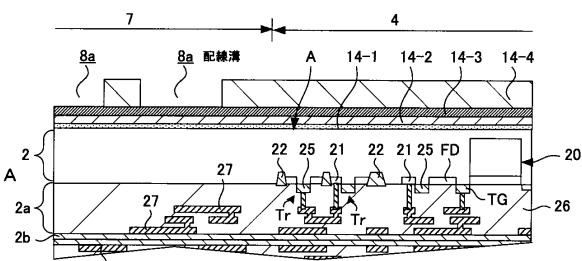

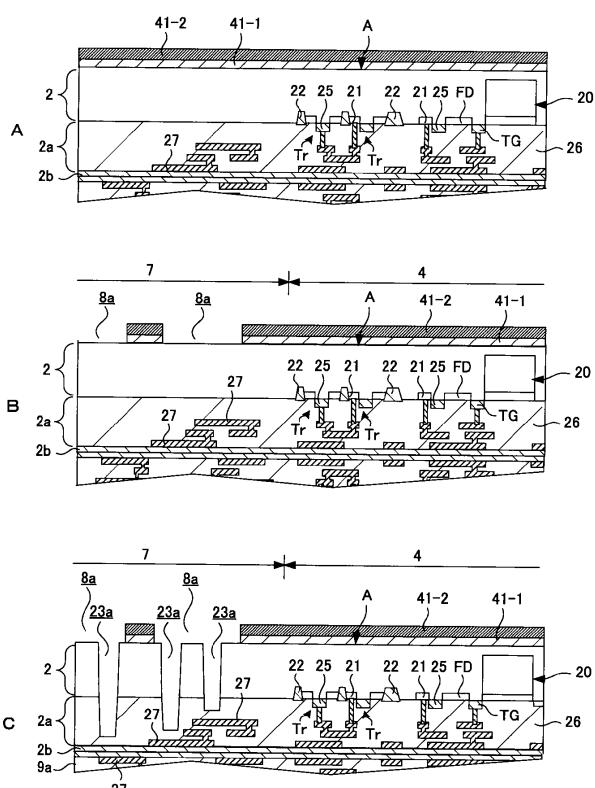

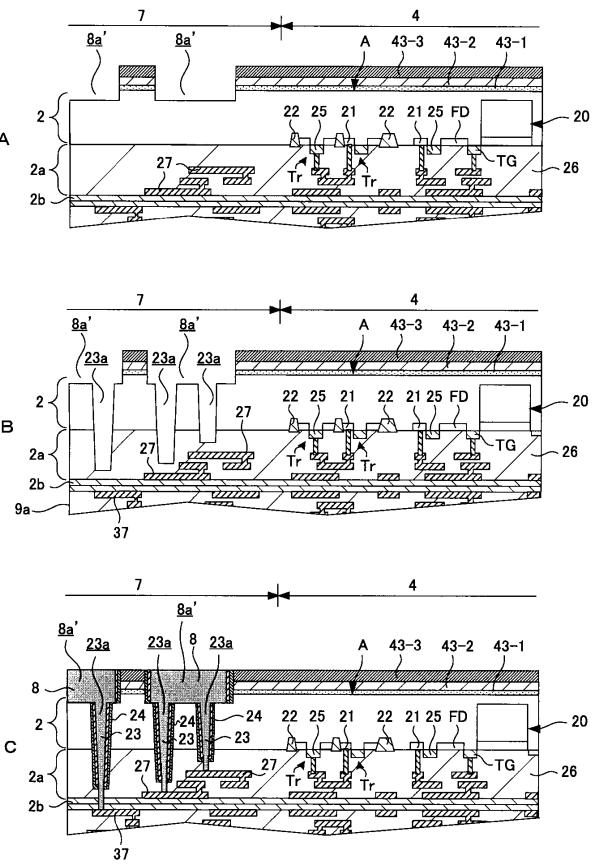

【図3】第1実施形態の固体撮像装置の製造手順を示す断面工程図（その1）である。

【図4】第1実施形態の固体撮像装置の製造手順を示す断面工程図（その2）である。

【図5】第1実施形態の固体撮像装置の製造手順を示す断面工程図（その3）である。

【図6】第1実施形態の固体撮像装置の製造手順を示す断面工程図（その4）である。

【図7】第2実施形態の固体撮像装置の構成を示す要部断面図である。

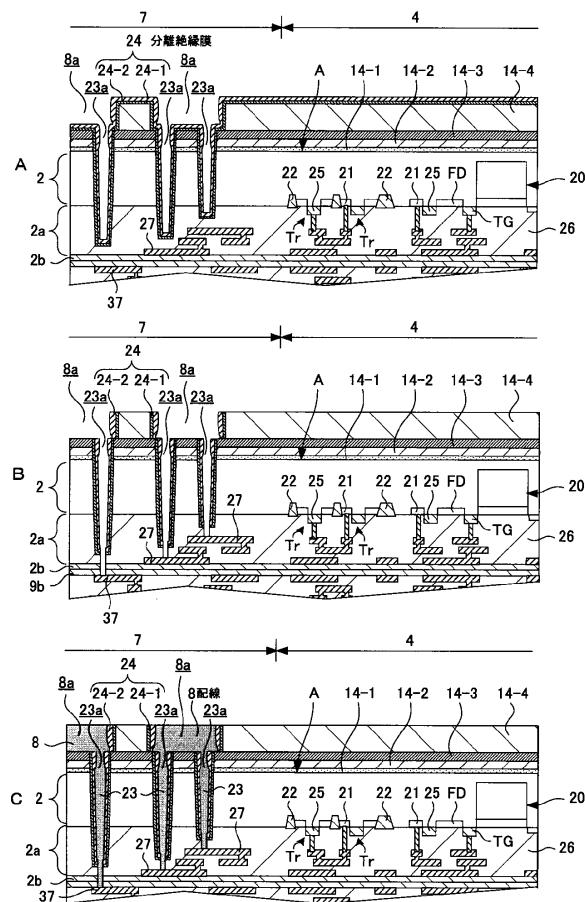

【図8】第2実施形態の固体撮像装置の製造手順を示す断面工程図（その1）である。

【図9】第2実施形態の固体撮像装置の製造手順を示す断面工程図（その2）である。

10

【図10】第2実施形態の固体撮像装置の製造手順を示す断面工程図（その3）である。

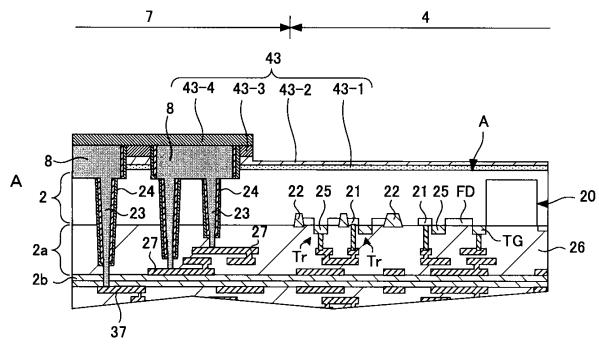

【図11】第3実施形態の固体撮像装置の構成を示す要部断面図である。

【図12】第3実施形態の固体撮像装置の製造手順を示す断面工程図（その1）である。

【図13】第3実施形態の固体撮像装置の製造手順を示す断面工程図（その2）である。

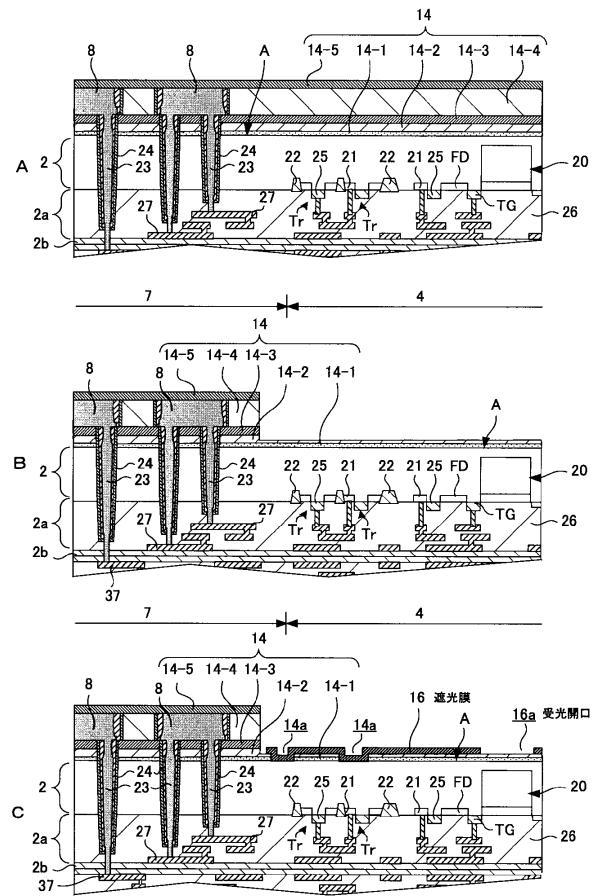

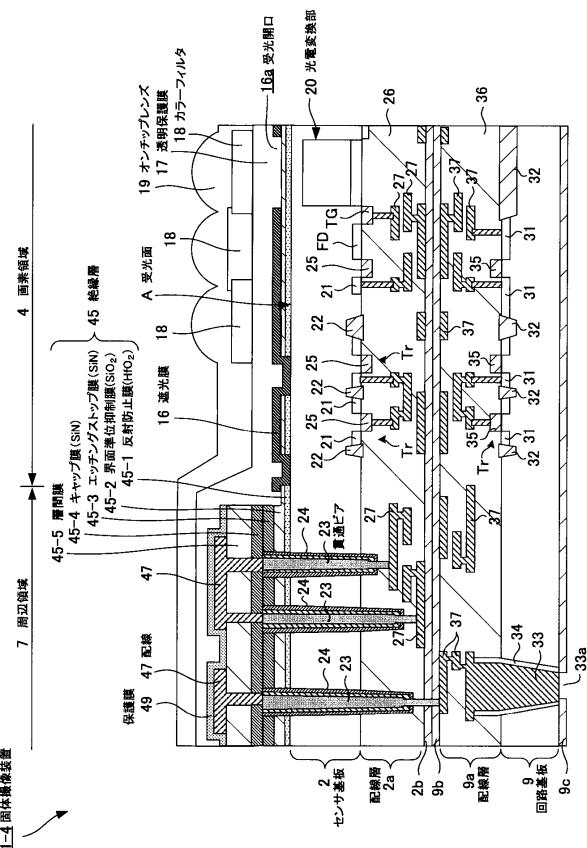

【図14】第4実施形態の固体撮像装置の構成を示す要部断面図である。

【図15】第4実施形態の固体撮像装置の製造手順を示す断面工程図（その1）である。

【図16】第4実施形態の固体撮像装置の製造手順を示す断面工程図（その2）である。

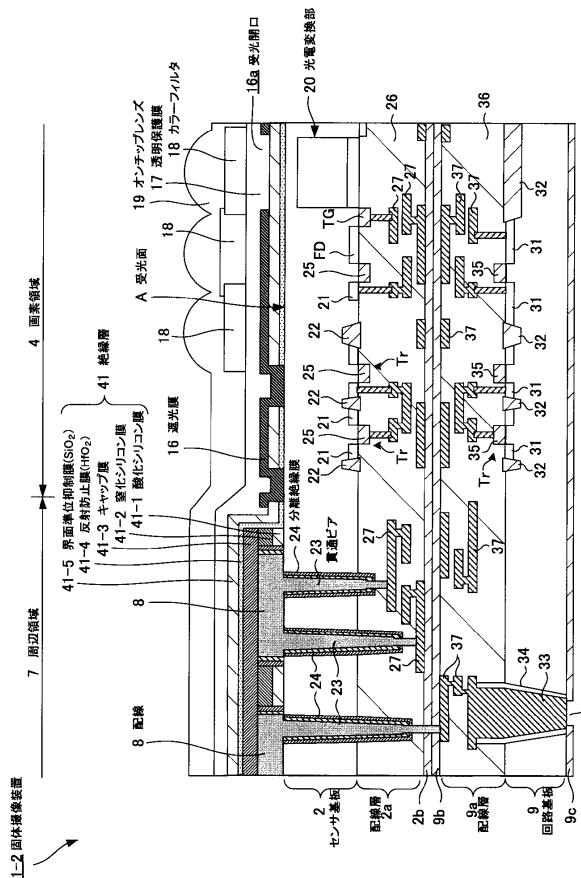

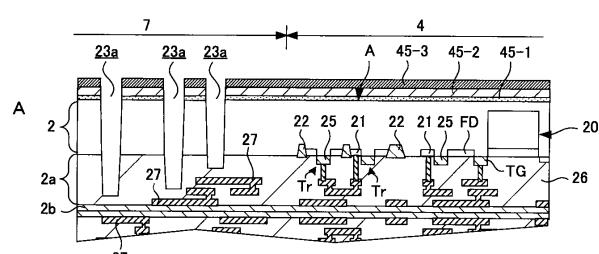

【図17】第5実施形態の固体撮像装置の構成を示す要部断面図である。

【図18】本技術を適用して得られた固体撮像装置を用いた電子機器の構成図である。

## 【発明を実施するための形態】

20

## 【0013】

以下、本技術の実施の形態を、図面に基づいて次に示す順に説明する。

1. 実施形態の固体撮像装置の概略構成例

2. 第1実施形態（段差構造の絶縁層を設けた例）

3. 第2実施形態（絶縁パターンを絶縁膜で覆った段差構造の絶縁層を設けた例）

4. 第3実施形態（段差構造の絶縁層とセンサ基板を掘り込んだ埋込配線を設けた例）

5. 第4実施形態（段差構造の絶縁層と積層配線を設けた例）

6. 第5実施形態（センサ基板内の配線の接続にシェアコンを設けた例）

7. 電子機器（固体撮像装置を用いた電子機器の例）

尚、各実施形態において共通の構成要素には同一の符号を付し、重複する説明は省略する。

30

## 【0014】

1. 実施形態の固体撮像装置の概略構成例

図1に、本技術が適用される裏面照射型の固体撮像装置の一例として、三次元構造の固体撮像装置の概略構成を示す。この図に示す固体撮像装置1は、光電変換部が配列形成されたセンサ基板2と、このセンサ基板2に対して積層させた状態で貼り合わされた回路基板9とを備えている。

## 【0015】

センサ基板2は、一方の面を受光面Aとし、光電変換部を含む複数の画素3が受光面Aに対して2次元的に配列された画素領域4を備えている。画素領域4には、複数の画素駆動線5が行方向に配線され、複数の垂直信号線6が列方向に配線されており、1つの画素3が1本の画素駆動線5と1本の垂直信号線6とに接続される状態で配置されている。これらの各画素3には、光電変換部と、電荷蓄積部と、複数のトランジスタ（いわゆるMOSトランジスタ）および容量素子等で構成された画素回路とが設けられている。尚、画素回路の一部は、受光面Aとは反対側の表面側に設けられている。また複数の画素で画素回路の一部を共有していくても良い。

40

## 【0016】

またセンサ基板2は、画素領域4の外側に周辺領域7を備えている。この周辺領域7には、電極パッドを含む配線8が設けられている。この配線8は、必要に応じてセンサ基板2に設けられた画素駆動線5、垂直信号線6、および画素回路、さらには回路基板9に設

50

けられた駆動回路に接続されている。

【0017】

回路基板9は、センサ基板2側に向かう一面側に、センサ基板2に設けられた各画素3を駆動するための垂直駆動回路10、カラム信号処理回路11、水平駆動回路12、およびシステム制御回路13などの駆動回路を備えている。これらの駆動回路は、センサ基板2側の配線8に接続されている。尚、センサ基板2の表面側に設けられた画素回路も、駆動回路の一部である。

【0018】

2. 第1実施形態

<固体撮像装置の構成>

10

(段差構造の絶縁層と埋込配線を設けた例)

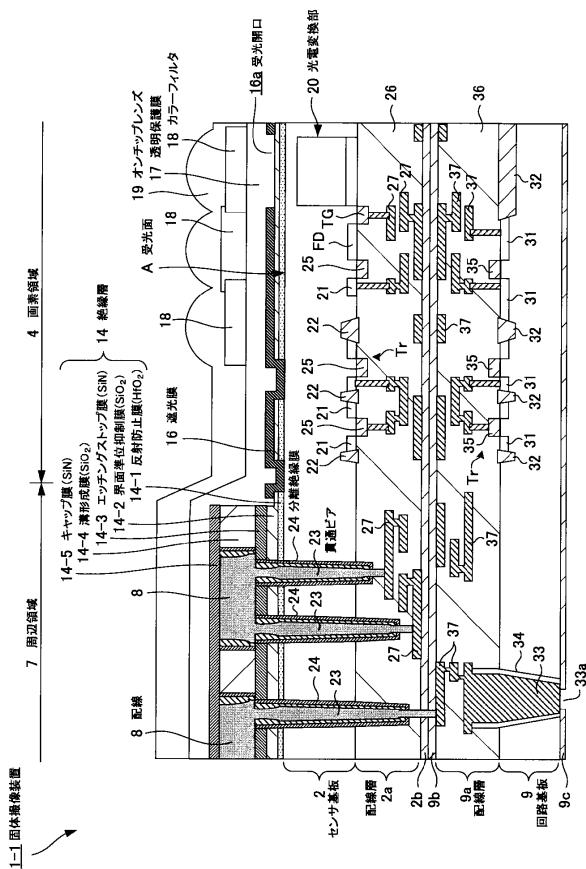

図2は、第1実施形態の固体撮像装置1-1の構成を示す要部断面図であり、図1における画素領域4と周辺領域7との境界付近の断面図である。以下、この要部断面図に基づいて第1実施形態の固体撮像装置1-1の構成を説明する。

【0019】

図2に示す第1実施形態の固体撮像装置1-1は、上述したようにセンサ基板2と回路基板9とを積層させた状態で貼り合わせた3次元構造の固体撮像装置である。センサ基板2の表面側、すなわち回路基板9側に向かう面上には、配線層2aと、配線層2aを覆う保護膜2bとが設けられている。一方、回路基板9の表面側、すなわちセンサ基板2側に向かう面上には、配線層9aと、配線層9aを覆う保護膜9bとが設けられている。また回路基板9の裏面側には、保護膜9cが設けられている。これらのセンサ基板2と回路基板9とは、保護膜2bと保護膜9bとの間で貼り合わせられている。

20

【0020】

またセンサ基板2における回路基板9と反対側の面、すなわち受光面A上には、段差構造を有する絶縁層14と、配線8と、遮光膜16とが設けられ、さらに遮光膜16上には、透明保護膜17、カラーフィルタ18、およびオンチップレンズ19がこの順に積層されている。本第1実施形態においては、特に、絶縁層14が段差構造を有しており、この段差構造の下部にオンチップレンズ19が配置されているところが特徴的である。

30

【0021】

次に、センサ基板2側の各層、および回路基板9側の各層の構成、段差構造を有する絶縁層14、配線8、遮光膜16、透明保護膜17、カラーフィルタ18、およびオンチップレンズ19の構成をこの順に説明する。

【0022】

[センサ基板2]

センサ基板2は、例えば単結晶シリコンからなる半導体基板を薄膜化したものである。このセンサ基板2における画素領域4には、受光面Aに沿って複数の光電変換部20が配列形成されている。各光電変換部20は、例えばn型拡散層とp型拡散層との積層構造で構成されている。尚、光電変換部20は画素毎に設けられており、図面においては1画素分の断面を図示している。

40

【0023】

またセンサ基板2において受光面Aとは逆の表面側には、n+型不純物層からなるフローティングディフュージョンFD、トランジスタTrのソース/ドレイン21、さらにはここでの図示を省略した他の不純物層、および素子分離22などが設けられている。

【0024】

さらにセンサ基板2において、画素領域4の外側の周辺領域7には、センサ基板2を貫通する貫通ビア23が設けられている。この貫通ビア23は、センサ基板2を貫通して形成された接続孔内に、分離絶縁膜24を介して埋め込まれた導電性材料によって構成されている。

【0025】

[配線層2a(センサ基板2側)]

50

センサ基板 2 の表面上に設けられた配線層 2 a は、センサ基板 2 との界面側に、ここで図示を省略したゲート絶縁膜を介して転送ゲート T G およびトランジスタ T r のゲート電極 2 5、さらにはここでの図示を省略した他の電極を有している。またこれらの転送ゲート T G およびゲート電極 2 5 は、層間絶縁膜 2 6 で覆われており、この層間絶縁膜 2 6 に設けられた溝パターン内には、例えば銅 (Cu) を用いた埋込配線 2 7 が多層配線として設けられている。これらの埋込配線 2 7 は、ビアによって相互に接続され、また一部がソース / ドレイン 2 1、転送ゲート T G、さらにはゲート電極 2 5 に接続された構成となっている。また、埋込配線 2 7 には、センサ基板 2 に設けられた貫通ビア 2 3 も接続され、トランジスタ T r および埋込配線 2 7 等によって画素回路が構成されている。

【0026】

10

以上のような埋込配線 2 7 が形成された層間絶縁膜 2 6 上に、絶縁性の保護膜 2 b が設けられ、この保護膜 2 b 表面においてセンサ基板 2 が回路基板 9 に貼り合わせられている。

【0027】

[回路基板 9]

回路基板 9 は、例えば単結晶シリコンからなる半導体基板を薄膜化したものである。この回路基板 9 において、センサ基板 2 側に向かう表面層には、トランジスタ T r のソース / ドレイン 3 1、さらにはここでの図示を省略した不純物層、および素子分離 3 2 などが設けられている。

【0028】

20

さらに回路基板 9 には、これを貫通する貫通ビア 3 3 が設けられている。この貫通ビア 3 3 は、回路基板 9 を貫通して形成された接続孔内に、分離絶縁膜 3 4 を介して埋め込まれた導電性材料によって構成されている。

【0029】

[配線層 9 a (回路基板 9 側)]

回路基板 9 の表面上に設けられた配線層 9 a は、回路基板 9 との界面側に、ここで図示を省略したゲート絶縁膜を介して設けられたゲート電極 3 5、さらにはここでの図示を省略した他の電極を有している。これらのゲート電極 3 5 および他の電極は、層間絶縁膜 3 6 で覆われており、この層間絶縁膜 3 6 に設けられた溝パターン内にはたとえば銅 (Cu) を用いた埋込配線 3 7 が多層配線として設けられている。これらの埋込配線 3 7 は、ビアによって相互に接続され、また一部がソース / ドレイン 3 1 やゲート電極 3 5 に接続された構成となっている。また、埋込配線 3 7 には、回路基板 9 に設けられた貫通ビア 3 3 も接続され、トランジスタ T r および埋込配線 3 7 等によって駆動回路が構成されている。

30

【0030】

以上のような埋込配線 3 7 が形成された層間絶縁膜 3 6 上に、絶縁性の保護膜 9 b が設けられ、この保護膜 9 b 表面において回路基板 9 がセンサ基板 2 に貼り合わせられている。また、回路基板 9 において、配線層 9 a が設けられた表面側とは逆の裏面側には、回路基板 9 を覆う保護膜 9 c が設けられ、この保護膜 9 c には貫通ビア 3 3 を露出させるパッド開口 3 3 a が設けられている。

40

【0031】

[絶縁層 1 4]

絶縁層 1 4 は、センサ基板 2 の受光面 A 上に設けられている。この絶縁層 1 4 は、画素領域 4 の膜厚が周辺領域 7 の膜厚よりも薄い段差構造を有しているところが特徴的である。このような絶縁層 1 4 は、例えば異なる絶縁材料を用いた積層膜として構成され、ここでは一例として受光面 A 側から順に反射防止膜 1 4 -1、界面準位抑制膜 1 4 -2、エッチングストップ膜 1 4 -3、溝形成膜 1 4 -4、キャップ膜 1 4 -5 の 5 層構造である。

【0032】

反射防止膜 1 4 -1 は、例えば酸化ハフニウム (HfO<sub>2</sub>)、酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>)、または窒化シリコンなど、酸化シリコンよりも高屈折率の絶縁性材料を用いて構成さ

50

れる。界面準位抑制膜 14-2は、例えば酸化シリコン (SiO<sub>2</sub>) を用いて構成される。エッティングストップ膜 14-3は、上層の溝形成膜 14-4を構成する材料に対してエッティング選択比が低く抑えられる材料が用いられ、例えば窒化シリコン (SiN) を用いて構成される。溝形成膜 14-4は、例えば酸化シリコン (SiO<sub>2</sub>) を用いて構成される。キャップ膜 14-5は、例えば窒化シリコン (SiN) を用いて構成される。

#### 【0033】

以上のような 5 層構造の絶縁層 14 は、画素領域 4 においては、上層部分のキャップ膜 14-5、溝形成膜 14-4、およびエッティングストップ膜 14-3が除去され、反射防止膜 14-1と界面準位抑制膜 14-2との 2 層構造に薄型化されている。一方、周辺領域 7 の厚膜部分では、上層から 2 番目の溝形成膜 14-4に、次に説明する配線 8 を内設する配線溝が形成されている。

10

#### 【0034】

##### [配線 8]

配線 8 は、受光面 A 側における周辺領域 7 において、絶縁層 14 に埋め込まれた埋込配線として設けられている。この配線 8 は、絶縁層 14 を構成する溝形成膜 14-4に形成された配線溝内に埋め込まれ、その下層のエッティングストップ膜 14-3、界面準位抑制膜 14-2、および反射防止膜 14-1を貫通して設けられた貫通ビア 23 に接続されている。

#### 【0035】

このような配線 8 および貫通ビア 23 は、溝形成膜 14-4に形成された配線溝とその下層の接続孔の内壁を連続的に覆う分離絶縁膜 24 を介して、これらの配線溝及び接続孔に銅 (Cu) を埋め込んで一体に構成されている。この分離絶縁膜 24 は、例えば窒化シリコンのような銅 (Cu) の拡散防止機能を有する材料を用いて構成される。尚、配線 8 の上部は、絶縁層 14 の最上層を構成するキャップ膜 14-5で覆われた状態となっている。

20

#### 【0036】

##### [遮光膜 16]

遮光膜 16 は、受光面 A 側における画素領域 4 において、絶縁層 14 の段差下部、つまり、絶縁層 14 において積層構造の下層部分を構成する界面準位抑制膜 14-2の上部に設けられている。このような遮光膜 16 は、各光電変換部 20 に対応する複数の受光開口 16a を備えている。

#### 【0037】

30

このような遮光膜 16 は、アルミニウム (Al) やタンゲステン (W) のような遮光性に優れた導電性材料を用いて構成され、絶縁層 14 に設けた開口においてセンサ基板 2 に対して接地された状態で設けられている。

#### 【0038】

##### [透明保護膜 17]

透明保護膜 17 は、絶縁層 14 および遮光膜 16 を覆う状態で設けられている。この透明平坦化膜 17 は、例えばアクリル樹脂などが用いられる。

#### 【0039】

##### [カラーフィルタ 18]

カラーフィルタ 18 は、各光電変換部 20 に対応して設けられ、各光電変換部 20 に対応する各色で構成されている。各色のカラーフィルタ 18 の配列が限定されることはない。

40

#### 【0040】

##### [オンチップレンズ 19]

オンチップレンズ 19 は、各光電変換部 20 に対応して設けられ、各光電変換部 20 に入射光が集光されるように構成されている。

#### 【0041】

##### <固体撮像装置の製造方法>

次に、上述した構成の固体撮像装置 1-1の製造方法を図 3 ~ 図 6 の断面工程図に基づいて説明する。

50

## 【0042】

## [図3A]

先ず図3Aに示すように、センサ基板2における画素領域4に、複数の光電変換部20を配列形成すると共に、センサ基板2にフローティングディフュージョンFD他の不純物層や素子分離22を形成する。次に、センサ基板2の表面上に転送ゲートTGおよびゲート電極25を形成し、さらに層間絶縁膜26と共に埋込配線27を形成して配線層2aを設け、この配線層2aの上部を保護膜2bで覆う。一方、回路基板9に、ソース／ドレイン31他の不純物層や素子分離32を形成する。次に、回路基板9の表面上にゲート電極35を形成し、さらに層間絶縁膜36と共に埋込配線37を形成して配線層9aを設け、また配線層9aから回路基板9にかけてビア33を形成し、配線層9aの上部を保護膜9bで覆う。

10

## 【0043】

以上の後、センサ基板2と回路基板9とを、保護膜2bと保護膜9bとの間で貼り合わせる。貼り合わせの終了後には、必要に応じてセンサ基板2の受光面A側を薄膜化する。以上までの工程は、特に手順が限定されることはなく、通常の貼り合わせ技術を適用して行うことができる。

## 【0044】

## [図3B]

次に図3Bに示すように、センサ基板2の受光面A上に、反射防止膜14-1、界面準位抑制膜14-2、エッチングストップ膜14-3、および溝形成膜14-4をこの順に積層成膜する。反射防止膜14-1は、例えば酸化ハフニウム(HfO<sub>2</sub>)からなり、原子層蒸着法によって膜厚10nm～300nm(例えば60nm)で成膜される。界面準位抑制膜14-2は、例えば酸化シリコン(SiO<sub>2</sub>)からなり、P-CVD(plasma-chemical vapor deposition)法によって膜厚200nmで成膜される。エッチングストップ膜14-3は、例えば窒化シリコン(SiN)からなり、P-CVD法によって膜厚360nmで成膜される。溝形成膜14-4は、例えば酸化シリコン(SiO<sub>2</sub>)からなり、P-CVD法によって膜厚200nmで成膜される。

20

## 【0045】

以上の4層は、上述した段差構造を有する絶縁層(14)の一部を構成する膜として成膜される。

30

## 【0046】

## [図4A]

その後、図4Aに示すように、センサ基板2の周辺領域7において、最上層の溝形成膜14-4に配線溝8aを形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、酸化シリコン(SiO<sub>2</sub>)からなる溝形成膜14-4のエッチングを行う。このエッチングにおいては、下層の窒化シリコン(SiN)からなるエッチングストップ膜14-3でエッチングをストップさせる。エッチングの終了後にはレジストパターンを除去する。

## 【0047】

## [図4B]

次に、図4Bに示すように、配線溝8aの底部に、必要に応じた深さの各接続孔23aを形成する。これらの各接続孔23aは、センサ基板2の表面側に設けられた、配線層2aの埋込配線27または配線層9aの埋込配線37の上部に達する各深さで形成されれば良く、底部に埋込配線27および埋込配線37を露出させなくても良い。この際、接続孔23aの深さ毎に、ここでの図示を省略した複数のレジストパターンを形成し、これらのレジストパターンをマスクにしてセンサ基板2および層間絶縁膜26に対して複数回のエッチングを行う。各エッチングの終了後には各レジストパターンを除去する。

40

## 【0048】

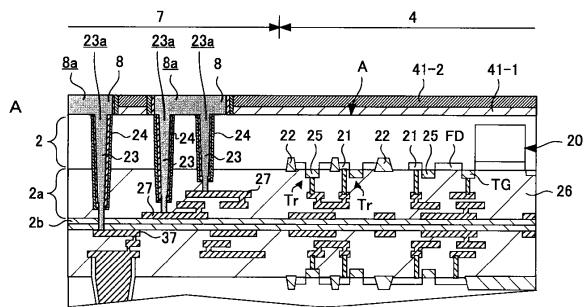

## [図5A]

次いで図5Aに示すように、配線溝8aおよび接続孔23aの内壁を覆う状態で、溝形

50

成膜 1 4 -4 上に、分離絶縁膜 2 4 を成膜する。ここでは例えば 2 層構造の分離絶縁膜 2 4 を形成することとし、先ず p - C V D 法によって膜厚 7 0 n m の窒化シリコン膜 2 4 -1 を成膜し、次いで p - C V D 法によって膜厚 9 0 0 n m の酸化シリコン膜 2 4 -2 を成膜する。尚、分離絶縁膜 2 4 は、積層構造に限定されることはなく、例えば酸化シリコン膜または窒化シリコン膜の単層構造であっても良い。

【 0 0 4 9 】

【 図 5 B 】

その後、図 5 B に示すように、異方性の高いエッティング条件により分離絶縁膜 2 4 をエッティング除去することにより、溝形成膜 1 4 -4 上および配線溝 8 a の底部、さらには接続孔 2 3 a の底部の分離絶縁膜 2 4 を除去する。引き続き、異方性の高いエッティング条件により接続孔 2 3 a の底部の層間絶縁膜 2 6 、保護膜 2 b 、および保護膜 9 b をエッティング除去し、接続孔 2 3 a を掘り進める。これにより、各接続孔 2 3 a の底部に埋込配線 2 7 または埋込配線 3 7 を露出させる。

【 0 0 5 0 】

尚、このようなエッティングにおいては、層間絶縁膜 2 6 が酸化シリコン膜で構成されている場合、分離絶縁膜 2 4 の下層の酸化シリコンからなる溝形成膜 1 4 -4 の表面層もエッティングによって膜減りする。また保護膜 2 b および保護膜 9 b が窒化シリコン膜で構成されている場合、配線溝 8 a の底部の窒化シリコンからなるエッティングストップ膜 1 4 -3 もエッティングによって膜減りする。したがって、これらの膜減り量を考慮して、窒化シリコンからなるエッティングストップ膜 1 4 -3 および酸化シリコンからなる溝形成膜 1 4 -4 の成膜時の膜厚を設定する。

【 0 0 5 1 】

【 図 5 C 】

次に、図 5 C に示すように、配線溝 8 a および接続孔 2 3 a を導電性材料で一体に埋め込むことにより、配線溝 8 a 内に埋込配線として配線 8 を形成し、さらにセンサ基板 2 を貫通する接続孔 2 3 a 内に貫通ビア 2 3 を形成する。ここでは先ず、配線溝 8 a および接続孔 2 3 a 内を埋め込む状態で、溝形成膜 1 4 -4 上に導電性材料膜 [ 例えば銅 ( C u ) 膜 ] を成膜し、次に化学的機械研磨 ( C M P ) 法によって溝形成膜 1 4 -4 上の導電性材料膜を研磨除去する。これにより、配線溝 8 a および接続孔 2 3 a 内のみに導電性材料膜を残し、センサ基板 2 の受光面 A 側における周辺領域 7 に、配線 8 およびこれに接続された貫通ビア 2 3 を形成する。

【 0 0 5 2 】

【 図 6 A 】

次いで図 6 A に示すように、配線 8 および溝形成膜 1 4 -4 上を覆う状態で、配線 8 を構成する銅 ( C u ) に対する拡散防止効果を有するキャップ膜 1 4 -5 を成膜する。ここではキャップ膜 1 4 -5 として、例えば窒化シリコン膜を 7 0 n m の膜厚で成膜する。これにより、センサ基板 2 の受光面 A 上に、反射防止膜 1 4 -1 、界面準位抑制膜 1 4 -2 、エッティングストップ膜 1 4 -3 、溝形成膜 1 4 -4 、およびキャップ膜 1 4 -5 をこの順に積層させた 5 層構造の絶縁層 1 4 を形成する。尚、最上層の窒化シリコンからなるキャップ膜 1 4 -5 上には、さらに必要に応じて酸化シリコン膜を成膜しても良い。

【 0 0 5 3 】

【 図 6 B 】

その後、図 6 B に示すように、絶縁層 1 4 において画素領域 4 に対応する部分を、周辺領域 7 に対して選択的に薄膜化し、これにより絶縁層 1 4 に段差構造を形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、窒化シリコン ( S i N ) からなるキャップ膜 1 4 -5 をエッティングし、その後条件を変えて酸化シリコン ( S i O <sub>2</sub> ) からなる溝形成膜 1 4 -4 をエッティングする。この際、下層の窒化シリコン ( S i N ) からなるエッティングストップ膜 1 4 -3 でエッティングをストップさせる。その後、さらに条件を変えてエッティングストップ膜 1 4 -3 をエッティングする。

【 0 0 5 4 】

10

20

30

40

50

以上により、受光面 A 上の絶縁層 14 は、画素領域 4 の膜厚が周辺領域 7 の膜厚よりも薄い段差構造であって、画素領域 4 上において薄膜化したキャビティ構造となる。このような状態において、画素領域 4 には、反射防止膜 14-1 と界面準位抑制膜 14-2 のみが残される。一方、周辺領域 7 には、5 層構造の絶縁層 14 がそのまま残される。また絶縁層 14 の段差構造における段差は 500 nm 程度となる。

【0055】

尚、絶縁層 14 における薄膜部分は、配線 8 に影響のない範囲でできるだけ広範囲に設定されて良く、これによって絶縁層 14 の段差形状が、以降に形成する透明平坦化膜の塗布ムラを悪化させることによって光電変換部 20 への光入射に影響を及ぼすことを防止する。

10

【0056】

【図 6C】

次に、図 6C に示すように、絶縁層 14 の段差下部に、センサ基板 2 を露出させる開口 14a を形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、界面準位抑制膜 14-2 と反射防止膜 14-1 をエッチングする。尚、この開口 14a は、光電変換部 20 の上方を避けた位置に形成される。

【0057】

次に、絶縁層 14 の段差下部に、開口 14a を介してセンサ基板 2 に接地された遮光膜 16 をパターン形成する。この遮光膜 16 は、光電変換部 20 に対応する受光開口 16a を有している。ここでは先ず、スパッタ成膜法によって、絶縁層 14 上にアルミニウム (A1) やタンゲステン (W) のような遮光性を有する導電性材料膜を成膜する。その後、ここでの図示を省略したレジストパターンをマスクにして導電性材料膜をパターンエッチングすることにより、絶縁層 14 の段差下部を広く覆うと共に、各光電変換部 20 に対応する受光開口 16a を有し、センサ基板 2 に接地された遮光膜 16 を形成する。

20

【0058】

このような遮光膜 16 は、絶縁層 14 の段差上部で除去され、段差下部を広く覆う形状で良い。これにより、絶縁層 14 の段差を広い範囲で軽減する。

【0059】

【図 2】

以上の後には先の図 2 に示したように、遮光膜 16 を覆う状態で光透過性を有する材料からなる透明保護膜 17 を成膜する。透明保護膜 17 の成膜は、スピンドルコート法のような塗布法によって行う。次に、透明保護膜 17 上に、光電変換部 20 に対応する各色のカラーフィルタ 18 を形成し、さらにこの上部に光電変換部 20 に対応するオンチップレンズ 19 を形成する。また回路基板 9 の露出面を研磨することで回路基板 9 を薄膜化し、ピア 33 を露出させて貫通ピア 33 とする。その後、貫通ピア 33 を覆う状態で回路基板 9 上に保護膜 9c を成膜し、貫通ピア 33 を露出するパッド開口 33a を形成することにより、固体撮像装置 1-1 を完成させる。

30

【0060】

<第 1 実施形態の効果>

以上説明した構成の固体撮像装置 1-1 は、画素領域 4 の外側の周辺領域 7 に配線 8 を設けた裏面照射型の固体撮像装置である。このような構成において、受光面 A 上には、周辺領域 7 に対して画素領域 4 で膜厚が薄い段差構造の絶縁層 14 を設け、この上部にオンチップレンズ 19 を設けている。これにより、周辺領域 7 においては配線 8 の構成に影響を与えることなく絶縁層 14 の膜厚が確保され、一方、画素領域 4 においては絶縁層 14 を薄膜化してこの上部のオンチップレンズ 19 と受光面 A との距離を小さくすることができる。

40

【0061】

ここで従来構造のように、遮光膜を絶縁層で覆い、この絶縁層の上部に配線を設けた構成であれば、さらにこの配線を覆う状態で絶縁膜を設けてこの上方にオンチップレンズが配置される。このため受光面上には、少なくとも二層の絶縁膜を介してこの上部にオンチ

50

ップレンズが配置されることになり、受光面からオンチップレンズまでの距離が大きく、光電変換部においての受光特性を劣化させる要因となっていた。しかも、遮光膜上に成膜した絶縁膜の表面には、遮光膜のパターン形状が引き継がれるため、このような絶縁膜に対して埋込配線形成のための配線溝を形成しようとした場合、精度の良いパターニングを行うことができない。そこで、遮光膜の上部に平坦化絶縁膜を形成することで、配線溝形成のためのパターニングの精度を確保することが考えられる。しかしながら、平坦化絶縁膜の形成によって受光面からオンチップレンズまでの距離がさらに大きくなるため、光電変換部においての受光特性はさらに劣化することになる。

#### 【0062】

これに対して上述した第1実施形態の製造方法は、絶縁層14とこれに埋め込まれた配線8とを形成した後、画素領域4における絶縁層14を薄膜化して段差構造に成形し、その後、画素領域4にオンチップレンズ19を形成する手順である。このため、画素領域4には配線8の形成に必要な絶縁層部分が厚膜で残されることではなく、オンチップレンズ19と受光面Aとの距離を小さくすることができる。

10

#### 【0063】

以上により本第1実施形態によれば、画素領域4の外側の周辺領域7に配線8を設けた裏面照射型の固体撮像装置1-1において、配線8のパターン精度を確保しつつ、オンチップレンズ19と受光面Aとの距離を小さくして光電変換部20においての受光特性の向上を図ることが可能になる。具体的には、受光面Aとカラーフィルタ18の下面と間の距離を600nm程度とすることができる。これにより、光電変換部20に対する入射光の減衰や、斜め光入射の場合の隣接画素への光の漏れ込みによる混色の悪化などの光学特性を改善することが可能となる。尚、本第1実施形態は、遮光膜16を設けない構成にも適用可能である。この場合であれば、受光面Aとカラーフィルタ18間の距離を300nm程度にまで近づけることが可能であり、入射角が大きくなったときの、シェーディングや混色をさらに大幅に改善することが可能である。

20

#### 【0064】

また特に第1実施形態の製造方法では、図6Bを用いて説明したように、絶縁層14に段差構造を形成する場合に、エッチングストップ膜14-3でエッチングをストップさせた後に、条件を変えてエッチングストップ膜14-3をエッチングする手順としている。これにより、画素領域4の受光面A上に、制御性良好に反射防止膜14-1と界面準位抑制膜14-2とを残すことができる。この結果、安定した受光特性および暗電流防止効果を得ることが可能になる。また、受光面Aをエッチングダメージに晒すことなく良好に保つことも可能である。

30

#### 【0065】

##### 第2実施形態

###### <固体撮像装置の構成>

(絶縁パターンを絶縁膜で覆った段差構造の絶縁層を設けた例)

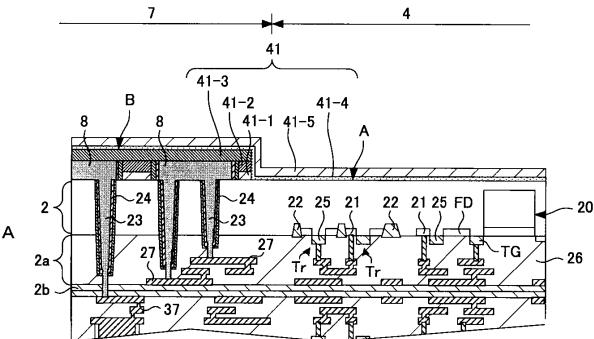

図7は、第2実施形態の固体撮像装置1-2の構成を示す要部断面図であり、図1における画素領域4と周辺領域7との境界付近の断面図である。以下、この要部断面図に基づいて第2実施形態の固体撮像装置1-2の構成を説明する。

40

#### 【0066】

図7に示す第2実施形態の固体撮像装置1-2が、図2を用いて説明した第1実施形態の固体撮像装置と異なるところは、段差構造を有する絶縁層41の層構造にあり、他の構成は第1実施形態と同様である。

#### 【0067】

すなわち絶縁層41は、例えば酸化シリコン膜41-1と、窒化シリコン膜41-2と、窒化シリコンからなるキャップ膜41-3とを、受光面A側からこの順に積層させた3層構造の絶縁パターンを周辺領域7に有している。また絶縁層41は、このような3層構造の絶縁パターンを覆う状態で、反射防止膜41-4と界面準位抑制膜41-5とを、画素領域4および周辺領域7に有している。

50

## 【0068】

このような5層構造の絶縁層41は、画素領域4においては反射防止膜41-4と界面準位抑制膜41-5との2層構造である。これに対して周辺領域7においては、酸化シリコン膜41-1と、窒化シリコン膜41-2と、窒化シリコンからなるキャップ膜41-3と、反射防止膜41-4と、界面準位抑制膜41-5との5層構造である。

## 【0069】

以上のような積層構造の絶縁層41において周辺領域7の厚膜部分では、下層の酸化シリコン膜41-1と窒化シリコン膜41-2が溝形成膜となり、配線8を内設する配線溝が形成されている。そして、センサ基板2を貫通して設けられた貫通ビア23が配線8に接続された構成となっている。

10

## 【0070】

またこの絶縁層41上における段差下部には、絶縁パターンを覆う反射防止膜41-4および界面準位抑制膜41-5の上方に、遮光膜16が設けられている。この遮光膜16は、第1実施形態と同様のものであり、絶縁層41に設けた開口においてセンサ基板2に対して接地された状態で設けられている。

## 【0071】

## &lt;固体撮像装置の製造方法&gt;

次に、上述した構成の固体撮像装置1-2の製造方法を図8～図10の断面工程図に基づいて説明する。

## 【0072】

20

## [図8A]

先ず図8Aに示すように、センサ基板2と回路基板とを貼り合わせ、必要に応じてセンサ基板2の受光面A側を薄膜化するまでを、第1実施形態で図3Aを用いて説明したと同様に行う。その後、センサ基板2の受光面A上に、酸化シリコン膜41-1および窒化シリコン膜41-2をこの順に成膜する。

## 【0073】

## [図8B]

次に図8Bに示すように、センサ基板2の周辺領域7において、酸化シリコン膜41-1および窒化シリコン膜41-2に配線溝8aを形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、窒化シリコン膜41-2をエッチングし、さらに酸化シリコン膜41-1をエッチングする。このエッチングにおいては、さらに下層のセンサ基板2の表面層をエッチングしても良い。エッチングの終了後にはレジストパターンを除去する。

30

## 【0074】

## [図8C]

次いで図8Cに示すように、配線溝8aの底部に、必要に応じた深さの各接続孔23aを形成する。これらの各接続孔23aは、第1実施形態と同様であり、センサ基板2の表面側に設けられた埋込配線27または埋込配線37の上部に達する各深さで形成される。その後は、第1実施形態において図5A～図5Cを用いて説明した手順と同様の手順を行う。

40

## 【0075】

## [図9A]

以上により図9Aに示すように、配線溝8aおよび接続孔23aの内壁に、積層構造の分離絶縁膜24を形成し、これらの内部を銅(Cu)で一体に埋め込むと共に埋込配線27または埋込配線37に接続された配線8と貫通ビア23とを形成する。

## 【0076】

## [図9B]

その後図9Bに示すように、配線8および窒化シリコン膜41-2上を覆う状態で、配線8を構成する銅(Cu)に対する拡散防止効果を有するキャップ膜41-3を成膜する。ここではキャップ膜41-3として、例えば窒化シリコン膜を70nmの膜厚で成膜する。こ

50

れにより、センサ基板2の受光面A上に、酸化シリコン膜41-1、窒化シリコン膜41-2、およびキャップ膜41-3の3層を積層させる。

【0077】

次に、これらの3層の積層膜における画素領域4に対応する部分を、周辺領域7に対して選択的にエッティング除去する。これにより、周辺領域7に対応する受光面A上に、3層の積層膜をパターニングしてなる絶縁パターンBを形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、窒化シリコンからなるキャップ膜41-3および窒化シリコン膜41-2をエッティングし、さらにエッティング条件を変更して酸化シリコン膜41-1をエッティングする。酸化シリコン膜41-1のエッティングにおいては、ウェットエッティングを行うことにより、センサ基板2に対するダメージを抑えて画素領域4の受光面Aを露出させる。

【0078】

【図10A】

その後、図10Aに示すように、周辺領域7の絶縁パターンBを覆う状態で、センサ基板2における受光面A上に、例えば酸化ハフニウム(HfO<sub>2</sub>)からなる反射防止膜41-4、および酸化シリコン(SiO<sub>2</sub>)からなる界面準位抑制膜41-5をこの順に成膜する。これにより、受光面A上には、絶縁パターンBとこれを覆う反射防止膜41-4と界面準位抑制膜41-5とで構成された絶縁層41が形成される。

【0079】

この絶縁層41は、画素領域4の膜厚が周辺領域7の膜厚よりも薄い段差構造であって、画素領域4上において薄膜化したキャビティ構造となる。このような状態において、画素領域4には、反射防止膜41-4と界面準位抑制膜41-5のみが配置される。一方、周辺領域7には、絶縁パターンBと反射防止膜41-4と界面準位抑制膜41-5とで構成された5層構造の絶縁層41部分が配置される。

【0080】

尚、絶縁層41における薄膜部分は、配線8に影響のない範囲でできるだけ広範囲に設定されて良く、これによって絶縁層41の段差形状が、以降に形成する透明平坦化膜の塗布ムラを悪化させることによって光電変換部20への光入射に影響を及ぼすことを防止することは、第1実施形態と同様である。

【0081】

【図10B】

次に、図10Bに示すように、絶縁層41の段差下部にセンサ基板2を露出させる開口41aを形成し、次いで画素領域4における絶縁層41上に開口41aを介してセンサ基板2に接地された遮光膜16をパターン形成する。この遮光膜16には、各光電変換部20に対応する受光開口16aを設ける。以上の工程は、第1実施形態において図6Cを用いて説明した手順と同様の手順で行う。また、このような遮光膜16は、絶縁層41の段差上部で除去され、段差下部を広く覆う形状で良く、これにより、絶縁層41の段差を広い範囲で軽減することができることも第1実施形態と同様である。

【0082】

【図7】

以上の後には先の図7に示したように、遮光膜16を覆う状態で光透過性を有する材料からなる透明保護膜17を、スピンドルコート法のような塗布法によって成膜する。次に、透明保護膜17上に、光電変換部20に対応する各色のカラーフィルタ18を形成し、さらにこの上部に光電変換部20に対応する各オンチップレンズ19を形成する。また回路基板9の露出面を研磨することで回路基板9を薄膜化し、ビア33を露出させて貫通ビア33とする。その後、貫通ビア33を覆う状態で回路基板9上に保護膜9cを成膜し、貫通ビア33を露出するパッド開口33aを形成することにより、固体撮像装置1-2を完成させる。

【0083】

<第2実施形態の効果>

10

20

30

40

50

以上説明した構成の固体撮像装置 1-2は、第1実施形態の固体撮像装置と同様に、周辺領域 7 に配線 8 を設けた裏面照射型であり、受光面 A 上には画素領域 4 で膜厚が薄い段差構造の絶縁層 4 1 を設け、この上部にオンチップレンズ 1 9 を設けた構成である。したがって、第1実施形態と同様に、配線 8 のパターン精度を確保しつつ、オンチップレンズ 1 9 と受光面 A との距離を小さくして光電変換部 2 0 においての受光特性の向上を図ることが可能である。

【0084】

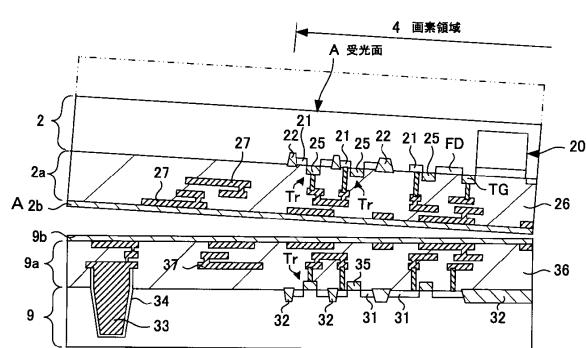

第3実施形態

<固体撮像装置の構成>

(段差構造の絶縁層とセンサ基板を掘り込んだ埋込配線を設けた例)

10

図 1 1 は、第 3 実施形態の固体撮像装置 1-3 の構成を示す要部断面図であり、図 1 における画素領域 4 と周辺領域 7 との境界付近の断面図である。以下、この要部断面図に基づいて第 3 実施形態の固体撮像装置 1-3 の構成を説明する。

【0085】

図 1 1 に示す第 3 実施形態の固体撮像装置 1-3 が、図 2 を用いて説明した第 1 実施形態の固体撮像装置と異なるところは、段差構造を有する絶縁層 4 3 の層構造と、配線 8 の埋込部分にあり、他の構成は第 1 実施形態と同様である。

【0086】

すなわち絶縁層 4 3 は、受光面 A 側から順に反射防止膜 4 3-1、界面準位抑制膜 4 3-2、エッチングストップ膜 4 3-3、キャップ膜 4 3-4 の 4 層構造である。このような 4 層構造の絶縁層 4 3 は、画素領域 4 においては、反射防止膜 4 3-1 と界面準位抑制膜 4 3-2 との 2 層構造に薄型化されており、これによって画素領域 4 の膜厚が周辺領域 7 の膜厚よりも薄い段差構造となっている。

20

【0087】

以上のような積層構造の絶縁層 4 3 において周辺領域 7 の厚膜部分では、キャップ膜 4 3-4 よりも下層のエッチングストップ膜 4 3-3、界面準位抑制膜 4 3-2、反射防止膜 4 3-1、およびセンサ基板 2 の表面層に、配線 8 を内設する配線溝が形成されている。つまり、センサ基板 2 の表面層にも、エッチングによって掘り込んだ配線溝が形成されており、この配線溝内に配線 8 が埋め込まれているのである。また、センサ基板 2 を貫通して設けられた貫通ピア 2 3 が、配線 8 に接続された構成となっている。

30

【0088】

<固体撮像装置の製造方法>

次に、上述した構成の固体撮像装置 1-3 の製造方法を図 1 2 ~ 図 1 3 の断面工程図に基づいて説明する。

【0089】

[図 1 2 A]

先ず図 1 2 A に示すように、センサ基板 2 と回路基板とを貼り合わせ、必要に応じてセンサ基板 2 の受光面 A 側を薄膜化するまでを、第 1 実施形態で図 3 A を用いて説明したと同様に行う。その後、センサ基板 2 の受光面 A 上に、例えば酸化ハフニウム (HfO<sub>2</sub>) からなる反射防止膜 4 3-1、酸化シリコン (SiO<sub>2</sub>) からなる界面準位抑制膜 4 3-2、および窒化シリコン (SiN) からなるエッチングストップ膜 4 3-3 をこの順に積層成膜する。以上の 3 層は、上述した段差構造を有する絶縁層 (4 3) の一部を構成する膜として成膜される。

40

【0090】

その後、センサ基板 2 の周辺領域 7 において、反射防止膜 4 3-1、界面準位抑制膜 4 3-2、エッチングストップ膜 4 3-3、さらにはセンサ基板 2 の表面層に、配線溝 8 a' を形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、エッチングストップ 4 3-3 からセンサ基板 2 の表面層までをエッチングする。エッチングの終了後にはレジストパターンを除去する。

【0091】

50

## [図12B]

次に図12Bに示すように、配線溝8a'の底部に、必要に応じた深さの各接続孔23aを形成する。これらの各接続孔23aは、第1実施形態と同様であり、センサ基板2の表面側に設けられた埋込配線27または埋込配線37の上部に達する各深さで形成される。その後は、第1実施形態において図5A～図5Cを用いて説明した手順と同様の手順を行う。

## 【0092】

## [図12C]

以上により図12Cに示すように、配線溝8a'および接続孔23aの内壁に、積層構造の分離絶縁膜24を形成し、これらの内部を銅(Cu)で一体に埋め込むと共に埋込配線27または埋込配線37に接続された配線8と貫通ビア23とを形成する。

10

## 【0093】

## [図13A]

その後、図13Aに示すように、配線8およびエッティングトップ膜43-3上を覆う状態で、配線8を構成する銅(Cu)に対する拡散防止効果を有するキャップ膜43-4を成膜する。ここでは例えばキャップ膜として、窒化シリコン膜を70nmの膜厚で成膜する。これにより、センサ基板2の受光面A上に、反射防止膜43-1、界面準位抑制膜43-2、エッティングトップ膜43-3、およびキャップ膜43-4をこの順に積層させた4層構造の絶縁層43を形成する。尚、最上層の窒化シリコンからなるキャップ膜43-4上には、さらに必要に応じて酸化シリコン膜を成膜しても良い。

20

## 【0094】

以上のようにして積層構造の絶縁層43および配線8を形成した後、絶縁層43において画素領域4に対応する部分を選択的に薄膜化し、これにより絶縁層43に段差構造を形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、窒化シリコン(SiN)からなるキャップ膜43-4およびエッティングトップ膜43-3をエッティングする。

## 【0095】

以上により、センサ基板2における受光面A上には、画素領域4の膜厚が周辺領域7の膜厚よりも薄い段差構造であって、画素領域4上において薄膜化したキャビティ構造の絶縁層43が設けられた状態となる。このような状態において、画素領域4には、反射防止膜43-1と界面準位抑制膜43-2のみが残される。一方、周辺領域7には、4層構造の絶縁層43がそのまま残される。

30

## 【0096】

尚、絶縁層43における薄膜部分は、配線8に影響のない範囲でできるだけ広範囲に設定されて良く、これによって絶縁層43の段差形状が、以降に形成する透明平坦化膜の塗布ムラを悪化させることによって光電変換部20への光入射に影響を及ぼすことを防止することは、第1実施形態と同様である。

## 【0097】

## [図13B]

次に、図13Bに示すように、絶縁層43の段差下部にセンサ基板2を露出させる開口43aを形成し、次いで画素領域4における絶縁層43上に開口43aを介してセンサ基板2に接地された遮光膜16をパターン形成する。この遮光膜16には、各光電変換部20に対応する受光開口16aを設ける。以上の工程は、第1実施形態において図6Cを用いて説明した手順と同様の手順で行う。また、このような遮光膜16は、絶縁層43の段差上部で除去され、段差下部を広く覆う形状で良く、これにより、絶縁層43の段差を広い範囲で軽減することができることも第1実施形態と同様である。

40

## 【0098】

## [図11]

以上の後には先の図11に示したように、遮光膜16を覆う状態で光透過性を有する材料からなる透明保護膜17を、スピンドルコート法のような塗布法によって成膜する。次に、

50

透明保護膜17上に、光電変換部20に対応する各色のカラーフィルタ18を形成し、さらにこの上部に光電変換部20に対応する各オンチップレンズ19を形成する。また回路基板9の露出面を研磨することで回路基板9を薄膜化し、ビア33を露出させて貫通ビア33とする。その後、貫通ビア33を覆う状態で回路基板9上に保護膜9cを成膜し、貫通ビア33を露出するパッド開口33aを形成することにより、固体撮像装置1-3を完成させる。

#### 【0099】

##### <第3実施形態の効果>

以上説明した構成の固体撮像装置1-3は、第1実施形態の固体撮像装置と同様に、周辺領域7に配線8を設けた裏面照射型であり、受光面A上には画素領域4で膜厚が薄い段差構造の絶縁層43を設け、この上部にオンチップレンズ19を設けた構成である。10 したがって、第1実施形態と同様に、配線8のパターン精度を確保しつつ、オンチップレンズ19と受光面Aとの距離を小さくして光電変換部20においての受光特性の向上を図ることが可能である。また第1実施形態と同様に、受光面Aをエッチングダメージに晒すことなく良好に保つことも可能である。

#### 【0100】

尚、本第3実施形態においては、配線8を埋め込む配線溝8a'を、センサ基板2と絶縁層43の下部とに設けた構成を説明した。しかしながら、配線溝8a'をセンサ基板2のみに形成し、センサ基板2に対して完全に埋め込まれた配線8としても良い。この場合であっても、絶縁層43は、周辺領域7においては配線8上を覆うのに必要な膜厚に確保され、画素領域4においてはこれよりも薄い膜厚に薄膜化された段差構造とすることで同様の効果を得ることができる。20

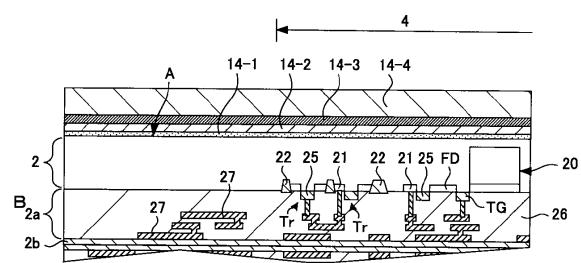

#### 【0101】

##### 第4実施形態

##### <固体撮像装置の構成>

##### (段差構造の絶縁層と積層配線を設けた例)

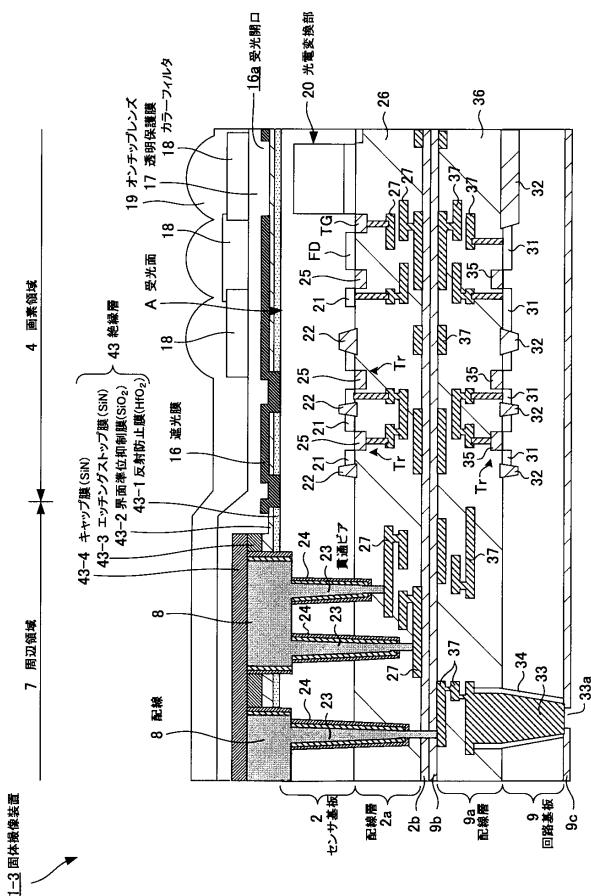

図14は、第4実施形態の固体撮像装置1-4の構成を示す要部断面図であり、図1における画素領域4と周辺領域7との境界付近の断面図である。以下、この要部断面図に基づいて第4実施形態の固体撮像装置1-4の構成を説明する。

#### 【0102】

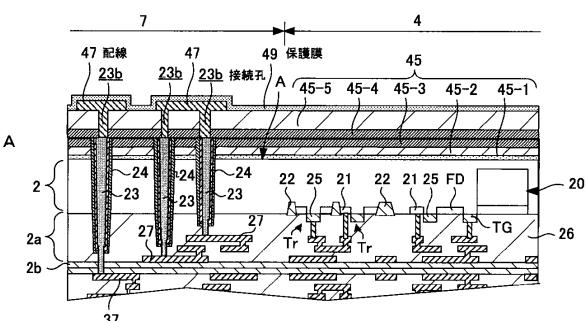

図14に示す第4実施形態の固体撮像装置1-4が、図2を用いて説明した第1実施形態の固体撮像装置と異なるところは、段差構造を有する絶縁層45の層構造と、配線47の構成にあり、他の構成は第1実施形態と同様である。30

#### 【0103】

すなわち絶縁層45は、受光面側から順に反射防止膜45-1、界面準位抑制膜45-2、エッチングストップ膜45-3、キャップ膜45-4、および酸化シリコンからなる層間膜45-5の5層構造である。このような5層構造の絶縁層45は、画素領域4においては、反射防止膜45-1と界面準位抑制膜45-2との2層構造に薄型化されており、これによって画素領域4の膜厚が周辺領域7の膜厚よりも薄い段差構造となっている。

#### 【0104】

以上のような積層構造の絶縁層45において周辺領域7の厚膜部分では、センサ基板2を貫通して設けられた貫通ビア23が、エッチングストップ膜45-3の表面にまで延設されている。

#### 【0105】

また配線47は、周辺領域7における絶縁層45の厚膜部分上にパターン形成されている。この配線47は、例えばアルミニウムのようなエッチング可能な導電性材料で構成され、絶縁層45の上層を構成するキャップ膜45-4および層間膜45-5に設けた接続孔を介して貫通ビア23に接続されている。このような配線47は、絶縁性の保護膜49で覆われている。

#### 【0106】

50

20

30

40

50

## &lt; 固体撮像装置の製造方法 &gt;

次に、上述した構成の固体撮像装置 1-4 の製造方法を図 15 ~ 図 16 の断面工程図に基づいて説明する。

## 【 0107 】

## [ 図 15 A ]

先ず図 15 A に示すように、センサ基板 2 と回路基板とを貼り合わせ、必要に応じてセンサ基板 2 の受光面 A 側を薄膜化するまでを、第 1 実施形態で図 3 A を用いて説明したと同様に行う。その後、センサ基板 2 の受光面 A 上に、例えば酸化ハフニウム ( HfO<sub>2</sub> ) からなる反射防止膜 45-1、酸化シリコン ( SiO<sub>2</sub> ) からなる界面準位抑制膜 45-2、および窒化シリコン ( SiN ) からなるエッチングストップ膜 45-3 をこの順に積層成膜する。以上の 3 層は、上述した段差構造を有する絶縁層 ( 45 ) の一部を構成する膜として成膜される。

10

## 【 0108 】

その後、センサ基板 2 の周辺領域 7 において、エッチングストップ膜 45-3、界面準位抑制膜 45-2、反射防止膜 45-1、センサ基板 2、および配線層 2a を構成する層間絶縁膜 26 に、必要に応じた深さの各接続孔 23a を形成する。これらの各接続孔 23a は、第 1 実施形態と同様であり、埋込配線 27 または埋込配線 37 の上部に達する各深さで形成される。

20

## 【 0109 】

## [ 図 15 B ]

次に図 15 B に示すように、接続孔 23a の内壁に、積層構造の分離絶縁膜 24 を形成し、これらの内部を銅 ( Cu ) で埋め込むことにより、各接続孔 23a 内に埋込配線 27 および埋込配線 37 に接続された貫通ビア 23 を形成する。このような分離絶縁膜 24 および貫通ビア 23 は、第 1 実施形態において図 5 A ~ 図 5 C を用いて説明した手順と同様の手順で形成することができる。

20

## 【 0110 】

## [ 図 15 C ]

次いで図 15 C に示すように、貫通ビア 23 およびエッチングストップ膜 45-3 を覆う状態で、貫通ビア 23 を構成する銅 ( Cu ) に対する拡散防止効果を有するキャップ膜 45-4 として、例えば窒化シリコン膜を 70 nm の膜厚で成膜する。さらにこの上部に、層間膜 45-5 として、酸化シリコン膜を成膜する。これにより、センサ基板 2 の受光面 A 上に、反射防止膜 45-1、界面準位抑制膜 45-2、エッチングストップ膜 45-3、キャップ膜 45-4、および層間膜 45-5 をこの順に積層させた 5 層構造の絶縁層 45 を形成する。

30

## 【 0111 】

## [ 図 16 A ]

その後、図 16 A に示すように、周辺領域 7 において、層間膜 45-5 およびキャップ膜 45-4 に、貫通ビア 23 に達する各接続孔 23b を形成する。その後、接続孔 23b を介して貫通ビア 23 に接続された配線 47 を、層間膜 45-5 上に形成する。この際、先ずスパッタ成膜法によって層間膜 45-5 上にアルミニウムのような導電性材料膜を成膜し、次にこの上部に形成したレジストパターンをマスクにして導電性材料膜をエッチングすることにより、導電性材料膜をパターニングしてなる配線 47 を形成する。以上の後には、必要に応じて配線 47 を覆う保護膜 49 を層間膜 45-5 上に成膜する。尚、この保護膜 49 も、絶縁層 45 を構成する膜とすることもできる。

40

## 【 0112 】

## [ 図 16 B ]

次に図 16 B に示すように、絶縁層 45 において画素領域 4 に対応する部分を選択的に薄膜化し、これにより絶縁層 45 に段差構造を形成する。この際、ここでの図示を省略したレジストパターンをマスクにして、保護膜 49、層間膜 45-5、キャップ膜 45-4、およびエッチングストップ膜 45-3 をエッチングする。

50

## 【 0113 】

以上により、センサ基板における受光面A上には、画素領域4の膜厚が周辺領域7の膜厚よりも薄い段差構造であって、画素領域4上において薄膜化したキャビティ構造の絶縁層45が設けられた状態となる。このような状態において、画素領域4には、反射防止膜45-1と界面準位抑制膜45-2のみが残される。一方、周辺領域7には、5層構造の絶縁層45および保護膜49がそのまま残される。

【0114】

尚、絶縁層45における薄膜部分は、配線47のレイアウトに影響のない範囲でできるだけ広範囲に設定されて良く、これによって絶縁層45の段差形状が、以降に形成する透明平坦化膜の塗布ムラを悪化させることによって光電変換部20への光入射に影響を及ぼすことを防止することは、第1実施形態と同様である。

10

【0115】

【図16C】

次に、図16Cに示すように、絶縁層45の段差下部にセンサ基板2を露出させる開口45aを形成し、次いで画素領域4における絶縁層45上に開口45aを介してセンサ基板2に接地された遮光膜16をパターン形成する。この遮光膜16には、各光電変換部20に対応する受光開口16aを設ける。以上の工程は、第1実施形態において図6Cを用いて説明した手順と同様の手順で行う。また、このような遮光膜16は、絶縁層45の段差上部で除去され、段差下部を広く覆う形状で良く、これにより、絶縁層45の段差を広い範囲で軽減することができることも第1実施形態と同様である。

【0116】

20

【図14】

以上の後には先の図14に示したように、遮光膜16を覆う状態で光透過性を有する材料からなる透明保護膜17を、スピンドルコート法のような塗布法によって成膜する。次に、透明保護膜17上に、光電変換部20に対応する各色のカラーフィルタ18を形成し、さらにこの上部に光電変換部20に対応するオンチップレンズ19を形成する。また回路基板9の露出面を研磨することで回路基板9を薄膜化し、ピア33を露出させて貫通ピア33とする。その後、貫通ピア33を覆う状態で回路基板9上に保護膜9cを成膜し、貫通ピア33を露出するパッド開口33aを形成する。さらに必要に応じて、アルミニウム等からなる配線47上に、ここでの図示を省略した配線47を露出するパッド開口を形成し、固体撮像装置1-4を完成させる。

30

【0117】

<第4実施形態の効果>

以上説明した構成の固体撮像装置1-4は、第1実施形態の固体撮像装置と同様に、周辺領域7に配線47を設けた裏面照射型であり、受光面A上には画素領域4で膜厚が薄い段差構造の絶縁層45を設け、この上部にオンチップレンズ19を設けた構成である。したがって、配線47の構成に必要な膜厚の絶縁層45を周辺領域7に残しつつ、画素領域4においてはオンチップレンズ19と受光面Aとの距離を小さくして光電変換部20においての受光特性の向上を図ることが可能である。また第1実施形態と同様に、受光面Aをエッチングダメージに晒すことなく良好に保つことも可能である。

【0118】

40

6. 第5実施形態

(センサ基板内の配線の接続にシェアコンを設けた例)

図17は、第5実施形態の固体撮像装置1-5の構成を示す要部断面図であり、図1における画素領域4と周辺領域7との境界付近の断面図である。以下、この要部断面図に基づいて第5実施形態の固体撮像装置1-5の構成を説明する。

【0119】

図17に示す変形例の固体撮像装置1-5が、図2を用いて説明した第1実施形態の固体撮像装置と異なるところは、貫通ピア51の構成および絶縁層53の層構造にあり、その他の構成は第1実施形態と同様である。

【0120】

50

すなわち貫通ビア 5 1 は、例えば配線層 2 a に設けた埋込配線 2 7 と、配線層 9 a に設けた埋込配線 3 7 との間を接続する、いわゆるシェアコンであって、これらの埋込配線 2 7 と埋込配線 3 7 との間を接続する配線として設けられている。このような配線として一体形成された貫通ビア 5 1 は、高さが異なる底面において埋込配線 2 7 と埋込配線 3 7 とに接続されている。また、貫通ビア 5 1 は、センサ基板 2 の受光面 A の上方に突出しており、突出した上部が絶縁層 5 3 に埋め込まれている。

#### 【 0 1 2 1 】

このような配線を兼ねる貫通ビア 5 1 は、絶縁層 5 3 からセンサ基板 2 を貫通してさらに配線層 2 a に設けられた接続孔 5 1 a 内に、分離絶縁膜 2 4 を介して埋め込まれた導電性材料によって構成されている。

10

#### 【 0 1 2 2 】

絶縁層 5 3 は、画素領域 4 の膜厚が周辺領域 7 の膜厚よりも薄い段差構造を有しており、例えば異なる絶縁材料を用いた積層膜として構成されていることは第1実施形態と同様である。このような絶縁層 5 3 は、一例として受光面側から順に反射防止膜 5 3 -1、界面準位抑制膜 5 3 -2、エッチングストップ膜 5 3 -3、キャップ膜 5 3 -4 の 4 層構造である。例えば反射防止膜 5 3 -1 は酸化ハフニウム (HfO<sub>2</sub>) 膜からなる。界面準位抑制膜 5 3 -2 は酸化シリコン (SiO<sub>2</sub>) 膜からなる。エッチングストップ膜 5 3 -3 は、窒化シリコン (SiN) からなる。さらにキャップ膜 5 3 -4 は窒化シリコン (SiN) からなる。

#### 【 0 1 2 3 】

このような 4 層構造の絶縁層 5 3 は、画素領域 4 においては、反射防止膜 5 3 -1 と界面準位抑制膜 5 3 -2 の 2 層構造に薄型化されている。また絶縁層 5 3 において周辺領域 7 の厚膜部分では、上層から 2 番目のエッチングストップ膜 5 3 -3 から下層に設けられた接続孔 5 1 a に、上述した配線としても貫通ビア 5 1 が延設されている。

20

#### 【 0 1 2 4 】

このような構成の固体撮像装置 1 -5 の製造は、第 4 実施形態において図 15 A を用いて説明した接続孔 2 3 a の形成において、埋込配線 2 7 と埋込配線 3 7 との両方の上部に 1 つの接続孔 5 1 a が配置されるようにパターニングを行う。次いで、図 15 B を用いて説明した手順と同様の手順を行うことにより、接続孔 5 1 a 内に分離絶縁膜 2 4 を介して銅 (Cu) を埋め込んだ貫通ビア 5 1 を、埋込配線 2 7 と埋込配線 3 7 とに接続された配線として形成する。次に、キャップ膜 5 3 -4 の成膜、画素領域 4 におけるキャップ膜 5 3 -4 およびエッチングストップ膜 5 3 -3 の選択的な除去を行うことで、絶縁層 5 3 を段差構造とする。以上の後には他の実施形態で説明したと同様の手順を行うことにより、受光開口 1 6 a を有する遮光膜 1 6 、透明保護膜 1 7 、カラーフィルタ 1 8 、およびオンチップレンズ 1 9 を形成する。また、回路基板 9 を薄膜化してビア 3 3 を露出させて貫通ビア 3 3 とし、回路基板 9 上に保護膜 9 c を成膜し、貫通ビア 3 3 を露出するパッド開口 3 3 a を形成することにより、固体撮像装置 1 -5 を完成させる。

30

#### 【 0 1 2 5 】

##### < 第 5 実施形態の効果 >

以上説明した構成の固体撮像装置 1 -5 は、第 1 実施形態の固体撮像装置と同様に、周辺領域 7 に配線としての貫通ビア 5 1 を設けた裏面照射型であり、受光面 A 上には画素領域 4 で膜厚が薄い段差構造の絶縁層 5 3 を設け、この上部にオンチップレンズ 1 9 を設けた構成である。したがって、配線としての貫通ビア 5 1 の構成に必要な膜厚の絶縁層 5 3 を周辺領域 7 に残しつつ、画素領域 4 においてはオンチップレンズ 1 9 と受光面 A との距離を小さくして光電変換部 2 0 においての受光特性の向上を図ることが可能である。また第 1 実施形態と同様に、受光面 A をエッチングダメージに晒すことなく良好に保つことも可能である。

40

#### 【 0 1 2 6 】

尚、上述した第 1 実施形態～第 5 実施形態においては、裏面照射型の固体撮像装置の一例として三次元構造の固体撮像装置に本技術を適用した構成を説明した。しかしながら本技術は、三次元構造に限定されることなく裏面照射型の固体撮像装置に広く適用可能であ

50

る。また段差構造を有する絶縁層は、各実施形態で説明した積層構造に限定されることはなく、配線の形成および受光特性の向上に適する様々な積層構造を適用することができる。

【0127】

7. 固体撮像装置を用いた電子機器の一例

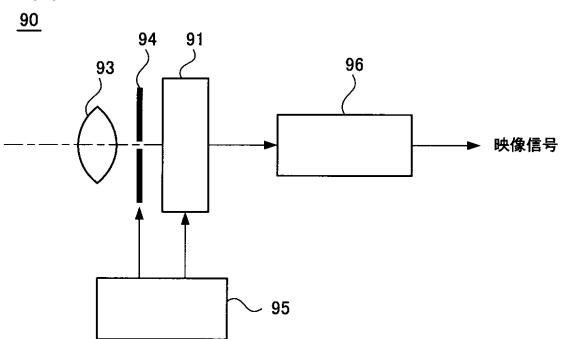

上述の実施形態で説明した本技術に係る固体撮像装置は、例えばデジタルカメラやビデオカメラ等のカメラシステム、さらには撮像機能を有する携帯電話、あるいは撮像機能を備えた他の機器などの電子機器に適用することができる。

【0128】

図18は、本技術に係る電子機器の一例として、固体撮像装置を用いたカメラの構成図を示す。本実施形態例に係るカメラは、静止画像又は動画撮影可能なビデオカメラを例としたものである。このカメラ90は、固体撮像装置91と、固体撮像装置91の受光センサ部に入射光を導く光学系93と、シャッタ装置94と、固体撮像装置91を駆動する駆動回路95と、固体撮像装置91の出力信号を処理する信号処理回路96とを有する。

【0129】

固体撮像装置91は、上述した実施形態で説明した構成の固体撮像装置が適用される。光学系(光学レンズ)93は、被写体からの像光(入射光)を固体撮像装置91の撮像面上に結像させる。これにより、固体撮像装置91内に、一定期間信号電荷が蓄積される。このような光学系93は、複数の光学レンズから構成された光学レンズ系としても良い。シャッタ装置94は、固体撮像装置91への光照射期間及び遮光期間を制御する。駆動回路95は、固体撮像装置91及びシャッタ装置94に駆動信号を供給し、供給した駆動信号(タイミング信号)により、固体撮像装置91の信号処理回路96への信号出力動作の制御、およびシャッタ装置94のシャッタ動作を制御する。すなわち、駆動回路95は、駆動信号(タイミング信号)の供給により、固体撮像装置91から信号処理回路96への信号転送動作を行う。信号処理回路96は、固体撮像装置91から転送された信号に対して、各種の信号処理を行う。信号処理が行われた映像信号は、メモリなどの記憶媒体に記憶され、或いは、モニタに出力される。

【0130】

以上説明した本実施形態に係る電子機器によれば、上述した第1実施形態～第5実施形態の何れかの受光特性の良好な固体撮像装置を用いたことにより、撮像機能を有する電子機器における高精彩な撮像な撮像や小型化を達成することが可能になる。

【0131】

尚、本技術は以下のよう構成も取ることができる。

【0132】

(1)

光電変換部が配列形成された画素領域を有するセンサ基板と、

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、

前記受光面上に設けられ、前記画素領域の膜厚が当該画素領域の外側に設けられた周辺領域の膜厚よりも薄い段差構造を有する絶縁層と、

前記受光面側における前記周辺領域に設けられた配線と、

前記絶縁層上において前記光電変換部に対応する各位置に設けられたオンチップレンズとを備えた

固体撮像装置。

【0133】

(2)

前記配線は、前記絶縁層に埋め込まれた埋込配線として設けられている

(1)記載の固体撮像装置。

【0134】

(3)

10

20

30

40

50

前記配線は、前記センサ基板の受光面側に埋め込まれた埋込配線として設けられている（1）または（2）記載の固体撮像装置。

## 【0135】

(4)

前記画素領域における前記絶縁層と前記オンチップレンズとの間には、前記光電変換部に対応した受光開口を有する遮光膜が設けられている

（1）～（3）の何れかに記載の固体撮像装置。

## 【0136】

(5)

前記絶縁層は、異なる材料を用いて構成された積層構造であり、

10

前記画素領域においては、前記絶縁層において積層構造の上層部分を構成する膜が除去されている

（1）～（4）の何れかに記載の固体撮像装置。

## 【0137】

(6)

前記絶縁層は、前記周辺領域にパターン形成された絶縁パターンと、当該絶縁パターンを覆う状態で前記センサ基板上に設けられた絶縁膜とを含み、

前記画素領域には、前記絶縁膜が設けられている

（1）～（4）の何れかに記載の固体撮像装置。

## 【0138】

(7)

前記センサ基板の表面側には、前記駆動回路を有する回路基板が貼り合わせられた

（1）～（6）の何れかに記載の固体撮像装置。

20

## 【0139】

(8)

前記センサ基板には、前記受光面側の前記配線と前記表面側に配置された前記駆動回路とを接続する貫通ピアが設けられている

（1）～（7）の何れかに記載の固体撮像装置。

## 【0140】

(9)

前記配線は、前記貫通ピアと一体に形成されている

30

（8）記載の固体撮像装置。

## 【0141】

(10)

前記遮光膜は、前記絶縁層の薄膜部分に形成された開口を介して前記センサ基板に接地されている

（4）記載の固体撮像装置。

## 【0142】

(11)

センサ基板に設定された画素領域に光電変換部を配列形成することと、

40

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に駆動回路を形成することと、

前記センサ基板における前記受光面上に絶縁層を成膜することと、

前記受光面側において、前記画素領域の外側に設けられた周辺領域に配線を形成することと、

前記絶縁層および前記配線を形成した後、当該絶縁層において前記画素領域に対応する部分を前記周辺領域に対して選択的に薄膜化することにより当該絶縁層に段差構造を形成することと、

前記段差構造が形成された前記絶縁層上において前記光電変換部に対応する各位置にオンチップレンズを形成することを含む

50

固体撮像装置の製造方法。

【0143】

(12)

前記配線を形成する際には、前記絶縁層に埋め込まれた埋込配線として当該配線を形成する

(11)記載の固体撮像装置の製造方法。

【0144】

(13)

前記絶縁層を成膜する際には、異なる材料を用いて構成された積層構造として当該絶縁層を成膜し、

10

前記絶縁層に段差構造を形成する際には、当該絶縁層において積層構造の上層部分を構成する膜を、下層部分を構成する膜に対して選択的に除去する

(11)または(12)に記載の固体撮像装置の製造方法。

【0145】

(14)

光電変換部が配列形成された画素領域を有するセンサ基板と、

前記センサ基板において前記光電変換部に対する受光面とは逆の表面側に設けられた駆動回路と、

前記受光面上に設けられ、前記画素領域の膜厚が当該画素領域の外側に設けられた周辺領域の膜厚よりも薄い段差構造を有する絶縁層と、

20

前記受光面側における前記周辺領域に設けられた配線と、

前記絶縁層上において前記光電変換部に対応する各位置に設けられたオンチップレンズと、

前記光電変換部に入射光を導く光学系を備えた

電子機器。

【符号の説明】

【0146】

1-1, 1-2, 1-3, 1-4, 1-5...固体撮像装置、2...センサ基板、4...画素領域、7...

周辺領域、8, 47...配線、9...回路基板、10~13...駆動回路、14, 41, 43,

45, 53...絶縁層、16...遮光膜、16a...受光開口、19...オンチップレンズ、20

30

...光電変換部、23, 51...貫通ビア(配線)、90...電子機器、93...光学系、A...受光面、B...絶縁パターン

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 図 1 1 】

### 【図12】

【図13】

### 【図14】

【図15】

This cross-sectional diagram illustrates a semiconductor device structure. At the top, a horizontal line with a double-headed arrow indicates a width of 4. The structure below is divided into several regions. On the left, a region labeled 'B' contains vertical columns of contacts labeled 23a, 24, 23, 23, 24, 23, and 27. To the right of these, a region labeled 'A' contains contacts labeled 45-3, 45-2, and 45-1. A central region contains contacts labeled 22, 25, 21, 22, 21, 25, FD, Tr, Tr, TG, and 26. The bottom layer is labeled 2, 2a, and 2b. A contact labeled 27 is shown at the very bottom. The diagram uses various hatching patterns to distinguish between different layers and regions.

This cross-sectional diagram illustrates a thermal insulation structure. At the top, a horizontal layer is labeled '45' with a bracket. Below it is a layer labeled 'A'. The central part of the diagram shows a vertical channel labeled '20' on the right, with '21' and '25' on either side. Above the channel, '22' is labeled on both sides. To the left of the channel, '23' and '24' are labeled vertically. At the bottom, '26' is labeled on the right, with '27' on both sides. The bottom-most layer is labeled '37'. On the left side, there are labels '2', '2a', and '2b' with arrows pointing to specific sections. The entire diagram is labeled with a large letter 'C' on the left.

【図16】

This cross-sectional diagram illustrates a complex semiconductor structure. At the top, a series of contacts are labeled with numbers: 47, 23b, 49, 23b, 47, 23b, 45-5, 45-4, 45-3, 45-2, and 45-1. A bracket above the first four contacts groups them together. Below this, a horizontal layer contains labels A and B. Layer B is further divided into regions 2, 2a, and 2b. The structure features a central vertical column of contacts labeled 24, 23, 23, 27, 27, 22, 25, 21, 22, 21, 25, and FD. To the right, a region labeled TG is shown with a contact labeled 26. A label 'Tr' is placed between the 22 and 25 contacts. The entire structure is bounded by a thick outer line.

Diagram C shows a cross-section of a semiconductor device structure. The structure includes a substrate 16, a gate electrode 45, and a source/drain region 16a. Below the substrate, there are various layers and contacts labeled with numbers: 2, 2a, 2b, 23, 24, 25, 27, 45a, 45b, 16, A, 16a, 20, 26, 27, Tr, TG, and FD. The diagram illustrates the complex multi-layered architecture of the device, with labels indicating specific regions and contacts.

【図17】

【図18】

---

フロントページの続き

(51)Int.Cl. F I

H 04N 5/374 (2011.01)

(56)参考文献 特開2010-245506 (JP, A)

特開2011-096851 (JP, A)

中国特許出願公開第102110700 (CN, A)

特開2009-252949 (JP, A)

米国特許出願公開第2010/0032782 (US, A1)

特開2005-285988 (JP, A)

特開2011-091400 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 27/14-148

H 01L 21/768

H 01L 23/522-532

H 04N 5/335-378