(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5164745号

(P5164745)

(45) 発行日 平成25年3月21日(2013.3.21)

(24) 登録日 平成24年12月28日(2012.12.28)

(51) Int.Cl.

G 11 C 13/00 (2006.01)

F 1

G 11 C 13/00 140

G 11 C 13/00 180

G 11 C 13/00 110Z

請求項の数 3 (全 29 頁)

(21) 出願番号 特願2008-219066 (P2008-219066)

(22) 出願日 平成20年8月28日 (2008.8.28)

(65) 公開番号 特開2009-80922 (P2009-80922A)

(43) 公開日 平成21年4月16日 (2009.4.16)

審査請求日 平成23年8月1日 (2011.8.1)

(31) 優先権主張番号 特願2007-227386 (P2007-227386)

(32) 優先日 平成19年9月3日 (2007.9.3)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100099173

弁理士 濵谷 孝

(72) 発明者 斎藤 利彦

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 後藤 彰

(56) 参考文献 特開2007-188603 (JP, A)

特開2006-352104 (JP, A)

最終頁に続く

(54) 【発明の名称】 記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、記憶素子と、電源線と、を有し、

前記記憶素子は、一対の電極と、前記一対の電極間に挟まれた有機化合物層と、を有し、

前記第1のトランジスタのソース端子又はドレイン端子の一方には、前記記憶素子が電気的に接続され、

前記第1のトランジスタのソース端子又はドレイン端子の他方には、前記第2のトランジスタのソース端子又はドレイン端子の一方が電気的に接続され、

前記第2のトランジスタのソース端子又はドレイン端子の他方には、前記第3のトランジスタのソース端子又はドレイン端子の一方が電気的に接続され、

前記第3のトランジスタのソース端子又はドレイン端子の他方には、前記電源線が電気的に接続され、

前記第2のトランジスタのゲート端子には、アドレス信号が入力され、

前記第3のトランジスタのゲート端子は、接地され、

前記第2のトランジスタは、前記記憶素子の抵抗値の変化に応じて、しきい値電圧を制御するための第4の端子を有することを特徴とする記憶装置。

## 【請求項 2】

第1のトランジスタと、第2のトランジスタと、第3のトランジスタと、記憶素子と、

10

20

電源線と、を有し、

前記記憶素子は、一対の電極と、前記一対の電極間に挟まれた有機化合物層と、を有し、

前記第1のトランジスタのソース端子又はドレイン端子の一方には、前記記憶素子が電気的に接続され、

前記第1のトランジスタのソース端子又はドレイン端子の他方には、前記第2のトランジスタのソース端子又はドレイン端子の一方が電気的に接続され、

前記第2のトランジスタのソース端子又はドレイン端子の他方には、前記第3のトランジスタのソース端子又はドレイン端子の一方が電気的に接続され、

前記第3のトランジスタのソース端子又はドレイン端子の他方には、前記電源線が電気的に接続され、

前記第2のトランジスタのゲート端子には、アドレス信号が入力され、

前記第3のトランジスタのゲート端子は、接地され、

前記第3のトランジスタは、前記記憶素子の抵抗値の変化に応じて、しきい値電圧を制御するための第4の端子を有することを特徴とする記憶装置。

### 【請求項3】

請求項1又は2において、

前記有機化合物層には、絶縁物が混合されていることを特徴とする記憶装置。

### 【発明の詳細な説明】

#### 【技術分野】

20

#### 【0001】

本発明は、記憶装置に関する。また記憶装置を搭載した半導体装置に関する。さらに半導体装置を搭載した電子機器に関する。

#### 【背景技術】

#### 【0002】

近年、コンピュータなど様々な電子機器の多くは、様々なデータを用いることにより所望の動作をさせることができる。これらのデータは、例えば記憶装置（メモリともいう）などに保持することにより、一時的または永久的に用いることができる。記憶装置とは、広義にはハードディスクや、フレキシブルディスクなどの外部記憶装置（補助記憶装置）も含むが、CPU（中央処理装置）などの半導体記憶装置のことを意味する場合がほとんどである。記憶装置には、大きく分けて揮発性メモリと、不揮発性メモリとが存在する。揮発性メモリとは、データを保持した後であってもデータが消えてしまう記憶装置をいう。また不揮発性メモリとは、データを保持した後でそのデータを半永久的に保持できる記憶装置をいう。

30

#### 【0003】

揮発性メモリは、データが失われてしまう可能性はあるが、アクセス時間が短いというメリットを有する。また、不揮発性メモリは、データを保持することはできるが、消費電力が高いというデメリットを有する。このように記憶装置には、各々に特徴があり、各記憶装置は扱うデータの種類又は用途に応じて使い分けられている。

#### 【0004】

40

上記記憶装置の中には、記憶素子内の抵抗を変化させ、その抵抗を変化させた前と後のそれぞれの電圧を判別して、その電圧をデータとして保持することにより記憶装置として機能させるものがある（以下抵抗変化型記憶装置という）。この抵抗変化型記憶装置の例として、例えば上記不揮発性メモリの一つである有機メモリがある。この有機メモリの例としては、例えば一対の電極間に少なくとも一層からなる有機化合物を有する層（以下有機化合物層）を挟んで設けられた構造である記憶素子を有し、電極間に高電圧を与え、有機化合物層を流動化させることにより、対となる電極同士を短絡（ショートともいう）させることにより記憶素子における抵抗値を低下させ、この短絡の有無により書き込み状態または未書き込み状態を区別し、それぞれの状態における電圧を保持することにより記憶装置として機能せるもの（以下短絡型有機メモリという）がある。（例えば特許文献1

50

)

【特許文献 1】特開 2006 - 352104 号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

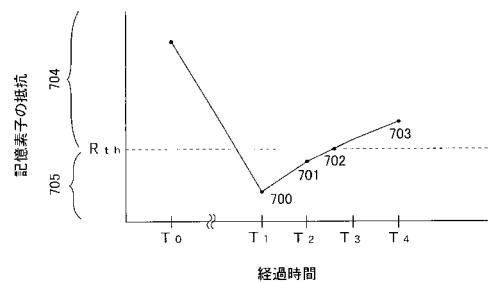

しかしながら、このような抵抗変化型記憶装置において、書き込み動作によりデータが書き込まれた後、時間が経過すると、記憶素子の電気抵抗（以下抵抗という）が徐々に変化し、書き込んだデータを正確な値に維持できなくなる現象（以下データ保持機能劣化現象という）が起こる問題がある。このデータ保持機能劣化現象について図14を用いて説明する。図14は、例として記憶素子に有機メモリを適用した、時間経過における記憶素子の抵抗値の変化を示す図である。なお、本明細書において、書き込み状態と判別される抵抗値の範囲と未書き込み状態と判別される抵抗値の範囲の境目の抵抗値（以下しきい値抵抗という）をR<sub>t h</sub>とし、しきい値抵抗R<sub>t h</sub>より高い抵抗値における電圧の範囲を未書き込み状態の範囲704とし、しきい値抵抗R<sub>t h</sub>より低い抵抗値における電圧の範囲を書き込み状態の範囲705とする。

10

【0006】

図14に示すように、書き込み後時間T<sub>1</sub>では抵抗値700であるのに対し、時間が経過するとともに、T<sub>2</sub>では抵抗値700から抵抗値701に、T<sub>3</sub>では抵抗値701から702と上がっていき、T<sub>4</sub>ではしきい値抵抗R<sub>t h</sub>を超えて未書き込み状態の範囲704である抵抗値703まで上昇してしまう。

20

【0007】

また、このような記憶素子の抵抗はある値まで上昇するとそれ以上は上昇せず飽和状態となる。このことより、書き込んだデータを維持するためには、しきい値抵抗R<sub>t h</sub>が書き込み前の初期抵抗R<sub>0</sub>と、書き込み後に抵抗上昇した後の最大抵抗R<sub>m a x</sub>との間の値であることが好ましい。

【0008】

本発明は上記問題を鑑みてなされたものであり、記憶素子の記憶特性が経時劣化した場合でも、書き込んだデータの維持が可能な高信頼性の記憶装置を提供することを課題とする。

30

【課題を解決するための手段】

【0009】

本発明の一は、抵抗値を変化させることにより、それぞれの抵抗値を利用してデータ保持を行う記憶素子を有するメモリセルと、メモリセルに記憶されたデータを読み出す読み出し回路と、を有し、読み出し回路は、しきい値電圧制御手段を有することにより、記憶素子の抵抗値の経時変化に応じてしきい値電圧を変化させ、データを正常な値のまま維持する記憶装置である。

【0010】

より具体的には、本発明の一は、抵抗値が変化する記憶素子を有し、記憶素子の抵抗値の状態を利用してデータ保持を行うメモリセルと、メモリセルに保持されたデータを読み出す読み出し回路と、電源線と、第1の信号線と、第2の信号線と、記憶素子の抵抗値の状態に従って、電源線の電位またはメモリセルに保持されたデータに対応する電位を出力する出力端子とを有し、読み出し回路は、トランジスタを有し、トランジスタは、電源線に電気的に接続され、ソース端子及びドレイン端子の一方となる第1端子と、第2の信号線を介してメモリセル及び出力端子に電気的に接続され、ソース端子及びドレイン端子の他方となる第2端子と、第1の信号線に電気的に接続され、ゲート端子となる第3端子と、第4端子とを有し、トランジスタは第3端子を介してチャネル領域に第1の電位が与えられてオンし、第4端子を介してチャネル領域に第2の電位が与えられることによりしきい値電圧が制御される記憶装置である。

40

【0011】

本発明の一は、抵抗値が変化する記憶素子を有し、記憶素子の抵抗値の状態を利用して

50

データ保持を行うメモリセルと、メモリセルに保持されたデータを読み出す読み出し回路と、電源線と、第1の信号線と、第2の信号線と、記憶素子の抵抗値の状態に従って、電源線の電位またはメモリセルに保持されたデータに対応する電位を出力する出力端子とを有し、読み出し回路は、トランジスタを有し、トランジスタは、第1のゲート電極と、ゲート電極を覆うように設けられた第1のゲート絶縁膜と、第1のゲート絶縁膜の上に設けられ、ソース領域、ドレイン領域、及びソース領域とドレイン領域との間に設けられたチャネル領域を有する半導体層と、半導体層を覆うように設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜の上に設けられた第2のゲート電極とを有し、トランジスタは、前記第1のゲート電極及び前記第2のゲート電極の一方を介して前記チャネル領域に第1の電位が与えられてオンし、前記第1のゲート電極及び前記第2のゲート電極の他方を介して前記チャネル領域に第2の電位が与えられることによりしきい値電圧が制御される記憶装置である。 10

#### 【0012】

本発明の一は、抵抗値が変化する記憶素子を有し、記憶素子の抵抗値の状態を利用してデータ保持を行うメモリセルと、メモリセルに保持されたデータを読み出す読み出し回路と、電源線と、第1の信号線と、第2の信号線と、記憶素子の抵抗値の状態に従って、電源線の電位またはメモリセルに保持されたデータに対応する電位を出力する出力端子とを有し、読み出し回路は、トランジスタを有し、トランジスタは、ソース領域及びドレイン領域の一方となる第1の不純物領域、ソース領域及びドレイン領域の他方となる第2の不純物領域、第1の不純物領域及び第2の不純物領域の間に設けられたチャネル領域、及び第3の不純物領域とを有する半導体基板と、チャネル領域上に設けられたゲート絶縁膜と、ゲート絶縁膜の上に設けられたゲート電極と、を有し、トランジスタは、ゲート電極を介してチャネル領域に第1の電位が与えられてオンし、第3の不純物領域を介してチャネル領域に第2の電位が与えられることによりしきい値電圧が制御される記憶装置である。 20

#### 【0013】

また、記憶素子は、第1の電極と、第2の電極と、第1の電極及び第2の電極に挟まれた有機化合物層と、を有することもできる。

#### 【0014】

本発明の一は、上記記載の記憶装置と、データの送受信を行うアンテナと、アンテナから受信した信号を用いて電源電圧を生成する高周波回路と、電源電圧が入力され、演算処理を行うロジック回路と、を有する半導体装置である。 30

#### 【0015】

本発明の一は、上記記載の半導体装置を有する電子機器である。

#### 【0016】

なお、本書類（明細書、特許請求の範囲又は図面など）におけるトランジスタのゲート端子（第3端子ともいう）とは、ゲート電極の部分（ゲートとなる領域、導電膜、及び配線などを含む）または、ゲート電極と電気的に接続されている部分の一部のことを言う。また、ソース端子とは、ソース電極の部分（ソースとなる領域、導電膜、及び配線などを含む）や、ソース電極と電気的に接続されている部分の一部のことを言う。また、ドレイン端子とは、ドレイン電極の部分（ドレインとなる領域、導電膜、及び配線などを含む）や、ドレイン電極と電気的に接続されている部分の一部のことを言う。 40

#### 【0017】

また、ソース端子とドレイン端子は、トランジスタの構造や動作条件等によって変わるために、いずれがソース端子またはドレイン端子であるかを限定することが困難である。そこで、本書類（明細書、特許請求の範囲又は図面など）においては、ソース端子及びドレイン端子として機能する領域を、それぞれを第1端子、第2端子と表記する。

#### 【発明の効果】

#### 【0018】

本発明により、記憶素子のデータ保持特性が経時劣化した場合においても書き込まれた値を正確に維持し、読み出すことが可能な記憶装置を提供できる。 50

**【発明を実施するための最良の形態】****【0019】**

本発明の実施の形態及び実施例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態及び実施例の記載内容に限定して解釈されるものではないとする。

**(実施の形態1)****【0020】**

本実施の形態では、本発明の記憶装置について説明する。

**【0021】**

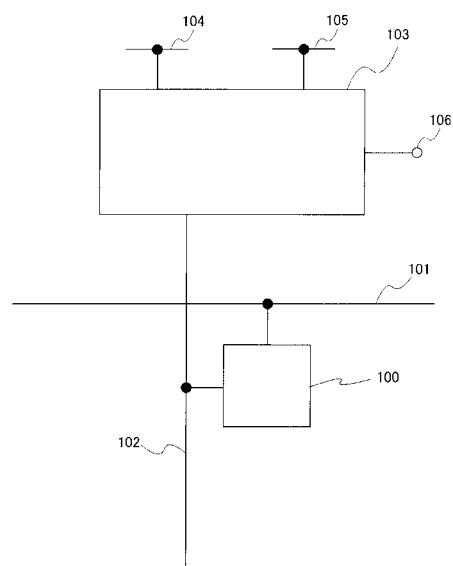

まず本実施の形態の記憶装置の構成について図1を用いて説明する。図1は、本実施の形態の記憶装置の構成を示すブロック図である。

**【0022】**

図1に示すように本実施の形態の記憶装置は、メモリセル100と、メモリセル100に電気的に接続されたワード線101及び第2の信号線(ビット線ともいう)102と、ワード線101及び第2の信号線102に電気的に接続された読み出し回路103と、読み出し回路103に電気的に接続された電源線104と、第1の信号線(アドレス信号線ともいう)105と、出力端子106を有する。

**【0023】**

メモリセル100は、外部からの信号に従ってデータを記憶する機能を有する。また、読み出し回路103は、選択したメモリセル100に記憶されたデータを読み出して出力端子106から出力する機能を有する。ワード線101及び第2の信号線102は、外部からの信号に従ってメモリセル100に信号を供給する機能を有する。

**【0024】**

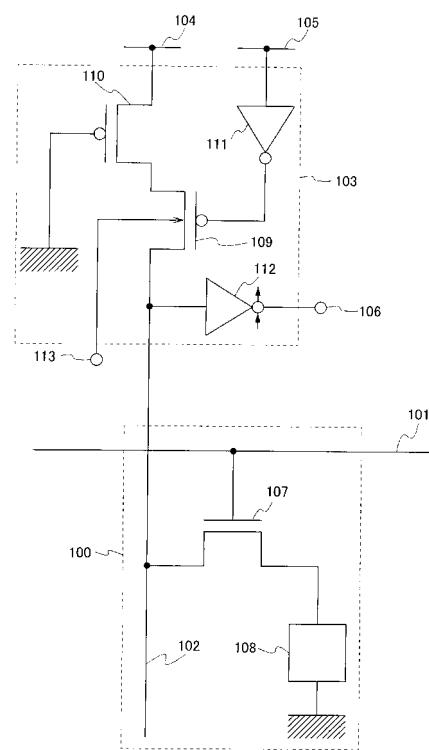

さらにメモリセル100及び読み出し回路103のより具体的な構成の例について図2を用いて説明する。図2は、本実施の形態における記憶装置の構成の一例を示す回路図である。

**【0025】**

本実施の形態における記憶装置は、メモリセル100と、メモリセル100に電気的に接続されたワード線101及び第2の信号線102と、ワード線101及び第2の信号線102に電気的に接続された読み出し回路103と、読み出し回路103に電気的に接続された電源線104と、第1の信号線105と、を有する。

**【0026】**

メモリセル100は、ゲート端子がワード線101に電気的に接続され、第1端子が第2の信号線102に電気的に接続された第1のトランジスタ107と、第1のトランジスタ107の第2端子に電気的に接続された記憶素子108と、を有する。

**【0027】**

第1のトランジスタ107は、ワード線101からの信号に従ってオン状態となり、第2の信号線102からの信号を記憶素子108に出力する機能を有する。

**【0028】**

記憶素子108は、外部から入力された信号に従って抵抗値が変化することにより、変化した抵抗値における電圧をデータとして保持する機能を有する。記憶素子108としては、例えば、第1の電極と、第2の電極と、第1の電極及び第2の電極の間に設けられた有機化合物層を有する記憶素子(以下有機メモリといふ)、第1の電極と、第2の電極と、第1の電極及び第2の電極の間に設けられたアモルファスシリコンなどの半導体層を有する記憶素子、相変化メモリ(PRAM: Phase Change Random Access Memory)など、素子内の電気抵抗の変化によりデータを保持する記憶素子であつて、経時変化により抵抗値などの特性が変化し、データの保持機能が劣化するものであれば適用することができる。

**【0029】**

10

20

30

40

50

読み出し回路 103 は、第 2 のトランジスタ 109 と、第 3 のトランジスタ 110 と、インバータ 111 と、クロックドインバータ 112 と、を有する。

#### 【0030】

第 2 のトランジスタ 109 は、第 3 のトランジスタ 110 を介して電源線 104 に電気的に接続され、ソース端子及びドレイン端子の一方となる第 1 端子と、第 2 の信号線 102 を介してメモリセル 100 に電気的に接続され、且つ第 2 の信号線 102 及びクロックドインバータ 112 を介して出力端子 106 に電気的に接続され、ソース端子及びドレイン端子の他方となる第 2 端子と、インバータ 111 を介して第 1 の信号線 105 に電気的に接続され、ゲート端子となる第 3 端子と、第 4 端子と、を有する。

#### 【0031】

第 3 のトランジスタ 110 は、電源線 104 に電気的に接続され、ソース端子及びドレイン端子の一方となる第 1 端子と、第 2 のトランジスタ 109 の第 1 端子に電気的に接続されたソース端子及びドレイン端子の他方となる第 2 端子と、接地され、ゲート端子となる第 3 端子とを有する。

#### 【0032】

インバータ 111 は、第 1 の信号線 105 に電気的に接続された入力端子、第 2 のトランジスタ 109 の第 3 端子に電気的に接続された出力端子と、を有する。

#### 【0033】

クロックドインバータ 112 は、第 2 のトランジスタ 109 の第 2 端子に電気的に接続された入力端子と、出力端子 106 に電気的に接続された出力端子と、を有する。

#### 【0034】

第 2 のトランジスタ 109 は、第 1 の信号線 105 からインバータ 111 を介してゲート端子に入力された信号に従ってオン状態となる機能を有する。このため、第 2 のトランジスタ 109 のしきい値電圧を制御することによりメモリセル 100 の読み出し動作の制御を行う。また、第 3 のトランジスタ 110 は、メモリセル 100 に保持されたデータを読み出す際に所望の抵抗値のときに所望の値のデータを読み出すために読み出し回路 103 とメモリセル 100 の抵抗値を調整する機能を有する。第 3 のトランジスタ 110 の代わりに抵抗素子を用いた場合であっても同様の動作を実現することができる。また、第 2 のトランジスタ 109 は、第 3 のトランジスタ 110 より抵抗値を低くすることにより、動作をより高速に行うことができる。

#### 【0035】

第 2 のトランジスタ 109 としては、しきい値電圧の制御が可能なトランジスタを適用することができる。例えば、第 2 のトランジスタ 109 に第 4 端子までを有するトランジスタを適用し、第 1 の信号線 105 からインバータ 111 および第 3 端子を介して第 1 の電位をチャネル領域に与えてトランジスタをオンし、外部端子 113 から第 4 端子を介して第 2 の電位をチャネル領域に与えることにより、しきい値電圧を制御することができる。また、第 3 のトランジスタ 110 についても同様にしきい値電圧の制御が可能なトランジスタを適用することもできる。第 3 のトランジスタ 110 にもしきい値電圧の制御が可能なトランジスタを適用することにより、より確実に記憶素子 108 に書き込まれたデータを維持することができる。

#### 【0036】

クロックドインバータ 112 は、メモリセル 100 における記憶素子 108 の抵抗値の状態に従って、メモリセル 100 からの出力、または電源線 104 からの出力が入力され、入力された出力電位の極性を反転させ、反転させた電位を外部に出力する機能を有する。なおクロックドインバータ 112 における第 1 のクロック信号が入力される第 1 のクロック信号入力端子と、第 1 のクロック信号とは反対の極性である第 2 のクロック信号が入力される第 2 のクロック信号入力端子には第 1 の信号線 105 からアドレス信号が入力される。

#### 【0037】

次の本実施の形態における記憶装置の動作について説明する。

10

20

30

40

50

**【0038】**

まず書き込み動作について説明する。書き込み動作は、記憶素子の抵抗を変化させることで行う。ここでは、例として変化させる前の状態（未書き込み状態）を0のデータとし、変化させた後の状態（書き込み状態）を1のデータとして説明する。

**【0039】**

1のデータを書き込む場合、書き込みを行うメモリセル100を選択し、選択されたメモリセル100にワード線101及び第2の信号線102から信号が入力され、第1のトランジスタ107がオン状態となり、電源電位が記憶素子108に入力され、記憶素子108における抵抗が変化することにより書き込み状態となる。

**【0040】**

次に書き込み後のデータ保持動作について説明する。

**【0041】**

データの書き込み後、記憶素子108の経時変化による抵抗上昇を考慮して、読み出し回路103における第2のトランジスタ109の第4端子から、電位をチャネル領域に与えることにより、しきい値電圧を下げ、しきい値電圧を調整する。このとき、しきい値電圧 $V_{th}$ の範囲は、記憶されたデータが正確に出力される値となることが望ましく、記憶素子108において、しきい値抵抗を $R_{th}$ とし、経時変化により上昇した抵抗の最大値を $R_{max}$ とし、未書き込み状態の初期抵抗値を $R_0$ とした場合、 $R_{max} < R_{th} < R_0$ となるように第2のトランジスタ109のしきい値電圧 $V_{th}$ を設定し、読み出し回路103の読み出し能力を調整することが望ましい。なお、このしきい値電圧 $V_{th}$ の調整は、記憶素子108の経時変化による抵抗上昇を考慮して予め設定する方法、また、別途モニタ回路などを用いて経時変化による抵抗上昇に合わせてしきい値電圧 $V_{th}$ を変化させる方法など、いずれの方法を用いても行うことができる。

**【0042】**

次に読み出し動作について説明する。

**【0043】**

読み出し動作は、まず読み出しを行うメモリセル100のアドレスを選択する。具体的にはアドレス信号が第1の信号線105から読み出し回路103に出力される。読み出し回路103に入力されたアドレス信号は、インバータ111で反転され、第2のトランジスタ109のゲート端子に出力される。アドレス信号が入力された第2のトランジスタ109は、オン状態となる。読み出し回路103により選択されたメモリセル100では、ワード線101からの信号により第1のトランジスタ107がオン状態となる。つまり、クロックドインバータ112の入力端子が電源電位 $VDD$ 及び記憶素子108と電気的に接続された状態となる。ここで、記憶素子108が未書き込み状態の場合は、記憶素子108の抵抗値が高いため、電源電位 $VDD$ がクロックドインバータ112に入力され、書き込み状態の場合には、記憶素子108の抵抗値が低いため、保持されたデータに対応した電位がクロックドインバータ112に入力される。クロックドインバータ112に入力された電位は反転され、出力端子106から出力される。

**【0044】**

また、第2のトランジスタ109に第1端子乃至第3端子を設けたトランジスタを適用し、第3のトランジスタ110に第1端子乃至第4端子を設けた、しきい値電圧の制御が可能なトランジスタを適用することもできる。この場合、第3のトランジスタ110のゲート端子は接地され、常にトランジスタがオンの状態になっているが、第4端子を介してチャネル領域に電位を与えることにより、しきい値電圧が変化するのに伴い、オン抵抗の値も変化する。ここで、 $R_{max} < R_{th} < R_0$ となるように第3のトランジスタ110のオン抵抗の値を設定し、読み出し回路103の読み出し能力を調整すればよい。

**【0045】**

以上により、記憶素子の抵抗値が経時変化する場合においても書き込まれたデータを正確な状態に維持したまま読み出すことができる。

**【0046】**

10

20

30

40

50

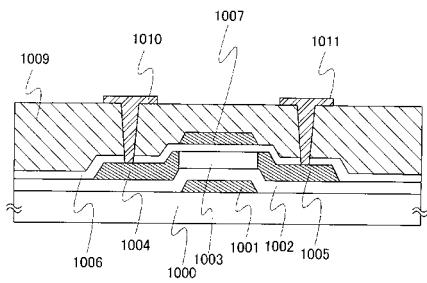

ここで第2のトランジスタ109及び第3のトランジスタ110に適用することが可能なトランジスタについて図3を用いて説明する。図3は、トランジスタの断面を模式的に示した図である。

#### 【0047】

図3のトランジスタは、基板1000と、基板1000上に設けられた第1のゲート電極1001と、第1のゲート電極1001上に設けられた第1のゲート絶縁膜1002と、第1のゲート絶縁膜1002上に設けられた半導体層1003と、半導体層1003上に設けられた第2のゲート絶縁膜1006と、第2のゲート絶縁膜1006上に設けられた第2のゲート電極1007と、を有する。さらに半導体層1003は、第1の不純物領域1004及び第2の不純物領域1005を有する。第1の不純物領域1004及び第2の不純物領域1005の間には、チャネル領域を有する。第2のゲート電極1007上には、絶縁層1009を有し、絶縁層1009の一部には、任意の数のコンタクト部を有し、コンタクト部を介して第1の不純物領域1004上に設けられた第1の配線1010、及び第2の不純物領域1005上に設けられた第2の配線1011をそれぞれ有する。

#### 【0048】

基板1000としては、例えばガラス基板、石英基板、セラミック基板、金属基板（例えばステンレス基板など）などを用いることができる。他にもプラスチック基板として、ポリエチレンテレフタラート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）、アクリルなどの基板を選択することもできる。

#### 【0049】

また、第1のゲート絶縁膜1002、第2のゲート絶縁膜1006、及び絶縁層1009は、酸化シリコン、窒化シリコン、酸化窒化シリコン、及び窒化酸化シリコンのいずれか一つまたは複数を用いることができる。また選ばれた材料を用いて積層構造とすることもできる。絶縁層は、C V D法やスパッタリング法等を用いて形成することができる。

#### 【0050】

また、半導体層1003としては、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどを単層または積層して用いることができる。また半導体層1003はスパッタリング法、L P C V D法、プラズマC V D法等により形成することができる。

#### 【0051】

また、半導体層1003は、レーザビームを照射することにより結晶化を行うことができる。なお、レーザビームの照射と、R T Aまたはファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により半導体層1003の結晶化を行ってもよい。その後、得られた結晶性半導体膜を所望の形状にエッチングすることにより半導体層1003が形成される。

#### 【0052】

第1のゲート電極1001及び第2のゲート電極1007は、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等から選択された元素、またはこれらの元素を主成分とする合金材料、若しくは化合物材料を用いて形成することができる。また、リン等の不純物元素をドーピングした多結晶シリコンに代表される半導体材料を用いて形成することもできる。また上記材料の一つまたは複数を選択し、積層構造とすることも可能である。上記材料の組み合わせの例を挙げると、窒化タンタル膜とタングステン膜、窒化タングステン膜とタングステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、ゲート電極の1層目と2層目を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層の積層のみではなく、3層以上の構造とすることも可能である。例えば3層の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

#### 【0053】

第1の不純物領域1004及び第2の不純物領域1005は、半導体層1003の一部に不純物元素を添加することにより形成することができる。また、所定の領域に添加した

10

20

30

40

50

い場合には、別途レジストを形成し、レジストをマスクとして不純物元素を添加することにより、所望の領域に所望の元素を含む第1の不純物領域1004及び第2の不純物領域1005を形成することができる。なお、不純物元素にはリンやボロンを用いることができる。

#### 【0054】

また、絶縁層1009としては、シリコンの酸化物及びシリコンの窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、及びエポキシ等の有機材料、及びシロキサン材料のいずれか一種または複数種を用いることができる。また上記材料から選ばれた一種または複数種を用いて積層構造を形成することも可能である。

#### 【0055】

また、第1の配線1010及び第2の配線1011は、ソース配線またはドレイン配線として機能する。アルミニウム、タンゲステン、チタン、タンタル、モリブデン、ニッケル、白金、銅、金、銀、マンガン、ネオジム、炭素、及びシリコンから選択された元素、またはこれらの元素を主成分とする合金材料または化合物材料を用いることができる。また、上記材料の一種または複数種を選択して用いることにより積層構造とすることも可能である。アルミニウムを主成分とする合金材料としては、例えば、アルミニウムを主成分として有し、さらにニッケルを含む材料や、アルミニウムを主成分として有し、さらにニッケル、及び炭素とシリコンの一方または両方とを含む合金材料などを用いることができる。第1の配線1010及び第2の配線1011は、例えば、バリア膜とアルミニウムシリコン(A1-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(A1-Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、またはモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、第1の配線1010及び第2の配線1011を形成する材料としてより好適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶性半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶性半導体膜と良好なコンタクトをとることができる。

#### 【0056】

第1の不純物領域1004と第1の配線1010、及び第2の不純物領域1005と第2の配線1011は、ソース端子またはドレイン端子として機能する。第1の不純物領域1004及び第2の不純物領域1005の間にはチャネル領域が形成される。

#### 【0057】

第1のゲート電極1001または第2のゲート電極1007は、トランジスタの第4端子として機能する。第1のゲート電極1001及び第2のゲート電極1007の一方を介して、外部からの任意の電位がチャネル領域に与えられることにより、トランジスタのしきい値電圧を制御することができる。

#### 【0058】

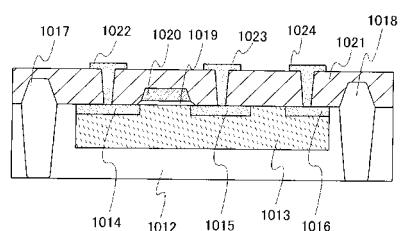

さらに本実施の形態において、第4端子を有するトランジスタに用いることのできるトランジスタの他の一例として単結晶半導体膜を有するトランジスタについて図4を用いて説明する。図4はトランジスタの断面を模式的に示した図である。

#### 【0059】

図4のトランジスタは、第1の絶縁層1017及び第2の絶縁層1018を有する基板1012と、基板1012上に設けられたゲート絶縁膜1019と、ゲート絶縁膜1019上に設けられたゲート電極1020と、を有する。さらに基板1012は、一部にウェル領域1013を有し、ウェル領域1013の一部には、第1の不純物領域1014、第2の不純物領域1015、及び第3の不純物領域1016を有する。ゲート絶縁膜1019及びゲート電極1020は、基板1012における第1の不純物領域1014及び第2の不純物領域1015の間の領域に設けられている。さらにゲート電極1020及び基板1012上には、絶縁層1021を有し、絶縁層1021の一部には、任意の数のコンタ

10

20

30

40

50

クト部を有し、コンタクト部を介して第1の不純物領域1014上に設けられた第1の配線1022、第2の不純物領域1015上に設けられた第2の配線1023、第3の不純物領域1016上に設けられた第3の配線1024をそれぞれ有する。

#### 【0060】

基板1012としては、例えば、n型またはp型の導電型を有する単結晶シリコン基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、またはZnSe基板等)、及び貼り合わせ法またはSIMOX(Separation by Implanted Oxygen)法を用いて作製されたSOI(Silicon on Insulator)基板のいずれかを用いることができる。また、ガラス基板上に単結晶シリコンを貼り合わせたものも用いることができる。10

#### 【0061】

第1の絶縁層1017及び第2の絶縁層1018の形成には、選択酸化法(LOCOS: Local Oxidation of Silicon法)またはトレンチ分離法等を用いることができる。

#### 【0062】

ゲート電極1020としては、タンタル、タンクステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等を用いることができる。また、ゲート電極1020は、上記金属で形成された膜の他に、上記金属を主成分とする合金で形成された膜、或いは上記金属を含む化合物を用いて形成された膜を用いて形成することもできる。または、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶シリコンなどの半導体を用いて形成することもできる。また、ゲート電極1020は、所定の形状に加工(パターニングなど)することによって形成することができる。20

#### 【0063】

ウェル領域1013及び第1の不純物領域1014、第2の不純物領域1015、及び第3の不純物領域1016は不純物元素を添加することで形成することができる。不純物元素としては、n型を付与する不純物元素またはp型を付与する不純物元素を用いる。n型を付与する不純物元素としては、リンやヒ素等を用いることができる。p型を付与する不純物元素としては、ボロンやアルミニウムやガリウム等を用いることができる。また所定の領域に添加したい場合には、別途レジストを形成し、レジストをマスクとして不純物元素を添加することにより所望の領域に所望の元素を含むウェル領域1013及び第1の不純物領域1014、第2の不純物領域1015、及び第3の不純物領域1016を形成することができる。30

#### 【0064】

ゲート絶縁膜1019としては、無機材料、有機材料、または有機材料と無機材料の混合材料を用いて形成することができる。例えば酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、DLC(ダイヤモンドライクカーボン)に代表される炭素を含む膜、アクリル、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、またはベンゾシクロブテンなどを用いることができる。また、第1の絶縁層1017及び第2の絶縁層1018はその材料に応じて、CVD法、スパッタ法、液滴吐出法または印刷法などで形成することができる。40

#### 【0065】

第1の不純物領域1014と第1の配線1022、及び第2の不純物領域1015と第2の配線1023は、ソース端子またはドレイン端子として機能する。また、第1の不純物領域1014及び第2の不純物領域1015の間にはチャネル領域が形成される。

#### 【0066】

ボディ領域となる第3の不純物領域1016及び第3の配線1024は、トランジスタの第4端子として機能する。よって第4端子を介して、任意の電位がチャネル領域に与えられることにより、トランジスタのしきい値電圧を制御することができる。

#### 【0067】

なお、図2における第2のトランジスタ109及び第3のトランジスタ110の極性は50

特に限定されない。本実施の形態の動作を実現できるのであれば、Pチャネル型またはNチャネル型のトランジスタを適宜選択して用いることできる。また、第1の信号線から入力されるアドレス信号の値によっては、インバータ111を取り除いても、本実施の形態の動作を実現することもできる。

#### 【0068】

以上のように上記しきい値電圧の制御が可能なトランジスタを図2の読み出し回路103における第2のトランジスタ109に適用することにより、しきい値電圧を所望の値に設定することができるため、記憶素子の記憶特性が経時劣化した場合においても書き込まれたデータを正常の値として維持することができる。

#### 【0069】

また、読み出し回路103のトランジスタにしきい値電圧の制御可能なトランジスタを適用してしきい値制御を行うため、ゲート長などを変化させるなどの回路面積を増大させてしきい値制御を行う方法を用いずに信頼性の高い記憶装置を提供することができる。

#### (実施の形態2)

#### 【0070】

本実施の形態では、本発明の記憶装置のより具体的な構成について説明する。

#### 【0071】

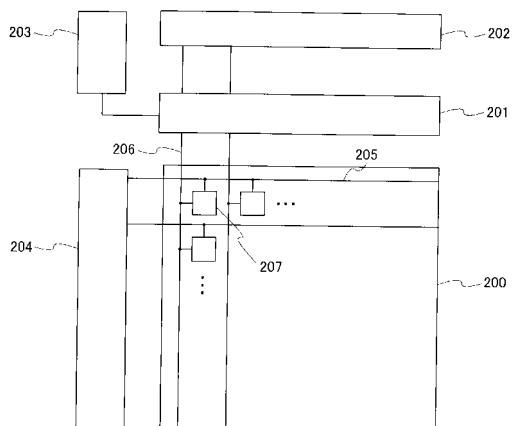

本実施の形態の記憶装置の構成について図5を用いて説明する。図5は、本実施の形態の記憶装置の構成を示すブロック図である。

#### 【0072】

図5に示すように本実施の形態における記憶装置は、複数のメモリセル207がマトリクス状に設けられたメモリセルアレイ200と、読み出し/書き込み回路201と、カラムデコーダ202と、セレクタ回路203と、ロウデコーダ204と、を有する。なお、ここで示す記憶装置の構成はあくまで一例であり、センスアンプ、出力回路、バッファ等の他の回路を有する構成とすることもできる。

#### 【0073】

読み出し/書き込み回路201は、それぞれ別の回路により構成され、読み出し/書き込み動作の際にはセレクタ回路203によって回路が選択され動作を行う。

#### 【0074】

複数のメモリセル207は、それぞれロウデコーダ204に接続されたワード線205及びカラムデコーダ202に接続された第2の信号線206に接続される。

#### 【0075】

なお、メモリセル207及び読み出し/書き込み回路201の回路構成は、上記実施の形態1において説明した構成及び素子を適用することができる。

#### 【0076】

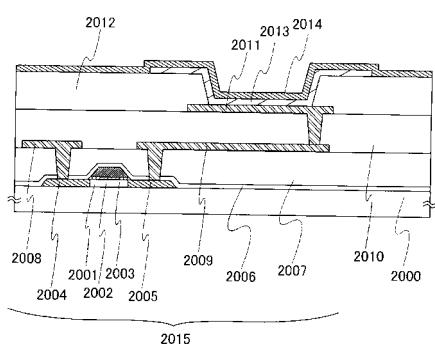

次に本実施の形態の記憶装置のメモリセルに適用可能な構造について図6を用いて説明する。図6は、本実施の形態におけるメモリセルの構造を示す断面図である。なお、本実施の形態では、メモリセルの記憶素子に短絡型有機メモリを適用した場合について説明する。

#### 【0077】

図6に示すように、本実施の形態におけるメモリセルは、基板2000上に設けられ、不純物領域2004及び2005を有する半導体層2001と、半導体層2001の一部の上に設けられたゲート絶縁膜2002と、ゲート絶縁膜2002の一部の上に設けられたゲート電極2003と、ゲート電極2003及び半導体層2001上に設けられ、開口部を有する第1の絶縁層2006と、第1の絶縁層2006上に設けられ、開口部を有する第2の絶縁層2007と、第1の絶縁層2006及び第2の絶縁層2007の開口部を介して不純物領域2004及び2005の一部の上面に接するように設けられた配線2008及び2009と、を有するトランジスタ2015と、配線2008及び2009上に設けられ、開口部を有する第3の絶縁層2010と、第3の絶縁層2010の開口部を介して配線2009の一部の上面に接するように設けられた第1の電極2011と、第1の

10

20

30

40

50

電極 2011 上及び第3の絶縁層 2010 上に設けられ、開口部を有する第4の絶縁層 2012 と、第4の絶縁層 2012 の開口部を介して第1の電極 2011 の上面に接するよう に設けられた有機化合物層 2013 と、有機化合物層 2013 の上面に接するよう に設けられた第2の電極 2014 と、を有する。

#### 【0078】

第1の電極 2011 、有機化合物層 2013 、及び第2の電極 2014 は、図5の記憶 素子としての機能を有する。

#### 【0079】

トランジスタ 2015 としては、例えば薄膜トランジスタ (TFT : Thin Film Transistor) 、電界効果トランジスタ (FET : Field Effect Transistor) などを適用することができる。

10

#### 【0080】

基板 2000 としては、ガラス基板や可撓性基板の他、石英基板、シリコン基板、金属 基板、ステンレス基板等を用いることができる。可撓性基板とは、折り曲げることができ る(フレキシブルである)基板のことであり、例えば、ポリカーボネート、ポリアリレート、ポリエーテルスルファン等からなるプラスチック基板等が挙げられる。また、貼り合 わせフィルム(ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニル などからなる)、繊維状な材料からなる紙、基材フィルム(ポリエステル、ポリアミド、 無機蒸着フィルム、紙類等)などを用いることもできる。

#### 【0081】

また、この他にも、シリコン等の半導体基板上に形成された電界効果トランジスタの上 部や、ガラス等の基板上に形成された薄膜トランジスタの上部にメモリセルアレイ 200 を設けることができる。

20

#### 【0082】

また、基板 2000 としては、例えば、n型またはp型の導電型を有する単結晶シリコ ン基板、化合物半導体基板 (GaN 基板、InP 基板、SiC 基板、サファイア基板、 またはZnSe 基板等) 、及び貼り合わせ法またはSIMOX (Separation by Implanted Oxygen) 法を用いて作製されたSOI (Silicon on Insulator) 基板のいずれかを用いることができる。また、ガラス基板上に単結晶シリコンを貼り合わせたものも用いることができる。

30

#### 【0083】

ゲート絶縁膜 2002 、第1の絶縁層 2006 、第2の絶縁層 2007 、第3の絶縁層 2010 、及び第4の絶縁層 2012 としては、酸化シリコン、窒化シリコン、酸化窒化シリコン、及び窒化酸化シリコンのいずれか一つまたは複数を適用することができる。また、選ばれた材料を用いて積層構造とすることもできる。絶縁層は、CVD法やスパッタリング法等を用いて形成することができる。

#### 【0084】

ゲート電極 2003 としては、タンタル、タングステン、チタン、モリブデン、アルミニウム、銅、クロム、ニオブ等を適用することができる。また、ゲート電極 2003 は、上記金属で形成された膜の他に、上記金属を主成分とする合金で形成された膜、或いは上記金属を含む化合物を用いて形成された膜を適用することもできる。また、半導体膜に導電性を付与するリン等の不純物元素をドーピングした、多結晶シリコンなどの半導体を適用することもできる。また、ゲート電極 2003 は、所定の形状に加工(パターニングなど)することによって形成することができる。

40

#### 【0085】

第1の電極 2011 と第2の電極 2014 と、第1の電極 2011 と第2の電極 2014 に挟まれて設けられた有機化合物層 2013 と、は、図2における記憶素子 108 とし て機能する。

#### 【0086】

第1の電極 2011 及び第2の電極 2014 としては、導電性の高い元素や化合物等を

50

適用することができる。一例としては、金、銀、白金、ニッケル、タングステン、クロム、モリブデン、鉄、コバルト、銅、パラジウム、炭素、アルミニウム、マンガン、チタン、タンタル等から選ばれた一種の元素または当該元素を複数含む合金からなる単層または積層構造を用いることができる。上記元素を複数含んだ合金としては、例えば、AlとTiを含んだ合金Al-TiとCを含んだ合金、AlとNiを含んだ合金、AlとCを含んだ合金、AlとNiとCを含んだ合金またはAlとMoを含んだ合金等を適用することができる。第1の電極2011及び第2の電極2014は、蒸着法、スパッタ法、CVD法、印刷法または液滴吐出法を用いて形成することができる。

#### 【0087】

有機化合物層2013としてはポリイミド、アクリル、ポリアミド、ベンゾシクロブテン、エポキシ等に代表される有機樹脂と、正孔輸送性を有する有機化合物又は電子輸送性を有する有機化合物を組み合わせて適用することができる。10

#### 【0088】

正孔輸送性の有機化合物としては、例えば、フタロシアニン（略称：H<sub>2</sub>Pc）、銅フタロシアニン（略称：CuPc）、バナジルフタロシアニン（略称：VOPc）の他、4,4',4'',4'''-トリス（N,N-ジフェニルアミノ）トリフェニルアミン（略称：TDA-TA）、4,4',4'',4'''-トリス[N-(3-メチルフェニル)-N-フェニルアミノ]トリフェニルアミン（略称：MTDATA）、1,3,5-トリス[N,N-ジ(m-トリル)アミノ]ベンゼン（略称：m-MTDAB）、N,N'-ジフェニル-N,N'-ビス(3-メチルフェニル)-1,1'-ビフェニル-4,4'-ジアミン（略称：TPD）、4,4'-ビス[N-(1-ナフチル)-N-フェニルアミノ]ビフェニル（略称：NPB）、4,4'-ビス{N-[4-ジ(m-トリル)アミノ]フェニル-N-フェニルアミノ}ビフェニル（略称：DNTPD）、4,4'-ビス[N-(4-ビフェニリル)-N-フェニルアミノ]ビフェニル（略称：BBPB）、4,4',4'''-トリ(N-カルバゾリル)トリフェニルアミン（略称：CTCA）などが挙げられるが、これらに限定されることはない。ここに述べた物質は、主に10<sup>-6</sup> cm<sup>2</sup>/Vs以上の正孔移動度を有する物質である。20

#### 【0089】

電子輸送性を有する有機化合物としては、トリス(8-キノリノラト)アルミニウム（略称：Alq<sub>3</sub>）、トリス(4-メチル-8-キノリノラト)アルミニウム（略称：Almq<sub>3</sub>）、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム（略称：BeBq<sub>2</sub>）、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム（略称：BA1q）等キノリン骨格またはベンゾキノリン骨格を有する金属錯体等からなる材料を用いることができる。また、この他、ビス[2-(2-ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛（略称：Zn(BOX)<sub>2</sub>）、ビス[2-(2-ヒドロキシフェニル)ベンゾチアゾラト]亜鉛（略称：Zn(BTZ)<sub>2</sub>）などのオキサゾール系、チアゾール系配位子を有する金属錯体などの材料も用いることができる。さらに、金属錯体以外にも、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール（略称：PBD）、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン（略称：OXD-7）、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール（略称：TAZ）、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール（略称：p-EtTAZ）、バソフェナントロリン（略称：BPhen）、バソキュプロイン（略称：BCP）等を用いることができる。ここに述べた物質は、主に10<sup>-6</sup> cm<sup>2</sup>/Vs以上の電子移動度を有する物質である。40

#### 【0090】

なお、上記範囲外の移動度を有する物質であっても良く、例えば2,3-ビス(4-ジフェニルアミノフェニル)キノキサリン（略称：TPAQn）、9-[4-(N-カルバゾリル)]フェニル-10-フェニルアントラセン（以下、CzPAと記す。）等を用い50

て形成してもよい。

**【0091】**

また、有機化合物層2013は上記に示す有機化合物を複数混合して形成してもよい。

また、上記に示す有機化合物を積層して形成してもよい。

**【0092】**

また、有機化合物層2013は、正孔輸送性もしくは電子輸送性を有する有機化合物に絶縁物が混合されていても良い。なお、絶縁物は、均一に分散されている必要はない。絶縁物を混合することにより、有機化合物層2013のモルフォロジーを向上することができる。よって、部分的な膜の結晶化等を抑制することができるため、さらに記憶素子毎の挙動のばらつきを抑制することができる。

10

**【0093】**

また、有機化合物層2013の厚さは、第1の電極2011及び第2の電極2014への電圧印加により記憶素子の電気抵抗が変化する厚さであることが好適である。有機化合物層2013の代表的な膜厚は、1nmから100nm、好ましくは5nmから60nm、更に好ましくは5nmから30nmである。

**【0094】**

ここで本実施の形態における記憶素子の書き込みの原理について説明する。

**【0095】**

有機化合物層2013は、その物質のガラス転移温度まで温度が上昇すると、流動性を有する。よって、有機化合物材料を用いた有機化合物層2013は、ガラス転移点以上の温度となると、流動性を有し、一定の形状を保たない状態となる。流動性を有するようになると、その材料の固体時の形状は保持されず、時間と共に変化する。よって有機化合物層2013は変形し、第1の電極2011と第2の電極2014との間に有機化合物層2013がない領域が形成され、この領域で第1の電極2011と第2の電極2014が短絡する。第1の電極2011と第2の電極2014が短絡することにより、記憶素子における抵抗値が下がる。この抵抗値が変化する原理を利用してデータの書き込みを行う。

20

**【0096】**

また、第1の電極2011と第2の電極2014との間に絶縁層を設ける構成を適用することもできる。絶縁層を設けることにより、流動性を有する有機化合物層の広がりを制御することができ、より確実に第1の電極2011と第2の電極2014を短絡させることができる。

30

**【0097】**

次に本実施の形態における記憶装置の動作について説明する。なお、本実施の形態において、読み出し回路及びメモリセルにおける具体的な動作は、上記実施の形態1の読み出し回路103及びメモリセル100と同じであるため、一部説明を省略して説明する。

**【0098】**

まず書き込み動作について説明する。カラムデコーダ202及びロウデコーダ204により書き込みを行うメモリセル207を選択する。具体的にはロウデコーダ204によって選択されたメモリセル207に接続されたワード線205に所定の電位を与え、また、カラムデコーダ202及びセレクタ回路203によって選択されたメモリセル207に接続された第2の信号線206に読み出し/書き込み回路201からデータに対応した電位を与える。選択されたメモリセル207は、第2の信号線206の電位が記憶素子に入力されることにより記憶素子が短絡し、書き込み状態となる。

40

**【0099】**

なお、非選択のワード線205及び非選択の第2の信号線206は、接続されるメモリセル207にデータが書き込まれないように制御する。例えば、非選択の第2の信号線206を浮遊状態とすることにより誤書き込みを防止することができる。

**【0100】**

データ維持動作については、上記実施の形態1におけるデータ維持動作と同様であるため説明を省略する。

50

**【0101】**

次に読み出し動作について説明する。カラムデコーダ202及びロウデコーダ204によりデータを読み出したいメモリセル207を選択する。具体的には、ロウデコーダ204によって選択されたメモリセル207に接続されたワード線205に所定の電位を与え、また、カラムデコーダ202及びセレクタ回路203によって選択されたメモリセル207は記憶素子が書き込み状態であれば書き込まれたデータとなる電位が第2の信号線206に出力され、また未書き込み状態であれば電源電位VDDが第2の信号線206に出力される。

**【0102】**

以上のことより、本実施の形態における記憶装置は、読み出し回路においてトランジスタのしきい値電圧を制御することにより、記憶素子のデータ保持特性が経時劣化した場合でも正常な書き込み状態を維持することができる。10

**【0103】**

また、本実施の形態における記憶装置の記憶素子に有機材料を用いた短絡型有機メモリを適用することにより、安価に作製することができ、また、構成する材料を変えることで特性を容易に変えることもできる。また、本発明の記憶装置の記憶素子には、短絡型有機メモリだけではなく、上記実施の形態1で述べた様々な種類のものを適用することができる。

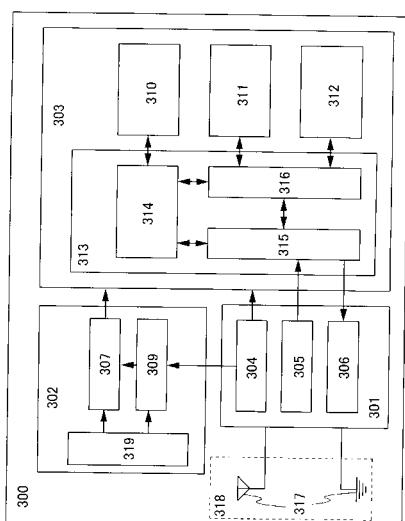

**(実施の形態3)****【0104】**

本実施の形態では、本発明の記憶装置を有する半導体装置について説明する。20

**【0105】**

本実施の形態における半導体装置は、内部に記憶回路を有し、記憶回路に必要な情報を記憶し、非接触手段、例えば無線通信を用いて外部と情報のやりとりを行うものである。この特徴を利用して、本実施の形態における半導体装置は、物品などの個体情報を記憶させておき、その情報を読み取ることにより物品の認識をさせる個体認証システムなどの用途があり、これらの用途に用いるには、個体情報のデータを記憶して物品の識別などを行うため、より高い信頼性が要求される。

**【0106】**

本実施の形態における半導体装置の構成について図7を用いて説明する。図7は、本実施の形態における半導体装置の構成を示すブロック図である。30

**【0107】**

図7に示すように半導体装置300は、高周波回路301、クロック生成回路302、ロジック回路303、及びアンテナ部318におけるアンテナ317により構成されている。なお、図7には示していないが、半導体装置300は、無線通信装置などの外部の回路とアンテナ317を介して無線信号の送受信を行っている。なお、データの伝送形式は、一対のコイルを対向配置して相互誘導によって交信を行う電磁結合方式、誘導電磁界によって交信する電磁誘導方式、電波を利用して交信する電波方式の3つに大別され、本実施の形態ではいずれの方式でも適用することができる。

**【0108】**

次に各回路の構成について説明する。高周波回路301は電源回路304と、復調回路305と、変調回路306と、を有する。また、クロック生成回路302は、分周回路307と、カウンタ回路309と、基準クロック生成回路319と、を有する。また、ロジック回路303は、演算処理を行う機能を有し、コントローラ313と、CPU(中央演算装置ともいう)310と、ROM(Read Only Memory)311と、RAM(Random Access Memory)312と、を有する。40

**【0109】**

また、コントローラ313は、CPUインターフェイス314と、RFインターフェイス315と、メモリコントローラ316と、を有する。

**【0110】**

また、高周波回路 301において、電源回路 304は、整流回路と、保持容量と、を有し、受信した信号から電源電圧を生成し、その他の回路に供給する機能を有する。また復調回路 305は、整流回路と、LPF（ローパスフィルタ）と、を有し、通信信号からコマンドやデータを抽出する機能を有する。変調回路 306は、送信データを変調する機能を有し、変調されたデータは、アンテナ 317から送信信号として送信される。

#### 【0111】

次に本実施の形態における半導体装置の動作について説明する。まず、外部の通信装置から送信された信号が、半導体装置で受信される。半導体装置に入力された受信信号は、復調回路 305で復調された後、コントローラ 313におけるRFインターフェイス 315に出力される。RFインターフェイス 315に入力された受信信号は、CPUインターフェイス 314を介してCPU 310で演算処理される。また、RFインターフェイス 315に入力された受信信号により、メモリコントローラ 316を介してROM 311、RAM 312に対するアクセスが行われる。10

#### 【0112】

そして、CPU 310による演算処理、ROM 311、RAM 312におけるデータの入出力後に送信データが生成され、送信データは、信号として変調回路 306で変調され、アンテナ 317から外部の通信装置に送信される。

#### 【0113】

本実施の形態では、本発明の記憶装置を半導体装置のROM 311、RAM 312、またはその他の記憶回路として搭載することができる。本発明の記憶装置を搭載することにより、信頼性の高い半導体装置を提供することができる。また、本発明の記憶装置は安価に製造することができるため、半導体装置の製造コストを低減することができる。20

#### 【0114】

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

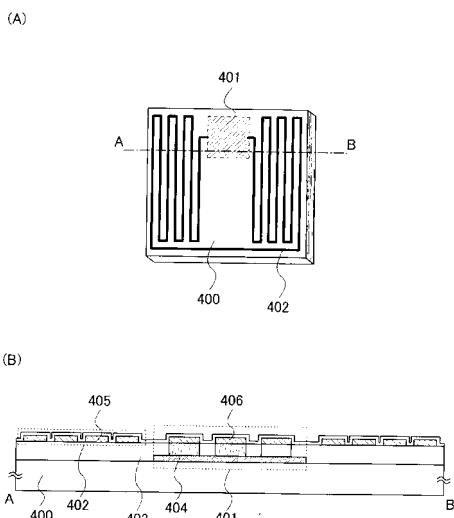

#### (実施の形態4)

#### 【0115】

本実施の形態では、本発明の記憶装置を有する半導体装置の作製方法について説明する。。

#### 【0116】

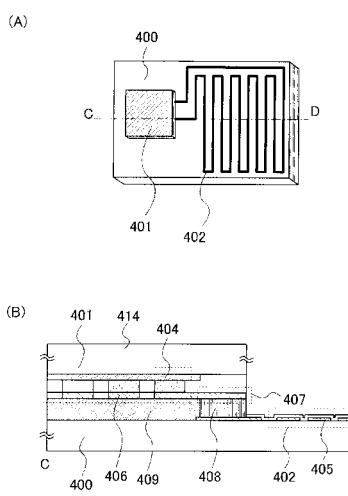

本実施の形態の半導体装置について図8を用いて説明する。図8は、本実施の形態における半導体装置の構成を示す模式図及び断面図である。30

#### 【0117】

図8(A)に示すように本実施の形態における半導体装置は、基板400と、基板400に設けられた素子部401と、素子部401に電気的に接続されたアンテナ402と、を有する。

#### 【0118】

素子部401は、記憶素子等の複数の素子を有し、外部から受信した信号を処理する機能を有し、アンテナ402は、半導体装置におけるデータの伝送を行う機能を有する。

#### 【0119】

さらに図8(B)に示すように本実施の形態における半導体装置は、基板400上に設けられた素子404と、素子404及び基板400上に設けられた層間膜403と層間膜403上に設けられたアンテナ402として機能する導電層405と、素子404に接続された導電層406及び素子404と電気的に接続された導電層406を有する素子部401と、を有する。40

#### 【0120】

なお、図8(B)の構成において、導電層406と同じ層にアンテナ402として機能する導電層405を設けているが、これに限定されない。素子部401を設けた後、素子部を覆うように別途絶縁膜を設け、絶縁膜上に導電層405を設ける構成も適用することができる。

#### 【0121】

また、本実施の形態の半導体装置は、図8の構成に限定されない。本実施の形態の半導体装置の他の構成例について図9を用いて説明する。図9は、本実施の形態における半導体装置の他の構成の模式図及び断面図である。

#### 【0122】

図9(A)に示すように本実施の形態における半導体装置は、基板400と、基板400上に設けられた素子部401及び素子部401に電気的に接続されたアンテナ402と、を有する。

#### 【0123】

図8の構成と同様に素子部401は、記憶素子等の複数の素子を有し、外部から受信した信号を処理する機能を有し、アンテナ402は、半導体装置におけるデータの伝送を行う機能を有する。

10

#### 【0124】

さらに図9(B)に示すように本実施の形態における半導体装置は、基板400と、基板400の一部の上に設けられたアンテナ402となる導電層405及び樹脂409と、導電層405の一部の上に設けられた導電性粒子408と、樹脂409の一部の上及び導電性粒子408の一部の上に設けられた導電層406と、導電層406上に設けられた素子部401と、素子部401上に設けられた基板414と、を有する。

#### 【0125】

図9の構成の場合、端子部407を設けており、導電層406と同じ層に設けた導電層が端子部407として用いられる。そして、端子部407に電気的に接続するように、素子部401が設けられた基板414とアンテナ402が設けられた基板400とが貼り合わされている。

20

#### 【0126】

本実施の形態において、素子部401における記憶装置として本発明の記憶装置を適用することができる。本発明の記憶装置を適用することにより高い信頼性を有する半導体装置を安価に製造することができる。

#### 【0127】

素子部401は、予め大きな面積の基板上に複数形成し、その後、分断することで形成すれば、安価に形成することができる。このときに用いる基板400及び基板414としては、ガラス基板、石英基板、セラミック基板、金属基板(例えばステンレス基板など)、または半導体基板(例えばシリコン基板など)などを適用することができる。他にもプラスチック基板として、ポリエチレンテレフタラート(PET)、ポリエチレンタレート(PEN)、ポリエーテルサルファン(PES)、アクリルなどの可撓性基板等を適用することができる。

30

#### 【0128】

素子部401に含まれる複数のトランジスタや記憶装置等は、同じ層に設ける構成に限定されず、複数の層に形成した構成とすることもできる。複数の層に素子部401を形成する際には、層間絶縁膜を用いるが、当該層間絶縁膜の材料としては、エポキシ樹脂やアクリル樹脂等の樹脂材料、透過性を有するポリイミド樹脂等の樹脂材料、シロキサン樹脂等のシロキサン材料を有する化合物材料、水溶性ホモポリマーと水溶性共重合体を含む材料、無機材料を適用することができ、また、これらの材料を複数種選択して積層構造とすることもできる。シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。有機基は、フルオロ基を含んでもよい。また、層間絶縁膜は、CVD法、スパッタリング法、SOG法、液滴吐出法、スクリーン印刷法等により、形成することができる。

40

#### 【0129】

また、層間絶縁膜の材料として、層間で発生する寄生容量の減少を目的として、低誘電率材料を適用することも好適である。寄生容量が減少すれば、高速の動作を実現し、また、低消費電力化を実現する。

50

## 【0130】

導電層405及び導電層406は、CVD法、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、またはメッキ法等を用いて形成することができる。導電層405及び導電層406としては、アルミニウム、チタン、銀、銅、金、白金、ニッケル、パラジウム、タンタル、モリブデンから選択された元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造または積層構造で形成することができる。

## 【0131】

例えば、スクリーン印刷法を用いて導電層405及び導電層406を形成する場合には、粒径が数nmから数十μmの導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀、金、銅、ニッケル、白金、パラジウム、タンタル、モリブデンおよびチタン等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。また、導電層の形成において、焼成工程は導電性のペーストを押し出した後に行うことが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子（例えば粒径1nm以上100nm以下）を用いる場合、150以上300以下の温度範囲で焼成することにより硬化させて導電層を得ることができる。また、微粒子として、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径20μm以下の微粒子を用いることが好ましい。はんだや鉛フリーのはんだを用いることにより、低コストで製造することができる。

## 【0132】

素子部401に上記集積回路などを設ける場合など、素子部に用いられるトランジスタは、非晶質半導体、微結晶半導体（マイクロクリスタル半導体ともいう）、多結晶半導体、または有機半導体等のいずれの半導体を単層または積層させて活性層として作製されたものを適用することができる。良好な特性のトランジスタを得るために、金属元素を触媒として結晶化した活性層、レーザ照射法により結晶化した活性層を用いるとよい。また、プラズマCVD法により、SiH<sub>4</sub>/F<sub>2</sub>ガス、SiH<sub>4</sub>/H<sub>2</sub>ガス（Arガス）を用いて形成した半導体層や、半導体層にレーザ照射を行ったものを活性層として適用することができる。

## 【0133】

また、素子部401に用いられるトランジスタは、200度から600度の温度（好適には350度から500度）で結晶化した結晶質半導体層（低温ポリシリコン層）や、600度以上の温度で結晶化した結晶質半導体層（高温ポリシリコン層）を用いることができる。なお、基板上に高温ポリシリコン層を作成する場合は、ガラス基板では熱に脆弱な場合があるので、石英基板を使用するとよい。

## 【0134】

素子部401に用いられるトランジスタの活性層（特にチャネル領域）には、 $1 \times 10^{19}$  atoms/cm<sup>3</sup> ~  $1 \times 10^{22}$  atoms/cm<sup>3</sup> の濃度、好適には $1 \times 10^{11}$  atoms/cm<sup>3</sup> ~  $5 \times 10^{20}$  atoms/cm<sup>3</sup> の濃度で、水素又はハロゲン元素を添加するとよい。そうすると、欠陥が少なく、クラックが生じにくい活性層を得ることができる。

## 【0135】

また、素子部401に用いられるトランジスタを包むように、又は素子部401自身を包むように、アルカリ金属等の汚染物質をブロックするバリア膜を設けるとよい。そうすると、汚染されることはなく、信頼性が向上した素子部401を提供することができる。なおバリア膜としては、窒化珪素膜、窒化酸化珪素膜又は酸化窒化珪素膜等が挙げられる。また、素子部401が含むトランジスタの活性層の厚さは、20nm ~ 200nm、好

10

20

30

40

50

ましくは40nm～170nm、さらに好ましくは45nm～55nm、145nm～155nm、さらに好ましくは50nm、150nmとするよい。そうすると、折り曲げても、クラックが生じにくい素子部401を提供することができる。

#### 【0136】

また、素子部401に用いられるトランジスタの活性層を構成する結晶は、キャリアの流れる方向（チャネル長方向）と平行に延びる結晶粒界を有するように形成するとよい。このような活性層は、連続発振レーザや、10MHz以上、好ましくは60～100MHzで動作するパルスレーザを用いて形成するとよい。

#### 【0137】

また、素子部401に用いられるトランジスタは、S値（サブスレッシュホールド値）0.35V/dec以下（好ましくは0.09～0.25V/dec）、移動度 $10\text{ cm}^2/\text{Vs}$ 以上の特性を有するとよい。このような特性は、活性層を、連続発振レーザや、10MHz以上で動作するパルスレーザで形成すれば、実現することができる。

#### 【0138】

また、素子部401に用いられるトランジスタは、リングオシレータレベルで1MHz以上、好適には10MHz以上（3～5Vにて）の特性を有する。または100kHz以上、好適には1MHz以上（3～5Vにて）のゲートあたりの周波数特性を有する。

#### 【0139】

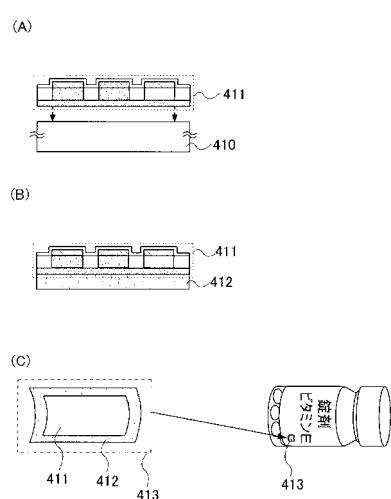

また、素子部が形成された基板をそのまま用いることができるがこれに限定されない。素子部が形成された基板とは別の基板を用いる例について図10を用いて説明する。図10は、本実施の形態における半導体装置の他の構成及び作製方法を示す模式図である。

#### 【0140】

図10（A）に示すように、素子部411が形成された基板410において、基板410上の素子部411を剥離する。さらに図10（B）に示すように剥離した素子部411を基板410とは別の基板412に貼り合わせた構成とすることもできる。なお、基板412としては、例えば可撓性基板などを適用することができる。

#### 【0141】

基板410からの素子部411の剥離は、耐熱性の高い基板410と素子部411の間に金属酸化膜を設け、当該金属酸化膜を結晶化により脆弱化して、素子部411を剥離する方法、耐熱性の高い基板410と素子部411の間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッチングにより当該非晶質珪素膜を除去することで、素子部411を剥離する方法、または素子部411が形成された耐熱性の高い基板410を機械的に削除又は溶液やCF<sub>3</sub>等のガスによるエッチングで除去することで、素子部411を切り離す方法等を用いて行うことができる。

#### 【0142】

また、上記記載の方法以外にも、基板410と素子部411の間に剥離層として機能する金属膜（例えば、タンゲステン、モリブデン、チタン、タンタル、コバルト）、金属酸化膜（例えば、タンゲステン酸化物、モリブデン酸化物、チタン酸化物、タンタル酸化物、コバルト酸化物または金属膜と金属酸化膜との積層構造）を設け、基板410と素子部411とを物理的手段を用いて剥離することも可能である。また、他にも選択的に開口部を形成して剥離層を露出させた後に、フッ化ハロゲン（例えば、ClF<sub>3</sub>）等のエッチング剤によって剥離層の一部を除去した後に、基板410から素子部411を物理的に剥離することもできる。

#### 【0143】

また、剥離した素子部411の基板412への貼り付けは、市販の接着剤を用いればよく、例えば、エポキシ樹脂系接着剤や樹脂添加剤等の接着剤を用いればよい。

#### 【0144】

上記のように、素子部411を基板412に貼り合わせて半導体装置を作製することにより、薄くて軽く、落下した場合にも壊れにくい半導体装置を提供することができる。また、基板412は可撓性を有する基板を適用するため、曲面や異形の形状上に貼り合わせ

10

20

30

40

50

ることが可能となり、多種多様の用途が実現する。例えば、図10(C)に示すように、薬の瓶のような曲面上に、本発明の半導体装置413を密着して貼り合わせることができる。さらに、基板410を再利用することにより、より安価に半導体装置を提供することができる。

**【0145】**

なお、本実施の形態は、他の実施の形態と適宜組み合わせができる。

(実施の形態5)

**【0146】**

本実施の形態は、剥離プロセスを用いて、可撓性を有する半導体装置を作製する場合について説明する。

10

**【0147】**

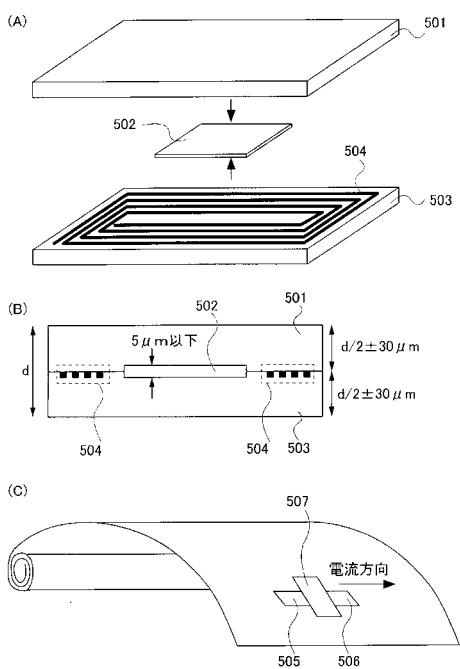

本実施の形態における半導体装置を作製する方法について図11を用いて説明する。図11は、本実施の形態における半導体装置の構成を示す上面図である。

**【0148】**

図11(A)に示すように本実施の形態における半導体装置は、可撓性を有する保護層501と、アンテナ504を含む可撓性を有する保護層503と、剥離プロセスにより形成する素子部502とを有する。保護層503上に形成されたアンテナ504は、素子部502に電気的に接続する。図示する構成では、アンテナ504は保護層503上にのみ形成されているが、本発明はこの構成に限定されず、アンテナ504を保護層501上にも形成することもできる。また、素子部502と、保護層501、503との間には、窒化珪素膜等からなるバリア膜を形成する構成とすることにより、素子部502が汚染されることなく、信頼性を向上させた半導体装置を提供することもできる。

20

**【0149】**

アンテナ504として機能する導電層としては、上記実施の形態4において述べた材料を適用することができる。なお、本実施の形態では、素子部502とアンテナ504とは、異方性導電膜を用いてUV処理又は超音波処理を行うことで接続させるが、この方法に限定されず、様々な方法を用いることができる。

**【0150】**

図11(B)に示すように保護層501、503に挟まれた素子部502の厚さは、5μm以下、好ましくは0.1μm～3μmの厚さを有するように形成するとよい。また、保護層501、503を重ねたときの厚さをdとしたとき、保護層501、503の厚さは、好ましくは(d/2)±30μm、さらに好ましくは(d/2)±10μmとする。また、保護層501、503の厚さは10μm～200μmであることが望ましい。さらに、素子部502の面積は5mm角(25mm<sup>2</sup>)以下であり、望ましくは0.3mm角～4mm角(0.09mm<sup>2</sup>～16mm<sup>2</sup>)の面積を有するとよい。

30

**【0151】**

保護層501、503は、有機樹脂材料で形成されているため、折り曲げに対して強い特性を有する。また、剥離プロセスにより形成した素子部502自体も、単結晶半導体に比べて、折り曲げに対して強い特性を有する。そして、素子部502と、保護層501、503とは空隙がないように、密着させることができるために、完成した半導体装置自体も折り曲げに対して強い特性を有する。このような保護層501、503で囲われた素子部502は、他の個体物の表面または内部に配置しても良いし、紙の中に埋め込んでも良い。

40

**【0152】**

次に剥離プロセスにより形成する素子部を、曲面を有する基板に貼る場合について説明する。

**【0153】**

図11(C)に示すように、剥離プロセスにより形成した素子部から選択された1つのトランジスタは、電流が流れる方向に直線状である。つまり、ドレイン電極505～ゲート電極507～ソース電極506の位置は直線状である。そして、電流が流れる方向と、

50

基板が弧を描く方向は垂直に配置される。このような配置にすれば、基板が折り曲げられて、弧を描いても、応力の影響が少なく、素子部に含まれるトランジスタの特性の変動を抑制することができる。

#### 【 0 1 5 4 】

また、トランジスタなどのアクティブ素子の活性領域（シリコンアイランド部分）の面積を基板全体の面積に対して、1%～50%（好ましくは1～30%）にすることにより、応力を起因とする素子の破壊を防止することができる。

#### 【 0 1 5 5 】

また、アクティブ素子の存在しない領域には、下地絶縁膜材料、層間絶縁膜材料及び配線材料が主として設けられる。トランジスタ等の活性領域以外の面積は、基板全体の面積の60%以上にすることが好ましい。このようにすると、曲げやすく、高い集積度を有する半導体装置を提供することができる。10

#### 【 0 1 5 6 】

以上のように、本実施の形態における半導体装置の作製方法を用いて本発明の記憶装置を有する半導体装置を作製することにより、曲面上においても作製することができ、半導体装置の適用分野をより拡大することができる。

#### 【 0 1 5 7 】

なお、本実施の形態は他の実施の形態と適宜組み合わせることができる。

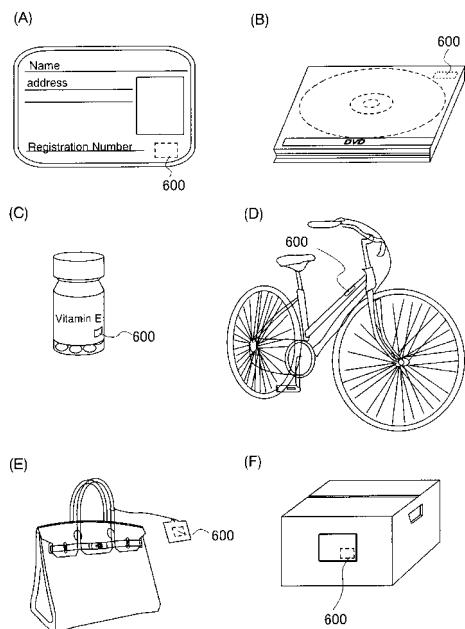

（実施の形態 6 ）

#### 【 0 1 5 8 】

本実施の形態では、上記実施の形態における記憶装置を備えた半導体装置の使用例について説明する。20

#### 【 0 1 5 9 】

上記実施の形態における記憶装置を備えた半導体装置の使用例について図12を用いて説明する。図12は、本発明の半導体装置の使用例を示す模式図である。

#### 【 0 1 6 0 】

図12に示すように、半導体装置の用途は広範囲にわたるが、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類（運転免許証や住民票等、図12（A）参照）、包装用容器類（包装紙やボトル等、図12（C）参照）、記録媒体（DVDソフトやビデオテープ等、図12（B）参照）、乗り物類（自転車等、図12（D）参照）、身の回り品（鞄や眼鏡等）、食品類、植物類、動物類、人体、衣類、生活用品類、または電子機器（液晶表示装置、EL表示装置、テレビジョン装置、または携帯電話）等の物品、若しくは各物品に取り付ける荷札（図12（E）、図12（F）参照）等に設けて使用することができる。30

#### 【 0 1 6 1 】

本発明の半導体装置600は、プリント基板に実装、表面に貼る、または埋め込むことにより、物品に固定される。例えば、本であれば紙に埋め込む、または有機樹脂からなるパッケージであれば当該有機樹脂に埋め込み、各物品に固定される。本発明の半導体装置600は、小型、薄型、軽量を実現するため、物品に固定した後もその物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、または証書類等に本発明の半導体装置600を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。また、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、または電子機器等に本発明の半導体装置を取り付けることにより、検品システム等のシステムの効率化を図ることができる。また、乗り物類であっても、本発明の半導体装置を取り付けることにより、盗難などに対するセキュリティ性を高めることができる。40

#### 【 0 1 6 2 】

以上のように、本発明の記憶装置を備えた半導体装置を本実施の形態に挙げた各用途に用いることにより、情報のやりとりに用いられるデータを正確な値のまま維持することができるため、物品の認証性、またはセキュリティ性を高めることができる。50

**【0163】**

なお、本実施の形態は、他の実施の形態と適宜組み合わせることができる。

**【実施例1】****【0164】**

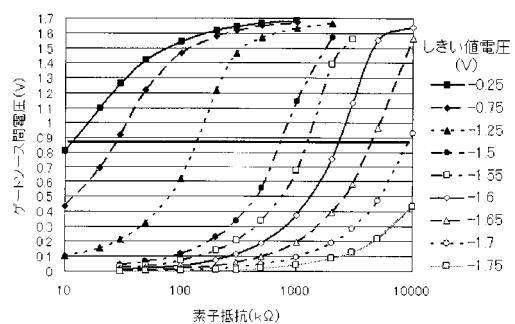

本実施例では、本発明の記憶装置の読み出しトランジスタにおいて、しきい値電圧を所定の値となるように制御した場合におけるしきい値抵抗の変化についてシミュレーションによる計算結果について説明する。

**【0165】**

本実施例における記憶装置のしきい値電圧変化によるしきい値抵抗変化計算結果について図13に示す。図13は、本実施例の記憶装置のしきい値電圧としきい値抵抗の関係を示す図である。なお本実施例の読み出し回路におけるトランジスタは、Pチャネル型トランジスタであり、ゲート幅が8μm、ゲート長が10μmとする。

10

**【0166】**

図13の結果では、しきい値電圧が-0.75Vのとき、しきい値抵抗は約30kΩであるのに対し、しきい値電圧を-1.6Vに変化させたときは、しきい値抵抗は約2MΩとなり、2MΩと高い抵抗値まで書き込み状態と認識されることがわかる。

**【0167】**

以上のように、計算結果では、読み出しトランジスタのしきい値電圧の絶対値を増大させる方向にシフトさせた場合は、書き込み状態／未書き込み状態を区別するしきい値抵抗もまた増大する。前述したように書き込み状態／未書き込み状態のしきい値抵抗R<sub>th</sub>は、経時変化により変化した抵抗の最大値R<sub>max</sub>と未書き込み状態での抵抗の初期値R<sub>0</sub>の間に設定しなくてはならないため、経時変化により変化した抵抗の最大値を1MΩ、未書き込み状態における抵抗の初期値を5MΩとした場合、好適なPチャネル型トランジスタのしきい値電圧は-1.55V以下-1.65V以上の範囲となる。

20

**【図面の簡単な説明】****【0168】**

【図1】実施の形態1における本発明の記憶装置の構成を示すブロック図である。

【図2】実施の形態1における本発明の記憶装置の構成を示す回路図である。

【図3】実施の形態1における本発明の記憶装置に適用可能なトランジスタの構成例を示す断面図である。

30

【図4】実施の形態1における本発明の記憶装置に適用可能なトランジスタの構成例を示す断面図である。

【図5】実施の形態2における本発明の記憶装置の構成を示すブロック図である。

【図6】実施の形態2における本発明の記憶装置のメモリセルの構成を示す断面図である。

。

【図7】実施の形態3における本発明の半導体装置の構成を示すブロック図である。

【図8】実施の形態4における本発明の半導体装置の構成を示す模式図及び断面図である。

。

【図9】実施の形態4における本発明の半導体装置の構成を示す模式図及び断面図である。

40

【図10】実施の形態4における本発明の半導体装置の作製方法の一例を示す断面図及び模式図である。

【図11】実施の形態5における本発明の半導体装置の作製方法の一例を示す模式図及び断面図である。

【図12】実施の形態6における本発明の半導体装置の使用例を示す模式図である。

【図13】実施例1におけるトランジスタのしきい値電圧としきい値抵抗との関係を示す図である。

【図14】従来例における時間経過に対する記憶素子の抵抗値の変化を示す図である。

**【符号の説明】****【0169】**

50

|         |                     |    |

|---------|---------------------|----|

| 1 0 0   | メモリセル               |    |

| 1 0 1   | ワード線                |    |

| 1 0 2   | 第2の信号線(ビット線ともいう)    |    |

| 1 0 3   | 読み出し回路              |    |

| 1 0 4   | 電源線                 |    |

| 1 0 5   | 第1の信号線(アドレス信号線ともいう) |    |

| 1 0 6   | 出力端子                |    |

| 1 0 7   | 第1のトランジスタ           |    |

| 1 0 8   | 記憶素子                |    |

| 1 0 9   | 第2のトランジスタ           | 10 |

| 1 1 0   | 第3のトランジスタ           |    |

| 1 1 1   | インバータ               |    |

| 1 1 2   | クロックドインバータ          |    |

| 1 1 3   | 外部端子                |    |

| 1 0 0 0 | 基板                  |    |

| 1 0 0 1 | 第1のゲート電極            |    |

| 1 0 0 2 | 第1のゲート絶縁膜           |    |

| 1 0 0 3 | 半導体層                |    |

| 1 0 0 4 | 第1の不純物領域            |    |

| 1 0 0 5 | 第2の不純物領域            | 20 |

| 1 0 0 6 | 第2のゲート絶縁膜           |    |

| 1 0 0 7 | 第2のゲート電極            |    |

| 1 0 0 9 | 絶縁層                 |    |

| 1 0 1 0 | 第1の配線               |    |

| 1 0 1 1 | 第2の配線               |    |

| 1 0 1 2 | 基板                  |    |

| 1 0 1 3 | ウェル領域               |    |

| 1 0 1 4 | 第1の不純物領域            |    |

| 1 0 1 5 | 第2の不純物領域            |    |

| 1 0 1 6 | 第3の不純物領域            | 30 |

| 1 0 1 7 | 第1の絶縁層              |    |

| 1 0 1 8 | 第2の絶縁層              |    |

| 1 0 1 9 | ゲート絶縁膜              |    |

| 1 0 2 0 | ゲート電極               |    |

| 1 0 2 1 | 絶縁層                 |    |

| 1 0 2 2 | 第1の配線               |    |

| 1 0 2 3 | 第2の配線               |    |

| 1 0 2 4 | 第3の配線               |    |

| 2 0 0   | メモリセルアレイ            |    |

| 2 0 1   | 読み出し/書き込み回路         | 40 |

| 2 0 2   | カラムデコーダ             |    |

| 2 0 3   | セレクタ回路              |    |

| 2 0 4   | ロウデコーダ              |    |

| 2 0 5   | ワード線                |    |

| 2 0 6   | 第2の信号線              |    |

| 2 0 7   | メモリセル               |    |

| 2 0 0 0 | 基板                  |    |

| 2 0 0 1 | 半導体層                |    |

| 2 0 0 2 | ゲート絶縁膜              |    |

| 2 0 0 3 | ゲート電極               | 50 |

|         |                                              |    |

|---------|----------------------------------------------|----|

| 2 0 0 4 | 不純物領域                                        |    |

| 2 0 0 5 | 不純物領域                                        |    |

| 2 0 0 6 | 第1の絶縁層                                       |    |

| 2 0 0 7 | 第2の絶縁層                                       |    |

| 2 0 0 8 | 配線                                           |    |

| 2 0 0 9 | 配線                                           |    |

| 2 0 1 0 | 第3の絶縁層                                       |    |

| 2 0 1 1 | 第1の電極                                        |    |

| 2 0 1 2 | 第4の絶縁層                                       |    |

| 2 0 1 3 | 有機化合物層                                       | 10 |

| 2 0 1 4 | 第2の電極                                        |    |

| 3 0 0   | 半導体装置                                        |    |

| 3 0 1   | 高周波回路                                        |    |

| 3 0 2   | クロック生成回路                                     |    |

| 3 0 3   | ロジック回路                                       |    |

| 3 0 4   | 電源回路                                         |    |

| 3 0 5   | 復調回路                                         |    |

| 3 0 6   | 変調回路                                         |    |

| 3 0 7   | 分周回路                                         |    |

| 3 0 9   | カウンタ回路                                       | 20 |

| 3 1 0   | C P U (中央演算装置ともいう)                           |    |

| 3 1 1   | R O M (R e a d O n l y M e m o r y )         |    |

| 3 1 2   | R A M (R a n d o m A c c e s s M e m o r y ) |    |

| 3 1 3   | コントローラ                                       |    |

| 3 1 4   | C P U インターフェイス                               |    |

| 3 1 5   | R F インターフェイス                                 |    |

| 3 1 6   | メモリコントローラ                                    |    |

| 3 1 7   | アンテナ                                         |    |

| 3 1 8   | アンテナ部                                        |    |

| 3 1 9   | クロック生成回路                                     | 30 |

| 4 0 0   | 基板                                           |    |

| 4 0 1   | 素子部                                          |    |

| 4 0 2   | アンテナ                                         |    |

| 4 0 3   | 層間膜                                          |    |

| 4 0 4   | 素子                                           |    |

| 4 0 5   | 導電層                                          |    |

| 4 0 6   | 導電層                                          |    |

| 4 0 7   | 端子部                                          |    |

| 4 0 8   | 導電性粒子                                        |    |

| 4 0 9   | 樹脂                                           | 40 |

| 4 1 0   | 基板                                           |    |

| 4 1 1   | 素子部                                          |    |

| 4 1 2   | 基板                                           |    |

| 4 1 3   | 半導体装置                                        |    |

| 4 1 4   | 基板                                           |    |

| 5 0 1   | 保護層                                          |    |

| 5 0 2   | 素子部                                          |    |

| 5 0 3   | 保護層                                          |    |

| 5 0 4   | アンテナ                                         |    |

| 5 0 5   | ドレイン電極                                       | 50 |

|       |                     |

|-------|---------------------|

| 5 0 6 | ソース電極               |

| 5 0 7 | ゲート電極               |

| 6 0 0 | 半導体装置               |

| 7 0 0 | 抵抗値                 |

| 7 0 1 | 抵抗値                 |

| 7 0 2 | 抵抗値                 |

| 7 0 3 | 抵抗値                 |

| 7 0 4 | 未書き込み状態と判別される抵抗値の範囲 |

| 7 0 5 | 書き込み状態と判別される抵抗値の範囲  |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(58)調査した分野(Int.Cl., DB名)

G 11 C 13 / 00