(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5127117号

(P5127117)

(45) 発行日 平成25年1月23日(2013.1.23)

(24) 登録日 平成24年11月9日(2012.11.9)

(51) Int.Cl.

F 1

**G09G 3/30 (2006.01)**

**G09G 3/20 (2006.01)**

**H01L 51/50 (2006.01)**

GO9G 3/30 J

GO9G 3/30 H

GO9G 3/20 611A

GO9G 3/20 612A

GO9G 3/20 621M

請求項の数 6 (全 43 頁) 最終頁に続く

(21) 出願番号

特願2005-80838 (P2005-80838)

(22) 出願日

平成17年3月22日 (2005.3.22)

(65) 公開番号

特開2005-338777 (P2005-338777A)

(43) 公開日

平成17年12月8日 (2005.12.8)

審査請求日

平成20年3月13日 (2008.3.13)

(31) 優先権主張番号

特願2004-80739 (P2004-80739)

(32) 優先日

平成16年3月19日 (2004.3.19)

(33) 優先権主張国

日本国 (JP)

(31) 優先権主張番号

特願2004-134759 (P2004-134759)

(32) 優先日

平成16年4月28日 (2004.4.28)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 棚田 好文

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 納 光明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 安西 彩

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

最終頁に続く

(54) 【発明の名称】表示装置、電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の画素を含む画素領域、ソースドライバ、第1のゲートドライバ及び第2のゲートドライバを有し、

前記複数の画素の各々は、発光素子、第1のトランジスタ及び第2のトランジスタを有し、

前記ソースドライバは第1の選択回路を、前記第1のゲートドライバ及び前記第2のゲートドライバは第2の選択回路を、それぞれ有し、

前記第1のトランジスタは、ゲートはゲート線に、ソース又はドレインの一方はソース線に、ソース又はドレインの他方は前記第2のトランジスタのゲートに電気的に接続され、

前記第2のトランジスタは、ソース又はドレインの一方は電源線に、ソース又はドレインの他方は前記発光素子に電気的に接続され、

前記第1のトランジスタのオンとオフは、前記ゲート線を介して、前記第1のゲートドライバと前記第2のゲートドライバのそれぞれが含む前記第2の選択回路の出力ノードから出力される信号により制御され、

前記第1の選択回路の入力ノードに入力される信号を、前記第2の選択回路の入力ノードに入力される信号よりも遅延させる遅延回路を有し、

前記第1のゲートドライバは、信号の書き込みをする画素行を選択する第1の選択動作を行う機能を有し、

10

20

前記第2のゲートドライバは、画素へ書き込まれた信号を消去する画素行を選択する第2の選択動作を行う機能を有し、

前記第1の選択回路は、画素への書き込み信号を出力する機能、または画素へ書き込まれた信号を消去するための信号を出力する機能の一方を選択する第3の選択動作を行う機能を有し、

前記第2の選択回路は、前記第1のゲートドライバ、または前記第2のゲートドライバの一方を選択する第4の選択動作を行う機能を有し、

前記遅延回路は、前記第1の選択回路の第3の選択動作を、前記第2の選択回路の第4の選択動作より遅延させる機能を有することを特徴とする表示装置。

#### 【請求項2】

10

複数の画素を含む画素領域、ソースドライバ、第1のゲートドライバ及び第2のゲートドライバを有し、

前記複数の画素の各々は、発光素子、第1のトランジスタ及び第2のトランジスタを有し、

前記ソースドライバは第1の選択回路を、前記第1のゲートドライバ及び前記第2のゲートドライバは第2の選択回路を、それぞれ有し、

前記第1のトランジスタは、ゲートはゲート線に、ソース又はドレインの一方はソース線に、ソース又はドレインの他方は前記第2のトランジスタのゲートに電気的に接続され、

前記第2のトランジスタは、ソース又はドレインの一方は電源線に、ソース又はドレインの他方は前記発光素子に電気的に接続され、

20

前記第1のトランジスタのオンとオフは、前記ゲート線を介して、前記第1のゲートドライバと前記第2のゲートドライバのそれそれが含む前記第2の選択回路の出力ノードから出力される信号により制御され、

前記第1の選択回路の入力ノードに入力される信号を、前記第2の選択回路の入力ノードに入力される信号よりも遅延させる遅延回路を有し、

前記第1のゲートドライバは、第1のサブフレームに対応する信号の書き込みをする画素行を選択する第1の選択動作を行う機能を有し、

前記第2のゲートドライバは、第2のサブフレームに対応する信号の書き込みをする画素行を選択する第2の選択動作を行う機能を有し、

30

前記第1の選択回路は、第1のサブフレームに対応する信号を出力する機能、または第2のサブフレームに対応する信号を出力する機能の一方を選択する第3の選択動作を行う機能を有し、

前記第2の選択回路は、前記第1のゲートドライバ、または前記第2のゲートドライバの一方を選択する第4の選択動作を行う機能を有し、

前記遅延回路は、前記第1の選択回路の第3の選択動作を、前記第2の選択回路の第4の選択動作より遅延させる機能を有することを特徴とする表示装置。

#### 【請求項3】

請求項1乃至請求項2において、

前記複数の画素の各々は、容量素子を有し、

40

前記容量素子は、第1の半導体層、絶縁層及び導電層を有し、

前記第1の半導体層、前記第1のトランジスタの第2の半導体層及び前記第2のトランジスタの第3の半導体層上に、前記絶縁層が設けられており、

前記絶縁層上に、前記導電層、前記第1のトランジスタのゲート及び前記第2のトランジスタのゲートが設けられていることを特徴とする表示装置。

#### 【請求項4】

請求項1乃至請求項2において、

前記複数の画素の各々は、容量素子を有し、

前記容量素子は、第1の導電層、第1の絶縁層及び第2の導電層を有し、

前記第1の導電層、前記第1のトランジスタのゲート及び前記第2のトランジスタのゲ

50

ート上に、前記第1の絶縁層が設けられており、

前記第1の絶縁層上に、前記第2の導電層、前記第1のトランジスタのソース又はドレインの一方に接続された前記ソース線、及び前記第2のトランジスタのソース又はドレインの一方に接続された前記電源線が設けられていることを特徴とする表示装置。

【請求項5】

請求項1乃至請求項2において、

前記画素領域には、前記電源線が列方向に複数本設けられ、

隣接する画素間で前記電源線を共有することを特徴とする表示装置。

【請求項6】

請求項1乃至請求項5のいずれか一項に記載の前記表示装置を用いた電子機器。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は自発光素子を含む表示装置及びその駆動方法、テレビジョン装置に関する。また、絶縁表面上に素子が設けられた素子基板に関する。また、複数の素子を含むソースドライバ、ゲートドライバに関する。

【0002】

また本発明は、発光素子を含む表示装置を用いた電子機器に関する。

【背景技術】

【0003】

近年、EL(Electro Luminescence)素子を代表とする発光素子を含む表示装置の開発が進められ、自発光型ゆえの高画質、広視野角、薄型、軽量等の利点を活かして、幅広い利用が期待されている。発光素子は、その輝度が電流値に比例する性質を有するため、階調を正確に表現するために、当該発光素子に一定の電流を流す定電流駆動を採用する表示装置がある(特許文献1参照)。

【特許文献1】特開2003-323159号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

情報端末や携帯電話機などの表示機能を搭載した電子機器の普及が進められているが、このような電子機器は、バッテリーを用いているものが多く、消費電力の削減が課題となっている。しかしながら、特許文献1に記載の表示装置のように、定電流駆動を採用すると、発光素子に直列に接続された駆動用のトランジスタを飽和領域で動作させなければいけないため、駆動電圧を高くする必要があり、消費電力の削減は見込めない。そこで本発明は、消費電力を削減することができる表示装置及びその駆動方法を提供することを課題とする。

【課題を解決するための手段】

【0005】

本発明の表示装置は、複数の画素を含む画素領域と、ソースドライバと、第1のゲートドライバと、第2のゲートドライバとを有する。複数の画素の各々は、発光素子と、画素に対するビデオ信号の入力を制御する第1のトランジスタと、発光素子の発光又は非発光を制御する第2のトランジスタと、ビデオ信号を保持する容量素子とを有する。 40

【0006】

第1のトランジスタのゲート電極は、ゲート線を介して、第1のゲートドライバと第2のゲートドライバに接続する。第1のトランジスタのソース電極及びドレイン電極の一方は、ソース線を介して、ソースドライバに接続する。第1のトランジスタのソース電極及びドレイン電極の他方は第2のトランジスタのゲート電極に接続する。第2のトランジスタのソース電極及びドレイン電極の一方は、発光素子の画素電極に接続する。第2のトランジスタのソース電極及びドレイン電極の他方は電源に接続することを特徴とする。

【0007】

10

20

30

40

50

上記構成を有する本発明は、画素に配置するトランジスタが2つだけであることから、高開口率を実現する。高開口率が実現すると、光を発する面積の増加に伴って、発光素子の輝度を下げることができる。従って、発光素子の駆動電圧を低くして、消費電力を削減することができる。

【0008】

本発明の表示装置は、発光素子に一定の電圧を印加する定電圧駆動を採用する。定電圧駆動は、駆動用のトランジスタを飽和領域で動作させる必要がなく、また、駆動電圧を高くする必要もないため、定電流駆動と比較して、消費電力を削減することができる。

【0009】

容量素子は、第1のトランジスタ及び第2のトランジスタが含む半導体層と同じ層に設けられた半導体層と、第1のトランジスタ及び第2のトランジスタが含むゲート電極と同じ層に設けられた導電層と、半導体層と導電層の間に設けられた絶縁層とを含むことを特徴とする。また、容量素子は、第1のトランジスタ及び第2のトランジスタが含むゲート電極と同じ層に設けられた第1の導電層と、第1のトランジスタ及び第2のトランジスタのソース電極又はドレイン電極に接続する導電層（ソース配線又はドレイン配線に相当）と同じ層に設けられた第2の導電層と、第1の導電層と第2の導電層の間に設けられた絶縁層とを含むことを特徴とする。

10

【0010】

上記構成を有する本発明は、容量素子はソース配線又はドレイン配線の下部に設けるため、1つの画素の面積を有効利用することができ、容量素子の配置による開口率の減少は生じない。

20

【0011】

また、第1のトランジスタ及び第2のトランジスタのソース電極又はドレイン電極に接続する導電層（ソース配線又はドレイン配線に相当）の厚さは500nm乃至1300nmであることを特徴とする。

【0012】

また、第1のトランジスタと第2のトランジスタの上部に設けられた第1の絶縁層と、第1の絶縁層に接する第2の絶縁層とを有し、第2の絶縁層上に発光素子が含む第1の電極が設けられることを特徴とする。

30

【0013】

また、発光素子が含む第1の電極の端部を覆う隔壁層（絶縁層）を有し、容量素子の上部に配置される隔壁層（絶縁層）の列方向の幅は10乃至25μmであることを特徴とする。また、発光素子が含む第1の電極の端部を覆う隔壁層（絶縁層）を有し、隔壁層（絶縁層）は遮光性を有することを特徴とする。

【0014】

また、発光素子の第1の電極及び第2の電極の一方は反射性を有し、他方は透光性を有することを特徴とする。また、発光素子の第1の電極及び第2の電極は透光性を有することを特徴とする。

【0015】

本発明の表示装置は、発光素子に逆方向バイアスを印加することができるよう、第1の電源と第2の電源の電位を変える電源制御回路を有することを特徴とする。

40

【0016】

本発明の表示装置は、周囲の温度に基づき動作するモニター回路と、モニター回路の出力に基づき、画素領域に供給する電源電位を変える電源制御回路とを有することを特徴とする。モニター回路は、モニター用発光素子を有することを特徴とする。

【0017】

本発明の表示装置が含むソースドライバは、パルス出力回路と、ラッチと、選択回路とを有し、パルス出力回路の入力ノードに接続する第1の保護回路と、パルス出力回路とラッチの間に設けられた第2の保護回路と、選択回路と画素領域の間に設けられた第3の保護回路とを有することを特徴とする。

50

**【 0 0 1 8 】**

本発明の表示装置が含む第1のゲートドライバと第2のゲートドライバの各々は、パルス出力回路と、選択回路とを有し、パルス出力回路の入力ノードに接続する第1の保護回路と、選択回路と画素領域の間に設けられた第2の保護回路とを有することを特徴とする。

**【 0 0 1 9 】**

保護回路は、抵抗素子、容量素子及び整流素子から選択された1種又は複数種であることを特徴とする。また、整流素子はゲート電極とドレイン電極が接続されたトランジスタ又はダイオードであることを特徴とする。また、パルス出力回路は複数のフリップフロップ回路又はデコーダ回路であることを特徴とする。

**【 0 0 2 0 】**

発光素子は、三重項励起状態からの赤色発光を呈する材料、一重項励起状態からの緑色発光を呈する材料、又は一重項励起状態からの青色発光を呈する材料とを有することを特徴とする。または、発光素子は、三重項励起状態からの赤色発光を呈する材料、三重項励起状態からの緑色発光を呈する材料、又は一重項励起状態からの青色発光を呈する材料とを有することを特徴とする。発光効率がよい三重項励起状態からの発光を呈する材料を用いることにより、消費電力の削減を実現することができる。

**【 0 0 2 1 】**

本発明の表示装置が含む画素領域には、第1の電源に接続する電源線が列方向に複数本設けられ、隣接する画素間で電源線を共有することを特徴とする。

**【 0 0 2 2 】**

本発明は、上記構成を有する表示装置において、発光素子の画素電極までを形成した状態である素子基板を提供する。より詳しくは、素子基板は、絶縁表面上に、トランジスタと、トランジスタに接続する画素電極までを形成した状態のものであり、電界発光層と対向電極を形成していない状態に相当する。

**【 0 0 2 3 】**

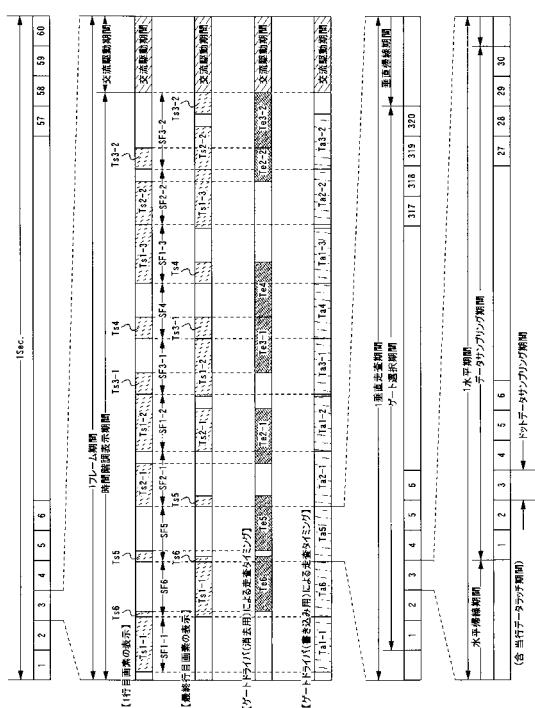

また本発明の表示装置は以下のように動作する。1フレーム期間は複数のサブフレーム期間S F 1、S F 2、…、S F n (nは自然数)を有し、複数のサブフレーム期間の各々は、複数の書き込み期間T a 1、T a 2、…、T a nから選択された1つと、複数の点灯期間T s 1、T s 2、…、T s nから選択された1つとを有し、複数の書き込み期間の各々は複数のゲート選択期間を有し、複数のゲート選択期間の各々は複数のサブゲート選択期間を有し、複数の点灯期間の長さはT s 1 : T s 2 : … : T s n = 2^(n-1) : 2^(n-2) : … : 2^0を満たし、複数の点灯期間の出現する順序はランダムであることを特徴とする。

**【 0 0 2 4 】**

又は、複数のサブフレーム期間から選択された1つ又は複数の期間は複数に分割され、分割された1つ又は複数のサブフレーム期間の各々と、分割されていない1つ又は複数のサブフレーム期間の各々は、複数の書き込み期間T a 1、T a 2、…、T a m (mは自然数)から選択された1つと、複数の点灯期間T s 1、T s 2、…、T s mから選択された1つとを有し、複数の書き込み期間の各々は複数のゲート選択期間を有し、複数のゲート選択期間の各々は複数のサブゲート選択期間を有することを特徴とする。

**【 0 0 2 5 】**

又は、複数のサブフレーム期間から選択された1つ又は複数の期間は複数に分割され、分割された1つ又は複数のサブフレーム期間の各々と、分割されていない1つ又は複数のサブフレーム期間の各々は、複数の書き込み期間T a 1、T a 2、…、T a m (mは自然数)から選択された1つと、複数の点灯期間T s 1、T s 2、…、T s mから選択された1つとを有し、複数の書き込み期間の各々は複数のゲート選択期間を有し、複数のゲート選択期間の各々は複数のサブゲート選択期間を有し、複数の点灯期間の出現する順序はランダムであることを特徴とする。

**【 0 0 2 6 】**

そして、複数のサブゲート選択期間から選択された1つの期間において、第1のゲートド

10

20

30

40

50

ライバ及び第2のゲートドライバの一方によりゲート線が選択され、複数のサブゲート選択期間から選択された1つの期間において、第1のゲートドライバ及び第2のゲートドライバの他方によりゲート線が選択され、発光素子は、第2のトランジスタのゲート電極に入力されるビデオ信号に基づき、発光又は非発光することを特徴とする。

#### 【0027】

なお、本発明において、適用可能なトランジスタの種類に限定はなく、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ(TFT)、半導体基板やSOI基板を用いて形成されるMOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類に限定はなく、単結晶基板、SOI基板、ガラス基板などに配置することができる。10

#### 【0028】

また、本発明において、接続されているとは、電気的に接続されていることと同義である。したがって、本発明が開示する構成において、所定の接続関係に加え、その間に電気的な接続を可能とする他の素子(例えば、別の素子やスイッチなど)が配置されていてもよい。

#### 【0029】

また、画素などにおける容量素子は、トランジスタなどのゲート容量によって、代用することが出来る。その場合は、容量素子を省略できる。20

#### 【0030】

また、スイッチは、電気的スイッチでも機械的スイッチでも何でも良い。スイッチは、電流の流れを制御できるものなら、何でも良い。トランジスタでもよいし、ダイオードでもよいし、それらを組み合わせた論理回路でもよい。よって、スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流が少ない方が望ましい場合、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないとトランジスタとしては、LDD領域を設けているもの等がある。また、スイッチとして動作させるトランジスタのソース端子の電位が、低電位側電源(VSS、Vgnd、0Vなど)に近い状態で動作する場合はnチャネル型を、反対に、ソース端子の電位が、高電位側電源(VDDなど)に近い状態で動作する場合はpチャネル型を用いることが望ましい。なぜなら、ゲート・ソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。なお、nチャネル型とpチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。30

#### 【発明の効果】

#### 【0031】

定電圧駆動を用いる本発明は、定電流駆動を用いる場合と比較すると、発光素子の駆動電圧を低くすることができるため、消費電力を削減することができる。

#### 【発明を実施するための最良の形態】

#### 【0032】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。40

#### 【0033】

#### (実施の形態1)

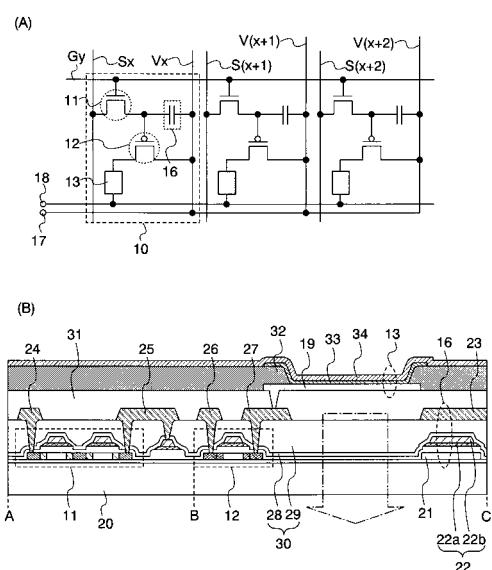

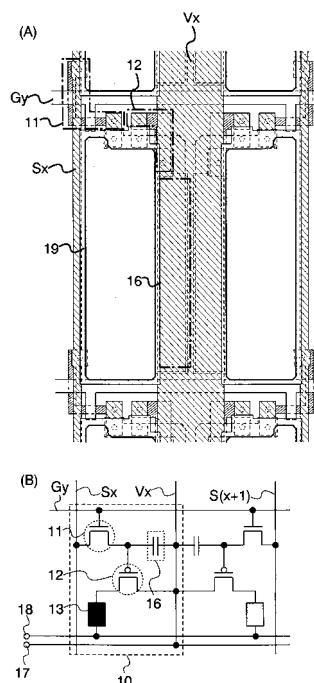

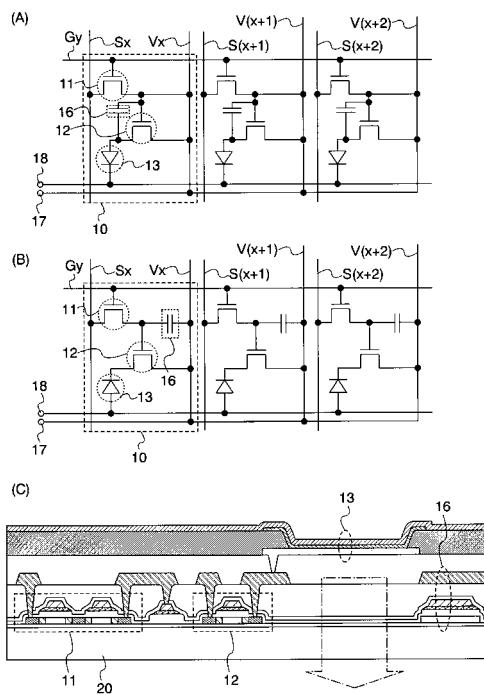

本発明の表示装置の構成について図1～3を参照して説明する。本発明の表示装置は、ソース線S<sub>x</sub>(xは自然数、1～m)と、ゲート線G<sub>y</sub>(yは自然数、1～n)が絶縁体を介して交差する領域に複数の素子を含む画素10を複数有する(図1(A)参照50)

）。画素10は、発光素子13と、容量素子16と、2つのトランジスタとを有する。2つのトランジスタのうち、1つは画素10に対するビデオ信号の入力を制御するスイッチング用トランジスタ11（以下TFT11と表記することがある）であり、もう1つは発光素子13の発光と非発光を制御する駆動用トランジスタ12（以下TFT12と表記と表記することがある）である。TFT11、12は電界効果トランジスタであり、ゲート電極、ソース電極、ドレイン電極の3つの端子を有する。

【 0 0 3 4 】

TFT11のゲート電極はゲート線Gyに接続し、ソース電極及びドレイン電極の一方はソース線Sxに接続し、他方はTFT12のゲート電極に接続する。TFT12のソース電極及びドレイン電極の一方は電源線Vx(xは自然数、1≤x≤m)を介して第1の電源17に接続し、他方は発光素子13の画素電極に接続する。発光素子13の対向電極は、電源線を介して、第2の電源18に接続する。容量素子16はTFT12のゲート電極とソース電極の間に設けられる。TFT11、12の導電型は制約されず、N型とP型のどちらの導電型でもよいが、図示する構成では、TFT11はN型、TFT12がP型の場合を示す。第1の電源17の電位と第2の電源18の電位も特に制約されないが、発光素子13に順方向バイアス又は逆方向バイアスの電圧が印加されるように、互いに異なる電位に設定する。

( 0 0 3 5 )

第1の電源17に接続された電源線Vxと、第2の電源18に接続された電源線は、一定の電位に保たれている。

[ 0 0 3 6 ]

上記構成を有する本発明の表示装置は、画素10に配置するトランジスタの個数が2つである点を特徴とする。上記特徴により、1つの画素10にレイアウトするトランジスタの個数が少なくし、またトランジスタの個数が少ないとから、必然的に配置する配線の本数を少なくすることができるため、高開口率、高精細化、高歩留まりを実現する。また、高開口率が実現すると、光を発する面積の増加に伴って、発光素子の輝度を下げるができる。つまり電流密度を下げることができる。従って、駆動電圧を下げることができるため、消費電力を削減することができる。また、駆動電圧を下げることで、信頼性向上させることができる。

[ 0 0 3 7 ]

TFT11、12を構成する半導体は、非晶質半導体（アモルファスシリコン）、微結晶半導体、多結晶半導体（ポリシリコン）、有機半導体等のいずれもよい。微結晶半導体は、シランガス( $\text{SiH}_4$ )とフッ素ガス( $\text{F}_2$ )を用いて形成するか、シランガスと水素ガスを用いて形成するか、上記に挙げたガスを用いて薄膜を形成後にレーザ光の照射を行って形成してもよい。

[ 0 0 3 8 ]

TFT11、12のゲート電極は、導電性材料により単層又は積層で形成する。例えば、タンゲステン(W)と窒化タンゲステン(WN、タンゲステン(W)と窒素(N)の組成比は制約されない)の積層構造や、モリブデン(Mo)、アルミニウム(Al)及びモリブデン(Mo)の積層構造、モリブデン(Mo)と窒化モリブデン(MoN、モリブデン(Mo)と窒素(N)の組成比は制約されない)の積層構造を採用するとよい。

( 0 0 3 9 )

TFT11、12が含む不純物領域（ソース電極とドレイン電極）に接続する導電層（ソース配線又はドレイン配線に相当）は、導電性材料により単層又は積層で形成する。例えば、チタン（Ti）、アルミニウムシリコン（Al-Si）、シリコン（Si）が添加されたアルミニウム（Al）、チタン（Ti）の積層構造、モリブデン（Mo）、アルミニウム-シリコン（Al-Si、シリコン（Si）が添加されたアルミニウム（Al）及びモリブデン（Mo）の積層構造、窒化モリブデン（MoN、モリブデン（Mo）と窒素（N）の組成比は制約されない）、アルミニウム-シリコン（Al-Si、シリコン（Si）が添加されたアルミニウム（Al））及び窒化モリブデン（MoN、モリブデン（Mo）

○)と窒素(N)の組成比は制約されない)の積層構造を採用するとよい。

#### 【0040】

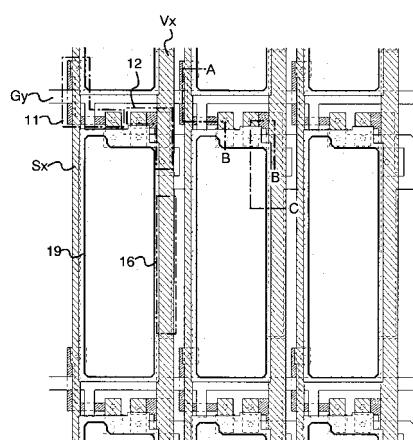

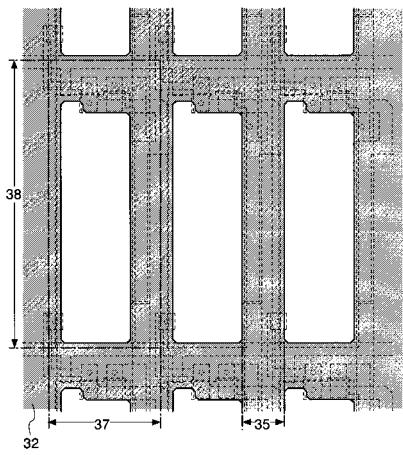

次に、上記構成を有する画素10のレイアウトを図2に示す。このレイアウトでは、TFT11、12、容量素子16、発光素子13の画素電極に相当する導電層19を示す。続いて、このレイアウトのA-B-Cに対応する断面構造を図1(B)に示す。ガラスや石英などの絶縁表面を有する基板20上にTFT11、12、発光素子13、容量素子16が設けられている。

#### 【0041】

発光素子13は、画素電極に相当する導電層19、電界発光層33、対向電極に相当する導電層34の積層体に相当する。導電層19、34の両者が透光性を有する場合、発光素子13は、導電層19に向かう方向と、導電層34に向かう方向に光を発する。つまり発光素子13は両面出射を行う。また、導電層19、34の一方が透光性を有し、他方が遮光性を有する場合、発光素子13は導電層19に向かう方向のみか、導電層34に向かう方向のみに光を発する。つまり発光素子13は上面出射又は下面出射を行う。図1(B)は、発光素子13が下面出射を行う場合の断面構造を示す。

10

#### 【0042】

容量素子16は、TFT12のゲート電極とソース電極の間に配置され、当該TFT12のゲート・ソース間電圧を保持する。容量素子16は、TFT11、12が含む半導体層と同じ層に設けられた半導体層21と、TFT11、12のゲート電極と同じ層に設けられた導電層22a、22b(以下総称して導電層22と表記)と、半導体層21と導電層22の間の絶縁層により容量を形成する点を特徴とする。

20

#### 【0043】

なお、TFT11の半導体層と、TFT12の半導体層と、容量素子16の半導体層21は、同じ下地用絶縁層上に設けられている。

#### 【0044】

また、容量素子16はTFT11、12のゲート電極と同じ層に設けられた導電層22と、TFT11、12のソース電極又はドレイン電極に接続する導電層(ソース配線又はドレイン配線に相当)24~27と同じ層に設けられた導電層23と、導電層22と導電層23の間の絶縁層により容量を形成する点を特徴とする。

上記特徴により、容量素子16はTFT12のゲート・ソース間電圧を保持するのに十分な容量値を得ることができる。また、容量素子16は、電源線を構成する導電層の下部に設けられており、そのために、容量素子16の配置による開口率の減少は生じない。

30

#### 【0045】

また、TFT11、12のソース配線又はドレイン配線に相当する導電層24~27と導電層23の厚さは、500nm乃至2000nm、好ましくは500nm乃至1300nmである点を特徴とする。導電層23~27は、ソース線Sxや電源線Vxを構成しているため、上記特徴のように、導電層23~27の膜厚を厚くすることで、電圧降下による影響を抑制することができる。なお、導電層23~27を厚くすると配線抵抗を小さくすることができるが、逆に、導電層23~27を厚くしすぎると、パターン加工を正確に行なうことが困難になったり、表面の凸凹が問題になったりする。つまり、導電層23~27の厚さは、配線抵抗と、パターン加工のし易さと表面の凸凹の影響とを考慮して、上記の範囲内で決定するとよい。

40

#### 【0046】

また、TFT11、12を覆う絶縁層28、29(以下総称して第1の絶縁層30と表記)と、第1の絶縁層30上に設けられた第2の絶縁層31とを有し、第2の絶縁層31上に画素電極に相当する導電層19を有する点を特徴とする。仮に、第2の絶縁層31を設けないとすると、ソース配線又はドレイン配線に相当する導電層24~27と導電層23は、導電層19とは同じ層に設けることになる。そうすると、導電層19を設ける領域は、導電層23~27を設けた領域以外に制約されてしまう。しかしながら、第2の絶縁層31を設けることにより、導電層19を設ける領域のマージンが広がり、高開口率を実現

50

する。上面出射の場合、この構成は特に有効である。高開口率を実現すると、光を発する面積の増加に伴って、駆動電圧を下げる、消費電力を削減することができる。

#### 【0047】

なお第1の絶縁層30と第2の絶縁層31は、酸化珪素や窒化珪素等の無機材料、ポリイミドやアクリル等の有機材料等を用いて形成する。第1の絶縁層30と第2の絶縁層31を同じ材料で形成してもよいし、互いに異なる材料で形成してもよい。また、第1の絶縁層30と第2の絶縁層31を形成する材料としては、シロキサン系の材料を用いればよく、例えば、シリコンと酸素との結合で骨格構造が構成され、置換基に少なくとも水素を含む有機基（例えば、アルキル基、芳香族炭化水素）が用いられるもの、又は、シリコンと酸素との結合で骨格構造が構成され、置換基にフルオロ基が用いられるもの、又はシリコンと酸素との結合で骨格構造が構成され、置換基に、少なくとも水素を含む有機基とフルオロ基とが用いられるものである。10

#### 【0048】

また、画素10の間に隔壁層32（バンク、土手、又は絶縁層ともよぶ）が設けられるが、容量素子16上の隔壁層32の幅35は、その下部に設けられた配線を隠すことができる幅であればよい。具体的には、幅35は、7.5乃至27.5μm、好ましくは10μm乃至25μmである点を特徴とする（図3参照）。このように、隔壁層32の幅を狭くすることで、高開口率を実現する。高開口率を実現すると、光を発する面積の増加に伴って、駆動電圧を下げる、消費電力を削減することができる。

#### 【0049】

なお、図示するレイアウトによれば、画素の開口率は約50%である。図示するレイアウトの画素10の列方向（縦方向）の長さは幅38で示し、行方向（横方向）の長さは幅37で示す。隔壁層32は、無機材料と有機材料のどちらの材料を用いて形成してもよい。但し、隔壁層32に接するように、電界発光層を設けるため、当該電界発光層にピンホールなどが生じないように、曲率半径が連続的に変化する形状を有するとよい。20

#### 【0050】

また、隔壁層32は遮光性を有する点を特徴とする。上記特徴により、画素10間の輪郭が明瞭なものとなり、高精細な画像を表示することができる。隔壁層32は、顔料やカーボンナノチューブを含み、これらの顔料やカーボン等の添加物により、着色され、そのために遮光性を有する。30

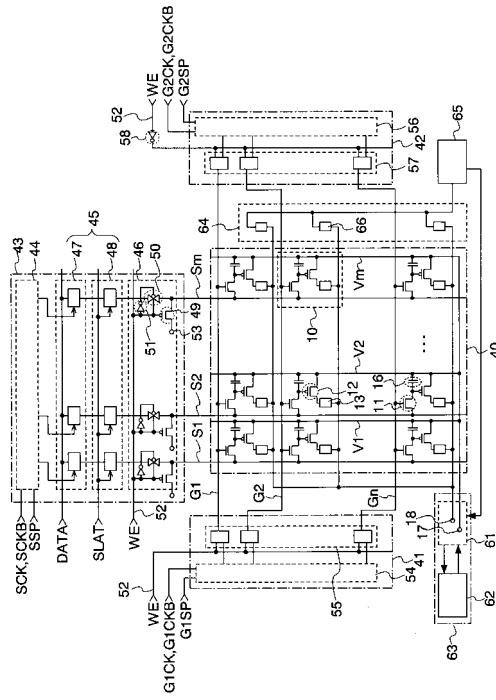

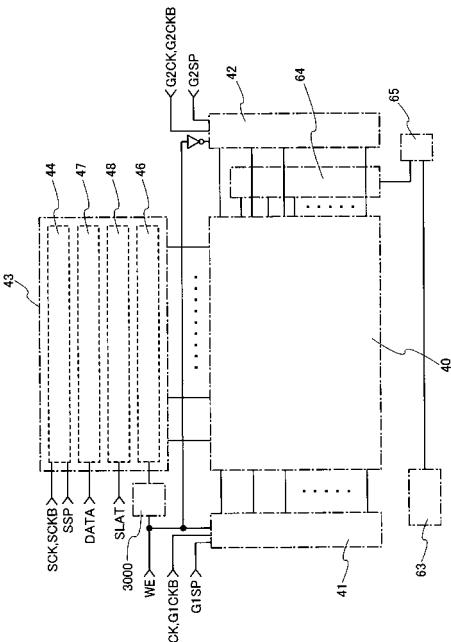

#### 【0051】

また、本発明の表示装置は、上述した画素10がマトリクス状に複数配置された画素領域40と、第1のゲートドライバ41と、第2のゲートドライバ42と、ソースドライバ43とを有する（図4参照）。第1のゲートドライバ41と第2のゲートドライバ42は、画素領域40を挟んで対向するように配置するか、画素領域40の上下左右の四方のうち一方に配置する。

#### 【0052】

ソースドライバ43は、パルス出力回路44、ラッチ45及び選択回路46を有する。ラッチ45は第1のラッチ47と第2のラッチ48を有する。選択回路46は、トランジスタ49（以下TFT49と表記）と、アナログスイッチ50を有する。TFT49とアナログスイッチ50は、ソース線Sxに対応して、各列に設けられる。インバータ51は、WE信号（Write Erase）の反転信号を生成するためのものであり、外部からWE信号の反転信号を供給する場合には設けなくてもよい。40

#### 【0053】

TFT49のゲート電極は選択信号線52に接続し、ソース電極及びドレイン電極の一方はソース線Sxに接続し、他方は電源53に接続する。アナログスイッチ50は、第2のラッチ48とソース線Sxの間に設けられる。つまり、アナログスイッチ50の入力ノードは第2のラッチ48に接続し、出力ノードはソース線Sxに接続する。アナログスイッチ50の2つの制御ノードは、一方は選択信号線52に接続し、他方はインバータ51を介して選択信号線52に接続する。電源53の電位は、画素10が含むTFT12をオフ50

にする電位であり、TFT12がN型の場合は電源53の電位をLレベルとし、TFT12がP型の場合は電源53の電位をHレベルとする。

#### 【0054】

第1のゲートドライバ41はパルス出力回路54と選択回路55を有する。第2のゲートドライバ42はパルス出力回路56と選択回路57を有する。選択回路55、57は、選択信号線52に接続する。但し、第2のゲートドライバ42が含む選択回路57は、インバータ58を介して選択信号線52に接続する。つまり、選択信号線52を介して、選択回路55、57に入力されるWE信号は、互いに反転した関係にある。

#### 【0055】

選択回路55、57の各々はトライステートバッファを有する。トライステートバッファの入力ノードはパルス出力回路54又はパルス出力回路56に接続し、制御ノードは選択信号線52に接続する。トライステートバッファの出力ノードはゲート線Gyに接続する。トライステートバッファは、選択信号線52から伝達される信号がHレベルのときに動作状態となり、Lレベルのときに不定状態となる。

10

#### 【0056】

なお、不定状態とは、動作状態の反対の状態である。

#### 【0057】

ソースドライバ43が含むパルス出力回路44、第1のゲートドライバ41が含むパルス出力回路54、第2のゲートドライバ42が含むパルス出力回路56は、複数のフリップフロップ回路からなるシフトレジスタやデコーダ回路に相当する。パルス出力回路44、54、56として、デコーダ回路を適用すれば、ソース線Sx又はゲート線Gyをランダムに選択することができる。ソース線Sx又はゲート線Gyをランダムに選択することができると、時間階調方式を適用した場合に生じる疑似輪郭の発生を抑制することができる。

20

#### 【0058】

なおソースドライバ43の構成は上記の記載に制約されず、レベルシフタやバッファを設けてもよい。また、第1のゲートドライバ41と第2のゲートドライバ42の構成も上記の記載に制約されず、レベルシフタやバッファを設けてもよい。また、上記には記載していないが、ソースドライバ43、第1のゲートドライバ41、第2のゲートドライバ42は、保護回路を有することを特徴とする。保護回路を有するドライバの構成については、以下の実施の形態3において後述する。

30

#### 【0059】

このように、第1のゲートドライバ41のn段目(nは自然数)の出力と、第2のゲートドライバ42のn段目の出力は、n行目のゲート線を制御する。第1のゲートドライバ41と第2のゲートドライバ42の出力端には、信号の出力を制御する選択回路が設けられている。また、第1のゲートドライバ41と第2のゲートドライバ42の一方は、ビデオ信号の書き込みが行われる画素行を選択するゲートドライバであり、他方は、画素に書き込まれた信号を消去する画素行を選択するゲートドライバである。

#### 【0060】

また本発明の表示装置は、電源制御回路63を有することを特徴とする。電源制御回路63は、発光素子13に電源を供給する電源回路61とコントローラ62を有する。電源回路61は、TFT12と電源線Vxを介して発光素子13の画素電極に接続する。また、電源回路61は、電源線を介して、発光素子13の対向電極に接続する。

40

#### 【0061】

発光素子13に順方向バイアスの電圧を印加して、発光素子13に電流を流して発光させるとときは、第1の電源17の電位が、第2の電源18の電位よりも高くなるように、第1の電源17と第2の電源18の電位差を設定する。

#### 【0062】

一方、発光素子13に逆方向バイアスの電圧を印加する際は、第1の電源17の電位が、第2の電源18の電位よりも低くなるように、第1の電源17と第2の電源18の電位を

50

設定する。このような電源電位の設定は、コントローラ 6 2 から電源回路 6 1 に所定の信号を供給することにより、行われる。

#### 【 0 0 6 3 】

本発明は、電源制御回路 6 3 を用いて、発光素子 1 3 に逆方向バイアスの電圧を印加することで、発光素子 1 3 の経時劣化を抑制し、信頼性を向上させることができる。また、発光素子 1 3 は、異物の付着や、陽極又は陰極にある微細な突起によるピンホール、電界発光層の不均一性を起因として、陽極と陰極が短絡する初期不良が生じることがある。このような初期不良が発生すると、信号に応じた画素の点灯及び非点灯が行われず、電流のほとんどすべてが陽極と陰極の短絡部を流れて素子全体が消光する現象が生じたり、特定の画素が点灯又は非点灯しない現象が生じたりして、画像の表示が良好に行われないという問題が発生する。しかしながら、本発明の構成によると、発光素子に逆方向バイアスを印加することができるため、陽極と陰極の短絡部のみに局所的に電流を流し、短絡部を発熱させ、その結果、短絡部を酸化又は炭化して絶縁化することができる。その結果、初期不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。なお、このような初期不良の絶縁化は、出荷前に行うとよい。また、初期不良だけでなく、時間の経過に伴い、新たに陽極と陰極の短絡が発生することがある。このような不良は進行性不良とも呼ばれるが、本発明の構成によると、定期的に発光素子に逆方向バイアスを印加することができるので、進行性不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。なお、発光素子 1 3 に逆方向バイアスの電圧を印加するタイミングには特に制約はない。10

#### 【 0 0 6 4 】

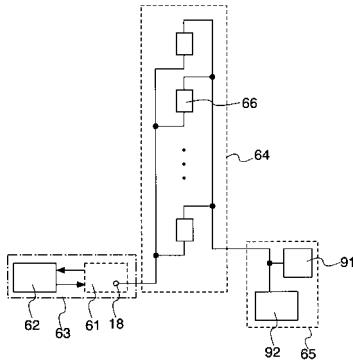

また本発明の表示装置は、モニター回路 6 4 と制御回路 6 5 を有することを特徴とする。モニター回路 6 4 は、周囲の温度（以下環境温度と表記）に基づき動作する。制御回路 6 5 は定電流源とバッファを有する。図示する構成では、モニター回路 6 4 は、モニター用発光素子 6 6（以下発光素子 6 6 と表記することがある）を有する。20

#### 【 0 0 6 5 】

制御回路 6 5 は、モニター回路 6 4 の出力に基づき、電源電位を変更する信号を、電源制御回路 6 3 に供給する。電源制御回路 6 3 は、制御回路 6 5 から供給される信号に基づき、画素領域 4 0 に供給する電源電位を変更する。上記構成を有する本発明は、環境温度の変化に起因した電流値の変動を抑制して、信頼性を向上させることができる。なおモニター回路 6 4 と制御回路 6 5 の詳しい構成については、以下の実施の形態 4 において後述する。30

#### 【 0 0 6 6 】

定電圧駆動を行う本発明の表示装置は、発光素子の輝度が  $500 \text{ cd/m}^2$ 、画素の開口率が 50 % のとき、消費電力が 1 W 以下 ( $950 \text{ mW}$ ) となった。一方、定電流駆動を行う表示装置は、発光素子の輝度が  $500 \text{ cd/m}^2$ 、画素の開口率が 25 % のとき、消費電力は約 2 W ( $2040 \text{ mW}$ ) であった。つまり、定電圧駆動を採用することで、消費電力を削減することができる事が分かる。なお、定電圧駆動を採用することで、消費電力は 1 W 以下、好ましくは 0.7 W 以下にまで削減することができる。40

#### 【 0 0 6 7 】

なお、上記の消費電力の値は、画素領域のみの消費電力であり、駆動回路部分の消費電力は含まれていない。また、両者とも時間階調の表示デューティー比は 70 % である。

#### 【 0 0 6 8 】

また、上記の消費電力の測定を行った、定電圧駆動を行う表示装置と定電流駆動を行う表示装置の画素領域の画素数は、 $240 \times 3 \times 320$  であり、両者で同じであった。

#### 【 0 0 6 9 】

なお、すでに述べたように、本発明におけるトランジスタは、どのようなタイプのトランジスタでもよいし、どのような基板上に形成されていてもよい。したがって、図 4 で示したような回路が、全てガラス基板上に形成されていてもよいし、プラスチック基板に形成されていてもよいし、単結晶基板に形成されていてもよいし、SOI 基板上に形成されて50

いてもよいし、どのような基板上に形成されていてもよい。あるいは、図4における回路の一部が、ある基板に形成されており、図4における回路の別の一部が、別の基板に形成されていてもよい。つまり、図4における回路の全てが同じ基板上に形成されていなくてもよい。例えば、図4において、画素領域40と第1のゲートドライバ41とは、ガラス基板上にTFTを用いて形成し、ソースドライバ43（もしくはその一部）は、単結晶基板上に形成し、そのICチップをCOG（Chip On Glass）で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB（Tape Auto Bonding）やプリント基板を用いてガラス基板と接続してもよい。

#### 【0070】

##### （実施の形態2）

10

上記の構成では、TFT12はP型の場合を例示したが、TFT12がN型の場合について、図19を参照して説明する。

#### 【0071】

画素10は、発光素子13と、容量素子16と、TFT11、12とを有する（図19（A）参照）。発光素子13が順積み構造を有する場合（画素電極が陽極、対向電極が陰極）、発光素子13の電流の流れる方向に従って、発光素子13に順方向バイアスの電圧を印加する際は、第1の電源17は高電位電源、第2の電源18は低電位電源となる。発光素子13に逆方向バイアスの電圧を印加する際は、第1の電源17は低電位電源、第2の電源18は高電位電源となる。また、容量素子16は、TFT12のゲート・ソース間電圧を保持するためのものであり、上記構成によると、TFT12のソース電極は、発光素子13の画素電極に接続する側の端子であるので、容量素子16は発光素子13の画素電極とTFT12のゲート電極の間に設けられる。

20

#### 【0072】

一方、発光素子13が逆積み構造を有する場合（画素電極が陰極、対向電極が陽極）、発光素子13の電流の流れる方向に従って、発光素子13に順方向バイアスの電圧を印加する際は、第1の電源17は低電位電源、第2の電源18は高電位電源となる。発光素子13に逆方向バイアスの電圧を印加する際は、第1の電源17は高電位電源、第2の電源18は低電位電源となる。また、TFT12のソース電極は、電源線Vxに接続する側の端子であるので、容量素子16は、電源線VxとTFT12のゲート電極の間に設けられる。

30

#### 【0073】

前者の図19（A）に示す表示装置の断面構造を図19（C）に示す。表示装置は、ガラスや石英などの絶縁表面を有する基板20上にTFT11、12、発光素子13、容量素子16が設けられている。TFT11の導電型は特に制約されないが、TFT11もN型とすれば、TFT11、12の両TFTは同じ導電型となる。そうすると、TFTを作り分ける必要がないため、歩留まりを向上させることができる。

#### 【0074】

上記構成を有する本発明の表示装置は、画素10に配置するトランジスタの個数が2つである点を特徴とする。上記特徴により、高開口率、高精細化、高歩留まりを実現する。また、高開口率を実現することで、駆動電圧を下げることができるため、消費電力を削減することができる。

40

#### 【0075】

##### （実施の形態3）

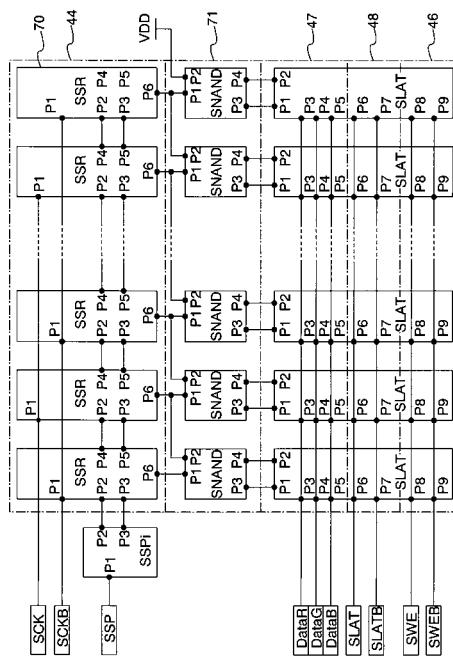

本発明の表示装置が有するソースドライバ43の構成について図5～7を参照して説明する。ソースドライバ43はパルス出力回路44、NAND71、第1のラッチ47、第2のラッチ48、選択回路46（第1のラッチ47、第2のラッチ48及び選択回路46を総称して図面ではSLATと表記）を有する（図5参照）。パルス出力回路44は、複数の単位回路（SSR）70が縦列接続した構成を有する。パルス出力回路44には、クロック信号（SCK）、クロックバック信号（SCKB）、スタートパルス（SSP）が供給される。第1のラッチ47にはデータ信号（DataR、DataG、DataB）が

50

供給される。第2のラッチ48にはラッチパルス(SLAT)、ラッチパルスの反転パルス(SLATB)が供給される。選択回路46には書き込み消去信号(SWE、Write Erase信号、以下WE信号と表記することがある)と、WE信号の反転信号(SWEB)が供給される。

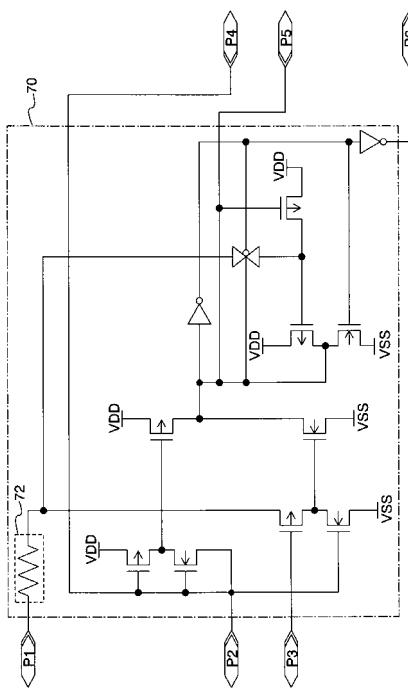

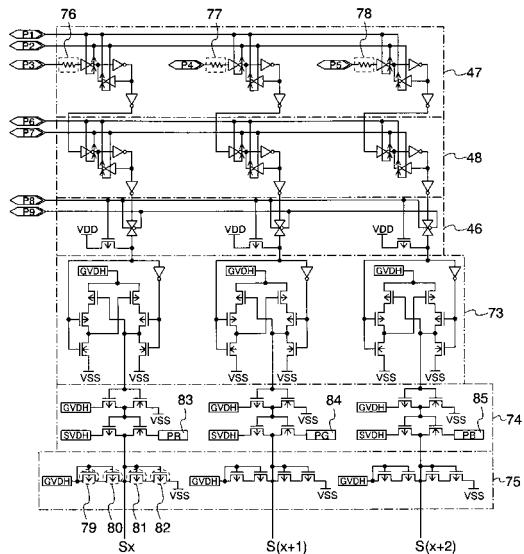

#### 【0076】

パルス出力回路44が含む単位回路70は、複数のトランジスタと論理回路を有する(図6参照)。単位回路70は、クロック信号又はクロックバック信号が入力される入力ノード(P1)に、保護回路として抵抗素子72が設けられている。また第1のラッチ47の入力ノードであって、データ信号が供給される入力ノード(P3、P4、P5)に、保護回路として抵抗素子76~78が設けられている(図7参照)。また図5には示していないが、選択回路46の下段には、レベルシフタ73、バッファ74が設けられ、当該バッファ74の下段に、保護回路75が設けられている。保護回路75は、ソース線1本に対して、4つのトランジスタ79~82を含む。なおバッファ74に供給される電源電位83~85は、ソース線Sxに接続する画素が発光する色に応じて、電位が設定される。

10

#### 【0077】

ソースドライバ43は、パルス出力回路44の入力ノード(P1)に接続する第1の保護回路(図示する構成では抵抗素子72に相当)と、第1のラッチ47の入力ノード(P3、P4、P5)に接続する第2の保護回路(図示する構成では抵抗素子76~78に相当)と、選択回路46の下段に設けられた第3の保護回路(図示する構成ではトランジスタ79~82に相当)とを有する点を特徴とする。上記特徴により、静電気に起因した素子の劣化や破壊を抑制することができる。

20

#### 【0078】

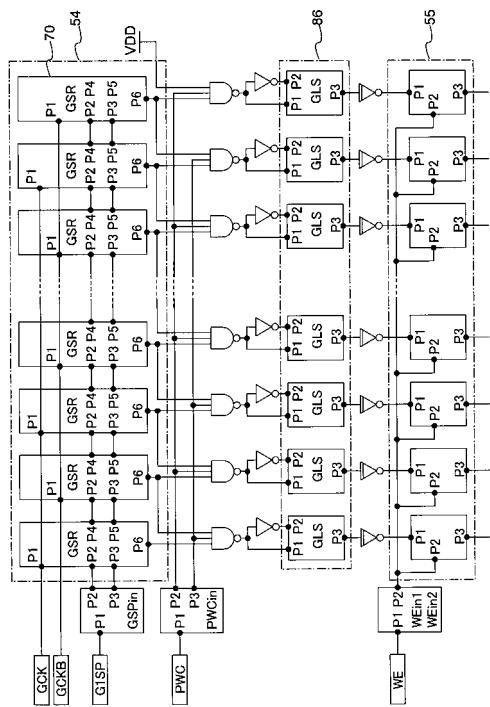

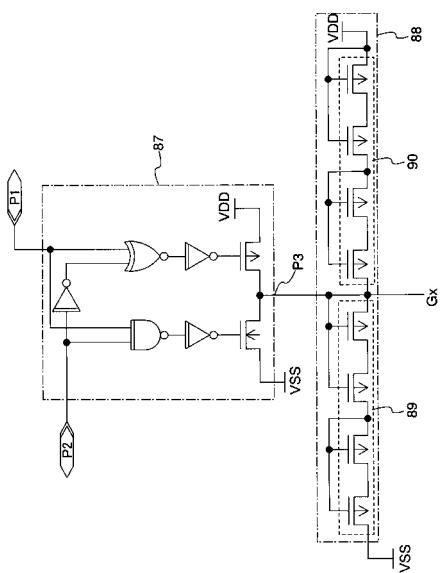

次に、第1のゲートドライバ41の構成について図8、9を参照して説明する。第2のゲートドライバ42の構成は、第1のゲートドライバ41と同様であるため、ここでは、その構成の説明を省略する。第1のゲートドライバ41は、パルス出力回路54、レベルシフタ(GLS)86、選択回路55を有する(図8参照)。パルス出力回路54の構成は、ソースドライバ43が含むパルス出力回路44と同じ構成であり、複数の単位回路(GSR)70が継続接続した構成を有し、その入力ノード(P1)には保護回路が設けられている。

30

#### 【0079】

選択回路55はトライステートバッファ87と、保護回路88を有する(図9参照)。トライステートバッファ87は、第1のゲートドライバ41及び第2のゲートドライバ42の一方がゲート線Gyの充放電を行う際に、他方のドライバの出力がそれを阻害しないようにするものである。従って、選択回路55としては、上記のような機能を有するものであれば、トライステートバッファだけでなく、アナログスイッチやクロックドインバータ等を用いてもよい。保護回路88は、素子群89、90を有する。

#### 【0080】

第1のゲートドライバ41は、パルス出力回路54の入力ノード(P1)に接続する第1の保護回路(図6に示す構成では抵抗素子72に相当)と、選択回路55の下段に設けられた第2の保護回路88を有する点を特徴とする。上記特徴により、静電気に起因した素子の劣化や破壊を抑制することができる。より具体的には、入力ノードに入力されるクロック信号やデータ信号には雑音が含まれている場合があり、この雑音により、瞬間的に高い電圧又は低い電圧が素子に与えられることがある。しかしながら、保護回路を有する本発明は、素子の誤作動、素子の劣化や破壊を抑制することができる。

40

#### 【0081】

なお保護回路は、抵抗素子やトランジスタだけでなく、抵抗素子、容量素子及び整流素子から選択された1種又は複数種から構成される。整流素子とはゲート電極とドレイン電極が接続されたトランジスタ又はダイオードである。

#### 【0082】

次に、保護回路の動作について簡単に説明する。ここでは、第1のゲートドライバ41が

50

含む保護回路 8 8 の動作について説明する。

まず、雑音等の影響により、トライステートバッファ 8 7 の出力ノードから、VDD よりも高い電圧の信号が供給されたとする。そうすると、そのゲート・ソース間電圧の関係から、素子群 8 9 はオフ、素子群 9 0 はオンとなる。そうすると、トライステートバッファ 8 7 にチャージした電荷は、VDD を伝達する電源線に放電して、ゲート線 G<sub>X</sub> の電位は、VDD、又は VDD + ( は 0 以上の数であり、VDD + は VDD よりも高い電位を意味する ) の電位となる。

#### 【 0 0 8 3 】

一方、トライステートバッファ 8 7 の出力ノードから、VSS よりも低い電圧の信号が供給されたとする。そうすると、そのゲート・ソース間電圧の関係から、素子群 8 9 がオン、素子群 9 0 はオフとなる。そうすると、ゲート線 G<sub>X</sub> の電位は、VSS、又は VSS - ( は 0 以上の数であり、VSS - は VSS よりも低い電位を意味する ) の電位となる。

10

このように、雑音等により、トライステートバッファ 8 7 の出力ノードから供給される電圧が、瞬間に、VDD より高くなったり、VSS よりも低くなったりしても、ゲート線 G<sub>X</sub> に与えられる電圧は、VDD よりも高くならず、また VSS よりも低くならない。従って、雑音や静電気等に起因した素子の誤作動、損傷、破壊を抑制することができる。

#### 【 0 0 8 4 】

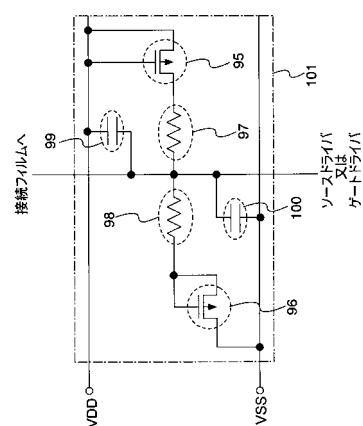

また本発明の表示装置は、FPC (Flexible Print Circuit) 等の接続フィルムと、第 1 のゲートドライバ 4 1、第 2 のゲートドライバ 4 2 又はソースドライバ 4 3 との間に設けられた保護回路 1 0 1 を有する (図 18 参照)。ソースドライバ 4 3 であれば、SCK、SSP、DataR、DataG、DataB、SLAT 及び SWE 等の信号は、接続フィルムを介して外部から供給されるが、保護回路 1 0 1 は、上記に挙げた信号を伝達する配線と、接続フィルムとの間に設けられる。また、第 1 のゲートドライバ 4 1 であれば、GCK、G1SP、PW C 及び WE 等の信号は、接続フィルムを介して外部から供給されるが、保護回路 1 0 1 は、上記に挙げた信号を伝達する配線と、接続フィルムとの間に設けられる。図示する構成では、保護回路 1 0 1 は、ゲート電極とドレイン電極が接続するトランジスタ 9 5、9 6、抵抗素子 9 7、9 8、容量素子 9 9、1 0 0 を含む。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

20

#### 【 0 0 8 5 】

30

##### ( 実施の形態 4 )

本発明の温度補償機能は、周囲の温度に基づき動作するモニター回路 6 4、制御回路 6 5 及び電源制御回路 6 3 により実行される (図 10 参照)。モニター回路 6 4 は、図示する構成では発光素子 6 6 を有する。発光素子 6 6 の一方の電極は一定の電位の保たれた電源に接続し (図示する構成では接地している)、他方の電極は制御回路 6 5 に接続する。制御回路 6 5 は、定電流源 9 1 とアンプ 9 2 を有する。電源制御回路 6 3 は電源回路 6 1 とコントローラ 6 2 とを有する。なお、電源回路 6 1 は、供給する電源電位を変えることができる可変電源であることが好ましい。

#### 【 0 0 8 6 】

40

発光素子 6 6 が環境温度を検出する仕組みについて説明する。発光素子 6 6 の両電極間に定電流源 9 1 から一定の電流が供給される。つまり発光素子 6 6 の電流値は常に一定である。この状態で環境温度が変化すると、発光素子 6 6 自体の抵抗値が変化する。発光素子 6 6 の抵抗値が変化すると、当該発光素子 6 6 の電流値は常に一定であることから、発光素子 6 6 の両電極間の電位差が変化する。この温度変化による発光素子 6 6 の両電極間の電位差の変化を検出することで、環境温度の変化を検出する。より詳しくは、発光素子 6 6 の一定の電位に保たれている側の電極の電位は変わらないので、定電流源 9 1 に接続する側の電極の電位の変化を検出する。

#### 【 0 0 8 7 】

このような発光素子の電位の変化の情報を含む信号は、アンプ 9 2 に供給され、当該アンプ 9 2 で増幅された後、電源制御回路 6 3 に出力される。電源制御回路 6 3 は、アンプ 9

50

2を介して、モニター回路64の出力に基づき、画素領域40に供給する電源の電位を変える。そうすると、温度変化に合わせて、電源電位を補正することができる。つまり、温度変化に起因した電流値の変動を抑制することができる。

#### 【0088】

なお図示する構成では、発光素子66を複数有するが、本発明はこれに制約されない。モニター回路64に設ける発光素子66の個数は制約されない。また、発光素子66を用いる場合であっても、当該発光素子66にトランジスタを直列に接続した構成を適用してもよい。その場合は、必要なときに、発光素子66に直列に接続するトランジスタをオン状態にする。

#### 【0089】

またモニター回路64として、発光素子66を用いているが、本発明はこれに制約されず、公知の温度センサを用いてもよい。公知の温度センサを用いる場合は、画素領域40と同じ基板上に設けてもよいし、ICを用いて外付けにしてもよい。本発明の温度補償機能は、ユーザによる操作を必要としないため、エンドユーザに表示装置が渡った後も、継続して補正することができるため、製品として、長寿命化を図ることができる。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

10

#### 【0090】

##### (実施の形態5)

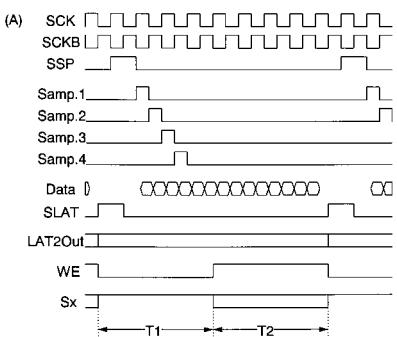

本発明の表示装置の動作について図4、11を参照して説明する。まず、ソースドライバの動作について説明する(図4、11(A)参照)。パルス出力回路44には、クロック信号(以下SCKと表記)、クロック反転信号(以下SCKBと表記)及びスタートパルス(以下SSPと表記)が入力され、これらの信号のタイミングに従って、第1のラッチ47にサンプリングパルスを出力する。データが入力される第1のラッチ47は、サンプリングパルスが入力されるタイミングに従って、1列目から最終列目までビデオ信号を保持する。第2のラッチ48は、ラッチパルスが入力されると、第1のラッチ47に保持されていたビデオ信号を、一斉に第2のラッチ48に転送する。

20

#### 【0091】

ここで、選択信号線52から伝達されるWE信号がLレベルのときを期間T1とし、WE信号がHレベルのときを期間T2として、各期間における選択回路46の動作について説明する。期間T1、T2は水平走査期間の半分の期間に相当し、期間T1を第1のサブゲート選択期間、期間T2を第2のサブゲート選択期間ともよぶ。

30

#### 【0092】

期間T1(第1のサブゲート選択期間)において、選択信号線52から伝達されるWE信号はLレベルであり、TFT49はオン状態、アナログスイッチ50は非導通状態となる。そうすると、複数の信号線S1～Smは、各列に配置されたTFT49を介して、電源53と電気的に接続する。つまり、複数の信号線S1～Smは、電源53と同電位になる。

#### 【0093】

このとき、画素10が含むTFT11はオン状態であり、当該TFT11を介して、電源53の電位がTFT12のゲート電極に伝達される。そうすると、TFT12はオフ状態となり、発光素子13が含む2つの電極は同電位となる。つまり、発光素子13が含む両電極間には電流が流れず非発光となる。このように、ビデオ線に入力されるビデオ信号の状態に関係なく、電源53の電位がTFT12のゲート電極に伝達されて、当該TFT11がオフ状態になり、発光素子13が含む2つの電極の電位が同電位になる動作を消去動作とよぶ。

40

#### 【0094】

期間T2(第2のサブゲート選択期間)において、選択信号線52から伝達されるWE信号はHレベルであり、TFT49はオフ状態、アナログスイッチ50は導通状態となる。そうすると、第2のラッチ48に保持されたビデオ信号は、1行分が同時に複数の信号線S1～Smに伝達される。このとき、画素10が含むTFT11はオン状態であり、当該

50

TFT11を介して、ビデオ信号がTFT12のゲート電極に伝達される。そうすると、入力されたビデオ信号に従って、TFT12はオン状態又はオフ状態となり、発光素子13が含む2つの電極は、互いに異なる電位又は同電位となる。より詳しくは、TFT12がオン状態になると、発光素子13が含む2つの電極は互いに異なる電位となり、発光素子13に電流が流れる。つまり、発光素子13は発光する。なお発光素子13に流れる電流は、TFT12のソース電極とドレイン電極の間に流れる電流と同じである。

#### 【0095】

一方、TFT12がオフ状態になると、発光素子13が含む2つの電極は同電位となり、発光素子13に電流は流れない。つまり、発光素子13は非発光となる。このように、ビデオ信号に従って、TFT12がオン状態又はオフ状態になり、発光素子13が含む2つの電極の電位が互いに異なる電位又は同電位となる動作を書き込み動作とよぶ。10

#### 【0096】

次に、第1のゲートドライバ41、第2のゲートドライバ42の動作について説明する。パルス出力回路54には、G1CK、G1CKB、G1SPが入力され、これらの信号のタイミングに従って、選択回路55に順次パルスを出力する。パルス出力回路56には、G2CK、G2CKB、G2SPが入力され、これらの信号のタイミングに従って、選択回路57に順次パルスを出力する。図11(B)には、i行目、j行目、k行目、p行目(*i*、*j*、*k*、*p*は自然数、1 *i*、*j*、*k*、*p* *n*)の各列の選択回路55、57に供給されるパルスの電位を示す。

#### 【0097】

ここで、ソースドライバ43の動作の説明と同様に、選択信号線52から伝達されるWE信号がLレベルのときを期間T1とし、WE信号がHレベルのときを期間T2として、各期間における第1のゲートドライバ41が含む選択回路55と、第2のゲートドライバ42が含む選択回路57の動作について説明する。なお、図11(B)のタイミングチャートでは、第1のゲートドライバ41から信号が伝達されたゲート線Gy(*y*は自然数、1 *y* *n*)の電位をGy41と表記し、第2のゲートドライバ42から信号が伝達されたゲート線の電位をGy42と表記する。そして、言うまでもなく、Gy41とGy42は、同じ配線を示す。20

#### 【0098】

期間T1(第1のサブゲート選択期間)において、選択信号線52から伝達されるWE信号はLレベルである。そうすると、第1のゲートドライバ41が含む選択回路55には、LレベルのWE信号が入力され、選択回路55は不定状態となる。一方、第2のゲートドライバ42が含む選択回路57には、WE信号が反転したHレベルの信号が入力され、選択回路57は動作状態となる。つまり、選択回路57はHレベルの信号(行選択信号)を*i*行目のゲート線Giに伝達し、ゲート線GiはHレベルの信号と同電位となる。つまり、第2のゲートドライバ42により*i*行目のゲート線Giが選択される。30

#### 【0099】

その結果、画素10が含むTFT11はオン状態となる。そして、ソースドライバ43が含む電源53の電位がTFT12のゲート電極に伝達され、TFT12はオフ状態となり、発光素子13の両電極の電位は同電位となる。つまり、この期間では、発光素子13が非発光となる消去動作が行われる。40

#### 【0100】

期間T2(第2のサブゲート選択期間)において、選択信号線52から伝達されるWE信号はHレベルである。そうすると、第1のゲートドライバ41が含む選択回路55には、HレベルのWE信号が入力され、選択回路55は動作状態となる。つまり、選択回路55はHレベルの信号を*i*行目のゲート線Giに伝達し、ゲート線GiはHレベルの信号と同電位となる。つまり、第1のゲートドライバ41により、*i*行目のゲート線Giが選択される。

#### 【0101】

その結果、画素10が含むTFT11はオン状態となる。そして、ソースドライバ43が50

含む第2のラッチ48からビデオ信号がTFT12のゲート電極に伝達され、TFT12はオン状態又はオフ状態となり、発光素子13が含む2つの電極の電位は、互いに異なる電位又は同電位となる。つまり、この期間では、発光素子13は発光又は非発光となる書き込み動作が行われる。一方、第2のゲートドライバ42が含む選択回路57には、Lレベルの信号が入力され、不定状態となる。

#### 【0102】

このように、ゲート線Gyは、期間T1(第1のサブゲート選択期間)において第2のゲートドライバ42により選択され、期間T2(第2のサブゲート選択期間)において第1のゲートドライバ41により選択される。つまり、ゲート線は、第1のゲートドライバ41と第2のゲートドライバ42により、相補的に制御される。そして、第1のサブゲート選択期間及び第2のサブゲート選択期間において、一方で消去動作を行って、他方で書き込み動作を行う。10

#### 【0103】

なお第1のゲートドライバ41がi行目のゲート線Giを選択する期間では、第2のゲートドライバ42は動作していない状態(選択回路57が不定状態)、又はi行目を除く他の行のゲート線に行選択信号を伝達する。同様に、第2のゲートドライバ42がi行目のゲート線Giに行選択信号を伝達する期間は、第1のゲートドライバ41は不定状態、又はi行目を除く他の行のゲート線に行選択信号を伝達する。

#### 【0104】

また上記のような動作を行う本発明は、発光素子13を強制的にオフにすることができるため、階調数が多くなった場合にも、デューティー比の向上を実現する。さらに、発光素子13を強制的にオフにすることができるにも関わらず、容量素子16の電荷を放電するTFTを設ける必要がないために、高開口率を実現する。高開口率を実現すると、光を発する面積の増加に伴って、発光素子の輝度を下げることができる。つまり、駆動電圧を下げるため、消費電力を削減することができる。20

#### 【0105】

なお、本発明は、ゲート選択期間を2分割する上記の形態に制約されない。ゲート選択期間を3つ以上に分割してもよい。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

#### 【0106】

なお、ゲート選択期間の前半(第1のサブゲート選択期間)には、画素に消去信号が入力され、ゲート選択期間の後半(第2サブゲート選択期間)には、画素に画像(ビデオ)信号が入力されているが、これに限定されない。ゲート選択期間の前半(第1のサブゲート選択期間)には、画素に画像(ビデオ)信号が入力され、ゲート選択期間の後半(第2サブゲート選択期間)には、画素に消去信号が入力されてもよい。30

#### 【0107】

またあるいは、ゲート選択期間の前半(第1のサブゲート選択期間)にも、画素に画像(ビデオ)信号が入力され、ゲート選択期間の後半(第2サブゲート選択期間)にも、画素に画像(ビデオ)信号が入力されてもよい。各々には、異なるサブフレームに相当する信号を入力すればよい。その結果、消去期間を設けずに、点灯期間が連続的に配置されるようにして、サブフレーム期間を設けることが出来る。この場合は、消去期間を設ける必要が無いため、デューティー比を高くすることが出来る。40

#### 【0108】

##### (実施の形態6)

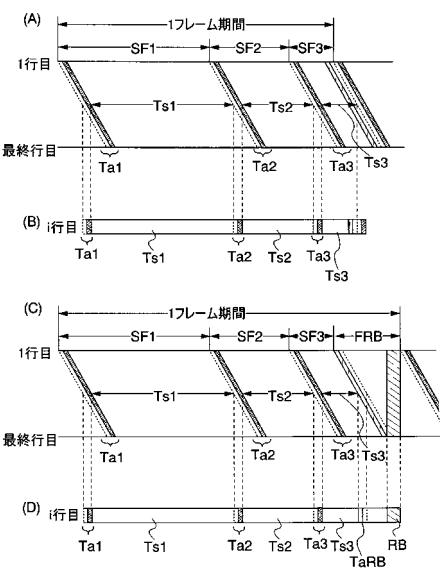

本発明の表示装置の動作について、縦軸が走査線、横軸が時間のタイミングチャート(図12(A)(C))と、i行目のゲート線Gi(1 i m)のタイミングチャート(図12(B)(D))を用いて説明する。時間階調方式は、1フレーム期間は複数のサブフレーム期間SF1、SF2、…、SFn(nは自然数)を有する。

#### 【0109】

複数のサブフレーム期間の各々は、書き込み動作又は消去動作を行う複数の書き込み期間50

$T_{a1}$ 、 $T_{a2}$ 、…、 $T_{an}$ から選択された一つと、複数の点灯期間 $T_{s1}$ 、 $T_{s2}$ 、…、 $T_{sn}$ から選択された一つとを有する。複数の書き込み期間の各々は、複数のゲート選択期間を有する。複数のゲート選択期間の各々は、複数のサブゲート選択期間を有する。ゲート選択期間の各々の分割数は特に制約されないが、好ましくは2つ～8つに分割し、さらに好ましくは2つ～4つに分割するとよい。また点灯期間 $T_{s1} : T_{s2} : \dots : T_{sn}$ は、その長さの比を、例えば $2^{(n-1)} : 2^{(n-2)} : \dots : 2^1 : 2^0$ とする。つまり、点灯期間 $T_{s1}$ 、 $T_{s2}$ 、…、 $T_{sn}$ は、各ビットで長さが異なるように設定する。

#### 【0110】

以下には、まず、交流駆動期間F R B (Frame Reverse Bias)を含まない場合であって、3ビット階調(8階調)を表現する場合のタイミングチャートについて説明する(図12(A)(B)参照)。この場合、1フレーム期間を3つのサブフレーム期間S F 1～S F 3に分割する。サブフレーム期間S F 1～S F 3は、書き込み期間 $T_{a1} \sim T_{a3}$ から選択された1つと、点灯期間 $T_{s1} \sim T_{s3}$ から選択された1つとを有する。書き込み期間は、複数のゲート選択期間を有する。複数のゲート選択期間の各々は、複数のサブゲート選択期間を有するが、ここでは、複数のゲート選択期間の各々は、2つのサブゲート選択期間を有し、第1のサブゲート選択期間において消去動作を行い、第2のサブゲート選択期間において書き込み動作を行う場合について示す。

#### 【0111】

なお、消去動作は、発光素子を非発光にするために行う動作であり、必要なサブフレーム期間においてのみに行う動作である。

#### 【0112】

次に、交流駆動期間F R Bを含む場合のタイミングチャートについて説明する(図12(C)(D)参照)。交流駆動期間F R Bは消去動作のみを行う書き込み期間T a R Bと、発光素子に印加する電位の上下関係(高低差)を逆にして、全ての発光素子に同時に逆方向バイアスを印加する交流駆動期間F R Bを有する。

#### 【0113】

なお、交流駆動期間F R Bは、各フレーム期間に設ける必要はなく、複数のフレーム期間毎に設けてもよい。また、サブフレーム期間S F 1～S F 3と交流駆動期間(逆方向バイアス印加期間ともいう)F R Bを別に設ける必要はなく、あるサブフレーム期間の点灯期間 $T_{s1} \sim T_{s3}$ 中に設けてもよい。

#### 【0114】

また、サブフレーム期間の順序は、上位ビットから下位ビットの順序に出現する上記記載に制約されず、出現する順序はランダムでもよい。さらに、フレーム期間毎に、サブフレーム期間が出現する順序をランダムにしてもよい。

また、複数のサブフレーム期間から選択された1つ又は複数の期間を複数に分割してもよい。その場合、分割された1つ又は複数のサブフレーム期間の各々と、分割されていない1つ又は複数のサブフレーム期間の各々は、複数の書き込み期間 $T_{a1}$ 、 $T_{a2}$ 、…、 $T_{am}$ (mは自然数)から選択された1つと、複数の点灯期間 $T_{s1}$ 、 $T_{s2}$ 、…、 $T_{sm}$ から選択された1つとを有する。

#### 【0115】

そこで、上位ビットのサブフレーム期間が複数に分割され、なお且つ、サブフレーム期間の出現する順序がランダムである場合のタイミングチャートについて説明する(図13参照)。図示するタイミングチャートは、6ビット階調を表現するものであり、サブフレーム期間S F 1を3つに分割し(図中S F 1-1～S F 1-3で示す)、サブフレーム期間S F 2を2つに分割し(図中S F 2-1、S F 2-2で示す)、サブフレーム期間S F 3を2つに分割(図中S F 3-1、S F 3-2で示す)している。そして、初行画素の表示のタイミングと、最終行画素の表示のタイミングと、消去用のゲートドライバの走査タイミングと、書き込み用のゲートドライバの走査タイミングとを示す。なお図示するタイミングチャートの表示duty比は51%である。本実施の形態は、上記の実施の形態と自

10

20

30

40

50

由に組み合わせることができる。

**【 0 1 1 6 】**

(実施の形態 7 )

本発明の表示装置は、発光素子 13 と、容量素子 16 と、TFT 11、12 を含む画素 10 を複数有するものであることは上述した通りであるが、ここでは、隣接する画素間で電源線  $V_x$  を共有する形態について、図 14 を参照して説明する。このように、隣接する画素間で電源線  $V_x$  を共有する場合、隣接する画素の配置は、互いに水平反転した関係にある。隣接する画素同士で電源線  $V_x$  を共有すると、配置する配線の本数を少なくすることができるために、高開口率を実現する。高開口率を実現すると、光を発する面積の増加に伴って、発光素子の輝度を下げることができる。つまり、駆動電圧を下げるため、消費電力を削減することができる。10

**【 0 1 1 7 】**

上記構成の場合、発光素子から単色又は白色の発光を呈する構成とするとよい。そして、光の出射側にフィルター又は色変換層を設けた構成とすれば、カラー表示を行うことができる。このように、電源線を共有している場合は、電界発光層の塗り分けを行うよりも、単色又は白色の発光を呈する構成とすると、劣化に対する電源電位の補正を行いやすい。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

**【 0 1 1 8 】**

(実施の形態 8 )

本発明の表示装置には、コントラストの向上を図るために、偏光板、波長板、円偏光板を設けてもよい。また、本発明の表示装置が含む発光素子は、一対の電極の間に電界発光層を含む構成を有する。カラー表示を行う場合は、発光波長帯の異なる電界発光層を画素毎に形成するとよく、典型的には、赤 (R)、緑 (G)、青 (B) の各色に対応した電界発光層を形成する。この場合、発光素子の光の出射側に、その発光波長帯の光を透過するフィルター (着色層) を設けた構成とすると、色純度の向上や、画素部の鏡面化 (映り込み) の防止を図ることができる。また、フィルターを設けると、従来必要であるとされていた円偏光板等を省略することが可能となり、電界発光層から出射する光の損失を無くすことができる。さらに、斜方から画素領域を見た場合に起こる色調の変化を低減することができる。また、電界発光層は単色又は白色の発光を呈する構成とすることができます。白色発光材料を用いる場合には、発光素子の光の出射側に特定の波長の光を透過するフィルターを設けた構成とすれば、カラー表示を行うことができる。20

**【 0 1 1 9 】**

電界発光層には、一重項励起からの発光を呈する材料 (以下一重項励起材料と表記) や、三重項励起からの発光を呈する材料 (以下三重項励起材料と表記) を用いる。例えば、赤色に発光する発光素子、緑色に発光する発光素子及び青色に発光する発光素子のうち、輝度半減時間が比較的短い赤色のものを三重項励起発光材料で形成し、他のものを一重項励起発光材料で形成する。三重項励起発光材料は発光効率が良いので、同じ輝度を得るのに消費電力が少なくて済むという利点がある。30

**【 0 1 2 0 】**

また、赤色のものと緑色のものとを三重項励起発光材料で形成し、青色のものを一重項励起発光材料で形成しても良い。人間の視感度が高い緑色の発光素子も三重項励起発光材料で形成することで、さらなる低消費電力化を図ることができる。なお三重項励起発光材料の一例としては、金属錯体をドーパントとして用いたものがあり、第三遷移系列元素である白金を中心金属とする金属錯体、イリジウムを中心金属とする金属錯体などがある。40

**【 0 1 2 1 】**

発光素子は、下から陽極、電界発光層、陰極を順に積層する順積み構造や、下から陰極、電界発光層、陽極を順に積層する逆積み構造のどちらを用いてもよい。発光素子が含む電極には、透光性を有するITO (インジウム錫酸化物) や、ITOに珪素が添加されたITSO、IZO (インジウム亜鉛酸化物) 、GZO (ガリウム亜鉛酸化物) を用いるとよい。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。50

**【0122】**

(実施の形態9)

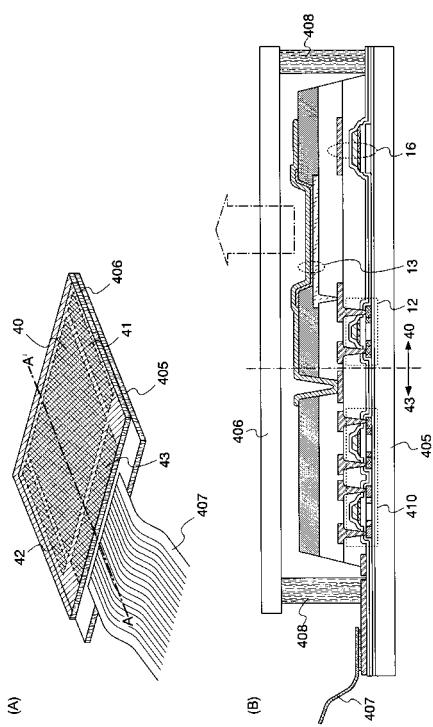

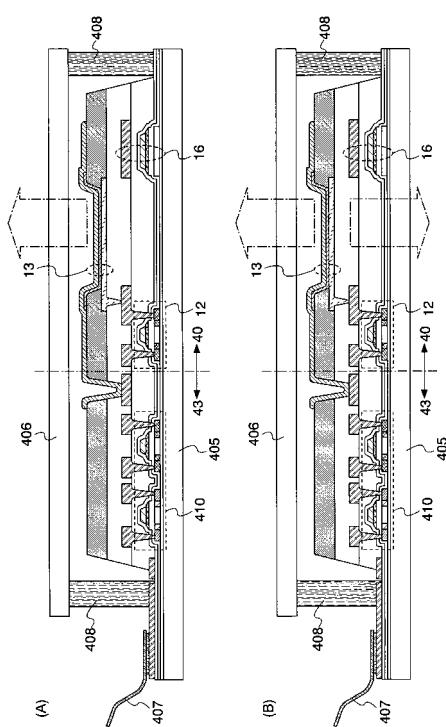

本発明の表示装置の一形態である、画素領域40と第1のゲートドライバ41、第2のゲートドライバ42及びソースドライバ43を搭載したパネルについて説明する。基板405上には、発光素子13を含む画素を複数有する画素領域40、第1のゲートドライバ41、第2のゲートドライバ42、ソースドライバ43及び接続フィルム407が設けられる(図15(A)参照)。接続フィルム407は外部回路(ICチップ)と接続する。

**【0123】**

図15(B)はパネルのA-A'における断面図を示し、画素領域40に設けられたTFT12と発光素子13、ソースドライバ43に設けられたCMOS回路410を示す。

10

**【0124】**

画素領域40と第1のゲートドライバ41、第2のゲートドライバ42及びソースドライバ43の周囲にはシール材408が設けられ、発光素子13は、該シール材408と対向基板406により封止される。この封止処理は、発光素子13を水分から保護するための処理であり、ここではカバー材(ガラス、セラミックス、プラスチック、金属等)により封止する方法を用いるが、熱硬化性樹脂や紫外光硬化性樹脂を用いて封止する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法を用いてもよい。基板405上に形成される素子は、非晶質半導体に比べて移動度等の特性が良好な結晶質半導体(ポリシリコン)により形成することが好適であり、そうすると、同一表面上におけるモノリシック化が実現される。上記構成を有するパネルは、接続する外部ICの個数が減少するため、小型・軽量・薄型が実現される。

20

**【0125】**

なお上記構成では、発光素子13の画素電極は透光性を有し、発光素子13の対向電極は遮光性を有する。従って、発光素子13は下面出射を行う。

**【0126】**

また上記とは異なる構成として、発光素子13の画素電極は遮光性を有し、発光素子13の対向電極は透光性を有する場合がある(図16(A)参照)。この場合、発光素子13は上面出射を行う。

**【0127】**

また上記とは異なる構成として、発光素子13の画素電極と、発光素子13の対向電極の両者が透光性を有する場合がある(図16(B)参照)。この場合、発光素子13は両面出射を行う。

30

**【0128】**

本発明の表示装置には、下面出射、上面出射、両面出射のいずれの構成を採用してもよい。但し、下面出射と両面出射を行う場合は、TFT12が含む不純物領域に接続する導電層(ソース配線又はドレイン配線に相当)は、アルミニウム(A1)と、モリブデン(Mo)等の反射率の低い材料とを組み合わせたもので形成するとよい。具体的には、モリブデン(Mo)、アルミニウム-シリコン(A1-Si)、シリコン(Si)が添加されたアルミニウム(A1)及びモリブデン(Mo)の積層構造、窒化モリブデン(MoN、モリブデン(Mo)と窒素(N)の組成比は制約されない)、アルミニウム-シリコン(A1-Si)、シリコン(Si)が添加されたアルミニウム(A1)及び窒化モリブデン(MoN、モリブデン(Mo)と窒素(N)の組成比は制約されない)等の積層構造を採用するとよい。そうすれば、発光素子から発せられた光がソース配線又はドレイン配線に反射することを防止することができ、光を外部に取り出すことができる。

40

**【0129】**

なお、画素領域40は絶縁表面上に形成された非晶質半導体(アモルファスシリコン)をチャネル部としたTFTにより構成し、第1のゲートドライバ41、第2のゲートドライバ42及びソースドライバ43はICチップにより構成してもよい。ICチップは、COG方式により基板405上に貼り合わせたり、基板405に接続する接続フィルム407に貼り合わせたりしてもよい。非晶質半導体は、CVD法を用いることで、大面積の基板

50

に簡単に形成することができ、かつ結晶化の工程が不要であることから、安価なパネルの提供を可能とする。また、この際、インクジェット法に代表される液滴吐出法により導電層を形成すると、より安価なパネルの提供を可能とする。本実施の形態は、上記の実施の形態と自由に組み合わせることができる。

#### 【0130】

##### (実施の形態10)

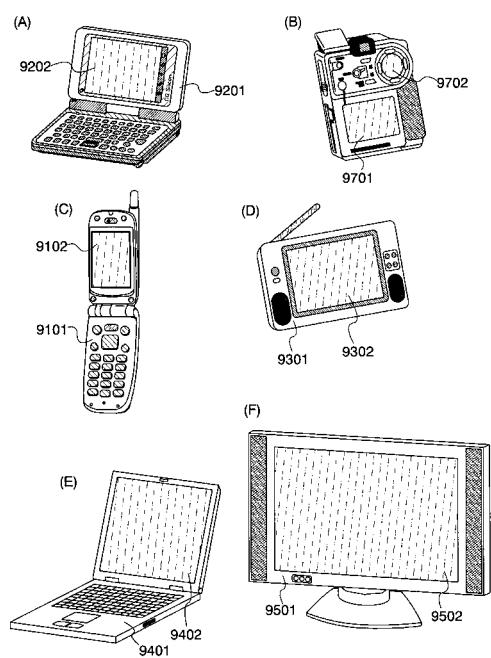

発光素子を含む画素領域を備えた表示装置を用いた電子機器として、テレビジョン装置(テレビ、テレビジョン受信機)、デジタルカメラ、デジタルビデオカメラ、携帯電話装置(携帯電話機)、PDA等の携帯情報端末、携帯型ゲーム機、モニター、コンピュータ、カーオーディオ等の音響再生装置、家庭用ゲーム機等の記録媒体を備えた画像再生装置等が挙げられる。その具体例について、図17を参照して説明する。10

#### 【0131】

図17(A)に示す本発明の表示装置を用いた携帯情報端末は、本体9201、表示部9202等を含み、本発明により消費電力を削減することができる。図17(B)に示す本発明の表示装置を用いたデジタルビデオカメラは、表示部9701、9702等を含み、本発明により消費電力を削減することができる。図17(C)に示す本発明の表示装置を用いた携帯端末は、本体9101、表示部9102等を含み、本発明により消費電力を削減することができる。図17(D)に示す本発明の表示装置を用いた携帯型のテレビジョン装置は、本体9301、表示部9302等を含み、本発明により消費電力を削減することができる。図17(E)に示す本発明の表示装置を用いた携帯型のコンピュータは、本体9401、表示部9402等を含み、本発明により消費電力を削減することができる。図17(F)に示す本発明の表示装置を用いたテレビジョン装置は、本体9501、表示部9502等を含み、本発明により消費電力を削減することができる。上記に挙げた電子機器において、バッテリーを用いているものは、消費電力を削減した分、電子機器の使用時間を長持ちさせることができ、バッテリーを充電する手間を省くことができる。20

#### 【実施例1】

##### 【0132】

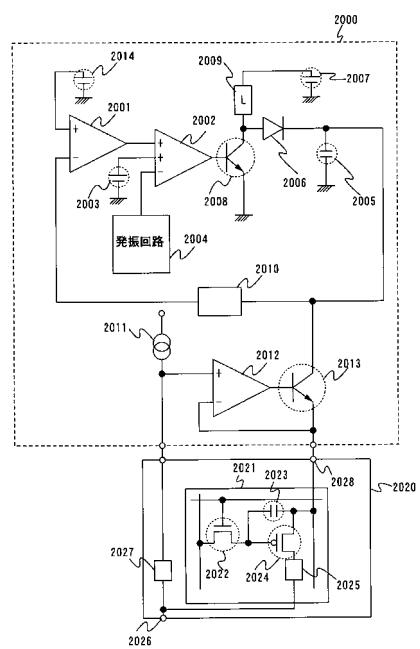

温度特性、輝度特性の補償回路の具体例を図20に示す。表示パネル2020と電源2000によって構成されている。電源2000は、実施の形態1の図4で示した表示装置の制御回路65に相当する。表示パネルは画素部2021、モニター素子2027、第1の電源端子2026によって構成されており、さらに画素部2021はスイッチングTFT2022、保持容量2023、駆動TFT2024、発光素子2025によって構成されている。駆動TFT2024がオンして発光素子2025が第2の電源端子2028に接続されると発光素子2025が発光する。30

#### 【0133】

発光素子2025は温度に対して電流・電圧特性が変化するため、一定の電圧を印加した場合、高温で高輝度となり、低温で低輝度となる。これを補正するため、定電流源2011よりモニター素子2027に流し、そこで発生する電圧をアンプ2012、トランジスタ2013を介して、第2の電源端子2028に印加している。モニター素子2027と発光素子2025が同一材料で形成されれば、温度特性はキャンセルされ、温度に対して輝度を一定に保つことが可能となる。40

#### 【0134】

電源2000はスイッチングレギュレータであり、第1のコンパレータ2001、第2のコンパレータ2002、発振回路2004、平滑容量2005、ダイオード2006、スイッチトランジスタ2008、インダクタ2009、基準電源2003、2007、2014、アッテネータ2010から構成される。基準電源2007は電流容量の大きな電源、たとえばバッテリーなどを用いる。

#### 【0135】

スイッチングレギュレータの構成は上記には限定されず他の構成を用いても良い。また、図20ではスイッチトランジスタをNPN型バイポーラトランジスタとしているがこれも50

それには限定されない。

**【0136】**

発振回路2004の出力信号と基準電源2003、第1のコンパレータ2001の出力信号を第2のコンパレータ2002で比較し、第2のコンパレータ2002の出力信号でスイッチトランジスタ2008をオンオフさせる。スイッチトランジスタ2008がオンするとインダクタ2009に電流がながれ、磁界エネルギーがインダクタ2009に保持される。スイッチトランジスタ2008がオフすると、磁界エネルギーは電圧に変わり、ダイオード2006を介して平滑容量2005を充電する。スイッチトランジスタ2008のオンオフデューティーによって、平滑容量に発生する直流電圧は変化する。

**【0137】**

平滑容量2005の直流電圧はアッテネータ2010でアッテネートされ、第1のコンパレータ2001に入力される。第1のコンパレータ2001は基準電源2014とアッテネータ2010の電圧を比較し、その出力を第2のコンパレータ2002に入力する。このようにして帰還がかかり、必要な電圧を平滑容量2005に発生させることができる。ここでは定電流源2011、アンプ2012、モニター素子2027を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続しても良い。

**【実施例2】**

**【0138】**

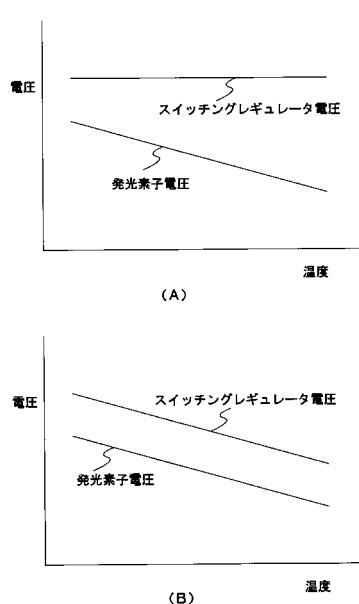

図20に示した実施例では平滑容量2005の電圧が温度に依存せず一定の値をとるが、発光素子は温度特性をもっている。一般に発光素子の電圧は低温で大きく、高温で小さくなる。図21(A)にその様子を示す。高温においては発光素子電圧と平滑容量電圧(図21ではスイッチングレギュレータ電圧と表記)の差が大きくなりこの分は無駄な電力を消費することになる。図21(B)に示すように高温でスイッチングレギュレータ電圧を発光素子電圧に連動して低下すれば無駄な電力を削減できる。

**【0139】**

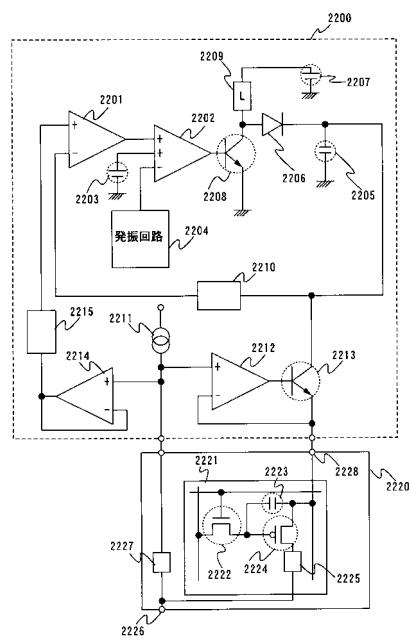

図22はこのような問題を解決するために考えられた実施例である。モニター素子の電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧を発光素子電圧に連動させている。

**【0140】**

図22は温度特性、輝度特性の補償回路の具体例である。表示パネル2220と電源2200によって構成されている。電源2200は、実施の形態1の図4で示した表示装置の制御回路65に相当する。表示パネルは画素部2221、モニター素子2227、第1の電源端子2226によって構成されており、さらに画素部2221はスイッチングTFT2222、保持容量2223、駆動TFT2224、発光素子2225によって構成されている。駆動TFT2224がオンして発光素子2225が第2の電源端子2228に接続されると発光素子2225が発光する。

**【0141】**

発光素子2225は温度に対して電流・電圧特性が変化するため、一定の電圧を印加した場合、高温で高輝度となり、低温で低輝度となる。これを補正するため、定電流を定電流源2211よりモニター素子2227に流し、そこで発生する電圧をアンプ2212、トランジスタ2213を介して、第2の電源端子2228に印加している。モニター素子2227と発光素子2225が同一材料で形成されていれば、温度特性はキャンセルされ、温度に対して輝度を一定に保つことが可能となる。

**【0142】**

電源2200はスイッチングレギュレータであり、第1のコンパレータ2201、第2のコンパレータ2202、発振回路2204、平滑容量2205、ダイオード2206、スイッチトランジスタ2208、インダクタ2209、基準電源2203、2207、アッテネータ2210から構成される。基準電源2207は電流容量の大きな電源、たとえばバッテリーなどを用いる。

**【0143】**

10

20

30

40

50

スイッチングレギュレータの構成は上記には限定されず他の構成を用いても良い。また、図22ではスイッチトランジスタをNPN型バイポーラトランジスタとしているがこれもそれには限定されない。

#### 【0144】

発振回路2204の出力信号と基準電源2203、第1のコンパレータ2201の出力信号を第2のコンパレータ2202で比較し、第2のコンパレータ2202の出力信号でスイッチトランジスタ2208をオンオフさせる。スイッチトランジスタ2208がオンするとインダクタ2209に電流がながれ、磁界エネルギーがインダクタ2209に保持される。スイッチトランジスタ2208がオフすると、磁界エネルギーは電圧に変わり、ダイオード2206を介して平滑容量2205を充電する。スイッチトランジスタ2208のオンオフデューティーによって、平滑容量に発生する直流電圧は変化する。10

#### 【0145】

モニター素子2227の電圧はアンプ2214、アッテネータ2215を介して第1のコンパレータ2201に入力される。平滑容量2205の直流電圧はアッテネータ2210でアッテネートされ、第1のコンパレータ2201に入力される。第1のコンパレータ2201はアッテネータ2215とアッテネータ2210の電圧を比較し、その出力を第2のコンパレータ2202に入力する。このようにして帰還がかかり、必要な電圧を平滑容量2205に発生させることができる。

#### 【0146】

ここでは定電流源2211、アンプ2212、2214、モニター素子2227を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続しても良い。20

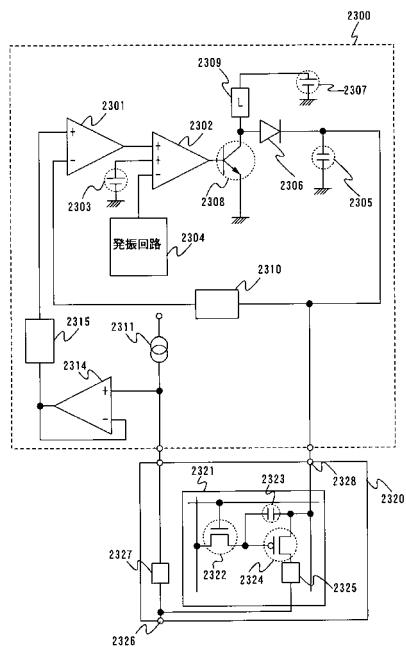

#### 【実施例3】

#### 【0147】

図23はスイッチングレギュレータの出力を直接表示パネルの第2の電源端子に接続した実施例である。モニター素子の電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧を発光素子電圧に連動させている。

#### 【0148】

図23は温度特性、輝度特性の補償回路の具体例である。表示パネル2320と電源2300によって構成されている。電源2300は、実施の形態1の図4で示した表示装置の制御回路65に相当する。表示パネルは画素部2321、モニター素子2327、第1の電源端子2326によって構成されており、さらに画素部2321はスイッチングTFT2322、保持容量2323、駆動TFT2324、発光素子2325によって構成されている。駆動TFT2324がオンして発光素子2325が第2の電源端子2328に接続されると発光素子2325が発光する。30

#### 【0149】

発光素子2325は温度に対して電流・電圧特性が変化するため、一定の電圧を印加した場合、高温で高輝度となり、低温で低輝度となる。これを補正するため、定電流を定電流源2311よりモニター素子2327に流し、そこで発生するスイッチングレギュレータ電圧を介して、第2の電源端子2328に印加している。モニター素子2327と発光素子2325が同一材料で形成されていれば、温度特性はキャンセルされ、温度に対して輝度を一定に保つことが可能となる。図22の実施例に比べて、安定度は落ちるがアンプとトランジスタを削減できるという長所がある。40

#### 【0150】

電源2300はスイッチングレギュレータであり、第1のコンパレータ2301、第2のコンパレータ2302、発振回路2304、平滑容量2305、ダイオード2306、スイッチトランジスタ2308、インダクタ2309、基準電源2303、2307、アッテネータ2310から構成される。基準電源2307は電流容量の大きな電源、たとえばバッテリーなどを用いる。発振回路2304の出力信号と基準電源2303、第1のコンパレータ2301の出力信号を第2のコンパレータ2302で比較し、第2のコンパレータ2302の出力信号でスイッチトランジスタ2308をオンオフさせる。スイッチトランジスタ2308のオンオフによって、平滑容量2305に発生する直流電圧は変化する。50

ンジスタ 2308 がオンするとインダクタ 2309 に電流がながれ、磁界エネルギーがインダクタ 2309 に保持される。スイッチトランジスタ 2308 がオフすると、磁界エネルギーは電圧に変わり、ダイオード 2306 を介して平滑容量 2305 を充電する。スイッチトランジスタ 2308 のオンオフデューティーによって、平滑容量に発生する直流電圧は変化する。

#### 【0151】

モニター素子 2327 の電圧はアンプ 2314、アッテネータ 2315 を介して第 1 のコンパレータ 2301 に入力される。平滑容量 2305 の直流電圧はアッテネータ 2310 でアッテネートされ、第 1 のコンパレータ 2301 に入力される。第 1 のコンパレータ 2301 はアッテネータ 2315 とアッテネータ 2310 の電圧を比較し、その出力を第 2 のコンパレータ 2302 に入力する。このようにして帰還がかかり、必要な電圧を平滑容量 2305 に発生させることができる。ここでは定電流源 2311、アンプ 2314、モニター素子 2327 を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続しても良い。

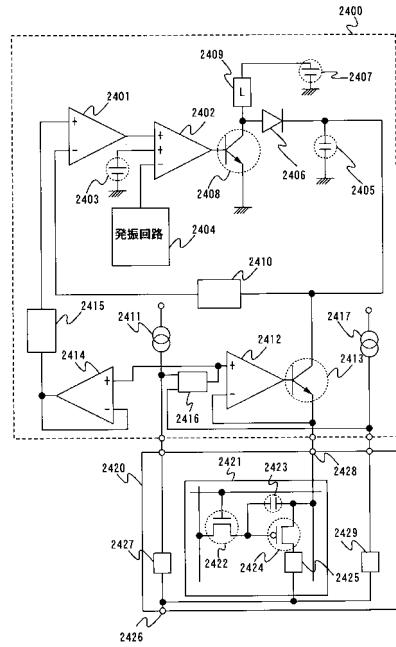

#### 【実施例 4】

#### 【0152】

図 24 はモニター素子を複数設けた実施例である。複数のモニター素子の電圧をスイッチングレギュレータにも入力し、スイッチングレギュレータ電圧を発光素子電圧に連動させている。

#### 【0153】

図 24 は温度特性、輝度特性の補償回路の具体例である。表示パネル 2420 と電源 2400 によって構成されている。電源 2400 は、実施の形態 1 の図 4 で示した表示装置の制御回路 65 に相当する。表示パネルは画素部 2421、モニター素子 2427、モニター素子 2429、第 1 の電源端子 2426 によって構成されており、さらに画素部 2421 はスイッチング TFT 2422、保持容量 2423、駆動 TFT 2424、発光素子 2425 によって構成されている。駆動 TFT 2424 がオンして発光素子 2425 が第 2 の電源端子 2428 に接続されると発光素子 2425 が発光する。

#### 【0154】

発光素子 2425 は温度に対して電流・電圧特性が変化するため、一定の電圧を印加した場合、高温で高輝度となり、低温で低輝度となる。これを補正するため、定電流を定電流源 2411、定電流源 2417 よりモニター素子 2427、モニター素子 2429 に流し、そこで発生する電圧をアンプ 2412、トランジスタ 2413 を介して、第 2 の電源端子 2428 に印加している。モニター素子 2427、モニター素子 2429 と発光素子 2425 が同一材料で形成されれば、温度特性はキャンセルされ、温度に対して輝度を一定に保つことが可能となる。

ここでモニター素子を 2 個、画素部の両側に設け、加算回路 2416 で平均化したのちアンプ 2412、2414 に接続すれば、より正確なモニターが可能になる。さらに、本発明ではモニター素子の数を更に増やすことも可能である。モニター素子の数を増やせばモニター素子と発光素子の差を少なくできる。

#### 【0155】

電源 2400 はスイッチングレギュレータであり、第 1 のコンパレータ 2401、第 2 のコンパレータ 2402、発振回路 2404、平滑容量 2405、ダイオード 2406、スイッチトランジスタ 2408、インダクタ 2409、基準電源 2403、2407、アッテネータ 2410 から構成される。基準電源 2407 は電流容量の大きな電源、たとえばバッテリーなどを用いる。発振回路 2404 の出力信号と基準電源 2403、第 1 のコンパレータ 2401 の出力信号を第 2 のコンパレータ 2402 で比較し、第 2 のコンパレータ 2402 の出力信号でスイッチトランジスタ 2408 をオンオフさせる。スイッチトランジスタ 2408 がオンするとインダクタ 2409 に電流がながれ、磁界エネルギーがインダクタ 2409 に保持される。スイッチトランジスタ 2408 がオフすると、磁界エネルギーは電圧に変わり、ダイオード 2406 を介して平滑容量 2405 を充電する。スイ

10

20

30

40

50

ツチトランジスタ 2408 のオンオフデューティーによって、平滑容量に発生する直流電圧は変化する。

**【0156】**

モニター素子 2427、モニター素子 2429 の電圧は加算回路 2416、アンプ 2414、アッテネータ 2415 を介して第 1 のコンパレータ 2401 に入力される。平滑容量 2405 の直流電圧はアッテネータ 2410 でアッテネートされ、第 1 のコンパレータ 2401 に入力される。第 1 のコンパレータ 2401 はアッテネータ 2415 とアッテネータ 2410 の電圧を比較し、その出力を第 2 のコンパレータ 2402 に入力する。

**【0157】**

このようにして帰還がかかり、必要な電圧を平滑容量 2405 に発生させることができる。ここでは定電流源 2411、定電流源 2417、アンプ 2412、モニター素子 2427、モニター素子 2429 を直接接続しているが間に抵抗やスイッチなど他の素子を介して接続しても良い。

**【実施例 5】**

**【0158】**

実施例 1 ~ 4 において、表示パネルの第 1 の電源端子、第 2 の電源端子は固定であるが、これらの端子に加わる電圧を切換スイッチなどを挟むことにより定期的に入れ替え、発光素子やモニター素子を交流駆動しても良い。

**【0159】**

また、実施例 1 ~ 4 では温度補償について述べたが、モニター素子と発光素子が同様に劣化することによって、発光素子の劣化に対しても補償をおこなうことができる。

**【実施例 6】**

**【0160】**

本発明は図 4 に示すような線順次駆動のソースドライバ 43 に限られず、点順次駆動のソースドライバを適用することも可能である。そこで、本実施例では本発明の表示装置に適用することができる点順次駆動のソースドライバの一例を図 25 に示す。なお、図 4 のソースドライバ 43 の構成と同じ所は共通の符号を用いている。

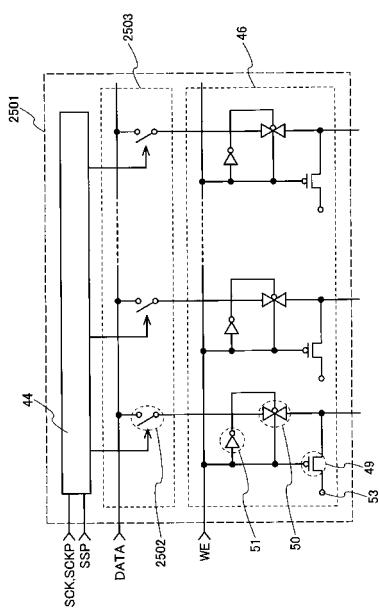

**【0161】**

図 25 のソースドライバ 2501 は、パルス出力回路 44 と、スイッチ群 2503 と、選択回路 46 とを有する。スイッチ群には画素の各列に対応するスイッチ 2502 を有する。また、選択回路 46 にも画素の各列に対応するインバータ 51 と、アナログスイッチ 50 と、TFT 49 とを有する。TFT 49 の一方の端子は電源 53 に接続されている。なお、パルス出力回路 44 としては、例えばシフトレジスタを用いることができる。

**【0162】**

このソースドライバ 2501 の動作方法について簡単に説明する。

**【0163】**

ソースドライバ 2501 が書き込み動作時には WE 信号を H レベルにし、アナログスイッチ 50 をオンにする。このとき消去信号を伝える TFT 49 はオフとなる。そして、DATA 信号を書き込みたい列のスイッチ 2502 をパルス出力回路 44 により順次選択し DATA 信号を画素に書き込む。

**【0164】**

ソースドライバ 2501 が消去動作を行う際には WE 信号を L レベルにし、アナログスイッチ 50 をオフにし、消去用の TFT 49 をオンにする。すると消去用の TFT 49 の端子の一方は電源 53 に接続されており、電源 53 の電位を信号線の電位とすることができるため、画素を駆動する TFT のゲート電位を設定することができる。つまり、画素を駆動する TFT のゲート電極とソース電極の間の電位差を無くすようにすることができる。ゲート・ソース間電圧を保持している保持容量に蓄積されている電荷を放電することができる。この画素を駆動する TFT とは図 4 の TFT 12 に、信号線が図 4 の信号線 S1 ~ Sm に、保持容量が容量素子 16 に相当する。そして、TFT 12 のソース電位は電源線 Vx の電位である。つまり電源 53 の電位と電源線 Vx の電位を等しくしておくと良い。こ

10

20

30

40

50

うして、ソースドライバにより書き込まれた信号を消去することができる。

**【実施例 7】**

**【0165】**

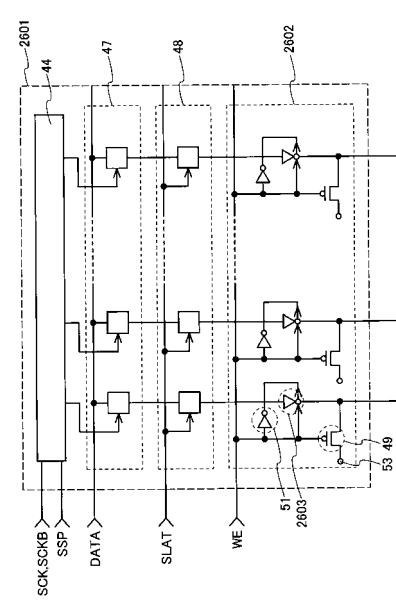

本実施例では図4のソースドライバ43が有する選択回路46の他の構成を図26に示す。本実施例は図4に示したソースドライバ43の選択回路46に用いられているアナログスイッチ50の代わりにクロックドインバータ2603を適用した構成である。なお、図4のソースドライバ43の構成と同じ所は共通の符号を用いている。

**【0166】**

本実施例に示すソースドライバ2601はパルス出力回路44と、第1のラッチ47、第2のラッチ48、選択回路2602とを有する。選択回路2602はインバータ51、クロックドインバータ2603及びTFT49を有する。TFT49の一方の端子は電源53に接続されている。

10

**【0167】**

本実施例に示す選択回路2602の動作方法について簡単に説明する。

**【0168】**

ソースドライバ2601が書き込み動作時にはWE信号をHレベルにし、クロックドインバータ2603に入力される信号を出力することができる。このとき消去信号を伝えるTFT49はオフとなる。こうして第2のラッチ48からの信号を画素に書き込むことが出来る。

20

**【0169】**

ソースドライバが消去動作を行う際にはWE信号をLレベルにし、クロックドインバータ2603に入力される信号を出力しないようとする。そしてTFT49をオンにする。こうして、信号線S1～Smを電源53の電位にすることができ、画素に書き込まれた信号を消去することができる。

**【0170】**

なお、本実施例で示した選択回路2602は、実施例6の図25で示したソースドライバ2501に適用することも出来る。

**【実施例 8】**

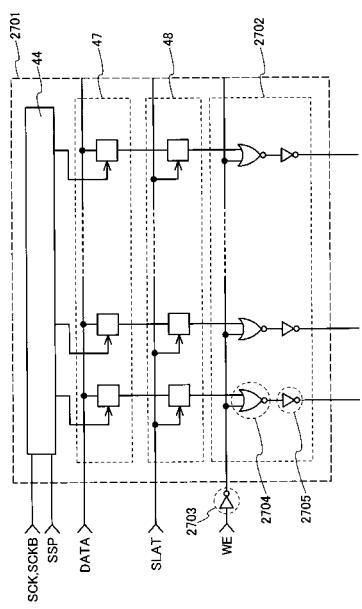

**【0171】**

また、信号がデジタル信号の場合には回路を論理ゲートで表すことができる、そこで本実施例では図4に示すソースドライバ43が有する選択回路46に論理ゲートの回路で表したものを利用した場合について図27に示す。なお、図4のソースドライバ43の構成と同じ所は共通の符号を用いている。

30

**【0172】**

ソースドライバ2701は、パルス出力回路44と、第1のラッチ47、第2のラッチ48、選択回路2702とを有する。選択回路2702はNORゲート2704、インバータ2705を有する。なお、選択回路2702の各列のNORゲート2704の一方の端子に入力される信号はWE信号がインバータ2703により反転された信号が入力される。ソースドライバが書き込み動作の時はWE信号をHレベルにする。すると、インバータ2703により反転され、各列のNORゲート2704の一方の入力端子にはLのレベルが入力される。他方の端子には第2のラッチ48の各列からの信号が入力される。そして、第2のラッチ48からの信号がHレベルの時にNORゲートの出力がLレベルになり、さらにインバータ2705により反転され、ソース信号線にはHのレベルが出力される。そして、ゲート線により選択されている画素のTFT12のゲート電位がHのレベルになりTFT12はオンする。第2のラッチ48からの信号がLレベルの時には、NORゲート2704の出力がHのレベルになり、さらにインバータ2705により反転されLのレベルがソース信号線に出力される。そして、ゲート線により選択されている画素のTFT12のゲート電位がLのレベルになりTFT12はオフする。そして、これらの電位を容量素子16に蓄積する。こうして、画素に信号を書き込むことができる。

40

**【0173】**

50

消去動作の時には、W E 信号をL レベルにする。すると、インバータ2703により反転され、各列のN O R ゲート2704の一方の入力端子にはH レベルが入力される。すると、第2のラッチ48からの信号(つまり、N O R ゲートの他方の入力端子の入力信号)とは無関係にN O R ゲートの出力はL レベルとなり、さらにインバータ2705により反転され、ソース信号線にはH レベルが出力される。そして、ゲート線により選択されている画素のT F T 12 のゲート電位はH レベルとなり、容量素子16 を放電し、T F T 12 はオフする。こうして画素に書き込まれた信号を消去することができる。

#### 【0174】

なお、本実施例で示した選択回路2702は、実施例6の図25で示したソースドライバ2501に適用することも出来る、

10

#### 【実施例9】

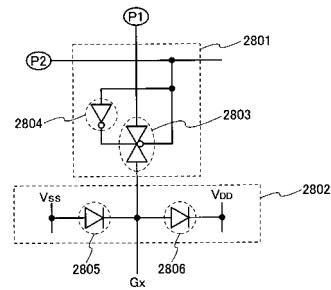

#### 【0175】

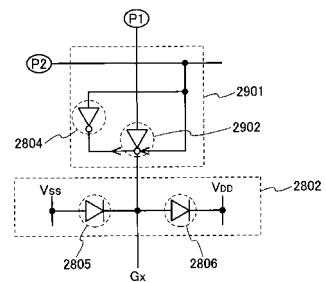

本実施例では、図4に示した第1のゲートドライバ41が備える選択回路55の有するトライステートバッファ87と保護回路88を他の構成に置き換えた例を図28に示す。図9に示すトライステートバッファ87は、第1のゲートドライバ41及び第2のゲートドライバ42の一方がゲート線Gy の充放電を行う際に、他方のドライバの出力がそれを阻害しないようにするものである。従って、上記のような機能を有するものであれば、トライステートバッファだけでなく、図28に示すようなアナログスイッチ2803を用いたイネーブル回路2801を用いてもよい。また、保護回路2802は整流素子2805及び整流素子2806を有する。

20

#### 【0176】

イネーブル回路2801はアナログスイッチ2803及びインバータ2804を有する。P2信号によってアナログスイッチ2803はオンオフを切り替え、P1の信号をゲート線に送る。つまり、第1のゲートドライバ41及び第2のゲートドライバ42の一方がゲート線Gy の充放電を行う際に、他方のドライバの出力がそれを阻害しないようにするには、第1のゲートドライバ41と第2のゲートドライバ42のイネーブル回路2801のP2信号は互いに反転した信号とする。

#### 【0177】

第1のゲートドライバ41は、パルス出力回路54の入力ノードに接続する第1の保護回路(図示する構成では抵抗素子72に相当)と、選択回路46の下段に設けられた第2の保護回路2802を有する点を特徴とする。上記特徴により、静電気に起因した素子の劣化や破壊を抑制することができる。より具体的には、入力ノードに入力されるクロック信号やデータ信号には雑音が含まれている場合があり、この雑音により、瞬間的に高い電圧又は低い電圧が素子に与えられることがある。しかしながら、保護回路を有する本発明は、素子の誤作動、素子の劣化や破壊を抑制することができる。

30

#### 【0178】

なお保護回路は、抵抗素子やトランジスタだけでなく、抵抗素子、容量素子及び整流素子から選択された1種又は複数種から構成される。整流素子とはゲート電極とドレイン電極が接続されたトランジスタ又はダイオードである。本実施例では保護回路2802に整流素子2805及び2806を適用しているが抵抗素子、抵抗素子、容量素子及び整流素子から選択された1種又は複数種から構成してもよい。なお、整流素子としてはダイオード接続したトランジスタの他にも、P N 接合やP I N 接合のダイオードやショットキー型のダイオードなどを用いても良い。

40

#### 【0179】

次に、保護回路の動作について簡単に説明する。ここでは、第1のゲートドライバ41が含む保護回路2802の動作について説明する。

#### 【0180】

まず、雑音等の影響により、イネーブル回路2801の出力ノードから、V D Dよりも高い電圧の信号が供給されたとする。そうすると、整流素子2806には順方向にバイアスが加わり、イネーブル回路2801にチャージした電荷は、V D Dを伝達する電源線に放

50

電して、ゲート線  $G_x$  の電位は、 $V_{DD}$ 、又は  $V_{DD} + \Delta$  ( $\Delta$  は 0 以上の数であり、 $V_{DD} + \Delta$  は  $V_{DD}$  よりも高い電位を意味する) の電位となる。

#### 【0181】

一方、イネーブル回路 2801 の出力ノードから、 $V_{SS}$  よりも低い電圧の信号が供給されたとする。そうすると、整流素子 2805 には順方向にバイアスが加わり、ゲート線  $G_x$  の電位は、 $V_{SS}$ 、又は  $V_{SS} - \Delta$  ( $\Delta$  は 0 以上の数であり、 $V_{SS} - \Delta$  は  $V_{SS}$  よりも低い電位を意味する) の電位となる。

#### 【0182】

このように、雑音等により、イネーブル回路 2801 の出力ノードから供給される電圧が、瞬間に、 $V_{DD}$  より高くなったり、 $V_{SS}$  よりも低くなったりしても、ゲート線  $G_x$  に与えられる電圧は、 $V_{DD}$  よりも高くならず、また  $V_{SS}$  よりも低くならない。従って、雑音や静電気等に起因した素子の誤作動、損傷、破壊を抑制することができる。10

#### 【実施例10】

#### 【0183】

本実施例では、図 4 に示した第 1 のゲートドライバ 41 が備える選択回路 55 の有するトライステートバッファ 87 と保護回路 88 を他の構成に置き換えた例を図 28 に示す。図 9 に示すトライステートバッファ 87 は、第 1 のゲートドライバ 41 及び第 2 のゲートドライバ 42 の一方がゲート線  $G_y$  の充放電を行う際に、他方のドライバの出力がそれを阻害しないようにするものである。従って、上記のような機能を有するものであれば、トライステートバッファだけでなく、図 29 に示すようなクロックドインバータ 2902 を用いたイネーブル回路 2901 を用いてもよい。また、保護回路 2802 は整流素子 2805 及び整流素子 2806 を有する。なお、本構成は実施例 9 に示したイネーブル回路 2801 の有するアナログスイッチの代わりにクロックドインバータを適用したもので、動作方法については実施例 9 の図 28 に示したイネーブル回路 2801 及び保護回路 2802 と同様なので省略する。20

#### 【実施例11】

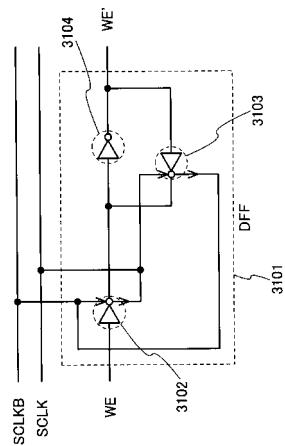

#### 【0184】

本実施例では、図 4 などにおける選択信号線 52 に関して述べる。WE 信号は、選択信号線 52 を介して、ゲートドライバやソースドライバに入力される。このとき、実際に画素に入力される信号のタイミングに注意する必要がある。30

#### 【0185】

つまり、ゲート信号線から画素に送られる選択信号がオフするタイミング（ゲート信号線の選択が解除されるタイミング）と、ソース信号線から画素に送られてくるビデオ信号や消去信号が変化するタイミングとを考慮する必要がある。例えば、ゲート信号線から画素に送られる選択信号がオフする前に、ビデオ信号や消去信号が変化してしまうと、変化してしまった信号が画素に入力されてしまう。したがって、画素に入力したいビデオ信号や消去信号は、選択信号がオフするまで（ゲート信号線の選択が解除されるまで）、変わらないようにしておくことが重要である。選択信号がオフした後（ゲート信号線の選択が解除された後）であれば、次の画素に入力するためのビデオ信号や消去信号の値に変化しても問題ない。40

#### 【0186】

そこで、図 30 に示すように、ソースドライバ 43 に WE 信号を入力する前に、遅延回路 3000 を設ければよい。そして、ゲートドライバには、WE 信号をそのまま入力すればよい。その結果、WE 信号が変化したとき、ソースドライバには遅延回路によって遅れて WE 信号が伝わるため、ビデオ信号や消去信号が変化するタイミングを選択信号よりも遅くする（ビデオ信号や消去信号が変化するタイミングを、ゲート信号線の選択が解除されるタイミングよりも遅くする）ことが可能となる。その結果、画素に正しい信号を入力することができる。なお、図 30 は図 4 の表示装置と同様の構成のところは同じ符号を用いて模式的に示した図である。

#### 【0187】

50

30

40

50

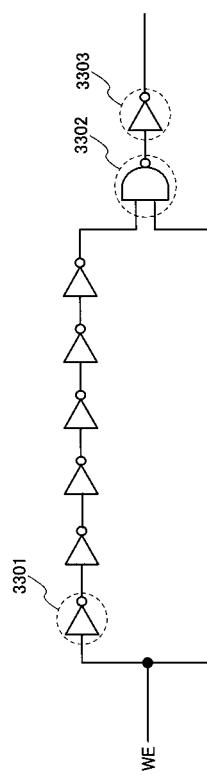

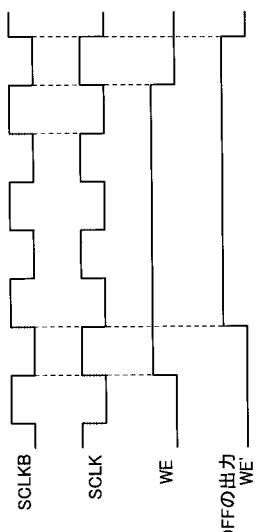

次に、図31に、遅延回路の例を示す。基本的には、入力された信号を遅延させて出力すればよい。図31では、フリップフロップ回路を用いた場合の例を示している。ここで、図31のようなフリップフロップ回路3101は、クロックドインバータ3102、クロックドインバータ3103及びインバータ3104を有し、一般的に、ディレイ型フリップフロップ回路(DFF)と呼ばれている。DFFを構成するクロックドインバータ3102及び3103は、そこに入力されるクロック信号に同期して動作する。そのため、遅延回路としてDFFを一段配置すると、DFFに供給されるクロック信号の分だけ(クロック信号の周期の半分の時間だけ)、信号が遅延することになる。

#### 【0188】

図34に、タイミングチャートを示す。DFF3101への入力信号(WE信号)に対して、クロック信号の周期の半分の時間だけ、DFFからの出力信号(WE'信号)が遅延していることが分かる。

10

#### 【0189】

ここで、遅延回路のDFF3101に入力するクロック信号は、どのような信号でもよい。しかし、別の目的で入力している信号を利用できるのであれば、その方が効率的である。したがって、ソースドライバに入力しているクロック信号を用いればよい。

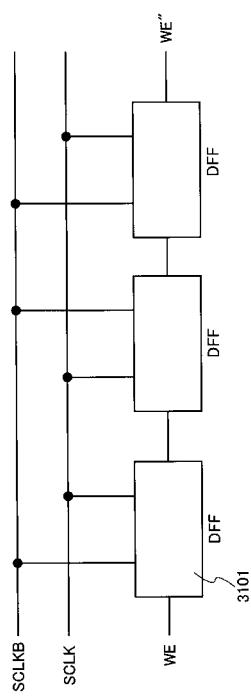

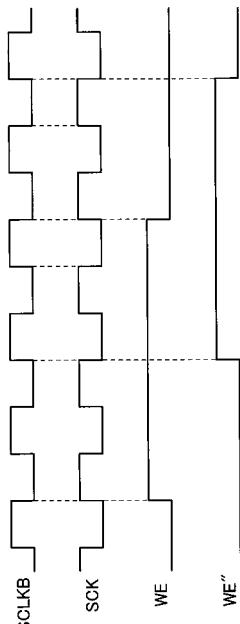

#### 【0190】

また、図31の場合は、DFF3101に入力するクロック信号の分だけ(クロック信号の周期の半分の時間だけ)が遅延するが、もっと遅延させたい場合は、図32のように、DFF3101を複数段直列に接続すればよい。DFF3101を何段で接続するかを調整することにより、遅延時間を任意に設計することが可能となる。図32では、DFFを3段分だけ直列に接続している。したがって、図35のタイミングチャートに示すように、クロック信号の周期の半分の時間の3倍分だけ、DFFへの入力信号(WE信号)に対して、DFFからの出力信号(WE'信号)が遅延していることが分かる。

20

#### 【0191】

なお、図31、図32では、DFFを用いた場合の構成を示したが、これに限定されない。シフトレジスタで用いられるような回路であれば、どのような構成でも、適用可能である。

#### 【0192】

また、別の手法としては、クロック信号に同期させて遅延させるのではなく、複数の回路を信号が順に伝播していくときの遅延時間を利用して、信号を遅延させてもよい。その場合の構成を図33に示す。ここでは、インバータ3301を複数段接続させて信号を遅延させている。それだけでも構わないが、さらに、遅延させた後の信号と、遅延させる前の信号を、NAND3302に入力し、NAND3302の出力を用いて信号のパルス幅を狭くしてもよい。そして反転したWE信号をインバータ3303で戻している。

30

#### 【実施例12】

#### 【0193】

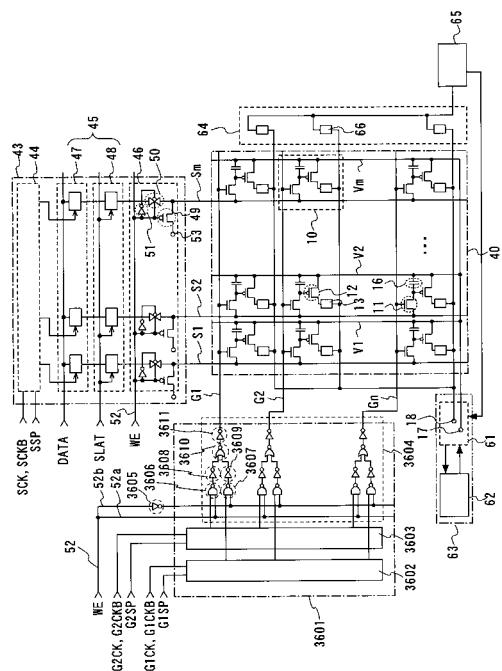

図4に記載した表示装置は画素領域40を挟んで対向するように第1のゲートドライバ41と第2のゲートドライバを配置した構成となっているが、本実施例では、一つのゲートドライバを片側に配置した構成で図4の構成の表示装置と同様の動作をする表示装置を図36に示す。なお、図4に示した表示装置と構成が同じ所は共通の符号を用いている。

40

#### 【0194】

ソースドライバ43は、パルス出力回路44、ラッチ45及び選択回路46を有する。ラッチ45は第1のラッチ47と第2のラッチ48を有する。選択回路46は、TFT49と、アナログスイッチ50を有する。TFT49とアナログスイッチ50は、ソース線Sxに対応して、各列に設けられる。インバータ51は、WE信号(Write Erase)の反転信号を生成するためのものであり、外部からWE信号の反転信号を供給する場合には設けなくてもよい。

#### 【0195】

TFT49のゲート電極は選択信号線52に接続し、ソース電極及びドレイン電極の一方

50

はソース線 S<sub>x</sub>に接続し、他方は電源 5<sub>3</sub>に接続する。アナログスイッチ 5<sub>0</sub>は、第 2 のラッチ 4<sub>8</sub>とソース線 S<sub>x</sub>の間に設けられる。つまり、アナログスイッチ 5<sub>0</sub>の入力ノードは第 2 のラッチ 4<sub>8</sub>に接続し、出力ノードはソース線 S<sub>x</sub>に接続する。アナログスイッチ 5<sub>0</sub>の 2 つの制御ノードは、一方は選択信号線 5<sub>2</sub>に接続し、他方はインバータ 5<sub>1</sub>を介して選択信号線 5<sub>2</sub>に接続する。電源 5<sub>3</sub>の電位は、画素 1<sub>0</sub>が含む TFT 1<sub>2</sub>をオフにする電位であり、TFT 1<sub>2</sub>が N 型の場合は電源 5<sub>3</sub>の電位を L レベルとし、TFT 1<sub>2</sub>が P 型の場合は電源 5<sub>3</sub>の電位を H レベルとする。

#### 【0196】

ゲートドライバ 3601 は第 1 のパルス出力回路 3603、第 2 のパルス出力回路 3602 及び選択回路 3604 を有する。選択回路 3604 は、NAND ゲート 3606、3607、インバータ 3608、3609、3611 及び NOR ゲート 3610 をゲート線の各列に対応して有する。選択信号線 5<sub>2</sub> は分岐され一方の選択信号線 5<sub>2a</sub> は NAND ゲート 3606 の一方の端子に接続され、NAND ゲート 3606 の他方の端子は第 1 のパルス出力回路 3603 に接続されている。他方の選択信号線 5<sub>2b</sub> はインバータ 3605 を介して NAND ゲート 3607 の一方の端子に接続され、NAND ゲート 3607 の他方の端子は第 2 のパルス出力回路 3602 に接続されている。NAND ゲート 3606 の出力端子はインバータ 3608 の入力端子に接続され、NAND ゲート 3607 の出力端子はインバータ 3609 の入力端子に接続されている。インバータ 3608 及び 3609 の出力端子は NOR ゲート 3610 の入力端子に接続され、NOR ゲート 3610 の出力端子はインバータ 3611 の入力端子に接続されている。つまり、選択信号線 5<sub>2a</sub> から選択回路 3604 に入力される信号と選択信号線 5<sub>2b</sub> から選択回路 3604 に入力される信号は反転していることになる。10 20

#### 【0197】

ここで、本実施例のゲートドライバの動作方法について説明する。

#### 【0198】

NAND ゲート 3606 又は NAND ゲート 3607 の入力端子の双方の入力端子が H レベルとなったときにゲート線 G<sub>x</sub> は H レベルの信号が入力される。

#### 【0199】

ここで、画素に信号を書き込む時には WE 信号は H レベルとする。すると、選択信号線 5<sub>2a</sub> から NAND ゲート 3606 トの一方の端子に H レベルが入力される。よって、この NAND ゲート 3606 の他方の端子が接続されている第 1 のパルス出力回路 3603 から H レベルの出力される行の対応するゲート線の行が書き込みのため選択された画素行になる。つまり、信号を書き込む画素行のトランジスタ 1<sub>1</sub> がオンする。そして WE 信号が H レベルの時には選択回路 4<sub>6</sub> のアナログスイッチはオンし、第 2 のラッチ 4<sub>8</sub> からの信号が信号線 S<sub>x</sub> へ出力される。こうして画素を駆動する TFT 1<sub>2</sub> のゲート電位を保持する容量素子 1<sub>6</sub> に電荷が蓄積し、画素に信号を書き込むことができる。30

#### 【0200】

画素に書き込まれた信号を消去する消去動作時には WE 信号は L レベルとする。すると、選択信号線 5<sub>2b</sub> からインバータ 3605 を介して NAND ゲート 3607 トの一方の端子に H レベルが入力される。よって、この NAND ゲート 3607 の他方の端子が接続されている第 2 のパルス出力回路 3602 から H レベルの出力される行の対応するゲート線の行が消去のため選択された画素行になる。つまり、消去する画素行のトランジスタ 1<sub>1</sub> がオンする。そして WE 信号が L レベルの時には選択回路 4<sub>6</sub> の TFT 4<sub>9</sub> はオンし、電源 5<sub>3</sub> の電位が信号線 S<sub>x</sub> の電位となる。こうして画素を駆動する TFT 1<sub>2</sub> のゲート電位を保持する容量素子 1<sub>6</sub> は放電し、画素に書き込まれた信号を消去することができる。40

#### 【0201】

ソースドライバ 4<sub>3</sub> が含むパルス出力回路 4<sub>4</sub>、ゲートドライバ 3601 が含む第 1 のパルス出力回路 3603 及び第 2 のパルス出力回路 3602 は、複数のフリップフロップ回路からなるシフトレジスタやデコーダ回路に相当する。パルス出力回路 4<sub>4</sub>、3602、3603 として、デコーダ回路を適用すれば、ソース線 S<sub>x</sub> 又はゲート線 G<sub>y</sub> をランダム50

に選択することができる。ソース線 S<sub>x</sub> 又はゲート線 G<sub>y</sub> をランダムに選択することができると、時間階調方式を適用した場合に生じる疑似輪郭の発生を抑制することができる。

#### 【 0 2 0 2 】

なおソースドライバ 4 3 の構成は上記の記載に制約されず、レベルシフタやバッファを設けてもよい。また、ゲートドライバ 3 6 0 1 の構成も上記の記載に制約されず、レベルシフタやバッファを設けてもよい。また、上記には記載していないが、ソースドライバ 4 3 、ゲートドライバ 3 6 0 1 は、保護回路を有することを特徴とする。保護回路を有するドライバの構成については、実施の形態 3 に説明した構成を用いることができる。

#### 【 0 2 0 3 】

なお、本実施例に示す図 3 6 の表示装置に実施例 1 1 で示した図 3 1 ~ 3 3 に示す遅延回路を適用することも出来る。 10

#### 【 0 2 0 4 】

また本発明の表示装置は、電源制御回路 6 3 を有することを特徴とする。電源制御回路 6 3 は、発光素子 1 3 に電源を供給する電源回路 6 1 とコントローラ 6 2 を有する。電源回路 6 1 は、TFT 1 2 と電源線 V<sub>x</sub> を介して発光素子 1 3 の画素電極に接続する。また、電源回路 6 1 は、電源線を介して、発光素子 1 3 の対向電極に接続する。

#### 【 0 2 0 5 】

発光素子 1 3 に順方向バイアスの電圧を印加して、発光素子 1 3 に電流を流して発光させることは、第 1 の電源 1 7 の電位が、第 2 の電源 1 8 の電位よりも高くなるように、第 1 の電源 1 7 と第 2 の電源 1 8 の電位差を設定する。 20

一方、発光素子 1 3 に逆方向バイアスの電圧を印加する際は、第 1 の電源 1 7 の電位が、第 2 の電源 1 8 の電位よりも低くなるように、第 1 の電源 1 7 と第 2 の電源 1 8 の電位を設定する。このような電源電位の設定は、コントローラ 6 2 から電源回路 6 1 に所定の信号を供給することにより、行われる。

#### 【 0 2 0 6 】

本発明は、電源制御回路 6 3 を用いて、発光素子 1 3 に逆方向バイアスの電圧を印加することで、発光素子 1 3 の経時劣化を抑制し、信頼性を向上させることができる。また、発光素子 1 3 は、異物の付着や、陽極又は陰極にある微細な突起によるピンホール、電界発光層の不均一性を起因として、陽極と陰極が短絡する初期不良が生じることがある。このような初期不良が発生すると、信号に応じた画素の点灯及び非点灯が行われず、電流のほとんどすべてが陽極と陰極の短絡部を流れて素子全体が消光する現象が生じたり、特定の画素が点灯又は非点灯しない現象が生じたりして、画像の表示が良好に行われないという問題が発生する。しかしながら、本発明の構成によると、発光素子に逆方向バイアスを印加することができるため、陽極と陰極の短絡部のみに局所的に電流を流し、短絡部を発熱させ、その結果、短絡部を酸化又は炭化して絶縁化することができる。その結果、初期不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。なお、このような初期不良の絶縁化は、出荷前に行うとよい。また、初期不良だけでなく、時間の経過に伴い、新たに陽極と陰極の短絡が発生することがある。このような不良は進行性不良とも呼ばれるが、本発明の構成によると、定期的に発光素子に逆方向バイアスを印加することができるので、進行性不良が生じても、その不良を解消し、画像の表示を良好に行うことができる。なお、発光素子 1 3 に逆方向バイアスの電圧を印加するタイミングには特に制約はない。 30

#### 【 0 2 0 7 】

また本発明の表示装置は、モニター回路 6 4 と制御回路 6 5 を有することを特徴とする。モニター回路 6 4 は、周囲の温度（以下環境温度と表記）に基づき動作する。制御回路 6 5 は定電流源とバッファを有する。図示する構成では、モニター回路 6 4 は、モニター用発光素子 6 6 を有する。 40

#### 【 0 2 0 8 】

制御回路 6 5 は、モニター回路 6 4 の出力に基づき、電源電位を変更する信号を、電源制御回路 6 3 に供給する。電源制御回路 6 3 は、制御回路 6 5 から供給される信号に基づき 50

、画素領域40に供給する電源電位を変更する。上記構成を有する本発明は、環境温度の変化に起因した電流値の変動を抑制して、信頼性を向上させることができる。なおモニタ－回路64と制御回路65の詳しい構成については、実施の形態3において示した構成を用いることが出来る。

#### 【0209】

定電圧駆動を行う本発明の表示装置は、発光素子の輝度が $500\text{cd}/\text{m}^2$ 、画素の開口率が50%のとき、消費電力が1W以下(950mW)となった。一方、定電流駆動を行う表示装置は、発光素子の輝度が $500\text{cd}/\text{m}^2$ 、画素の開口率が25%のとき、消費電力は約2W(2040mW)であった。つまり、定電圧駆動を採用することで、消費電力を削減することができる事が分かる。なお、定電圧駆動を採用することで、消費電力は1W以下、好ましくは0.7W以下にまで削減することができる。

10

なお、上記の消費電力の値は、画素領域のみの消費電力であり、駆動回路部分の消費電力は含まれていない。また、両者とも時間階調の表示デューティー比は70%である。

#### 【0210】

また、上記の消費電力の測定を行った、定電圧駆動を行う表示装置と定電流駆動を行う表示装置の画素領域の画素数は、 $240 \times 3 \times 320$ であり、両者で同じであった。

#### 【図面の簡単な説明】

#### 【0211】

【図1】本発明の表示装置が含む画素とその断面構造を説明する図。

20

【図2】本発明の表示装置が含む画素のマスクレイアウトを説明する図。

【図3】本発明の表示装置が含む画素のマスクレイアウトを説明する図。

【図4】本発明の表示装置の構成を説明する図。

【図5】本発明の表示装置が含むソースドライバの構成を説明する図。

【図6】本発明の表示装置が含むソースドライバの構成を説明する図。

【図7】本発明の表示装置が含むソースドライバの構成を説明する図。

【図8】本発明の表示装置が含むゲートドライバの構成を説明する図。

【図9】本発明の表示装置が含むゲートドライバの構成を説明する図。

【図10】本発明の温度補償機能を説明する図。

【図11】本発明の表示装置の動作を説明する図。

30

【図12】時間階調方式を説明する図。

【図13】時間階調方式を説明する図。

【図14】本発明の表示装置が含む画素のマスクレイアウトを説明する図。

【図15】本発明の表示装置の一形態であるパネルを示す図。

【図16】本発明の表示装置の一形態であるパネルを示す図。

【図17】本発明の表示装置を具備する電子機器を示す図。

【図18】保護回路の構成を説明する図。

【図19】本発明の表示装置が含む画素とその断面構造を説明する図。

【図20】本発明の補償回路を説明する図。

【図21】発光素子の温度特性を説明する図。

40

【図22】本発明の補償回路を説明する図。

【図23】本発明の補償回路を説明する図。

【図24】本発明の補償回路を説明する図。

【図25】本発明に適用することができるソースドライバの例。

【図26】本発明に適用することができるソースドライバの例。

【図27】本発明に適用することができるソースドライバの例。

【図28】本発明の表示装置が含むゲートドライバの構成を説明する図。

【図29】本発明の表示装置が含むゲートドライバの構成を説明する図。

【図30】遅延回路を備えた本発明の表示装置の模式図。

【図31】本発明に適用することができる遅延回路の例。

【図32】本発明に適用することができる遅延回路の例。

50

【図33】本発明に適用することができる遅延回路の例。

【図34】本発明に適用することが出来る遅延回路のタイミングチャート。

【図35】本発明に適用することが出来る遅延回路のタイミングチャート。

【図36】本発明の表示装置の構成を説明する図。

【 四 1 】

【 四 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【 四 1 1 】

【 図 1 2 】

【 図 1 3 】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【 図 20 】

【図21】

【 図 2 2 】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図3-2】

【図3-3】

【図3-4】

【図3-5】

【図36】

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 622B

G 09 G 3/20 622J

G 09 G 3/20 624B

G 09 G 3/20 641E

G 09 G 3/20 642P

H 05 B 33/14 A

(72)発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 木村 肇

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 奈良田 新一

(56)参考文献 特開2001-324958 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 09 G 3/20, 3/30 - 3/32

H 01 L 51/50