(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5009500号

(P5009500)

(45) 発行日 平成24年8月22日(2012.8.22)

(24) 登録日 平成24年6月8日(2012.6.8)

(51) Int.Cl.

H01L 25/00 (2006.01)

F 1

H01L 25/00

B

請求項の数 18 (全 10 頁)

(21) 出願番号 特願2004-541592 (P2004-541592)

(86) (22) 出願日 平成15年9月17日 (2003.9.17)

(65) 公表番号 特表2006-501678 (P2006-501678A)

(43) 公表日 平成18年1月12日 (2006.1.12)

(86) 國際出願番号 PCT/US2003/029719

(87) 國際公開番号 WO2004/032188

(87) 國際公開日 平成16年4月15日 (2004.4.15)

審査請求日 平成18年9月14日 (2006.9.14)

(31) 優先権主張番号 10/262,217

(32) 優先日 平成14年9月30日 (2002.9.30)

(33) 優先権主張国 米国(US)

(73) 特許権者 592054856

クリー インコーポレイテッド

C R E E I N C.

アメリカ合衆国 ノースカロライナ州 2

7703 ダラム シリコン ドライブ

4600

(74) 代理人 110000855

特許業務法人浅村特許事務所

(74) 代理人 100066692

弁理士 浅村 皓

(74) 代理人 100072040

弁理士 浅村 肇

(74) 代理人 100159525

弁理士 大日方 和幸

最終頁に続く

(54) 【発明の名称】 RFパワーデバイス及びRFパワートランジスタデバイスにおける直線性を改善する方法

## (57) 【特許請求の範囲】

## 【請求項1】

a) 少なくとも一つのトランジスタと、

b) 前記トランジスタに結合されたRF信号入力リード線と、

c) 前記トランジスタに結合された接地端子と、

d) 前記トランジスタに結合されたRF信号出力リード線と、

e) 前記RF信号出力リード線に結合された出力マッチング回路であって前記トランジスタが該出力マッチング回路を介して前記RF信号出力リード線に結合された出力マッチング回路、および該出力マッチング回路を介して前記RF信号出力リード線に結合されたRF及びビデオバイパス回路と、

f) 要素a)及びe)を収容するパッケージで、要素b)、c)、及びd)が前記パッケージから延出された状態となるパッケージと、

g) 前記RF及びビデオバイパス回路に結合され、前記パッケージから延出したバイアスリード線と、

を備えた、パッケージに収納されたRFパワーデバイス。

## 【請求項2】

a) 少なくとも一つのトランジスタと、

b) 前記トランジスタに結合されたRF信号入力リード線と、

c) 前記トランジスタに結合された接地端子と、

d) 前記トランジスタに結合されたRF信号出力リード線と、

10

20

e ) 前記 R F 信号出力リード線に結合された出力マッチング回路であって前記トランジスタが該出力マッチング回路を介して前記 R F 信号出力リード線に結合された出力マッチング回路、および該出力マッチング回路を介して前記 R F 信号出力リード線に結合された R F 及びビデオバイパス回路と、

f ) 要素 a ) 及び e ) を収容するパッケージで、要素 b ) 、 c ) 、及び d ) が前記パッケージから延出された状態となるパッケージと、

g ) 前記 R F 及びビデオバイパス回路を介して前記トランジスタに D C バイアス電圧を印加するためのバイアスリード線とを備え、前記 R F 信号出力リード線と前記バイアスリード線は兼用されているパッケージに収納された R F パワーデバイス。

【請求項 3】

前記 R F 及びビデオバイパス回路は、少なくとも一つの個別キャパシタと、前記個別キャパシタを前記トランジスタに結合するワイヤボンディングとを備え、前記ワイヤボンディングは、前記 R F バイパス回路においてインダクタンスを提供する請求項 1 記載のパッケージに収納された R F パワーデバイス。

【請求項 4】

前記出力マッチング回路は、接地に直列で接続された誘導素子及び容量素子を、ワイヤボンディングによって前記容量素子と並列に接続された少なくとも一つの個別キャパシタと共に含む請求項 3 記載のパッケージに収納された R F パワーデバイス。

【請求項 5】

前記少なくとも一つの個別キャパシタは、複数の個別多層キャパシタを備える請求項 4 記載のパッケージに収納された R F パワーデバイス。

【請求項 6】

前記 R F 及びビデオバイパス回路は、少なくとも一つの個別キャパシタと、前記個別キャパシタを前記トランジスタに結合するワイヤボンディングとを備え、前記ワイヤボンディングは、前記 R F バイパス回路においてインダクタンスを備える請求項 1 記載のパッケージに収納された R F パワーデバイス。

【請求項 7】

前記出力マッチング回路は、接地に直列で接続された誘導素子及び容量素子を、ワイヤボンディングによって前記容量素子と並列に接続された少なくとも一つの個別キャパシタと共に含む請求項 6 記載のパッケージに収納された R F パワーデバイス。

【請求項 8】

前記少なくとも一つの個別キャパシタは、複数のキャパシタを備える請求項 7 記載のパッケージに収納された R F パワーデバイス。

【請求項 9】

前記少なくとも一つのトランジスタは、F E T を備える請求項 1 記載のパッケージに収納された R F パワーデバイス。

【請求項 10】

前記少なくとも一つのトランジスタは、バイポーラトランジスタを備える請求項 1 記載のパッケージに収納された R F パワーデバイス。

【請求項 11】

前記少なくとも一つのトランジスタは、複数のトランジスタを備える請求項 1 記載のパッケージに収納された R F パワーデバイス。

【請求項 12】

a ) 少なくとも一つの R F パワートランジスタをハウジング内に提供するステップと、

b ) 前記ハウジングから延出し、前記トランジスタに電気的に結合された R F 信号入力リード線及び R F 信号出力リード線を提供するステップと、

c ) 前記 R F 信号出力リード線に結合された出力マッチング回路であって前記トランジスタが該出力マッチング回路を介して前記 R F 信号出力リード線に結合された出力マッチング回路を前記ハウジング内に提供するステップと、

d ) 前記出力マッチング回路を介して前記 R F 信号出力リード線に接続され、D C 電力

10

20

30

40

50

を前記トランジスタに供給する時、R F 及びビデオ電流がD C 電源へ流れるのを防止するR F 及びビデオバイパス回路であって前記トランジスタが該出力マッチング回路を介して結合されたR F 及びビデオバイパス回路を前記ハウジング内に提供するステップと、

e ) 前記ハウジングから延出し、前記トランジスタ、前記R F およびビデオバイパス回路に接続されて前記D C 電源を供給するバイアスリード線を提供するステップと

を備え、前記R F 信号出力リード線と前記バイアスリード線は兼用されている広帯域R F パワートランジスタデバイスにおける直線性を改善する方法。

【請求項13】

ステップd ) の前記R F 及びビデオバイパス回路は、少なくとも一つの個別キャパシタと、前記個別キャパシタを前記トランジスタに結合するワイヤボンディングとを備え、前記ワイヤボンディングは、前記R F バイパス回路においてインダクタンスを提供する請求項12記載の方法。

【請求項14】

ステップc ) の前記出力マッチング回路は、接地に直列で接続された誘導素子及び容量素子を、ワイヤボンディングによって前記容量素子と並列に接続された少なくとも一つの個別キャパシタと共に含む請求項13記載の方法。

【請求項15】

ステップd ) の前記少なくとも一つの個別キャパシタは、複数のキャパシタを備える請求項14記載の方法。

【請求項16】

ステップd ) の前記R F バイパス回路は、少なくとも一つの個別キャパシタと、前記個別キャパシタを前記トランジスタに結合するワイヤボンディングとを備え、前記ワイヤボンディングは、前記R F バイパス回路においてインダクタンスを提供する請求項12記載の方法。

【請求項17】

ステップc ) の前記出力マッチング回路は、接地に直列で接続された誘導素子及び容量素子を、ワイヤボンディングによって前記容量素子と並列に接続された少なくとも一つの個別キャパシタと共に含む請求項16記載の方法。

【請求項18】

ステップd ) の前記少なくとも一つの個別キャパシタは、複数の個別キャパシタを備える請求項17記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、R F (高周波数帯域) パワートランジスタに関し、特にパッケージに収納されたR F パワートランジスタにおいて、出力マッチングとR F 及びビデオバイパス回路とを組み合わせる技術に関する。

【背景技術】

【0002】

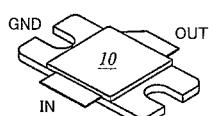

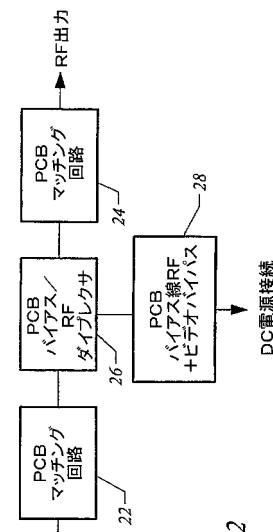

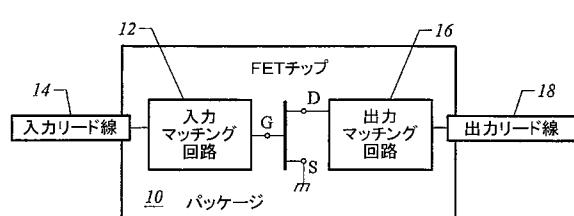

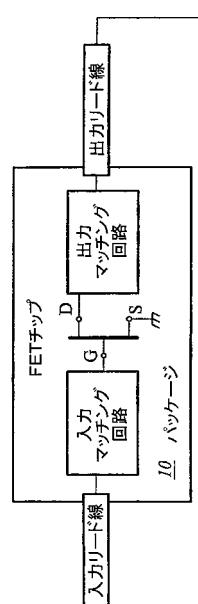

10ワット以上の電力を提供するR F パワートランジスタは、図1Aに符号10として全体図を示し、図1Bで概略図を示したように、通常、個別のデバイスとしてパッケージ化される。パッケージに収納されたトランジスタ(F E T又はバイポーラ)は、通常、入力リード線14をF E Tのゲート(又はバイポーラトランジスタの基部)に接続する入力マッチング回路12と、出力リード線18をF E Tのドレイン(又はバイポーラトランジスタのコレクタ若しくはエミッタ)に接続する出力マッチング回路16とを含む。通常、F E Tのソースは接地される。

【発明の開示】

【発明が解決しようとする課題】

【0003】

パッケージトランジスタは、図2に図示したように、通常、プリント回路基板20にマ

10

20

30

40

50

ウントされる。プリント回路基板には、更に、トランジスタ出力を R F 出力に接続するマッチング回路 22、24、及びバイアス / R F ダイプレクサ 26 がマウントされる。D C 電源は、R F 及びビデオバイパス回路 28 のバイアスリード線と、ダイプレクサ 26 と、マッチング回路 22 とを介して、トランジスタ出力リード線に接続される。こうしたプリント回路基板の二重機能は、搬送周波数での望ましいインピーダンス変換を提供し、ダイプレクサを介してデバイスに D C バイアス電流を投入する手段を提供する。回路は、更に、電源の接続を R F 及びビデオ周波数で適切にバイパスする必要がある。パッケージトランジスタからの回路の距離は、この従来のアプローチにおける制限となる。この分離は、大きな電気的遅延をもたらし、プリント回路基板において使用されるキャパシタに固有の特性によって、バイアス回路のビデオ帯域幅には不可避の制限が生じる。

10

【課題を解決するための手段】

【0004】

本発明によれば、出力マッチング回路及びダイプレクサは、R F 及びビデオバイパスネットワークと共に、トランジスタパッケージ内のパワートランジスタに統合される。これにより、回路は、トランジスタの近くに配置され、電源バイパスビデオ帯域幅が増加する。更に、パワートランジスタの直線性（忠実度）は、従来の広帯域信号用デバイスに比べて増加する。

【0005】

本発明の実施において、R F 及びビデオバイパスネットワークの個別多層キャパシタは、回路の誘導素子を提供するワイヤボンディングとの一体的な配置において、出力マッチング回路の（搬送波周波数での最適な特性を備えた）キャパシタと並列に接続できる。通常、ワイヤボンドは、トランジスタの寄生出力容量のリアクタンスと同等で正反対の分路誘導リアクタンスを提供するように設定される。R F 出力のための追加容量も、バイアス入力を提供するか、或いは分離したバイアス入力により機能するR F 出力によって提供できる。

20

【0006】

本発明及びその目的及び特徴は、図面と併せて考慮することで、以下の詳細な説明及び添付特許請求の範囲から容易に明らかとなろう。

【発明を実施するための最良の形態】

【0007】

30

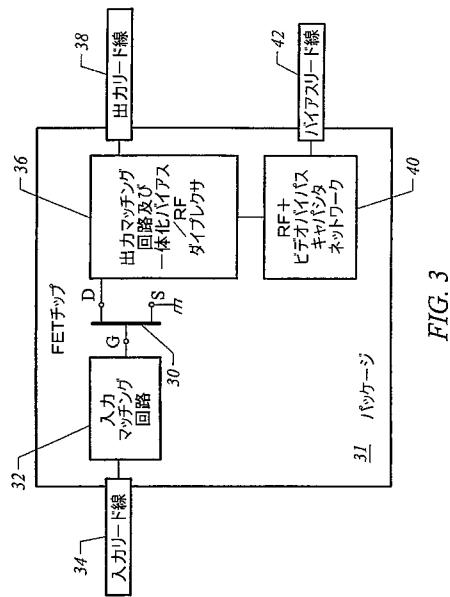

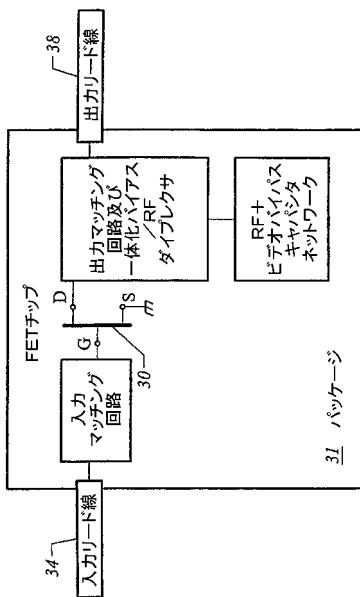

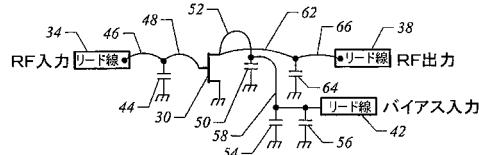

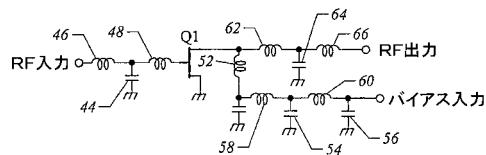

図 3 及び 4 は、本発明の二つの実施形態による、マッチング及びバイパス回路を備えたパッケージに収納された R F パワートランジスタの機能ブロック図である。二つの図において同様の符号を付した要素は、原則として同じものである。図 3 において、R F パワートランジスタ 30 は、パッケージ 31 内にマウントされる。F E T トランジスタが例示されているが、上記のように、パワートランジスタはバイポーラにもできる。更に、二つ以上のトランジスタをパッケージ内にマウントし、並列に接続できる。F E T 30 のゲートは、従来技術のように、入力マッチング回路 32 を介して入力リード線 34 に接続されるが、ドレインは、出力マッチング回路及び一体化バイアス / R F ダイプレクサ 36 を介して、出力リード線 38 と、トランジスタに D C バイアス電流を提供するバイアスリード線 42 とに接続される。図 2 に例示した従来技術の回路において、回路 36 及び 40 は、トランジスタからある程度の距離で、プリント回路基板上においてパッケージの外部にマウントされる。上記のように、パッケージ内での出力マッチング回路と、バイアス / R F ダイプレクサと、R F 及びビデオバイパスネットワークとの提供は、電源バイパスビデオ帯域幅を増加させ、広帯域信号でのパワートランジスタ回路の直線性を高める。図 4 の機能ブロック図は、出力リード線 38 がバイアスリード線としても機能することを除き、図 3 の回路と同様である。

40

【0008】

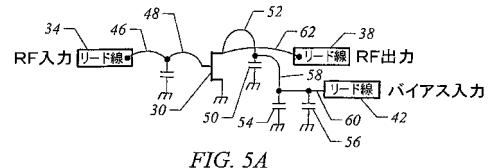

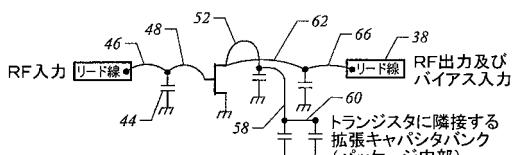

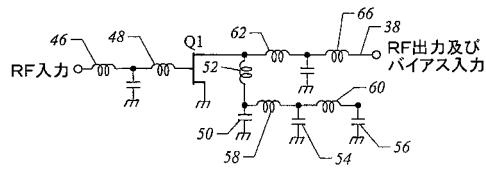

図 5 A、5 B は、それぞれ、ワイヤボンディングが誘導素子として利用され、個別多層キャパシタが出力マッチング及びバイパスネットワークにおいて利用される本発明の一実施形態の物理的及び電気的概略図である。図 5 A において、図 3 の入力マッチング回路 3

50

2は、ワイヤボンド46によってRF入力34に接続され、ワイヤボンド48によってトランジスタ30の基部に接続された分路キャパシタ44を備える。出力マッチング及びバイパスネットワークは、(搬送RF周波数での最適な特性を有する)キャパシタ50に接続され、更にワイヤボンド52、58、及び60を用いてトランジスタ30のドレインとバイアス入力リード線42に接続された、個別多層キャパシタ54、56を備える。代表的な実施形態において、ワイヤボンド52は、トランジスタの寄生出力容量と共振するのに必要な特定の値のインダクタンスを備える。この小さな値は、最適なビデオバイパスをサポートする。同様に、RF出力リード線38は、ワイヤボンド62を用いてドレインに接続される。

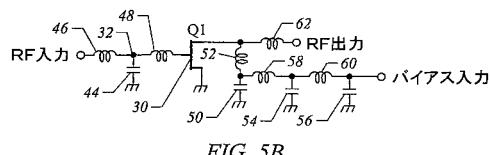

## 【0009】

10

図5Bは、ワイヤボンド図5Aの回路の電気的概略図であり、ワイヤボンドは、集中素子図において誘導素子として例示されている。

## 【0010】

図6A、6Bは、図5A、5Bの実施形態に類似した本発明の別の実施形態の物理的及び電気的概略図であり、RF出力リード線38及びトランジスタのドレイン30を分路して接地する個別キャパシタ64が追加され、出力マッチングネットワークにおいて誘導素子として機能するワイヤボンド62、66を備える。

## 【0011】

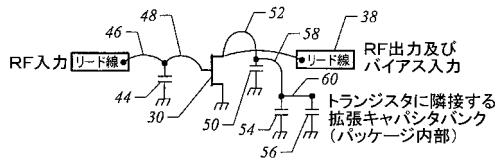

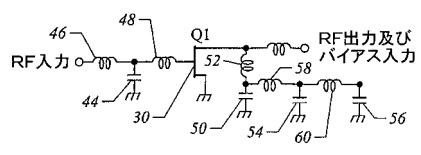

図7A、7Bは、図5A、5Bの実施形態に類似した物理的及び電気的概略図だが、分離したバイアス入力リード線42を利用しない。RF出力リード線38は、バイアス入力としても機能する。同様に、図8A、8Bは、図6A、6Bの実施形態に対応するが、ここでも、分離バイアス入力は提供されず、RF出力38は、バイアス入力として機能する。

20

## 【0012】

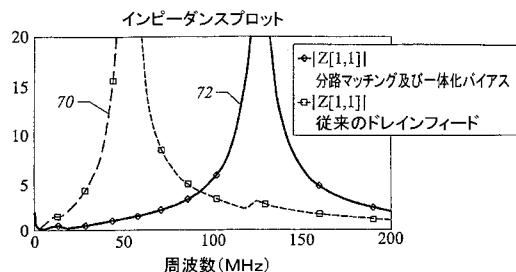

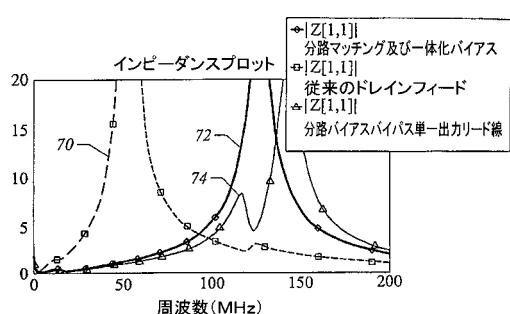

図9は、70で図示した従来デバイスと、72で図示した本発明によるデバイスとに関する、低周波数でトランジスタのドレインにおいて見られたインピーダンスの動作周波数に対するプロットである。デジタル通信信号による通常の電力增幅用途において、トランジスタから流れる電流は、RF(又はマイクロ波)周波数成分と、ビデオ周波数成分とを含む。理想的な状況において、ドレインには、ビデオ周波数の範囲においてインピーダンスゼロの完全な電源又は完全にRFバイパスされた電源が提供される。高電流電源をドレインに接続する一般的なアプローチでは、搬送波周波数で1/4波長となるように選択される場合がある導体又は高インピーダンス伝送線を、電源末端又は接続部のキャパシタバイパスアレイと共に使用する。このキャパシタアレイは、理想的なキャパシタに近付けることを意図したものだが、しかしながら、実際の物理的バイパスキャパシタは、固有の内部抵抗と内部インダクタンスとを有する。したがって、通常のバイパスキャパシタアレイでは、トランジスタの最も近くに、搬送周波数での優れた特性を備えた小さなキャパシタを挿入し、(低いビデオ周波数での最適な性能を備えた)大きなキャパシタは、電源の近くにする。バイパスキャパシタ間には必然的に有限の距離が存在し、短い電気的接続も、誘導的特性を有する。実際の物理的キャパシタでは、RFバイパスキャパシタアレイにおける不可避の共振が存在する。低いビデオ周波数インピーダンス(通常、1オーム)が望ましいものの、共振周波数においては、数十オームまで増加する場合が多い。本発明は、図9に例示したように、第一の有意な共振の周波数を高める一方で、回路の搬送波周波数特性を劣化させない。ここでは、従来の回路の第一の共振は約50MHzだが、本発明による回路は、第一の共振を約125MHzに高めている。現在のデジタル通信に対する電力增幅の用途では、数十MHzまでの非常に低いバイアス回路インピーダンスが求められ、こうした回路のインピーダンスは第一の共振周波数の1/4において大幅な増加を示すことから、こうした回路における共振は、100MHz以上の周波数にする必要がある。

30

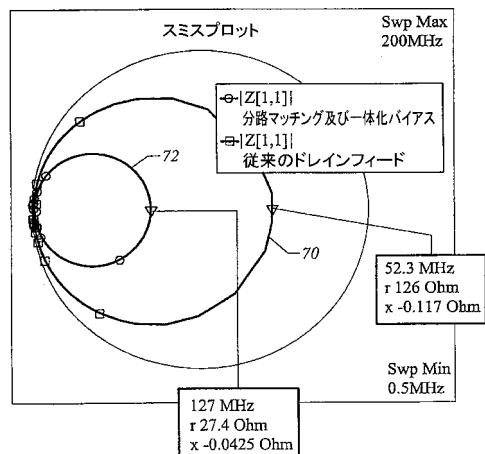

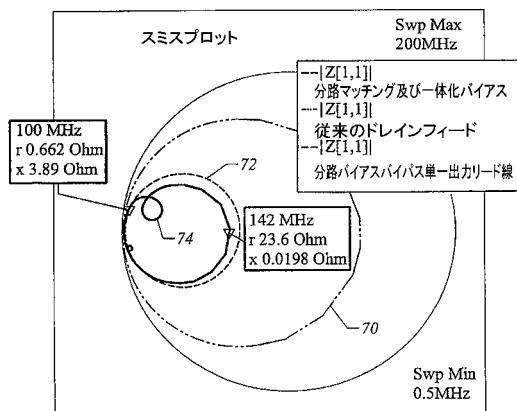

## 【0013】

40

図10は、本発明による回路に対する従来の回路の複素インピーダンスをスミスチャート上で図示している。あらゆる有意の寄生効果を有する回路モデルの第一の共振は、従来

50

の回路では 52 MHz となり、本発明による回路では 127 MHz となることは明らかである。この二倍を上回る改善は、新たな将来のデジタル通信用途にとって特に意義のあるものであり、こうしたデジタル通信用途において、従来の回路の低い共振は、出力信号における AM / PM 歪み及び AM / AM 歪みをもたらす。このような有害な影響は、こうした新しいシステムにとって重要なプリディストーション等の増幅器直線性増強技術の能力を低下させる。しかしながら、本発明によって、RF 電力増幅器は、こうした新技術において実用的なものとなる。

【0014】

図 11 は、バイアスリード線が分離リードではなく、RF 出力リード線に含まれる RF 電力増幅器の実施形態での、周波数に対するインピーダンスのプロットである。ここでは 10 、不要である余分な共振を導入可能な二つの RF バイパスキャパシタネットワーク（パッケージの内部及び外部）が存在する。図 11 に図示したように、追加の共振 74 は、インピーダンスプロット 72 における瘤として、更に、図 12 のスミスチャート表現において余分な円として持ち込まれている。図 12 からは、余分な共振が 100 MHz より上で持ち込まれているものの、この單一リード線による代替方法は、52 MHz での共振を有する従来の設計より優れていることが確認できる。更に、より大きな結合バイパスキャパシタンスが存在することから、インピーダンスの大きさは、低い周波数において低減されている。

【0015】

従来のパワートランジスタ出力マッチング回路内に存在する既存の RF バイパスキャパシタに電源ビデオバイパスキャパシタネットワークが統合された RF 電力増幅器のいくつかの実施形態を示した。分路共振素子の総キャパシタンスは、これにより、RF 及びビデオ周波数の両方で機能する多重キャパシタネットワークの使用を介して、従来技術に比べて少なくとも十倍増加する。前述したように、本発明は、シリコン及び III - V 材料の両方で、FET 及びバイポーラトランジスタに応用可能であり、本発明は、単一のトランジスタ、或いは単一のパッケージ内で並列に動作する複数のトランジスタに応用可能である。 20

【0016】

以上、本発明について特定の実施形態を参考して説明してきたが、説明は、本発明の例示であり、本発明を限定するものとして解釈されるべきではない。他の様々な適用例及び変形例は、付記した特許請求の範囲によって画定される本発明の本来の趣旨及び範囲から逸脱することなく、当業者によって想到され得よう。 30

【図面の簡単な説明】

【0017】

【図 1A】パッケージに収納された RF パワートランジスタの斜視図である。

【図 1B】パッケージに収納された RF パワートランジスタの機能ブロック図である。

【図 2】従来技術による、DC 電源用のマッチング回路及びバイアスリード線 RF バイパス回路と共にプリント回路基板にマウントされた図 1 のパッケージに収納された RF トランジスタの機能ブロック図である。 40

【図 3】本発明の実施形態による、マッチング及びバイパス回路を備えたパッケージに収納された RF パワートランジスタの機能ブロック図である。

【図 4】本発明の別の実施形態による、マッチング及びバイパス回路を備えたパッケージに収納された RF パワートランジスタの機能ブロック図である。

【図 5A】本発明の一実施形態による、RF パワートランジスタの物理的及び電気的概略図である。

【図 5B】本発明の一実施形態による、RF パワートランジスタの物理的及び電気的概略図である。

【図 6A】本発明の別の実施形態による、RF パワートランジスタの物理的及び電気的概略図である。

【図 6B】本発明の別の実施形態による、RF パワートランジスタの物理的及び電気的概 50

略図である。

【図 7 A】本発明の別の実施形態による、RFパワートランジスタの物理的及び電気的概略図である。

【図 7 B】本発明の別の実施形態による、RFパワートランジスタの物理的及び電気的概略図である。

【図 8 A】本発明の別の実施形態による、RFパワートランジスタの物理的及び電気的概略図である。

【図 8 B】本発明の別の実施形態による、RFパワートランジスタの物理的及び電気的概略図である。

【図 9】従来のRFパワートランジスタ及び本発明の実施形態によるRFパワートランジスタでの周波数に対するインピーダンスをプロットしたグラフである。 10

【図 10】図9において使用したトランジスタでのスミスチャート上の複素インピーダンスを示す説明図である。

【図 11】従来のRFパワートランジスタ及び本発明の別の実施形態によるRFパワートランジスタでの周波数に対するインピーダンスをプロットしたグラフである。

【図 12】図11において使用したトランジスタでのスミスチャート上の複素インピーダンスを示す説明図である。

【図 1 A】

FIG. 1A

【図 2】

FIG. 2

【図 1 B】

FIG. 1B

【図3】

FIG. 3

【 図 4 】

FIG. 4

【 図 5 A 】

FIG. 5A

### 【図5B】

FIG. 5B

【図 6 A】

FIG. 6A

【図6B】

FIG. 6B

【図7A】

FIG. 7A

〔 図 7 B 〕

FIG. 7B

【 図 8 A 】

FIG. 84

【図 8 B】

FIG. 8B

【図 9】

FIG. 9

【図 10】

FIG. 10

【図 11】

FIG. 11

【図 12】

FIG. 12

---

フロントページの続き

(74)代理人 100094673

弁理士 林 銀三

(74)代理人 100091339

弁理士 清水 邦明

(74)代理人 100138346

弁理士 畑中 孝之

(74)代理人 100147658

弁理士 岩見 晶啓

(74)代理人 110000028

特許業務法人明成国際特許事務所

(72)発明者 クレッセンジ・ジュニア・エミル・ジェームズ

アメリカ合衆国 カリフォルニア州 93428-0277 カンブリア, アッシュビー・レーン,

640

審査官 日比野 隆治

(56)参考文献 特開2002-176368 (JP, A)

特開平02-033963 (JP, A)

特開2002-064345 (JP, A)

特開2001-024148 (JP, A)

特開平08-222657 (JP, A)

特開平03-283901 (JP, A)

特開昭58-131775 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/00-25/18

H01L 23/12