(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년05월17일

(11) 등록번호 10-1622061

(24) 등록일자 2016년05월11일

- (51) 국제특허분류(Int. Cl.)

*H01L 21/58* (2006.01) *H01L 21/677* (2006.01)

*H05K 13/04* (2006.01)

- (21) 출원번호 10-2014-7016746

- (22) 출원일자(국제) 2012년11월07일

심사청구일자 2014년06월18일

- (85) 번역문제출일자 2014년06월18일

- (65) 공개번호 10-2014-0103279

- (43) 공개일자 2014년08월26일

- (86) 국제출원번호 PCT/US2012/063990

- (87) 국제공개번호 WO 2013/074355

국제공개일자 2013년05월23일

- (30) 우선권주장

13/372,277 2012년02월13일 미국(US)

(뒷면에 계속)

- (56) 선행기술조사문헌

JP2002240943 A\*

US20050232728 A1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 20 항

심사관 : 오순영

(54) 발명의 명칭 마이크로 소자 이송 헤드

**(57) 요 약**

마이크로 소자 이송 헤드 및 헤드 어레이가 개시된다. 일 실시예에서, 마이크로 소자 이송 헤드는, 베이스 기판, 측벽들을 갖는 메사 구조체, 메사 구조체 위에 형성된 전극, 및 전극을 덮는 유전체 층을 포함한다. 캐리어 기판으로부터 마이크로 소자를 꺽업하고 수용 기판 상에 마이크로 소자를 릴리즈하기 위해 마이크로 소자 이송 헤드 및 헤드 어레이에 전압이 인가될 수 있다.

**대 표 도** - 도3

(72) 발명자

로우, 흥-파이 스티븐

미국 95054 캘리포니아주 산타 클라라 와이어트 드

라이브 1705

후, 신-후아

미국 95054 캘리포니아주 산타 클라라 와이어트 드

라이브 1705

(30) 우선권주장

13/372,292 2012년02월13일 미국(US)

13/372,310 2012년02월13일 미국(US)

61/561,706 2011년11월18일 미국(US)

61/594,919 2012년02월03일 미국(US)

61/597,109 2012년02월09일 미국(US)

## 명세서

### 청구범위

#### 청구항 1

정전기 이송 헤드(electrostatic transfer head)로서,

베이스 기판(base substrate);

상기 베이스 기판 상에 형성된 메사 구조체(mesa structure) - 상기 메사 구조체는 상기 정전기 이송 헤드에 대한 국소적인 접점(localized contact point)을 제공하기 위해 상기 베이스 기판으로부터 멀어지게 돌출하는 측벽들을 포함함 - ;

상기 메사 구조체를 덮는 유전체 층; 및

상기 베이스 기판 위에 형성되고 상기 메사 구조체를 둘러싸는 전도성 접지면(ground plane)

을 포함하는, 정전기 이송 헤드.

#### 청구항 2

제1항에 있어서, 상기 메사 구조체는 상기 베이스 기판과 함께 통합적으로 형성되는, 정전기 이송 헤드.

#### 청구항 3

제1항에 있어서, 상기 베이스 기판 및 상기 메사 구조체는 각각 실리콘을 포함하는, 정전기 이송 헤드.

#### 청구항 4

제1항에 있어서, 상기 메사 구조체의 상부 표면 위에 형성된 전극을 추가로 포함하며, 상기 유전체 층은 상기 전극을 덮는, 정전기 이송 헤드.

#### 청구항 5

제4항에 있어서, 상기 메사 구조체의 상기 상부 표면 상의 상기 전극으로부터 그리고 상기 메사 구조체의 측벽을 따라 이어지는 전극 리드(electrode lead)를 추가로 포함하는, 정전기 이송 헤드.

#### 청구항 6

제5항에 있어서, 상기 유전체 층은 상기 메사 구조체의 상기 측벽을 따라 상기 전극 리드를 덮는, 정전기 이송 헤드.

#### 청구항 7

제4항에 있어서, 상기 메사 구조체를 통하여 전극 리드에 상기 전극을 연결하는 비아(via)를 추가로 포함하는, 정전기 이송 헤드.

#### 청구항 8

제4항에 있어서, 상기 전극은 백금, 티타늄, 바나듐, 크롬, 지르코늄, 니오븀, 몰리브덴, 루테늄, 로듐, 하프늄, 탄탈, 텅스텐, 레늄, 오스뮴 또는 이리듐으로부터 선택되는 재료를 포함하는, 정전기 이송 헤드.

#### 청구항 9

제4항에 있어서, 상기 전극은 TiW를 포함하는, 정전기 이송 헤드.

#### 청구항 10

제1항에 있어서, 상기 유전체 층은  $Al_2O_3$  또는  $Ta_2O_5$ 로부터 선택되는 유전체 재료를 포함하는, 정전기 이송

헤드.

### 청구항 11

제1항에 있어서, 상기 메사 구조체의 상부 표면 상에 형성된 한 쌍의 전극을 추가로 포함하며, 상기 유전체 층은 상기 한 쌍의 전극을 덮는, 정전기 이송 헤드.

### 청구항 12

제11항에 있어서, 한 쌍의 전극 리드를 추가로 포함하며, 각각의 전극 리드는 상기 메사 구조체의 측벽을 따라 상기 메사 구조체의 상기 상부 표면 상의 대응하는 전극으로부터 이어지는, 정전기 이송 헤드.

### 청구항 13

제12항에 있어서, 상기 유전체 층은 상기 메사 구조체의 상기 측벽을 따라 상기 한 쌍의 전극 리드를 덮는, 정전기 이송 헤드.

### 청구항 14

제11항에 있어서, 상기 메사 구조체를 통하여 전극 리드에 상기 한 쌍의 전극 중 하나를 연결하는 비아를 추가로 포함하는, 정전기 이송 헤드.

### 청구항 15

정전기 이송 헤드 어레이로서,

베이스 기판;

상기 베이스 기판 상에 형성된 메사 구조체들의 어레이 - 각각의 메사 구조체는 각각의 정전기 이송 헤드에 대한 국소적인 접점을 제공하기 위해 상기 베이스 기판으로부터 멀어지게 돌출하는 측벽들을 포함함 -;

상기 메사 구조체들의 어레이를 덮는 유전체 층; 및

상기 베이스 기판 위에 형성되고 상기 메사 구조체들의 상기 각각을 둘러싸는 전도성 접지면을 포함하는, 정전기 이송 헤드 어레이.

### 청구항 16

제15항에 있어서, 각각의 메사 구조체는 상기 베이스 기판과 함께 통합적으로 형성되는, 정전기 이송 헤드 어레이.

### 청구항 17

제15항에 있어서, 상기 베이스 기판 및 각각의 메사 구조체는 각각 실리콘을 포함하는, 정전기 이송 헤드 어레이.

### 청구항 18

제15항에 있어서, 각각의 메사 구조체의 상부 표면 위에 형성된 전극을 추가로 포함하며, 상기 유전체 층은 각각의 전극을 덮는, 정전기 이송 헤드 어레이.

### 청구항 19

제18항에 있어서, 각각의 전극은 백금, 티타늄, 바나듐, 크롬, 지르코늄, 니오븀, 몰리브덴, 루테늄, 로듐, 하프늄, 탄탈, 텉스텐, 레늄, 오스뮴 또는 이리듐으로부터 선택되는 재료를 포함하는, 정전기 이송 헤드 어레이.

### 청구항 20

제15항에 있어서, 상기 유전체 층은  $Al_2O_3$  또는  $Ta_2O_5$ 로부터 선택되는 유전체 재료를 포함하는, 정전기 이송 헤드 어레이.

## 발명의 설명

### 기술 분야

#### [0001] 관련 출원

본 출원은 그 전문이 본 명세서에 참조로서 편입되는, 2011년 11월 18일에 출원된 미국 가특허 출원 제61/561,706호, 2012년 2월 3일에 출원된 미국 가특허 출원 제61/594,919호 및 2012년 2월 9일에 출원된 미국 가특허 출원 제61/597,109호에 대해 우선권의 이익을 주장한다.

#### [0003] 기술분야

본 발명은 마이크로 소자들에 관한 것이다. 본 발명의 더욱 구체적인 실시예들은 마이크로 소자 이송 헤드(micro device transfer head), 및 수용 기판(receiving substrate)으로 하나 이상의 마이크로 소자를 이송하는 방법에 관한 것이다.

### 배경 기술

[0005] 집적화 및 패키징 이슈들은 무선 주파수(RF) 미소 전자 기계 시스템(MEMS) 마이크로스위치, 발광 다이오드(LED) 디스플레이 시스템, 및 MEMS 또는 석영-기반 오실레이터와 같은 마이크로 소자들의 상업화에 대한 주요 장애요인들 중 하나이다.

[0006] 소자들의 이송을 위한 종래의 기술들은 이송 웨이퍼로부터 수용 웨이퍼로 웨이퍼 접합에 의한 이송을 포함한다. 하나의 그러한 구현예는 이송 웨이퍼로부터 수용 웨이퍼로의 소자들의 어레이의 접합 한 단계를 수반하는 "직접 인쇄(direct printing)"이고, 이후 이송 웨이퍼의 제거로 이어진다. 다른 이러한 구현예는 접합/접합해제의 두 단계들을 수반하는 "전사 인쇄(transfer printing)"이다. 전사 인쇄에서는, 이송 웨이퍼가 도너 웨이퍼(donor wafer)로부터 소자들의 어레이를 꺽업(pick up)하고, 이어서 소자들의 어레이를 수용 웨이퍼에 접합한 후, 이송 웨이퍼를 제거할 수 있다.

[0007] 이송 공정 중 소자가 선택적으로 접합 및 접합해제될 수 있는 일부 인쇄 공정 변형 형태가 개발되어 왔다. 전통적인 형태 및 변형 형태의 직접 인쇄 및 전사 인쇄 기술 둘 모두에서, 이송 웨이퍼는 소자를 수용 웨이퍼에 접합한 후에 소자로부터 접합해제된다. 또한, 소자들의 어레이를 갖는 전체 이송 웨이퍼는 이송 공정에 수반된다.

### 발명의 내용

[0008] 마이크로 소자 이송 헤드와 헤드 어레이, 및 수용 기판으로 하나 이상의 마이크로 소자를 이송하는 방법이 개시된다. 예를 들어, 수용 기판은, 디스플레이 기판, 조명 기판, 트랜지스터 또는 집적 회로(IC)와 같은 기능 소자를 갖춘 기판, 또는 금속 재분배선(redistribution line)을 갖춘 기판일 수 있지만, 이에 한정되지 않는다.

[0009] 일 실시예에서, 마이크로 소자 이송 헤드는, 베이스 기판(base substrate), 측벽들을 포함하는 메사 구조체(mesa structure), 메사 구조체 위에 형성된 적어도 하나의 전극, 및 전극을 덮는 유전체 층을 포함한다. 예를 들어, 마이크로 소자 이송 헤드는 모노폴라(monopolar) 또는 바이폴라(bipolar) 전극 구조를 포함할 수 있다. 메사 구조체는 베이스 기판과 별개로 또는 통합적으로 형성될 수 있다. 측벽들은 테이퍼지고(tapered) 베이스 기판으로부터 메사 구조체의 상부 표면으로 멀어지게 돌출될 수 있으며, 이때 전극은 상부 표면 상에 형성된다. 전극 리드는 베이스 기판의 배선과 접촉시키고 마이크로 소자 이송 헤드를 정전기 그리퍼 조립체(gripper assembly)의 작동 전자 장치에 연결하도록 전극으로부터 연장될 수 있다. 전극 리드들은 메사 구조체의 상부 표면 상의 전극으로부터 그리고 메사 구조체의 측벽을 따라 이어질 수 있다. 대신에 전극 리드는 메사 구조체 아래로 이어지고 메사 구조체를 통하여 전극으로 이어지는 비아에 연결될 수 있다.

[0010] 전극 및 전극 리드들은 부착된 유전체 층으로 덮일 수 있다. 유전체 층을 위한 적합한 재료들은 산화 알루미늄( $Al_2O_3$ ) 및 산화 탄탈( $Ta_2O_5$ )을 포함하지만, 이에 한정되지 않는다. 유전체 층이 부착되므로, 전극 및 전극 리드들은 높은 부착 온도를 견딜 수 있는 재료로 형성될 수 있고, 이는 백금과 같은 높은 용융 온도 금속 및 내화 금속들 또는 티타늄 텅스텐(TiW)과 같은 내화 금속 합금을 포함한다.

[0011] 일 실시예에서, 마이크로 소자를 이송하는 방법은 캐리어 기판에 연결된 마이크로 소자 위에 이송 헤드를 위치시키는 것을 포함한다. 마이크로 소자는 이송 헤드와 접촉되고, 마이크로 소자 상에 그립 압력(grip pressure)

e)을 생성하기 위해 이송 헤드 내의 전극에 전압이 인가된다. 이송 헤드는 마이크로 소자를 꾹업하고, 이어서 수용 기판 상에 마이크로 소자를 텔리즈(release)한다. 전압은 마이크로 소자를 이송 헤드와 접촉시키기 전에, 접촉시키는 동안 또는 접촉시킨 후에 인가될 수 있다. 전압은 정전류 전압 또는 교류 전류 전압일 수 있다. 일 실시예에서, 교류 전류 전압이 바이폴라 전극 구조에 인가된다. 일 실시예에서, 마이크로 소자를 꾹업하기 전이나 꾹업하는 동안에 마이크로 소자를 캐리어 기판에 연결하는 접합 층에 상 변화(phase change)를 일으키기 위해 작업이 추가로 수행된다.

[0012] 일 실시예에서, 접합 층은 마이크로 소자를 꾹업하기 전이나 꾹업하는 동안 고체에서 액체로 접합 층에 상 변화를 일으키기 위해 가열된다. 작업 조건들에 따라, 접합 층의 상당 부분이 마이크로 소자와 함께 꾹업되고 이송될 수 있다. 마이크로 소자 및 접합 층의 부분을 꾹업하고, 이송하며, 수용 기판과 접촉하고, 수용 기판 상에 텔리즈할 때 접합 층의 부분의 상(phase)을 제어하기 위해 다양한 작업들이 수행될 수 있다. 예를 들어, 마이크로 소자와 함께 꾹업된 접합 층의 부분은 수용 기판을 접촉할 때 그리고 수용 기판 상에 텔리즈 작업 동안 액체 상태로 유지될 수 있다. 다른 실시예에서, 접합 층의 부분은 꾹업된 후 고상(solid phase)으로 냉각되도록 허용될 수 있다. 예를 들어, 접합 층의 상기 부분은 수용 기판과 접촉하기 전에 또는 접촉하는 작업 중 고상일 수 있고, 텔리즈 작업 중 액체 상태로 다시 용융될 수 있다. 다양한 온도 및 재료 상 사이클(phase cycle)이 본 발명의 실시예들에 따라 수행될 수 있다.

[0013] 일 실시예에서, 마이크로 소자들의 어레이를 이송하는 방법은 마이크로 소자들의 어레이 위에 이송 헤드들의 어레이를 위치시키는 것을 포함한다. 마이크로 소자들의 어레이는 이송 헤드들의 어레이와 접촉되고, 전압이 이송 헤드들의 어레이의 일부분에 선택적으로 인가된다. 전압을 선택적으로 인가하는 것은 어레이 내의 모든 이송 헤드들에, 또는 어레이 내의 모든 이송 헤드들보다 적은 이송 헤드들에 대응하는 일부분에 전압을 인가하는 것을 포함할 수 있다. 이어서, 마이크로 소자들의 어레이의 대응하는 부분은 이송 헤드들의 어레이의 부분으로 꾹업되고, 마이크로 소자들의 어레이의 상기 부분은 적어도 하나의 수용 기판 상에 선택적으로 텔리즈된다. 일 실시예에서, 이송 헤드들의 어레이는 이송 헤드들이나 마이크로 소자들의 접촉 표면 상에 존재할 수 있는 임의의 입자를 제거하기 위해 접촉하는 동안 마이크로 소자들의 어레이 상에서 문질러질 수 있다. 일 실시예에서, 상 변화는 마이크로 소자들의 어레이를 꾹업하기 전에 캐리어 기판에 마이크로 소자들의 어레이를 연결하는 측방향으로 분리된 위치들의 접합 층의 어레이에 일어난다.

[0014] 일 실시예에서, 마이크로 소자 이송 헤드 어레이를 제조하는 방법은 베이스 기판 상에 메사 구조체들의 어레이를 형성하는 것을 포함하며, 각 메사 구조체는 측벽들을 포함한다. 개별 전극이 각각의 메사 구조체 위에 형성되고, 유전체 층이 메사 구조체들의 어레이 및 각각의 전극 위에 부착된다. 일 실시예에서, 유전체 층은 원자층 증착(ALD)에 의해 부착되며, 핀-홀이 없을(pin-hole free) 수 있다. 유전체 층은 하나 또는 다수의 유전체 층을 포함할 수 있다. 컨포멀 패시베이션 층(conformal passivation layer)은 각각의 대응하는 메사 구조체 위에 개별 전극을 형성하기 전에 메사 구조체들의 어레이 및 베이스 기판 위에 선택적으로 성장하거나 부착될 수 있다. 일 실시예에서, 전도성 접지면은 유전체 층 위에 형성되고, 각각의 메사 구조체를 둘러싼다.

## 도면의 간단한 설명

[0015] <도 1>

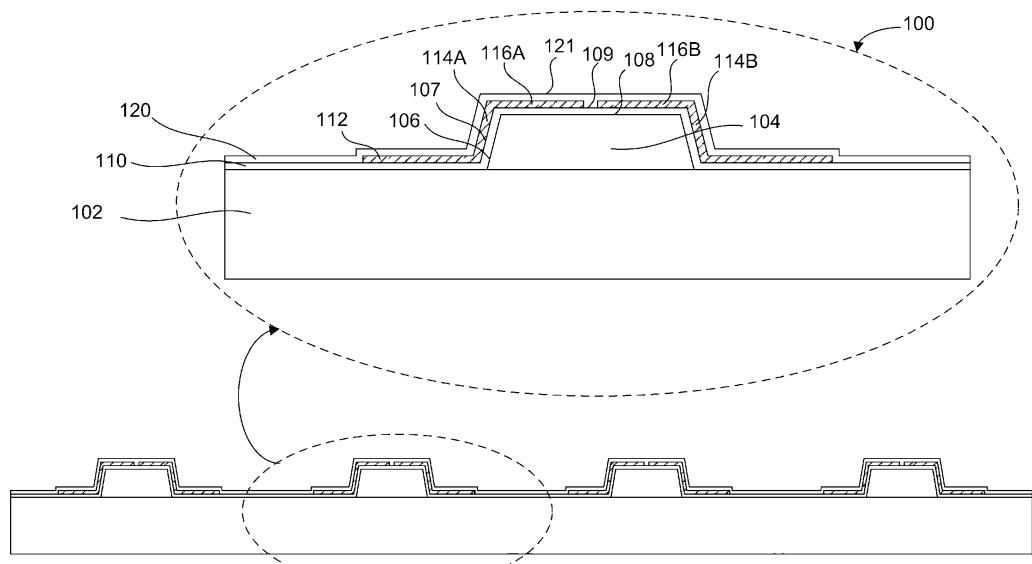

도 1은 본 발명의 일 실시예에 따른 모노폴라 마이크로 소자 이송 헤드의 측단면도이다.

<도 2>

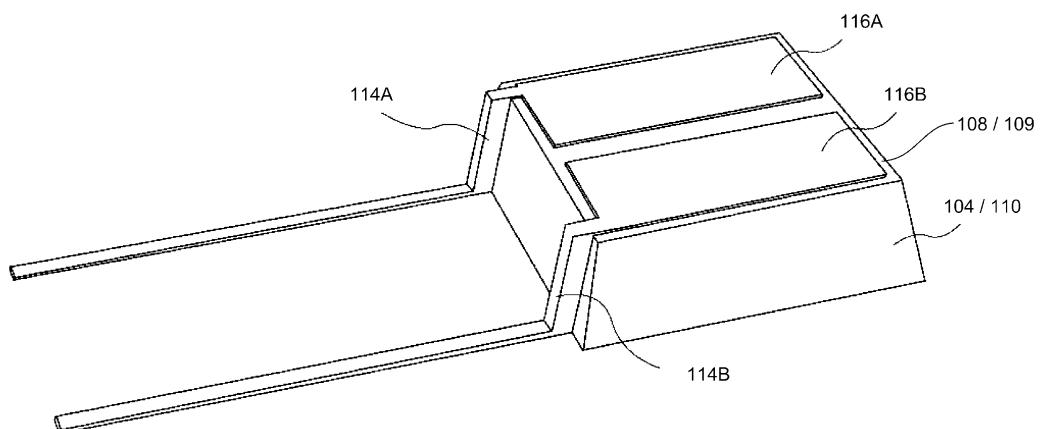

도 2는 본 발명의 일 실시예에 따른 모노폴라 마이크로 소자 이송 헤드의 등각도이다.

<도 3>

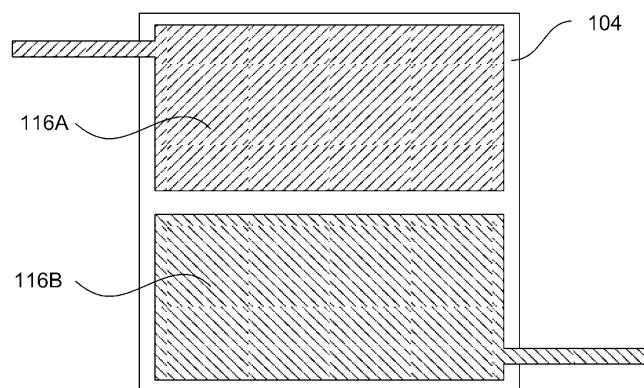

도 3은 본 발명의 일 실시예에 따른 바이폴라 마이크로 소자 이송 헤드의 측단면도이다.

<도 4>

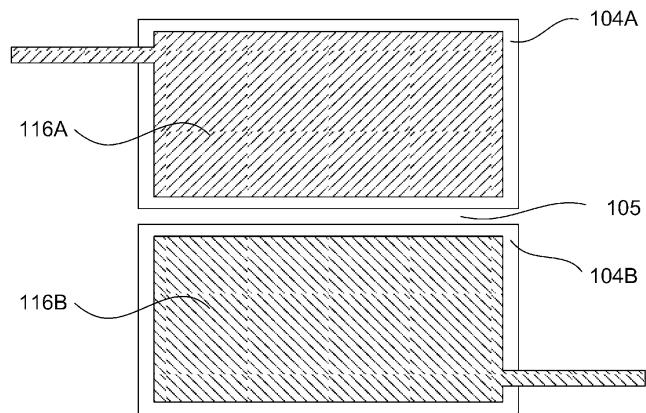

도 4는 본 발명의 일 실시예에 따른 바이폴라 마이크로 소자 이송 헤드의 등각도이다.

<도 5 및 도 6>

도 5 및 도 6은 본 발명의 일 실시예에 따른 바이폴라 마이크로 소자 이송 헤드의 평면도이다.

<도 7>

도 7은 본 발명의 일 실시예에 따른 전도성 비아들을 포함하는 바이폴라 마이크로 소자 이송 헤드의 등각도이다.

<도 8>

도 8은 본 발명의 일 실시예에 따른 바이폴라 마이크로 소자 이송 헤드 어레이의 등각도이다.

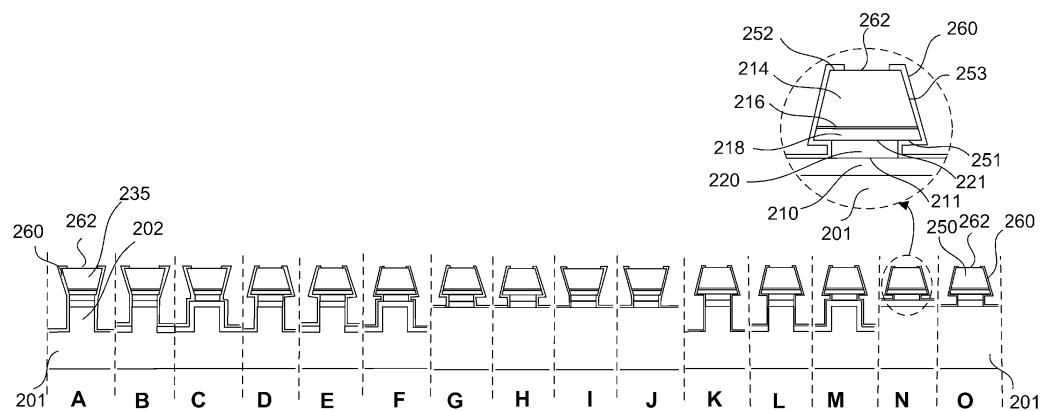

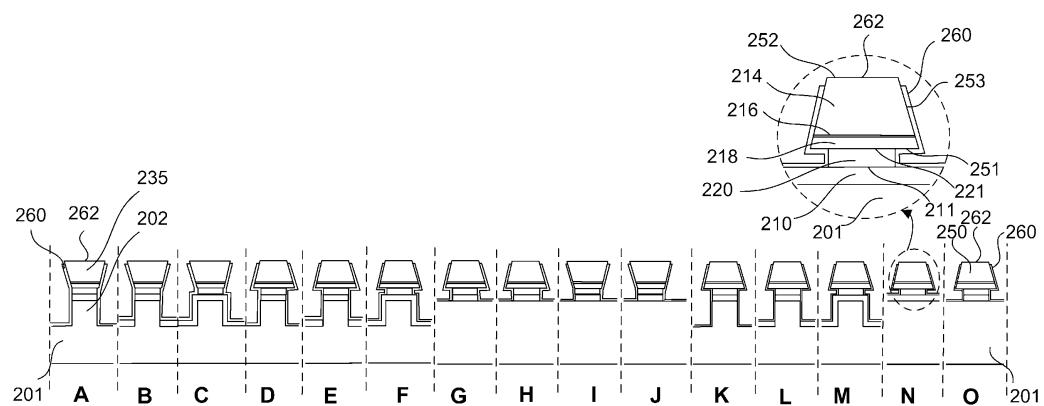

<도 9>

도 9는 본 발명의 일 실시예에 따른 전도성 접지면을 포함하는 바이폴라 마이크로 소자 이송 헤드 어레이의 등각도이다.

<도 10>

도 10은 본 발명의 일 실시예에 따른 전도성 접지면을 포함하는 바이폴라 마이크로 소자 이송 헤드 어레이의 측단면도이다.

<도 11>

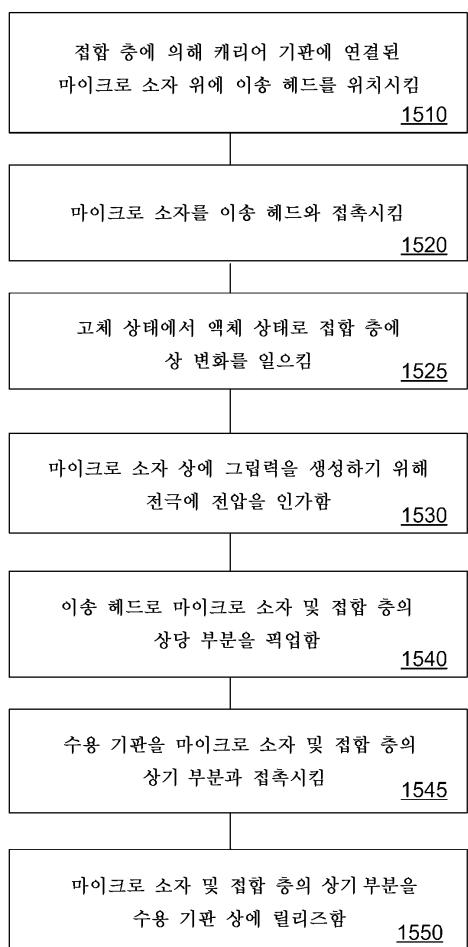

도 11은 본 발명의 일 실시예에 따른 캐리어 기판으로부터 수용 기판으로 마이크로 소자를 꾹업하고 이송하는 방법을 예시한 흐름도이다.

<도 12>

도 12는 본 발명의 일 실시예에 따라 바이폴라 전극에 걸쳐서 인가된 교류 전압 개략도이다.

<도 13>

도 13은 본 발명의 일 실시예에 따라 바이폴라 전극에 인가된 정전압의 개략도이다.

<도 14>

도 14는 본 발명의 일 실시예에 따라 모노폴라 전극에 인가된 정전압의 개략도이다.

<도 15>

도 15는 본 발명의 일 실시예에 따른 캐리어 기판으로부터 수용 기판으로 마이크로 소자를 꾹업하고 이송하는 방법을 예시하는 흐름도이다.

<도 16>

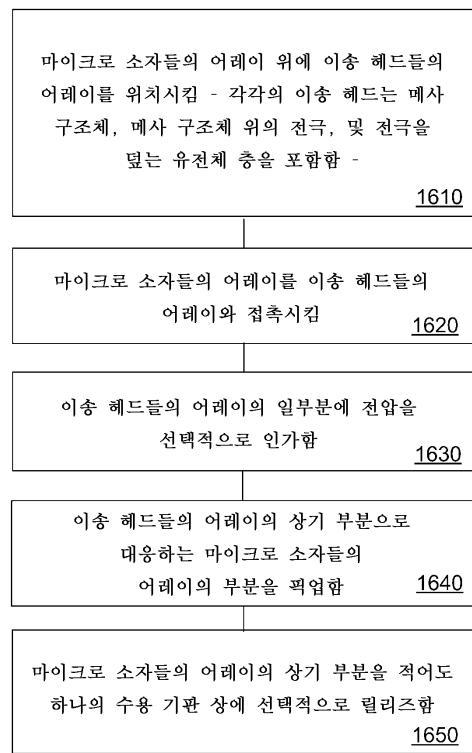

도 16은 본 발명의 일 실시예에 따른 캐리어 기판으로부터 적어도 하나의 수용 기판으로 마이크로 소자들의 어레이를 꾹업하고 이송하는 방법을 예시한 흐름도이다.

<도 17>

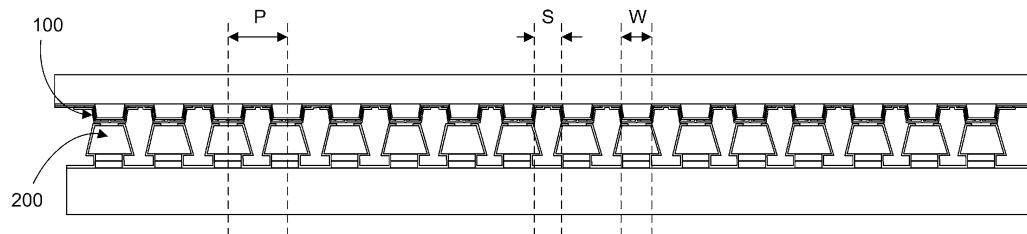

도 17은 본 발명의 일 실시예에 따른 마이크로 LED 소자들의 어레이와 접촉하는 마이크로 소자 이송 헤드들의 어레이의 측단면도이다.

<도 18>

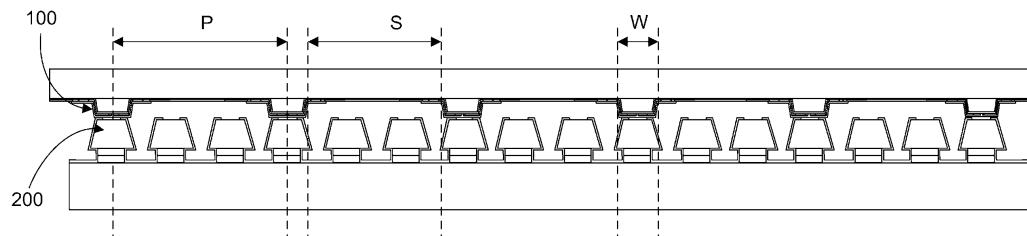

도 18은 본 발명의 일 실시예에 따른 마이크로 LED 소자들의 어레이와 접촉하는 마이크로 소자 이송 헤드들의 어레이의 측단면도이다.

<도 19>

도 19는 본 발명의 일 실시예에 따른 마이크로 LED 소자들의 어레이를 꾹업하는 마이크로 소자 이송 헤드들의 어레이의 측단면도이다.

<도 20>

도 20은 본 발명의 일 실시예에 따른 마이크로 LED 소자들의 어레이의 일부분을 꾹업하는 마이크로 소자 이송 헤드들의 어레이의 측단면도이다.

<도 21>

도 21은 본 발명의 일 실시예에 따른 수용 기판 위에 위치된 마이크로 LED 소자들의 어레이를 갖는 마이크로 소

자 이송 헤드들의 어레이의 측단면도이다.

<도 22>

도 22는 본 발명의 일 실시예에 따른 수용 기판 상에 선택적으로 릴리즈되는 마이크로 소자의 측단면도이다.

<도 23>

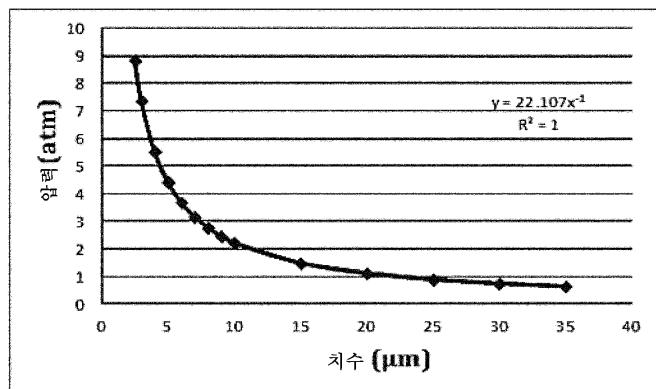

도 23은 본 발명의 일 실시예에 따른 다양한 치수의 마이크로 소자를 꾹업하기 위해 표면 장력을 극복하는 데 요구되는 압력을 나타낸 그래프 도면이다.

<도 24>

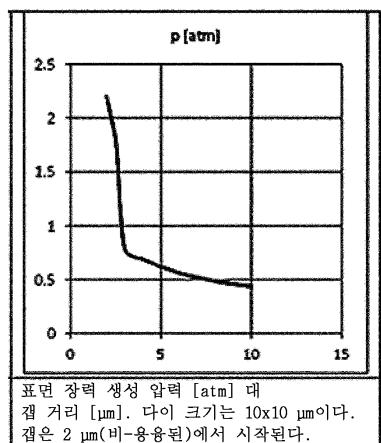

도 24는 본 발명의 일 실시예에 따른 꾹업 작업 중 생성되는 증가하는 갭 거리와 표면 장력 사이의 관계의 그래프 도면이다.

<도 25>

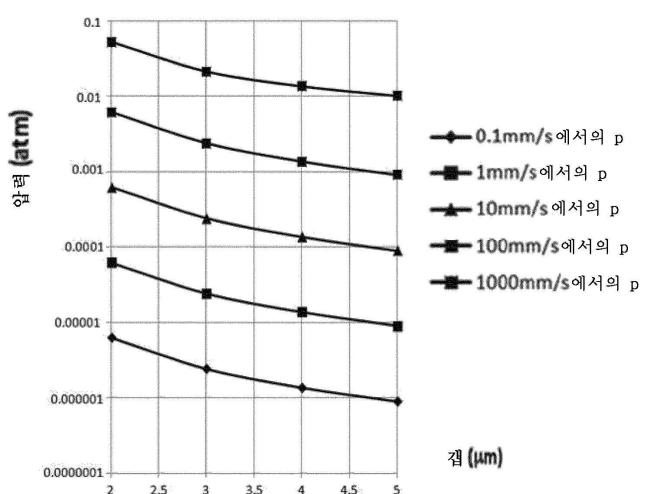

도 25는 본 발명의 일 실시예에 따른 다양한 견인 속도(pull rate)로 꾹업 작업 중 생성된 증가하는 갭 거리와 점성력 압력 사이의 관계의 그래프 도면이다.

<도 26>

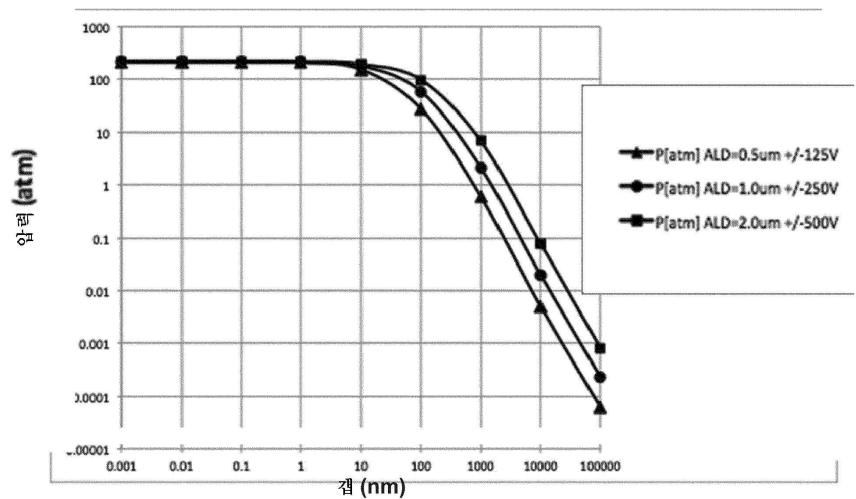

도 26은 본 발명의 일 실시예에 따른 이송 헤드가 마이크로 소자로부터 인출됨에 따라 마이크로 소자 상에 이송 헤드에 의해 가해지는 그립 압력을 나타낸 모델링 분석에 의해 얻어진 그래프 도면이다.

<도 27>

도 27은 본 발명의 일 실시예에 따른 마이크로 p-n 다이오드의 상부 표면보다 작은 폭을 갖는 접촉 개구들을 포함하는 다양한 마이크로 LED 구조체들의 측단면도이다.

<도 28>

도 28은 본 발명의 일 실시예에 따른 마이크로 p-n 다이오드의 상부 표면보다 큰 폭을 갖는 접촉 개구들을 포함하는 다양한 마이크로 LED 구조체들의 측단면도이다.

<도 29>

도 29는 본 발명의 일 실시예에 따른 마이크로 p-n 다이오드의 상부 표면과 동일한 폭을 갖는 접촉 개구들을 포함하는 다양한 마이크로 LED 구조체들의 측단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0016] 본 발명의 실시예들은 마이크로 소자 이송 헤드와 헤드 어레이, 및 마이크로 소자와 마이크로 소자들의 어레이를 수용 기판으로 이송하는 방법을 기술한다. 예를 들어, 수용 기판은, 디스플레이 기판, 조명 기판, 트랜지스터 또는 집적 회로(IC)와 같은 기능 소자를 갖춘 기판, 또는 금속 재분배선(redistribution line)을 갖춘 기판일 수 있지만, 이에 한정되지 않는다. 일부 실시예에서, 본 명세서에 기술된 마이크로 소자들 및 마이크로 소자들의 어레이는 도 27 내지 도 29에 예시된 임의의 마이크로 LED 소자 구조체들일 수 있고, 관련된 미국 가출원 제61/561,706호 및 미국 가출원 제61/594,919호에 기술된 것들일 수 있다. 본 발명의 일부 실시예가 마이크로 LED들에 관해 특정하여 기술되지만, 본 발명의 실시예들은 그렇게 한정되지 않고 소정 실시예들은 또한 다이오드, 트랜지스터, IC 및 MEMS와 같은 기타 마이크로 소자들에 적용가능할 수 있다는 것이 인식되어야 한다.

[0017] 다양한 실시예에서, 도면을 참조하여 기술된다. 그러나, 소정 실시예들은 이들 특정 세부 사항 중 하나 이상 없이, 또는 다른 알려진 방법 및 구성과 조합되어 실시될 수 있다. 하기의 기재에서, 본 발명의 완전한 이해를 제공하기 위해 특정 구성, 치수 및 공정 등과 같은 많은 특정 세부 사항이 언급된다. 다른 경우에, 잘 알려진 반도체 공정 및 제조 기술은 본 발명을 불필요하게 불명료하게 하지 않기 위해 특별히 상세히 기술되지 않았다. 본 명세서 전반에 걸쳐 "하나의 실시예", "일 실시예" 등에 대한 언급은 그러한 실시예와 관련되어 기술되는 특정 특징, 구조, 구성 또는 특성이 본 발명의 적어도 하나의 실시예에 포함됨을 의미한다. 따라서, 본 명세서 전반에 걸쳐 다양한 곳에서 어구 "하나의 실시예에서", "일 실시예" 등의 출현은 반드시 본 발명의 동일한 실시예를 가리키지는 않는다. 또한, 특정 특징, 구조, 구성 또는 특성은 하나 이상의 실시예에서 적절한 방식으로 조합될 수 있다.

- [0018] 본 명세서에 사용되는 바와 같은 용어 "위에", "에", "사이의" 및 "상의"는 하나의 층의 다른 층에 대한 상대 위치를 지칭할 수 있다. 다른 층 "위에" 또는 "상의" 또는 다른 층 "에" 접합되는 하나의 층은 다른 층과 직접 접촉할 수 있거나 하나 이상의 개재하는 층을 구비할 수 있다. 층들 "사이의" 하나의 층은 그러한 층들과 직접 접촉할 수 있거나, 하나 이상의 개재하는 층을 구비할 수 있다.

- [0019] 본 명세서에 사용되는 바와 같은 용어 "마이크로" 소자 또는 "마이크로" LED 구조체는 본 발명의 실시예에 따른 소정 소자 또는 구조체의 서술적인 크기를 지칭할 수 있다. 본 명세서에 사용되는 바와 같이, 용어 "마이크로" 소자 또는 구조체는 1 내지 100  $\mu\text{m}$ 의 스케일을 가리키도록 의도된다. 그러나, 본 발명의 실시예가 반드시 그렇게 한정되지는 않으며, 실시예의 소정 양태들이 보다 큰 그리고 가능하게는 보다 작은 크기 스케일로 적용가능 할 수 있다는 것이 인식되어야 한다.

- [0020] 일 양태에서, 본 발명의 실시예들은 이송 헤드들의 어레이를 이용하여 미리 제조된 마이크로 소자들의 어레이를 대량 이송하는 방법을 기술한다. 예를 들어, 미리 제조된 마이크로 소자들은 발광용 LED, 로직 및 메모리용 실리콘 IC, 및 무선 주파수(RF) 통신용 갈륨 비소(GaAs) 회로를 들 수 있으나 이에 한정되지 않는 특정 기능을 가질 수 있다. 일부 실시예에서, 핀업할 준비가 되어 있는 마이크로 LED 소자들의 어레이는  $10 \mu\text{m} \times 10 \mu\text{m}$  피치, 또는  $5 \mu\text{m} \times 5 \mu\text{m}$  피치를 갖는 것으로서 기술된다. 이러한 밀도에서, 15.2 cm (6 인치) 기판은, 예를 들어,  $10 \mu\text{m} \times 10 \mu\text{m}$  피치를 갖는 대략 1억 6천 5백만 개의 마이크로 LED 소자들, 또는  $5 \mu\text{m} \times 5 \mu\text{m}$  피치를 갖는 대략 6억 6천만 개의 마이크로 LED 소자들을 수용할 수 있다. 대응하는 마이크로 LED 소자들의 어레이의 피치를 매칭하는 이송 헤드들의 어레이를 포함하는 이송 툴은 수용 기판으로 마이크로 LED 소자들의 어레이를 핀업하고 이송하는 데 사용될 수 있다. 이 방식으로, 마이크로 LED 소자들을 마이크로 디스플레이에서 대면적 디스플레이에 이르는 임의의 크기의 기판을 비롯한 이종 접착 시스템 내에 높은 이송 속도로 통합하고 조립하는 것이 가능하다. 예를 들어, 마이크로 소자 이송 헤드들의  $1 \text{ cm} \times 1 \text{ cm}$  어레이가 100,000개 초과의 마이크로 소자를 핀업하고 이송할 수 있으며, 마이크로 소자 이송 헤드들의 어레이가 더 클수록 더 많은 마이크로 소자들을 이송할 수 있다. 이송 헤드들의 어레이 내의 각각의 이송 헤드는 또한 독립적으로 제어가능할 수 있으며, 이는 마이크로 소자들의 선택적인 핀업 및 릴리즈를 가능하게 한다.

- [0021] 일 양태에서, 특정 이론으로 한정됨이 없이, 본 발명의 실시예는 마이크로 소자들을 핀업하기 위해 반대 전하들의 인력을 사용하는 정전기 그리퍼의 원리에 따라 동작하는 마이크로 소자 이송 헤드들 및 헤드 어레이들을 기술한다. 본 발명의 실시예에 따르면, 마이크로 소자 상에 그립력(grip force)을 생성하여 마이크로 소자를 핀업하기 위해 마이크로 소자 이송 헤드에 풀인 전압(pull-in voltage)이 인가된다. 그립력은 하전된 판 면적에 비례하며, 따라서 압력으로 계산된다. 이상적인 정전기 이론에 따르면, 모노폴라 전극과 전도성 기판 사이의 비-전도성 유전체 층은 다음의 방정식 (1)에서 퍼스칼(Pa) 단위의 그립 압력을 산출한다:

- $$P = [\varepsilon_0 / 2] [V \varepsilon_r / d]^2 \quad \text{--- (1)}$$

- [0022] 여기에서,  $\varepsilon_0 = 8.85 \cdot 10^{-12}$ ,  $V$  = 볼트(V) 단위의 전극-기판 전압,  $\varepsilon_r$  = 유전 상수, 및  $d$  = 미터(m) 단위의 유전체 두께이다. 두 그립 전극을 사용하는 바이폴라 그리퍼의 경우에, 위의 방정식에서 전압(V)은 전극 A와 B 사이의 전압의 절반, 즉  $[V_A - V_B] / 2$ 이다. 기판 전위는 평균 전위, 즉  $[V_A = V_B]/2$ 에 중심 설정된다. 이러한 평균은  $V_A = [-V_B]$ 인 경우에 일반적으로 0이다.

- [0023] 일 양태에서, 본 발명의 실시예들은 소정 처리 및 취급 작업들 동안 캐리어 기판 상의 마이크로 소자를 유지할 수 있는 접합층을 기술하고, 상 변화를 겪으면, 핀업 작업 중 마이크로 소자가 그 위에 유지될 수 있지만 또한 그로부터 용이하게 릴리즈될 수 있는 매체를 제공한다. 예를 들어, 접합 층은 재용융가능하거나 리플로우(reflow)가능할 수 있어, 접합 층이 핀업 작업 이전에 또는 핀업 작업 중 고체 상태에서 액체 상태로 상 변화를 겪게 한다. 액체 상태에서, 접합 층은 마이크로 소자를 캐리어 기판 상의 적소에 유지시킴과 동시에 또한 마이크로 소자가 그것으로부터 쉽게 릴리즈될 수 있는 매체를 제공할 수 있다. 특정 이론으로 한정됨이 없이, 캐리어 기판으로부터 마이크로 소자를 핀업하는 데 필요한 그립 압력을 결정함에 있어서, 그립 압력은 마이크로 소자를 캐리어 기판에 유지시키는 힘을 초과해야 하는데, 이러한 힘에는 표면 장력, 모세관력, 점성 효과, 탄성 복원력, 반 데르 발스 힘, 정지 마찰력(stiction) 및 중력을 포함될 수 있지만, 이에 한정되지 않는다.

- [0024] 본 발명의 실시예에 따르면, 마이크로 소자의 치수가 소정 범위 아래로 감소될 때, 마이크로 소자를 캐리어 기판에 유지시키는 액체 접합 층의 표면 장력이 마이크로 소자를 유지시키는 다른 힘에 비해 우세해질 수 있다. 도 23은 156.7 °C의 용융 온도에서 표면 장력이 560 mN/m인 액체 인듐(In) 접합 층임을 가정하여, 다양한 치수

의 마이크로 소자를 꾹업하기 위해 표면 장력을 극복하는 데 필요한 압력을 나타낸 모델링 분석에 의해 얻어진 일 실시예의 그래프 도면이다. 예를 들어, 도 23을 참조하면, 예시적인  $10 \mu\text{m} \times 10 \mu\text{m}$  폭의 마이크로 소자가  $156.7^\circ\text{C}$ 의 자신의 용융 온도에서 액체 표면 장력이  $560 \text{ mN/m}$ 인 인듐 접합 층에 의해 대략  $222.9 \text{ kPa}$ ( $2.2 \text{ atm}$ )의 표면 장력 압력으로 캐리어 기판 상에 유지된다. 이는 중력으로 인한 압력보다 상당히 큰데, 이때 중력으로 인한 압력은 예시적인  $10 \mu\text{m} \times 10 \mu\text{m}$  폭  $\times 3 \mu\text{m}$  높이의 질화갈륨(GaN) 조각의 경우 대략  $0.18 \text{ Pa}$ ( $1.8 \times 10^{-6} \text{ atm}$ )이다.

[0026] 표면 장력 압력과 접성 효과는 또한 꾹업 작업 중 동적일 수 있다. 도 24는 용융된 인듐(In) 접합 층으로 캐리어 기판 상에 유지된 예시적인  $10 \mu\text{m} \times 10 \mu\text{m}$  폭의 마이크로 소자의 꾹업 작업 중 생성된 증가하는 갭 거리와 표면 장력의 관계를 나타낸 모델링 분석에 의해 얻어진 일 실시예의 그래프 도면이다. 도 24에서 지칭되는 갭 거리는 마이크로 소자의 저부와 캐리어 기판 사이의 거리이고, In 접합 층의 비-용융된 두께에 해당하는  $2 \mu\text{m}$ 에서 시작된다. 도 24에 예시된 바와 같이,  $222.9 \text{ kPa}$ ( $2.2 \text{ atm}$ )의 표면 장력 압력이 꾹업 작업 시작시의 그립 압력에 의해 초기에 극복된다. 이어서, 마이크로 소자가 캐리어 기판으로부터 들어올려짐에 따라, 표면 장력이 급속히 줄어들고, 이때 마이크로 소자가 캐리어 기판으로부터 더욱 멀어지게 들어올려짐에 따라 압력은 평준화된다.

[0027] 도 25는 용융된 인듐(In) 접합 층으로 캐리어 기판 상에 유지된 예시적인  $10 \mu\text{m} \times 10 \mu\text{m}$  마이크로 소자에 대한 다양한 견인 속도로 꾹업 작업 중 생성된 증가하는 갭 거리( $\mu\text{m}$ )와 접성력 압력( $\text{atm}$ )의 관계를 나타낸 모델링 분석에 의해 얻어진 일 실시예의 그래프 도면이다. 도 25에서 지칭되는 갭 거리는 마이크로 소자의 저부와 캐리어 기판 사이의 거리이고, In 접합 층의 비-용융된 두께에 해당하는  $2 \mu\text{m}$ 에서 시작된다. 예시된 바와 같이, 접성력 압력은  $0.1 \text{ mm/s}$ 와 같은 보다 느린 들어올림 속도보다  $1,000 \text{ mm/s}$ 와 같은 보다 빠른 들어올림 속도 중에 더욱 명백하다. 그렇지만, 도 25에 예시된 예시적인 들어올림 속도를 사용하는 접성 효과로부터 생성된 압력은 도 24에 예시된 생성된 표면 장력 압력보다 상당히 작으며, 이는 표면 장력 압력이 꾹업 작업 중 그립 압력에 의해 극복되어야 하는 지배적인 압력임을 말한다.

[0028] 크기(g)의 에어 갭(air gap)이 마이크로 소자 이송 헤드의 유전체 층과 마이크로 소자의 상부 전도성 표면 사이에 존재하는 경우, 방정식 (2)에서 그립 압력은 다음과 같다:

$$P = [\varepsilon_0 / 2] [V \varepsilon_r / (d + \varepsilon_r g)]^2 \quad \text{--- (2)}$$

[0030] 미립자 오염, 휨(warpage), 및 이송 헤드 표면 또는 마이크로 소자 표면의 오정렬(misalignment), 또는 이송 헤드 또는 마이크로 소자 상에의 추가 층, 예컨대 마이크로 소자의 상부 전도성 표면 주위의 컨포멀 유전체 장벽 층의 립(lip)의 존재를 포함하지만 이로 한정되지 않는 다양한 원인으로 인해 에어 갭이 존재할 수 있다는 것이 고려된다. 일 실시예에서, 컨포멀 유전체 장벽 층의 립이 접촉 개구가 형성되는 에어 갭을 생성할 수 있고, 립이 존재하는 이송 헤드의 유전체 층의 유효 두께를 증가시킬 수 있다.

[0031] 위의 방정식 (1) 및 (2)로부터 보여지는 바와 같이, 꾹업하고자 하는 마이크로 소자와 마이크로 소자 이송 헤드 사이에 에어 갭이 존재하지 않는 경우에 보다 낮은 전압이 사용될 수 있다. 그러나, 에어 갭이 존재할 때, 이는 공기 커패시턴스가 유전체 층 커패시턴스에 필적할 수 있는 적렬 커패시턴스를 제공한다. 꾹업하고자 하는 대응하는 마이크로 소자들의 어레이 위의 마이크로 소자 이송 헤드들의 어레이 중 임의의 어레이 사이의 공기 커패시턴스의 가능성을 보상하기 위하여, 더 높은 작동 전압, 유전체 재료에 대한 더 높은 유전 상수, 또는 더 얇은 유전체 재료가 사용되어 전계(electric field)를 최대화할 수 있다. 그러나, 보다 높은 전계의 사용은 있을 수 있는 유전 파괴(dielectric breakdown)와 아킹(arcing)으로 인해 제한을 갖는다.

[0032] 도 26은 증가하는 에어 갭 크기에 해당하는, 이송 헤드가 마이크로 소자의 상부 전도성 표면으로부터 인출됨에 따라 마이크로 소자 상에 이송 헤드에 의해 가해지는 그립 압력을 나타낸 모델링 분석에 의해 얻어진 일 실시예의 그래프 도면이다. 상이한 선은 이송 헤드 상의  $0.5 \mu\text{m}$  내지  $2.0 \mu\text{m}$ 의 상이한  $\text{Ta}_2\text{O}_5$  유전체 층 두께에 해당하며, 이때 전계는 일정하게 유지된다. 예시된 바와 같이, 이들 조건에서 에어 갭 크기가 대략  $1 \text{ nm}$ ( $0.001 \mu\text{m}$ )의 미만에서, 그리고 일부 조건의 경우에는 심지어  $10 \text{ nm}$ ( $0.01 \mu\text{m}$ )만큼이나 높은 정도에서도 그립 압력에 대한 어떠한 주목할 만한 영향도 관찰되지 않는다. 그러나, 허용가능한 에어 갭이 조건을 변화시킴으로써 증가되거나 감소될 수 있다는 것이 인식되어야 한다. 따라서, 본 발명의 일부 실시예에 따르면, 꾹업 작업 중 소정 양의 에어 갭 허용 오차가 가능하고, 마이크로 소자 이송 헤드 및 마이크로 소자의 상부 전도성 표면과의 실제 접촉이 필요하지 않을 수 있다.

[0033] 이제 캐리어 기판으로부터 마이크로 소자를 꽂업하는 데 요구되는 그립 압력이 (에어 캡으로 인한 임의의 압력 감소뿐만 아니라) 마이크로 소자를 캐리어 기판 상에 유지시키는 압력의 합을 초과하여야 한다고 가정하면, 작동 전압, 유전 상수 및 마이크로 소자 이송 헤드 내의 유전체 재료의 유전체 두께의 상호 관계를 그립 압력 방정식을 풀어 도출하는 것이 가능하다. 명확성을 위하여, 에어 캡 거리가 0이라고 가정하면, 모노폴라 전극에 대해 이는 다음과 같이 된다:

[0034]  $\text{sqrt} (P*2 / \epsilon_r) = V \epsilon_r / d \quad \text{--- (3)}$

[0035] 본 발명의 일 실시예에 따른 그립 압력, 전압, 유전 상수 및 유전체 두께의 상호 의존성을 예시하기 위해 25 V 내지 300 V의 작동 전압 사이에서  $\text{Al}_2\text{O}_3$  및  $\text{Ta}_2\text{O}_5$  유전체 재료에 대하여 202650 Pa (2 atm) 및 2026500 Pa (20 atm)의 원하는 그립 압력에 대한 계산된 유전체 두께 값의 예시적인 범위가 표 1에 제공된다. 제공된 유전 상수는 근사치이며, 형성 방식에 따라 값이 변할 수 있는 것이 이해되어야 한다.

### 표 1

| 유전체 재료                      | 전압 (V) | 유전 상수, $\epsilon_r$ (Hz - MHz 범위) | 유전체 두께, d (마이크로미터) |

|-----------------------------|--------|-----------------------------------|--------------------|

| 그립 압력 = 202.65 kPa (2 atm)  |        |                                   |                    |

| $\text{Al}_2\text{O}_3$     | 25     | 9.8                               | 1.1                |

| $\text{Al}_2\text{O}_3$     | 100    | 9.8                               | 4.6                |

| $\text{Al}_2\text{O}_3$     | 300    | 9.8                               | 13.7               |

| $\text{Ta}_2\text{O}_5$     | 25     | 25                                | 2.9                |

| $\text{Ta}_2\text{O}_5$     | 100    | 25                                | 11.7               |

| $\text{Ta}_2\text{O}_5$     | 300    | 25                                | 35.0               |

| 그립 압력 = 2026.5 kPa (20 atm) |        |                                   |                    |

| $\text{Al}_2\text{O}_3$     | 25     | 9.8                               | 0.4                |

| $\text{Al}_2\text{O}_3$     | 100    | 9.8                               | 1.4                |

| $\text{Al}_2\text{O}_3$     | 300    | 9.8                               | 4.3                |

| $\text{Ta}_2\text{O}_5$     | 25     | 25                                | 0.9                |

| $\text{Ta}_2\text{O}_5$     | 100    | 25                                | 3.7                |

| $\text{Ta}_2\text{O}_5$     | 300    | 25                                | 11.1               |

[0036]

[0037] 그립 압력이 유전체 두께의 역제곱에 비례하기 때문에, 표 1의 계산된 유전체 두께는 설정 작동 전압으로 필요한 그립 압력을 달성하도록 형성될 수 있는 최대 두께를 나타낸다. 표 1에 제공된 것보다 작은 두께는 설정 작동 전압에서 보다 높은 그립 압력을 생성할 수 있지만, 더 얇은 두께는 유전체 층에 걸쳐서 인가되는 전계를 증가시키며, 이는 유전체 재료가 단락 없이 인가되는 전계를 견디기에 충분한 유전 강도(dielectric strength)를 가질 것을 요구한다. 표 1에 제공된 그립 압력, 전압, 유전 상수 및 유전체 두께 값이 사실상 예시적이고, 본 발명의 실시예에 따른 마이크로 소자 이송 헤드의 작동 범위에 대한 기초를 제공하기 위해 제공된다는 것이 인식되어야 한다. 표 1에 제공된 그립 압력, 전압, 유전 상수 및 유전체 두께 값 사이의 관계는 이상적인 정전기 이론에 따라 예시되었으며, 본 발명의 실시예는 그에 의해 한정되지 않는다.

[0038]

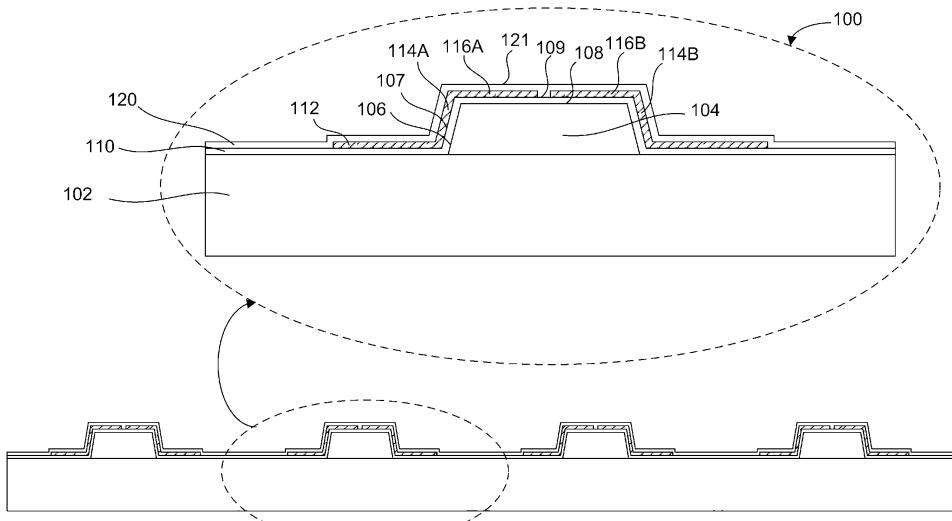

이제 도 1을 참조하면, 본 발명의 일 실시예에 따른 모노폴라 마이크로 소자 이송 헤드 및 헤드 어레이의 측면 도가 제공된다. 도시된 바와 같이, 각각의 모노폴라 소자 이송 헤드(100)는 베이스 기판(102), 상부 표면(108)과 측벽들(106)을 포함하는 메사 구조체(104), 메사 구조체(104) 위에 형성되고 상부 표면(109)과 측벽들(107)을 포함하는 선택적인 패시베이션 층(110), 메사 구조체(104)(그리고 선택적인 패시베이션 층(110)) 위에 형성되는 전극(116), 및 전극(116)을 덮는 상부 표면(121)을 갖춘 유전체 층(120)을 포함할 수 있다. 베이스 기판(102)은 구조적 지지를 제공할 수 있는 실리콘, 세라믹 및 중합체와 같은 다양한 재료로 형성될 수 있다. 일 실시예에서, 베이스 기판은  $10^3$  내지  $10^{18}$  ohm-cm의 전도율을 갖는다. 베이스 기판(102)은 마이크로 소자 이송 헤드들(100)을 정전기 그리퍼 조립체의 작동 전자 장치에 연결하기 위한 배선(미도시)을 추가로 포함할 수 있다.

[0039]

메사 구조체(104)는 적합한 처리 기법들을 사용하여 형성될 수 있으며, 베이스 기판(102)과 동일하거나 상이한 재료로 형성될 수 있다. 일 실시예에서, 메사 구조체(104)는 예를 들어 리소그래피 패터닝과 에칭, 또는 캐스팅(casting) 기법들을 사용함으로써 베이스 기판(102)과 함께 통합적으로 형성된다. 일 실시예에서, 이방성 에칭 기법들은 메사 구조체(104)를 위한 테이퍼형(tapered) 측벽들(106)을 형성하는 데 이용될 수 있다. 다른 실시예에서, 메사 구조체(104)는 베이스 기판(102)의 상부 상에 부착되거나 성장되고 패턴화될 수 있다. 일 실시

예에서, 메사 구조체(104)는 실리콘과 같은 반도체 기판 위에 형성된 이산화규소와 같은 패턴화된 산화물 층이다.

[0040] 일 양태에서, 메사 구조체들(104)은 베이스 기판으로부터 멀어지게 돌출하는 프로파일을 생성하여, 광업 작업 중 특정 마이크로 소자를 광업하기 위한 국소적인 접점(contact point)을 제공하도록 한다. 일 실시예에서, 메사 구조체들(104)은 높이가 대략  $1 \mu\text{m}$  내지  $5 \mu\text{m}$ , 또는 더욱 구체적으로는 대략  $2 \mu\text{m}$ 이다. 메사 구조체들(104)의 특정 치수들은 광업하고자 하는 마이크로 소자들의 특정 치수들, 및 메사 구조체들 위에 형성된 임의의 층의 두께에 종속될 수 있다. 일 실시예에서, 베이스 기판(102) 상의 메사 구조체들(104)의 어레이의 높이, 폭 및 평면성은 베이스 기판에 걸쳐서 균일하여, 각각의 마이크로 소자 이송 헤드(100)가 광업 작업 중 각각의 대응하는 마이크로 소자와 접촉할 수 있다. 일 실시예에서, 각각의 마이크로 소자 이송 헤드의 상부 표면(121)을 가로지른 폭은 광업 작업 중 이송 헤드가 의도된 대응하는 마이크로 소자에 인접한 마이크로 소자와 의도하지 않게 접촉하지 않도록 대응하는 마이크로 소자 어레이 내의 각각의 마이크로 소자의 상부 표면의 폭보다 약간 크거나, 그와 대략 동일하거나, 또는 그보다 작다. 아래에 더욱 상세하게 기술하는 바와 같이, 추가 층들(110, 112, 120)이 메사 구조체(104) 위에 형성될 수 있으므로, 메사 구조체의 폭은 각각의 마이크로 소자 이송 헤드의 상부 표면(121)을 가로지른 폭이 대응하는 마이크로 소자 어레이 내의 각각의 마이크로 소자의 상부 표면의 폭보다 약간 크거나, 그와 대략 동일하거나, 또는 그보다 작게 되도록 위에 있는 층들의 두께를 고려할 수 있다.

[0041] 여전히 도 1을 참조하면, 메사 구조체(104)는 평탄할 수 있는 상부 표면(108), 및 측벽들(106)을 구비한다. 일 실시예에서, 측벽들(106)은 예를 들어, 최대 10도만큼 테이퍼질 수 있다. 측벽들(106)을 테이퍼지게 하는 것은 아래에 더 기술하는 바와 같이 전극들(116) 및 전극 리드들(114)을 형성하는 데 이로울 수 있다. 이어서, 패시베이션 층(110)이 베이스 기판(102) 및 메사 구조체들(104)의 어레이 위에 선택적으로 부착되거나 성장될 수 있다. 패시베이션 층(110)은 화학 기상 증착(CVD), 스퍼터링, 또는 원자 층 증착(ALD)과 같은 다양한 적절한 기법들에 의해 부착될 수 있다. 일 실시예에서, 패시베이션 층(110)은 산화 규소( $\text{SiO}_2$ ), 산화 알루미늄( $\text{Al}_2\text{O}_3$ ) 또는 산화 탄탈( $\text{Ta}_2\text{O}_5$ )을 들 수 있으나 이에 한정되지 않는  $0.5 \mu\text{m}$  내지  $2.0 \mu\text{m}$  두께의 산화물일 수 있다.

[0042] 이어서, 전도성 층(112)이 메사 구조체들(104)의 어레이 및 선택적인 패시베이션 층(110) 위에 부착되고, 전극들(116) 및 전극 리드들(114)을 형성하기 위해 패턴화될 수 있다. 예를 들어, 전극들(116) 및 전극 리드들(114)을 형성하기 위해 리프트 오프(lift off) 기술이 이용될 수 있는데, 이 기술에서는 레지스트 층이 기판 위에 부착되고 패턴화된 후, 금속 층을 부착하고, 레지스트 및 레지스트 상의 금속 층의 부분을 리프트 오프하여 원하는 패턴을 남긴다. 대안적으로, 원하는 패턴을 달성하기 위해, 금속 층 부착 후에 패턴화 및 에칭이 수행될 수 있다. 전극 리드들(114)은 전극(116)으로부터 메사 구조체(104)의 상부 표면(108)(그리고 선택적인 패시베이션 층(110)의 상부 표면(109)) 위에 그리고 메사 구조체(104)의 측벽(106)을 따라(그리고 선택적인 패시베이션(110)의 측벽(107)을 따라) 이어질 수 있다. 전극들(116) 및 전극 리드들(114)을 형성하는 데 사용된 전도성 층(112)은 단층 또는 다층일 수 있다. 금속, 금속 합금, 내화 금속 및 내화 금속 합금을 비롯한 다양한 전도성 재료가 전도성 층(112)을 형성하기 위해 채용될 수 있다. 일 실시예에서, 전도성 층(112)은 두께가 최대 5,000 옹스트롬( $0.5 \mu\text{m}$ )이다. 일 실시예에서, 전도성 층(112)은 백금 또는 내화 금속이나 내화 금속 합금과 같은 고 용융 온도 금속을 포함한다. 예를 들어, 전도성 층은 백금, 티타늄, 바나듐, 크롬, 지르코늄, 닉오븀, 몰리브덴, 루테늄, 로듐, 하프늄, 탄탈, 텉스텐, 레늄, 오스뮴, 이리듐 및 이들의 합금을 포함할 수 있다. 내화 금속과 내화 금속 합금은 일반적으로 다른 금속보다 열과 마모에 대한 더욱 높은 저항을 보인다. 일 실시예에서, 전도성 층(112)은 대략 500 옹스트롬( $0.05 \mu\text{m}$ ) 두께의 티타늄 텉스텐( $\text{TiW}$ ) 내화 금속 합금이다.

[0043] 이어서, 유전체 층(120)이 전극들(116) 및 베이스 기판(102) 상의 다른 노출된 층들 위에 부착된다. 일 실시예에서, 유전체 층(120)은 마이크로 소자 이송 헤드(100)의 요구되는 그립 압력을 달성하기에 적합한 두께 및 유전 상수와 작동 전압에서 파괴되지 않기에 충분한 유전 강도를 갖는다. 유전체 층은 단층 또는 다층일 수 있다. 일 실시예에서, 유전체 층은 두께가  $0.5 \mu\text{m}$  내지  $2.0 \mu\text{m}$ 이지만, 두께는 이송 헤드(100)와 밑에 있는 메사 구조체(104)의 특정 토포그래피에 따라 보다 크거나 보다 작을 수 있다. 적합한 유전체 재료는 산화 알루미늄( $\text{Al}_2\text{O}_3$ )과 산화 탄탈( $\text{Ta}_2\text{O}_5$ )을 이에 한정됨이 없이 포함할 수 있다. 다시 위의 표 1을 참조하면,  $22 \text{ V}/\mu\text{m}$  내지  $71 \text{ V}/\mu\text{m}$ 의 인가 전계(전압을 유전체 두께로 나누어 결정됨)를 갖는  $\text{Al}_2\text{O}_3$  유전체 층들 및  $9 \text{ V}/\mu\text{m}$  내지  $28 \text{ V}/\mu\text{m}$ 의 인가 전계를 갖는  $\text{Ta}_2\text{O}_5$  유전체 층들의 실시예가 제공되었다. 본 발명의 실시예에 따르면, 유전체 층(120)은 작업 중 이송 헤드의 단락을 피하기 위해 인가 전계보다 큰 유전 강도를 갖는다. 유전체 층(120)은 화학 기상 증착(CVD), 원자 층 증착(ALD) 및 물리 기상 증착(PVD), 예컨대 스퍼터링과 같은 다양한 적합한 기술에 의

해 부착될 수 있다. 유전체 층(120)은 또한 부착 후 추가로 어닐링될 수 있다. 일 실시예에서, 유전체 층(120)은 적어도  $400 \text{ V}/\mu\text{m}$ 의 유전 강도를 갖는다. 그러한 높은 유전 강도는 예시적인 표 1에 제공된 계산된 두께보다 얇은 유전체 층의 사용을 허용할 수 있다. 균일하고, 컨포멀하고, 치밀하고, 그리고/또는 핀-홀이 없는 유전체 층들을 우수한 유전 강도를 갖고서 부착하기 위해 ALD와 같은 기술이 이용될 수 있다. 다수의 층이 또한 그러한 핀-홀 없는 유전체 층(120)을 달성하기 위해 이용될 수 있다. 상이한 유전체 재료의 다수의 층이 또한 유전체 층(120)을 형성하기 위해 이용될 수 있다. 일 실시예에서, 밑에 있는 전도성 층(112)은 유전체 층의 부착 온도를 선택하는데 있어 제한 인자가 되지 않도록 유전체 층 재료(들)의 부착 온도를 초과하는 용융 온도를 갖는 백금 또는 내화 금속 또는 내화 금속 합금을 포함한다. 일 실시예에서, 유전체 층(120)의 부착 후에, 측 방향 마찰을 추가하여 핵심 작업 중 마이크로 소자들이 이송 헤드로부터 떨어져 나오는 것을 방지하기 위한 특정 정지 마찰 계수를 제공하도록 얇은 코팅(미도시)이 유전체 층(120) 위에 형성될 수 있다. 이러한 실시예에서, 추가 얇은 코팅은 접촉 표면으로서 상부 표면(121)을 대체하고, 이 표면은 본 명세서에 기술된 치수 어레이 요구들을 유지한다. 또한, 추가 코팅은 마이크로 소자 이송 헤드의 작업성에 영향을 줄 수 있는 마이크로 소자 이송 헤드의 유전 특성에 영향을 줄 수 있다. 일 실시예에서, 추가 코팅 두께는 그립 압력에 주목할 만한 영향을 거의 내지는 전혀 갖지 않도록 하기 위하여 최소(예를 들어,  $10 \text{ nm}$  미만)일 수 있다.

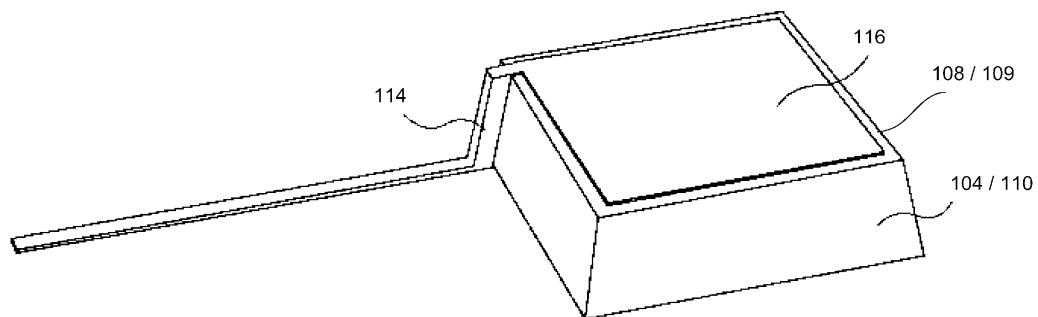

[0044] 도 2는 메사 구조체(104)를 덮는 선택적인 패시베이션 층(110) 위에 형성된 전극(116) 및 전극 리드(114)의 확대 등각도이다. 명확성을 위하여, 위에 있는 유전체 층(120)은 예시되지 않고, 선택적인 패시베이션 층(110) 및 메사 구조체(104)는 단일 메사 구조체/패시베이션 층(104/110)으로서 예시된다. 예시적인 실시예에서, 패시베이션 층(110) 및 유전체 층(120)이 둘 모두 두께가  $0.5 \mu\text{m}$ 인 경우, 전극(116)이 그 위에 형성된 메사 구조체/패시베이션 층(104/110)의 상부 표면(108/109)은 이송 헤드(100)의  $8 \mu\text{m} \times 8 \mu\text{m}$  상부 표면을 달성하기 위해 대략  $7 \mu\text{m} \times 7 \mu\text{m}$ 이다. 일 실시예에 따르면, 전극(116)은 패터닝 허용 오차 내에 있으면서 가능한 한 메사 구조체/패시베이션 층(104/110)의 상부 표면(108/109)의 최대량의 표면적을 덮는다. 빈 공간(free space)의 양을 최소화하는 것은 커판시턴스, 및 마이크로 소자 이송 헤드에 의해 달성될 수 있는 최종 그립 압력을 증가시킨다. 소정 양의 빈 공간이 도 2에서 메사 구조체/패시베이션 층(104/110)의 상부 표면(108/109)에 예시되지만, 전극(116)은 전체 상부 표면(108/109)을 덮을 수 있다. 전극(116)은 또한 상부 표면(108/109)의 완전한 커버리지를 보장하기 위해 상부 표면(108/109)보다 약간 크게 되고, 메사 구조체/패시베이션 층(104/110)의 측벽들(106/107) 아래로 부분적으로 연장될 수 있다. 메사 어레이는 다양한 상이한 피치를 가질 수 있고, 본 발명의 실시예들은  $10 \mu\text{m}$  피치의 메사 구조체/패시베이션 층(104/110)의 예시적인  $7 \mu\text{m} \times 7 \mu\text{m}$  상부 표면에 한정되지 않는다는 것이 인식되어야 한다.

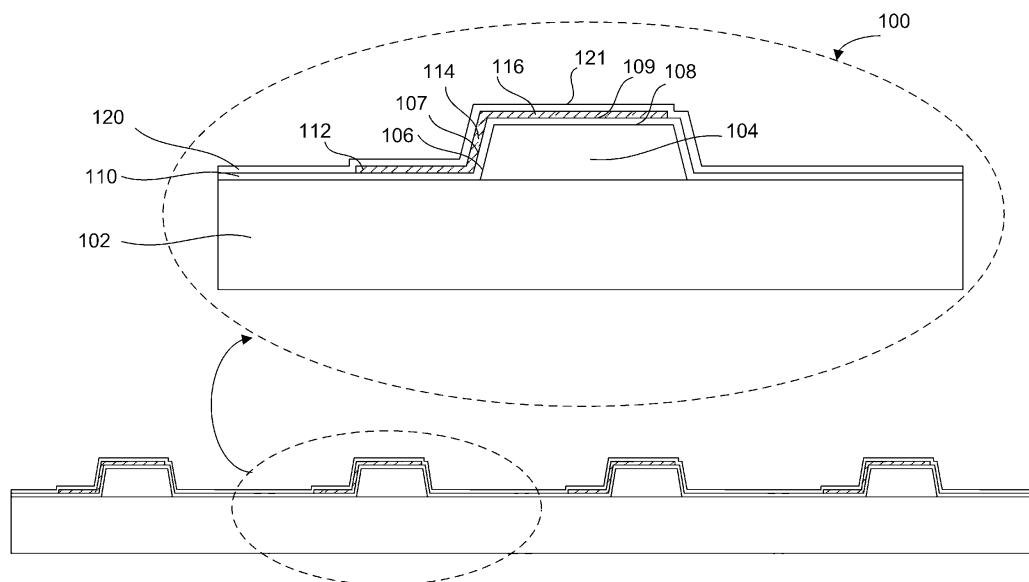

[0045] 이제 도 3을 참조하면, 본 발명의 일 실시예에 따른 바이폴라 마이크로 소자 이송 헤드(100) 및 헤드 어레이의 측면도가 제공된다. 도시된 바와 같이, 바이폴라 소자 이송 헤드(100)는 베이스 기판(102), 상부 표면(108)과 측벽들(106)을 포함하는 메사 구조체(104), 상부 표면(109) 및 측벽들(107)을 포함하는 패시베이션 층(110), 메사 구조체(104) 위에 형성된 한 쌍의 전극(116A, 116B)과 전극 리드들(114A, 114B), 선택적인 패시베이션 층(110), 및 한 쌍의 전극(116A, 116B)을 덮는 유전체 층(120)을 포함할 수 있다.

[0046] 도 4는 메사 구조체(104)를 덮는 선택적인 패시베이션 층(110) 위에 형성된 전극들(116A, 116B) 및 전극 리드들(114A, 114B)의 확대 등각도이다. 명확성을 위하여, 위에 있는 유전체 층(120)은 예시되지 않고, 선택적인 패시베이션 층(110) 및 메사 구조체(104)는 단일 메사 구조체/패시베이션 층(104/110)으로서 예시된다. 도 4는 전극 리드들(114A, 114B)이 메사 구조체/패시베이션 층(104/110)의 대향하는 측벽들 상에서보다는 단일 측벽을 따라 이어지는 것으로서 예시되어 있다는 점에서 도 3과 약간 상이하다. 전극 리드들(114A, 114B)은 본 발명의 일 실시예에 따라 임의의 적합한 측벽을 따라 이어질 수 있다. 예시적인 일 실시예에서, 메사 구조체/패시베이션 층(104/110)의 상부 표면(108/109)이  $10 \mu\text{m}$  피치를 갖는 메사 어레이에 대응하는 대략  $7 \mu\text{m} \times 7 \mu\text{m}$ 인 경우에, 이를 전극은 전극들(116A, 116B) 사이의 분리를 여전히 제공하면서 가능한 한 메사 구조체/패시베이션 층(104/110)의 상부 표면(108/109)의 최대량의 표면적을 덮을 수 있다. 분리 거리의 최소량은 전극들로부터의 전계의 중첩을 피하면서 표면적의 최대화를 고려함으로써 균형을 맞출 수 있다. 예를 들어, 전극들(116A, 116B)은  $0.5 \mu\text{m}$  이하 만큼 분리될 수 있고, 최소 분리 거리는 전극들의 높이에 의해 한정될 수 있다. 일 실시예에서, 전극들은 일 방향으로 상부 표면(108/109)보다 약간 길고, 메사 구조체/패시베이션 층(104/110)의 측벽들 아래로 부분적으로 연장되어 상부 표면(108/109)의 최대 커버리지를 보장한다. 메사 어레이는 다양한 상이한 피치를 가질 수 있고, 본 발명의 실시예들은  $10 \mu\text{m}$  피치의 메사 구조체/패시베이션 층(104/110)의 예시적인  $7 \mu\text{m} \times 7 \mu\text{m}$  상부 표면에 한정되지 않는다는 것이 인식되어야 한다.

[0047] 이제 도 5 및 도 6을 참조하면, 바이폴라 마이크로 소자 이송 헤드의 전극들(116A, 116B)의 평면도가 본 발명의

실시예에 따라 제공된다. 지금까지, 메사 구조체(104)는 도 5에 도시된 바와 같이 단일 메사 구조체로서 기술되었다. 그러나, 본 발명의 실시예들은 그렇게 한정되지 않는다. 도 6에 예시된 실시예에서, 각각의 전극(116)은 트렌치(105)에 의해 분리된 개별 메사 구조체(104A, 104B) 상에 형성된다. 선택적인 패시베이션 층(110)(미도시)이 메사 구조체들(104A, 104B) 둘 모두를 덮을 수 있다.

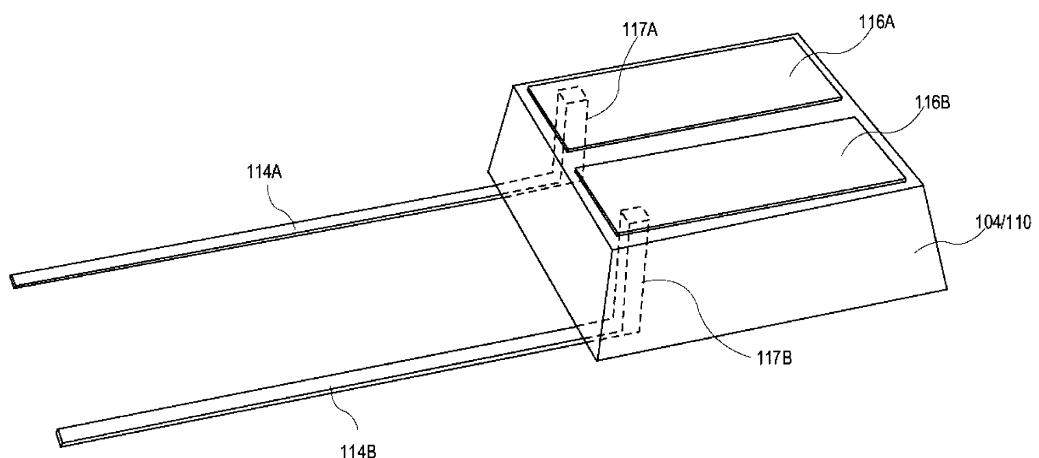

[0048] 이제 도 7을 참조하면, 대안적인 전극 리드 구성의 등각도가 본 발명의 실시예에 따라 제공된다. 이러한 실시예에서, 전극 리드들(114A, 114B)은 메사 구조체(104)의 일부분 아래로 이어지고, 전도성 비아들(117A, 117B)은 메사 구조체(104)(그리고 예시되지 않은 선택적인 패시베이션 층(110))을 통하여 이어져 개별의 전극 리드들(114A, 114B)에 전극들(116A, 116B)을 연결한다. 이러한 실시예에서, 전극 리드들(114A, 114B)은 메사 구조체(104)의 형성 이전에 형성될 수 있고, 전극 리드들(114A, 114B) 및 전극들(116A, 116B)과 동일하거나 상이한 전도성 재료로 형성될 수 있다. 비아들(117A, 117B)이 도 7에서 바이폴라 전극 구조에 관하여 예시되지만, 전술된 비아 또는 비아들은 또한 모노폴라 전극 구조들로 통합될 수 있다는 것이 인식되어야 한다.

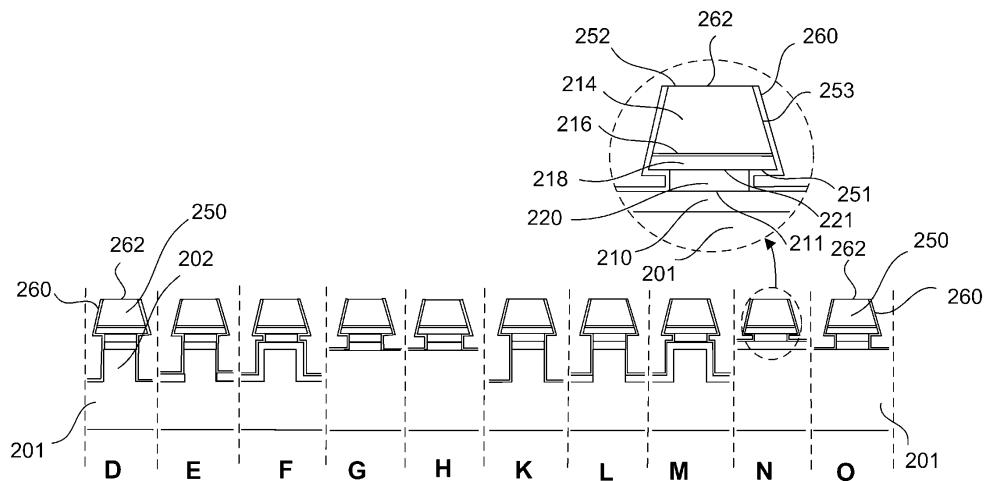

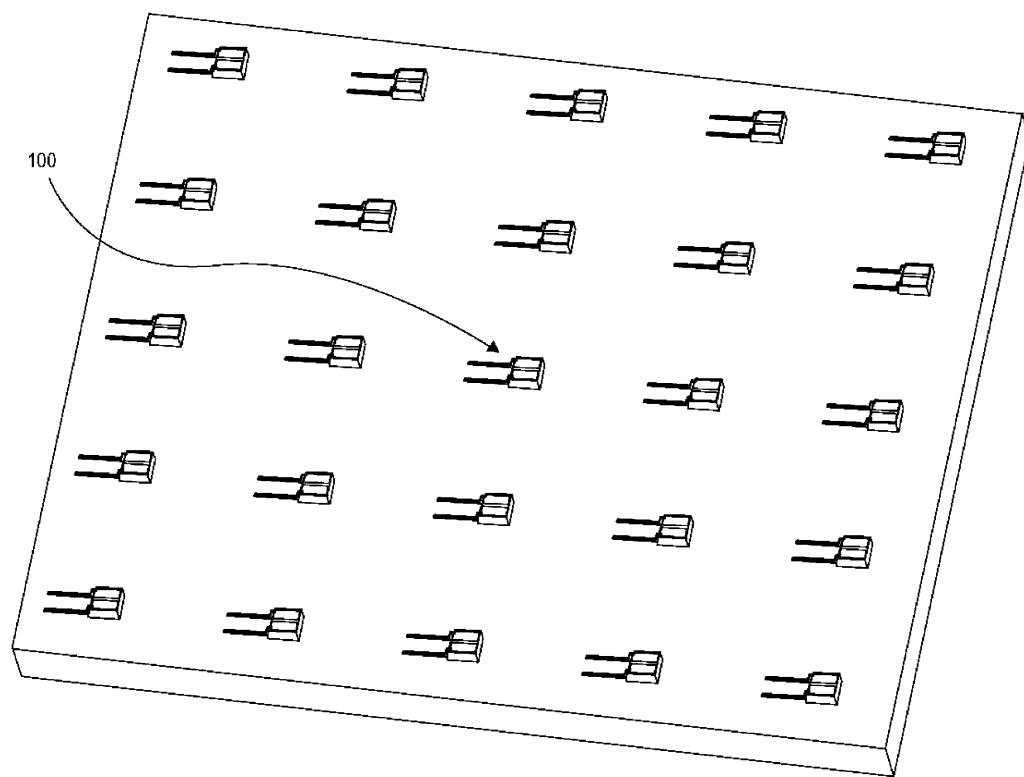

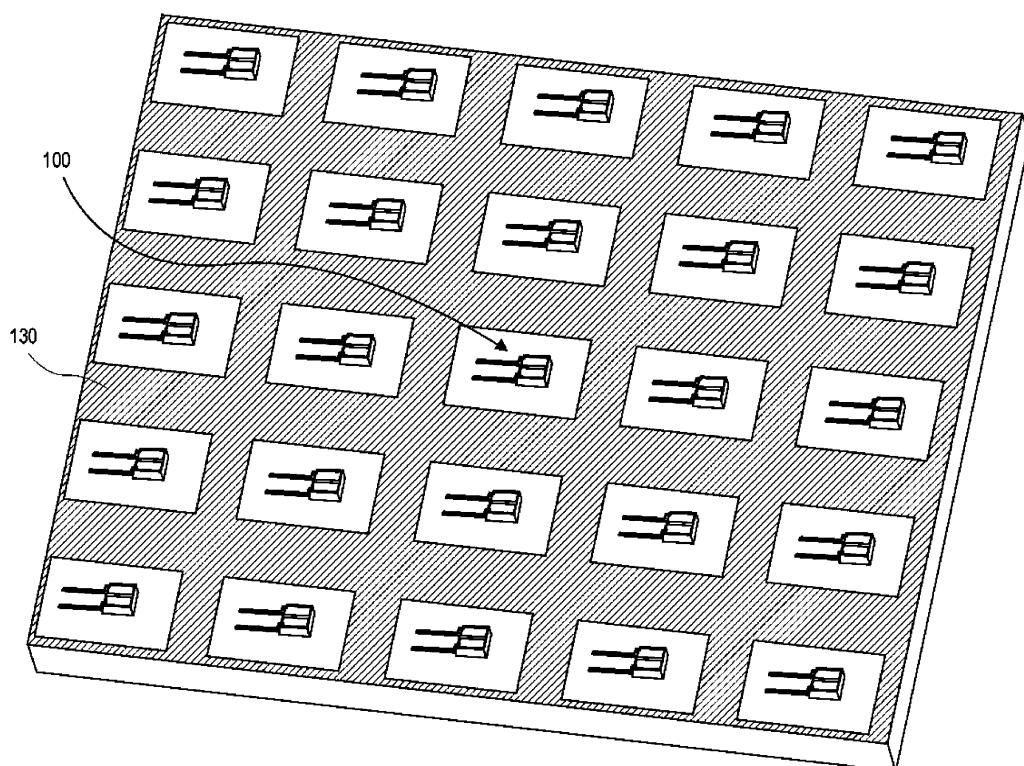

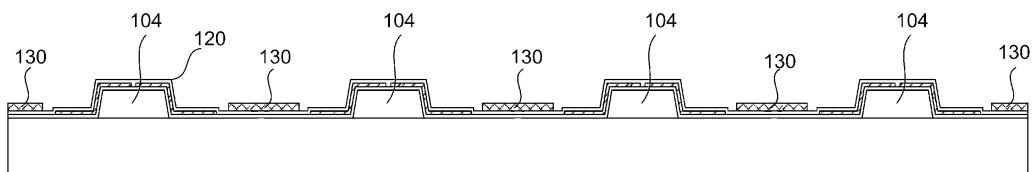

[0049] 이제 도 8 내지 도 10을 참조하면, 전도성 접지면이 유전체 층 위에 형성되어 메사 구조체들의 어레이를 둘러싸는 본 발명의 실시예가 예시된다. 도 8은 도 4에 관하여 전술된 바와 같이 바이폴라 전극 구성을 갖는 마이크로 소자 이송 헤드들(100)의 어레이의 등각도이다. 명확성을 위하여, 선택적인 밑에 있는 패시베이션 층 및 위에 있는 유전체 층은 예시되지 않았다. 이제 도 9 및 도 10을 참조하면, 전도성 접지면(130)은 유전체 층(120) 위에 형성되며 메사 구조체들(104)의 어레이를 둘러싼다. 접지면(130)의 존재는 특히 고전압의 인가 동안 이송 헤드들(100) 사이의 아킹을 방지하는 것을 도울 수 있다. 접지면(130)은 전극들 또는 비아들을 형성하는 데 사용된 전도성 재료와 동일하거나 그와 상이할 수 있는 전도성 재료로 형성될 수 있다. 접지면(130)은 또한 전극들을 형성하는 데 사용된 전도성 재료보다 낮은 용융 온도를 갖는 전도성 재료로 형성될 수 있고, 이는 접지면(130)의 형성 후에 유전체 층(120)과 유사한 질(예를 들어, 유전 강도)의 유전체 층을 부착할 필요가 없기 때문이다.

[0050] 도 11은 본 발명의 일 실시예에 따른 캐리어 기판으로부터 수용 기판으로 마이크로 소자를 꾹 업하고 이송하는 방법을 예시한 흐름도이다. 작업(1110)에서, 캐리어 기판에 연결된 마이크로 소자 위에 이송 헤드가 위치된다. 이송 헤드는 위의 실시예에 기술된 바와 같이 메사 구조체, 메사 구조체 위의 전극, 및 전극을 덮는 유전체 층을 포함할 수 있다. 따라서, 이송 헤드는 모노폴라 또는 바이폴라 전극 구성을, 및 상기 실시예들에서 기술된 바와 같은 임의의 다른 구조적 변경을 가질 수 있다. 이어서, 마이크로 소자는 작업(1120)에서 이송 헤드와 접촉된다. 일 실시예에서, 마이크로 소자는 이송 헤드의 유전체 층(120)과 접촉된다. 대안적인 실시예에서, 이송 헤드는 마이크로 소자 위에 위치되되, 그들을 분리하는, 그립 압력에 상당한 영향을 미치지 않는, 예를 들어 1 nm(0.001  $\mu$ m) 또는 10 nm(0.01  $\mu$ m)의 적합한 에어 캡을 갖고서 위치된다. 작업(1130)에서, 전압이 마이크로 소자 상에 그립 압력을 생성하기 위해 전극에 인가되고, 작업(1140)에서 마이크로 소자가 이송 헤드로 꾹 업된다. 이어서, 작업(1150)에서 마이크로 소자는 수용 기판 상에 릴리즈된다.

[0051] 작업들(1110 내지 1150)이 도 11에 순차적으로 예시되었지만, 실시예들이 그렇게 한정되지 않으며, 추가의 작업들이 수행될 수 있고, 소정 작업들이 상이한 순서로 수행될 수 있다는 것이 인식되어야 한다. 예를 들어, 일 실시예에서, 마이크로 소자를 이송 헤드와 접촉시킨 후, 이송 헤드나 마이크로 소자의 접촉 표면 상에 존재할 수 있는 임의의 입자를 제거하기 위해 이송 헤드는 마이크로 소자의 상부 표면에 걸쳐서 문질러진다. 다른 실시예에서, 마이크로 소자를 꾹 업하기 전이나 꾹 업하는 동안에 마이크로 소자를 캐리어 기판에 연결하는 접합 층에 상 변화를 일으키기 위해 작업이 수행된다. 접합 층의 일부분이 마이크로 소자와 함께 꾹 업되면, 후속 처리 중 접합 층의 상기 부분의 상을 제거하기 위해 추가 작업들이 수행될 수 있다.

[0052] 마이크로 소자 상에 그립 압력을 생성하기 위해 전극에 전압을 인가하는 작업(1130)은 다양한 순서로 수행될 수 있다. 예를 들어, 전압은 마이크로 소자를 이송 헤드와 접촉시키기 전에, 마이크로 소자를 이송 헤드와 접촉시키는 동안에, 또는 마이크로 소자를 이송 헤드와 접촉시킨 후에 인가될 수 있다. 전압은 또한 접합 층에 상 변화를 일으키기 전에, 일으키는 동안에, 또는 일으킨 후에 인가될 수 있다.

[0053] 도 12는 본 발명의 일 실시예에 따른 이송 헤드가 마이크로 소자와 접촉한 상태에서의 바이폴라 전극에 걸쳐서 인가된 교류 전압의 개략도이다. 예시된 바와 같이, 개별 교류 전류(AC) 전압원은 음 전압이 전극(116A)에 인가되는 특정 시점에 양 전압이 전극(116B)에 인가되고 그 반대로도 그러하도록 한 쌍의 전극(116A, 116B)에 걸쳐서 인가되는 교류 전압으로 각각의 전극 리드(114A, 114B)에 인가될 수 있다. 이송 헤드로부터 마이크로 소자를 릴리즈하는 것은 전압원을 끄는 것, 한 쌍의 전극에 걸쳐서 전압을 낮추는 것, AC 전압의 파형을 변화시키는 것, 및 전압원을 접지시키는 것을 비롯한 다양한 방법으로 달성될 수 있다. 도 13은 본 발명의 일 실시예에

따라 바이폴라 전극에 인가된 정전압의 개략도이다. 예시된 특정 실시예에서, 음 전압이 전극(116A)에 인가되는 한편, 양 전압이 전극(116B)에 인가된다. 도 14는 본 발명의 일 실시예에 따라 모노폴라 전극에 인가된 정전압의 개략도이다. 이송 헤드가 도 14에 예시된 마이크로 소자를 꾹업하면, 이송 헤드가 마이크로 소자를 유지할 수 있는 시간의 양은 단일 전압만이 전극(116)에 인가되므로 유전체 층의 방전율의 함수일 수 있다. 도 14에 예시된 이송 헤드로부터 마이크로 소자를 릴리즈하는 것은 전압원을 끄는 것, 전압원을 접지시키는 것, 또는 정전압의 극성을 반대로 하는 것에 의해 달성될 수 있다.

[0054] 도 12 내지 도 14에 예시된 특정 실시예들에서, 마이크로 소자들(200)은 도 27, 예 270에 예시된 그것이다. 그렇지만 도 12 내지 도 14에 예시된 마이크로 소자들은 도 27 내지 도 29에 예시된 임의의 마이크로 LED 소자 구조체들 및 관련된 미국 출원 제61/561,706호 및 미국 출원 제61/594,919호에 기술된 것들일 수 있다. 예를 들어, 마이크로 LED 소자(200)는 마이크로 p-n 다이오드(235, 250) 및 금속화 층(220)을 포함할 수 있고, 이때 금속화 층은 기판(201) 상에 형성된 접합 층(210)과 마이크로 p-n 다이오드(235, 250) 사이에 있다. 일 실시예에서, 마이크로 p-n 다이오드(250)는 상부 n-도핑된 층(214), 하나 이상의 양자 우물 층들(216), 및 하부 p-도핑된 층(218)을 포함한다. 마이크로 p-n 다이오드들은 수직형(straight) 측벽들 또는 테이퍼형 측벽들을 갖도록 제조될 수 있다. 소정 실시예들에서, 마이크로 p-n 다이오드들(250)은 (상부에서 하부로) 바깥쪽으로 테이퍼진 측벽들(253)을 갖추고 있다. 소정 실시예들에서, 마이크로 p-n 다이오드들(235)은 (상부에서 하부로) 안쪽으로 테이퍼진 측벽들(253)을 갖추고 있다. 금속화 층(220)은 하나 이상의 층을 포함할 수 있다. 예를 들어, 금속화 층(220)은 전극 층 및 전극 층과 접합 층 사이의 장벽 층을 포함할 수 있다. 마이크로 p-n 다이오드 및 금속화 층은 상부 표면, 저부 표면 및 측벽들을 각각 가질 수 있다. 일 실시예에서, 마이크로 p-n 다이오드(250)의 저부 표면(251)은 마이크로 p-n 다이오드의 상부 표면(252)보다 넓고, 측벽들(253)은 상부에서 하부로 바깥쪽으로 테이퍼진다. 마이크로 p-n 다이오드(235)의 상부 표면은 p-n 다이오드의 저부 표면보다 넓거나, 대략 동일한 폭일 수 있다. 일 실시예에서 마이크로 p-n 다이오드(250)의 저부 표면(251)은 금속화 층(220)의 상부 표면(221)보다 넓다. 마이크로 p-n 다이오드의 저부 표면은 또한 금속화 층의 상부 표면보다 넓거나, 금속화 층의 상부 표면과 대략 동일한 폭일 수 있다.

[0055] 컨포멀 유전체 장벽 층(260)은 마이크로 p-n 다이오드(235, 250) 및 기타 노출된 표면들 위에 선택적으로 형성될 수 있다. 컨포멀 유전체 장벽 층(260)은 마이크로 p-n 다이오드(235, 250), 금속화 층(220) 및 선택적으로 접합 층(210)보다 얇을 수 있어, 컨포멀 유전체 장벽 층(260)이 그 위에 형성된 토포그래피(topography)의 아웃라인을 형성하게 된다. 일 실시예에서, 마이크로 p-n 다이오드(235, 250)는 두께가 3  $\mu\text{m}$ 와 같은 수 마이크로미터이고, 금속화 층(220)은 두께가 0.1  $\mu\text{m}$  내지 2  $\mu\text{m}$ 이며, 접합 층(210)은 두께가 0.1  $\mu\text{m}$  내지 2  $\mu\text{m}$ 이다. 일 실시예에서, 컨포멀 유전체 장벽 층(260)은 대략 50 내지 600 옹스트롬 두께의 산화 알루미늄( $\text{Al}_2\text{O}_3$ )이다. 컨포멀 유전체 장벽 층(260)은 원자 층 증착(ALD)을 들 수 있으나 이에 한정되지 않는 다양한 적합한 기법들에 의해 부착될 수 있다. 컨포멀 유전체 장벽 층(260)은 꾹업 공정 중 인접한 마이크로 p-n 다이오드들 사이의 전하 아킹에 대하여 보호하고, 꾹업 공정 중 인접한 마이크로 p-n 다이오드들이 함께 달라붙는 것으로부터 보호할 수 있다. 컨포멀 유전체 장벽 층(260)은 또한 마이크로 p-n 다이오드들의 측벽들(253), 양자 우물 층(216) 및 저부 표면(251)을 마이크로 p-n 다이오드의 완전성에 영향을 미칠 수 있는 오염으로부터 보호할 수 있다. 예를 들어, 컨포멀 유전체 장벽 층(260)은 마이크로 p-n 다이오드들(250)의 측벽들 및 양자 우물 층(216) 위로의 접합 층 재료(210)의 위킹(wicking)에 대해 물리적 장벽으로서 기능할 수 있다. 컨포멀 유전체 장벽 층(260)은 또한 일단 마이크로 p-n 다이오드들(250)이 수용 기판 상에 배치되면 이를 절연시킬 수 있다. 일 실시예에서, 컨포멀 유전체 장벽 층(260)은 마이크로 p-n 다이오드의 측벽들(253)에 걸쳐 이어지고, 마이크로 p-n 다이오드 내의 양자 우물 층(216)을 덮을 수 있다. 컨포멀 유전체 장벽 층은 또한 마이크로 p-n 다이오드의 저부 표면(251)에 부분적으로 걸쳐 이어지고 금속화 층(220)의 측벽들에 걸쳐 이어질 수 있다. 일부 실시예에서, 컨포멀 유전체 장벽 층은 또한 패턴화된 접합 층(210)의 측벽들에 걸쳐 이어진다. 접촉 개구(262)가 컨포멀 유전체 장벽 층(260) 내에 형성되어 마이크로 p-n 다이오드의 상부 표면(252)을 노출시킬 수 있다.

[0056] 도 27을 참조하면, 접촉 개구(262)는 마이크로 p-n 다이오드의 상부 표면(252)보다 작은 폭을 가질 수 있으며, 컨포멀 유전체 장벽 층(260)은 마이크로 p-n 다이오드의 상부 표면(252)의 에지 주위에 립을 형성한다. 도 28을 참조하면, 접촉 개구(262)는 마이크로 p-n 다이오드의 상부 표면보다 약간 큰 폭을 가질 수 있다. 이러한 실시예에서, 접촉 개구(262)는 마이크로 p-n 다이오드의 상부 표면(252) 및 마이크로 p-n 다이오드의 측벽들(253)의 상부 부분을 노출시키며, 컨포멀 유전체 장벽 층(260)은 양자 우물 층(216)을 덮고 절연한다. 도 29를 참조하면, 컨포멀 유전체 층(260)은 마이크로 p-n 다이오드의 상부 표면과 대략 동일한 폭을 가질 수 있다. 컨포멀 유전체 층(260)은 또한 도 27 내지 도 29에 예시된 마이크로 p-n 다이오드의 저부 표면(251)을

따라 걸쳐 이어질 수 있다.

[0057] 일 실시예에서, 컨포멀 유전체 장벽 층(260)은 접합 헤드의 유전체 층(120)과 동일한 재료로 형성된다. 특정 마이크로 LED 소자 구조체에 따라, 컨포멀 유전체 장벽 층(260)은 또한 접합 층(210)의 측벽들, 및 존재한다면 캐리어 기판과 포스트(post)들에 걸쳐 이어질 수 있다. 접합 층(210)은 소정 처리 및 취급 작업들 중 캐리어 기판(201) 상에 마이크로 LED 소자(200)를 유지할 수 있고, 상 변화를 겪을 때, 마이크로 LED 소자(200)가 위에 유지될 수 있으면서도 여전히 또한 광업 작업 중 용이하게 릴리즈가능할 수 있는 매체를 제공할 수 있는 재료로 형성될 수 있다. 예를 들어, 접합 층은 재용융가능하거나 리플로우(reflow)가능할 수 있어, 접합 층이 광업 작업 이전에 또는 광업 작업 중 고체 상태에서 액체 상태로 상 변화를 겪게 한다. 액체 상태에서, 접합 층은 캐리어 기판 상의 적소에 마이크로 LED 소자를 유지할 수 있고, 또한 마이크로 LED 소자(200)가 그로부터 용이하게 릴리즈가능한 매체를 제공한다. 일 실시예에서, 접합 층(210)은 대략 350°C 미만, 또는 더욱 구체적으로 대략 200 °C 미만의 액상선 온도 또는 용융 온도를 갖는다. 이러한 온도에서, 접합 층은 마이크로 LED 소자의 다른 구성요소들에 실질적으로 영향을 미치지 않고 상 변화를 겪을 수 있다. 예를 들어, 접합 층은 금속 또는 금 속 합금, 또는 제거가능한 열가소성 중합체로 형성될 수 있다. 예를 들어, 접합 층은 인듐, 주석, 또는 폴리에틸렌 또는 폴리프로필렌과 같은 열가소성 중합체를 포함할 수 있다. 일 실시예에서, 접합 층은 전도성일 수 있다. 예를 들어, 접합 층이 온도의 변화에 응하여 고체에서 액체로 상 변화를 겪는 경우에, 접합 층의 일부분은 광업 작업 중 마이크로 LED 소자 상에 남을 수 있다. 이러한 실시예에서, 접합 층이 전도성 재료로 형성되어 이후에 수용 기판으로 이송될 때 마이크로 LED 소자에 악영향을 주지 않도록 하는 것이 유리할 수 있다. 이러한 경우에, 이송 중 마이크로 LED 소자 상에 남아 있는 전도성 접합 층의 상기 부분은 마이크로 LED 소자를 수용 기판 상의 전도성 패드에 접합시키는 데 도움을 줄 수 있다. 특정 실시예에서, 접합 층은 156.7 °C의 용융 온도를 갖는 인듐으로 형성될 수 있다. 접합 층은 기판(201)에 걸쳐서 측방향으로 연속적일 수 있거나, 또한 측방향으로 분리된 위치들에 형성될 수 있다. 예를 들어, 측방향으로 분리된 위치의 접합 층은 마이크로 p-n 다이오드의 저부 표면 또는 금속화 층보다 좁은 폭을 갖거나 그와 대략 동일한 폭을 가질 수 있다. 일부 실시예에서, 마이크로 p-n 다이오드들은 기판 상의 포스트들(202) 상에 선택적으로 형성될 수 있다.

[0058] 솔더들은 접합 층(210)에 적합한 재료들일 수 있는데, 그 이유는 다수의 솔더가 일반적으로 그들의 고체 상태에서 연성 재료들이고 반도체 및 금속 표면과의 양호한 습윤을 나타내기 때문이다. 통상적인 합금은 단일 온도로 용융되지 않고, 온도 범위에 걸쳐 용융된다. 따라서, 솔더 합금은 종종 합금이 액체로 남아 있는 최저 온도에 대응하는 액상선 온도, 및 합금이 고체로 남아 있는 최고 온도에 대응하는 고상선 온도에 의해 특징지어 진다. 본 발명의 실시예들과 이용될 수 있는 낮은 용융 솔더 재료들의 예시적인 리스트가 표 2에 제공된다.

## 표 2

| 화학 조성                | 액상선 온도(°C) | 고상선 온도(°C) |

|----------------------|------------|------------|

| 100 In               | 156.7      | 156.7      |

| 66.3In33.7Bi         | 72         | 72         |

| 51In32.5Bi16.5Sn     | 60         | 60         |

| 57Bi26In17Sn         | 79         | 79         |

| 54.02Bi29.68In16.3Sn | 81         | 81         |

| 67Bi33In             | 109        | 109        |

| 50In50Sn             | 125        | 118        |

| 52Sn48In             | 131        | 118        |

| 58Bi42Sn             | 138        | 138        |

| 97In3Ag              | 143        | 143        |

| 58Sn42In             | 145        | 118        |

| 99.3In0.7Ga          | 150        | 150        |

| 95In5Bi              | 150        | 125        |

| 99.4In0.6Ga          | 152        | 152        |

| 99.6In0.4Ga          | 153        | 153        |

| 99.5In0.5Ga          | 154        | 154        |

| 60Sn40Bi             | 170        | 138        |

| 100Sn                | 232        | 232        |

| 95Sn5Sb              | 240        | 235        |

[0059]

삭제

[0060] 본 발명의 실시예들과 사용될 수 있는 열가소성 중합체들의 예시적인 리스트가 표 3에 제공된다.

표 3

| 종합체                 | 용융 온도(°C)  |

|---------------------|------------|

| 아크릴(PMMA)           | 130 내지 140 |

| 폴리옥시메틸렌(POM 또는 아세탈) | 166        |

| 폴리부틸렌 테레프탈레이트(PBT)  | 160        |

| 폴리카프로락톤(PCL)        | 62         |

| 폴리에틸렌 테레프탈레이트(PET)  | 260        |

| 폴리카보네이트(PC)         | 267        |

| 폴리에스테르              | 260        |

| 폴리에틸렌(PE)           | 105 내지 130 |

| 폴리에테르에테르케톤(PEEK)    | 343        |

| 폴리락트산(PLA)          | 50 내지 80   |

| 폴리프로필렌(PP)          | 160        |

| 폴리스티렌(PS)           | 240        |

| 폴리염화비닐리텐(PVDC)      | 185        |

[0062]

도 15는 본 발명의 일 실시예에 따른 캐리어 기판으로부터 수용 기판으로 마이크로 소자를 꾹입하고 이송하는 방법을 예시하는 흐름도이다. 작업(1510)에서, 접합 층에 의해 캐리어 기판에 연결된 마이크로 소자 위에 이송 헤드가 위치된다. 이송 헤드는 본 명세서에서 기술된 임의의 이송 헤드일 수 있다. 마이크로 소자는 도 27 내지 도 29에 예시된 임의의 마이크로 LED 소자 구조체들, 및 관련된 미국 가출원 제61/561,706호 및 미국 가출원 제61/594,919호에 기술된 것들일 수 있다. 이어서, 마이크로 소자는 작업(1520)에서 이송 헤드와 접촉된다. 일 실시예에서, 마이크로 소자는 이송 헤드의 유전체 층(120)과 접촉된다. 대안적인 실시예에서, 이송 헤드는 마이크로 소자 위에 위치되되, 그들을 분리하는, 그립 압력에 상당한 영향을 미치지 않는, 예를 들어 1 nm(0.001  $\mu\text{m}$ ) 또는 10 nm(0.01  $\mu\text{m}$ )의 적합한 에어 캡을 갖고서 위치된다. 작업(1525)에서, 고체 상태에서 액체 상태로 접합 층(210)에서 상 변화를 일으키기 위해 작업이 수행된다. 예를 들어, 작업은 156.7 °C의 용융 온도에서 또는 그 초과로 인듐(In) 접합 층을 가열하는 것을 포함할 수 있다. 다른 실시예에서, 작업(1525)은 작업(1520) 이전에 수행될 수 있다. 작업(1530)에서, 마이크로 소자 상에 그립 압력을 생성하기 위해 전극에 전압이 인가되고, 마이크로 소자 및 접합 층(210)의 상당 부분이 작업(1540)에서 이송 헤드에 의해 꾹입된다. 예를 들어, 접합 층(210)의 대략 절반이 마이크로 소자와 함께 꾹입될 수 있다. 대안적인 실시예에서, 접합 층(210)의 어느 부분도 이송 헤드에 의해 꾹입되지 않는다. 작업(1545)에서, 마이크로 소자 및 접합 층(210)의 부분은 수용 기판과 접촉하게 배치된다. 이어서, 마이크로 소자 및 접합 층(210)의 부분은 작업(1550)에서 수용 기판 상에 릴리즈된다. 마이크로 소자 및 접합 층(210)의 부분을 꾹입하고, 이송하며, 수용 기판과 접촉시키고, 수용 기판 상에 릴리즈할 때, 접합 층의 부분의 상을 제어하기 위해 다양한 작업들이 수행될 수 있다. 예를 들어, 마이크로 소자와 함께 꾹입되는 접합 층의 부분은 접촉 작업(1545) 중 그리고 릴리즈 작업(1550) 중 액체 상태로 유지될 수 있다. 다른 실시예에서, 접합 층의 부분은 꾹입된 후 고상으로 냉각되는 것이 허용될 수 있다. 예를 들어, 접합 층의 상기 부분은 접촉 작업(1545) 중 고상일 수 있고, 릴리즈 작업(1550) 전에 또는 릴리즈 작업(1550) 동안에 액체 상태로 다시 용융될 수 있다. 다양한 온도 및 재료 상 사이클(phase cycle)이 본 발명의 실시예들에 따라 수행될 수 있다.

[0064]

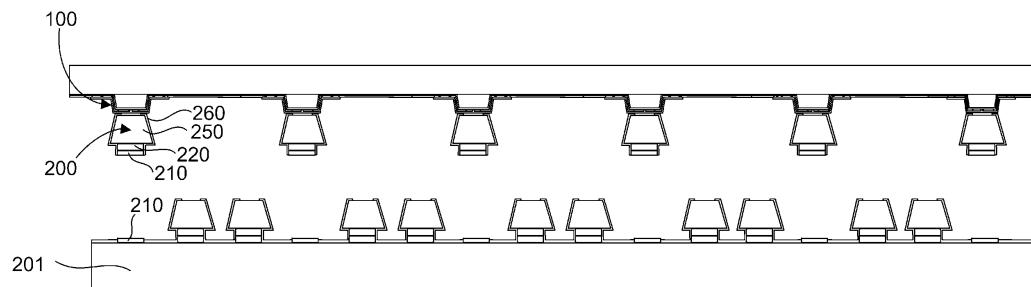

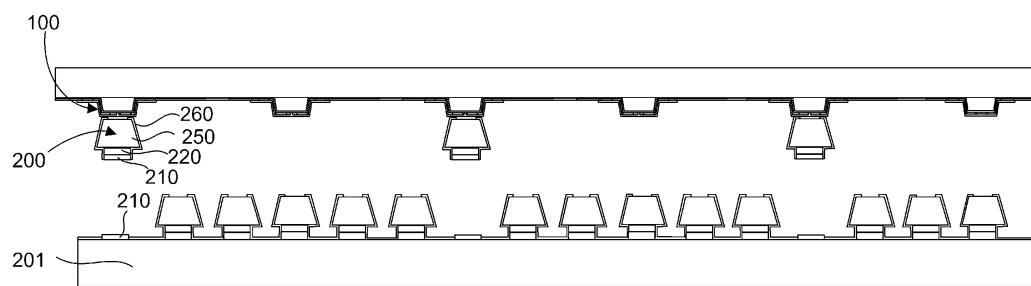

도 16은 본 발명의 일 실시예에 따른 캐리어 기판으로부터 적어도 하나의 수용 기판으로 마이크로 소자들의 어레이를 꾹입하고 이송하는 방법을 예시한 흐름도이다. 작업(1610)에서, 이송 헤드들의 어레이가 마이크로 소자들의 어레이 위에 위치되며, 이때 각각의 이송 헤드는 메사 구조체, 메사 구조체 위의 전극, 및 전극을 덮는 유전체 층을 구비한다. 작업(1620)에서, 마이크로 소자들의 어레이는 이송 헤드들의 어레이와 접촉된다. 대안적인 실시예에서, 이송 헤드들의 어레이는 마이크로 소자들의 어레이 위에 위치되되, 그것들을 분리하는, 그립 압력에 현저히 영향을 미치지 않는, 예를 들어 1 nm(0.001  $\mu\text{m}$ ) 또는 10 nm(0.01  $\mu\text{m}$ )인 적합한 에어 캡을 갖고서 위치된다. 도 17은 본 발명의 일 실시예에 따른 마이크로 LED 소자들(200)의 어레이와 접촉하는 마이크로 소자 이송 헤드들(100)의 어레이의 측면도이다. 도 17에 예시된 바와 같이, 이송 헤드들(100)의 어레이의 피치(P)는 마이크로 LED 소자들(200)의 피치와 매칭되며, 이때 이송 헤드들의 어레이의 피치(P)는 이송 헤드들 사이의 간격(S)과 이송 헤드의 폭(W)의 합이다.

[0065]

일 실시예에서, 마이크로 LED 소자들(200)의 어레이는 10  $\mu\text{m}$ 의 피치를 가지며, 이때 각각의 마이크로 LED 소자는 2  $\mu\text{m}$ 의 간격과 8  $\mu\text{m}$ 의 최대 폭을 갖는다. 예시적인 실시예에서, 수직형 측벽을 갖춘 마이크로 p-n 다이오드(250)를 가정하면, 각각의 마이크로 LED 소자(200)의 상부 표면은 폭이 대략 8  $\mu\text{m}$ 이다. 이러한 예시적인 실시

예에서, 대응하는 이송 헤드(100)의 상부 표면(121)의 폭은 인접한 마이크로 LED 소자와의 의도하지 않은 접촉을 피하기 위해 대략  $8 \mu\text{m}$  이하이다. 다른 실시예에서, 마이크로 LED 소자들(200)의 어레이는  $5 \mu\text{m}$ 의 피치를 가질 수 있으며, 이때 각각의 마이크로 LED 소자는  $2 \mu\text{m}$ 의 간격과  $3 \mu\text{m}$ 의 최대 폭을 갖는다. 예시적인 실시예에서, 각각의 마이크로 LED 소자(200)의 상부 표면은 폭이 대략  $3 \mu\text{m}$ 이다. 이러한 예시적인 실시예에서, 대응하는 이송 헤드(100)의 상부 표면(121)의 폭은 인접한 마이크로 LED 소자(200)와의 의도하지 않은 접촉을 피하기 위해 대략  $3 \mu\text{m}$  이하이다. 그러나, 본 발명의 실시예는 이들 특정 치수로 한정되지 않고, 임의의 적절한 치수일 수 있다.

[0066] 도 18는 본 발명의 일 실시예에 따른 마이크로 LED 소자들(200)의 어레이와 접촉하는 마이크로 소자 이송 헤드들의 어레이의 측면도이다. 도 18에 예시된 실시예에서, 이송 헤드들의 피치(P)는 마이크로 소자들의 어레이의 피치의 정수배이다. 예시된 특정 실시예에서, 이송 헤드들의 피치(P)는 마이크로 LED 소자들의 어레이의 피치의 3배이다. 이러한 실시예에서, 보다 큰 이송 헤드 피치를 갖는 것은 이송 헤드들 사이의 아킹을 방지할 수 있다.

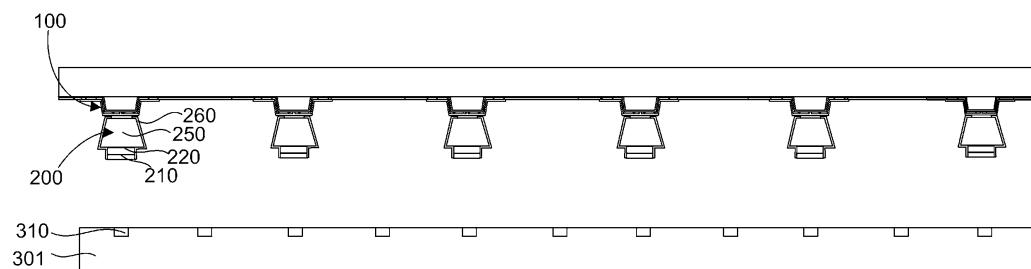

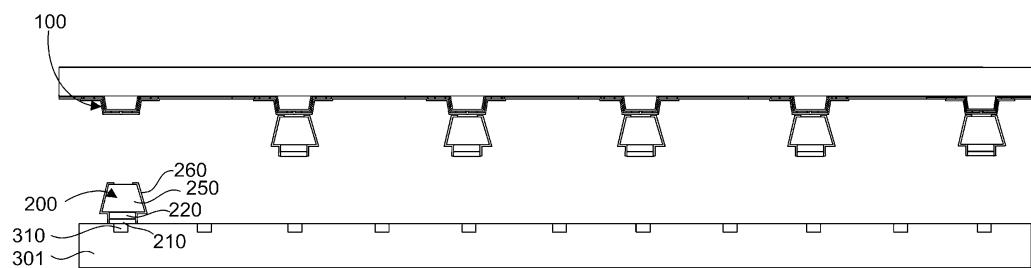

[0067] 다시 도 16를 참조하면, 작업(1630)에서, 이송 헤드들(100)의 어레이의 일부분에 전압이 선택적으로 인가된다. 따라서, 각각의 이송 헤드(100)는 독립적으로 작동될 수 있다. 작업(1640)에서, 전압이 선택적으로 인가되었던 이송 헤드들의 어레이의 상기 부분으로 마이크로 소자들의 어레이의 대응하는 부분이 꾹눌린다. 일 실시예에서, 이송 헤드들의 어레이의 일부분에 전압을 선택적으로 인가하는 것은 이송 헤드들의 어레이 내의 모든 이송 헤드에 전압을 인가하는 것을 의미한다. 도 19는 본 발명의 일 실시예에 따른 마이크로 LED 소자들(200)의 어레이를 꾹눌린 마이크로 소자 이송 헤드들의 어레이 내의 모든 이송 헤드의 측면도이다. 다른 실시예에서, 이송 헤드들의 어레이의 일부분에 전압을 선택적으로 인가하는 것은 이송 헤드들의 어레이 내의 모든 이송 헤드보다 적은 이송 헤드들(예컨대, 이송 헤드들의 부분 세트)에 전압을 인가하는 것을 의미한다. 도 20은 본 발명의 일 실시예에 따른 마이크로 LED 소자들(200)의 어레이의 일부분을 꾹눌린 마이크로 소자 이송 헤드들의 어레이의 부분 세트의 측면도이다. 도 19 및 도 20에 예시된 특정 실시예에서, 꾹눌림 작업은 마이크로 LED 소자(200)에 대한 마이크로 p-n 다이오드(250), 금속화 층(220), 및 컨포멀 유전체 장벽 층(260)의 일부분을 꾹눌린 것을 포함한다. 도 19 및 도 20에 예시된 특정 실시예에서, 꾹눌림 작업은 접합 층(210)의 상당 부분을 꾹눌린 것을 포함한다. 따라서, 도 16 내지 도 22에 관하여 기술된 임의의 실시예가 또한 도 15에 관하여 기술된 바와 같이 접합 층(210)의 상기 부분의 온도를 제어하는 것을 동반할 수 있다. 예를 들어, 도 16 내지 도 22에 관하여 기술된 실시예들은 마이크로 소자들의 어레이를 꾹눌리하기 전에 마이크로 소자들의 어레이를 캐리어 기판(201)에 연결하는 복수의 위치의 접합 층에 고체 상태에서 액체 상태로 상 변화를 일으키기 위해 작업을 수행하는 것을 포함할 수 있다. 일 실시예에서, 복수의 위치의 접합 층은 동일한 접합 층의 영역들일 수 있다. 일 실시예에서, 복수의 위치의 접합 층은 접합 층의 측방향으로 분리된 위치들일 수 있다.

[0068] 이어서, 작업(1650)에서, 마이크로 소자들의 어레이의 부분이 적어도 하나의 수용 기판 상에 텔리즈된다. 따라서, 마이크로 LED들의 어레이가 모두 단일 수용 기판 상에 텔리즈되거나 다수의 기판 상에 선택적으로 텔리즈될 수 있다. 예를 들어, 수용 기판은 디스플레이 기판, 조명 기판, 트랜지스터 또는 IC와 같은 기능 소자를 갖춘 기판, 또는 금속 재분배선을 갖춘 기판일 수 있지만 이에 한정되지 않는다. 텔리즈는 도 12 내지 도 14에 관하여 기술된 임의의 방식으로 인가 전압에 영향을 줌으로써 달성될 수 있다.

[0069] 도 21은 복수의 드라이버 콘택(driver contact)(310)을 포함하는 수용 기판(301) 위에 대응하는 마이크로 LED 소자들(200)의 어레이를 유지시키는 마이크로 소자 이송 헤드들의 어레이의 측면도이다. 이어서, 마이크로 LED 소자들(200)의 어레이가 수용 기판과 접촉하도록 배치된 다음에 선택적으로 텔리즈될 수 있다. 도 22는 본 발명의 일 실시예에 따른 드라이버 콘택(310) 위로 수용 기판(301) 상에 선택적으로 텔리즈된 단일 마이크로 LED 소자(200)의 측면도이다. 다른 실시예에서, 2개 이상의 마이크로 LED 소자(200)가 텔리즈되거나, 또는 마이크로 LED 소자들(200)의 어레이 전체가 텔리즈된다.

[0070] 본 발명의 다양한 양태를 활용함에 있어, 마이크로 소자 이송 헤드 및 헤드 어레이를 형성하고 마이크로 소자 및 마이크로 소자 어레이를 이송하기 위해 위의 실시예의 조합 또는 변형이 가능한 것이 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 명백해질 것이다. 본 발명이 구조적 특징 및/또는 방법론적 동작에 특정한 표현으로 기술되었지만, 첨부된 특허청구범위에 정의된 발명이 반드시 기술된 특정 특징 또는 동작으로 한정되지는 않는 것이 이해되어야 한다. 대신에, 개시된 특정 특징 및 동작은 본 발명을 예시하는 데 유용한 청구된 발명의 특히 세련된 구현으로 이해되어야 한다.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

## 도면14

## 도면15

## 도면16

## 도면17

## 도면18

도면19

도면20

도면21

도면22

## 도면23

## 도면24

## 도면25

도면26

도면27

도면28

도면29