(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6396450号

(P6396450)

(45) 発行日 平成30年9月26日(2018.9.26)

(24) 登録日 平成30年9月7日(2018.9.7)

(51) Int.Cl.

F 1

H01Q 5/378 (2015.01)

H01Q 1/52 (2006.01)H01Q 5/378

H01Q 1/52

請求項の数 9 (全 19 頁)

(21) 出願番号 特願2016-523801 (P2016-523801)

(86) (22) 出願日 平成26年6月18日 (2014.6.18)

(65) 公表番号 特表2016-524427 (P2016-524427A)

(43) 公表日 平成28年8月12日 (2016.8.12)

(86) 國際出願番号 PCT/US2014/043017

(87) 國際公開番号 WO2015/002741

(87) 國際公開日 平成27年1月8日 (2015.1.8)

審査請求日 平成29年5月19日 (2017.5.19)

(31) 優先権主張番号 13/932,105

(32) 優先日 平成25年7月1日 (2013.7.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

Q U A L C O M M I N C O R P O R A T

E D

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】共有された接地構造を有するアンテナ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のモノポール素子と、

第2のモノポール素子と、

前記第1および第2のモノポール素子の両方に容量結合された共通構造と、

前記共通構造を接地素子に導電結合するように構成された接続ストリップと、ここにおいて、前記接続ストリップは、前記第1および第2のモノポール素子の間に位置する、を備え、

ここにおいて、前記第1のモノポール素子、前記共通構造、および前記接続ストリップは、第1のモノポールアンテナのための共振器構造を形成するように構成され、前記第2のモノポール素子、前記共通構造、および前記接続ストリップは、第2モノポールアンテナのための共振器構造を形成するように構成され。

10

前記第1および第2のモノポール素子の各々は、それぞれの駆動ポートにそれぞれの短い伝導性ストリップにより結合され、前記短い導電ストリップおよび前記接続ストリップは、前記第1および前記第2のモノポール素子が提供されている水平面上に垂直な垂直面上に位置している、装置。

## 【請求項 2】

ボードをさらに備え、前記第1および第2のモノポール素子は、前記ボードの反対側に配置されており、任意で、前記第1および第2のモノポール素子は、前記ボードの端上に位置する、請求項1に記載の装置。

**【請求項 3】**

前記共通構造は、接続点によって結合された第1および第2のブランチを備え、前記第1および第2のブランチは、それぞれ、前記第1および第2のモノポール素子に容量結合されている、請求項1に記載の装置。

**【請求項 4】**

前記第1および第2のブランチのうちの少なくとも1つは、パターン化導電素子を備える、請求項3に記載の装置。

**【請求項 5】**

前記モノポール素子および前記接続ストリップの間の空間を満たすFR4基板をさらに備える、請求項1に記載の装置。 10

**【請求項 6】**

前記共通構造は、前記垂直面上に位置している部分および前記水平面上に位置している部分を備える、請求項1に記載の装置。

**【請求項 7】**

前記共通構造は、前記2つのモノポール素子と比べてかなり大きなサイズを有する、請求項1に記載の装置。

**【請求項 8】**

前記モノポール素子および共通構造により占有されたのと同じボリュームで提供された追加のモジュールをさらに備える、請求項1に記載の装置。 20

**【請求項 9】**

前記追加のモジュールは、USBコネクタを備える、請求項8に記載の装置。

**【発明の詳細な説明】****【関連出願の相互参照】****【0001】**

[0001] 本願は、2013年7月1日に出願された、同一出願人による米国仮特許出願第13/932,105号からの優先権を主張し、その内容は、ここに全文を参照により明確に組み込まれる。

**【技術分野】****【0002】**

[0002] 本開示は、ワイヤレス通信デバイスのためのアンテナに関する。 30

**【背景技術】****【0003】**

[0003] スマートフォンといった最先端のワイヤレス通信デバイスは、例えばロングタームエボリューション(LTE)システムおよび他の既存のワイヤレスワイドエリアネットワーク(WWAN)モバイルネットワークによって要求される(dictated)ように、複数の周波数帯域を収容するためにプロードバンドアンテナをしばしば必要とする。例えば、現在の第4世代(4G)LTEスマートフォンは、典型的に、グローバルポジショニングシステム(GPS)帯(1.575GHz)といった他の帯に加えて、LTE700(698-787MHz)、GSM(登録商標)850(824-894MHz)、GSM900(880-960MHz)等を含む、複数の周波数帯をサポートすることを必要とする。いくつかの実現において、ワイヤレスデバイスは、8または9周波数帯と同数、またはそれ以上にわたって無線信号を処理することを必要とし得る。 40

**【0004】**

[0004] そのような複数の周波数帯をサポートするために、ワイヤレスデバイスは、例えば、700MHz-960MHzにわたる低プロードバンドおよび1710MHz-2690MHzにわたる高プロードバンドといった上述した周波数帯を集合的にカバーする2つまたはそれ以上のプロードバンドにわたって動作するアンテナを用い得る。アンテナ設計の技法により、小さなアンテナサイズは通常狭帯域幅および低放射効率に対応する。したがって、そのようなプロードバンドを収容するために、各アンテナは最小のボリュームまたは隙間(clearance)を必要とし、それは設計のために最小サイズを指定する。現 50

代のワイヤレスデバイスの別の態様において、複数のアンテナが、ワイヤレスチャネル容量を向上するために多入力多出力（MIMO）として知られる特徴を実現することが必要とされる。

#### 【0005】

[0005] 上述した特徴を収容するために、ワイヤレスデバイスは、典型的に2つまたはそれ以上のアンテナを含むことが必要とされ得る。しかしながら、電話サイズの縮小、インダストリアルデザイン（ID：industrial design）の最適化、および機能の増加への継続的な傾向により、ワイヤレスデバイス内に非常に限られた内部のスペースがアンテナのために残されている。これらの考慮すべき事項は、アンテナが制限された小さなスペースで提供されるが、それにもかかわらず十分に大きな帯域幅および放熱性能（radiation performance）を提示しなければならないため、ワイヤレスデバイスのためのLTE/MIMOアンテナの設計を複雑にする。10

#### 【0006】

[0006] したがって、比較的小さな物理的寸法を有する、十分な帯域幅および性能を有するワイヤレスデバイスのための複数のアンテナを設計するための技法を提供することが所望され得る。

#### 【図面の簡単な説明】

#### 【0007】

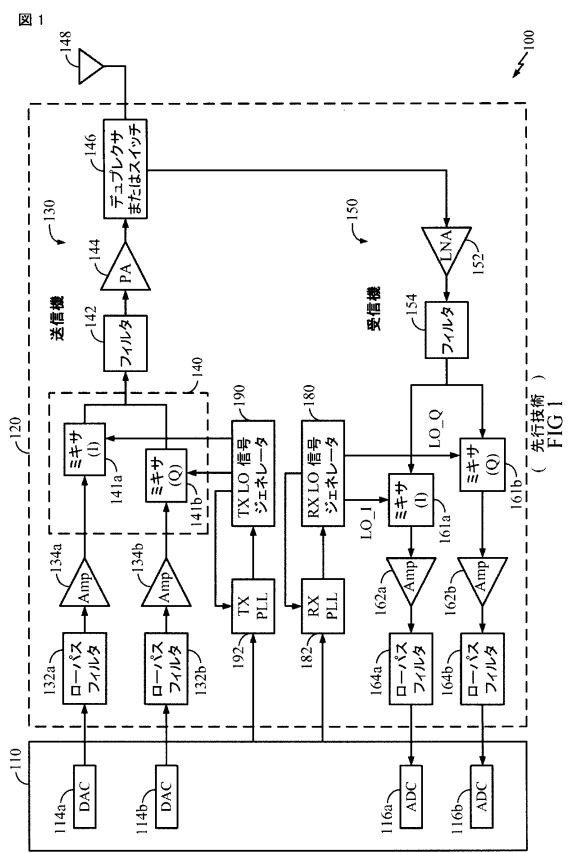

【図1】[0007] 図1は、本開示の技法が実現され得る先行技術のワイヤレス通信デバイス100の設計のブロック図を図示する。20

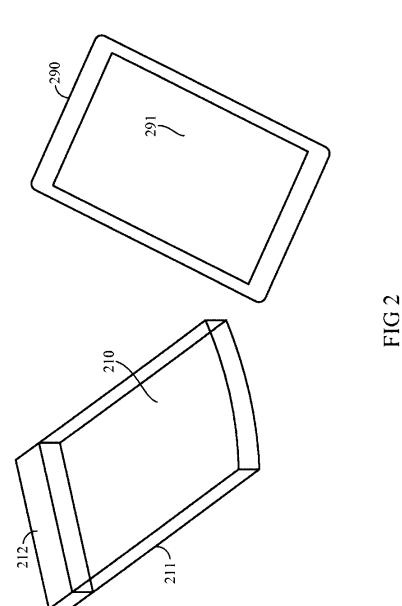

【図2】[0008] 図2は、本開示にしたがって複数のアンテナを収容する装置の例示的な実施形態を図示する。

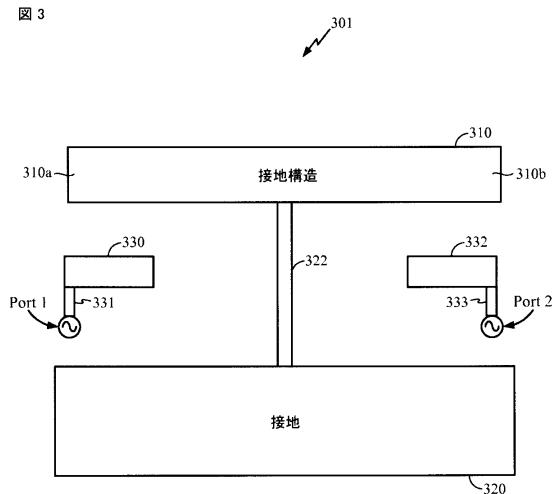

【図3】[0009] 図3は、本開示にしたがうアンテナ構造の例示的な実施形態を図示する。。

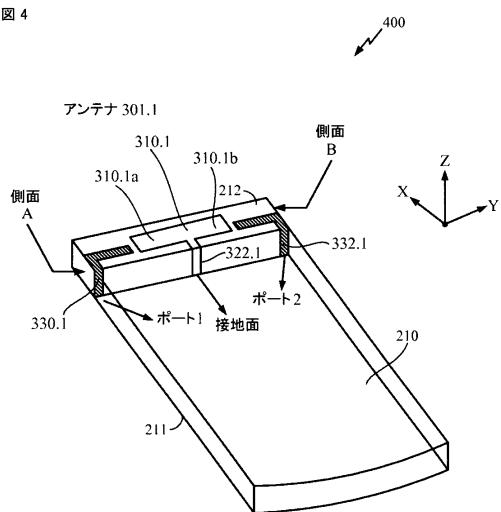

【図4】[0010] 図4は、本開示にしたがうモバイルデバイスと統合されたアンテナ素子を示す装置の例示的な実施形態を図示する。

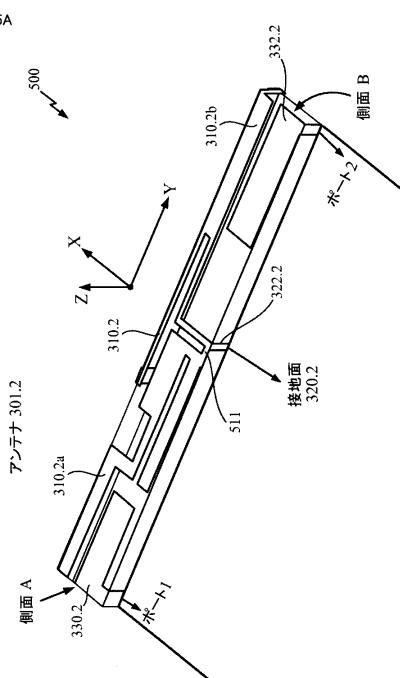

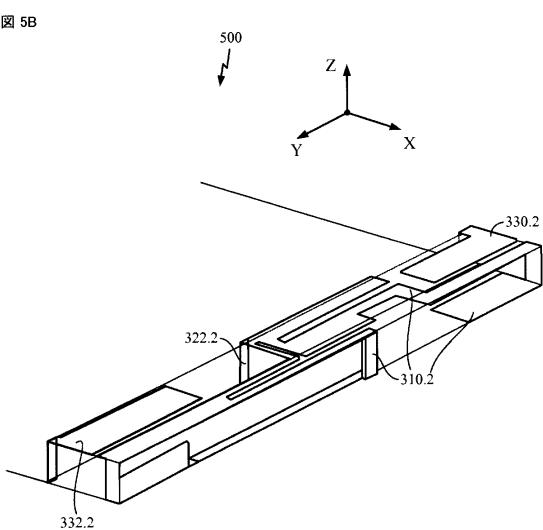

【図5A】[0011] 図5Aは、本開示にしたがうアンテナの代替的な例示的な実施形態の透視図を図示する。

【図5B】[0011] 図5Bは、本開示にしたがうアンテナの代替的な例示的な実施形態の透視図を図示する。30

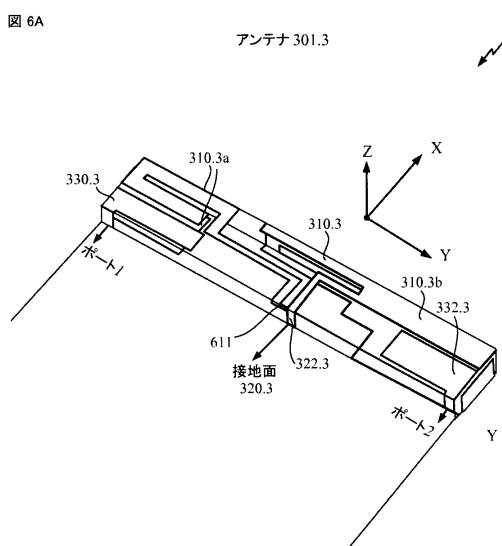

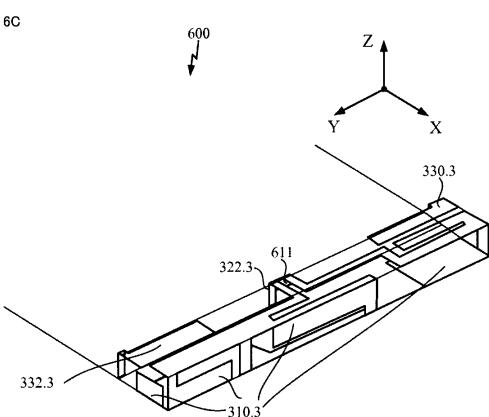

【図6A】[0012] 図6Aは、本開示にしたがうアンテナの代替的な例示的な実施形態の透視図を図示する。

【図6B】[0012] 図6Bは、本開示にしたがうアンテナの代替的な例示的な実施形態の透視図を図示する。

【図6C】[0012] 図6Cは、本開示にしたがうアンテナの代替的な例示的な実施形態の透視図を図示する。

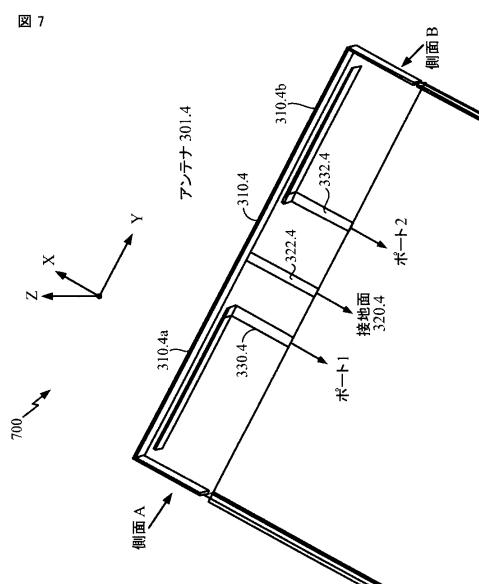

【図7】[0013] 図7は、アンテナの代替的な例示的な実施形態を図示する。

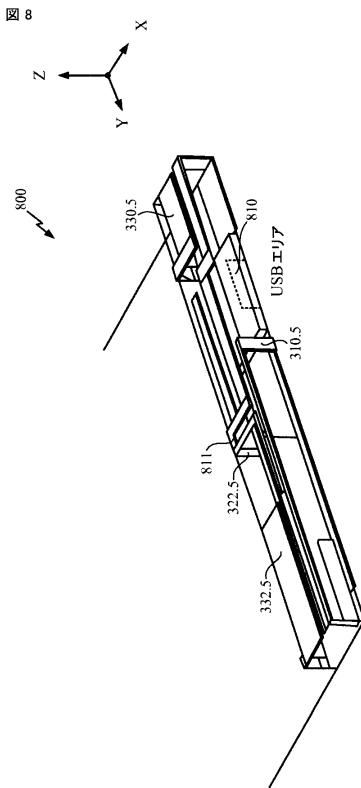

【図8】[0014] 図8は、本開示の代替的な例示的な実施形態を図示し、本開示のアンテナ技法は装置の追加のモジュールを収容するための技法と統合される。

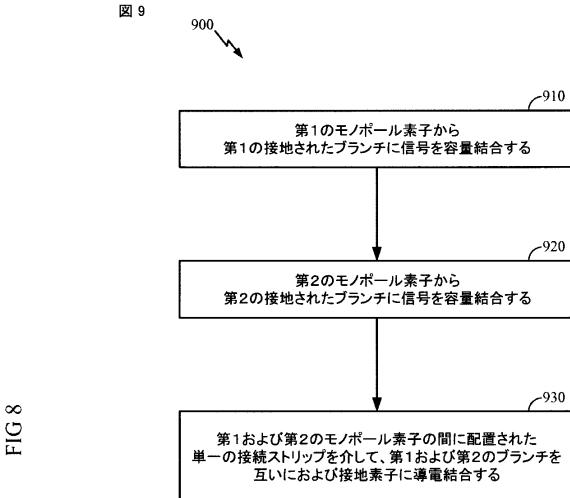

【図9】[0015] 図9は、本開示にしたがう方法の例示的な実施形態を図示する。40

#### 【詳細な説明】

#### 【0008】

[0016] 下記において、添付の図面を参照し、本開示の様々な態様がより十分に説明される。しかしながら、本開示は、多くの異なる形態で具現化できることができる、この開示全体を通して提示される任意の特定の構成または機能に限定されると解釈されなければならない。むしろ、これらの態様は、本開示が徹底的で完全であり、当業者に本開示の範囲を十分に伝えるように提供される。本明細書における教示に基づいて、本開示の範囲が、本発明の任意の他の態様から独立して、または、それらと組み合わせて、実現されるか否かにかかわらず、ここに開示する開示の任意の態様をカバーするように意図されていることを、当業者は理解するべきである。例えば、ここで述べられる態様の任意の数を使用して50

、装置が実現され、または方法が実施され得る。加えて、本開示の範囲は、ここで述べた開示の様々な態様に加えた、または、それら以外の、他の構成、機能性、または、構成および機能性を使用して実施されるこのような装置または方法をカバーすることを意図している。ここで開示される開示の任意の態様が、請求項の1つまたはそれ以上の要素によって具現化され得ることが理解されるべきである。

#### 【0009】

[0017] 添付図面に関連して以下に述べられる詳細な説明は、本発明の例示的な態様の説明として意図され、本発明が実施され得る唯一の例示的な態様を表すようには意図されない。本明細書の全体にわたって使用される「例示的 (exemplary)」という用語は、「例、事例、または例示としての役目をする」ことを意味し、他の例示的な態様に対して必ずしも好ましいまたは有利であると解釈されるべきではない。詳細な説明は、本発明の例示的な態様の完全な理解を提供する目的のために特定の詳細を含む。本発明の例示的な態様は、これらの特定の詳細なしで実現され得ることが当業者にとって明らかであろう。いくつかの事例では、周知の構造およびデバイスが、ここに提示される例示的な態様の新規性を曖昧にすることを避けるために、ブロック図形式で示される。本明細書および特許請求の範囲では、「モジュール」という用語は、説明された動作を実行するように構成されたエンティティを指すために交換可能に使用され得る。10

#### 【0010】

[0018] 図1は、本開示の技法が実現され得る先行技術のワイヤレス通信デバイス100の設計のブロック図を図示する。図1は、例示的なトランシーバ設計を示す。一般的に、送信機および受信機における信号の条件は、増幅器、フィルタ、アップコンバータ、ダウンコンバータ等の1つまたはそれ以上の段によって実行され得る。これらの回路ブロックは、図1に示された構成とは異なるように配置され得る。さらに、図1に示されていない他の回路ブロックも、送信機および受信機における信号を調整するために使用され得る。記載されない限り、図1における任意の信号、または図面における任意の他の図 (figure) は、シングルエンド (single-ended) または差分 (differential) のいずれかであり得る。図1におけるいくつかの回路ブロックはまた、省略され得る。20

#### 【0011】

[0019] 図1に示される設計において、ワイヤレスデバイス100はトランシーバ120およびデータプロセッサ110を含む。データプロセッサ110は、データおよびプログラムコードを記憶するためにメモリ (示されていない) を含み得る。トランシーバ120は、双方向通信をサポートする送信機130および受信機150を含む。一般的に、ワイヤレスデバイス100は、任意の数の通信システムおよび周波数帯のための任意の数の送信機および / または受信機を含み得る。トランシーバ120の全てまたは一部は、1つまたはそれ以上のアナログ集積回路 (IC)、RF IC (RFIC)、混合信号IC等の上で実現され得る。30

#### 【0012】

[0020] 送信機または受信機は、スーパーへテロダインアーキテクチャ (super-heterodyne architecture) またはダイレクトコンバージョンアーキテクチャ (direct-conversion architecture) によって実現され得る。スーパーへテロダインアーキテクチャにおいて、信号は、例えば1つの段において無線周波数 (RF) から中間周波数 (IF) へ、そして受信機のための別の段においてIFからベースバンドへというように、多段でRFおよびベースバンド間で周波数変換される。ダイレクトコンバージョンアーキテクチャにおいて、信号は、1つの段においてRFおよびベースバンド間で周波数変換される。スーパーへテロダインおよびダイレクトコンバージョンアーキテクチャは、異なる回路ブロックを使用し得る、および / または異なる要件を有し得る。図1に示される設計において、送信機130および受信機150は、ダイレクトコンバージョンアーキテクチャによって実現される。40

#### 【0013】

[0021] 送信経路において、データプロセッサ110は、送信されるべきデータを処理50

し、送信機 130 に I および Q アナログ出力信号を提供する。示される例示的な実施形態において、データプロセッサ 110 は、さらなる処理のために、データプロセッサ 110 によって生成されたデジタル信号を I および Q アナログ出力信号、例えば I および Q 出力電流に変換するためのデジタルアナログ変換器 (D A C) 114a および 114b を含む。

#### 【0014】

[0022] 送信機 130 内で、ローパスフィルタ 132a および 132b は、以前のデジタルアナログ変換によって生じた所望されない画像を除去するために、それぞれ、I および Q アナログ出力信号をフィルタリングする。増幅器 (Amp) 134a および 145b は、それぞれ、ローパスフィルタ 132a および 132b からの信号を増幅し、I および Q ベースバンド信号を提供する。アップコンバータ 140 は、送信 (T X) 局部発振器 (L O) 信号ジェネレータ 190 からの I および Q T X L O 信号を用いて I および Q ベースバンド信号をアップコンバートし、アップコンバートされた信号を提供する。フィルタ 142 は、周波数アップコンバージョンおよび受信周波数帯におけるノイズによって生じる所望でない画像を除去するためにアップコンバートされた信号をフィルタリングする。電力増幅器 (P A) 144 は、所望の出力電力レベルを取得し、送信 R F 信号を提供するために、フィルタ 142 からの信号を増幅する。送信 R F 信号は、デュプレクサまたはスイッチ 146 を通り (routed through)、アンテナ 148 を介して送信される。

#### 【0015】

[0023] 受信経路において、アンテナ 148 は、基地局によって送信された信号を受信し、受信された R F 信号を提供し、それはデュプレクサまたはスイッチ 146 を通り、低ノイズ増幅器 (L N A) 152 に提供される。デュプレクサ 146 は、R X 信号が T X 信号から切り離されるように、特定の R X T X デュプレクサ周波数分離によって動作するように設計される。受信された R F 信号は、所望の R F 入力信号を取得するために、L N A 152 によって増幅され、フィルタ 154 によってフィルタリングされる。ダウンコンバージョンミキサ 161a および 161b は、I および Q ベースバンド信号を生成するために、フィルタ 154 の出力を、R X L O 信号ジェネレータ 180 からの I および Q 受信 (R X) L O 信号 (すなわち、L O\_I および L O\_Q) とミキシングする。I および Q ベースバンド信号は、I および Q アナログ入力信号を取得するために、増幅器 162a および 162b によって増幅され、ローパスフィルタ 164a および 164b によってさらにフィルタリングされ、それはデータプロセッサ 110 に提供される。示される例示的な実施形態において、データプロセッサ 110 は、データプロセッサ 110 によってさらに処理されるようにアナログ入力信号をデジタル信号に変換するためのアナログデジタルコンバータ (A D C) 116a および 116b を含む。

#### 【0016】

[0024] 図 1において、T X L O 信号ジェネレータ 190 は、周波数アップコンバージョンに使用される I および Q T X L O 信号を生成し、一方で R X L O 信号ジェネレータ 180 は、周波数ダウンコンバージョンに使用される I および Q T X L O 信号を生成する。各 L O 信号は、特定の基本周波数を有する周期信号である。P L L 192 は、データプロセッサ 110 からタイミング情報を受信し、L O 信号ジェネレータ 190 からの T X L O 信号の周波数および / または位相を調節するために使用される制御信号を生成する。同様に、P L L 182 は、データプロセッサ 110 からタイミング情報を受信し、L O 信号ジェネレータ 180 からの R X L O 信号の周波数および / または位相を調節するために使用される制御信号を生成する。

#### 【0017】

[0025] (図 1 に示されていない) ある実現において、バラン (balun) が、受信機 150 の L N A 152 および ミキサ 161a、161b の出力の間で提供され得る。バランは、シングルエンド信号を差分信号に変換し得、例えば、信号を一次巻線 (primary winding) から二次巻線 (secondary winding) に相互に結合する変換器を含み得る。さらに、示されていないある代替的な実現において、複数の L N A 152 が提供され得、各 L N A

10

20

30

40

50

は特定の周波数帯における入力 R F 信号を処理するために最適化される。

**【 0 0 1 8 】**

[0026] ある特定の実現において、1つより多いアンテナ 148 は、電話内のある特定のワイヤレス技法、例えば多入力多出力（MIMO）またはダイバーシティアプリケーションを収容するために提供され得る。そのような実現において、複数のアンテナは電話内のスペースの相当量、例えば電話の底面の1つのプライマリアンテナ、および電話の上部の1つのダイバーシティアンテナを占有し得る。代わりに、2つのアンテナは、電話の底面に並んで提供され得、それはアンテナサイズ全体を縮小するが、性能を望ましくなく妥協し得る。現代のワイヤレスデバイスにおける厳格なフォームファクター制限により、デバイスにおいてより少ないエリアを消費するアンテナを提供する目的で、多くの設計者がアンテナ帯域幅を制限することを、またはそうでなければアンテナ性能を犠牲にすることを選ぶ。

10

**【 0 0 1 9 】**

[0027] 本開示は、先行技術の技法と比べてワイヤレスデバイスにおいてより少ないエリアを消費しながら、広帯域幅にわたって改善された放射効率を有する二重のまたはそれ以上のアンテナを設計するための技法を提供する。

**【 0 0 2 0 】**

[0028] 図2は、本開示にしたがって複数のアンテナを収容する装置200の一部を図示する。図2に示されるパーツは例示的な目的のために提供されるにすぎず、本開示の範囲を限定することは意図しないことに留意する必要がある。例えば、他の図、開示、および特許請求の範囲に関連して以下にさらに説明されるように、代替的な例示的な実施形態が、代替的な構成、例えば図2に明示的に示されるものとは異なるものを組み込み得る。

20

**【 0 0 2 1 】**

[0029] 図2において、装置200のコンポーネント、例えば携帯電話が、本開示のある特定の態様を強調表示するために図示される。特に、例えばスクリーン291（例えば、タッチスクリーンまたは他のタイプのスクリーン）を組み込む、装置200の前面290が、装置200の本体211から切り離して示される。電話の本体211の一端、例えば上端または下端で提供されるのが、基板212である。ある例示的な実施形態において、基板212は、当業者に知られるFR-4基板であり得る。例示的な実施形態において、基板212は、以下にさらに説明されるアンテナ素子を適所に保持するための支持構造を提供し得る。例示的な実施形態において、基板212は、空洞を有し得、装置200の（示されていない）追加の要素は、基板212のそのような空洞によって定義されるスペース内に提供され得る。電話の本体211は、平らで水平な伝導性表面（flat horizontal conducting surface）であり、および/または装置200の本体211の大きな表面エリアと実質的に物理的に同延（co-extensive）であり得る接地板210をさらにサポートする。

30

**【 0 0 2 2 】**

[0030] 図3は、本開示にしたがうアンテナ構造301の例示的な実施形態を図示する。アンテナ装置構造301は、例示の目的のみで示され、本開示の範囲を限定することは意図しないことに留意する必要がある。アンテナ構造301の素子と、ワイヤレスデバイスの残りの部分、例えば図2に示されるような装置200、との統合が、例えば図4-8に関して、以下のさらなる開示を参照して当業者に明確になるであろうことが理解される。

40

**【 0 0 2 3 】**

[0031] 図3において、アンテナ構造301は、第1および第2のモノポール（アンテナ）素子330、332を含む。第1のモノポール素子330が、図3におけるポート1でも表される、駆動端（driving terminal）に短い伝導性ストリップ（short conductive strip）331によって結合される。第2のモノポール素子332は、駆動端ポート0に短い伝導性ストリップ333によって結合される。2つのモノポール素子330、332は、互いに独立した設計仕様を有し得、それぞれ、例えばプライマリアンテナおよびセカ

50

ンダリアンテナに対応し得る。プライマリおよびセカンダリアンテナは、本願に依存して、例えば独立信号によって、駆動され得ることが理解されるべきである。

#### 【0024】

[0032] ある特定の例示的な実施形態において、2つのモノポール素子330、332は、アンテナの高帯域放射に部分的に関与し得る。例えば、例示的な実施形態において、プライマリモノポール素子は、-4dBの利得を有する700-960MHzおよび1710-2170MHzの周波数範囲をカバーするように設計され得る一方で、ダイバーシティモノポール素子は、-7dBの利得を有する734-960MHzおよび1805-2170MHzの周波数帯をカバーするように設計され得る。

#### 【0025】

[0033] モノポール素子330、332の各々は、共通のまたは共有された接地構造310（本明細書において「共通構造」としても表される）に容量結合（capacitively coupled）される。接地構造310は、接地素子（または接地板）320に接地ストリップ322（本明細書において「接続ストリップ」としても表される）を介して導電結合（conductively coupled）される。例示的な実施形態において、接地板320は、図2における接地板210に対応し得る。接地構造310、接地ストリップ322、および接地素子320は全て導体であり、互いに相互に導電結合されることに留意する必要がある。共通の接地構造310は、2つのプランチ310aおよび310bを含み得、310aは第1のモノポール素子330により物理的に近く、310bは第1のモノポール素子332により物理的に近い。したがって、プランチ310aは、第1のモノポール素子330と容量結合されていると理解され得る一方で、プランチ310bは、第2のモノポール素子332と容量結合されていると理解され得る。

#### 【0026】

[0034] 2つのプランチ310aおよび310bへの接地構造の図3における区切りは、説明目的でのみなされることに留意する必要がある。実践的な実現では、接地構造310の全ての部分は単一の導体素子を形成するために互いに導電結合されることが理解されるため、プランチ310a、310b間に実際の物理的な区切りが存在する必要はない。

#### 【0027】

[0035] 第1のモノポール素子330と関連付けられた第1のプランチ310aを第2のモノポール素子332と関連付けられた第2のプランチ310bに導電結合することによって、2つのモノポール素子330、332は、単一の接地構造310を効率的に共有する。増加された共振器サイズは、特により低い周波数で、共振の線質係数（quality factor）を減少させ、帯域幅を増加することが理解される。（「共振器」構造は、ポート1励振のための330、322、310、およびポート2励振のための332、322、および310の組み合わせに対応するとしてここに定義され得ることに留意すべきである。）したがって、共有された接地構造310を提供することは、例えば、第1のモノポール素子330と関連付けられた接地構造が第2のモノポール素子332と関連付けられた接地構造と物理的に分離された、代替的な実現と比較して、各モノポールアンテナの有効なサイズを有利に増加させる。モノポールアンテナの有効なサイズを増加させることは、構造のコンパクトな物理的次元が与えられたモノポール素子330、332の両方について比較的広い帯域幅を達成しながら、それらの放熱性能を改善することが理解される。

#### 【0028】

[0036] 例示的な実施形態において、「1つのポート励振」スキームが適用されることができ、2つのモノポール素子330、332のうちの1つのみが任意の時間に駆動される。モノポール素子330、332のうちの1つがアクティブな信号により駆動されるとき、駆動されるモノポール素子に物理的により近い接地されたプランチ310aまたは310bは、強く共振することが予期され、駆動されないモノポール素子にはより弱く結合される。例えば、ポート1が素子330を駆動するがポート2が素子332を駆動しない場合、接地構造310のプランチ310aのみが強く共振することが予期される一方で、プランチ310bは弱くのみ共振することが予期される。

10

20

30

40

50

## 【0029】

[0037] 例示的な実施形態において、共有された接地構造310を接地板320に結合する伝導性ストリップ322は、モノポール素子330、332間で提供される。例えば、1つの例示的な定義につき、(図3に示されていない)「連結軸(connecting axis)」が、第1のモノポール素子330上の点を第2のモノポール素子332上の点と接続することとして定義される場合、接地ストリップ322上の点は、一般的に、第1および第2のモノポール素子330および332に対応する座標間に位置するそのような連結軸に沿って座標を有し得る。「連結軸」のこの例示的な定義は、例示的な目的でのみ与えられ、当業者は第1および第2のモノポール素子330および332「間の」接地ストリップ322の配置の代替的な定義を容易に導出し得ることに留意する必要がある。

10

## 【0030】

[0038] 例示的な実施形態において、接地構造310は、モノポール素子330、332と比較して大きく、例えば、(図2に示されていない)装置200の外側部分からモノポール素子330、332を追加的にシールドし得る。比較的大きなサイズの接地構造310は、静電放電(ESD)によるダメージから、それぞれ、ポート1およびポート2を通じてモノポール素子330、332を給電(feed)する入力/出力信号線をさらに保護し得る。

## 【0031】

[0039] 例示的な実施形態において、基板212(図3に示されていない)、例えばFR-4基板は、図2と関連して上述したアンテナ301の導体素子間の空間に提供され得る。

20

## 【0032】

[0040] 図4は、本開示にしたがってモバイルデバイスと統合されたアンテナ素子を示す装置400の例示的な実施形態を図示する。図4は、例示目的でのみ示され、本開示の範囲を限定することを意図しないことに留意する必要がある。図3の要素と共に数値的識別子を有する図4および残りの図面における特定の要素は、注記されない限り、同様の機能性を有し得ることが理解されるべきである。例えば、図4における接地構造310.1は、図3等における接地構造310について説明されたものと同様の機能性を有し得る。

## 【0033】

30

[0041] 図4において、アンテナ301.1を有する装置400は、それぞれ、ポート1、ポート2によって駆動される第1および第2のモノポール素子330.1、332.1を含む。接地構造310.1は、第1および第2のモノポール素子330.1、332.1の両方に容量結合される。接地ストリップ322.1は、接地構造310.1を装置400の接地板(図4にラベルされていない)に導電結合する。

## 【0034】

[0042] 示される例示的な実施形態において、モノポール素子330.1および332.1は、装置400の反対側、側面Aおよび側面Bに位置付けられる。モノポール素子330.1および332.1のそのような配置は、互いとのそれらのアイソレーションを有利に増加し得ることが理解されるべきである。

40

## 【0035】

[0043] 例示的な実施形態において、アンテナ301.1は8.5mmの(例えば、Z軸に沿って拡張する)接地に対する隙間、4.6mmの(例えば、X軸に沿って拡張する)厚さ、および6.8.5mmの(例えば、Y軸に沿って拡張する)板幅(board width)を有する。特定の寸法は例示目的でのみ与えられ、本開示の範囲を限定することを意図しないことに留意する必要がある。示されるようにアンテナ301.1の素子を提供することによって、二重のまたはもしかするとより多くのアンテナが、比較的コンパクトなボリュームの装置400においてサポートされ得る。

## 【0036】

[0044] 例示的な実施形態400は、モノポール素子330.1、332.1のパーツ

50

および装置 400 の上面（例えば、図 2 に示されるように前面カバー 290 により近い表面）に隣接して配置された接地構造 310.1 を示す一方で、代替的な例示的な実施形態において、モノポール素子 330.1、332.1 および接地構造 310.1 は、代わりに装置 440 の底面に隣接して容易に配置され得る。そのような代替的な例示的な実施形態は、本開示の範囲内であると考慮される。

#### 【0037】

[0045] 図 5A および 5B は、本願にしたがうアンテナ 301.2 の代替的な例示的な実施形態の透視図を図示する。図 5A および図 5B は、例示目的でのみ示され、本開示の範囲を、示される任意の特定のアンテナ構成に限定することを意図しないことに留意する必要がある。

10

#### 【0038】

[0046] 図 5A および図 5B において、第 1 のモノポール素子 330.2 はポート 1 に結合され、第 2 のモノポール素子 332.2 はポート 2 に結合される。接地ストリップ 322.2 は、第 1 および第 2 のモノポール素子 330.2 および 332.2 の両方に容量結合された共有された接地構造 310.2 に接地板 320.2 を結合する。接地構造 310.2 は、短い接続ストリップ 511 を介して（第 2 のモノポール素子 332.2 と容量結合された）第 2 のプランチ 310.2b と導電結合された（第 1 のモノポール素子 330.2 と容量結合された）第 1 のプランチ 310.2a を含む。接地構造 310.2 は、複数の次元（X、Y、および Z 軸に沿って）に拡張し得、例えば、設計の要件にしたがってアンテナ性能を最適化するために、広範囲にパターン化され得る。

20

#### 【0039】

[0047] 示される例示的な実施形態において、接続ストリップ 511 は、接地ストリップ 322.2 に隣接するように提供され、例えば、接続ストリップ 511 および接地ストリップ 322.2 は、アンテナ 301.2 の全体寸法を与えられると互いに比較的に近い X 座標（図 5 で示される X 軸を参照）を有する。接続ストリップ 511 は、モノポール素子の 2 つの接地プランチ 310.2a および 310.2b を互いに導電結合するため、各モノポールアンテナ（例えば、各モノポールアンテナは、モノポール素子のジョイントサイズおよびその関連付けられた接地プランチにより特徴付けられる）の効果的なアンテナサイズを拡大することが理解されるべきである。

30

#### 【0040】

[0048] 図 5A および図 5B において、第 1 のプランチ 310.2a の形状は、例えば、3 つの側面に沿って（例えば、X、Y、および Z 軸に沿って）第 1 のモノポール素子 330.2 に容量結合されるスタブ（stub）および線によって、特徴付けられるパターン化形成（patterned formation）を例示的に含む。第 2 のプランチ 310.2b の形状は、例えば、Y 軸に沿って第 2 のモノポール素子 332.2 に容量結合される導電線によって特徴付けられるパターン化形成を例示的に含む。

#### 【0041】

[0049] 接地構造 310.2 の第 1 のプランチ 310.2a および第 2 のプランチ 310.2b の形状は、例示的な目的でのみ示され、本開示の範囲を限定することを意図しないことが理解されるべきである。代替的な例示的な実施形態において、接地構造 310.2 は、図 5A、図 5B において例示的に示される、または本明細書の他の図面で示されるようにパターン化される必要はない。むしろ、接地構造 310.2 は、図 4 等、またはいずれか任意のプロファイルにより示されるような、単純なプロファイル、例えば、直線の長方形の導電素子を有し得る。そのような代わりの例示的な実施形態は、本開示の範囲内であると考慮される。

40

#### 【0042】

[0050] 2 つのプランチ 310.2a、310.2b の先端を互いから離れて提供することは、ポート 1 およびポート 2 間のより少ない結合（less coupling）を有利にもたらし得ることに留意する必要がある。したがって、接地されたプランチ 310.2a および 310.2b の 2 つの端は、装置 500 の隣接する反対側、側面 A および側面 B に提供さ

50

れ得る。

#### 【0043】

[0051] 給電構造（例えば、素子330.2および332.2）、接続点511、および短絡位置（例えば、素子322.2のY軸に沿う位置）を最適に選択することによって、2つのモノポールアンテナ素子間のアイソレーションは拡大され、またはそうでなければ設計要件にしたがって最適化され得ることがさらに理解されるべきである。

#### 【0044】

[0052] 図6A、図6B、および図6Cは、本開示にしたがってアンテナ301.3を組み込む装置600の代替的な例示的な実施形態の透視図を図示する。図6A、図6B、および図6Cは、例示的な目的でのみ示され、本開示の範囲を限定することを意図しないことに留意する必要がある。

10

#### 【0045】

[0053] 特に、第1のモノポール素子330.3は、ポート1に結合され、第2のモノポール素子332.3は、ポート2に結合される。接地ストリップ322.3は、第1および第2のモノポール素子330.3および332.3の両方を容量結合する共有された接地構造310.3に、接地板320.3を結合する。接地構造310.3は、短い接続ストリップ611を介して（第2のモノポール素子332.3に容量結合された）第2のプランチ310.3bに導電結合された（第1のモノポール素子330.3に容量結合された）第1のプランチ310.3aを含む。示される例示的な実施形態において、接続ストリップ611は、接地ストリップ322.3および共有された接地構造310.3間の接続に隣接して提供される。

20

#### 【0046】

[0054] 接地構造310.3の第1のプランチ310.3aおよび第2のプランチ310.3bのパターン化形状は、例示的な目的でのみ示され、本開示の範囲を限定することを意図しないことが理解されるべきである。（示される軸Zの方向性から留意され得るように）装置600の裏面が表向きに示される透視図を示す図6Bから明確に分かるように、接地素子310.3は、基板212の底面側上の第1のモノポール素子330.3と反対側のエリアをカバーする比較的大きな表面310.3aaを含む。さらに、接地素子310.3は、基板212の底面側上の第2のモノポール素子332.3と反対のエリアをカバーする比較的大きな表面310.3baを含む。

30

#### 【0047】

[0055] ある例示的な実施形態にしたがって、モノポール素子およびそれらのそれぞれの駆動ポート間の接続は、アンテナ構造をサポートする装置の反対側に提供される必要がない。例えば、図7は、アンテナ301.4を組み込む装置700の代替的な例示的な実施形態を図示する。図7において、第1のモノポール素子330.4はポート1に結合され、第2のモノポール素子332.4はポート2に結合される。接地ストリップ322.4は、第1および第2のモノポール素子330.4および332.4の両方に容量結合された、共有された接地構造310.4に接地板320.4を結合する。接地構造310.4は、（第2のモノポール素子332.4に容量結合された）第2のプランチ310.4bに導電結合された（第1のモノポール素子330.4に容量結合された）第1のプランチ310.4aを含む。

40

#### 【0048】

[0056] 例示的な実施形態301.4において、ポート1への第1のモノポール素子330.4の接続、およびポート2へのモノポール素子332.4の接続は、アンテナ301.4を収容する装置700の両側（側面Aおよび側面B）から離れて提供される。特に、ポート1または2へのモノポール素子の接続は、Y軸に沿って、接地ストリップ322.4により近い。

#### 【0049】

[0057] 図8は、本開示のアンテナ技法が装置800の追加のモジュールを収容するための技法と統合された、本開示の代替的な例示的な実施形態を図示する。図8は、例示的

50

な目的でのみ示され、本開示の範囲を限定することを意図しないことに留意する必要がある。図8の特定の素子の機能は、前述の説明を鑑みると明らかであり、そのような機能の説明はしたがって説明を容易にするために以下では省略され得ることが理解されるべきである。

#### 【0050】

[0058] 図8において、装置800は、アンテナ301.5の素子をサポートする基板212により別な方法で(otherwise)専有され得るエリア810を含む。エリア810は、装置800の追加のモジュールが提供され得る基板212のくり抜かれた部分を表す。例えば、マイクロフォン、スピーカー、USBコネクタ等は、したがって、アンテナ301.5により専有された装置800の同一のエリアに統合され得る。ある例示的な実施形態において、そのような追加のコンポーネントがこの方式でアンテナ空間に挿入されるとき、アンテナ性能におけるいくらかの劣化が生じ得る。しかしながら、そのような劣化は、特定のアプリケーションにおける設計トレードオフとして許容され得ることが理解されるべきである。10

#### 【0051】

[0059] 図9は、本開示にしたがう方法900の例示的な実施形態を図示する。方法900は、例示的な目的のみのために提示され、本開示の範囲を限定するようには意図されていないことに留意する必要がある。

#### 【0052】

[0060] 図9において、ブロック910において、信号は、第1のモノポール素子から第1の接地されたプランチに容量結合される。20

#### 【0053】

[0061] ブロック920において、信号は、第2のモノポール素子から第2の接地されたプランチに容量結合される。

#### 【0054】

[0062] ブロック930において、第1および第2のプランチは、第1および第2のモノポール素子間に配置された単一の接続ストリップを介して、互いに、および接地素子に容量結合される。

#### 【0055】

[0063] 例示的な構成が、例えば、比較的短い接地ストリップ322および2つのプランチ310a、310bを含む接地構造310について列挙され、説明されてきたが、代替的な例示的な実施形態が、第1のモノポールアンテナ素子330および第2のモノポールアンテナ素子332の両方に共有された容量結合を維持する接地された素子のための任意の形状を一般的に採用し得ることに留意する必要がある。さらに、プランチ310a、310bは、パターン化導電設計を含んでいるとして本明細書においてある特定の図として図示されてきたが、示されたパターン化設計は、代替的な例示的な実施形態において、パターン化されていない形状、例えばパターン化されていない導電板(conducting sheet)（例えば、単純な長方形の形状を有する、等）、により置き換えられ得る。そのような代替的な例示的な実施形態は、本開示の範囲内であると考慮される。30

#### 【0056】

[0064] 本開示の技法が、例えば、5インチフォン、小さな電話、薄い電話等、異なる電話プラットフォームに適用し得ることが理解されるべきである。例えば、ある特定の例示的な実施形態において、より大きなまたはより小さなサイズの寸法をもつブロードバンドアンテナが、開示された技法にしたがって設計され得る。さらに、本開示の技法は、2つのアンテナモジュールに限定されない。例えば、tri-fedおよびquad-fedアンテナモジュールも設計され得る。例えば、それにもかかわらず単一の共通の接地構造を共有する、追加の給電および放射構造（例えば、上述された2つのモノポール素子を超える）が提供され得る。そのような代替的な例示的な実施形態は、本開示の範囲内であると考慮される。40

#### 【0057】

[0065] 本明細書および特許請求の範囲では、要素が別の要素に「接続される」または「結合される」として言及されるとき、それは他の要素に直接接続、または結合されることができるまたは介在する要素が存在し得ることは理解されるだろう。対照的に、要素が別の要素に「直接接続される」または「直接結合される」として言及されるとき、どの介在する要素も存在しない。さらに、要素が別の要素に「電気的に結合される」として称されるときに低抵抗のパスがそのような要素間に存在する一方で、要素が単に別の要素に「結合される」として言及されるときは、そのような要素間に低抵抗のパスが存在することも、または存在しないこともある。

#### 【0058】

[0066] 当業者であれば、情報および信号は、様々な異なる技術および技法のうちのいずれかを用いて表され得ることを理解するであろう。例えば、上記説明の全体にわたって参考され得るデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場または磁性粒子、光場または光粒子、あるいはこれらの任意の組み合わせによって表され得る。 10

#### 【0059】

[0067] 当業者はさらに、本明細書に開示された例示的な態様と関連して説明される様々な例示的な論理ブロック、モジュール、回路、アルゴリズムステップが電子ハードウェア、コンピュータソフトウェアまたは両方の組み合わせとして実現され得ることを認識するであろう。ハードウェアおよびソフトウェアのこの互換性を明確に説明するために、様々な例示的なコンポーネント、ブロック、モジュール、回路、およびステップが、それらの機能の観点で一般的に上述してきた。このような機能が、ハードウェアとして実現されるか、あるいはソフトウェアとして実現されるかは、特定のアプリケーションおよびシステム全体に課せられる設計制約に依存する。当業者は、各特定のアプリケーションに関して、多様な方法で、説明された機能を実現し得るが、このような実現の決定は、本発明の例示的な実施形態の範囲から逸脱を引き起こしていると解釈されるべきでない。 20

#### 【0060】

[0068] ここに開示された例示的な実施形態に関連して説明された様々な例示的な論理ブロック、モジュール、および回路は、汎用プロセッサ、デジタル信号プロセッサ（D S P）、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）、または他のプログラマブル論理デバイス、ディスクリートゲートまたはトランジスタロジック、ディスクリートハードウェアコンポーネント、あるいはここに説明された機能を実行するように設計されるこれらの任意の組み合わせで、実現または実行され得る。汎用プロセッサは、マイクロプロセッサであり得るが、代替において、このプロセッサは、任意の従来型のプロセッサ、コントローラ、マイクロコントローラ、またはステートマシン（state machine）であり得る。プロセッサはまた、例えば、D S Pとマイクロプロセッサの組み合わせ、複数のマイクロプロセッサ、D S Pコアと連携した1つまたはそれ以上のマイクロプロセッサ、あるいはその他任意のこののような構成であるコンピュティングデバイスの組み合わせとして実現され得る。 30

#### 【0061】

[0069] ここに開示された例示的な態様に関連して説明されたアルゴリズムまたは方法のステップは、直接ハードウェアにおいて、プロセッサによって実行されるソフトウェアモジュールにおいて、またはこれら2つの組み合わせにおいて、具現化され得る。ソフトウェアモジュールは、ランダムアクセスメモリ（R A M）、フラッシュメモリ、読み出し専用メモリ（R O M）、電気的プログラマブルR O M（E P R O M）、電気的消去可能プログラマブルR O M（E E P R O M（登録商標））、レジスタ、ハードディスク、リムーバルディスク、C D - R O M、または当該技術分野において周知であるその他任意の形状の記憶媒体において存在し得る。例示的な記憶媒体は、プロセッサがこの記憶媒体から情報を読み取り、またこの記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。あるいは、記憶媒体は、プロセッサに組み込まれ得る。プロセッサと記憶媒体は、A S I Cにおいて存在し得る。A S I Cは、ユーザ端末に存在していてもよい。代替 40

において、プロセッサおよび記憶媒体は、ユーザ端末内にディスクリートコンポーネントとして存在し得る。

**【0062】**

[0070] 1つまたはそれ以上の例示的な態様では、説明された機能は、ハードウェア、ソフトウェア、ファームウェア、またはこれらの任意の組み合わせで実現され得る。ソフトウェアで実現される場合、機能は、コンピュータ読み取り可能な媒体上で、1つまたはそれ以上の命令またはコードとして、記憶または伝送することができる。コンピュータ可読媒体は、1つの場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体とコンピュータ記憶媒体との両方を含む。記憶媒体は、コンピュータによってアクセスされ得る任意の利用可能な媒体であり得る。限定ではなく例として、このようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMまたは他の光ディスク記憶装置、磁気ディスク記憶装置またはその他の磁気記憶デバイス、あるいは、データ構造または命令の形式で所望のプログラムコードを記憶または伝送するために使用可能であり、かつコンピュータによってアクセスされ得るその他任意の媒体を備えうる。また、任意の接続は、コンピュータ読み取り可能な媒体と厳密には称される。例えば、ソフトウェアが、ウェブサイト、サーバ、または他のリモートソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(DSL)、または赤外線、無線、およびマイクロ波のようなワイヤレス技術を使用して伝送される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波のようなワイヤレス技術は、媒体の定義に含まれる。ここで使用される場合、ディスク(disk)およびディスク(disc)は、コンパクトディスク(CD)、レーザーディスク(登録商標)、光ディスク、デジタル多目的ディスク(DVD)、フロッピー(登録商標)ディスクおよびブルーレイ(登録商標)ディスクを含み、ここでディスク(disks)は、通常磁気的にデータを再生し、一方ディスク(discs)は、レーザーを用いて光学的にデータを再生する。上記の組み合わせは、また、コンピュータ読み取り可能な媒体の範囲内に含まれるべきである。10

**【0063】**

[0071] 開示された例示的な実施形態の上記説明は、いかなる当業者であっても、本発明の製造または使用を可能にするように提供される。これらの例示的な態様に対する様々な変更は当業者に容易に明らかとなり、ここに定義された一般的な原理は、本開示の趣旨または範囲を逸脱することなく、他の態様に適用され得る。したがって、本開示は、ここに示された例示的な態様に限定されるようには意図されず、ここに開示される原理および新規な特徴と一致する最も広い範囲を与えられることとなる。30

以下に、本願の出願当初の特許請求の範囲に記載された発明を付記する。

**[C1]**

第1のモノポール素子と、

第2のモノポール素子と、

前記第1および第2のモノポール素子の両方に容量結合された共通構造と、

前記共通構造を接地素子に導電結合するように構成された接続ストリップと、ここにおいて、前記接続ストリップは、前記第1および第2のモノポール素子の間に位置する、を備える、装置。40

**[C2]**

ボードをさらに備え、前記第1および第2のモノポール素子は、前記ボードの反対側に配置されている、C1に記載の装置。

**[C3]**

前記第1および第2のモノポール素子は、前記ボードの端上に位置する、C2に記載の装置。

**[C4]**

前記共通構造は、接続点によって結合された第1および第2のブランチを備え、前記第1および第2のブランチは、それぞれ、前記第1および第2のモノポール素子に容量結合50

されている、C 1 に記載の装置。

[ C 5 ]

前記第 1 および第 2 のプランチのうちの少なくとも 1 つは、パターン化導電素子を備える、C 1 に記載の装置。

[ C 6 ]

前記モノポール素子および前記接続ストリップの間の空間を満たすFR4 基板をさらに備える、C 1 に記載の装置。

[ C 7 ]

前記第 1 および第 2 のモノポール素子の各々は、それぞれの駆動ポートにそれぞれの短い伝導性ストリップにより結合された、C 1 に記載の装置。

10

[ C 8 ]

前記短い導電ストリップおよび前記接続ストリップは、前記第 1 および前記第 2 のモノポール素子が提供されている水平面上に垂直な垂直面上に位置している、C 7 に記載の装置。

[ C 9 ]

前記共通構造は、前記垂直面上に位置している部分および前記水平面上に位置している部分を備える、C 8 に記載の装置。

[ C 10 ]

前記共通構造は、前記 2 つのモノポール素子と比べてかなり大きなサイズを有する、C 1 に記載の装置。

20

[ C 11 ]

前記モノポール素子および共通構造により占有されたのと同じボリュームで提供された追加のモジュールをさらに備える、C 1 に記載の装置。

[ C 12 ]

前記追加のモジュールは、USB コネクタを備える、C 11 に記載の装置。

[ C 13 ]

第 1 のモノポール素子から第 1 のプランチに信号を容量結合するための手段と、

第 2 のモノポール素子から第 2 のプランチに信号を容量結合するための手段と、

前記第 1 および第 2 のモノポール素子の間に配置された接続ストリップを介して前記第 1 および第 2 のプランチを互いにおよび接地素子に導電結合するための手段と、を備える、装置。

30

[ C 14 ]

1 つのポート励起スキームにしたがって前記第 1 および第 2 のモノポール素子を駆動するための手段をさらに備える、C 13 に記載の装置。

[ C 15 ]

前記第 1 および第 2 のプランチのうちの少なくとも 1 つは、パターン化導電素子を備える、C 13 に記載の装置。

[ C 16 ]

導電結合するための前記手段は、前記接続ストリップに隣接して提供されている、C 1 3 に記載の装置。

40

[ C 17 ]

第 1 のモノポール素子から第 1 の接地されたプランチに信号を容量結合することと、

第 2 のモノポール素子から第 2 の接地されたプランチに信号を容量結合することと、

前記第 1 および第 2 のモノポール素子の間に配置された単一の接続ストリップを介して前記第 1 および第 2 のプランチを互いにおよび接地素子に導電結合することと、を備える、方法。

[ C 18 ]

1 つのポート励起スキームにしたがって前記第 1 および第 2 のモノポール素子を駆動することをさらに備える、C 17 に記載の方法。

[ C 19 ]

50

前記第1および第2のブランチのうちの少なくとも1つは、パターン化導電素子を備える、C 17に記載の方法。

【C 20】

前記第1の接地されたブランチは、前記接続ストリップに隣接した短いストリップにより前記第2の接地されたブランチに導電結合される、C 17に記載の方法。

【図1】

【図2】

FIG 2

【図3】

FIG 3

【図4】

FIG 4

【図5A】

FIG 5A

【図5B】

FIG 5B

【図 6 A】

【図 6 B】

FIG 6B

FIG 6A

【図 6 C】

【 図 7 】

FIG 7

【図8】

【図9】

FIG 8

FIG 9

---

フロントページの続き

(72)発明者 ドン、ヤンダン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 シ、グウイニン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 トラン、アレン・ミン - トリエット

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 佐藤 当秀

(56)参考文献 國際公開第2013/077302 (WO, A1)

特表2007-524310 (JP, A)

特開2012-178810 (JP, A)

特開2014-068233 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01Q 1/00 - 1/52

H01Q 5/00 - 9/46